JP5917543B2 - 複数の複数コーナー複数モードのシナリオにおける設計要求違反を修正する方法および装置 - Google Patents

複数の複数コーナー複数モードのシナリオにおける設計要求違反を修正する方法および装置 Download PDFInfo

- Publication number

- JP5917543B2 JP5917543B2 JP2013539990A JP2013539990A JP5917543B2 JP 5917543 B2 JP5917543 B2 JP 5917543B2 JP 2013539990 A JP2013539990 A JP 2013539990A JP 2013539990 A JP2013539990 A JP 2013539990A JP 5917543 B2 JP5917543 B2 JP 5917543B2

- Authority

- JP

- Japan

- Prior art keywords

- scenario

- design

- value

- eco

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/32—Circuit design at the digital level

- G06F30/327—Logic synthesis; Behaviour synthesis, e.g. mapping logic, HDL to netlist, high-level language to RTL or netlist

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

本開示は、電子設計自動化(EDA)に関連する。より具体的には、本開示は、複数の複数コーナー複数モードのシナリオにおける設計要求違反を修正するシステムおよび技術に関連する。

(関連技術)

コンピュータ技術の急速な進歩は、時には何兆バイトほどに大きいデータセット上で毎秒何兆ものコンピュータによる動作を行うことを可能にしてきた。これらの進歩は、主として、集積回路のサイズおよび複雑性の指数関数的増加が原因でありうる。

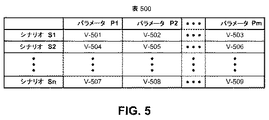

本発明の一実施形態は、複数のシナリオにおいて回路設計の設計要求違反を修正するシステムを提供する。動作中、システムは、シナリオイメージおよび複数シナリオECO(engineering change order)データベースを受け取りうる。シナリオイメージは、シナリオにおける回路対象についてのパラメータの値を記憶しえ、複数シナリオECOデータベースは、複数のシナリオにおける回路対象の下位セットについてのパラメータの値の下位セットを記憶しうる。各々のシナリオは、工程コーナー、動作条件、または動作モードのうちの1つ以上と関連づけられうる。次に、システムは、1つ以上の設計要求違反を修正するECOを決定しえ、その決定することは、シナリオイメージおよび複数シナリオECOデータベース内に記憶されたパラメータの値に基づいて、複数のシナリオにおける回路対象についてのパラメータの値を推定することを含みうる。本開示において、別な方法で述べられない限り、「基づく」という句は、「単にまたは部分的に基づく」を意味する。

以下の説明は、当業者の誰もが本発明を生産し、かつ使用することができるように与えられ、特定の用途およびその要求の文脈において提供される。開示された実施形態に対する種々の改変は、当業者にとって容易に明白であり、本明細書中に定義される概括的な原理は、本発明の精神および範囲から逸脱することなく、他の実施形態および用途に応用されうる。したがって、本発明は、示される実施形態に制限されずに、本明細書中に開示される原理および特徴と一致する最も広い範囲を授けられる。

上記の説明は、当業者の誰もが実施形態を生産し、かつ使用することができるように与えられる。開示された実施形態に対する種々の改変は、当業者にとって容易に明白であり、本明細書中に定義される概括的な原理は、本開示の精神および範囲から逸脱することなく、他の実施形態および用途に応用できる。したがって、本発明は、示される実施形態に制限されずに、本明細書に開示される原理および特徴と一致する最も広い範囲を授けられる。

Claims (24)

- 複数のシナリオにおいて回路設計の設計要求違反を修正する方法であって、該方法は、

シナリオイメージを受信することを含み、該シナリオイメージは、シナリオにおける回路対象についてのパラメータの値を記憶しており、

複数シナリオECO(engineering change order)データベースを受信することを含み、該複数シナリオECOデータベースは、前記複数のシナリオにおける回路対象の下位セットについてのパラメータの値の下位セットを記憶しており、

1つ以上のプロセッサによって1つ以上の設計要求違反を修正するECOを決定することとを含み、該決定することは、該シナリオイメージおよび該複数シナリオECOデータベース内に記憶されたパラメータの値に基づいて、前記複数のシナリオの少なくともいくつかにおける回路対象についてのパラメータの値を推定することを含む、

方法。 - 前記複数のシナリオにおける各々のシナリオは、工程コーナー、動作条件、または動作モードのうちの1つ以上と関連づけられる、請求項1に記載の方法。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでのタイミングスラックの値を含む、請求項1に記載の方法。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでの容量性負荷の値を含む、請求項1に記載の方法。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでの遷移時間の値を含む、請求項1に記載の方法。

- 前記パラメータの値は、前記回路設計におけるゲートについての漏れ電力の値を含む、請求項1に記載の方法。

- 前記1つ以上の設計要求違反は、セットアップタイミング違反を含む、請求項1に記載の方法。

- 前記1つ以上の設計要求違反は、ホールドタイミング違反を含む、請求項1に記載の方法。

- 前記1つ以上の設計要求違反は、電気的設計規則違反を含む、請求項1に記載の方法。

- 前記1つ以上の設計要求違反は、電力バジェット違反を含む、請求項1に記載の方法。

- コンピュータ読み取り可能なプログラムであって、コンピュータにより実行されるとき、該コンピュータに、複数のシナリオにおいて回路設計の設計要求違反を修正する方法を行わせ、該方法は、

シナリオイメージを受け取ることであって、該シナリオイメージは、シナリオにおける回路対象についてのパラメータの値を記憶する、ことと、

複数シナリオECO(engineering change order)データベースを受け取ることであって、該複数シナリオECOデータベースは、前記複数のシナリオにおける回路対象の下位セットについてのパラメータの値の下位セットを記憶する、ことと、

1つ以上の設計要求違反を修正するECOを決定することとを含み、該決定することは

、該シナリオイメージおよび該複数シナリオECOデータベース内に記憶されたパラメータの値を使用して、前記複数のシナリオの少なくともいくつかにおける回路対象についてのパラメータの値を推定することを含む、

コンピュータ読み取り可能なプログラム。 - 各々のシナリオは、工程コーナー、動作条件、または動作モードのうちの1つ以上と関連づけられる、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでのタイミングスラックの値を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでの容量性負荷の値を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記パラメータの値は、前記回路設計における1つ以上のピンでの遷移時間の値を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記パラメータの値は、前記回路設計におけるゲートについての漏れ電力の値を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記1つ以上の設計要求違反は、セットアップタイミング違反を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記1つ以上の設計要求違反は、ホールドタイミング違反を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記1つ以上の設計要求違反は、電気的設計規則違反を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- 前記1つ以上の設計要求違反は、電力バジェット違反を含む、請求項11に記載のコンピュータ読み取り可能なプログラム。

- システムであって、該システムは、

プロセッサーと、

メモリーとを含み、該メモリーは、

シナリオイメージであって、該シナリオイメージは、シナリオにおける回路対象についてのパラメータの値を記憶する、シナリオイメージと、

複数シナリオECO(engineering change order)データベースであって、該複数シナリオECOデータベースは、前記複数のシナリオにおける回路対象の下位セットについてのパラメータの値の下位セットを記憶する、複数シナリオECOデータベースと、

命令とを記憶し、該命令は、該プロセッサーにより実行されるとき、該システムに、1つ以上の設計要求違反を修正するECOを決定させ、該決定することは、該シナリオイメージおよび該複数シナリオECOデータベース内に記憶されたパラメータの値を使用して、前記複数のシナリオの少なくともいくつかにおける回路対象についてのパラメータの値を推定することを含む、

システム。 - 前記複数のシナリオにおける各々のシナリオは、工程コーナー、動作条件、または動作モードのうちの1つ以上と関連づけられる、請求項21に記載のシステム。

- 前記パラメータの値は、

前記回路設計における1つ以上のピンでのタイミングスラックの値と、

前記回路設計における1つ以上のピンでの容量性負荷の値と、

前記回路設計における1つ以上のピンでの遷移時間の値と、

前記回路設計におけるゲートについての漏れ電力の値と、のうちの1つ以上を含む、請求項21に記載のシステム。 - 前記1つ以上の設計要求違反は、

セットアップタイミング違反と、

ホールドタイミング違反と、

電気的設計規則違反と、

電力バジェット違反とのうちの1つ以上を含む、請求項21に記載のシステム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/949,689 | 2010-11-18 | ||

| US12/949,689 US8407655B2 (en) | 2010-11-18 | 2010-11-18 | Fixing design requirement violations in multiple multi-corner multi-mode scenarios |

| PCT/US2011/061086 WO2012068314A1 (en) | 2010-11-18 | 2011-11-16 | Method and apparatus for fixing design requirement violations in multiple multi-corner multi-mode scenarios |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014501968A JP2014501968A (ja) | 2014-01-23 |

| JP5917543B2 true JP5917543B2 (ja) | 2016-05-18 |

Family

ID=46065614

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013539990A Active JP5917543B2 (ja) | 2010-11-18 | 2011-11-16 | 複数の複数コーナー複数モードのシナリオにおける設計要求違反を修正する方法および装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8407655B2 (ja) |

| JP (1) | JP5917543B2 (ja) |

| WO (1) | WO2012068314A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9053264B2 (en) * | 2011-03-16 | 2015-06-09 | Synopsys, Inc. | What-if simulation methods and systems |

| US8875082B1 (en) * | 2012-12-28 | 2014-10-28 | Cadeńce Design Systems, Inc. | System and method for detecting and prescribing physical corrections for timing violations in pruned timing data for electronic circuit design defined by physical implementation data |

| US9026965B2 (en) | 2013-03-12 | 2015-05-05 | Synopsys, Inc. | Arrival edge usage in timing analysis |

| US9280630B1 (en) | 2014-11-07 | 2016-03-08 | International Business Machines Corporation | Modified standard cells to address fast paths |

| US10339258B2 (en) * | 2015-06-30 | 2019-07-02 | Synopsys, Inc. | Look-ahead timing prediction for multi-instance module (MIM) engineering change order (ECO) |

| US10691854B1 (en) * | 2018-11-13 | 2020-06-23 | Avatar Integrated Systems, Inc. | Graph-based timing analysis timing calibration |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5018215A (en) * | 1990-03-23 | 1991-05-21 | Honeywell Inc. | Knowledge and model based adaptive signal processor |

| JPH10321725A (ja) * | 1997-05-14 | 1998-12-04 | Toshiba Corp | 半導体集積回路の設計方法及び装置 |

| US7315990B2 (en) | 2004-01-12 | 2008-01-01 | International Business Machines Corporation | Method and system for creating, viewing, editing, and sharing output from a design checking system |

| US7331028B2 (en) | 2004-07-30 | 2008-02-12 | Lsi Logic Corporation | Engineering change order scenario manager |

| US7454731B2 (en) * | 2006-09-22 | 2008-11-18 | Synopsys, Inc. | Generation of engineering change order (ECO) constraints for use in selecting ECO repair techniques |

| JP5041882B2 (ja) * | 2007-06-07 | 2012-10-03 | ルネサスエレクトロニクス株式会社 | 半導体集積回路の設計方法及び設計支援装置 |

| JP2009163490A (ja) * | 2008-01-07 | 2009-07-23 | Fujitsu Microelectronics Ltd | 集積回路のタイミング調整方法、及びそのコンピュータプログラム |

| US20100153897A1 (en) | 2008-12-11 | 2010-06-17 | Lsi Corporation | System and method for employing signoff-quality timing analysis information concurrently in multiple scenarios to reduce leakage power in an electronic circuit and electronic design automation tool incorporating the same |

-

2010

- 2010-11-18 US US12/949,689 patent/US8407655B2/en active Active

-

2011

- 2011-11-16 WO PCT/US2011/061086 patent/WO2012068314A1/en not_active Ceased

- 2011-11-16 JP JP2013539990A patent/JP5917543B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2012068314A1 (en) | 2012-05-24 |

| JP2014501968A (ja) | 2014-01-23 |

| US20120131525A1 (en) | 2012-05-24 |

| US8407655B2 (en) | 2013-03-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102324782B1 (ko) | 집적 회로의 정적 타이밍 분석 방법 | |

| US8266570B2 (en) | Density-based area recovery in electronic design automation | |

| JP5917543B2 (ja) | 複数の複数コーナー複数モードのシナリオにおける設計要求違反を修正する方法および装置 | |

| US8413099B2 (en) | Performing scenario reduction | |

| US10318684B2 (en) | Network flow based framework for clock tree optimization | |

| US8869091B2 (en) | Incremental clock tree synthesis | |

| Han et al. | A global-local optimization framework for simultaneous multi-mode multi-corner clock skew variation reduction | |

| US9183335B2 (en) | Dynamic power driven clock tree synthesis (CTS) | |

| US9141742B2 (en) | Priori corner and mode reduction | |

| US11003821B1 (en) | Deterministic loop breaking in multi-mode multi-corner static timing analysis of integrated circuits | |

| US12073159B2 (en) | Computing device and method for detecting clock domain crossing violation in design of memory device | |

| US9390222B2 (en) | Determining a set of timing paths for creating a circuit abstraction | |

| US9064073B2 (en) | Hyper-concurrent optimization over multi-corner multi-mode scenarios | |

| US10339258B2 (en) | Look-ahead timing prediction for multi-instance module (MIM) engineering change order (ECO) | |

| US9047426B2 (en) | Performing scenario reduction in a circuit design flow | |

| US8418116B2 (en) | Zone-based optimization framework for performing timing and design rule optimization | |

| US8527927B2 (en) | Zone-based area recovery in electronic design automation | |

| US8707241B2 (en) | Performing scenario reduction using a dominance relation on a set of corners | |

| US8762915B1 (en) | System and method for integrated circuit die size reduction | |

| US10628545B2 (en) | Providing guidance to an equivalence checker when a design contains retimed registers | |

| US20180173818A1 (en) | Exact delay synthesis |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140821 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20150414 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20150416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20150414 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150929 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20151225 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160128 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160322 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160406 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5917543 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |