JP5904240B2 - A / D conversion circuit, electronic device, and A / D conversion method - Google Patents

A / D conversion circuit, electronic device, and A / D conversion method Download PDFInfo

- Publication number

- JP5904240B2 JP5904240B2 JP2014155183A JP2014155183A JP5904240B2 JP 5904240 B2 JP5904240 B2 JP 5904240B2 JP 2014155183 A JP2014155183 A JP 2014155183A JP 2014155183 A JP2014155183 A JP 2014155183A JP 5904240 B2 JP5904240 B2 JP 5904240B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- code

- conversion

- signal

- successive approximation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Analogue/Digital Conversion (AREA)

Description

本発明は、A/D変換回路、電子機器及びA/D変換方法等に関する。 The present invention relates to an A / D conversion circuit, an electronic device, an A / D conversion method, and the like.

従来より、アナログ信号をデジタルデータに変換するA/D変換回路として、逐次比較型のA/D変換回路が知られている。この逐次比較型のA/D変換回路は、比較回路と、逐次比較レジスターと、D/A変換回路を備え、入力信号をサンプリング(サンプル・ホールド)した信号を逐次比較動作によりA/D変換することでデジタルデータを出力する。このような逐次比較型のA/D変換回路の従来技術としては特許文献1等に開示される技術が知られている。

Conventionally, a successive approximation type A / D conversion circuit is known as an A / D conversion circuit for converting an analog signal into digital data. This successive approximation type A / D conversion circuit includes a comparison circuit, a successive approximation register, and a D / A conversion circuit, and performs A / D conversion on a signal obtained by sampling (sample-holding) an input signal by a successive approximation operation. To output digital data. As a conventional technique of such a successive approximation type A / D conversion circuit, a technique disclosed in

このようなA/D変換回路では、その変換精度の大部分はD/A変換回路の精度に依存する。そして、D/A変換回路の精度を高めようとすると、キャパシタの面積(電荷再分配型の場合)が抵抗の面積(ラダー抵抗型の場合)が要因となって、回路が大規模化してしまう。一方、回路の大規模化を抑制するために、D/A変換回路の回路に工夫を加えると、今度は、微分非直線性であるDNL(Differential Non Linearity)や積分非直線性であるINL(Integral Non Linearity)の誤差が原因で、いわゆるミッシングコードが発生するなどの問題が生じる。 In such an A / D conversion circuit, most of the conversion accuracy depends on the accuracy of the D / A conversion circuit. When trying to increase the accuracy of the D / A conversion circuit, the area of the capacitor (in the case of the charge redistribution type) is caused by the area of the resistor (in the case of the ladder resistance type), and the circuit becomes large in scale. . On the other hand, if the circuit of the D / A converter circuit is devised in order to suppress an increase in the scale of the circuit, this time, DNL (Differential Non Linearity) which is differential nonlinearity or INL (which is integral nonlinearity) Due to the error of Integral Non Linearity, problems such as so-called missing codes occur.

また、このようなDNLやINLなどのA/D変換特性が改善したとしても、A/D変換のダイナミックレンジが減少してしまうと、A/D変換に求められる性能としては望ましくない。 Even if the A / D conversion characteristics such as DNL and INL are improved, if the dynamic range of A / D conversion decreases, the performance required for A / D conversion is not desirable.

本発明の幾つかの態様によれば、A/D変換特性を改善しながらダイナミックレンジの減少も抑止できるA/D変換回路、電子機器、A/D変換方法等を提供できる。 According to some aspects of the present invention, it is possible to provide an A / D conversion circuit, an electronic device, an A / D conversion method, and the like that can improve the A / D conversion characteristics and suppress a decrease in dynamic range.

本発明の一態様は、比較回路と、前記比較回路からの比較結果信号によりレジスター値が設定される逐次比較レジスターを有し、逐次比較用データを出力する制御回路と、前記制御回路からの前記逐次比較用データをD/A変換して、前記逐次比較用データに対応するD/A出力信号を出力する第1のD/A変換回路と、時間的に変化するコードデータをD/A変換して、前記コードデータに対応するコード信号を出力する第2のD/A変換回路と、補正処理を行う補正部とを含み、前記比較回路は、入力信号のサンプリング信号と前記コード信号の加算信号と、前記D/A出力信号とを比較する処理、或いは前記サンプリング信号と、前記D/A出力信号と前記コード信号の加算信号とを比較する処理を行い、前記制御回路は、前記逐次比較レジスターの逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記入力信号のA/D変換データとして出力し、前記補正部は、前記コードデータを用いたコードシフトにより前記逐次比較結果データがオーバーフローするのを補正する補正処理を行うA/D変換回路に関係する。 One embodiment of the present invention includes a comparison circuit, a successive approximation register in which a register value is set by a comparison result signal from the comparison circuit, a control circuit that outputs successive comparison data, and the control circuit A first D / A conversion circuit for D / A converting the successive approximation data and outputting a D / A output signal corresponding to the successive approximation data, and D / A conversion of code data that changes over time A second D / A conversion circuit that outputs a code signal corresponding to the code data, and a correction unit that performs correction processing, and the comparison circuit adds the sampling signal of the input signal and the code signal A process for comparing a signal with the D / A output signal, or a process for comparing the sampling signal with an addition signal of the D / A output signal and the code signal. Output data obtained based on the successive comparison result data of the register and the code data is output as A / D conversion data of the input signal, and the correction unit performs the successive comparison result by code shift using the code data. The present invention relates to an A / D conversion circuit that performs correction processing for correcting overflow of data.

本発明の一態様によれば、逐次比較レジスターを有する制御回路からの逐次比較用データが第1のD/A変換回路に入力されて、逐次比較用データに対応するD/A出力信号が出力される。また時間的に変化するコードデータが第2のD/A変換回路に入力されて、コードデータに対応するコード信号が出力される。そして入力信号のサンプリング信号とコード信号の加算信号と、D/A出力信号とを比較する処理、或いはサンプリング信号と、D/A出力信号とコード信号の加算信号とを比較する処理が行われる。そして逐次比較結果データとコードデータとに基づき求められる出力データが、入力信号のA/D変換データとして出力される。このようにすれば、時間的に変化するコードデータによりコードシフトが行われるようになり、A/D変換特性を改善できる。 According to one aspect of the present invention, the successive approximation data from the control circuit having the successive approximation register is input to the first D / A conversion circuit, and the D / A output signal corresponding to the successive approximation data is output. Is done. Also, code data that changes with time is input to the second D / A conversion circuit, and a code signal corresponding to the code data is output. Then, a process of comparing the sampling signal of the input signal and the addition signal of the code signal and the D / A output signal or a process of comparing the sampling signal and the addition signal of the D / A output signal and the code signal is performed. Then, output data obtained based on the successive comparison result data and the code data is output as A / D conversion data of the input signal. In this way, code shift is performed by code data that changes over time, and the A / D conversion characteristics can be improved.

更に本発明の一態様によれば、このようなコードデータを用いたコードシフトにより逐次比較結果データがオーバーフローしてしまうのを、補正処理により抑止できる。従って、コードシフトによりA/D変換特性を改善しながら、コードシフトによるダイナミックレンジの減少も抑止することが可能になる。 Furthermore, according to an aspect of the present invention, it is possible to prevent the sequential comparison result data from overflowing due to the code shift using such code data by the correction process. Accordingly, it is possible to suppress a decrease in dynamic range due to code shift while improving A / D conversion characteristics by code shift.

また本発明の一態様では、前記第1のD/A変換回路の最小分解能をRS1、前記第2のD/A変換回路の最小分解能をRS2とした場合に、RS2≧RS1であってもよい。 In the aspect of the present invention, RS2 ≧ RS1 may be satisfied when the minimum resolution of the first D / A converter circuit is RS1 and the minimum resolution of the second D / A converter circuit is RS2. .

このようにすれば、第1のD/A変換回路の最小分解能RS1以上の大きさのコード信号の加算処理を行って、コードシフトを実現できるようになる。 In this way, the code shift can be realized by performing the addition process of the code signal having a magnitude equal to or larger than the minimum resolution RS1 of the first D / A conversion circuit.

また本発明の一態様では、前記補正部は、前記コードデータを補正することで前記補正処理を行ってもよい。 In the aspect of the invention, the correction unit may perform the correction process by correcting the code data.

このようにすれば、コードシフトによるダイナミックレンジの減少を抑止する補正処理を、コードデータを補正するという簡素な処理で実現することが可能になる。 In this way, it is possible to realize the correction process for suppressing the decrease in the dynamic range due to the code shift by a simple process of correcting the code data.

また本発明の一態様では、前記補正部は、前回のA/D変換での逐次比較結果データである前回逐次比較結果データに基づき前記コードデータを補正することで、前記補正処理を行ってもよい。 In the aspect of the invention, the correction unit may perform the correction process by correcting the code data based on the previous successive comparison result data that is the successive comparison result data in the previous A / D conversion. Good.

このようにすれば、前回のA/D変換での逐次比較結果データを利用し、今回のA/D変換での逐次比較結果データがオーバーフローするかどうかを予測することで、コードシフトによるダイナミックレンジの減少を抑止する補正処理を実現できるようになる。 In this way, by using the successive approximation result data in the previous A / D conversion and predicting whether or not the successive approximation result data in the current A / D conversion overflows, the dynamic range by the code shift is determined. It is possible to realize a correction process that suppresses a decrease in the amount of noise.

また本発明の一態様では、前記補正部は、前記前回逐次比較結果データが、A/D入力電圧範囲の高電位側の第1の範囲に対応するデータである場合には、今回のA/D変換での前記逐次比較結果データが低電位側にシフトするように、前記コードデータの補正処理を行い、前記前回逐次比較結果データが、前記A/D入力電圧範囲の低電位側の第2の範囲に対応するデータである場合には、今回のA/D変換での前記逐次比較結果データが高電位側にシフトするように、前記コードデータの補正処理を行ってもよい。 In the aspect of the invention, the correction unit may determine that the previous A / D input voltage range corresponds to the first range on the high potential side of the A / D input voltage range. The code data is corrected so that the successive approximation result data in D conversion is shifted to the low potential side, and the previous successive comparison result data is the second potential on the low potential side of the A / D input voltage range. If the data corresponds to the above range, the code data correction processing may be performed so that the successive comparison result data in the current A / D conversion is shifted to the high potential side.

このようにすれば、前回逐次比較結果データが高電位側の第1の範囲のデータである場合には、逐次比較結果データが低電位側にシフトするようにコードデータを補正することで、コードシフトによりダイナミックレンジが減少するを抑止できる。また前回逐次比較結果データが低電位側の第2の範囲のデータである場合には、逐次比較結果データが高電位側にシフトするようにコードデータを補正することで、コードシフトによりダイナミックレンジが減少するのを抑止できる。 In this way, when the previous successive approximation result data is data in the first range on the high potential side, the code data is corrected so that the successive approximation result data is shifted to the lower potential side, thereby The dynamic range can be prevented from decreasing due to the shift. When the previous successive approximation result data is data in the second range on the low potential side, the code range is corrected so that the successive approximation result data is shifted to the higher potential side, so that the dynamic range is increased by the code shift. Decrease can be suppressed.

また本発明の一態様では、前記コードデータを生成して前記第2のD/A変換回路に出力するコードデータ生成部を含み、前記コードデータ生成部は、前記前回逐次比較結果データが、前記第1の範囲と前記第2の範囲の間の第3の範囲に対応するデータである場合には、交互に正、負となる前記コードデータを生成して前記第2のD/A変換回路に出力してもよい。 Further, in one aspect of the present invention, a code data generation unit that generates the code data and outputs the code data to the second D / A conversion circuit, the code data generation unit includes the previous successive comparison result data, In the case of data corresponding to a third range between the first range and the second range, the code data that is alternately positive and negative is generated to generate the second D / A conversion circuit May be output.

このようにコードデータが交互に正、負になることで、コードデータの変化による周波数成分の影響を低減することができ、A/D変換特性への悪影響を抑止できる。 As described above, the code data alternately becomes positive and negative, so that the influence of the frequency component due to the change of the code data can be reduced, and the adverse effect on the A / D conversion characteristics can be suppressed.

また本発明の一態様では、前記補正部は、前記前回逐次比較結果データが、前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての情報を記憶する情報レジスターを含んでもよい。 In the aspect of the invention, the correction unit may include an information register that stores information about whether the previous successive approximation result data is data corresponding to the first range or the second range. But you can.

このようにすれば、情報レジスターに記憶された情報に基づいて、前回逐次比較結果データが第1の範囲又は第2の範囲に対応するデータであったか否かを判断して、今回のA/D変換でのコードデータを補正することが可能になる。 In this way, based on the information stored in the information register, it is determined whether or not the previous successive comparison result data was data corresponding to the first range or the second range, and the current A / D is determined. It becomes possible to correct the code data in the conversion.

また本発明の一態様では、前記情報レジスターは、複数のチャンネルの信号が時分割でA/D変換される場合に、前記複数のチャンネルの各チャンネルについて、前記前回逐次比較結果データが前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての前記情報を記憶してもよい。 In the aspect of the invention, the information register may include the first successive comparison result data for each channel of the plurality of channels when the signals of the plurality of channels are A / D converted in a time division manner. The information about whether the data corresponds to the range or the second range may be stored.

このようにすれば、複数のチャンネルの信号が時分割でA/D変換される場合にも、各チャンネルの前回逐次比較結果データが第1の範囲又は第2の範囲に対応するデータであったか否かを、情報レジスターに記憶された情報に基づき判断して、各チャンネルについてのコードデータを補正することが可能になる。 In this way, even when the signals of a plurality of channels are A / D converted in a time division manner, whether the previous successive comparison result data of each channel was data corresponding to the first range or the second range. This is determined based on the information stored in the information register, and the code data for each channel can be corrected.

また本発明の一態様では、前記コードデータを生成して、前記第2のD/A変換回路に対して出力するコードデータ生成部を含み、前記コードデータ生成部は、所定のデータ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるデータを、前記コードデータとして出力してもよい。 In one aspect of the present invention, a code data generation unit that generates the code data and outputs the code data to the second D / A conversion circuit is included. Data having a different value for each one or a plurality of A / D conversion timings may be output as the code data.

このようにすれば、1又は複数回のA/D変換タイミング毎に異なった値になるコードデータに対応するコード信号の加算処理が行われて、コードシフトが実現される。これにより、例えばDNL特性の悪化を周囲のコードに時間的に拡散させて、A/D変換特性を改善できる。 In this way, the code signal corresponding to the code data having a different value at every one or a plurality of A / D conversion timings is added, thereby realizing the code shift. Thereby, for example, the deterioration of the DNL characteristic can be diffused in the surrounding code over time, and the A / D conversion characteristic can be improved.

また本発明の一態様では、前記コードデータ生成部は、2のべき乗倍のオーバーサンプリングのA/D変換が行われる場合に、素数個のコードデータを生成して出力してもよい。 In one aspect of the present invention, the code data generation unit may generate and output a prime number of code data when an oversampling A / D conversion that is a power of 2 is performed.

このようにすれば、オーバーサンプリングとコードシフトの相乗効果によるA/D変換特性の向上を実現できるようになる。 In this way, it is possible to realize an improvement in A / D conversion characteristics by a synergistic effect of oversampling and code shift.

また本発明の一態様では、前記第1のD/A変換回路及び前記第2のD/A変換回路は、電荷再分配型のD/A変換回路であってもよい。 In the aspect of the invention, the first D / A conversion circuit and the second D / A conversion circuit may be a charge redistribution type D / A conversion circuit.

なお第1、第2のD/A変換回路の一部又は全部をラダー抵抗型で実現してもよい。 A part or all of the first and second D / A conversion circuits may be realized by a ladder resistance type.

また本発明の一態様では、前記第1のD/A変換回路は、前記比較回路の比較ノードに一端が接続される複数のキャパシタを有する第1のキャパシタアレイ部と、前記第1のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの上位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第1のスイッチアレイ部と、前記比較ノードと第1のノードとの間に設けられる第1の直列キャパシタと、前記第1のノードに一端が接続される複数のキャパシタを有する第2のキャパシタアレイ部と、前記第2のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの下位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第2のスイッチアレイ部を含み、前記第2のD/A変換回路は、前記比較ノードと第2のノードとの間に設けられる第2の直列キャパシタと、前記第2のノードに一端が接続される複数のキャパシタを有する第3のキャパシタアレイ部と、前記第3のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記コードデータに基づきスイッチ制御される複数のスイッチ素子を有する第3のスイッチアレイ部を含んでもよい。 In the aspect of the invention, the first D / A conversion circuit includes a first capacitor array unit having a plurality of capacitors, one end of which is connected to a comparison node of the comparison circuit, and the first capacitor array. A first switch array unit having a plurality of switch elements connected to the other ends of the plurality of capacitors of the unit and controlled to be switched based on upper bit data of the successive approximation data; the comparison node and the first node; A first series capacitor provided between the second capacitor array unit, a second capacitor array unit having a plurality of capacitors having one end connected to the first node, and the plurality of capacitors in the second capacitor array unit. And a second switch array unit having a plurality of switch elements connected to the ends and controlled to be switched based on the lower-order bit data of the successive approximation data. The second D / A conversion circuit includes a second series capacitor provided between the comparison node and the second node, and a plurality of capacitors having one end connected to the second node. And a third switch array unit having a plurality of switch elements connected to the other ends of the plurality of capacitors of the third capacitor array unit and controlled to be switched based on the code data. .

このような構成の第1のD/A変換回路を用いれば、回路面積の増加を最小限に抑えながら、A/D変換の高ビット化を図れる。またこのような構成の第2のD/A変換回路を用いれば、サンプリング信号と、D/A出力信号とコード信号の加算信号とを比較する処理を実現できる。 By using the first D / A conversion circuit having such a configuration, it is possible to increase the bit of A / D conversion while minimizing an increase in circuit area. Further, by using the second D / A conversion circuit having such a configuration, it is possible to realize processing for comparing the sampling signal, the D / A output signal, and the addition signal of the code signal.

また本発明の一態様では、前記制御回路は、前記サンプリング信号と前記コード信号の加算信号と、前記D/A出力信号との比較処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データから前記コードデータを減算する処理を行ってもよい。 In one aspect of the present invention, the control circuit may perform the successive approximation result of the successive approximation register when a comparison process is performed between the sampling signal and the addition signal of the code signal and the D / A output signal. A process of subtracting the code data from the data may be performed.

このようにすれば、サンプリング信号とコード信号の加算信号と、D/A出力信号との比較処理が行われる場合に、コードデータの減算処理を行うことで、適正なA/D変換データを出力できるようになる。 In this way, when comparison processing of the addition signal of the sampling signal and the code signal and the D / A output signal is performed, the code data is subtracted to output appropriate A / D conversion data. become able to.

また本発明の一態様では、前記制御回路は、前記サンプリング信号と、前記D/A出力信号と前記コード信号の加算信号との比較処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データに前記コードデータを加算する処理を行ってもよい。 In the aspect of the invention, the control circuit may perform the successive comparison result of the successive approximation register when the sampling signal is compared with the D / A output signal and the addition signal of the code signal. You may perform the process which adds the said code data to data.

このようにすれば、サンプリング信号と、D/A出力信号とコード信号の加算信号との比較処理が行われる場合に、コードデータの加算処理を行うことで、適正なA/D変換データを出力できるようになる。 In this way, when the comparison process of the sampling signal, the D / A output signal, and the addition signal of the code signal is performed, the code data addition process is performed to output appropriate A / D conversion data. become able to.

また本発明の他の態様は、上記のいずれかに記載のA/D変換回路を含む電子機器に関係する。 Another aspect of the invention relates to an electronic device including any of the A / D conversion circuits described above.

また本発明の他の態様は、比較回路と逐次比較レジスターとD/A変換回路を有する逐次比較型のA/D変換回路におけるA/D変換方法であって、時間的に変化するコードデータに対応するコード信号を生成し、入力信号のサンプリング信号と前記コード信号の加算信号と、前記D/A変換回路からのD/A出力信号とを比較する処理、或いは前記サンプリング信号と、前記D/A出力信号と前記コード信号の加算信号とを比較する処理を行い、前記逐次比較レジスターからの逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記入力信号のA/D変換データとして出力すると共に、前記コードデータを用いたコードシフトにより前記逐次比較結果データがオーバーフローするのを補正する補正処理を行うA/D変換方法に関係する。 Another aspect of the present invention is an A / D conversion method in a successive approximation type A / D conversion circuit having a comparison circuit, a successive approximation register, and a D / A conversion circuit. A corresponding code signal is generated, and the sampling signal of the input signal, the addition signal of the code signal, and the D / A output signal from the D / A conversion circuit are compared, or the sampling signal and the D / A A process of comparing the A output signal and the addition signal of the code signal is performed, and output data obtained based on the successive comparison result data from the successive approximation register and the code data is converted into A / D conversion data of the input signal. And a correction process for correcting overflow of the successive approximation result data due to code shift using the code data. Related to the conversion method.

本発明の他の態様によれば、コードデータに対応するコード信号が生成され、入力信号のサンプリング信号とコード信号の加算信号と、D/A出力信号とを比較する処理、或いはサンプリング信号と、D/A出力信号とコード信号の加算信号とを比較する処理が行われる。そして逐次比較結果データとコードデータとに基づき求められる出力データが、入力信号のA/D変換データとして出力される。このようにすれば、時間的に変化するコードデータによりコードシフトが行われるようになり、A/D変換特性を改善できる。 According to another aspect of the present invention, a code signal corresponding to code data is generated, a process of comparing a sampling signal of an input signal, an addition signal of the code signal, and a D / A output signal, or a sampling signal; A process of comparing the D / A output signal and the addition signal of the code signal is performed. Then, output data obtained based on the successive comparison result data and the code data is output as A / D conversion data of the input signal. In this way, code shift is performed by code data that changes over time, and the A / D conversion characteristics can be improved.

更に本発明の他の態様によれば、このようなコードデータを用いたコードシフトにより逐次比較結果データがオーバーフローしてしまうのを、補正処理により抑止できる。従って、コードシフトによりA/D変換特性を改善しながら、コードシフトによるダイナミックレンジの減少も抑止することが可能になる。 Furthermore, according to another aspect of the present invention, it is possible to prevent the sequential comparison result data from overflowing due to the code shift using such code data by the correction process. Accordingly, it is possible to suppress a decrease in dynamic range due to code shift while improving A / D conversion characteristics by code shift.

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。 Hereinafter, preferred embodiments of the present invention will be described in detail. The present embodiment described below does not unduly limit the contents of the present invention described in the claims, and all the configurations described in the present embodiment are indispensable as means for solving the present invention. Not necessarily.

1.構成

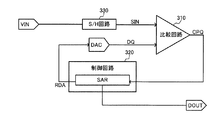

図1に本実施形態のA/D変換回路の構成例を示す。このA/D変換回路は、比較回路10、制御回路20、第1のD/A変換回路DAC1、第2のD/A変換回路DAC2、補正部80を含む。また、S/H(サンプル・ホールド)回路30やコードデータ生成部90を含むことができる。

1. Configuration FIG. 1 shows a configuration example of an A / D conversion circuit according to this embodiment. The A / D conversion circuit includes a

なお、本実施形態のA/D変換回路は図1の構成に限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えばS/H回路30の構成要素を省略し、D/A変換回路に入力信号VINのサンプル・ホールド機能を持たせてもよい。まだコードデータ生成部90の構成要素を省略し、コードデータCDAを外部から直接に入力してもよい。

The A / D conversion circuit according to the present embodiment is not limited to the configuration shown in FIG. 1, and various modifications such as omitting some of the components or adding other components are possible. For example, the components of the S /

比較回路10は、コンパレーター(例えばラッチ型コンパレーター)により実現され、例えば信号SADDと信号DQの比較処理を行う。

The

制御回路20は、逐次比較レジスターSAR(Successive Approximation Registor)を有し、逐次比較用データRDA(D/A入力データ)を出力する。逐次比較レジスターSARは、比較回路10からの比較結果信号CPQによりそのレジスター値が設定されるレジスターである。例えば比較回路10が、MSBのビットからLSBのビットに至るまでの逐次比較処理を行った場合に、各ビットにおける比較処理結果(「1」、「0」)が、逐次比較レジスターSARの各レジスター値として記憶される。

The

なお制御回路20は、A/D変換回路の各回路ブロックの制御処理も行うこともできる。例えばD/A変換回路DAC1、DAC2に含まれるスイッチ素子(スイッチアレイ)のオン・オフ制御を行う。

The

D/A変換回路DAC1は、制御回路20からの逐次比較用データRDAのD/A変換を行う。そして逐次比較用データRDAに対応するD/A出力信号DQ(RDAをD/A変換したアナログ信号)を出力する。このD/A変換回路DAC1は、キャパシタアレイを用いた電荷再分配型であってもよいし、その一部又は全部がラダー抵抗型であってもよい。

The D / A conversion circuit DAC1 performs D / A conversion of the successive approximation data RDA from the

D/A変換回路DAC2は、コードデータCDAをD/A変換する。そしてコードデータCDAに対応するコード信号SCD(CDAをD/A変換した信号)を出力する。ここでコードデータCDAは時間的に変化するデータ(所定タイミング毎に変化するデジタルデータ)である。具体的には所定のデータ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるデータである。 The D / A conversion circuit DAC2 performs D / A conversion on the code data CDA. Then, a code signal SCD (a signal obtained by D / A converting CDA) corresponding to the code data CDA is output. Here, the code data CDA is data that changes with time (digital data that changes at every predetermined timing). Specifically, the data is a different value for each one or a plurality of A / D conversion timings within a predetermined data range.

なおこの場合のデータ範囲は、第1のデジタルデータを上限値とし、第2のデジタルデータを下限値とする範囲である。A/D変換タイミングは例えばデジタルデータをアナログ信号に変換する各A/D変換期間に対応するタイミングである。 In this case, the data range is a range in which the first digital data is the upper limit value and the second digital data is the lower limit value. The A / D conversion timing is a timing corresponding to each A / D conversion period for converting digital data into an analog signal, for example.

S/H(サンプル・ホールド)回路30は、A/D変換の対象となる入力信号VINをサンプル・ホールドする回路である。なお電荷再分配型の場合にはS/H回路30の機能はD/A変換回路により実現できる。

The S / H (sample and hold)

コードデータ生成部90は、コードデータCDAを生成してD/A変換回路DAC2に出力する。例えば所定データ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるコードデータCDAを出力する。具体的には逐次比較用データの下位ビットデータのデータ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるコードデータCDAを出力する。

The code

補正部80は補正処理を行う。具体的には、コードデータCDAを用いたコードシフトによりダイナミックレンジが減少するのを防止するための補正処理を行う。この補正部80は情報レジスター84を有する。

The

そして本実施形態では比較回路10は、入力信号VINのサンプリング信号SIN(VINをサンプル・ホールドした信号)とコード信号SCDの加算信号SADDと、D/A出力信号DQとを比較する処理を行う。具体的には比較回路10は、第1の入力端子に入力される加算信号SADD(加算電圧)と第2の入力端子に入力されるD/A出力信号DQ(D/A変換電圧)を比較する。なお、電荷再分配型の場合等では、比較回路10は、サンプリング信号SINと、D/A出力信号DQとコード信号SCDの加算信号とを比較する処理を行う。例えば信号SINのサンプリング電圧と、信号DQとSCDの加算電圧を比較する。

In this embodiment, the

そして制御回路20は、逐次比較レジスターSARからの逐次比較結果データQDA(最終的なデータ)とコードデータCDAとに基づき求められる出力データDOUTを、入力信号VINのA/D変換データとして出力する。例えば制御回路20は、図1のようにサンプリング信号SINとコード信号SCDの加算信号SADDと、D/A出力信号DQとの比較処理が行われる場合には、逐次比較レジスターSARの逐次比較結果データQDAからコードデータCDAを減算する処理を行う。一方、後述する電荷再分配型のように、サンプリング信号SINと、D/A出力信号DQとコード信号SCDの加算信号との比較処理が行われる場合には、逐次比較結果データQDAにコードデータCDAを加算する処理を行う。

Then, the

また補正部80は、コードデータCDAを用いたコードシフトにより逐次比較結果データQDAがオーバーフローするのを補正(防止)する補正処理を行う。ここでコードデータによるコードシフトとは、入力信号のサンプリング信号とコード信号の加算処理を行うこと或いはD/A出力信号とコード信号の加算処理を行うことで、逐次比較結果データが、入力信号に対応するデータから高電位側又は低電位側にシフトすることである。

The

例えば補正部80は、コードデータCDAを補正することで当該補正処理を行う。そして補正指示信号SDRをコードデータ生成部90に出力する。具体的には、前回のA/D変換での逐次比較結果データである前回逐次比較結果データに基づきコードデータCDA(今回のコードデータ)を補正することで補正処理を行う。なお本実施形態の補正処理は、コードデータCDAを補正する処理には限定されず、逐次比較結果データQDAがオーバーフローするのを補正できるものであれば種々の変形実施が可能である。また前回逐次比較結果データに加えて、コードデータCDAの符号等を判定して、補正処理を行ってもよい。

For example, the

次に本実施形態のコードシフト手法について、A/D変換のビット数が8ビットである場合を例にとり説明する。 Next, the code shift method of the present embodiment will be described by taking an example in which the number of bits of A / D conversion is 8 bits.

まずS/H回路30が入力信号VINをサンプル・ホールドしてサンプリング信号SINを出力する。またコードデータ生成部90は、所定のデータ範囲内(例えば0000〜1111)の任意のコードデータCDAを出力し、D/A変換回路DAC2がCDAに対応するコード信号SCDを出力する。

First, the S /

制御回路20は、例えばMSBのビットが「1」に設定された逐次比較用データRDA=10000000を出力し、D/A変換回路DAC1がRDAに対応するD/A出力信号DQを出力する。

For example, the

そして比較回路10は、サンプリング信号SINにコード信号SCDを加算した信号SADDの電圧と、D/A出力信号DQの電圧を比較し、「1」又は「0」の比較結果信号CPQを出力する。例えば信号DQの電圧の方が信号SADDの電圧よりも大きければ「1」を出力し、小さければ「0」を出力する。これにより逐次比較レジスターSARのレジスター値のMSBのビットには「1」又は「0」が設定される。

The

次に制御回路20は、MSBの次のビットが「1」に設定された逐次比較用データRDA=11000000又は01000000を出力する。例えばMSBの比較結果が「1」である場合にはRDA=11000000を出力し、「0」である場合にはRDA=01000000を出力する。するとD/A変換回路DAC1はRDAに対応するD/A出力信号DQを出力する。

Next, the

そして比較回路10は、サンプリング信号SINにコード信号SCDを加算した信号SADDの電圧と、D/A出力信号DQの電圧を比較し、「1」又は「0」の比較結果信号CPQを出力する。これにより逐次比較レジスターSARのレジスター値のMSBの次のビットには「1」又は「0」が設定される。

The

以上のような逐次比較動作を、MSBのビットからLSBのビットに至るまで実行することで、最終的な逐次比較結果データQDAが取得される。即ち入力信号VINの電圧とD/A出力信号DQの電圧が等しくなるように逐次比較動作を行うことで、最終的な逐次比較結果データQDAが取得される。そして、取得された逐次比較結果データQDAからコードデータCDAを減算したデータが、入力信号VINをA/D変換したデータDOUTとして出力される。 By executing the successive approximation operation from the MSB bit to the LSB bit as described above, final successive comparison result data QDA is obtained. That is, the final successive approximation result data QDA is obtained by performing the successive approximation operation so that the voltage of the input signal VIN and the voltage of the D / A output signal DQ are equal. Then, data obtained by subtracting the code data CDA from the acquired successive comparison result data QDA is output as data DOUT obtained by A / D converting the input signal VIN.

図2に、本実施形態の第1の比較例のA/D変換回路を示す。この第1の比較例ではコードデータ生成部90や第2のD/A変換回路DAC2は設けられていない。そしてこの第1の比較例では、図3(A)に示すように、例えばDNLの誤差等が原因で特定のコードでミッシングコードが発生する。例えばDNLが1LSBを超えると、出力コードが存在しないコードが発生するというミッシングコードの現象が生じる。

FIG. 2 shows an A / D conversion circuit according to a first comparative example of the present embodiment. In the first comparative example, the code

この点、本実施形態によれば、このようなミッシングコードが発生したとしても、時間的に変化するコードデータCDAの信号SCDを、サンプリング信号SINに加算することで、図3(B)に示すようなコードシフトが行われる。なお図3(B)の実線はコードシフト後の特性を表すものであり、破線はコードシフト前の特性を表すものである。 In this regard, according to the present embodiment, even if such a missing code is generated, the signal SCD of the code data CDA that changes with time is added to the sampling signal SIN, as shown in FIG. A code shift like this is performed. Note that the solid line in FIG. 3B represents the characteristic after code shift, and the broken line represents the characteristic before code shift.

即ち本実施形態では1又は複数回のA/D変換タイミング毎にコードデータCDAを異なった値にすることで、図3(B)に示すように、ミッシングコードが発生するコードの場所が1又は複数回のA/D変換タイミング毎に変化する。例えば00010000のコードでミッシングコードが発生したとしても、その場所が、00010001や00010010や00001111の場所にシフトする。この結果、長い時間範囲で見ると、図3(C)に示すようにDNLやINLが改善され、ミッシングコードの現象が生じない良好な特性を得ることができる。即ち、ある特定のコードで発生していたDNL特性の悪化(ミッシングコード)を、時間的に変化するコードデータCDAにより周囲のコードに拡散させることで、特性の改善を図っている。 That is, in this embodiment, the code data CDA is set to a different value for each one or a plurality of A / D conversion timings, so that the code location where the missing code is generated is 1 or as shown in FIG. It changes at every A / D conversion timing. For example, even if a missing code is generated with a code of 1000010000, the location is shifted to a location of 00010001, 00010010, or 00001111. As a result, when viewed over a long time range, as shown in FIG. 3C, DNL and INL are improved, and good characteristics that do not cause the phenomenon of missing codes can be obtained. In other words, the deterioration of the DNL characteristic (missing code) that has occurred in a specific code is diffused to surrounding codes by the code data CDA that changes with time to improve the characteristic.

つまり図3(A)に示すようにミッシングコードが発生している状態で、入力電圧に意図的にオフセット電圧を加えた場合を考える。その時のDNL、INL特性は、図3(B)に示すように、あたかも加えたオフセット電圧に相当するコードだけシフトしたようになる。この場合に、A/D変換回路で変換されたデジタルデータは、オフセット電圧に相当するコードが加えられているので、オフセット電圧に相当するコードを減算することで最終結果が得られる。本実施形態のコードシフト手法は、この特性を利用し、入力電圧に毎回異なるオフセット電圧を加える。これを行うことで、図3(C)に示す特性のA/D変換回路で、見かけ上、変換を行っていることになる。 That is, consider a case where an offset voltage is intentionally added to the input voltage in the state where the missing code is generated as shown in FIG. At this time, the DNL and INL characteristics are shifted as if by a code corresponding to the applied offset voltage, as shown in FIG. In this case, since the code corresponding to the offset voltage is added to the digital data converted by the A / D conversion circuit, the final result can be obtained by subtracting the code corresponding to the offset voltage. The code shift method of this embodiment uses this characteristic and adds a different offset voltage to the input voltage every time. By doing this, the conversion is apparently performed by the A / D conversion circuit having the characteristics shown in FIG.

例えば、ミッシングコードが発生しているコードに対応する電圧をA/D変換する場合を考える。コードシフトを行わない場合、この入力電圧周辺では非線形な変換が行われてしまう。これに対して、ある値だけコードシフトを行った場合、上記の入力電圧周辺では、線形性が良い変換が行われる。つまり、さまざまな値でコードシフトさせることで、あるコードシフト値では非線形であるが、大半のコードシフト値では線形な変換が行われる。最終的に、コードシフトを行うことで、本来ミッシングコードが発生している入力電圧においても比較的線形な変換が行われるようになる。 For example, consider a case in which a voltage corresponding to a code in which a missing code is generated is A / D converted. When code shift is not performed, nonlinear conversion is performed around this input voltage. On the other hand, when code shift is performed by a certain value, conversion with good linearity is performed around the input voltage. In other words, by performing code shift with various values, a certain code shift value is non-linear, but most code shift values are linearly converted. Finally, by performing the code shift, a relatively linear conversion is performed even in the input voltage where the missing code is originally generated.

以上のように、本実施形態によれば、コードデータCDAを発生して加算するという簡素な処理により、ミッシングコードの発生を防止し、A/D変換回路のDNLやINLの特性を改善することに成功している。 As described above, according to the present embodiment, by the simple process of generating and adding the code data CDA, the occurrence of the missing code is prevented, and the DNL and INL characteristics of the A / D conversion circuit are improved. Has succeeded.

2.補正処理

さて、以上のように説明したコードシフト手法には、ダイナミックレンジが減少してしまう問題があることが判明した。即ち、ダイナミックレンジの限界付近の入力電圧の時に、コードシフトによるオフセット電圧を加えてしまうと、実際にA/D変換するデータはダイナミックレンジをオーバーしてしまうので、実効的にダイナミックレンジが減少してしまう。

2. Correction Processing Now, it has been found that the code shift method described above has a problem that the dynamic range decreases. In other words, if an offset voltage due to code shift is applied when the input voltage is near the limit of the dynamic range, the data that actually undergoes A / D conversion will exceed the dynamic range, effectively reducing the dynamic range. End up.

このような問題を回避するため、本実施形態では例えば前回の変換値を記憶しておき、コードシフトによってダイナミックレンジをオーバーしそうな場合は、記憶しておいた変換値に基づいて、ダイナミックレンジをオーバーしないコードデータを生成する。そして生成されたコードデータをコードシフト用のD/A変換回路DAC2に入力することで、ダイナミックレンジの劣化を回避する。 In order to avoid such a problem, in the present embodiment, for example, the previous conversion value is stored, and when the dynamic range is likely to be exceeded due to code shift, the dynamic range is calculated based on the stored conversion value. Generate code data that does not exceed. Then, the generated code data is input to the D / A conversion circuit DAC2 for code shift, thereby avoiding deterioration of the dynamic range.

例えば図4において、A/D入力電圧範囲はA/D変換回路のダイナミックレンジを表すものであり、A/D変換回路は、このA/D入力電圧範囲の入力電圧については適正にA/D変換を行うことが可能になっている。 For example, in FIG. 4, the A / D input voltage range represents the dynamic range of the A / D conversion circuit, and the A / D conversion circuit appropriately sets the A / D input voltage within this A / D input voltage range. Conversion can be performed.

そして、入力電圧がA/D入力電圧範囲の高電位側の第1の範囲RA1である場合に、A1に示すように高電位側方向(正方向)へのコードシフトが行われてしまうと、ダイナミックレンジをオーバーしてしまい、実効的にダイナミックレンジが減少してしまう。同様に、入力電圧がA/D入力電圧範囲の低電位側の第2の範囲RA2である場合に、A2に示すように低電位側方向(負方向)へのコードシフトが行われてしまうと、ダイナミックレンジをオーバーしてしまい、実効的にダイナミックレンジが減少してしまう。 When the input voltage is the first range RA1 on the high potential side of the A / D input voltage range, if the code shift in the high potential side direction (positive direction) is performed as indicated by A1, The dynamic range is exceeded and the dynamic range is effectively reduced. Similarly, when the input voltage is the second range RA2 on the low potential side of the A / D input voltage range, if a code shift in the low potential side direction (negative direction) is performed as indicated by A2. The dynamic range is exceeded, and the dynamic range is effectively reduced.

このような問題を解決するために、本実施形態では、入力電圧が高電位側の第1の範囲RA1である場合には、図5のB1に示すようにA/D変換結果が低電位側にシフトするようにコードデータを補正する。また入力電圧が低電位側の第2の範囲RA2である場合には、B2に示すようにA/D変換結果が高電位側にシフトするようにコードデータを補正する。なお、第1の範囲RA1は、例えばA/D入力電圧範囲の最大電圧(例えば電源電圧)を含む高電位側の電圧範囲であり、第2の範囲RA2は、例えばA/D入力電圧範囲の最少電圧(例えば0V)を含む低電位側の電圧範囲である。また第3の電圧範囲RA3は第1の範囲RA1と第2の範囲RA2の間の電圧範囲(中間電圧範囲)である。 In order to solve such a problem, in this embodiment, when the input voltage is in the first range RA1 on the high potential side, the A / D conversion result is on the low potential side as shown in B1 of FIG. The code data is corrected so as to shift to. When the input voltage is in the second range RA2 on the low potential side, the code data is corrected so that the A / D conversion result is shifted to the high potential side as indicated by B2. The first range RA1 is a high-potential side voltage range including, for example, the maximum voltage (for example, power supply voltage) of the A / D input voltage range, and the second range RA2 is, for example, the A / D input voltage range. This is a voltage range on the low potential side including the minimum voltage (for example, 0 V). The third voltage range RA3 is a voltage range (intermediate voltage range) between the first range RA1 and the second range RA2.

例えば本実施形態では補正部80は、前回のA/D変換での逐次比較結果データである前回逐次比較結果データに基づきコードデータを補正する。

For example, in the present embodiment, the

具体的には図6(A)に示すように補正部80は、前回の逐次比較結果データQDAが、A/D入力電圧範囲の高電位側の第1の範囲RA1に対応するデータである場合には、今回のA/D変換での逐次比較結果データQDAが低電位側にシフトするように、コードデータCDAの補正処理を行う。例えば前回の逐次比較結果データQDAが第1の範囲RA1内のデータであり、コードシフトの方向が図4のA1に示すように高電位側方向(正方向)であったとする。この場合には、コードデータ生成部90は、補正部80からの補正指示信号SDRにより、図5のB1に示すように逐次比較結果データQDAが低電位側方向にシフトするように、コードデータCDAを補正して、コードシフト用の第2のD/A変換回路DAC2に出力する。

Specifically, as illustrated in FIG. 6A, the

また図6(B)に示すように補正部80は、前回の逐次比較結果データQDAが、A/D入力電圧範囲の低電位側の第2の範囲RA2に対応するデータである場合には、今回のA/D変換での逐次比較結果データQDAが高電位側にシフトするように、コードデータCDAの補正処理を行う。例えば前回の逐次比較結果データQDAが第2の範囲RA2内のデータであり、コードシフトの方向が図4のA2に示すように低電位側方向(負方向)であったとする。この場合には、コードデータ生成部90は、補正部80からの補正指示信号SDRにより、図5のB2に示すように逐次比較結果データQDAが高電位側方向にシフトするように、コードデータCDAを補正して、第2のD/A変換回路DAC2に出力する。

As shown in FIG. 6B, the

また前回の逐次比較結果データQDAが、図5の第1の範囲RA1と第2の範囲RA2の間の第3の範囲RA3に対応するデータであったとする。この場合には図6(C)に示すように、コードデータ生成部90は、交互に正、負となるコードデータを生成して、第2のD/A変換回路DAC2に出力する。

Further, it is assumed that the previous successive approximation result data QDA is data corresponding to the third range RA3 between the first range RA1 and the second range RA2 in FIG. In this case, as shown in FIG. 6C, the code

補正部80が含む情報レジスター84は、前回の逐次比較結果データQDAが、第1の範囲RA1又は第2の範囲RA2に対応するデータであったか否かについての情報を記憶する。なお、後述するように複数のチャンネルの信号が時分割でA/D変換される場合には、情報レジスター84は、複数のチャンネルの各チャンネルについて、前回の逐次比較結果データが第1の範囲RA1又は第2の範囲RA2に対応するデータであったか否かについての情報を記憶する。

The information register 84 included in the

具体的には補正部80は、例えば前回のA/D変換での逐次比較結果データQDAが第1の範囲RA1のデータであり且つコードシフトの方向が高電位側方向であるか否か、或いは、前回の逐次比較結果データQDAが第2の範囲RA2のデータであり且つコードシフトの方向が低電位側方向であるか否かを判定する。この判定結果情報が情報レジスター84に記憶される。そして補正部80は、記憶された判定結果情報に基づいて補正指示信号SDRを生成して、コードデータ生成部90に出力し、コードデータCDAの補正を指示する。これによりコードデータ生成部90が、今回のA/D変換でのコードデータCDAを補正して、第2のD/A変換回路DAC2に出力する。

Specifically, for example, the

3.補正部、コードデータ生成部

図7、図8に補正部80、コードデータ生成部90の構成例を示す。なお、補正部80、コードデータ生成部90は図7、図8の構成に限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

3. Correction Unit, Code Data Generation Unit FIGS. 7 and 8 show configuration examples of the

補正部80は、判定部82、情報レジスター84、セレクター86、出力レジスター88を含む。

The

判定部82は、コードシフト用カウンター92から、コードデータの符号ビットである上位の1ビットを反転した反転符号ビットを受ける。また逐次比較レジスターSARから、逐次比較結果データQDAの上位の2ビットを受ける。コードシフト用カウンター92は、5ビットのカウンターであり、2の補数表現の5ビットのコードデータを出力する。従って、コードデータの上位の1ビットは符号ビットになる。また逐次比較レジスターSARからの逐次比較結果データQDAの上位の2ビットは、MSBビットとMSBの次のビットである。

The

判定部82は、コードデータの反転符号ビットと逐次比較結果データQDAの上位の2ビットからなる3ビットの全てが、「1」或いは「0」かを判断し、全てが「1」或いは「0」である場合には、判定結果信号RS=1を出力する。

The

ここで、コードデータの上位の1ビットが「1」であることはコードデータの符号が正であることを意味し、「0」であることは符号が負であることを意味する。そして後述するようにコードデータはA/D変換毎に交互に正、負になる。従って、判定部82に入力される反転符号ビットが「1」であることは、前回のA/D変換でのコードデータの符号が負であり、今回のA/D変換のコードデータの符号が正になることを意味する。また反転符号ビットが「0」であることは、前回のA/D変換でのコードデータの符号が正であり、今回のA/D変換のコードデータの符号が負になることを意味する。

Here, the upper one bit of the code data being “1” means that the sign of the code data is positive, and “0” means that the sign is negative. As will be described later, the code data alternately becomes positive and negative every A / D conversion. Therefore, if the inverted sign bit input to the

また逐次比較結果データQDAの上位の2ビットが「11」であることは、QDAが図5の第1の範囲RA1に対応するデータであることを意味し、上位の2ビットが「00」であることは、QDAが第2の範囲RA2に対応するデータであることを意味する。 Further, the upper 2 bits of the successive approximation result data QDA being “11” means that the QDA is data corresponding to the first range RA1 of FIG. 5, and the upper 2 bits are “00”. Being present means that QDA is data corresponding to the second range RA2.

そして、コードデータの反転符号ビットと逐次比較結果データQDAの上位の2ビットからなる3ビットが「111」又は「000」である場合に、判定結果信号がRS=1になる。従って、判定結果信号RS=1は、前回のA/D変換の逐次比較結果データQDAが第1の範囲RA1内であり且つ今回のコードデータの符号が正(シフト方向が高電位側方向)であること、或いは、QDAが第2の範囲RA2内であり且つ今回のコードデータの符号が負(シフト方向が低電位側方向)であることを意味する。 When the 3 bits consisting of the inverted sign bit of the code data and the upper 2 bits of the successive approximation result data QDA are “111” or “000”, the determination result signal is RS = 1. Accordingly, the determination result signal RS = 1 indicates that the successive comparison result data QDA of the previous A / D conversion is within the first range RA1 and the sign of the current code data is positive (the shift direction is the high potential side direction). It means that the QDA is in the second range RA2 and the sign of the current code data is negative (the shift direction is the low potential side direction).

情報レジスター84は、判定部82から判定結果信号RSを受けて記憶する。ここで図9に示すように、本実施形態ではA/D変換回路530が複数チャンネルCH1〜CH16の信号を時分割でA/D変換している。即ちA/D変換回路530の前段側にマルチプレクサー500が設けられ、このマルチプレクサー500が、チャンネル選択用のインデックス信号CHIDXに基づいて複数チャンネルCH1〜CH16のうちの1つのチャンネルの信号を選択する。そしてA/D変換回路530は、選択されたチャンネルの信号(電圧)をA/D変換する。この時、インデックス信号CHIDXはCH1、CH2、CH3・・・CH16の順でチャンネルの選択を指示するため、A/D変換回路530は、CH1、CH2、CH3・・・CH16の順で各チャンネルの信号をA/D変換することになる。

The information register 84 receives and stores the determination result signal RS from the

情報レジスター84は、CH1〜CH16の16チャンネル(広義にはNチャンネル)に対応する16ビット(広義にはNビット)のレジスターになっている。情報レジスター84は、上述したチャンネル選択用のインデックス信号CHIDXと判定部82からの1ビットの判定結果信号RSを受ける。そして、判定結果情報IRSの16ビットのうち、現在A/D変換中のチャンネルに対応するビットを、判定結果信号RSの値に設定する。例えば判定結果信号RSが「1」である場合には、判定結果情報IRSの対応するビットは「1」に設定され、RSが「0」である場合にはIRSの対応するビットは「0」に設定される。例えばチャンネルCH1では、逐次比較結果データQDAが第1の範囲RA1内であり且つコードデータの符号が正(或いはRA2内であり且つ符号が負)であり、他のチャンネルCH2〜CH16では、QDAが第3の範囲RA3内であったとする。この場合には、判定結果情報IRSは「1000000000000000」に設定される。

The information register 84 is a 16-bit register (N bits in a broad sense) corresponding to 16 channels (N channels in a broad sense) of CH1 to CH16. The information register 84 receives the above-described channel selection index signal CHIDX and the 1-bit determination result signal RS from the

セレクター86は情報レジスター84から判定結果情報IRSを受ける。そして、16ビットの判定結果情報IRSのビットのうち、チャンネル選択用のインデックス信号CHIDXで指定されるチャンネルに対応するビットの値を、1ビットの信号SRQとして出力する。例えば判定結果情報IRSが前述のように「1000000000000000」であり、インデックス信号CHIDXがチャンネルCH1を指定していた場合には、セレクター86は信号SRQ=1を出力する。一方、インデックス信号CHIDXがチャンネルCH2〜CH16を指定していた場合には、セレクター86は信号SRQ=0を出力する。

The

出力レジスター88は、セレクター86からの信号SRQをラッチし、ラッチした信号を次のA/D変換のタイミングで補正指示信号SDRとしてコードデータ生成部90に出力する。

The output register 88 latches the signal SRQ from the

以上のようにすることで、前回のA/D変換における逐次比較結果データが第1の範囲RA1であり且つ今回のA/D変換でのコードシフトの方向が高電位側方向(コードデータの符号が正)である場合には、今回のA/D変換における補正指示信号はSDR=1になる。同様に、前回のA/D変換における逐次比較結果データが第2の範囲RA2であり且つ今回のA/D変換でのコードシフトの方向が低電位側方向(コードデータの符号が負)である場合にも、今回のA/D変換における補正指示信号はSDR=1になる。一方、前回の逐次比較結果データが第3の範囲RA3である場合には、今回のA/D変換における補正指示信号はSDR=0になる。従って、コードデータ生成部90が、補正指示信号がSDR=1になった場合にコードデータの符号を反転させることで、コードシフトによるオーバーフローを防止できるようになる。

By doing as described above, the successive approximation result data in the previous A / D conversion is in the first range RA1, and the code shift direction in the current A / D conversion is the high potential side direction (the sign of the code data). Is positive), the correction instruction signal in the current A / D conversion is SDR = 1. Similarly, the successive approximation result data in the previous A / D conversion is in the second range RA2, and the code shift direction in the current A / D conversion is the low potential side direction (the sign of the code data is negative). Even in this case, the correction instruction signal in the current A / D conversion is SDR = 1. On the other hand, when the previous successive approximation result data is in the third range RA3, the correction instruction signal in the current A / D conversion is SDR = 0. Therefore, the code

図8に示すように、コードデータ生成部90は、コードシフト用カウンター92、並び替え部94、反転部96、セレクター98を含む。

As shown in FIG. 8, the code

コードシフト用カウンター92は、前述のように5ビットのカウンターであり、5ビットのカウント値CCTを生成して、並び替え部94に出力する。並び替え部94は、5ビットのカウント値CCTをバイナリで並び替えて、15、−1、14、−2、13、−3、12、−4、11、−5・・・・2、−14、1、−15、0というような−15〜+15の範囲の31個(広義には素数個)のデータDA2を、ノードNC2に順次出力する。反転部96はノードNC2のデータDA2の符号を反転して、−15、1、−14、2、−13、3、−12、4、−11、5・・・・−2、14、−1、15、0というような−15〜+15の範囲の31個のデータDA1を順次出力する。

The

セレクター98は、補正部80からの補正指示信号SDRに基づいてデータDA1、DA2のいずれかを選択して、コードデータCDAとして出力する。例えばSDR=0である場合には、端子IN1に入力されるデータDA1を選択してコードデータCDAとして出力する。SDR=1である場合には、端子IN2に入力されるデータDA2を選択してコードデータCDAとして出力する。データDA2はデータDA1の符号を反転したデータになる。従って、補正指示信号がSDR=1になると、DA1を反転した信号がコードデータCDAとして出力されるようになる。

The

例えば前回の逐次比較結果データQDAが図5の第1の範囲RA1内であり、データDA1が14であったとする。この場合に、このデータDA1=14が今回のコードデータとしてセレクター98により選択されてしまうと、図4のA1に示すようにダイナミックレンジの正側へのオーバーフローが生じてしまう。従って、この場合には補正指示信号がSDR=1になり、セレクター98がデータDA1=14の符号を反転したデータDA2=−14を選択する。従って、コードデータCDAとしてDA2=−14が出力されるようになり、図5のB1に示すようにダイナミックレンジの正側へのオーバーフローが抑止される。

For example, it is assumed that the previous successive approximation result data QDA is within the first range RA1 of FIG. In this case, if the data DA1 = 14 is selected as the current code data by the

一方、前回の逐次比較結果データQDAが第2の範囲RA2内であり、データDA1が−15であったとする。この場合に、このデータDA1=−15が今回のコードデータとして選択されてしまうと、図4のA2に示すようにダイナミックレンジの負側へのオーバーフローが生じてしまう。従って、この場合にも補正指示信号がSDR=1になり、セレクター98がデータDA1=−15の符号を反転したデータDA2=15を選択する。従って、コードデータCDAとしてDA2=15が出力されるようになり、図5のB2に示すようにダイナミックレンジの負側へのオーバーフローが抑止される。

On the other hand, it is assumed that the previous successive approximation result data QDA is in the second range RA2 and the data DA1 is −15. In this case, if this data DA1 = -15 is selected as the current code data, an overflow to the negative side of the dynamic range occurs as shown by A2 in FIG. Accordingly, in this case as well, the correction instruction signal becomes SDR = 1, and the

以上のように本実施形態によれば、コードデータを用いたコードシフトにより逐次比較結果データがオーバーフローするのが補正されるため、コードシフトによるダイナミックレンジの減少を抑止できる。従って、コードシフトによりA/D変換回路のDNLやINLの特性を改善しながら、コードシフトを要因とするダイナミックレンジの減少も抑止できるようになる。 As described above, according to the present embodiment, the overflow of the successive comparison result data due to the code shift using the code data is corrected, so that the reduction of the dynamic range due to the code shift can be suppressed. Accordingly, it is possible to suppress a decrease in the dynamic range caused by the code shift while improving the DNL and INL characteristics of the A / D conversion circuit by the code shift.

なお、前回の逐次比較結果データQDAが第3の範囲RA3内である場合には、補正指示信号がSDR=0になるため、セレクター98によりデータDA1が選択されて、交互に正、負となるコードデータCDAが出力されるようになる。このようにコードデータCDAが交互に正、負になることで、コードデータCDAの変化の周波成分(低周波成分)が、A/D変換特性に悪影響を及ぼす事態を抑止できる。即ち、コードデータCDAが交互に正、負になることで、コードデータCDAの変化の周波数成分が高周波数側がシフトする。そして、このような高周波数成分については、例えばA/D変換回路の後段のデジタルフィルター(ローパスフィルター)によりカットできるため、コードデータCDAの変化の周波数成分の影響を低減することができ、A/D変換特性への悪影響を抑止できるようになる。

If the previous successive approximation result data QDA is within the third range RA3, the correction instruction signal is SDR = 0, so that the data DA1 is selected by the

また図1のように入力信号のサンプリング信号SINとコード信号SCDの加算信号と、D/A出力信号SCDとを比較する方式を採用した場合には、正の符号のコードデータはQDAを高電位側方向にシフトさせるデータになり、負の符号のコードデータはQDAを低電位側方向にシフトさせるデータになる。しかしながら、サンプリング信号SINと、D/A出力信号DQとコード信号SCDの加算信号とを比較する方式を採用した場合には、正の符号のコードデータはQDAを低電位側方向にシフトさせるデータになり、負の符号のコードデータはQDAを高電位側方向にシフトさせるデータになる。 In addition, as shown in FIG. 1, when a method of comparing the sum signal of the sampling signal SIN of the input signal and the code signal SCD and the D / A output signal SCD is adopted, the code data of the positive sign has a high potential of QDA The data is shifted in the lateral direction, and the code data with a negative sign is data that shifts the QDA in the lower potential direction. However, when the method of comparing the sampling signal SIN, the D / A output signal DQ, and the addition signal of the code signal SCD is adopted, the code data with a positive sign is data that shifts the QDA in the low potential side direction. Therefore, the code data with a negative sign is data for shifting the QDA in the high potential side direction.

4.オーバーサンプリング

本実施形態では、2のべき乗倍のオーバーサンプリングのA/D変換を行っている。例えば8倍のオーバーサンプリングを例にとれば、図10(A)に示すように、8回のA/D変換AD1〜AD8が行われる毎に、最終的な1個のA/D出力データが出力される。即ち、本来必要な帯域よりも広い帯域(速い周波数)でA/D変換回路を動作させ、A/D変換回路の後段のデジタルフィルターを用いて必要な帯域にフィルターを掛けて信号を取り出す。この時に、必要な帯域外の量子化ノイズがデジタルフィルターにより除去され、その結果、SNR(Signal to Noise Ratio)が向上する。例えばOSR(Over-Sampling-Ratio)を2倍にすると、理論上は、SNRは3dB(0.5ビット)だけ改善する効果が得られる。またオーバーサンプリングを行うことで、A/D変換回路の前段の前置きフィルターの次数を減少させることができるというメリットもある。

4). Oversampling In the present embodiment, oversampling A / D conversion that is a power of 2 is performed. For example, when 8 times oversampling is taken as an example, as shown in FIG. 10A, every time A / D conversion AD1 to AD8 is performed eight times, one final A / D output data is obtained. Is output. That is, the A / D converter circuit is operated in a wider band (faster frequency) than the originally required band, and a signal is extracted by filtering the required band using a digital filter subsequent to the A / D converter circuit. At this time, necessary out-of-band quantization noise is removed by the digital filter, and as a result, the SNR (Signal to Noise Ratio) is improved. For example, when OSR (Over-Sampling-Ratio) is doubled, theoretically, an effect of improving SNR by 3 dB (0.5 bits) can be obtained. Further, by performing oversampling, there is an advantage that the order of the pre-filter in the preceding stage of the A / D conversion circuit can be reduced.

しかしながら、このようなオーバーサンプリングのA/D変換を行った時に、コードデータの変化の周期と、オーバーサンプリングの周期の間に相関性があると、オーバーサンプリングによるSNRの向上が抑制されてしまうおそれがある。例えば図10(A)のように2のべき乗倍のオーバーサンプリングが行われる場合に、コードデータの個数も2のべき乗個であると、2のべき乗回の各A/D変換と各コードデータとの対応づけが一定になってしまう。従って、オーバーサンプリングとコードシフトの相乗効果によるSNR等の向上が抑制されてしまう。 However, when such oversampling A / D conversion is performed, if there is a correlation between the change period of the code data and the oversampling period, the improvement of the SNR due to oversampling may be suppressed. There is. For example, when oversampling of a power of 2 is performed as shown in FIG. 10A, if the number of code data is also a power of 2, each A / D conversion of each power of 2 and each code data Will become constant. Therefore, an improvement in SNR and the like due to a synergistic effect of oversampling and code shift is suppressed.

そこで本実施形態ではコードデータ生成部90は、2のべき乗倍(2倍、4倍、8倍、16倍、32倍等)のオーバーサンプリングのA/D変換が行われる場合に、素数個のコードデータを生成するようにしている。図8を例にとれば、コードデータ生成部90は、素数個である31個のコードデータを生成して順次出力する。このようにすれば、2のべき乗回の各A/D変換と各コードデータとの対応づけが一定にならないようになる。従って、オーバーサンプリングとコードシフトの相乗効果によるSNR等の向上を実現できる。

Therefore, in the present embodiment, the code

なおオーバーサンプリングのA/D変換は図10(A)の手法に限定されず、種々の変形実施が可能である。またコードデータの個数や生成パターンも図8に示した例には限定されない。 The oversampling A / D conversion is not limited to the method shown in FIG. 10A, and various modifications can be made. Further, the number of code data and the generation pattern are not limited to the example shown in FIG.

また図9に示すように複数チャンネルの信号を時分割でA/D変換する場合には、図10(B)に示すようにA/D変換回路は動作することになる。例えばチャンネルCH1の信号についてのサンプリングSC1及び変換CC1を実行した後に、チャンネルCH2の信号についてのサンプリングSC2及び変換CC2を実行する。その後、同様にしてCH3〜CH16の各チャンネルのサンプリング及び変換を順次実行する。この場合に図10(B)のC1が今回のA/D変換である場合には、C2が前回のA/D変換になる。従って、図7の情報レジスター84には、C2に示す前回のA/D変換の判定結果情報が記憶され、このC2での判定結果情報に基づいて、C1に示す今回のA/D変換におけるコードデータが補正されるようになる。 Further, when A / D conversion is performed on a plurality of channels of signals in a time division manner as shown in FIG. 9, the A / D conversion circuit operates as shown in FIG. For example, after executing sampling SC1 and conversion CC1 for the signal of channel CH1, sampling SC2 and conversion CC2 for the signal of channel CH2 are executed. Thereafter, sampling and conversion of each channel of CH3 to CH16 are sequentially executed in the same manner. In this case, when C1 in FIG. 10B is the current A / D conversion, C2 is the previous A / D conversion. Accordingly, the information register 84 of FIG. 7 stores the determination result information of the previous A / D conversion indicated by C2, and the code in the current A / D conversion indicated by C1 is based on the determination result information of C2. Data will be corrected.

5.詳細な構成例

図11に本実施形態のA/D変換回路の詳細な構成例を示す。図11は、図1のDAC1、DAC2、比較回路10の詳細な構成例を示すものであり、DAC1、DAC2は電荷再分配型のD/A変換回路により構成される。

5. Detailed Configuration Example FIG. 11 shows a detailed configuration example of the A / D conversion circuit of this embodiment. FIG. 11 shows a detailed configuration example of the

具体的には第1のD/A変換回路DAC1は、第1のキャパシタアレイ部41と第1のスイッチアレイ部51を含む。また比較ノードNCと第1のノードN1との間に設けられる第1の直列キャパシタCS1を含む。またDAC1は、第2のキャパシタアレイ部42と第2のスイッチアレイ部52を含む。またサンプリング期間において、ノードNC、N1をGND(AGND)に設定するためのスイッチ素子SS1、SS2を含む。

Specifically, the first D / A conversion circuit DAC1 includes a first

なお、ノードN1に対して第3の直列キャパシタの一端を接続し、この第3の直列キャパシタの他端側に、キャパシタアレイ部42、スイッチアレイ部52と同様の構成のキャパシタアレイ部、スイッチアレイ部を設けてもよい。

Note that one end of the third series capacitor is connected to the node N1, and the capacitor array unit and the switch array having the same configuration as the

DAC1の第1のキャパシタアレイ部41は、複数のキャパシタCA1〜CA4を含む。これらのキャパシタCA1〜CA4は、その一端が比較回路10の比較ノードNCに接続される。ここで比較ノードNC(サンプリングノード)は、比較回路10の第1の入力端子(反転入力端子)に接続されるノードであり、比較回路10の第2の入力端子(非反転入力端子)はGNDに設定される。またキャパシタCA1〜CA4はバイナリで重み付けされており、例えばCA1、CA2、CA3、CA4の容量値は、4ビットの場合にはC、2C、4C、8Cになっている。また第1のキャパシタアレイ部41は、ダミーキャパシタCDMも含む。

The first

DAC1の第1のスイッチアレイ部51は、複数のスイッチ素子SA1〜SA4を含む。これらのスイッチ素子SA1〜SA4は、第1のキャパシタアレイ部41のキャパシタCA1〜CA4の他端に接続される。そしてスイッチ素子SA1〜SA4は、逐次比較用データRDAの上位ビットのデータ(例えばRDAが8ビットの場合には上位の4ビットのデータ)に基づきスイッチ制御される。

The first

DAC1の第2のキャパシタアレイ部42は、複数のキャパシタCB1〜CB4を含む。これらのキャパシタCB1〜CB4は、その一端が第1のノードN1に接続される。ここで第1のノードN1は、一端が比較ノードNCに接続される直列キャパシタCS1の他端側のノードである。またキャパシタCB1〜CB4はバイナリで重み付けされており、例えばCB1、CB2、CB3、CB4の容量値は、4ビットの場合にはC、2C、4C、8Cになっている。

The second

DAC1の第2のスイッチアレイ部52は、複数のスイッチ素子SB1〜SB4を含む。これらのスイッチ素子SB1〜SB4は、第2のキャパシタアレイ部42のキャパシタCB1〜CB4の他端に接続される。そしてスイッチ素子SB1〜SB4は、逐次比較用データRDAの下位ビットのデータ(例えばRDAが8ビットの場合には下位の4ビットのデータ)に基づきスイッチ制御される。

The second

第2のD/A変換回路DAC2は、比較ノードNCと第2のノードN2との間に設けられる第2の直列キャパシタCS2を含む。また第3のキャパシタアレイ部43と第3のスイッチアレイ部53を含む。またサンプリング期間において、第2のノードN2をGNDに設定するためのスイッチ素子SS3を含む。

The second D / A conversion circuit DAC2 includes a second series capacitor CS2 provided between the comparison node NC and the second node N2. A third

DAC2の第3のキャパシタアレイ部43は、複数のキャパシタCC1〜CC4を含む。これらのキャパシタCC1〜CC4は、その一端が第2のノードN2に接続される。ここで第2のノードN2は、一端が比較ノードNCに接続される直列キャパシタCS2の他端側のノードである。またキャパシタCC1〜CC4はバイナリで重み付けされており、例えばCC1、CC2、CC3、CC4の容量値は、4ビットの場合にはC、2C、4C、8Cになっている。

The third

DAC2の第3のスイッチアレイ部53は、複数のスイッチ素子SC1〜SC4を含む。これらのスイッチ素子SC1〜SC4は、第3のキャパシタアレイ部43のキャパシタCC1〜CC4の他端に接続される。そしてスイッチ素子SC1〜SC4は、コードデータCDAに基づきスイッチ制御される。

The third

即ち図1のコードデータ生成部90は、D/A変換回路DAC2に対してコードデータCDAを出力し、このコードデータCDAに基づいてスイッチ素子SC1〜SC4はスイッチ制御される。例えばコードデータ生成部90は、逐次比較用データRDAの下位ビットデータのデータ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるデータを、コードデータCDAとして出力する。

That is, the code

具体的には図11の8ビットのA/D変換の場合には、逐次比較用データRDAの下位の4ビットのデータ範囲内において、コードデータCDAを変化させる。例えば0000〜1111のデータ範囲内(或いは0000〜1111よりも狭いデータ範囲内)においてコードデータCDAをランダムに変化させて、D/A変換回路DAC2のスイッチアレイ部53のスイッチ素子SC1〜SC4をスイッチ制御する。このときD/A変換回路DAC1のスイッチアレイ部52のスイッチ素子SB1〜SB4も、逐次比較用データRDAの下位の4ビットのデータによりスイッチ制御される。このように、コードデータCDAを変化させる範囲を、DAC1のスイッチ素子SB1〜SB4をスイッチ制御する逐次比較用データRDAのデータ範囲内に設定することで、ミッシングコードの発生を効果的に防止できる。

Specifically, in the case of 8-bit A / D conversion in FIG. 11, the code data CDA is changed within the lower 4-bit data range of the successive approximation data RDA. For example, the code data CDA is randomly changed within the data range of 0000 to 1111 (or within the data range narrower than 0000 to 1111) to switch the switch elements SC1 to SC4 of the

なお、D/A変換回路DAC1の最小分解能(LSBに相当する電圧、量子化電圧)をRS1とし、D/A変換回路DAC2の最小分解能をRS2としたとする。この場合に図11ではRS2=RS1になっている。具体的には例えば直列キャパシタCS1とCS2の容量値は同一(ほぼ同一)になっており、DAC1のLSBに相当するキャパシタCB1の容量値と、DAC2のLSBに相当するキャパシタCC1の容量値も同一(ほぼ同一)になっている。即ちDAC2は、DAC1の最小分解能RS1(LSB)未満のノイズ電圧ではなく、ノイズ電圧よりも大きなコード電圧を出力している。このようにすることで図3(B)に示すようなコードシフトを実現できる。なおRS2=RS1には限定されず、RS2≧RS1であってもよい。

It is assumed that the minimum resolution (voltage corresponding to LSB, quantization voltage) of the D / A conversion circuit DAC1 is RS1, and the minimum resolution of the D / A conversion circuit DAC2 is RS2. In this case, RS2 = RS1 in FIG. Specifically, for example, the capacitance values of the series capacitors CS1 and CS2 are the same (substantially the same), and the capacitance value of the capacitor CB1 corresponding to the LSB of the DAC1 and the capacitance value of the capacitor CC1 corresponding to the LSB of the DAC2 are also the same. (Almost the same). That is, the

次に、図12を用いて本実施形態の動作について詳細に説明する。図12に示すように、入力信号VINのサンプリング期間では、メインのD/A変換回路DAC1のスイッチ素子SS1、SS2がオンになり、ノードNC、N1がGNDに設定される。またD/A変換回路DAC1のスイッチ素子SA1〜SA4、SB1〜SB4を介して、キャパシタCA1〜CA4、CB1〜CB4の他端がVINの電圧レベルに設定される。 Next, the operation of this embodiment will be described in detail with reference to FIG. As shown in FIG. 12, in the sampling period of the input signal VIN, the switch elements SS1 and SS2 of the main D / A conversion circuit DAC1 are turned on, and the nodes NC and N1 are set to GND. Further, the other ends of the capacitors CA1 to CA4 and CB1 to CB4 are set to the voltage level of VIN via the switch elements SA1 to SA4 and SB1 to SB4 of the D / A conversion circuit DAC1.

これにより入力信号VINのサンプリングが行われる。そしてスイッチ素子SA1〜SA4、SB1〜SB4がオフすると、そのタイミングでの入力信号VINの電圧がホールドされる。なおサンプリング期間では、ダミーキャパシタ用のスイッチ素子SDMを介して、ダミーキャパシタCDMの他端がVINの電圧レベルに設定される。 As a result, the input signal VIN is sampled. When the switch elements SA1 to SA4 and SB1 to SB4 are turned off, the voltage of the input signal VIN at that timing is held. In the sampling period, the other end of the dummy capacitor CDM is set to a voltage level of VIN via the dummy capacitor switching element SDM.

またサンプリング期間では、コードシフト用のD/A変換回路DAC2のスイッチ素子SS3がオンになり、ノードN2がGNDに設定される。またスイッチ素子SC1〜SC4を介して、キャパシタCC1〜CC4の他端がGNDに設定される。これによりキャパシタCC1〜CC4の両端がGNDに設定され、電荷が蓄積されない状態になる。 In the sampling period, the switch element SS3 of the D / A conversion circuit DAC2 for code shift is turned on, and the node N2 is set to GND. Also, the other ends of the capacitors CC1 to CC4 are set to GND via the switch elements SC1 to SC4. As a result, both ends of the capacitors CC1 to CC4 are set to GND, and no charge is accumulated.

次に、A/D変換の逐次比較期間になると、メインのD/A変換回路DAC1のスイッチ素子SS1、SS2がオフになる。またダミーキャパシタ用のスイッチ素子SDMの他端はGNDに設定される。 Next, in the successive comparison period of A / D conversion, the switch elements SS1 and SS2 of the main D / A conversion circuit DAC1 are turned off. The other end of the dummy capacitor switching element SDM is set to GND.

そして、逐次比較用データRDAの各ビットに基づいて、DAC1のスイッチ素子SA1〜SA4、SB1〜SB4がスイッチ制御され、キャパシタCA1〜CA4、CB1〜CB4の他端はVREF又はGNDに設定される。 Based on each bit of the successive approximation data RDA, the switch elements SA1 to SA4 and SB1 to SB4 of the DAC1 are switch-controlled, and the other ends of the capacitors CA1 to CA4 and CB1 to CB4 are set to VREF or GND.

例えば逐次比較用データがRDA=10000000である場合には、RDAのMSBに対応するキャパシタCA4の他端は基準電圧VREFに設定される。また、他のキャパシタCA3〜CA1、CB4〜CB1の他端はGNDに設定される。 For example, when the successive approximation data is RDA = 10000000, the other end of the capacitor CA4 corresponding to the MSB of RDA is set to the reference voltage VREF. The other ends of the other capacitors CA3 to CA1 and CB4 to CB1 are set to GND.

また逐次比較用データがRDA=10001000である場合には、キャパシタCA4とCB4の他端はVREFに設定される。また、他のキャパシタCA3〜CA1、CB3〜CB1の他端はGNDに設定される。 When the successive approximation data is RDA = 10001000, the other ends of the capacitors CA4 and CB4 are set to VREF. The other ends of the other capacitors CA3 to CA1 and CB3 to CB1 are set to GND.

またA/D変換の逐次比較期間になると、コードシフト用のD/A変換回路DAC2のスイッチ素子SS3がオフになる。そして、コードデータCDAの各ビットに基づいて、DAC2のスイッチ素子SC1〜SC4がスイッチ制御され、キャパシタCC1〜CC4の他端はVREF又はGNDに設定される。

In the successive comparison period of A / D conversion, the switch element SS3 of the D / A conversion circuit DAC2 for code shift is turned off. Based on each bit of the code data CDA, the switch elements SC1 to SC4 of the

例えばコードデータがCDA=1000である場合には、キャパシタCC4の他端はVREFに設定され、他のキャパシタCC3〜CC1の他端はGNDに設定される。またコードデータがCDA=1100である場合には、キャパシタCC4、CC3の他端はVREFに設定され、他のキャパシタCC2、CC1の他端はGNDに設定される。 For example, when the code data is CDA = 1000, the other end of the capacitor CC4 is set to VREF, and the other ends of the other capacitors CC3 to CC1 are set to GND. When the code data is CDA = 1100, the other ends of the capacitors CC4 and CC3 are set to VREF, and the other ends of the other capacitors CC2 and CC1 are set to GND.

この場合にコードデータCDAは、図12に示す1回のA/D変換タイミング毎に変化する。即ちサンプリング期間及び逐次比較期間により構成される1回のA/D変換期間毎にコードデータCDAは変化する。なお複数回のA/D変換タイミング毎にコードデータCDAを変化させてもよい。 In this case, the code data CDA changes at each A / D conversion timing shown in FIG. That is, the code data CDA changes for each A / D conversion period constituted by the sampling period and the successive approximation period. Note that the code data CDA may be changed at every A / D conversion timing.

図11の電荷再分配型のA/D変換回路においては、VINのサンプリング信号(サンプリング電圧)と、D/A出力信号とコード信号(コード電圧)の加算信号(加算電圧)との比較処理が行われる。この場合には図1の制御回路20は、逐次比較レジスターSARの逐次比較結果データQDAにコードデータCDAを加算する処理を行うことになる。

In the charge redistribution type A / D conversion circuit of FIG. 11, comparison processing of a VIN sampling signal (sampling voltage) and a D / A output signal and a code signal (code voltage) addition signal (addition voltage) is performed. Done. In this case, the

具体的にはサンプリング期間においては、入力信号VINに応じた電荷がキャパシタCA1〜CA4、CB1〜CB4に蓄積される。そして、このVINに応じて蓄積された電荷と、逐次比較期間において逐次比較用データRDA及びコードデータCDAに応じてキャパシタCA1〜CA4、CB1〜CB4、CC1〜CC4に蓄積された電荷とが比較される。そして、両者の電荷が一致した時の逐次比較用データRDAが、逐次比較結果データQDAとして逐次比較レジスターSARから出力される。そして、この逐次比較結果データQDAにコードデータCDAを加算したデータが、入力信号VINをA/D変換したデータDOUTとして出力されることになる。このようにすることで、図3(B)に示すようなコードデータCDAによるコードシフトを実現しながら、適正なA/D変換データを出力できるようになる。 Specifically, in the sampling period, charges corresponding to the input signal VIN are accumulated in the capacitors CA1 to CA4 and CB1 to CB4. Then, the charge accumulated according to VIN is compared with the charges accumulated in capacitors CA1 to CA4, CB1 to CB4, and CC1 to CC4 according to successive comparison data RDA and code data CDA in the successive approximation period. The Then, the successive approximation data RDA when the two charges coincide is output from the successive approximation register SAR as successive comparison result data QDA. Data obtained by adding the code data CDA to the successive comparison result data QDA is output as data DOUT obtained by A / D converting the input signal VIN. In this way, it is possible to output appropriate A / D conversion data while realizing code shift based on the code data CDA as shown in FIG.

図13に本実施形態の第2の比較例のA/D変換回路を示す。この第2の比較例は、図2の第1の比較例を電荷再分配型で実現した例であり、D/A変換回路DAC(及びS/H回路330)は、キャパシタアレイ部321、スイッチアレイ部331、スイッチ素子SSにより実現される。

FIG. 13 shows an A / D conversion circuit of a second comparative example of the present embodiment. The second comparative example is an example in which the first comparative example of FIG. 2 is realized by a charge redistribution type. The D / A conversion circuit DAC (and the S / H circuit 330) includes a

A/D変換回路の変換精度を決める大きな要因となるのは、DACの変換精度である。図13の第2の比較例において、DACの分解能をnビットとすると、キャパシタアレイ部321は、バイナリに重み付けされたn個のキャパシタCA1〜CAnと、1個のダミーキャパシタCDMにより構成される。そしてサンプリング期間では、キャパシタCA1〜CAnの他端は入力信号VINに接続され、比較ノードNCはGNDに設定される。

The major factor that determines the conversion accuracy of the A / D conversion circuit is the DAC conversion accuracy. In the second comparative example of FIG. 13, assuming that the DAC resolution is n bits, the

そして逐次比較期間において、最上位ビットであるMSBから順次、逐次比較処理が行われる。具体的には、キャパシタCA1〜CAnの他端を、スイッチアレイ部331のスイッチ素子SA1〜SAnを用いて、D/A変換回路の入力値に応じて、基準電圧VREFもしくはGNDに接続されるかを切り替える。これより比較回路310の反転入力端子の比較ノードNCの電圧は、DACの出力値からVINのサンプリング電圧を引いた電圧になる。

Then, in the successive approximation period, successive approximation processing is performed sequentially from the MSB that is the most significant bit. Specifically, the other end of the capacitors CA1 to CAn is connected to the reference voltage VREF or GND according to the input value of the D / A conversion circuit using the switch elements SA1 to SAn of the

しかしながら、図13の第2の比較例では、A/D変換回路の分解能を例えば12ビットにするために、DACの分解能を12ビットにすると、合計で212×Cの容量値が必要になってしまう。このため、回路が大規模化すると共に、キャパシタを充電するために大きな電流が必要になってしまう。A/D変換回路の分解能を高くするほど、この傾向は強くなるため、図13の第2の比較例には高ビット化に限界があるという問題がある。 However, in the second comparative example of FIG. 13, if the resolution of the DAC is set to 12 bits in order to set the resolution of the A / D conversion circuit to 12 bits, for example, a total capacitance value of 2 12 × C is required. End up. For this reason, the circuit becomes large and a large current is required to charge the capacitor. Since this tendency becomes stronger as the resolution of the A / D conversion circuit is increased, there is a problem that the second comparative example in FIG.

図14にA/D変換の第3の比較例を示す。この第3の比較例は、上述の第2の比較例の問題を解決するために、直列キャパシタCSを設け、バイナリに重み付けされたキャパシタを複数段にする構成にしている。即ち、一端が比較ノードNCに接続され、他端がノードN1に接続される直列キャパシタCSを設ける。また比較ノードNCに接続されるキャパシタアレイ部341及びそのスイッチ制御を行うスイッチアレイ部351と、ノードN1に接続されるキャパシタアレイ部342及びそのスイッチ制御を行うスイッチアレイ部352を設ける。

FIG. 14 shows a third comparative example of A / D conversion. In the third comparative example, in order to solve the problem of the second comparative example described above, a series capacitor CS is provided, and a binary weighted capacitor is provided in a plurality of stages. That is, a series capacitor CS having one end connected to the comparison node NC and the other end connected to the node N1 is provided. In addition, a

図14の第3の比較例の構成によれば、例えばキャパシタアレイ部341のキャパシタCA1の容量値と、キャパシタアレイ部342のキャパシタCB1の容量値を同じにできる。従って8ビットの場合を例にとると、図13の第2の比較例では28×Cの容量値が必要になるが、図14の第3の比較例では25×Cの容量値で済む。このため、回路の小面積化を図れると共にキャパシタの充電電流も小さくできる。

According to the configuration of the third comparative example in FIG. 14, for example, the capacitance value of the capacitor CA1 of the

ところが、図14の第3の比較例では、ノードN1に寄生する容量がDACのDNL(Differential Non Linearity)やINL(Integral Non Linearity)を劣化させるという問題が生じる。これは、バイナリごとに重み付けされた容量比が、寄生容量によって狂うことが原因である。この悪影響は、図14の8ビットの場合を例にとると、LSBから5ビット目が変化するコード付近で顕著に生じる。具体的には00001111と00010000(MSBが先頭)の変わり目で生じ、図3(A)に示すようなミッシングコードの問題が発生する。 However, in the third comparative example of FIG. 14, there is a problem that the capacitance parasitic to the node N1 deteriorates the DNL (Differential Non Linearity) or INL (Integral Non Linearity) of the DAC. This is because the capacitance ratio weighted for each binary is distorted by the parasitic capacitance. In the case of 8 bits in FIG. 14 as an example, this adverse effect is prominent in the vicinity of the code where the fifth bit changes from the LSB. Specifically, it occurs at the transition between 00001111 and 00010000 (MSB is first), and a problem of a missing code as shown in FIG. 3A occurs.

このような問題を解決する手法として、直列キャパシタCSの容量値をトリミングして、特性を微調整する手法も考えられる。しかしながら、トリミングだけでは、トリミングできる容量単位や範囲に限界がある。また製造工程にトリミング工程が必要になり、高コスト化等を招く。またA/D変換データをデジタル補正するデジタル補償処理などを行って、高精度化を図る手法も考えられるが、処理が繁雑化すると共に余分な処理が必要になってしまうという問題がある。 As a technique for solving such a problem, a technique of trimming the capacitance value of the series capacitor CS and finely adjusting the characteristics can be considered. However, with trimming alone, there is a limit to the capacity unit and range that can be trimmed. In addition, a trimming process is required in the manufacturing process, resulting in high costs. Although a method for achieving high accuracy by performing digital compensation processing for digitally correcting A / D conversion data is conceivable, there is a problem that processing becomes complicated and extra processing is required.

次に、図15を用いて、ノードNC、N1に寄生容量CP1、CP2が付加された場合のSAR型ADCの理論式について説明する。寄生容量CP1、CP2を含まない理論式は、CP1、CP2を0にすれば導出できる。なお、キャパシタCA1及びCB1、CA2及びCB2、CA3及びCB3、CA4及びCB4の容量値を、各々、C、2C、4C、8Cとする。また直列キャパシタCSの容量値をCとする。またダミーキャパシタCDMは、サンプリング時に充電される電荷量を調整する目的(フルスケール調整)で用いられるものであるが、ここでは説明の簡素化のためにダミーキャパシタCDMの容量値は無視する。 Next, a theoretical formula of the SAR type ADC when the parasitic capacitances CP1 and CP2 are added to the nodes NC and N1 will be described with reference to FIG. A theoretical formula that does not include the parasitic capacitances CP1 and CP2 can be derived by setting CP1 and CP2 to zero. Capacitance values of capacitors CA1 and CB1, CA2 and CB2, CA3 and CB3, CA4 and CB4 are C, 2C, 4C, and 8C, respectively. The capacitance value of the series capacitor CS is C. The dummy capacitor CDM is used for the purpose of adjusting the amount of charge charged at the time of sampling (full scale adjustment), but here the capacitance value of the dummy capacitor CDM is ignored for the sake of simplicity of explanation.

図15はサンプリング期間でのスイッチ素子の状態を示している。このサンプリング期間においてノードNCに充電される電荷量Q1は下式(1)のように表される。 FIG. 15 shows the state of the switch element during the sampling period. The amount of charge Q1 charged in the node NC during this sampling period is expressed by the following equation (1).

またサンプリング期間においてノードN1に充電される電荷量Q2は下式(2)のように表される。 In addition, the amount of charge Q2 charged in the node N1 during the sampling period is expressed by the following equation (2).

なお直列キャパシタCS及び寄生容量CP1、CP2は、両端の電圧がGND(接地電位)であるため、電荷は充電されない。 The series capacitor CS and the parasitic capacitances CP1 and CP2 are not charged because the voltage at both ends is GND (ground potential).

次に、逐次比較期間でのノードNCの電圧V1とノードN1の電圧V2を求める。例えば図15において、スイッチ素子SB1〜SB4は、逐次比較用データRDAの下位の4ビットD0〜D3によりスイッチ制御され、スイッチ素子SA1〜SA4は、RDAの上位の4ビットD4〜D7によりスイッチ制御される。具体的には、ビットDi=1(0≦i≦7)の場合にはVINに接続され、ビットDi=0の場合にはGNDに接続される。この場合に、逐次比較期間においてノードNC、N1に蓄積される電荷量Q1、Q2は下式(3)、(4)のように表される。 Next, the voltage V1 of the node NC and the voltage V2 of the node N1 in the successive approximation period are obtained. For example, in FIG. 15, the switch elements SB1 to SB4 are switched by the lower 4 bits D0 to D3 of the successive approximation data RDA, and the switch elements SA1 to SA4 are switched by the upper 4 bits D4 to D7 of the RDA. The Specifically, when bit Di = 1 (0 ≦ i ≦ 7), it is connected to VIN, and when bit Di = 0, it is connected to GND. In this case, the charge amounts Q1 and Q2 accumulated in the nodes NC and N1 in the successive approximation period are expressed as the following equations (3) and (4).

そして電荷保存の法則により、式(1)と式(3)の電荷量Q1は等しく、式(2)と式(4)の電荷量Q2は等しい。また、逐次比較用データRDAの全てのビットD0〜D7についての比較動作が完了したときには、比較回路310の反転入力端子のノードNCの電圧は、非反転入力端子のGNDと等しくなるため、下式(5)が成立する。

Then, according to the law of charge conservation, the amount of charge Q1 in the equations (1) and (3) is equal, and the amount of charge Q2 in the equations (2) and (4) is equal. When the comparison operation for all the bits D0 to D7 of the successive approximation data RDA is completed, the voltage of the node NC of the inverting input terminal of the

従って、式(1)〜(5)の連立方程式をVINについて解くと、下式(6)が導かれる。 Therefore, solving the simultaneous equations of the equations (1) to (5) for VIN leads to the following equation (6).

式(6)から明らかなように、VINのA/D変換結果には、ノードNCの寄生容量CP1の影響はなく、ノードN2の寄生容量CP2だけが特性に悪影響を与える。従って、寄生容量CP2の悪影響を低減するために直列キャパシタCSのトリミングが必要になる。また式(6)から、寄生容量CP2の悪影響はD4以上のビットに対応するスイッチ素子の接続が変化するときに現れ、これにより図3(A)に示すようなミッシングコードが発生することが理解される。 As is apparent from the equation (6), the A / D conversion result of VIN is not affected by the parasitic capacitance CP1 of the node NC, and only the parasitic capacitance CP2 of the node N2 adversely affects the characteristics. Therefore, the series capacitor CS needs to be trimmed in order to reduce the adverse effect of the parasitic capacitance CP2. Also, from equation (6), it can be understood that the adverse effect of the parasitic capacitance CP2 appears when the connection of the switch element corresponding to the bit of D4 or more changes, thereby generating a missing code as shown in FIG. Is done.

なお、図16(A)、図16(B)はDNL、INLの説明図である。図16(A)に示すDNLは、理想的なコード幅と測定されたコード幅の差分である。例えば図16(A)では、DNLの特性の悪化により、010のコードの幅が狭くなり、011のコードの幅が広くなっている。そして010のコードの幅が更に狭くなって消失すると、010のコードは図3(A)のようなミッシングコードになる。

16A and 16B are explanatory diagrams of DNL and INL. DNL shown in FIG. 16A is the difference between the ideal code width and the measured code width. For example, in FIG. 16A, due to the deterioration of the DNL characteristics, the width of the

また図16(B)のINLは、ゲイン誤差とオフセット誤差を除去した後の、実際のコード遷移点(破線)と、それに対応する理想的な遷移点(実線)の最大偏差である。正のINLは、遷移が理想よりも遅れていることを示し、負のINLは、遷移が理想よりも早いことを示している。 In FIG. 16B, INL is the maximum deviation between the actual code transition point (broken line) and the corresponding ideal transition point (solid line) after the gain error and offset error are removed. A positive INL indicates that the transition is later than ideal, and a negative INL indicates that the transition is earlier than ideal.

図17(A)、図17(B)にDNLのシミュレーション結果例を示す。ここでは、後述する全差動型のA/D変換回路を用い、メインのDAC1が14ビットであり、コードシフト用のDAC2が4ビットの場合を例にとり説明する。図11では、メインのDAC1は、4ビット+4ビットの2段の直列構成になっているが、14ビットのメインのDAC1の場合には、6ビット+4ビット+4ビットの3段構成になる。

FIG. 17A and FIG. 17B show examples of simulation results of DNL. Here, a case will be described as an example in which a fully differential A / D conversion circuit described later is used, the

図17(A)は本実施形態のコードシフト手法を採用しなかった場合のDNLのシミュレーション結果例である。図17(A)では、DNLが1LSB以上になるミッシングコードが発生している。 FIG. 17A is an example of a DNL simulation result when the code shift method of this embodiment is not employed. In FIG. 17A, a missing code with a DNL of 1 LSB or more is generated.

図17(B)は本実施形態のコードシフト手法を採用した場合のDNLのシミュレーション結果例である。図17(B)では、DNLが1LSB未満になっており、ミッシングコードの発生が防止されている。 FIG. 17B is an example of a DNL simulation result when the code shift method of the present embodiment is employed. In FIG. 17B, DNL is less than 1 LSB, and the occurrence of missing codes is prevented.

以上のように本実施形態によれば、図14の第3の比較例に対して、図11に示すようにコードシフト用のDAC2を追加し、DAC2によりコードデータの信号を加算することで、コードシフトを実現している。

As described above, according to the present embodiment, by adding the

即ち図14の第3の比較例では、ノードN1の寄生容量CP2が原因で、図3(A)や図17(A)に示すようなミッシングコードが発生している。これに対して本実施形態では、時間的に変化するコードデータの信号をDAC2により加算することで、特定のコードで発生していたDNLの悪化(ミッシングコード)を周囲のコードに時間的に拡散させる。例えばミッシングコードが00010000というようにMLSBから4ビット目で発生する場合に、0000〜1111のデータ範囲で変化するランダムなコードデータの信号を加算する。こうすることで、図3(B)や図17(B)に示すように、DNLを1LSB未満に抑えて、ミッシングコードの発生を防止できる。従って、回路規模を小さくするために直列キャパシタCS1を設けた場合にも、ノードN1の寄生容量を原因とするミッシングコードの発生を防止できる。この結果、回路規模の縮小化と、A/D変換特性の劣化防止とを両立することが可能になる。

That is, in the third comparative example of FIG. 14, the missing codes as shown in FIGS. 3A and 17A are generated due to the parasitic capacitance CP2 of the node N1. On the other hand, in this embodiment, the code data signal that changes over time is added by the

6.全差動型

図18に本実施形態のコードシフト手法を適用した全差動型のA/D変換回路の構成例を示す。図18のA/D変換回路は、比較回路10と、比較回路10の非反転入力端子に接続されるメインのD/A変換回路DAC1Pと、反転入力端子に接続されるメインのD/A変換回路DAC1Nを含む。また、比較回路10の非反転入力端子に接続されるコードシフト用のD/A変換回路DAC2Pと、反転入力端子に接続されるコードシフト用のD/A変換回路DAC2Nを含む。

6). Fully Differential Type FIG. 18 shows a configuration example of a fully differential type A / D conversion circuit to which the code shift method of this embodiment is applied. The A / D conversion circuit of FIG. 18 includes a

非反転側(正側)のメインのDAC1P及び反転側(負側)のメインのDAC1Nの構成は、図11のメインのDAC1と同様に、キャパシタアレイ部とスイッチアレイ部を含む。そしてDAC1Pには、差動信号を構成する非反転側(正側)の入力信号PINが入力され、DAC1Nには、差動信号を構成する反転側(負側)の入力信号NINが入力される。

The configuration of the main DAC 1P on the non-inversion side (positive side) and the main DAC 1N on the inversion side (negative side) includes a capacitor array unit and a switch array unit, similarly to the

そしてサンプリング期間では、DAC1PのノードNCP、N1Pは、スイッチ素子SS1P、SS2Pによりコモン電圧(中間電圧)VCMに設定される。またDAC1NのノードNCN、N1Nは、スイッチ素子SS1N、SS2Nによりコモン電圧VCMに設定される。 In the sampling period, the nodes NCP and N1P of the DAC 1P are set to the common voltage (intermediate voltage) VCM by the switch elements SS1P and SS2P. The nodes NCN and N1N of the DAC 1N are set to the common voltage VCM by the switch elements SS1N and SS2N.

またサンプリング期間では、DAC1Pのスイッチ素子SA1P〜SA4P、SB1P〜SB4Pの一端は、差動信号の非反転側の信号PINに接続され、DAC1Nのスイッチ素子SA1N〜SA4N、SB1N〜SB4Nの一端は、差動信号の反転側の信号NINに接続される。 In the sampling period, one end of the switch elements SA1P to SA4P and SB1P to SB4P of the DAC 1P is connected to the signal PIN on the non-inversion side of the differential signal, and one end of the switch elements SA1N to SA4N and SB1N to SB4N of the DAC 1N It is connected to the signal NIN on the inversion side of the motion signal.

一方、逐次比較期間では、DAC1Pのスイッチ素子SA1P〜SA4P、SB1P〜SB4Pの一端は、逐次比較用データの対応するビットが「1」である場合にはVREFに接続され、「0」である場合にはGNDに接続される。 On the other hand, in the successive approximation period, one end of the switching elements SA1P to SA4P and SB1P to SB4P of the DAC 1P is connected to VREF when the corresponding bit of the successive approximation data is “1”, and is “0”. Is connected to GND.

これに対して、DAC1Nのスイッチ素子SA1N〜SA4N、SB1N〜SB4Nの一端は、逐次比較用データの対応するビットが「1」である場合にはGNDに接続され、「0」である場合にはVREFに接続される。 On the other hand, one end of the switching elements SA1N to SA4N and SB1N to SB4N of the DAC 1N is connected to the GND when the corresponding bit of the successive approximation data is “1”, and is one when the bit is “0”. Connected to VREF.

非反転側のコードシフト用のDAC2P及び反転側のコードシフト用のDAC2Nは、図11のコードシフト用のDAC2と同様に、キャパシタアレイ部とスイッチアレイ部を含む。

The non-inverted code shift DAC 2P and the inverted code shift DAC 2N include a capacitor array unit and a switch array unit, similar to the

そしてサンプリング期間では、DAC2PのノードN2Pは、スイッチ素子SS3PによりVCMに設定される。またDAC2NのノードN2Nは、スイッチ素子SS3NによりVCMに設定される。またDAC2Pのスイッチ素子SC1P〜SC4P及びDAC2Nのスイッチ素子SC1N〜SC4Nの一端はVCMに接続される。 In the sampling period, the node N2P of the DAC 2P is set to VCM by the switch element SS3P. The node N2N of the DAC 2N is set to VCM by the switch element SS3N. Further, one ends of the switching elements SC1P to SC4P of the DAC 2P and the switching elements SC1N to SC4N of the DAC 2N are connected to the VCM.

一方、逐次比較期間では、DAC2Pのスイッチ素子SC1P〜SC4Pの一端は、コードデータの対応するビットが「1」である場合にはVREFに接続され、「0」である場合にはGNDに接続される。これに対して、DAC2Nのスイッチ素子SC1N〜SC4Nの一端は、コードデータの対応するビットが「1」である場合にはGNDに接続され、「0」である場合にはVREFに接続される。 On the other hand, in the successive approximation period, one end of the switch elements SC1P to SC4P of the DAC 2P is connected to VREF when the corresponding bit of the code data is “1”, and is connected to GND when the bit is “0”. The On the other hand, one end of each of the switching elements SC1N to SC4N of the DAC 2N is connected to GND when the corresponding bit of the code data is “1”, and is connected to VREF when the bit is “0”.

図18の構成によっても、コードシフト手法により、A/D変換回路のDNLやINLを改善し、ミッシングコード等の発生を防止できる。また全差動型でA/D変換回路を構成することで、振幅を大きく取ることができ、S/N比を向上できると共に、コモンモードノイズの影響を低減できる。 18 can also improve the DNL and INL of the A / D conversion circuit by the code shift method, and prevent the occurrence of missing codes and the like. Further, by configuring the A / D conversion circuit as a fully differential type, the amplitude can be increased, the S / N ratio can be improved, and the influence of common mode noise can be reduced.

7.電子機器

図19に本実施形態のA/D変換回路を含む電子機器の構成例を示す。この電子機器は、センサー510、検出回路520、A/D変換回路530、処理部540を含む。なおこれらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば検出回路520、A/D変換回路530、処理部540は集積回路装置により実現できる。

7). Electronic Device FIG. 19 shows a configuration example of an electronic device including the A / D conversion circuit of this embodiment. This electronic device includes a

図19の電子機器としては、例えば生体計測機器(脈拍計、歩数計等)、携帯型情報端末、映像機器(デジタルカメラ、ビデオカメラ)、時計などの種々の機器を想定できる。 As the electronic device in FIG. 19, various devices such as a biological measurement device (pulse meter, pedometer, etc.), a portable information terminal, a video device (digital camera, video camera), and a clock can be assumed.

センサー510は、ジャイロセンサー、加速度センサー、フォトセンサー、圧力センサー等であって、電子機器の用途に応じた様々なセンサーが用いられる。検出回路520はセンサー510から出力されるセンサー信号を増幅して、所望信号を抽出する。またA/D変換回路530は検出回路520からの検出信号(所望信号)をデジタルデータに変換して、処理部540へ出力する。