JP5735981B2 - 離散時間量子化信号の連続時間連続可変信号への変換 - Google Patents

離散時間量子化信号の連続時間連続可変信号への変換 Download PDFInfo

- Publication number

- JP5735981B2 JP5735981B2 JP2012544832A JP2012544832A JP5735981B2 JP 5735981 B2 JP5735981 B2 JP 5735981B2 JP 2012544832 A JP2012544832 A JP 2012544832A JP 2012544832 A JP2012544832 A JP 2012544832A JP 5735981 B2 JP5735981 B2 JP 5735981B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- input

- signal

- discrete

- noise shaping

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000007493 shaping process Methods 0.000 claims description 120

- 238000013139 quantization Methods 0.000 claims description 111

- 230000004044 response Effects 0.000 claims description 81

- 238000012545 processing Methods 0.000 claims description 67

- 238000012546 transfer Methods 0.000 claims description 39

- 238000005070 sampling Methods 0.000 claims description 34

- 238000006243 chemical reaction Methods 0.000 claims description 26

- 230000009021 linear effect Effects 0.000 claims description 26

- 238000013507 mapping Methods 0.000 claims description 20

- 239000002131 composite material Substances 0.000 claims 4

- 238000005259 measurement Methods 0.000 claims 2

- 230000006870 function Effects 0.000 description 43

- 238000000034 method Methods 0.000 description 40

- 238000000354 decomposition reaction Methods 0.000 description 34

- 238000010586 diagram Methods 0.000 description 23

- 238000007792 addition Methods 0.000 description 16

- 238000001914 filtration Methods 0.000 description 12

- 230000008901 benefit Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 238000005457 optimization Methods 0.000 description 7

- 230000003044 adaptive effect Effects 0.000 description 6

- 239000000872 buffer Substances 0.000 description 5

- 238000007796 conventional method Methods 0.000 description 5

- 230000001419 dependent effect Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 238000006731 degradation reaction Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000015654 memory Effects 0.000 description 3

- 230000003595 spectral effect Effects 0.000 description 3

- 238000012935 Averaging Methods 0.000 description 2

- 102400000267 Rhomboid-related protein 2, N-terminal fragment Human genes 0.000 description 2

- 101800000645 Rhomboid-related protein 2, N-terminal fragment Proteins 0.000 description 2

- 101800000716 Tumor necrosis factor, membrane form Proteins 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000000593 degrading effect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000008030 elimination Effects 0.000 description 2

- 238000003379 elimination reaction Methods 0.000 description 2

- 238000011156 evaluation Methods 0.000 description 2

- 238000009499 grossing Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000003278 mimic effect Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000007781 pre-processing Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 230000006978 adaptation Effects 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000001364 causal effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000012993 chemical processing Methods 0.000 description 1

- 230000001149 cognitive effect Effects 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007812 deficiency Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 229920005994 diacetyl cellulose Polymers 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 230000009022 nonlinear effect Effects 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000003362 replicative effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/50—Digital/analogue converters using delta-sigma modulation as an intermediate step

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/358—Continuously compensating for, or preventing, undesired influence of physical parameters of non-linear distortion, e.g. instability

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/50—Digital/analogue converters using delta-sigma modulation as an intermediate step

- H03M3/502—Details of the final digital/analogue conversion following the digital delta-sigma modulation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M7/00—Conversion of a code where information is represented by a given sequence or number of digits to a code where the same, similar or subset of information is represented by a different sequence or number of digits

- H03M7/30—Compression; Expansion; Suppression of unnecessary data, e.g. redundancy reduction

- H03M7/3002—Conversion to or from differential modulation

- H03M7/3004—Digital delta-sigma modulation

- H03M7/3015—Structural details of digital delta-sigma modulators

- H03M7/302—Structural details of digital delta-sigma modulators characterised by the number of quantisers and their type and resolution

- H03M7/3024—Structural details of digital delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only

- H03M7/3026—Structural details of digital delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only the quantiser being a multiple bit one

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M7/00—Conversion of a code where information is represented by a given sequence or number of digits to a code where the same, similar or subset of information is represented by a different sequence or number of digits

- H03M7/30—Compression; Expansion; Suppression of unnecessary data, e.g. redundancy reduction

- H03M7/3002—Conversion to or from differential modulation

- H03M7/3004—Digital delta-sigma modulation

- H03M7/3015—Structural details of digital delta-sigma modulators

- H03M7/3031—Structural details of digital delta-sigma modulators characterised by the order of the loop filter, e.g. having a first order loop filter in the feedforward path

- H03M7/3033—Structural details of digital delta-sigma modulators characterised by the order of the loop filter, e.g. having a first order loop filter in the feedforward path the modulator having a higher order loop filter in the feedforward path, e.g. with distributed feedforward inputs

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

- Analogue/Digital Conversion (AREA)

Description

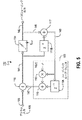

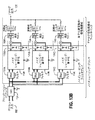

上述した実施形態において、ノイズシェーピング/量子化回路(例えば、112及び122)の各々は、図2A、図2B及び図3に示すものとは異なるように構築されるのが好ましい。好適な実施形態において、各処理ブランチ110又は120内の回路112又は122が効果、構築の容易さ及び構成の容易さの最適な組み合わせを達成することが分かっているため、本明細書においてマルチレート・デルタ−シグマ(μΔΣ)変調器と呼ばれる変更された誤差フィードバック構造は、そのような回路の変換ノイズシェーピング部分に使用される。なお、本発明の別の実施形態において、従来のデルタ−シグマ(ΔΣ)変調器を含む他の種類のノイズシェーピング回路を使用できる。いずれの場合においても、使用されるノイズシェーピング回路に対する主な検討事項は、非常に高いサンプリングレートにおいて安定した正確な動作を得られることが好ましいということである。従って、好適な実施形態に係る各ノイズシェーピング回路は少なくとも以下の3つの特性を有する。すなわち、(1)量子化/丸め誤差、サンプリング不確実性/ジッタ及び熱雑音に関連する性能低下等のノイズシェーピング回路の主な性能低下は、ノイズシェーピング応答の影響を受ける。(2)ノイズシェーピング回路は、4次以上のノイズシェーピング次数を有する安定した応答を生成する。(3)ノイズシェーピング回路の有効オーバサンプリング比は、構成要素の最大クロック周波数により制限されない。(4)NTFのヌルがプログラム可能パラメータ(例えば、ノイズシェーパ・フィードバックループフィルタ係数)の値により判定されるように、ノイズシェーピング回路はオールパス(又は少なくともほぼオールパス)信号伝達関数(STF)と帯域消去雑音伝達関数(NTF)とを有する。以下に更に詳細に説明するように、整形される雑音は、使用されるあらゆる量子化回路(例えば、回路112の内部にあり且つ図5に示す量子化回路114)により発生される雑音を含むが、マルチビット−可変レベル信号変換器113等の他の構成要素により発生される雑音を更に(又は代わりに)含む可能性がある。これらの特性を達成することは、一般にノイズシェーピング機能に対して従来のデルタ−シグマ変調器を使用することを含まない。

本発明の好適な実施形態に係るMBO信号再構成において使用されるバンドパスフィルタ(例えば、フィルタ115及び125)に対する主な検討事項は、(1)設計計算量(フィルタ品質ファクタ及び次数に関して表されるのが好ましい)、(2)周波数応答(特に、ストップバンド減衰量)及び(3)振幅及び位相歪みである。最適な変換器の分解能性能は、一般にフィルタ次数の増加と共に増加する大きいストップバンド減衰量を示す周波数応答を有する変換雑音除去フィルタ(すなわち、バンドパス又は信号再構成フィルタ115)に対して取得される。更に、フィルタ応答は、デジタル・プリディストーション・リニアライザ(DPL)104の計算量を最小限にするために可能な限り少ない振幅及び位相歪みを発生させるのが好ましい。変換器インタリーブファクタ(M)を増加することにより実現される性能向上は、フィルタの3dBの帯域に対するフィルタ中心周波数の比(すなわち、fC/f3dB)として定義される再構成フィルタの品質ファクタの比例した増加に左右される。本発明の好適な実施形態に係るMBO変換器の場合、品質ファクタは再構成フィルタバンクにおける最大周波数フィルタに対して算出される(すなわち、fC=1/2fS)。従って、アナログフィルタ(例えば、フィルタ115及び125)に対する好適な品質ファクタは、変換器のインタリーブファクタに直接関連し、より好適にはMと等しい。現在、標準的な集中定数素子又は分布定数素子アナログフィルタに対する品質ファクタは約30に制限される。その結果、MBO変換器に対するインタリーブファクタに対する一般的な実際の制限はM?32である。しかし、32個のフィルタから成るアナログ再構成フィルタバンクと関連する計算量のために、本発明の好適な実施形態は、インタリーブファクタをM=16以下(すなわち、16個以下のアナログフィルタ115のバンク)に制限する。

本発明の好適な実施形態において、図4及び図5に示すノイズシェーピング/量子化回路112の2進重み付き出力は、変更された従来の抵抗ラダー型回路網を使用して単一の比例アナログ電圧レベルに変換される。しかし、電流源を含むマルチビット信号を単一の可変レベル出力に変換する他の従来の方法が代わりに使用されてもよく、本発明の範囲内であると考えられるべきである。本明細書において抵抗ラダー型回路網を参照するが、そのような参照は単なる例示であり、一般に他のあらゆるマルチビット−可変レベル信号変換器に対する参照と置換できることが理解されるべきである。

デジタル・プリディストーション・リニアライザ(DPL)104とノイズシェーピング/量子化回路112内のμΔΣ変調器とは、マルチレート(ポリフェーズ)構造として実現可能であるため、図4に示す(マルチレートDPL104及びマルチレートノイズシェーピング/量子化回路112を含むより具体的で詳細な実施形態を図12に示す)変換器技術の瞬時帯域幅は、抵抗ラダー型回路網113を駆動するデジタル出力バッファの最大スイッチングレート及びアナログ再構成フィルタ(例えば、フィルタ115及び125)によってのみ制限される。

一般に、明示的に示さない限り、本明細書で説明するシステム、方法、機能性及び技術の全ては、1つ以上のプログラマブル汎用コンピューティングデバイスを使用して実現される。一般にそのようなデバイスは、例えば共通バスを介して相互接続される以下の構成要素、すなわち1つ以上の中央処理装置(CPU)と、読み出し専用メモリ(ROM)と、ランダムアクセスメモリ(RAM)と、他のデバイスとインタフェースする(例えば、シリアルポート、パラレルポート、USB接続又はFirewire接続等のハードワイヤード接続を使用するか又はBluetooth(登録商標)又は802.11プロトコル等の無線プロトコルを使用して)ための入出力ソフトウェア及び回路網と、符号分割多元接続(CDMA)、汎ヨーロッパデジタル移動通信システム(GSM(登録商標))、Bluetooth、802.11プロトコル又は他のあらゆるセルラシステム又は非セルラシステム等の無線プロトコル、あるいはEthernet(登録商標)カード等のハードワイヤード接続を使用して本発明の多くの実施形態においてインターネット又は他のあらゆるネットワークに接続する1つ以上のネットワークを接続するためのソフトウェア及び回路網と、ディスプレイ(ブラウン管ディスプレイ、液晶ディスプレイ、有機発光ディスプレイ、高分子発光ディスプレイ又は他のあらゆる薄膜ディスプレイ等)と、他の出力装置(1つ以上のスピーカ、ヘッドフォンセット及びプリンタ等)と、1つ以上の入力装置(マウス、タッチパッド、タブレット、タッチセンシティブディスプレイ又は他のポインティングデバイス、キーボード、キーパッド、マイク及びスキャナ等)と、大容量記憶装置(ハードディスクドライブ等)と、リアルタイムクロックと、取外し可能ストレージリード/ライトデバイス(例えばRAM、磁気ディスク、磁気テープ、光磁気ディスク又は光ディスク等からの読出し及びそれらへの書き込みのための)と、モデム(例えば、ダイヤルアップ接続を介してインターネット又は他のあらゆるコンピュータネットワークに接続するため又はファックスを送信するための)とのうちの少なくとも一部を含む。動作中、一般にそのような汎用コンピュータにより実行される範囲で上記方法及び機能性を実現する処理ステップは、最初に大容量記憶装置(例えば、ハードディスク)に格納され、RAMにダウンロードされ、RAMの外でCPUにより実行される。しかし、処理ステップは最初にRAM又はROMに格納される場合もある。

本発明のいくつかの異なる実施形態について、各々がある特定の特徴を含むものとして上述した。しかし、当業者には理解されるように、いずれかの単一の実施形態の説明と共に説明した特徴は、その実施形態に限定されず、他の実施形態のうちのいずれかの種々の組合せに含まれてもよく且つ/あるいは配置されてもよいことを意図する。

Claims (28)

- 離散時間量子化信号を連続時間連続可変信号に変換する装置であって、

時間及び値に関して離散的な入力信号を受け入れる入力線と、

前記入力線に結合された複数の処理ブランチであって、各処理ブランチが、(a)離散時間ノイズシェーピング/量子化回路、(b)前記離散時間ノイズシェーピング/量子化回路の出力に結合されたマルチビット−可変レベル信号変換器、(c)前記マルチビット−可変レベル信号変換器の出力に結合されたアナログ・バンドパスフィルタを含む、複数の処理ブランチと、

前記複数の処理ブランチの各々における前記アナログ・バンドパスフィルタの出力に結合された加算器と、

を備え、

前記複数の処理ブランチのうちの異なる処理ブランチにおける前記離散時間ノイズシェーピング/量子化回路は、異なる周波数で変換雑音周波数応答最小値を有し、

前記離散時間ノイズシェーピング/量子化回路の各々は、同一の処理ブランチにおける前記アナログ・バンドパスフィルタにより選択された周波数帯域に対応する変換雑音周波数応答最小値を有する

ことを特徴とする装置。 - 前記複数の処理ブランチの各々における前記離散時間ノイズシェーピング/量子化回路は、

入力と、

前記離散時間ノイズシェーピング/量子化回路の前記入力に結合された第1の入力、第2の入力及び出力を有する第2の加算器と、

信号のビット幅分解能を低下し、前記第2の加算器の前記出力に結合された入力を有し、且つ前記離散時間ノイズシェーピング/量子化回路の前記出力に結合された出力を有する量子化回路と、

前記量子化回路の前記出力に結合された入力及び前記第2の加算器の前記第2の入力に結合された出力を有するフィードバックループフィルタと、

を備えることを特徴とする請求項1に記載の装置。 - 前記量子化回路の前記入力は、前記量子化回路の前記入力及び前記出力の双方が前記フィードバックループフィルタを介して前記加算器の前記第2の入力に結合されるように前記フィードバックループフィルタの前記入力に結合されることを特徴とする請求項2に記載の装置。

- 前記量子化回路の前記出力は少なくとも4ビットを含むことを特徴とする請求項2記載の装置。

- 前記複数の処理ブランチのうちの少なくとも1つに対して、請求項2に記載の構成全体が複数の並列パスにわたり複製され、前記複数の並列パスにより出力されるサンプルは、共同で、前記離散時間ノイズシェーピング/量子化回路により出力される完全な信号を構成し、前記複数の並列パスにおける各パスのサンプルは、前記完全な信号の異なるサブサンプリング位相を表すことを特徴とする請求項2に記載の装置。

- 前記複数の処理ブランチの各々における前記フィードバックループフィルタは、複数の零点を含む変換雑音伝達関数を有し、前記零点のいずれも他の零点と等しくないことを特徴とする請求項2に記載の装置。

- 前記零点の各々は、6ビット以下で表される前記フィードバックループフィルタの設定可能なパラメータにより生成されることを特徴とする請求項6に記載の装置。

- 前記フィードバックループフィルタは、前記複数の処理ブランチにわたり同一の構造を有するが、少なくとも1つの設定可能なパラメータに対して異なる値を有することを特徴とする請求項2に記載の装置。

- 前記複数の処理ブランチのうちの少なくとも1つは、前記複数の処理ブランチのうちの当該少なくとも1つにおける前記マルチビット−可変レベル信号変換器の倍率パラメータの不完全性を補償するために非線形ビットマッピングを含むことを特徴とする請求項2に記載の装置。

- 前記非線形ビットマッピングは、出力変換雑音を最小限にする誤差計測値に基づいて動的に調整されることを特徴とする請求項9に記載の装置。

- 前記複数の処理ブランチの各々における前記マルチビット−可変レベル信号変換器は、重み付き抵抗器の回路網、重み付き電圧源の回路網又は重み付き電流源の回路網のうちの少なくとも1つを含むことを特徴とする請求項1に記載の装置。

- 前記入力線に結合された入力と前記処理ブランチに結合された出力とを有するデジタル・プリディストーション線形フィルタを更に備え、前記デジタル・プリディストーション線形フィルタは、前記処理ブランチにおける前記アナログ・バンドパスフィルタの組み合わせ伝達関数を表す合成伝達関数と畳み込まれる場合に少なくともほぼオールパス応答を生成する伝達関数を有することを特徴とする請求項1に記載の装置。

- 前記デジタル・プリディストーション線形フィルタは、ポリフェーズ構造として実現され、サブサンプリング位相毎に、前記デジタル・プリディストーション線形フィルタ全体のクロックレートの約数であるクロックレートで動作する部分構造を含むことを特徴とする請求項12に記載の装置。

- 前記デジタル・プリディストーション線形フィルタは、フィードフォワード成分及びフィードバック成分の双方を含むことを特徴とする請求項12に記載の装置。

- 前記アナログ・バンドパスフィルタは、バターワース、ベッセル及び楕円フィルタ構造のうちの少なくとも1つを含むことを特徴とする請求項1に記載の装置。

- 前記複数の処理ブランチの各々における前記離散時間ノイズシェーピング/量子化回路は、ポリフェーズ構造として実現され、別個の複数の並列な部分構造を含み、前記複数の並列な部分構造の出力が、共同で、前記離散時間ノイズシェーピング/量子化回路全体により出力される完全な信号を構成し、前記複数の並列な部分構造はそれぞれ、前記完全な信号の対応する異なるサブサンプリング位相を生成することを特徴とする請求項1に記載の装置。

- 前記部分構造の出力は、少なくとも1つのマルチプレクサを使用して単一の合成出力に組み合わされることを特徴とする請求項16に記載の装置。

- 前記部分構造の出力は、少なくとも1つの加算演算と少なくとも1つの遅延演算とを含む手段を使用して、連続時間信号として単一の合成出力に組み合わされることを特徴とする請求項16に記載の装置。

- 前記部分構造の出力は、加算演算を含む手段と共に逆移動平均フィルタを使用して単一の合成出力に組み合わされることを特徴とする請求項16に記載の装置。

- 離散時間量子化信号を連続時間連続可変信号に変換する装置であって、

時間及び値に関して離散的な入力信号を受け入れる入力線と、

前記入力線に結合された入力を有し、複数の並列パスを有する離散時間ノイズシェーピング/量子化回路であって、前記複数の並列パスの出力が、共同で、前記離散時間ノイズシェーピング/量子化回路全体により生成される完全な信号を構成し、前記複数の並列パスにおける各パスは、前記完全な信号の異なるサブサンプリング位相を生成する、離散時間ノイズシェーピング/量子化回路と、

前記離散時間ノイズシェーピング/量子化回路の出力に結合されたマルチビット−可変レベル信号変換器と、

前記マルチビット−可変レベル信号変換器の出力に結合されたアナログ・バンドパスフィルタと、

を備え、

前記複数の並列パスのうちの所与の1つの現在の出力は、前記入力線から結合された信号サンプルと、前記所与の並列パスにおいて生成された信号サンプルと、他の並列パスからの過去の出力サンプルとの関数であり、

前記離散時間ノイズシェーピング/量子化回路は、前記アナログ・バンドパスフィルタにより選択された周波数帯域に対応する変換雑音周波数応答最小値を有する

ことを特徴とする装置。 - 前記複数の並列パスの各々は、

入力と、

前記離散時間ノイズシェーピング/量子化回路の入力に結合された第1の入力、第2の入力及び出力を有する加算器と、

信号のビット幅分解能を低下し、前記加算器の前記出力に結合された入力及び出力を有する量子化回路と、

前記量子化回路の前記出力に結合された入力及び前記加算器の前記第2の入力に結合された出力を有するフィードバックループフィルタと、

を備えることを特徴とする請求項20に記載の装置。 - 前記複数の並列パスの各々における前記フィードバックループフィルタは、複数の零点を含む変換雑音伝達関数を有し、前記零点のいずれも他の零点と等しくないことを特徴とする請求項21に記載の装置。

- 前記複数の並列パスの各々は、前記マルチビット−可変レベル信号変換器の倍率パラメータの不完全性を補償するために非線形ビットマッピングを含むことを特徴とする請求項20に記載の装置。

- 前記非線形ビットマッピング機能は、出力変換雑音を最小限にする誤差計測値に基づいて動的に調整されることを特徴とする請求項23に記載の装置。

- 前記複数の並列パスの出力は、少なくとも1つのマルチプレクサを使用して単一の出力に組み合わされることを特徴とする請求項20に記載の装置。

- 前記複数の並列パスの出力は、少なくとも1つの加算演算と少なくとも1つの遅延演算とを含む手段を使用して、連続時間信号として単一の出力に組み合わされることを特徴とする請求項20に記載の装置。

- 前記複数の並列パスの出力は、加算演算を含む手段と共に逆移動平均フィルタを使用して単一の合成出力に組み合わされることを特徴とする請求項20に記載の装置。

- 前記複数の並列パスの各々の出力は、前記複数の並列パスのうちの他の並列パスにおいて生成されたいずれの現在の信号にも依存しないことを特徴とする請求項20に記載の装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US28707909P | 2009-12-16 | 2009-12-16 | |

| US61/287,079 | 2009-12-16 | ||

| PCT/US2010/060789 WO2011084609A1 (en) | 2009-12-16 | 2010-12-16 | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013515394A JP2013515394A (ja) | 2013-05-02 |

| JP2013515394A5 JP2013515394A5 (ja) | 2014-09-04 |

| JP5735981B2 true JP5735981B2 (ja) | 2015-06-17 |

Family

ID=43858356

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012544832A Active JP5735981B2 (ja) | 2009-12-16 | 2010-12-16 | 離散時間量子化信号の連続時間連続可変信号への変換 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8264390B2 (ja) |

| EP (1) | EP2514098B1 (ja) |

| JP (1) | JP5735981B2 (ja) |

| WO (1) | WO2011084609A1 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9276602B1 (en) * | 2009-12-16 | 2016-03-01 | Syntropy Systems, Llc | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

| US8018365B1 (en) * | 2010-03-14 | 2011-09-13 | Mediatek Inc. | Continuous-time delta-sigma ADC with compact structure |

| US9680497B2 (en) | 2014-03-26 | 2017-06-13 | Syntropy Systems, Llc | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

| US8847803B2 (en) * | 2011-09-09 | 2014-09-30 | Mstar Semiconductor, Inc. | Parallel multibit digital-to-digital sigma-delta modulation |

| US8638251B1 (en) | 2012-08-29 | 2014-01-28 | Mcafee, Inc. | Delay compensation for sigma delta modulator |

| EP3000175B1 (en) * | 2013-05-20 | 2019-02-27 | Analog Devices, Inc. | Relaxed digitization system linearization |

| US9197401B2 (en) * | 2013-11-19 | 2015-11-24 | Electronics And Telecommunications Research Institute | Multi-band receiver |

| US9609653B2 (en) * | 2014-10-15 | 2017-03-28 | National Instruments Corporation | Spectral stitching method to increase instantaneous bandwidth in vector signal generators |

| US9794000B2 (en) * | 2015-04-17 | 2017-10-17 | Maxlinear, Inc. | High-speed, low-power optical communications |

| CN107852171B (zh) * | 2015-11-18 | 2021-11-05 | 弗劳恩霍夫应用研究促进协会 | 信号处理系统和信号处理方法 |

| WO2018045201A1 (en) | 2016-09-03 | 2018-03-08 | National Instruments Corporation | Time sequenced spectral stitching |

| US10623212B2 (en) * | 2018-01-26 | 2020-04-14 | The Board Of Trustees Of The University Of Illinois | Space-time oversampling and error shaping for coarsely quantized arrays |

| EP3994867A4 (en) | 2019-07-03 | 2023-07-26 | The Board Of Trustees Of The University Of Illinois | SEPARATION OF SPACE-TIME SIGNALS WITH MOVING AND ASYNCHRONOUS ARRAYS |

| US11522557B1 (en) * | 2021-07-29 | 2022-12-06 | Nxp B.V. | System and method of calibration of sigma-delta converter using tone injection |

| US11716093B2 (en) * | 2021-12-22 | 2023-08-01 | Infineon Technologies Ag | Delta-sigmal modulator-based multi-rate digital-to-analog converter with digital pre-distortion |

| CN114900189B (zh) * | 2022-04-15 | 2024-05-31 | 上海交通大学 | 低噪声泄露的mashδς调制器 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB9103777D0 (en) * | 1991-02-22 | 1991-04-10 | B & W Loudspeakers | Analogue and digital convertors |

| GB9109637D0 (en) * | 1991-05-03 | 1991-06-26 | Marconi Gec Ltd | Analogue-to-digital and digital-to-analogue converters |

| DE19611879A1 (de) * | 1995-05-15 | 1996-11-21 | Charles Machine Works | Bandpaßfilter für Vorverstärker |

| US6727832B1 (en) * | 2002-11-27 | 2004-04-27 | Cirrus Logic, Inc. | Data converters with digitally filtered pulse width modulation output stages and methods and systems using the same |

| US7894536B2 (en) * | 2003-04-15 | 2011-02-22 | Texas Instruments Incorporated | Calibration model to mitigate data conversion errors |

| US6888484B2 (en) * | 2003-05-22 | 2005-05-03 | Agere Systems Inc. | Stable high-order delta-sigma error feedback modulators, and noise transfer functions for use in such modulators |

| US6963297B2 (en) * | 2003-11-12 | 2005-11-08 | Northrop Grumman Corporation | Delta-sigma digital-to-analog converter assembly |

| WO2007066274A1 (en) * | 2005-12-05 | 2007-06-14 | Nxp B.V. | Electronic quadrature device |

| US7633417B1 (en) * | 2006-06-03 | 2009-12-15 | Alcatel Lucent | Device and method for enhancing the human perceptual quality of a multimedia signal |

-

2010

- 2010-12-16 EP EP10798430.4A patent/EP2514098B1/en active Active

- 2010-12-16 JP JP2012544832A patent/JP5735981B2/ja active Active

- 2010-12-16 WO PCT/US2010/060789 patent/WO2011084609A1/en active Application Filing

- 2010-12-16 US US12/970,379 patent/US8264390B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013515394A (ja) | 2013-05-02 |

| US8264390B2 (en) | 2012-09-11 |

| WO2011084609A1 (en) | 2011-07-14 |

| US20110140942A1 (en) | 2011-06-16 |

| EP2514098A1 (en) | 2012-10-24 |

| EP2514098B1 (en) | 2016-11-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5735981B2 (ja) | 離散時間量子化信号の連続時間連続可変信号への変換 | |

| US9048865B2 (en) | Conversion of a discrete time quantized signal into a continuous time, continuously variable signal | |

| US9680497B2 (en) | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal | |

| JP6147706B2 (ja) | サンプリング/量子化変換器 | |

| US9735800B2 (en) | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal | |

| US8896471B1 (en) | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal | |

| US8943112B2 (en) | Sampling/quantization converters | |

| EP1081863B1 (en) | Delta-sigma modulator with two-step quantization, and method for using two-step quantization in delta-sigma modulation | |

| US8299947B2 (en) | Sampling/quantization converters | |

| US6980144B1 (en) | Method for reducing DAC resolution in multi-bit sigma delta analog-to digital converter (ADC) | |

| US7446687B2 (en) | Method and apparatus to reduce internal circuit errors in a multi-bit delta-sigma modulator | |

| US20150091745A1 (en) | Sampling/Quantization Converters | |

| JPH10507891A (ja) | ハイブリッドフィルタバンクアナログ/デジタルコンバータ | |

| CN111988038A (zh) | 基于vco的连续时间流水线adc | |

| JP2011234154A (ja) | アナログデジタル変換器およびその動作方法 | |

| US9685975B2 (en) | Distributed combiner for parallel discrete-to-linear converters | |

| CN114301464A (zh) | 具备抑制混叠功能的Sigma-Delta模数转换器 | |

| Johansson | Sampling and quantization | |

| US6473011B1 (en) | Serial D/A converter compensating for capacitor mismatch errors | |

| Johansson | Sampling and quantization | |

| GB2541861A (en) | Digital to analogue conversion | |

| EP2503696A1 (en) | Time-interleaved analog-to-digital converter system | |

| Kostyuchenko et al. | The Design of the CIC-HB Digital Decimation Filter for the Sigma-Delta Modulator | |

| EP1681769B1 (en) | Integrated circuit containing a delta-sigma modulator with two-step quantization | |

| CN117040484A (zh) | 一种高精度的数字抽取滤波器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131111 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131111 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140715 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141024 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20150123 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150327 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150417 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5735981 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |