JP5584331B2 - 半導体発光素子 - Google Patents

半導体発光素子 Download PDFInfo

- Publication number

- JP5584331B2 JP5584331B2 JP2013121691A JP2013121691A JP5584331B2 JP 5584331 B2 JP5584331 B2 JP 5584331B2 JP 2013121691 A JP2013121691 A JP 2013121691A JP 2013121691 A JP2013121691 A JP 2013121691A JP 5584331 B2 JP5584331 B2 JP 5584331B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- metal

- light emitting

- semiconductor light

- emitting device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

(素子構造)

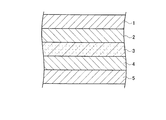

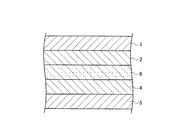

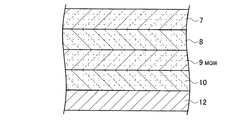

本発明の第1の実施の形態に係る半導体発光素子およびその製造方法に適用されるGaAs基板の導電型としては、p型、n型のいずれにおいても適用可能である。図1は、本発明の第1の実施の形態に係る半導体発光素子およびその製造方法に適用されるp型GaAs基板の模式的断面構造を示し、図2は、n型GaAs基板の模式的断面構造を示す。また、図3は、本発明の第1の実施の形態に係る半導体発光素子およびその製造方法に適用されるLEDの模式的断面構造を示す。

(素子構造)

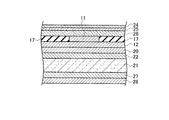

図5は、本発明の第2の実施の形態に係る半導体発光素子およびその製造方法に適用されるLEDの模式的断面構造を示す。また、図6は、本発明の第2の実施の形態の変形例に係る半導体発光素子およびその製造方法に適用されるLEDの模式的断面構造を示す。

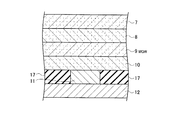

本発明の第2の実施の形態の変形例に係る半導体発光素子およびその製造方法に適用されるLEDは、図6に示すように、金属層12と、金属層12上に配置される金属バッファ層18と、金属バッファ層18上に配置され,パターニングされた金属コンタクト層11および絶縁層17と、パターニングされた金属コンタクト層11および絶縁層17上に配置されるp型クラッド層10と、p型クラッド層10上に配置されるMQW層9と、MQW層9上に配置されるn型クラッド層8と、n型クラッド層8上に配置されるウィンドウ層7を備える。

(素子構造)

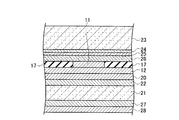

図8は、本発明の第3の実施の形態に係る半導体発光素子およびその製造方法に適用されるGaAs基板の模式的断面構造を示す。また、図9は、本発明の第3の実施の形態に係る半導体発光素子およびその製造方法に適用されるLEDの模式的断面構造を示す。

(素子構造)

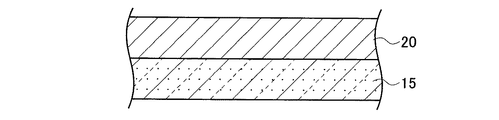

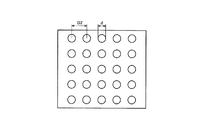

図11は、本発明の第4の実施の形態に係る半導体発光素子およびその製造方法に適用されるシリコン基板の模式的断面構造を示す。また、図12は、本発明の第4の実施の形態に係る半導体発光素子およびその製造方法に適用されるLEDの模式的断面構造を示す。図13は、本発明の第4の実施の形態に係る半導体発光素子およびその製造方法に適用されるLEDの模式的平面パターン構造を示し、図14は、別の模式的平面パターン構造を示す。

金属コンタクト層11のパターン幅が広い場合には、実質的な発光領域が制限されるため、面積効率が低下し発光効率が減少する。一方、金属コンタクト層11のパターン幅が狭い場合には、金属コンタクト層11の面積抵抗が増大し、LEDの順方向電圧Vfが上昇する。このため、最適なパターン幅WおよびパターンピッチD1が存在する。幾つかのパターン例では、六角形を基本とするハニカムパターン構造、或いは、円形ドット形状を基本構造とする円形ドットパターン構造が存在する。

本発明の第4の実施の形態に係る半導体発光素子の製造方法を以下に説明する。

図21は、本発明の第4の実施の形態の変形例に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造を示す。また、図22は、本発明の第4の実施の形態の別の変形例に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造を示す。

上記のように、本発明は第1乃至第4の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

2、4、18…金属バッファ層

3…p型GaAs層

6…n型GaAs層

7…ウィンドウ層

8…n型クラッド層

9…多重量子井戸(MQW)層

10…p型クラッド層

11…金属コンタクト層(AuBe−Ni合金)

15、23…GaAs基板

17…絶縁層

21…シリコン(Si)基板

22、27…チタン(Ti)層

24…AlInGaP層

25…n型GaAs層

26…エピタキシャル成長層

29…表面電極層

30…フロスト処理領域

31…阻止層

32、34…金属バッファ層(AuGe−Ni合金)

28、35…裏面電極層

Claims (18)

- 導電性の基板と、

前記基板上に配置されるとともに、Au系の合金材料からなる第1金属バッファ層と、

前記第1金属バッファ層上に形成されたAuからなる接合層と、

前記接合層上に形成された、金属コンタクト層および絶縁層と、

前記金属コンタクト層および前記絶縁層上に形成され、赤色系の光を発光する層を含む半導体層と、

前記半導体層上に形成された金属からなる電極と

を備え、

前記金属コンタクト層は、Au系の材料からなり、

前記絶縁層は、前記金属コンタクト層と略同じ厚みであって、パターニングされた開口部を有し、前記絶縁層の前記開口部に前記金属コンタクト層が形成されることを特徴とする半導体発光素子。 - 前記赤色系の光を発光する層は、GaAs/GaAlAs層からなるヘテロ接合ペアを積層した多重量子井戸構造からなる多重量子井戸層であることを特徴とする請求項1に記載の半導体発光素子。

- 前記絶縁層は、前記赤色系の光を発光する層からの発光波長に対して透明であることを特徴とする請求項1または2に記載の半導体発光素子。

- 前記金属コンタクト層および前記絶縁層側に予め配置された前記接合層によって、金属反射層が形成されることを特徴とする請求項1〜3のいずれか1項に記載の半導体発光素子。

- 前記赤色系の光を発光する層からの放射光は、前記絶縁層と前記接合層との界面に形成されたミラー面において反射されることを特徴とする請求項1〜4のいずれか1項に記載の半導体発光素子。

- 前記接合層と前記半導体層との界面に介在される前記金属コンタクト層は、前記ミラー面の一部を形成していることを特徴とする請求項5に記載の半導体発光素子。

- 前記接合層を熱圧着によって貼り付けることによって、前記基板と前記半導体層とを貼り付けることを特徴とする請求項1〜6のいずれか1項に記載の半導体発光素子。

- 前記基板は、GaAs基板、Si基板、サファイア基板、Ge基板、SiGe基板、SiC基板、GaN基板、またはSiC上のGaNエピタキシャル基板のいずれかで形成されることを特徴とする請求項1〜7のいずれか1項に記載の半導体発光素子。

- 前記半導体層は、

前記金属コンタクト層および前記絶縁層上であって、前記金属コンタクト層および前記絶縁層と前記赤色系の光を発光する層との間に配置されるp型クラッド層と、

前記赤色系の光を発光する層上に配置されるn型クラッド層と、

前記n型クラッド層上に配置されるウィンドウ層と

を備えることを特徴とする請求項1〜8のいずれか1項に記載の半導体発光素子。 - 前記接合層上に配置され,前記接合層と、前記金属コンタクト層および前記絶縁層との間に第2金属バッファ層をさらに備えることを特徴とする請求項1〜9のいずれか1項に記載の半導体発光素子。

- 前記第2金属バッファ層は、Ag、Al、Ni、Cr若しくはWのいずれかにより形成されることを特徴とする請求項10に記載の半導体発光素子。

- 前記接合層と前記絶縁層との界面に介在される前記第2金属バッファ層は、前記絶縁層と前記接合層との界面に形成されたミラー面の一部を形成していることを特徴とする請求項10に記載の半導体発光素子。

- 前記金属コンタクト層は、六角形を基本とするハニカムパターン構造、或いは、円形を基本とするドットパターン構造を有することを特徴とする請求項10〜12のいずれか1項に記載の半導体発光素子。

- 前記金属コンタクト層は、所定のパターン構造が所定の間隔で配置されており、前記金属コンタクト層のパターン幅は5μm〜11μmであることを特徴とする請求項10〜13のいずれか1項に記載の半導体発光素子。

- 前記金属コンタクト層は、AuBe層あるいはAuBeとNiとの合金層、若しくはAu層/AuBe−Ni合金層/Au層の積層構造により形成されることを特徴とする請求項1〜14のいずれか1項に記載の半導体発光素子。

- 前記絶縁層は、シリコン酸化膜、シリコン窒化膜、SiON膜、SiOxNy膜、或いはこれらの多層膜のいずれかにより形成されることを特徴とする請求項1〜15のいずれか1項に記載の半導体発光素子。

- 前記半導体層と前記電極との間には、電流集中を防止するための阻止層を配置することを特徴とする請求項1に記載の半導体発光素子。

- 前記阻止層は、GaAsにより形成されることを特徴とする請求項17に記載の半導体発光素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013121691A JP5584331B2 (ja) | 2013-06-10 | 2013-06-10 | 半導体発光素子 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013121691A JP5584331B2 (ja) | 2013-06-10 | 2013-06-10 | 半導体発光素子 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007107130A Division JP5346443B2 (ja) | 2007-04-16 | 2007-04-16 | 半導体発光素子およびその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014145623A Division JP5981493B2 (ja) | 2014-07-16 | 2014-07-16 | 半導体発光素子 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013175791A JP2013175791A (ja) | 2013-09-05 |

| JP5584331B2 true JP5584331B2 (ja) | 2014-09-03 |

Family

ID=49268359

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013121691A Active JP5584331B2 (ja) | 2013-06-10 | 2013-06-10 | 半導体発光素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5584331B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11955507B2 (en) | 2021-05-21 | 2024-04-09 | Au Optronics Corporation | Light-emitting device and manufacturing method thereof and manufacturing method of light-emitting apparatus |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113224108A (zh) * | 2020-02-05 | 2021-08-06 | 京东方科技集团股份有限公司 | 一种硅基oled显示面板、及其制备方法、显示装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6784462B2 (en) * | 2001-12-13 | 2004-08-31 | Rensselaer Polytechnic Institute | Light-emitting diode with planar omni-directional reflector |

| JP2003282946A (ja) * | 2003-02-06 | 2003-10-03 | Matsushita Electric Ind Co Ltd | 発光ダイオード装置及びその製造方法 |

| TWI230473B (en) * | 2003-03-10 | 2005-04-01 | Sanken Electric Co Ltd | Semiconductor light emitting device and manufacturing method thereof |

| JP2005123530A (ja) * | 2003-10-20 | 2005-05-12 | Shin Etsu Handotai Co Ltd | 発光素子の製造方法 |

| JP2005259820A (ja) * | 2004-03-09 | 2005-09-22 | Sharp Corp | Iii−v族化合物半導体発光素子とその製造方法 |

| US20070102692A1 (en) * | 2004-07-12 | 2007-05-10 | Hirokazu Asahara | Semiconductor light emitting device |

| JP2006128425A (ja) * | 2004-10-29 | 2006-05-18 | Shin Etsu Handotai Co Ltd | 発光素子および発光素子の製造方法 |

| JP4835377B2 (ja) * | 2006-10-20 | 2011-12-14 | 日立電線株式会社 | 半導体発光素子 |

-

2013

- 2013-06-10 JP JP2013121691A patent/JP5584331B2/ja active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11955507B2 (en) | 2021-05-21 | 2024-04-09 | Au Optronics Corporation | Light-emitting device and manufacturing method thereof and manufacturing method of light-emitting apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013175791A (ja) | 2013-09-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5123573B2 (ja) | 半導体発光素子およびその製造方法 | |

| JP5346443B2 (ja) | 半導体発光素子およびその製造方法 | |

| US7659553B2 (en) | Light-emitting semiconductor device protected against reflector metal migration | |

| JP2002217450A (ja) | 半導体発光素子及びその製造方法 | |

| JP6159130B2 (ja) | 半導体発光素子 | |

| JP5584331B2 (ja) | 半導体発光素子 | |

| JP5981493B2 (ja) | 半導体発光素子 | |

| JP5396526B2 (ja) | 半導体発光素子 | |

| JP2011071340A (ja) | 発光素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130617 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140317 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140415 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140611 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140624 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140717 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5584331 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |