JP5564194B2 - メモリコントローラ、メモリ制御装置およびメモリ装置 - Google Patents

メモリコントローラ、メモリ制御装置およびメモリ装置 Download PDFInfo

- Publication number

- JP5564194B2 JP5564194B2 JP2009097829A JP2009097829A JP5564194B2 JP 5564194 B2 JP5564194 B2 JP 5564194B2 JP 2009097829 A JP2009097829 A JP 2009097829A JP 2009097829 A JP2009097829 A JP 2009097829A JP 5564194 B2 JP5564194 B2 JP 5564194B2

- Authority

- JP

- Japan

- Prior art keywords

- key

- information

- key information

- hardware

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006243 chemical reaction Methods 0.000 claims description 52

- 230000004044 response Effects 0.000 claims description 15

- 230000010365 information processing Effects 0.000 description 65

- 238000000034 method Methods 0.000 description 28

- 230000006870 function Effects 0.000 description 23

- 230000008569 process Effects 0.000 description 17

- 238000001514 detection method Methods 0.000 description 9

- 238000010586 diagram Methods 0.000 description 8

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Storage Device Security (AREA)

Description

[1−1.構成概要]

図1は、メモリ情報保護システム1Aの外観構成を示す図である。

次に、メモリ情報保護システム1Aの機能について詳述する。図2は、第1実施形態に係るメモリ情報保護システム1Aの機能構成を示すブロック図である。

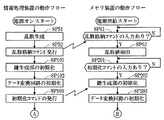

メモリ情報保護システム1Aの動作について説明する。図4および図5は、メモリ情報保護システム1Aの動作を示すフローチャートである。図4および図5では、左側に情報処理装置10Aの動作を示すフローチャート、右側にメモリ装置20の動作を示すフローチャートがそれぞれ示されている。なお、メモリ装置20は、CPUのような処理手段を含むものではなく、ハードウェアとしての回路による動作であるが、ここでは、情報処理装置10Aの動作の流れに対応させて便宜的にフローで示すものとする。

次に、本発明の第2実施形態について説明する。上記第2実施形態に係るメモリ情報保護システム1Bは、乱数生成部を備えている点以外は、メモリ情報保護システム1Aとほぼ同様の構造および機能を有しており、共通する部分については同じ符号を付して説明を省略する。図6は、第2実施形態に係るメモリ情報保護システム1Bの機能構成を示すブロック図である。

以上、この発明の実施の形態について説明したが、この発明は、上記に説明した内容に限定されるものではない。

10A,10B,10H 情報処理装置

20,20H メモリ装置

100A,100B 全体制御部

101 コマンド生成部

102 データ取得部

103 コマンド発行検知部

104 乱数生成部

105 制御レジスタ部

110A,110B,110H メモリ制御部

111,211 ハードウェア鍵

112,212,112H,212H 鍵生成部

113,213,113H,213H データ変換回路

120,220 インターフェース部

200 記憶部

210,210H メモリ内制御部

214 コマンド判別部

D1,D2 読出データ

K1,K2,K3 鍵情報

Claims (8)

- ハードウェアとして実装される第1ハードウェア鍵と、前記第1ハードウェア鍵を用いて第1初期鍵情報を生成し、所定タイミングごとに、前記第1初期鍵情報を構成するビット列を順次に更新させて、情報の暗復号化に用いる新たな第1鍵情報を生成する第1鍵生成手段と、を有するメモリ装置との間で通信するメモリコントローラであって、

前記所定タイミングに同期させて、情報の暗復号化に用いる、前記第1鍵情報と共通の第2鍵情報を新たに生成する第2鍵生成手段と、

所定情報を記憶した前記メモリ装置に出力する情報を前記第2鍵情報に基づいて暗号化するとともに、前記メモリ装置から入力される暗号化された前記所定情報を前記第2鍵情報に基づいて復号化するデータ変換手段と、

前記第1ハードウェア鍵と共通であり、ハードウェアとして実装された固定的な第2ハードウェア鍵と、

を備え、

前記データ変換手段では、前記第2鍵生成手段によって新たな第2鍵情報が生成される度に、当該新たな第2鍵情報を前記第2鍵情報とする鍵情報の更新が行われ、

前記第2鍵生成手段は、前記メモリコントローラの起動の際に、前記第2ハードウェア鍵を用いて、前記第1初期鍵情報と共通の第2初期鍵情報を生成し、

前記新たな第2鍵情報は、前記第2初期鍵情報を構成するビット列を順次に更新させて取得され、

前記第2鍵生成手段は、

前記所定タイミングごとに、前記ビット列をシフトさせて、前記新たな第2鍵情報を生成するシフト手段を有する、メモリコントローラ。 - 外部で生成された乱数値を取得する乱数取得手段をさらに備え、

前記第2鍵生成手段は、前記メモリコントローラの起動の際に、前記第2ハードウェア鍵と前記乱数値とを用いて前記第2初期鍵情報を生成する、請求項1に記載のメモリコントローラ。 - 前記シフト手段は、シフトレジスタを含む、請求項1または請求項2に記載のメモリコントローラ。

- 請求項1から請求項3のいずれかに記載のメモリコントローラを有する、メモリ制御装置。

- ハードウェアとして実装される第1ハードウェア鍵と、前記第1ハードウェア鍵を用いて第1初期鍵情報を生成し、所定タイミングごとに、前記第1初期鍵情報を構成するビット列を順次に更新させて、情報の暗復号化に用いる新たな第1鍵情報を生成する第1鍵生成手段と、を有するメモリコントローラとの間で通信するメモリ装置であって、

前記所定タイミングに同期して、情報の暗復号化に用いる、前記第1鍵情報と共通の第2鍵情報の生成指示を行う指示手段と、

前記生成指示に応じて、前記第2鍵情報を新たに生成する第2鍵生成手段と、

所定情報を記憶した記憶手段と、

前記所定情報のうち読出対象となった情報を前記第2鍵情報に基づいて暗号化するとともに、前記メモリコントローラから入力される暗号化された情報を前記第2鍵情報に基づいて復号化するデータ変換手段と、

前記第1ハードウェア鍵と共通であり、ハードウェアとして実装された固定的な第2ハードウェア鍵と、

を備え、

前記データ変換手段では、前記第2鍵生成手段によって新たな第2鍵情報が生成される度に、当該新たな第2鍵情報を前記第2鍵情報とする鍵情報の更新が行われ、

前記指示手段は、前記メモリコントローラからの初期化コマンドの入力に応じて前記第2鍵生成手段の初期化指示を行い、

前記第2鍵生成手段は、前記初期化指示に応じて、前記第2ハードウェア鍵を用いて、前記第1初期鍵情報と共通の第2初期鍵情報を生成し、

前記新たな第2鍵情報は、前記生成指示に応じて、前記第2初期鍵情報を構成するビット列を順次に更新させて取得され、

前記第2鍵生成手段は、

前記所定タイミングごとに、前記ビット列をシフトさせて、前記新たな第2鍵情報を生成するシフト手段を有する、メモリ装置。 - 前記メモリ装置は、外部で生成された乱数値を取得し、

前記第2鍵生成手段は、前記初期化指示に応じて、前記第2ハードウェア鍵と前記乱数値とを用いて前記第2初期鍵情報を生成する、請求項5に記載のメモリ装置。 - 前記シフト手段は、シフトレジスタを含む、請求項5または6に記載のメモリ装置。

- 前記指示手段は、前記メモリコントローラからのコマンドの入力に応じて前記生成指示を行う請求項5から請求項7のいずれかに記載のメモリ装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009097829A JP5564194B2 (ja) | 2009-04-14 | 2009-04-14 | メモリコントローラ、メモリ制御装置およびメモリ装置 |

| PCT/JP2010/056148 WO2010119784A1 (ja) | 2009-04-14 | 2010-04-05 | メモリコントローラ、メモリ制御装置、メモリ装置、メモリ情報保護システム、メモリ制御装置の制御方法、およびメモリ装置の制御方法 |

| US13/257,680 US8826042B2 (en) | 2009-04-14 | 2010-04-05 | Memory controller, memory control apparatus, memory device, memory information protection system, control method for memory control apparatus, and control method for memory device |

| TW099111023A TWI489280B (zh) | 2009-04-14 | 2010-04-09 | 記憶體控制器,記憶體控制裝置,記憶體裝置,記憶體資訊保護系統及記憶體控制裝置之控制方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009097829A JP5564194B2 (ja) | 2009-04-14 | 2009-04-14 | メモリコントローラ、メモリ制御装置およびメモリ装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014088738A Division JP2014135774A (ja) | 2014-04-23 | 2014-04-23 | メモリコントローラ、メモリ制御装置、メモリ装置、メモリ情報保護システムおよびメモリ制御装置の制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010250472A JP2010250472A (ja) | 2010-11-04 |

| JP2010250472A5 JP2010250472A5 (ja) | 2012-05-10 |

| JP5564194B2 true JP5564194B2 (ja) | 2014-07-30 |

Family

ID=43312743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009097829A Active JP5564194B2 (ja) | 2009-04-14 | 2009-04-14 | メモリコントローラ、メモリ制御装置およびメモリ装置 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP5564194B2 (ja) |

| TW (1) | TWI489280B (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6162556B2 (ja) * | 2013-09-18 | 2017-07-12 | 株式会社メガチップス | 記憶装置及び情報処理システム |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3358953B2 (ja) * | 1996-09-17 | 2002-12-24 | アイオニクス沖縄株式会社 | 擬似ランダムビット列生成器及びそれを使用する暗号通信方法 |

| US6307940B1 (en) * | 1997-06-25 | 2001-10-23 | Canon Kabushiki Kaisha | Communication network for encrypting/deciphering communication text while updating encryption key, a communication terminal thereof, and a communication method thereof |

| JP2002300151A (ja) * | 2001-03-29 | 2002-10-11 | Fujitsu Fip Corp | 暗号キー管理方法、暗号キー管理プログラム、及び記録媒体 |

| JP2003249929A (ja) * | 2001-12-20 | 2003-09-05 | Nti:Kk | 通信装置 |

| EP1653653B1 (en) * | 2003-08-05 | 2017-11-15 | Panasonic Intellectual Property Management Co., Ltd. | Copyright protection system |

| JP4314986B2 (ja) * | 2003-12-08 | 2009-08-19 | ソニー株式会社 | 記録再生装置、記録再生方法 |

| US20060059372A1 (en) * | 2004-09-10 | 2006-03-16 | International Business Machines Corporation | Integrated circuit chip for encryption and decryption having a secure mechanism for programming on-chip hardware |

| US8219829B2 (en) * | 2005-12-08 | 2012-07-10 | Intel Corporation | Scheme for securing locally generated data with authenticated write operations |

| US8538015B2 (en) * | 2007-03-28 | 2013-09-17 | Intel Corporation | Flexible architecture and instruction for advanced encryption standard (AES) |

| JP2008269173A (ja) * | 2007-04-18 | 2008-11-06 | Hitachi Ltd | 計算機システム、ストレージシステムおよびデータ管理方法 |

-

2009

- 2009-04-14 JP JP2009097829A patent/JP5564194B2/ja active Active

-

2010

- 2010-04-09 TW TW099111023A patent/TWI489280B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| TWI489280B (zh) | 2015-06-21 |

| TW201040723A (en) | 2010-11-16 |

| JP2010250472A (ja) | 2010-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2010119784A1 (ja) | メモリコントローラ、メモリ制御装置、メモリ装置、メモリ情報保護システム、メモリ制御装置の制御方法、およびメモリ装置の制御方法 | |

| JP4865694B2 (ja) | プロセッサ装置 | |

| KR101735023B1 (ko) | 민감한 코드와 데이터를 보호하는 아키텍처를 포함하는 방법 및 장치 | |

| CN101231622B (zh) | 基于闪存的数据存储方法和设备、及数据读取方法和设备 | |

| TWI570590B (zh) | 與使用縮減回合編密的xts加密系統一起使用之動態加密金鑰 | |

| US7395165B2 (en) | Circuit arrangement with non-volatile memory module and method of en-/decrypting data in the non-volatile memory module | |

| EP2099154A3 (en) | On-chip storage, creation, and manipulation of an encryption key | |

| US10565381B2 (en) | Method and apparatus for performing firmware programming on microcontroller chip, and associated microcontroller chip | |

| EP3007094B1 (en) | Boot program, information processing apparatus, information processing system, information processing method, semiconductor apparatus, and program | |

| JP2003256282A (ja) | メモリカード | |

| US20150254477A1 (en) | Encryption/decryption system which performs encryption/decryption using register values, control method therefor, and storage medium | |

| JP5564194B2 (ja) | メモリコントローラ、メモリ制御装置およびメモリ装置 | |

| TW201828640A (zh) | 通信裝置、通信方法及記錄媒體 | |

| JP4119882B2 (ja) | メモリ情報保護システム、メモリ情報の保護方法、および半導体メモリ | |

| JP2014135774A (ja) | メモリコントローラ、メモリ制御装置、メモリ装置、メモリ情報保護システムおよびメモリ制御装置の制御方法 | |

| JP4592337B2 (ja) | データ記憶装置 | |

| CN113343215A (zh) | 嵌入式软件的授权和认证方法及电子设备 | |

| JP5302083B2 (ja) | メモリ装置およびメモリ装置の制御方法 | |

| JP2007193800A (ja) | カード認証システムのセキュリティレベルを向上させる装置及び方法 | |

| KR101565968B1 (ko) | 데이터 보호를 위한 메모리, 이를 포함하는 메모리 시스템 및 이의 동작 방법 | |

| JP5269661B2 (ja) | 携帯可能電子装置、及び携帯可能電子装置の制御方法 | |

| JP2018078610A (ja) | 暗号化/復号化システム及びその制御方法、並びにプログラム | |

| JP2018140500A (ja) | 情報処理装置、印刷システムおよびプログラム | |

| JP2007281994A (ja) | 半導体集積回路 | |

| JP7063628B2 (ja) | 暗号化装置、暗号化方法およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120315 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120315 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130903 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131028 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140423 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20140501 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140527 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140616 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5564194 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |