JP5462524B2 - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- JP5462524B2 JP5462524B2 JP2009116316A JP2009116316A JP5462524B2 JP 5462524 B2 JP5462524 B2 JP 5462524B2 JP 2009116316 A JP2009116316 A JP 2009116316A JP 2009116316 A JP2009116316 A JP 2009116316A JP 5462524 B2 JP5462524 B2 JP 5462524B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- layer

- semiconductor device

- via hole

- silicide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

本発明は、半導体基板に貫通電極層が形成された半導体装置に関するものである。 The present invention relates to a semiconductor device in which a through electrode layer is formed on a semiconductor substrate.

近年、電子機器に使用される集積回路において、パッケージ(半導体装置)の小型化が求められている。小型化の一例として、集積回路のパッケージ面積の低減を目的として、従来のワイヤーボンディングに代わって、半導体装置の半導体基板を貫通する貫通電極が用いられている。 In recent years, miniaturization of packages (semiconductor devices) has been required in integrated circuits used in electronic devices. As an example of downsizing, for the purpose of reducing the package area of an integrated circuit, a through electrode penetrating a semiconductor substrate of a semiconductor device is used instead of conventional wire bonding.

図9は、従来の半導体装置の一例を示す部分断面図である。 FIG. 9 is a partial cross-sectional view showing an example of a conventional semiconductor device.

図9において、半導体装置101は、シリコンなどの半導体基板102と、半導体基板102の裏面102bからパッド電極105に到達するビアホール107と、ビアホール107の側壁107a及び半導体基板102の裏面102bに形成された第2酸化膜109と、ビアホール107の内部及び半導体基板102の裏面102bに形成されたバリア層110及び再配線層111とから概略構成されている。

In FIG. 9, the

図10は、従来の半導体装置の製造方法を示すフローチャートであり、図11A〜図12Dは、従来の半導体装置の製造方法を説明するための部分断面図である。 FIG. 10 is a flowchart showing a conventional method for manufacturing a semiconductor device, and FIGS. 11A to 12D are partial cross-sectional views for explaining a conventional method for manufacturing a semiconductor device.

最初に、図11Aに示すように、不図示の電子回路が形成された半導体基板102の表面102aの上の第1酸化膜106の上にパッド電極105及びパッシベーション膜104が形成された後、パッシベーション膜104の上に、不図示の接着剤を介して、支持基板103が接着される(図10のステップS101参照)。

First, as shown in FIG. 11A, after the

次に、図11Bに示すように、半導体基板102の裏面102bの上に、パッド電極105に相当する位置を開口するために、レジスト112が形成される(図10のステップS102参照)。

Next, as shown in FIG. 11B, a

そして、図11Cに示すように、レジスト112をマスクとして、半導体基板102をエッチングすることにより、第1酸化膜106に到達するビアホール107が形成される(図10のステップS103参照)。

Then, as shown in FIG. 11C, the

続いて、図11Dに示すように、レジスト112をマスクとして、第1酸化膜106をエッチングすることにより、パッド電極105に到達するビアホール107が形成される(図10のステップS104参照)。

Subsequently, as shown in FIG. 11D, the

次に、図12Aに示すように、レジスト112を半導体基板102の裏面102bから除去する(図10のステップS105参照)。

Next, as shown in FIG. 12A, the

そして、図12Bに示すように、ビアホール107の側壁107a及び半導体基板102の裏面102bに第2酸化膜109をそれぞれ形成する(図10のステップS106参照)。

Then, as shown in FIG. 12B, a

次に、図12Cに示すように、ビアホール107の底部の第2酸化膜109をエッチングすることにより、パッド電極105を再度露出させる(図10のステップS107参照)。

Next, as shown in FIG. 12C, the

続いて、図12Dに示すように、バリア層110及び再配線層111を第2酸化膜109上に順に形成する(図10のステップS108参照)。

Subsequently, as shown in FIG. 12D, a

パッド電極105は、バリア層110及び再配線層111で構成される貫通電極108を通して、半導体基板102の裏面102bへ電気的に接続されている。

The

パッド電極105と貫通電極108は、ビアホール107の内径に応じた面積で接触しており、パッド電極105と貫通電極108の間の抵抗値は、この接触面積によって決定される。

The

しかしながら、前記従来の構成では、パッド電極105と貫通電極108の間の抵抗値はビアホール107の内径の寸法に依存するため、その抵抗値は、ビアホール107の内径の寸法のばらつきにより変動するという課題を有している。

However, in the conventional configuration, since the resistance value between the

本発明は、前記従来の課題を解決するもので、パッド電極と貫通電極との間の抵抗値がビアホールの内径の寸法のばらつきに依存しない、信頼性に優れた半導体装置を提供することを目的とする。 The present invention solves the above-described conventional problems, and an object of the present invention is to provide a highly reliable semiconductor device in which the resistance value between the pad electrode and the through electrode does not depend on the variation in the inner diameter of the via hole. And

上記目的を達成するために、本発明は以下のように構成する。 In order to achieve the above object, the present invention is configured as follows.

本発明の第1態様によれば、半導体基板の表面に形成された第1絶縁膜と、

前記第1絶縁膜の中に形成され、かつ、外部接続端子を有する電極部と、

前記半導体基板の裏面から前記表面に貫通するビアホールと、

前記ビアホールの側壁及び前記半導体基板の前記裏面に形成された第2絶縁膜と、

前記ビアホールの前記側壁上の前記第2絶縁膜と前記半導体基板の前記裏面上の前記第2絶縁膜と前記ビアホールの底面の前記第1絶縁膜とに形成された貫通電極層と、

前記電極部と前記貫通電極層との間に形成され、かつ前記電極部及び前記貫通電極層に接続されたシリサイド層と、

を備え、

前記ビアホールの中心軸を含む平面で切断された断面における、前記シリサイド層の幅Aと前記ビアホールの底部の幅Bとの関係が、A≦Bであることを特徴とする半導体装置を提供する。

According to the first aspect of the present invention, the first insulating film formed on the surface of the semiconductor substrate;

An electrode portion formed in the first insulating film and having an external connection terminal;

A via hole penetrating from the back surface of the semiconductor substrate to the front surface;

A second insulating film formed on a sidewall of the via hole and the back surface of the semiconductor substrate;

A through electrode layer formed on the second insulating film on the sidewall of the via hole, the second insulating film on the back surface of the semiconductor substrate, and the first insulating film on the bottom surface of the via hole;

A silicide layer formed between the electrode portion and the through electrode layer and connected to the electrode portion and the through electrode layer;

With

The semiconductor device is characterized in that the relation between the width A of the silicide layer and the width B of the bottom of the via hole in a cross section cut along a plane including the central axis of the via hole is A ≦ B.

本発明の第2態様によれば、前記シリサイド層と前記電極部とは、コンタクト電極を介して接続されたことを特徴とする第1の態様に記載の半導体装置を提供する。 According to a second aspect of the present invention, there is provided the semiconductor device according to the first aspect, wherein the silicide layer and the electrode portion are connected via a contact electrode .

本発明の第3態様によれば、前記ビアホールの前記中心軸を含む前記平面において、前記シリサイド層の前記幅と前記コンタクト電極の幅が等しいことを特徴とする第2の態様に記載の半導体装置を提供する。 According to a third aspect of the present invention, in the semiconductor device according to the second aspect, the width of the silicide layer and the width of the contact electrode are equal in the plane including the central axis of the via hole. I will provide a.

本発明の第4態様によれば、前記ビアホールの前記中心軸を含む前記平面において、前記ビアホールの前記底部の前記幅より前記電極部の幅が大きいことを特徴とする第1〜3のいずれか1つの態様に記載の半導体装置を提供する。 According to a fourth aspect of the present invention, in any one of the first to third aspects, in the plane including the central axis of the via hole, the width of the electrode portion is larger than the width of the bottom portion of the via hole . A semiconductor device according to one aspect is provided.

本発明の第5態様によれば、前記電極部は、

前記電極部の本体部と、

前記電極部の前記本体部と前記第1絶縁膜との間に配置された第1バリア層とを備えることを特徴とする第1〜4のいずれか1つの態様に記載の半導体装置を提供する。

According to a fifth aspect of the present invention, the electrode portion is

A body portion of the electrode portion;

The semiconductor device according to any one of the first to fourth aspects, further comprising a first barrier layer disposed between the main body portion of the electrode portion and the first insulating film. .

本発明の第6態様によれば、前記電極部は、

前記電極部の本体部と、

前記電極部の前記本体部と前記第1絶縁膜との間に配置されかつ前記シリサイド層に接触する第1バリア層と、

前記第1絶縁膜の外面側でかつ前記電極部の前記本体部の外面に配置されて前記外部接続端子として機能するパッド電極部とを備えることを特徴とする第1〜4のいずれか1つの態様に記載の半導体装置を提供する。

According to a sixth aspect of the present invention, the electrode portion is

A body portion of the electrode portion;

A first barrier layer disposed between the main body portion of the electrode portion and the first insulating film and in contact with the silicide layer;

One of the first to fourth aspects, further comprising: a pad electrode portion that is disposed on the outer surface side of the first insulating film and on the outer surface of the main body portion of the electrode portion and functions as the external connection terminal. to provide a semiconductor device mounting serial to embodiment.

本発明の第7態様によれば、前記シリサイド層は、前記半導体基板、ポリシリコン膜、又はアモルファスシリコン膜のいずれかに形成されることを特徴とする

第1〜6のいずれか1つの態様に記載の半導体装置を提供する。

According to a seventh aspect of the present invention, the silicide layer is formed on any one of the semiconductor substrate, a polysilicon film, or an amorphous silicon film.

To provide a semiconductor device mounting serial to a sixth one of the aspects.

本発明の第8態様によれば、前記シリサイド層は、タングステンシリサイド、チタンシリサイド、コバルトシリサイド、又は、ニッケルシリサイドのいずれかからから成ることを特徴とする

第1〜7のいずれか1つの態様に記載の半導体装置を提供する。

According to an eighth aspect of the present invention, the silicide layer is made of any of tungsten silicide, titanium silicide, cobalt silicide, or nickel silicide.

To provide a semiconductor device mounting serial to first to seventh any one aspect.

本発明の第9態様によれば、前記電極部の本体部は、タングステン、アルミニウム、又はその合金、銅のいずれかからから成ることを特徴とする

第7又は8の態様に記載の半導体装置を提供する。

According to a ninth aspect of the present invention, the main body portion of the electrode portion is made of tungsten, aluminum, an alloy thereof, or copper.

Providing a semiconductor device mounting serial to aspects of the seventh or eighth.

本発明の第10態様によれば、前記第1バリア層は、チタン、チタンナイトライド、チタンタングステン、タンタル、タンタルナイトライド、又は、高融点金属の積層膜から成ることを特徴とする

第6の態様に記載の半導体装置を提供する。

本発明の第11態様によれば、前記貫通電極層は、

前記ビアホールの前記側壁上の前記第2絶縁膜と前記半導体基板の前記裏面上の前記第2絶縁膜と前記ビアホールの底面の前記第1絶縁膜とに形成された第2バリア層と、

前記第2バリア層上に形成された再配線層とを備え、

前記第2バリア層は、チタン、チタンナイトライド、チタンタングステン、タンタル、タンタルナイトライド、又は、高融点金属の積層膜から成ることを特徴とする

第1〜10のいずれか1つの態様に記載の半導体装置を提供する。

本発明の第12態様によれば、前記電極部が、単一のコンタクト電極部材又は複数のコンタクト電極部材で構成されていることを特徴とする

第1〜11のいずれか1つの態様に記載の半導体装置を提供する。

本発明の第13態様によれば、前記パッド電極は、アルミニウム、銅又はその合金と、チタン、チタンナイトライド、タンタル、タンタルナイトライド、高融点金属、又は、その化合物のいずれかからから成ることを特徴とする

第6の態様に記載の半導体装置を提供する。

According to a tenth aspect of the present invention, the first barrier layer is composed of a laminated film of titanium, titanium nitride, titanium tungsten, tantalum, tantalum nitride, or a refractory metal.

To provide a semiconductor device mounting serial to a sixth aspect of.

According to an eleventh aspect of the present invention, the through electrode layer comprises:

A second barrier layer formed on the second insulating film on the side wall of the via hole, the second insulating film on the back surface of the semiconductor substrate, and the first insulating film on the bottom surface of the via hole;

A rewiring layer formed on the second barrier layer,

The second barrier layer is composed of titanium, titanium nitride, titanium tungsten, tantalum, tantalum nitride, or a laminated film of a refractory metal.

A semiconductor device according to any one of the first to tenth aspects is provided.

According to a twelfth aspect of the present invention, the electrode portion is composed of a single contact electrode member or a plurality of contact electrode members.

A semiconductor device according to any one of the first to eleventh aspects is provided.

According to the thirteenth aspect of the present invention, the pad electrode is composed of aluminum, copper, or an alloy thereof, and any of titanium, titanium nitride, tantalum, tantalum nitride, a refractory metal, or a compound thereof. Characterized by

A semiconductor device according to a sixth aspect is provided.

以上のように、本発明の半導体装置によれば、パッド電極を含む電極部と貫通電極層との間の抵抗値は、前記電極部及び前記貫通電極層に接続されたシリサイド層の幅(例えば、シリサイド層が円形の場合の直径)寸法に依存し、ビアホールの幅(例えば、ビアホールが円形の場合の内径)寸法のばらつきに依存しないため、抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供することができる。 As described above, according to the semiconductor device of the present invention, the resistance value between the electrode portion including the pad electrode and the through electrode layer has the width of the silicide layer connected to the electrode portion and the through electrode layer (for example, Depends on the dimension of the diameter when the silicide layer is circular) and does not depend on the variation of the width of the via hole (for example, the inner diameter when the via hole is circular). Can be provided.

また、ビアホールの幅(例えば、ビアホールが円形の場合の内径)寸法は電極部のパッド電極の幅(例えば、パッド電極が円形の場合の直径)寸法よりも大きくすることが可能であるため、ビアホールのアスペクト比を低減することもできる。 Also, the width of the via hole (for example, the inner diameter when the via hole is circular) can be made larger than the width of the pad electrode (for example, the diameter when the pad electrode is circular) of the electrode portion. It is also possible to reduce the aspect ratio.

さらに、ビアホールの幅(例えば、ビアホールが円形の場合の内径)寸法は、電極部のパッド電極の幅(例えば、パッド電極が円形の場合の直径)寸法よりも大きくすることが可能であるため、電極部のパッド電極の大きさを縮小することにより、半導体装置の一例としての半導体チップの面積を削減することもできる。 Furthermore, the width of the via hole (for example, the inner diameter when the via hole is circular) can be made larger than the width of the pad electrode of the electrode portion (for example, the diameter when the pad electrode is circular). By reducing the size of the pad electrode in the electrode portion, the area of a semiconductor chip as an example of a semiconductor device can be reduced.

以下、本発明の実施の形態について、図面を参照しながら説明する。以下の説明において、同じ構成には同じ符号を付して説明を省略している。 Hereinafter, embodiments of the present invention will be described with reference to the drawings. In the following description, the same components are denoted by the same reference numerals and description thereof is omitted.

(実施の形態1)

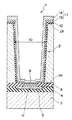

図1は、本発明の実施の形態1における半導体装置の部分断面図である。

(Embodiment 1)

FIG. 1 is a partial cross-sectional view of the semiconductor device according to the first embodiment of the present invention.

図1において、半導体装置1は、半導体基板2と、第1酸化膜8と、電極部18(パッド電極5と、コンタクト電極6と、第1バリア層7)と、シリサイド層9と、ビアホール10と、第2酸化膜12と、貫通電極層11(第2バリア層13と再配線層14)と、支持基板3と、絶縁膜の一例であるパッシベーション膜4とで構成されている。

In FIG. 1, the

第1酸化膜8は、例えばSiO2などで構成され、絶縁膜の一例として、半導体基板2の表面(図1では下面)2aに形成されて、半導体基板2とパッド電極5とを絶縁する機能を有している。

The

パッド電極5は、電極部の外部接続端子の一例として機能し、後述する導電性材料で構成され、第1酸化膜8の表面に、第1酸化膜8の表面から突出して形成されている。

The

コンタクト電極6は、電極部の本体部の一例として機能し、後述する導電性材料で構成され、第1酸化膜8の内部に形成され、かつ外面がパッド電極5に接触してパッド電極5と接続されている。図1では、コンタクト電極6は、パッド電極5よりも幅が小さく形成されている。

The

第1バリア層7は、電極部の一部を構成し、後述する導電性材料で構成され、パッド電極5と接続された外面を除くコンタクト電極6の他の面(側面及び内面)をすべて覆うように形成されて、第1酸化膜8とコンタクト電極6との密着性を高める機能を有している。なお、この第1バリア層7は、パッド電極5と接続された外面に形成されていても良い。

The

シリサイド層9は、後述するように金属とシリコンの合金で構成された導電性材料を有し、かつ、コンタクト電極6の内面側に、第1バリア層7を介して配置される。このシリサイド層9は、コンタクト電極6と貫通電極層11との間の低抵抗を目的とするものである。すなわち、コンタクト電極6上の第1バリア層7と後述する貫通電極層11との間に形成されて、貫通電極層11及び第1バリア層7に接続されるように形成されている。このシリサイド層9を配置した目的は、パッド電極5と貫通電極層11との間の抵抗値が、ビアホール10の内径に依存しないようにすることである。そのため、シリサイド層9の材料は、低抵抗を目的にTiSi2などを用いる。

The

本実施の形態でのシリサイド層9は、ビアホール10内に向けて(表面2aよりも上向きに)、ビアホール10の底面より少し突出して形成されているが、Siと相互拡散せずにシリサイドを形成する材料の場合は、必ずしも突出する必要はない。

The

ビアホール10は、半導体基板2の裏面(図1の紙面上面)2bから表面(図1の紙面下面)2aまで、すなわち、シリサイド層9及び第1酸化膜8に到達するように、半導体基板2を貫通して、形成されている。ビアホール10は、図1に示すように、裏面2bから表面2aに向かうに従い内径が徐々に小さくなるように側壁10aが傾斜した、やや先すぼまりの円錐面形状を側壁10aが有するように形成されている。

The via

第2酸化膜12は、例えばSiO2などで構成され、絶縁膜の一例として、ビアホール10の側壁10aの全面及び半導体基板2の裏面2bに形成されて、貫通電極層11と半導体基板2とを絶縁する機能を有している。

The

貫通電極層11は、第2バリア層13と再配線層14とで構成されている。

The through

第2バリア層13は、第2酸化膜12と再配線層14との密着性を高めるためのものであり、後述するような材料で構成され、ビアホール10の底面(すなわち、半導体基板2の表面2aとシリサイド層9)上とビアホール10の側壁10aの第2酸化膜12の上と半導体基板2の裏面2bの第2酸化膜12の上とに一体的に形成され、かつビアホール10の底面でシリサイド層9と接続されている。シリサイド層9と接続する部分では、シリサイド層9がビアホール10の底面より少し突出している分だけ、ビアホール10の底面より少し盛り上がった状態で、第2バリア層13が形成されている。

The

再配線層14は、第2バリア層13の上に形成されている。すなわち、ビアホール10の底面上の第2バリア層13と、ビアホール10の側壁10aの第2酸化膜12の上の第2バリア層13と、半導体基板2の裏面2bの第2酸化膜12の上の第2バリア層13とにそれぞれ一体的に再配線層14が形成されている。この再配線層14は、パッド電極5(基板表面)から、基板裏面への電気配線を目的として形成されるものであり、例えばCuなどから構成される。

The

よって、パッド電極5と貫通電極層11は、コンタクト電極6と第1バリア層7とシリサイド層9とを通して電気的に接続されており、それ以外の箇所は、第1酸化膜8により電気的に絶縁されている。

Therefore, the

半導体基板2と貫通電極層11は、ビアホール10の側壁10a及び半導体基板2の裏面2bに形成された第2酸化膜12により電気的に絶縁されている。

The

パッド電極5とコンタクト電極6は、パッド電極5とコンタクト電極6との間の抵抗が低くなる材質であれば良い。一例として、パッド電極5は、アルミニウム、銅、又はその合金と、チタン、チタンナイトライド、タンタル、タンタルナイトライド、高融点金属、又は、その化合物などで構成される導電性材料の積層膜として形成されている。コンタクト電極6は、タングステン、アルミニウム若しくはその合金、又は、銅などの導電性材料で形成されている。

The

コンタクト電極6は、単一の太いコンタクト電極部材で構成してもよく、代わりに、図13〜図14に示すように、単一のコンタクト電極部材6を複数の細いコンタクト電極部材6Aに分割したような、複数のコンタクト電極部材で構成するようにしてもよい。なお、図13は、本発明の実施の形態1の半導体装置において、コンタクト電極形成前にシリサイドを形成する場合に、コンタクト電極が複数のコンタクト電極部材である例を示す部分断面図である。図14は、本発明の実施の形態1の半導体装置において、コンタクト電極形成後にシリサイドを形成する場合に、コンタクト電極が複数のコンタクト電極部材である例を示す部分断面図である。

The

コンタクト電極6が円形の場合の直径は、パッド電極5が円形の場合の直径よりも必ずしも小さい必要はなく、大きくても、同じでも良い。コンタクト電極6とパッド電極5の間の抵抗値は、コンタクト電極6とパッド電極5の接触面積で決まるため、この直径は、目的とする抵抗値を達成するための接触面積に基づいて決定される。

The diameter when the

第1バリア層7は、第1酸化膜8とコンタクト電極6との密着性を高めるために、チタン、チタンナイトライド、チタンタングステン、タンタル、タンタルナイトライド、又は、高融点金属の積層膜で形成されている。

The

半導体基板2は、シリコン等の材質からなり、導電性であっても、絶縁性であっても、半絶縁性であっても良い。

The

シリサイド層9は、半導体基板2の表面2aのコンタクト電極6上に形成され、低抵抗を目的に、タングステンシリサイド、チタンシリサイド、コバルトシリサイド、又は、ニッケルシリサイドなどで形成されている。

The

シリサイド層9が円形の場合の直径は、コンタクト電極6が円形の場合の直径と必ずしも同じである必要はない。

The diameter when the

ビアホール10の中心軸を含む平面で切断された断面(例えば図1)における、シリサイド層9の幅Aとビアホール10の底部の幅Bとの関係が、以下の(式1)の関係が成立するようにする。具体的には、シリサイド層9が円形の場合の直径Aは、ビアホール10の底部での内径Bとの間に以下の(式1)の関係が成り立つようにする。このような関係の式が成立すれば、シリサイド層9は、半導体基板2から物理的にも電気的にも確実に分離することができるためである。

The relationship between the width A of the

次に、上述した半導体装置1の製造方法について、図面を参照しながら説明する。図2は、本発明の実施の形態1における半導体装置の製造方法を示すフローチャートであり、図3A〜図4Cは、本発明の実施の形態1における半導体装置の製造方法の工程をそれぞれ説明するための部分断面図である。

Next, a method for manufacturing the

最初に、図3Aに示すように、不図示の電子回路が形成された半導体基板2の表面2aの上の第1酸化膜8の中に、シリサイド層9と第1バリア層7及びコンタクト電極6を形成した後、パッド電極5及びパッシベーション膜4が形成される(図2のステップS1参照)。

First, as shown in FIG. 3A, a

シリサイド層9は、第1バリア層7を熱処理することで形成しても良いし、半導体基板2の表面2aに別の膜(例えば、タングステン、チタン、コバルト、又は、ニッケルなど)を成膜後に熱処理することで、タングステンシリサイド、チタンシリサイド、コバルトシリサイド、又は、ニッケルシリサイドなどとして形成しても良い。第1バリア層7を熱処理することにより半導体基板2の表面2aにシリサイド層9を形成する場合、シリサイド層9が円形の場合の直径はコンタクト電極6が円形の場合のホール径と等しくなる。一方、タングステン、チタン、コバルト、又は、ニッケルなどを成膜後に熱処理することで半導体基板2の表面2aにシリサイド層9を形成する場合、シリサイド層9が円形の場合の直径はコンタクト電極6が円形の場合のホール径と等しくても良いし、等しくなくても良い。

The

そして、パッシベーション膜4の上に、不図示の接着剤を介して、支持基板3が接着される(図3A参照)。

And the

次に、図3Bに示すように、半導体基板2の裏面2bの上に、パッド電極5に相当する位置を開口するために、レジスト15が形成される(図2のステップS2参照)。

Next, as shown in FIG. 3B, a resist 15 is formed on the

そして、図3Cに示すように、レジスト15をマスクとして、半導体基板2をエッチングすることにより、シリサイド層9及び第1酸化膜8に到達するビアホール10が形成される。半導体基板2のエッチングは、ウェットエッチングでもドライエッチングでも良い(図2のステップS3参照)。

Then, as shown in FIG. 3C, the via

シリサイド層9の直径Aとビアホール10の内径Bとの間に前記(式1)の関係が成り立つようにすることにより、シリサイド層9は半導体基板2から物理的にも電気的にも分離される。ビアホール10とシリサイド層9の加工精度は異なり、ビアホール10の内径のばらつきが約1μmであるのに対して、シリサイド層9の直径の加工ばらつきは約1nmである。

The

また、半導体基板2をエッチングすることで、導電層としてシリサイド層9が露出されるため、第1酸化膜8のエッチングは不要である。

Further, since the

次に、図3Dに示すように、レジスト15を半導体基板2の裏面2bから除去する(図2のステップS4参照)。レジスト15の除去は、ウェットプロセスでもドライプロセスでも良い。

Next, as shown in FIG. 3D, the resist 15 is removed from the

そして、図4Aに示すように、ビアホール10の側壁10a及び半導体基板2の裏面2bに第2酸化膜12を形成する(図2のステップS5参照)。第2酸化膜12の形成は、熱酸化法でも良いし、CVD法でも良いし、又は、スパッタ法でも良い。

Then, as shown in FIG. 4A, the

次に、図4Bに示すように、シリサイド層9及び第1酸化膜8の上の第2酸化膜12をエッチングすることにより、シリサイド層9を再度露出させる(図2のステップS6参照)。第1酸化膜8の上の第2酸化膜12はエッチングされずに残っても良い。第2酸化膜12のエッチングは、ドライエッチングが望ましい。これは、ビアホール側壁の酸化膜をエッチングせずにビアホール底部の酸化膜のみエッチングするために、異方性エッチングが必要なためである。

Next, as shown in FIG. 4B, the

続いて、図4Cに示すように、第2バリア層13及び再配線層14を形成する(図2のステップS7参照)。第2バリア層13の形成は、CVD法でも良いし、スパッタ法でも良い。再配線層14の形成は、メッキ法が望ましいが、CVD法でも良いし、スパッタ法でも良いし、又は、これらの組み合わせでも良い。再配線層14は、ビアホール10を不完全に埋め込んだ形状でも良いし、又は、完全に埋め込んだ形状でも良い。

Subsequently, as shown in FIG. 4C, the

本実施の形態1の半導体装置1の数値例は、以下の通りである。半導体基板2の厚みは250μm、支持基板3の厚みは500μm、パッシベーション膜4の厚みは1μm、パッド電極5の大きさは一辺が150μmの正方形(ただし、必ずしも正方形である必要はない。)でかつその厚みは500nm、コンタクト電極6の直径は100μm(必ずしも円形である必要はない。)でかつその厚みは1000nm、第1バリア層7の厚みは10nm、第1酸化膜8の厚みは1μm、シリサイド層9の膜厚は10nmで直径はφ80μm(必ずしも円形である必要はない。)、ビアホール10の直径はφ200μm(必ずしも円形である必要はない。)、第2酸化膜12の厚みは500nm、第2バリア層13の厚みは20nm、再配線層14の厚みは20μm、レジスト15の厚みは20μmである。

Numerical examples of the

本実施の形態1にかかる構成によれば、パッド電極5と貫通電極層11との間の抵抗値は、シリサイド層9の直径寸法に依存し、ビアホール10の内径寸法に依存しない状態にすることができるため、パッド電極5と貫通電極層11との間の抵抗値は、ビアホール10の内径寸法のばらつきに影響されなくなり、信頼性に優れた半導体装置を提供することができるようになる。ビアホール10とシリサイド層9との加工精度は異なり、ビアホール10の内径寸法のばらつきが約1μm単位であるのに対して、シリサイド層9の直径寸法の加工ばらつきは約1nm単位であり、三桁異なるため、本実施の形態1にかかる半導体装置1は、従来よりもパッド電極5と貫通電極層11との間の抵抗値のばらつきを小さくすることができる。

According to the configuration according to the first embodiment, the resistance value between the

また、本実施の形態1にかかる半導体装置1において、ビアホール10の内径はパッド電極5の直径よりも大きくすることが可能であるため、ビアホール10のアスペクト比を低減することができ、さらには、パッド電極5の大きさを縮小することにより、半導体装置の一例としての半導体チップの面積を削減することができる。すなわち、本実施の形態1では、ビアホール10の中心軸方向(長手方向)の寸法と底部の幅(例えば、円形ビアホール10の直径)とのアスペクト比を従来と同じに設定すると、シリサイド層9の幅(例えば、円形シリサイド層9の直径)寸法をビアホール10の底部の幅よりも小さくすることができ、半導体チップ面積の削減が可能となる。逆に、シリサイド層9の幅(例えば、円形シリサイド層9の直径)寸法を、従来のパッド電極とビアホールの底部の幅(直径)寸法との接続部分の幅寸法と同じに設定すると、ビアホール10の幅(直径)寸法は、従来よりも大きくしてもよくなり、ビアホール10の加工がしやすくなる。

Further, in the

これに対して、従来の半導体装置においては、ビアホールの底部の幅(直径)寸法の精度を向上させようとしても、ビアホールの底部の幅(直径)寸法自体をコントロールすることができず、ビアホールの底部とは反対側の開口部側の幅(直径)寸法自体しかコントロールすることができなかった。また、ビアホールは、一般に、実際には、傾斜したテーパ側面を有するため、ビアホールの底部の幅(直径)寸法をコントロールすることは非常に困難である。 On the other hand, in the conventional semiconductor device, even if the accuracy of the width (diameter) dimension of the bottom of the via hole is to be improved, the width (diameter) dimension of the bottom of the via hole cannot be controlled. Only the width (diameter) dimension of the opening side opposite to the bottom could be controlled. In general, a via hole generally has an inclined tapered side surface, so that it is very difficult to control the width (diameter) dimension of the bottom of the via hole.

(実施の形態1の変形例1)

前記実施の形態1では、第1バリア層7とコンタクト電極6とを別々に形成しているが、これに限られるものではなく、前記実施の形態1の変形例1として、図4Dに示すように、第1バリア層7とコンタクト電極6とを一体化するようにしてもよい。すなわち、第1バリア層7を薄肉化又は省略するようにしてもよい。この変形例1を説明するにあたり、第1バリア層7の一例として、TiN層とTi層とが積層された積層膜を使用するとする。

(

In the first embodiment, the

この第1バリア層7のTi層は、半導体基板2の一例としてのSi基板とのオーミックコンタクト(オームの法則が成り立つ接続)を形成する機能と、第1酸化膜8と第1バリア層7のTiN層との密着力を向上させる機能とを有している。オーミックコンタクトを形成する機能として、例えば、Ti層のTiと半導体基板2のSiとの熱反応によりTiSi2のシリサイド層9を形成すれば、オーミックコンタクトになる。なお、第1バリア層7以外でシリサイド層9を形成すれば、このTi層は不要となる。

The Ti layer of the

また、第1バリア層7のTiN層は、半導体基板2(Si基板)へのコンタクト電極6のタングステン等の拡散防止機能を有している。なお、半導体基板2(Si基板)に拡散せずかつ密着力の良いコンタクト電極材料をコンタクト電極6として使用することができるならば、TiN層は不要となる。

The TiN layer of the

よって、前記したように、第1バリア層7以外でシリサイド層9を形成すれば、第1バリア層7のTi層を省略してTiN層のみとすることができる。また、半導体基板2(Si基板)に拡散せずかつ密着力の良いコンタクト電極材料をコンタクト電極6として使用すれば、第1バリア層7のTiN層を省略してTi層のみとすることができる。また、第1バリア層7以外でシリサイド層9を形成し、かつ、半導体基板2(Si基板)に拡散せずかつ密着力の良いコンタクト電極材料をコンタクト電極6として使用する場合には、第1バリア層7自体を形成せずに、コンタクト電極6のみとすることができる(図4D参照)。

Therefore, as described above, if the

このように、第1バリア層7とコンタクト電極6とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第1バリア層7の薄肉化又は省略を図ることが可能となり、その分、コンタクト電極6を大きくすることができる。

Thus, forming the

(実施の形態1の変形例2)

前記実施の形態1では、第1バリア層7とコンタクト電極6とパッド電極5とを別々に形成しているが、これに限られるものではなく、前記実施の形態1の変形例2として、図4Eに示すように、第1バリア層7とコンタクト電極6とパッド電極5とを一体化するようにしてもよい。第1バリア層7とコンタクト電極6との一体化については、前記変形例1と同じであるため、ここでは、コンタクト電極6とパッド電極5との一体化について主として説明する。

(

In the first embodiment, the

この変形例2において、コンタクト電極6は、低抵抗で半導体基板2(Si基板)とパッド電極5とに接続されている。パッド電極5は、低抵抗でコンタクト電極6に接続されており、ワイヤーボンディングを行うときには平坦部を確保する観点から必要である。すなわち、パッド電極5をコンタクト電極6とは別に設けることにより、外部電極端子として、コンタクト電極6だけの場合よりも、平坦度を向上させることができる。

In the second modification, the

しかしながら、低抵抗で半導体基板2(Si基板)に接続すれば、コンタクト電極6とパッド電極5とを一体化して、図4Eに示すように、パッド電極5を縦断面が凸形状にすることが可能となる。また、ワイヤーボンディングを使用しない場合には、パッド電極5が平坦である必要はない。

However, if it is connected to the semiconductor substrate 2 (Si substrate) with a low resistance, the

このように、第1バリア層7とコンタクト電極6とパッド電極5とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第1バリア層7とコンタクト電極6とパッド電極5とを一体化させて形成することも可能となる。

Thus, forming the

(実施の形態1の変形例3)

前記実施の形態1では、第2バリア層13と再配線層14とを別々に形成しているが、これに限られるものではなく、前記実施の形態1の変形例3として、図4Fに示すように、第2バリア層13と再配線層14とを一体化するようにしてもよい。なお、図4Fは図4Eの変形例2に変形例3を適用した図であるが、これに限られるものではなく、この変形例3は、前記変形例1又は図1などの前記実施の形態1にも適用可能なものである。

(

In the first embodiment, the

この変形例3において、第2バリア層13(例えば、Tiで構成する層)は、半導体基板2(Si基板)への再配線層14の拡散防止機能と、第2酸化膜12と再配線層14との密着力の向上機能とを有している。また、再配線層14(例えば、Cuで構成する層)は、低抵抗であり、かつ、半田ボールを搭載する機能を有している。なお、半導体基板2(Si基板)への拡散防止機能と密着力の良い再配線材料を再配線層14として使用することができるならば、第2バリア層13を不要として、図4Fに示すように、再配線層14を第2バリア層13の分だけ厚肉に形成することが可能となる。

In the third modification, the second barrier layer 13 (for example, a layer made of Ti) has a function of preventing the

このように、第2バリア層13と再配線層14とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第2バリア層13と再配線層14とを一体化させて形成することも可能となる。

Thus, forming the

(実施の形態2)

図5は、本発明の実施の形態2の半導体装置の部分断面図である。図5において、図1〜図4Cと同じ構成要素については同じ符号を用い、説明を省略する。

(Embodiment 2)

FIG. 5 is a partial cross-sectional view of the semiconductor device according to the second embodiment of the present invention. In FIG. 5, the same components as those in FIGS.

本実施の形態2の特徴的な部分は、前記実施の形態1と比較して、シリサイド層9が半導体基板2の表面2aよりもパッド電極5に近い側に形成されているため、シリサイド層9と接続する貫通電極層11の底部形状が下向きに凸になっている点である。すなわち、本実施の形態2では、第1酸化膜8の厚み方向の中間部にシリサイド層9が位置して、シリサイド層9の外面側に第1バリア層7とコンタクト電極6が配置されると共に、シリサイド層9の内面側に貫通電極層11の底部の中央部が入り込んだ形状となっている。なお、これに対して、前記実施の形態1では、シリサイド層9が半導体基板2の表面2aよりもパッド電極5に遠い側に形成されているため、シリサイド層9と接続する貫通電極層11の底部形状が上向きに凸になっている。

A characteristic part of the second embodiment is that the

このように貫通電極層11の底部形状が下向きに凸になっているのは、製造方法に起因するため、本実施の形態2の半導体装置1の製造方法について、図面を参照しながら説明する。図6は、本実施の形態2における半導体装置の製造方法を示すフローチャートであり、図7A〜図8Cは、本実施の形態2における半導体装置の製造方法を説明するための部分断面図である。図7A〜図8Cにおいて、図1〜図4Cと同じ構成要素については同じ符号を用い、説明を省略する。

Since the bottom shape of the through

最初に、図7Aに示すように、不図示の電子回路が形成された半導体基板2の表面2aの上の第1酸化膜8の中に、ポリシリコン膜16とシリサイド層9と第1バリア層7及びコンタクト電極6を形成した後、パッド電極5及びパッシベーション膜4が形成される(図6のステップS11参照)。このポリシリコン膜16は、その上にシリサイドを形成するための膜であり、シリサイド形成後は不要となる膜である。ただし、完全に取り除く必要は無く、Si基板とショートしない程度であれば、シリサイド形成後に残っていても問題はない。

First, as shown in FIG. 7A, a

ポリシリコン膜16は、第1酸化膜8が形成される前に形成されることが望ましいが、第1酸化膜8が形成された後に形成されても良い。

The

シリサイド層9は、第1バリア層7を熱処理することで形成しても良いし、ポリシリコン膜16の上に別の膜(例えば、タングステン、チタン、コバルト、又は、ニッケルなど)を成膜後に熱処理することで、タングステンシリサイド、チタンシリサイド、コバルトシリサイド、又は、ニッケルシリサイドなどとして形成しても良い。第1バリア層7を熱処理することによりポリシリコン膜16の上にシリサイド層9を形成する場合、シリサイド層9が円形の場合の直径はコンタクト電極6が円形の場合のホール径と等しくなる。一方、タングステン、チタン、コバルト、又は、ニッケルなどを成膜後に熱処理することでポリシリコン膜16の上にシリサイド層9を形成する場合、シリサイド層9が円形の場合の径はコンタクト電極6が円形の場合のホール径と等しくても良いし、等しくなくても良い。

The

コンタクト電極6は、単一の太いコンタクト電極部材で構成してもよく、代わりに、図15〜図16に示すように、単一のコンタクト電極部材6を複数の細いコンタクト電極部材6Aに分割したような、複数のコンタクト電極部材6Aで構成するようにしてもよい。コンタクト電極6が円形の場合の直径は、パッド電極5が円形の場合の直径よりも必ずしも小さい必要はなく、大きくても、同じでも良い。なお、図15は、本発明の実施の形態2の半導体装置において、コンタクト電極形成前にシリサイドを形成する場合に、コンタクト電極が複数のコンタクト電極部材である例を示す部分断面図である。図16は、本発明の実施の形態2の半導体装置において、コンタクト電極形成後にシリサイドを形成する場合に、コンタクト電極が複数のコンタクト電極部材である例を示す部分断面図である。

The

そして、パッシベーション膜4の上に、不図示の接着剤を介して、支持基板3が接着される(図7A参照)。

And the

次に、図7Bに示すように、半導体基板2の裏面2bの上に、パッド電極5に相当する位置を開口するために、レジスト15が形成される(図6のステップS12参照)。

Next, as shown in FIG. 7B, a resist 15 is formed on the

そして、図7Cに示すように、レジスト15をマスクとして、半導体基板2とポリシリコン膜16をエッチングすることにより、シリサイド層9及び第1酸化膜8に到達するビアホール10が形成される(図6のステップS13参照)。ここで、本実施の形態2の特徴であるシリサイド層9と接続する貫通電極層11の底部形状が下凸になる。半導体基板2とポリシリコン膜16のエッチングは、ウェットエッチングでもドライエッチングでも良い。

Then, as shown in FIG. 7C, the via

シリサイド層9の直径Aとビアホール10の内径Bとの間に前述の(式1)の関係が成り立つようにすることにより、シリサイド層9は半導体基板2とポリシリコン膜16とから物理的にも電気的にも分離される。ビアホール10とシリサイド層9とポリシリコン膜16の加工精度は異なり、ビアホール10の内径のばらつきが約1μm単位であるのに対して、シリサイド層9の直径の加工ばらつきは約1nm単位である。また、ポリシリコン膜16の直径の加工ばらつきは、シリサイド層9と同等であり、約1nm単位である。

By making the relationship of the above-mentioned (Formula 1) hold between the diameter A of the

ビアホール10の内径はパッド電極5の直径よりも大きくすることが可能であるため、ビアホール10のアスペクト比を低減することができ、さらには、パッド電極5の大きさを縮小することにより、半導体装置の一例としての半導体チップの面積を削減することができる。

Since the inner diameter of the via

また、半導体基板2とポリシリコン膜16とをエッチングすることで、導電層としてシリサイド層9が露出されるため、第1酸化膜8のエッチングは不要である。

Further, since the

次に、図7Dに示すように、レジスト15を半導体基板2の裏面2bから除去する(図6のステップS14参照)。レジスト15の除去は、ウェットプロセスでもドライプロセスでも良い。

Next, as shown in FIG. 7D, the resist 15 is removed from the

そして、図8Aに示すように、ビアホール10の側壁10a及び半導体基板2の裏面2bに第2酸化膜12を形成する(図6のステップS15参照)。第2酸化膜12の形成は、熱酸化法でも良いし、CVD法でも良いし、又は、スパッタ法でも良い。

Then, as shown in FIG. 8A, the

次に、図8Bに示すように、シリサイド層9及び第1酸化膜8の上の第2酸化膜12をエッチングすることにより、シリサイド層9を再度露出させる(図6のステップS16参照)。第1酸化膜8の上の第2酸化膜12はエッチングされずに残っても良い。また、第1酸化膜8の側壁に形成された第2酸化膜12もエッチングされずに残っても良い。第2酸化膜12のエッチングは、ドライエッチングが望ましい。

Next, as shown in FIG. 8B, the

続いて、図8Cに示すように、第2バリア層13及び再配線層14を形成する(図6のステップS17参照)。第2バリア層13の形成は、CVD法でも良いし、スパッタ法でも良いし、又は、これらの組み合わせでも良い。再配線層14の形成は、メッキ法が望ましいが、CVD法でも良いし、スパッタ法でも良いし、これらの組み合わせでも良い。再配線層14は、ビアホール10を不完全に埋め込んだ形状でも良いし、又は、完全に埋め込んだ形状でも良い。

Subsequently, as shown in FIG. 8C, the

本実施の形態2の半導体装置1の数値例は、前記実施の形態1の数値例に追加して、ポリシリコン膜16の厚みが150nm(ドーピング有無はどちらでも可。)である。

In the numerical example of the

本実施の形態2にかかる構成によれば、パッド電極5と貫通電極層11との間の抵抗値は、シリサイド層9の直径寸法に依存し、ビアホール10の内径寸法に依存しない状態にすることができるため、パッド電極5と貫通電極層11との間の抵抗値は、ビアホール10の内径寸法のばらつきに影響されなくなる。ビアホール10とシリサイド層9との加工精度は異なり、ビアホール10の内径寸法のばらつきが約1μm単位であるのに対して、シリサイド層9の直径寸法の加工ばらつきは約1nm単位であり、三桁異なるため、本実施の形態2にかかる半導体装置1は、従来よりもパッド電極5と貫通電極層11との間の抵抗値ばらつきを小さくすることができる。

According to the configuration according to the second embodiment, the resistance value between the

更に、本実施の形態2にかかる半導体装置1は、前記実施の形態1の半導体装置1よりも、パッド電極5と第1バリア層7との間のコンタクト電極6の長さが短いため、パッド電極5と貫通電極層11との間の抵抗値を小さくすることもできる。

Furthermore, since the

また、本実施の形態2にかかる半導体装置1においても、ビアホール10の内径はパッド電極5の直径よりも大きくすることが可能であるため、ビアホール10のアスペクト比を低減することができ、さらには、パッド電極5の大きさを縮小することにより、半導体装置の一例としての半導体チップの面積を削減することができる。すなわち、本実施の形態2でも、ビアホール10の中心軸方向(長手方向)の寸法と底部の幅(例えば、円形ビアホール10の直径)とのアスペクト比を従来と同じに設定すると、シリサイド層9の幅(例えば、円形シリサイド層9の直径)寸法をビアホール10の底部の幅よりも小さくすることができ、半導体チップ面積の削減が可能となる。逆に、シリサイド層9の幅(例えば、円形シリサイド層9の直径)寸法を、従来のパッド電極とビアホールの底部の幅(直径)寸法との接続部分の幅寸法と同じに設定すると、ビアホール10の幅(直径)寸法は、従来よりも大きくしてもよくなり、ビアホール10の加工がしやすくなる。

Also in the

これに対して、従来の半導体装置においては、ビアホールの底部の幅(直径)寸法の精度を向上させようとしても、ビアホールの底部の幅(直径)寸法自体をコントロールすることができず、ビアホールの底部とは反対側の開口部側の幅(直径)寸法自体しかコントロールすることができなかった。また、ビアホールは、一般に、実際には、傾斜したテーパ側面を有するため、ビアホールの底部の幅(直径)寸法をコントロールすることは非常に困難である。 On the other hand, in the conventional semiconductor device, even if the accuracy of the width (diameter) dimension of the bottom of the via hole is to be improved, the width (diameter) dimension of the bottom of the via hole cannot be controlled. Only the width (diameter) dimension of the opening side opposite to the bottom could be controlled. In general, a via hole generally has an inclined tapered side surface, so that it is very difficult to control the width (diameter) dimension of the bottom of the via hole.

なお、本実施の形態2において、ポリシリコン膜16は、アモルファスシリコン膜、または、単結晶シリコン膜であっても同様の効果が得られる。

In the second embodiment, the same effect can be obtained even if the

(実施の形態2の変形例1)

前記実施の形態2では、第1バリア層7とコンタクト電極6とを別々に形成しているが、これに限られるものではなく、前記実施の形態2の変形例1として、図8Dに示すように、第1バリア層7とコンタクト電極6とを一体化するようにしてもよい。すなわち、第1バリア層7を薄肉化又は省略するようにしてもよい。この変形例1を説明するにあたり、第1バリア層7の一例として、TiN層とTi層とが積層された積層膜を使用するとする。

(

In the second embodiment, the

この第1バリア層7のTi層は、半導体基板2の一例としてのSi基板とのオーミックコンタクトを形成する機能と、第1酸化膜8と第1バリア層7のTiN層との密着力を向上させる機能とを有している。オーミックコンタクトを形成する機能として、例えば、Ti層のTiと半導体基板2のSiとの熱反応によりTiSi2のシリサイド層9を形成すれば、オーミックコンタクトになる。なお、第1バリア層7以外でシリサイド層9を形成すれば、Ti層は不要となる。

The Ti layer of the

また、第1バリア層7のTiN層は、半導体基板2(Si基板)へのコンタクト電極6のタングステン等の拡散防止機能を有している。なお、半導体基板2(Si基板)に拡散しないコンタクト電極材料をコンタクト電極6として使用することができるならば、TiN層は不要となる。

The TiN layer of the

よって、前記したように、第1バリア層7以外でシリサイド層9を形成すれば、第1バリア層7のTi層を省略してTiN層のみとすることができる。また、半導体基板2(Si基板)に拡散せずかつ密着力の良いコンタクト電極材料をコンタクト電極6として使用すれば、第1バリア層7のTiN層を省略してTi層のみとすることができる。また、第1バリア層7以外でシリサイド層9を形成し、かつ、半導体基板2(Si基板)に拡散せずかつ密着力の良いコンタクト電極材料をコンタクト電極6として使用する場合には、第1バリア層7自体を形成せずに、コンタクト電極6のみとすることができる(図8D参照)。

Therefore, as described above, if the

このように、第1バリア層7とコンタクト電極6とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第1バリア層7の薄肉化又は省略を図ることが可能となり、その分、コンタクト電極6を大きくすることができる。

Thus, forming the

(実施の形態2の変形例2)

前記実施の形態2では、第1バリア層7とコンタクト電極6とパッド電極5とを別々に形成しているが、これに限られるものではなく、前記実施の形態2の変形例2として、図8Eに示すように、第1バリア層7とコンタクト電極6とパッド電極5とを一体化するようにしてもよい。第1バリア層7とコンタクト電極6との一体化については、前記変形例1と同じであるため、ここでは、コンタクト電極6とパッド電極5との一体化について主として説明する。この変形例2において、コンタクト電極6は、低抵抗で半導体基板2(Si基板)とパッド電極5とに接続されている。パッド電極5は、低抵抗でコンタクト電極6に接続されており、ワイヤーボンディングを行うときには平坦部を確保する観点から必要である。すなわち、パッド電極5をコンタクト電極6とは別に設けることにより、外部電極端子として、コンタクト電極6だけの場合よりも、平坦度を向上させることができる。しかしながら、低抵抗で半導体基板2(Si基板)に接続すれば、コンタクト電極6とパッド電極5とを一体化して、図8Eに示すように、パッド電極5を縦断面が凸形状にすることが可能となる。また、ワイヤーボンディングを使用しない場合には、パッド電極5が平坦である必要はない。

(

In the second embodiment, the

このように、第1バリア層7とコンタクト電極6とパッド電極5とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第1バリア層7とコンタクト電極6とパッド電極5とを一体化させて形成することも可能となる。

Thus, forming the

(実施の形態2の変形例3)

前記実施の形態2では、第2バリア層13と再配線層14とを別々に形成しているが、これに限られるものではなく、前記実施の形態2の変形例3として、図8Fに示すように、第2バリア層13と再配線層14とを一体化するようにしてもよい。なお、図8Fは図8Eの変形例2に変形例3を適用した図であるが、これに限られるものではなく、この変形例3は、前記変形例1又は図5などの前記実施の形態2にも適用可能なものである。

(

In the second embodiment, the

この変形例3において、第2バリア層13(例えば、Tiで構成する層)は、半導体基板2(Si基板)への再配線層14の拡散防止機能と、第2酸化膜12と再配線層14との密着力の向上機能とを有している。また、再配線層14(例えば、Cuで構成する層)は、低抵抗であり、かつ、半田ボールを搭載する機能を有している。なお、半導体基板2(Si基板)への拡散防止機能と密着力の良い再配線材料を再配線層14として使用することができるならば、第2バリア層13を不要として、図8Fに示すように、再配線層14を第2バリア層13の分だけ厚肉に形成することが可能となる。

In the third modification, the second barrier layer 13 (for example, a layer made of Ti) has a function of preventing the

このように、第2バリア層13と再配線層14とを別々に形成するのは、製造方法上の前記課題を解決するための1つの手段であるため、前記課題をそれぞれ解決できるならば、第2バリア層13と再配線層14とを一体化させて形成することも可能となる。

Thus, forming the

なお、上記様々な実施の形態のうちの任意の実施の形態を適宜組み合わせることにより、それぞれの有する効果を奏するようにすることができる。 It is to be noted that, by appropriately combining any of the above-described various embodiments, the effects possessed by them can be produced.

本発明の半導体装置は、パッド電極と貫通電極層との間の抵抗値がビアホールの内径の寸法のばらつきに依存しない、信頼性に優れた貫通電極層を有しており、半導体基板に貫通電極層を形成する半導体装置に広く適用できる。 The semiconductor device of the present invention has a highly reliable through electrode layer in which the resistance value between the pad electrode and the through electrode layer does not depend on the variation in the inner diameter of the via hole. The present invention can be widely applied to semiconductor devices for forming layers.

1 半導体装置

2 半導体基板

3 支持基板

4 パッシベーション膜

5 パッド電極

6 コンタクト電極

7 第1バリア層

8 第1酸化膜

9 シリサイド層

10 ビアホール

10a 側壁

11 貫通電極層

12 第2酸化膜

13 第2バリア層

14 再配線層

15 レジスト

16 ポリシリコン膜

18 電極部

DESCRIPTION OF

Claims (13)

前記第1絶縁膜の中に形成され、かつ、外部接続端子を有する電極部と、

前記半導体基板の裏面から前記表面に貫通するビアホールと、

前記ビアホールの側壁及び前記半導体基板の前記裏面に形成された第2絶縁膜と、

前記ビアホールの前記側壁上の前記第2絶縁膜と前記半導体基板の前記裏面上の前記第2絶縁膜と前記ビアホールの底面の前記第1絶縁膜とに形成された貫通電極層と、

前記電極部と前記貫通電極層との間に形成され、かつ前記電極部及び前記貫通電極層に接続されたシリサイド層と、を備え、

前記ビアホールの中心軸を含む平面で切断された断面における、前記シリサイド層の幅Aと前記ビアホールの底部の幅Bとの関係が、A≦Bであることを特徴とする

半導体装置。 A first insulating film formed on the surface of the semiconductor substrate;

An electrode portion formed in the first insulating film and having an external connection terminal;

A via hole penetrating from the back surface of the semiconductor substrate to the front surface;

A second insulating film formed on a sidewall of the via hole and the back surface of the semiconductor substrate;

A through electrode layer formed on the second insulating film on the sidewall of the via hole, the second insulating film on the back surface of the semiconductor substrate, and the first insulating film on the bottom surface of the via hole;

A silicide layer formed between the electrode part and the through electrode layer and connected to the electrode part and the through electrode layer;

A semiconductor device, wherein a relation between a width A of the silicide layer and a width B of the bottom of the via hole in a cross section cut along a plane including the central axis of the via hole is A ≦ B.

請求項1に記載の半導体装置。 The semiconductor device according to claim 1, wherein the silicide layer and the electrode portion are connected via a contact electrode.

請求項2に記載の半導体装置。 3. The semiconductor device according to claim 2, wherein the width of the silicide layer is equal to the width of the contact electrode in the plane including the central axis of the via hole.

請求項1〜3のいずれか1つに記載の半導体装置。 4. The semiconductor device according to claim 1, wherein a width of the electrode portion is larger than a width of the bottom portion of the via hole in the plane including the central axis of the via hole.

前記電極部の本体部と、

前記電極部の前記本体部と前記第1絶縁膜との間に配置された第1バリア層とを備えることを特徴とする

請求項1〜4のいずれか1つに記載の半導体装置。 The electrode part is

A body portion of the electrode portion;

5. The semiconductor device according to claim 1, further comprising: a first barrier layer disposed between the main body portion of the electrode portion and the first insulating film.

前記電極部の本体部と、

前記電極部の前記本体部と前記第1絶縁膜との間に配置されかつ前記シリサイド層に接触する第1バリア層と、

前記第1絶縁膜の外面側でかつ前記電極部の前記本体部の外面に配置されて前記外部接続端子として機能するパッド電極部とを備えることを特徴とする

請求項1〜4のいずれか1つに記載の半導体装置。 The electrode part is

A body portion of the electrode portion;

A first barrier layer disposed between the main body portion of the electrode portion and the first insulating film and in contact with the silicide layer;

The pad electrode part which is arrange | positioned on the outer surface side of the said 1st insulating film and is arranged in the outer surface of the said main-body part of the said electrode part, and functions as the said external connection terminal is provided. The semiconductor device described in one.

請求項1〜6のいずれか1つに記載の半導体装置。 The semiconductor device according to claim 1, wherein the silicide layer is formed on any one of the semiconductor substrate, a polysilicon film, and an amorphous silicon film.

請求項1〜7のいずれか1つに記載の半導体装置。 The semiconductor device according to claim 1, wherein the silicide layer is made of tungsten silicide, titanium silicide, cobalt silicide, or nickel silicide.

請求項7又は8に記載の半導体装置。 9. The semiconductor device according to claim 7, wherein the main body portion of the electrode portion is made of tungsten, aluminum, an alloy thereof, or copper.

請求項6に記載の半導体装置。 The semiconductor device according to claim 6 , wherein the first barrier layer is made of a laminated film of titanium, titanium nitride, titanium tungsten, tantalum, tantalum nitride, or a refractory metal.

前記ビアホールの前記側壁上の前記第2絶縁膜と前記半導体基板の前記裏面上の前記第2絶縁膜と前記ビアホールの底面の前記第1絶縁膜とに形成された第2バリア層と、

前記第2バリア層上に形成された再配線層とを備え、

前記第2バリア層は、チタン、チタンナイトライド、チタンタングステン、タンタル、タンタルナイトライド、又は、高融点金属の積層膜から成ることを特徴とする

請求項1〜10のいずれか1つに記載の半導体装置。 The through electrode layer includes:

A second barrier layer formed on the second insulating film on the side wall of the via hole, the second insulating film on the back surface of the semiconductor substrate, and the first insulating film on the bottom surface of the via hole;

A rewiring layer formed on the second barrier layer,

The said 2nd barrier layer consists of a laminated film of titanium, titanium nitride, titanium tungsten, tantalum, tantalum nitride, or a refractory metal, It is any one of Claims 1-10 characterized by the above-mentioned. Semiconductor device.

請求項1〜11のいずれか1つに記載の半導体装置。 The semiconductor device according to claim 1, wherein the electrode unit is configured by a single contact electrode member or a plurality of contact electrode members.

請求項6に記載の半導体装置。 7. The pad electrode according to claim 6, wherein the pad electrode is made of aluminum, copper, or an alloy thereof, and titanium, titanium nitride, tantalum, tantalum nitride, a refractory metal, or a compound thereof. Semiconductor device.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009116316A JP5462524B2 (en) | 2009-05-13 | 2009-05-13 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009116316A JP5462524B2 (en) | 2009-05-13 | 2009-05-13 | Semiconductor device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010267695A JP2010267695A (en) | 2010-11-25 |

| JP2010267695A5 JP2010267695A5 (en) | 2012-04-12 |

| JP5462524B2 true JP5462524B2 (en) | 2014-04-02 |

Family

ID=43364445

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009116316A Expired - Fee Related JP5462524B2 (en) | 2009-05-13 | 2009-05-13 | Semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5462524B2 (en) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5810693B2 (en) * | 2011-07-08 | 2015-11-11 | 富士通株式会社 | Electronic device and manufacturing method thereof |

| JP2014011438A (en) | 2012-07-03 | 2014-01-20 | Toshiba Corp | Semiconductor device and method of manufacturing the same |

| JP5917321B2 (en) * | 2012-07-12 | 2016-05-11 | 株式会社東芝 | Semiconductor device and manufacturing method thereof |

| JP6468071B2 (en) * | 2015-05-25 | 2019-02-13 | 富士通株式会社 | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005109347A (en) * | 2003-10-01 | 2005-04-21 | Seiko Epson Corp | Semiconductor device and method of manufacturing the same |

| JP2005276877A (en) * | 2004-03-23 | 2005-10-06 | Sanyo Electric Co Ltd | Semiconductor device and its manufacturing method |

| JP4373866B2 (en) * | 2004-07-16 | 2009-11-25 | 三洋電機株式会社 | Manufacturing method of semiconductor device |

-

2009

- 2009-05-13 JP JP2009116316A patent/JP5462524B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010267695A (en) | 2010-11-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5518091B2 (en) | Semiconductor device and manufacturing method of semiconductor device | |

| US6897570B2 (en) | Semiconductor device and method of manufacturing same | |

| JP4775007B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4373866B2 (en) | Manufacturing method of semiconductor device | |

| US9177893B2 (en) | Semiconductor component with a front side and a back side metallization layer and manufacturing method thereof | |

| JP5154000B2 (en) | Semiconductor device | |

| CN101465332B (en) | Semiconductor chip, method of fabricating the same and semiconductor chip stack package | |

| US20090121323A1 (en) | Semiconductor device and method of fabricating the same | |

| US20090061659A1 (en) | Through-hole interconnection structure for semiconductor wafer | |

| US8232202B2 (en) | Image sensor package and fabrication method thereof | |

| TWI296832B (en) | Bump structures and methods for forming solder bumps | |

| JP2008546174A5 (en) | ||

| US6696357B2 (en) | Method for manufacturing semiconductor integrated circuit devices using a conductive layer to prevent peeling between a bonding pad and an underlying insulating film | |

| CN108417550B (en) | Semiconductor device and method for manufacturing the same | |

| US6576970B2 (en) | Bonding pad structure of semiconductor device and method for fabricating the same | |

| JP5462524B2 (en) | Semiconductor device | |

| JP2008210952A (en) | Manufacturing method of semiconductor device, manufacturing method of silicone interposer and manufacturing method of semiconductor module | |

| JP7372423B2 (en) | Semiconductor elements and semiconductor devices | |

| US7781334B2 (en) | Method of manufacturing a semiconductor device with through-chip vias | |

| JP5324121B2 (en) | Manufacturing method of semiconductor device | |

| US8387459B2 (en) | MEMS sensor | |

| US20120018880A1 (en) | Semiconductor structure and manufacturing method thereof | |

| TW200849539A (en) | Semiconductor device, chip package and method of fabricating the same | |

| US7557455B1 (en) | System and apparatus that reduce corrosion of an integrated circuit through its bond pads | |

| JP2013239756A (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120228 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131011 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131022 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140117 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |