以下、添付図面に従って本発明に係る実施形態を詳細に説明する。なお、本実施形態では、FIPS197に定義されるAES-128(以下、単にAESと略記する)を例にとって説明する。

<第1の実施形態>

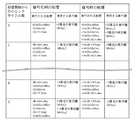

図1は第1の実施形態における各クロックサイクル内で実行される暗号化処理の処理内容を従来例と比較して示したものである。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。また、実行鍵wkeyi(iはラウンド数を示す)はFIPS197記載のRound Keyのことである。

本実施形態は、0サイクル目から8サイクル目ではAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算を実行する。そして、9サイクル目では、第1のAddRoundKey演算、ShiftRows演算、SubBytes演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey0、1サイクル目ではwkey1、…、8サイクル目ではwkey8が用いられ、9サイクル目では2つの実行鍵wkey9、wkey10が必要となる。

本実施形態は従来と比較して、トータルで実行している処理は同じであるが、本実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本実施形態において各クロックサイクル内で実行される暗号化処理に必要な処理時間について述べる。図2は、従来技術と第1の実施形態における各クロックサイクル内で実行される暗号化処理に必要な処理時間を比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図2に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本実施形態では、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う0〜8サイクル目の処理に必要な処理時間は、AddRoundKey演算、SubBytes演算、ShiftRows演算、AddRoundKey演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態もまた実施可能である。

本発明はAESの復号処理についても同様に適用可能である。

図3は実施形態において各クロックサイクル内で実行される復号処理の処理内容を従来例と比較して示したものである。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本実施形態は、0サイクル目では第1のAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、第2のAddRoundKey演算を行う。そして、1サイクル〜9サイクル目ではInvMixColumns演算、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算を実行する。実行鍵は0サイクル目では2つの実行鍵wkey9とwkey10、1サイクル目ではwkey8、2サイクル目ではwkey7、…、9サイクル目ではwkey0が用いられる。

本実施形態と従来技術はトータルで実行している処理は同じであるが、本実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間について述べる。図4は、第1の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図4に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本実施形態では、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う1〜9サイクル目の処理に必要な処理時間は、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、AddRoundKey演算を行う0サイクル目の処理に必要な処理時間よりも長い。本実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態もまた実施可能である。

ここまでで説明してきた本発明の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本発明では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。本発明は1サイクル内に実行される処理に必要な処理時間を増やすことなく、AESの暗号化処理、復号処理に要するクロックサイクル数を1サイクル削減しており、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

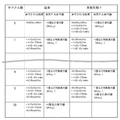

図5は、本実施形態のAES処理回路のブロック図を示したものである。

図5において、101はAESの処理を実行するAES処理回路、102は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。103は鍵拡張部102より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。104はAES処理回路101の外部からの制御信号を受け、鍵拡張部102および暗号化・復号処理部103の動作を制御するための信号を生成し、かつAES処理回路101の外部に対して動作完了を通知するための信号を生成する制御部である。

同図において、150は暗号化処理の対象となる平文データもしくは復号処理の対象となる暗号文データであるところの入力信号である。151は暗号化・復号処理部103において入力信号150を暗号化、または復号処理した結果であるところの出力信号である。152は暗号化・復号処理で用いられる共通鍵、153は暗号化処理、復号処理のどちらを行うかを選択するための暗号化・復号選択信号である。155は鍵拡張部102において共通鍵152から実行鍵を生成する鍵拡張を開始させるための鍵準備開始信号、157は暗号化処理または復号処理が1サイクル後に実行可能となることを示す暗号化・復号処理許可信号である。158は入力信号150に対して暗号化処理または復号処理を開始させるための暗号化・復号処理開始信号、159は暗号化・復号処理部103において暗号化または復号処理を行った結果が出力信号151に保持されていることを示す有効出力期間信号である。160は暗号化・復号処理部103に対して出力信号151を一定値に保持せしめるための出力保持制御信号である。161は鍵準備や暗号化・復号処理の際に、鍵準備開始信号155または暗号化・復号処理開始信号158の立ち上がりからのサイクル数を示すカウンタ信号である。162は実行鍵のうちの一つであるところの実行鍵Aである。163は鍵拡張部102で生成された暗号化処理の最後のサイクルで使用される実行鍵、もしくは復号時の最初のサイクルで使用される実行鍵であるところの実行鍵Bである。170は暗号化・復号処理部103においてサブブロック演算の接続を切り替えるための選択信号、171は暗号化・復号処理部103において被処理データを切り替えるための選択信号である。

上記構成において、外部からの入力信号150は暗号化・復号処理部103に入力され、出力信号151は暗号化・復号処理部103より外部に対して出力される。共通鍵152は外部より鍵拡張部102に対して入力され、暗号化・復号選択信号153は外部より鍵拡張部102、暗号化・復号処理部103および制御部104に対して入力される。鍵準備開始信号155は外部より鍵拡張部102および制御部104に対して入力される。暗号化・復号処理許可信号157は制御部104より外部に対して出力され、暗号化・復号処理開始信号158は外部より鍵拡張部102および制御部104に対して入力される。有効出力期間信号159は制御部104より外部に対して出力され、出力保持制御信号160は制御部104より暗号化・復号処理部103に対して入力される。カウンタ信号161は制御部104から鍵拡張部102に対して出力され、実行鍵A(参照番号162、以下、同様)は鍵拡張部102から暗号化・復号処理部103に対して出力される。実行鍵B(163)は鍵拡張部102から暗号化・復号処理部103に対して出力される。選択信号170は制御部104から暗号化・復号処理部103に対して出力され、選択信号171は制御部104から暗号化・復号処理部103に対して出力される。

次に、暗号化・復号処理部103について説明する。図6は暗号化・復号処理部103のブロック図を示したものである。同図において、105は、選択信号170による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理を行うラウンド処理部である。106は選択信号170による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて復号処理を行うラウンド処理部である。

107は暗号化・復号選択信号153に応じて、ラウンド処理部105の出力、もしくはラウンド処理部106の出力のいずれかを選択するためのセレクタである。108は出力保持制御信号160に応じてセレクタ107により選択された信号を保持するデータ保持部である。109は選択信号171に応じて、入力信号150、もしくはデータ保持部108の出力信号のいずれかを選択するためのセレクタである。

同図において、165はラウンド処理部105およびラウンド処理部106への入力信号、166は入力信号165に対してラウンド処理部105で処理を施した結果であるところの出力信号である。167は入力信号165に対してラウンド処理部106で処理を施した結果であるところの出力信号、168はセレクタ107の出力信号である。

上記構成において、セレクタ109には入力信号150、データ保持部の出力データおよび選択信号171が入力される。ラウンド処理部105にはセレクタ109の出力、実行鍵A(162)、実行鍵B(163)、選択信号170が入力される。ラウンド処理部106にはセレクタ109の出力、実行鍵A(162)、実行鍵B(163)、選択信号170が入力される。セレクタ107にはラウンド処理部105の出力信号、ラウンド処理部106の出力信号および暗号化・復号処理選択信号153が入力される。データ保持部108にはセレクタ107の出力およびデータ保持制御信号160が入力される。そして、データ保持部108は暗号化・復号処理部103の出力信号151を出力する。

また、上記構成において、セレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力信号151を選択し出力する。セレクタ109により選択された結果であるところの入力信号165は、ラウンド処理部105およびラウンド処理部106に入力され、それぞれ暗号化処理、復号処理を施される。セレクタ107は暗号化・復号選択信号153がNegateされている時はラウンド処理部105の出力結果であるところの出力信号166、Assertされている時はラウンド処理部106の出力結果であるところの出力信号167を選択し、出力する。セレクタ107の出力信号168は、データ保持部108へ入力され、一時保持される。データ保持部108の出力信号151は暗号化・復号処理部103の出力信号である。同時にセレクタ109の入力へも接続されており、セレクタ信号171がAssertされている間、ラウンド処理部105における暗号化処理、またはラウンド処理部106による復号処理が繰り返し実行される。

暗号化・復号処理が終了し、かつ次なる暗号化・復号処理が開始されていない場合、制御部104により出力保持制御信号160がAssertされる。その間、データ保持部108は出力信号168によらず出力信号151を一定値に保持し続ける。

次に、ラウンド処理部105について説明する。図7はラウンド処理部105のブロック図について示したものである。同図において、110は入力信号165および実行鍵A(162)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部(第1のAddRoundKey演算部に相当)である。111はAddRoundKey演算部110の出力を入力としSubBytes演算を行うところのSubBytes演算部である。112はSubBytes演算部111の出力を入力としShiftRows演算を行うところのShiftRows演算部である。113はShiftRows演算部112の出力を入力とし、MixColumns演算を行うところのMixColumns演算部である。114はShiftRows演算部112の出力および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部(第2のAddRoundKey演算部に相当)である。115は選択信号170に応じてMixColumns演算部113の出力、もしくはAddRoundKey演算部114の出力のいずれか一方を選択し、出力するセレクタである。セレクタ115の出力信号はラウンド処理部105の出力となる。

上記構成において、セレクタ115は選択信号170がNegateされている時はMixColumns演算部の出力、Assertされている時はAddRoundKey演算部の出力を選択し、出力する。

次に、ラウンド処理部106について、図8のブロック図を参照して説明する。

同図において、116は入力信号165を入力としInvMixColumns演算を行うところのInvMixColumns演算部である。117は入力信号165および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。118は選択信号170に応じて、InvMixColumns演算部116の出力かAddRoundKey演算部117の出力のいずれか一方を選択し、出力するセレクタである。119はセレクタ118の出力を入力としInvShiftRows演算を行うところのInvShiftRows演算部である。120はInvShiftRows演算部119の出力を入力としInvSubBytes演算を行うところのInvSubBytes演算部である。121はInvSubBytes演算部120の出力を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。AddRoundKey演算部121の出力はラウンド処理部106の出力となる。

上記構成において、セレクタ118は選択信号170がNegateされている時InvMixColumns演算部116の出力、Assertされている時はAddRoundKey演算部117の出力を選択し、出力する。

次に、上記構成における暗号化処理時の動作について説明する。図9は本実施形態の暗号化処理時のタイミングチャートを示したものである。図9において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33とタイミング名が割り当てられている。

同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図5〜図8で使用されている信号線のナンバと一対一で対応している。

図9のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)である。そして、4つ目は、2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定では、共通鍵152、暗号化・復号選択信号153の他、必要に応じて鍵長や暗号モードなど暗号化・復号処理の各種パラメータが設定される。暗号化・復号選択信号153および共通鍵152の値は、新たにパラメータ設定が行われるまで外部より値が常に保持されている必要がある。パラメータ設定期間はリセット直後からの任意長の期間であり、AES処理回路101の外部より鍵準備開始信号155がAssertされると(T06)、パラメータ設定期間が終了する。

パラメータ設定期間が終了すると同時に、次の鍵準備期間が開始される。鍵準備期間は、暗号処理の9サイクル目(T26)において、鍵拡張部102が2つの実行鍵(wkey9、wkey10)を暗号化・復号処理部103に対して同時に供給するために、事前に最後の実行鍵(wkey10)を生成するための期間である。鍵準備期間は鍵準備開始信号155がAssertされてから(T06)、最後の実行鍵(wkey10)が生成される11サイクル後(T17)までの期間である。

次に、鍵準備期間における各回路の動作について述べる。まず、鍵準備開始信号155がAssertされると、制御部104はカウンタ信号161を0から順次カウントアップする。鍵拡張部102はカウンタ信号161に合わせてwkey0(共通鍵152)を各クロックサイクルごとに拡張していき、10個の実行鍵wkey1、wkey2、…、wkey10を生成していく。生成された実行鍵は実行鍵A(162)より順次出力されるようになっている。

タイミングT16でカウンタ信号161が”10”になると、鍵拡張部102は、生成した実行鍵(wkey10)をレジスタに保持し、実行鍵B(163)より出力する。以後、wkey10は、再び鍵準備が実行されるまで保持され続ける。

鍵準備期間が終了すると(T17)、鍵拡張部102は、暗号化・復号処理で最初に用いられる実行鍵(暗号化時はwkey0、復号時はwkey9)を実行鍵A(162)より出力する。実行鍵A(162)の値は、暗号化・復号処理開始信号158がAssertされるまで保持される。そして、制御部104はカウンタ信号161のカウントアップを停止し、カウンタをゼロクリアする。

また、鍵準備期間の終了に合わせ、制御部104はT16において、T17で鍵準備が終了し、暗号化処理が可能となることを見越し、暗号化・復号処理許可信号157をAssertする。

AES処理回路101の外部にある入力信号供給部は、T17で暗号化・復号処理許可信号157のAssertを検知すると、入力信号150として平文データP0をAES処理回路101に供給する。そして、入力信号150に対する暗号化処理を開始せしめるため、暗号化・復号処理開始信号158をAssertする(T17)。なお、このタイミングチャートでは最短のサイクルで暗号化・復号処理開始信号158がAssertされているが、そのタイミングはAES処理回路101の外部で自由に決められる。

暗号化処理期間は、入力信号150に対して暗号化処理を行う期間である。暗号化処理期間は、暗号化・復号処理開始信号158がAssert(T17)されてから、その10サイクル後(T27)までの期間である。

制御部104は暗号化・復号処理開始信号158のAssertを検知すると、次サイクル(T18)で暗号化・復号処理許可信号157、有効出力期間信号159、出力保持制御信号160をNegateする。同時に、カウンタ信号161のカウントアップを開始する。

鍵拡張部102は、カウンタ信号161にしたがって実行鍵wkey0から順次鍵拡張を行い、T18ではwkey1、T19ではwkey2、…、T26ではwkey9を実行鍵A(162)として暗号化・復号処理部103に出力する。

ラウンド処理部105はT17〜T18では選択信号171がNegateされているため、入力信号150に対して、実行鍵Aとして出力されているwkey0を用いて各サブブロック演算を行う。そして、T18〜T27では選択信号171がAssertされているため、データ保持部108の出力に対して、T18〜T19ではwkey1、T19〜T20ではwkey2、…、T25〜T26ではwkey8を用いてサブブロック演算を行う。

暗号化処理の最終サイクルになると(T26)、制御部104は選択信号170をAssertする。それを受け、ラウンド処理部105のセレクタ115は、実行鍵B(163)を用いてAddRoundKey演算を行うAddRoundKey114の出力を選択し、最終サイクルのサブブロック演算を行う。T26において、ラウンド処理部105の出力信号166は入力信号である平文データP0を暗号化した結果である暗号文データC0を出力しており、その値は1サイクル後(T27)にデータ保持部108よりAES処理回路101の出力として、外部に出力される。同時に、制御部104は暗号化処理が終了し、出力信号151が有効であることをAES処理回路101の外部に対して通知するため、有効出力期間信号159をAssertする(T27)。有効出力期間信号159がAssertされている間、AES処理回路101は出力信号151が有効であることを保証する。

一方、出力保持制御信号160は、T27において有効出力期間信号159がAssertされているものの、同じくT27において暗号化・復号処理開始信号158もまたAssertされているため、Negateされたままである。もしT27において暗号化・復号処理開始信号158がAssertされなかった場合、T27において出力保持制御信号160がAssertされ、データ保持部108の値は暗号文データC0に保持される。

また、鍵拡張部102は暗号化処理が終了するT27において、実行鍵A(162)よりwkey0を出力する。そして、実行鍵A162の値は、次なる暗号化・復号処理開始信号156がAssertされるまで保持される。

さらに、制御部104は暗号化処理の完了(T27)を見越し、完了の1サイクル前(T26)に暗号化・復号処理許可信号157をAssertする。AES処理回路101の外部は、暗号化・復号処理許可信号157がAssertされていると、入力信号150の値を次なる平文データP1とし、2ブロック目の暗号化処理を開始することが可能となる。図9のタイミングチャートでは、AES処理回路101の外部は、最短のサイクルで次なる暗号化・復号処理開始信号をAssertしている(T27)。図9のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。2ブロック目以降の暗号化処理では、1ブロック目と同様の動作が繰り返し行われる。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本実施形態の復号処理の動作について説明する。図10は本実施形態の復号処理時のタイミングチャートについて示したものである。同図において横軸は時間を示しており、クロックの立ち上がりごとにT01、T02、・・・、T33のタイミング名が割り当てられている。また、同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図5〜図8で使用されている信号線のナンバと一対一で対応している。

復号処理時の動作もパラメータ設定期間(T01〜T06)、鍵準備期間(T06〜T17)、1ブロック目の復号処理期間(T17〜T27)、2ブロック目の復号処理期間(T27以降)の4つに大別される。

パラメータ設定期間はT01〜T06までの期間であり、その役割、開始条件、終了条件は本実施形態の暗号化処理時と同様である。ただし、復号処理時は暗号化・復号処理選択信号153はAssertされる。

鍵準備期間はT06〜T17までであり、開始条件および終了条件は本実施形態の暗号化処理時と同様である。各回路の動作も本実施形態の暗号化処理時とほぼ同様である。ただし、暗号化処理と復号処理では最初のサイクルで用いられる実行鍵が異なるため、鍵拡張部102は鍵準備期間の終了時(T17)にwkey10より逆順に鍵拡張を行い、wkey9を生成し、実行鍵A(162)より出力する。実行鍵A(162)の値は、暗号化・復号処理開始信号158がAssertされるまで保持される。そして、制御部104はカウンタ信号161のカウントアップを停止し、カウンタをゼロクリアする。

また、鍵準備期間の終了に合わせ、制御部104はT16において、T17で鍵準備が終了し、復号処理が可能となることを見越し、暗号化・復号処理許可信号157をAssertする。

AES処理回路101の外部にある入力信号供給部は、T17で暗号化・復号処理許可信号157のAssertを検知すると、入力信号150として暗号文データC0をAES処理回路101に供給する。そして、入力信号150に対する復号処理を開始せしめるため、暗号化・復号処理開始信号158をAssertする(T17)。なお、このタイミングチャートでは最短のサイクルで暗号化・復号処理開始信号158がAssertされているが、そのタイミングはAES処理回路101の外部で自由に決められる。

復号処理期間は、入力信号150に対して復号処理を行う期間である。復号処理期間は、暗号化・復号処理開始信号158がAssert(T17)されてから、その10サイクル後(T27)までの期間である。

制御部104は暗号化・復号処理開始信号158のAssertを検知すると、次サイクル(T18)で暗号化・復号処理許可信号157、有効出力期間信号159、出力保持制御信号160をNegateする。同時に、カウンタ信号161のカウントアップを開始する。

鍵拡張部102は、カウンタ信号161にしたがって実行鍵wkey9から逆順に鍵拡張を行い、T18ではwkey9、T19ではwkey8、…、T26ではwkey0を実行鍵A(162)として暗号化・復号処理部103に出力する。

ラウンド処理部106はT17〜T18では選択信号171がNegateされているため、入力信号150に対して実行鍵Aとして出力されているwkey9を用いて各サブブロック演算を行う。制御部104は、復号時には最初のサイクルにおいて選択信号170をAssertする。それを受け、ラウンド処理部106のセレクタ118は、実行鍵B(163)を用いてAddRoundKey演算を行うAddRoundKey117の出力を選択し、最初のサイクルのサブブロック演算を行う。

そして、T18〜T27では選択信号171がAssertされているため、データ保持部108の出力に対して、T18〜T19ではwkey8、T19〜T20ではwkey7、…、T26〜T27ではwkey0を用いてサブブロック演算を行う。

T26において、ラウンド処理部106の出力信号167は入力信号である暗号文データC0を復号した結果である平文データP0を出力しており、その値は1サイクル後(T27)にデータ保持部108よりAES処理回路101の出力として、外部に出力される。同時に、制御部104は復号処理が終了し、出力信号151が有効であることをAES処理回路101の外部に対して通知するため、有効出力期間信号159をAssertする(T27)。有効出力期間信号159がAssertされている間、AES処理回路101は出力信号151が有効であることを保証する。

一方、出力保持制御信号160は、T27において有効出力期間信号159がAssertされているものの、同じくT27において暗号化・復号処理開始信号158もまたAssertされているため、Negateされたままである。もしT27において暗号化・復号処理開始信号158がAssertされなかった場合、T27において出力保持制御信号160がAssertされ、データ保持部108の値は平文データP0に保持される。

また、鍵拡張部102は復号処理が終了するT27において、wkey10よりwkey9を逆算で求め、実行鍵A(162)より出力する。そして、実行鍵A162の値は、次なる暗号化・復号処理開始信号156がAssertされるまで保持される。

さらに、制御部104は復号処理の完了(T27)を見越し、完了の1サイクル前(T26)に暗号化・復号処理許可信号157をAssertする。AES処理回路101の外部は、暗号化・復号処理許可信号157がAssertされていると、入力信号150の値を次なる暗号文データC1とし、2ブロック目の復号処理を開始することが可能となる。図10のタイミングチャートでは、AES処理回路101の外部は、最短のサイクルで次なる暗号化・復号処理開始信号158をAssertしている(T27)。2ブロック目の復号処理の動作は1ブロック目と同様に行われる。以降、任意の回数復号処理の動作が繰り返される。

すべての復号処理が終了し、次なるジョブを開始する際には、再びパラメータ設定から始まる。

第1の実施形態は以上のようにして実施可能である。第1実施形態は、1サイクル内で実行しなければならない処理の処理時間の最大値を増やすことなく、AESの暗号化処理に要するクロックサイクル数を1サイクル削減している。これにより約10%程度の処理速度の向上が得られる。

<第2の実施形態>

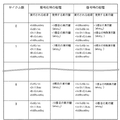

図11は第2の実施形態において各クロックサイクル内で実行される暗号化処理、復号処理の処理内容を示した図である。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本実施形態の暗号化処理は、0サイクル目では、第1のAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算、第2のAddRoundKey演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算を実行する。そして、9サイクル目では、AddRoundKey演算、ShiftRows演算、SubBytes演算を実行する。実行鍵は0サイクル目ではwkey0とwkey1、1サイクル目ではwkey2、…、9サイクル目ではwkey10が用いられる。

本第2の実施形態は従来技術とトータルで実行している処理は同じであるが、本実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第2の実施形態において各クロックサイクル内で実行される処理に必要な処理時間について述べる。図12は、本第2の実施形態において各クロックサイクル内で実行される処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第2の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図12に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本実施形態では、第1のAddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、第2のAddRoundKey演算を行う0サイクル目の処理に必要な処理時間は、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

本発明はAESの復号処理についても同様に適用可能である。

図11に示すように、本実施形態の復号処理は、0サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算を実行する。そして、9サイクル目では、第1のAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey10、1サイクル目ではwkey9、…、8サイクル目ではwkey2が用いられ、9サイクル目では2つの実行鍵wkey1、wkey0が必要となる。

本第2の実施形態は従来技術とトータルで実行している処理は同じであるが、本第2の実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第2の実施形態において各クロックサイクル内で実行される処理に必要な処理時間について述べる。図13は、第2の実施形態において各クロックサイクル内で実行される処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図13に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本第2の実施形態では、第1のAddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算、第2のAddRoundKey演算を行う9サイクル目の処理に必要な処理時間は、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算を行う0サイクル目の処理に必要な処理時間よりも長い。したがって、本第2の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本第2の実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

ここまでで説明してきた本第2の実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本発明では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。

本実施形態は1サイクル内で実行される処理に必要な処理時間の最大値をわずかに増やすため、従来技術が実施可能な条件下で必ずしも本実施形態が実施可能であるとは限らない。しかし、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理および復号処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

図14は、本実施形態のAES処理回路のブロック図を示したものである。

図14において、131はAESの処理を実行するAES処理回路である。132は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。133は鍵拡張部132より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。134はAES処理回路131の外部からの制御信号を受け、鍵拡張部132および暗号化・復号処理部133の動作を制御するための信号を生成し、かつAES処理回路131の外部に対して動作完了を通知するための信号を生成する制御部である。

同図において、175は制御部134より暗号化・復号処理部133に対して出力され、暗号化・復号処理部133においてサブブロック演算の接続を切り替えるための選択信号である。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、暗号化・復号処理部133について説明する。図15は暗号化・復号処理部133のブロック図について説明したものである。同図において、135は、選択信号170および選択信号175による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理を行うラウンド処理部である。136は選択信号170および選択信号175による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて復号処理を行うラウンド処理部である。

上記構成において、暗号化・復号処理部133のセレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略した。

次に、ラウンド処理部135について説明する。図16はラウンド処理部135のブロック図を示したものである。同図において、114は入力信号165および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。137は選択信号175に応じて入力信号165とAddRoundKey演算部114の出力のいずれか一方を選択し出力するセレクタである。111はセレクタ137の出力を入力としSubBytes演算を行うところのSubBytes演算部である。112はSubBytes演算部111の出力を入力としShiftRows演算を行うところのShiftRows演算部である。113はShiftRows演算部112の出力を入力とし、MixColumns演算を行うところのMixColumns演算部である。115は選択信号170に応じてMixColumns演算部113の出力とShiftRows演算部112の出力のいずれか一方を選択し出力するセレクタである。110はセレクタ115の出力および実行鍵A(162)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。AddRoundKey演算部110の出力信号はラウンド処理部135の出力となる。

上記構成において、セレクタ115は選択信号170がNegateされている時はMixColumns演算部113の出力、Assertされている時はShiftRows演算部112の出力を選択し、出力する。セレクタ137は選択信号175がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。

次に、ラウンド処理部136について説明する。図17はラウンド処理部136のブロック図について示したものである。同図において、121は入力信号165および実行鍵A(162)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。116はAddRoundKey演算部121の出力を入力としInvMixColumns演算を行うところのInvMixColumns演算部である。118は選択信号170に応じて、InvMixColumns演算部116の出力かAddRoundKey演算部121の出力のいずれか一方を選択し、出力するセレクタである。119はセレクタ118の出力を入力としInvShiftRows演算を行うところのInvShiftRows演算部である。120はInvShiftRows演算部119の出力を入力としInvSubBytes演算を行うところのInvSubBytes演算部である。117はInvSubBytes演算部120の出力および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。138は選択信号175に応じて、InvSubBytes演算部120の出力かAddRoundKey演算部117の出力のいずれか一方を選択し、出力するセレクタである。セレクタ138の出力はラウンド処理部136の出力となる。

上記構成において、セレクタ118は選択信号170がNegateされている時InvMixColumns演算部116の出力、Assertされている時はAddRoundKey演算部121の出力を選択し出力する。セレクタ138は選択信号175がNegateされている時はInvSubBytes演算部120の出力、Assertされている時はAddRoundKey演算部117の出力を選択し出力する。

次に、上記構成における暗号化処理時の動作について説明する。図18は本第2の実施形態の暗号化処理時のタイミングチャートを示したものである。図18において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33とタイミング名が割り当てられている。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図14〜図17で使用されている信号線のナンバと一対一で対応している。

図18のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)、そして。4つ目は、2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態と同様である。また、鍵準備期間はT06〜T17までであり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。ただし、タイミングT16における鍵拡張部132の動作、およびT17における鍵拡張部132と制御部134の動作には、第1の実施形態とは異なる点があるので、それについて述べる。

タイミングT16において、鍵拡張部132は実行鍵B(163)よりwkey0を出力する。ただし、wkey10は鍵拡張部132の内部に設けられたレジスタに保持されている。

タイミングT17において、鍵拡張部132は実行鍵A(162)よりwkey1を出力する。また、制御部134は選択信号175をAssertする。

1ブロック目の暗号化処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部134は選択信号175を暗号化処理の終了時にAssertし、暗号化処理の1サイクル目(T18,T28)にNegateする。そして、選択信号170を暗号化処理の最終サイクル(T16)でAssertし、暗号化処理の終了時(T17)にNegateする。さらに、選択信号171を暗号化処理の1サイクル目にAssertし、暗号化処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時はMixColumns演算部113の出力、Assertされている時はShiftRows演算部112の出力を選択し出力する。また、セレクタ137は選択信号175がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。

したがって、ラウンド処理部135は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行う。1サイクル目からは1サイクル時間前の結果に対して、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行った結果を出力する。そして、9サイクル目(T26〜T27)ではSubBytes演算、ShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部135は図11記載の通りに暗号化処理を実行可能である。

一方、鍵拡張部132は、鍵準備期間の後、実行鍵A(162)からはwkey1、実行鍵B(163)からはwkey0を出力している。したがって、暗号化処理の開始時(T17)において、ラウンド処理部135に対してwkey0およびwkey1が供給されている。鍵拡張部132は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey1を用いてwkey2を生成し、実行鍵Aレジスタに保持する。これによりT18において、ラウンド処理部135にはwkey2が供給される。以下、T26まで同様にして実行鍵が供給されていく。T26においてwkey10を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部132は次なる暗号化処理の開始に備え、共通鍵152として外部より供給されつづけているwkey0を用いてwkey1を生成し、実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部132が動作すると、ラウンド処理部135は各サイクルにおいて図11記載の通りに実行鍵を使用することができる。

本第2の実施形態の暗号化処理期間の動作は以上のようにして行われる。図18のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本実施形態の復号処理の動作について説明する。図19は本実施形態の復号処理時のタイミングチャートについて示したものである。図19において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、…、T33とタイミング名が割り当てられている。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図14〜図17で使用されている信号線のナンバと一対一で対応している。

図19のタイミングチャートに示される復号処理時の動作も4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目、1ブロック目の復号処理期間(T17〜T27)、そして、4つ目は、2ブロック目の復号処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態と同様である。また、鍵準備期間はT06〜T17までであり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。ただし、タイミングT16における鍵拡張部132の動作、およびタイミングT17における鍵拡張部132と制御部134の動作には、第1の実施形態とは異なる点があるので、それについて述べる。

タイミングT16において、鍵拡張部132は実行鍵B(163)よりwkey0を出力する。ただし、wkey10は鍵拡張部132の内部に設けられたレジスタに保持されている。

タイミングT17において、鍵拡張部132は実行鍵A(162)よりwkey10を出力する。また、制御部134は選択信号170をAssertする。

1ブロック目の復号処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部134は選択信号170を復号処理の終了時にAssertし、復号処理の1サイクル目(T18,T28)にNegateする。そして、選択信号175を復号処理の最終サイクル(T16)でAssertし、復号処理の終了時(T17)にNegateする。さらに、選択信号171を復号処理の1サイクル目にAssertし、復号処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ118は選択信号170がNegateされている時はInvMixColumns演算部116の出力、Assertされている時はAddRoundKey演算部121の出力を選択し出力する。また、セレクタ138は選択信号175がNegateされている時はInvSubBytes演算部120の出力、Assertされている時はAddRoundKey演算部117の出力を選択し出力する。

したがって、ラウンド処理部136は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、InvShiftRows演算、InvSubBytes演算を行う。1サイクル目からは1サイクル前の結果に対して、AddRoundKey演算、InvMixColumns演算、InvShiftRows演算、InvSubBytes演算を行った結果を出力する。そして、9サイクル目(T26〜T27)ではAddRoundKey演算、InvMixColumns演算、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部136は図11記載の通りに復号処理を実行可能である。

一方、鍵拡張部132は、鍵準備期間の後、実行鍵A(162)からはwkey10、実行鍵B(163)からはwkey0を出力している。したがって、復号処理の開始時(T17)において、ラウンド処理部136に対してwkey10が供給されている。鍵拡張部132は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey10を用いてwkey9を生成し、実行鍵Aレジスタに保持する。これによりT18において、ラウンド処理部136にはwkey9が供給される。以下、T26まで同様にして実行鍵が供給されていく。T26においてwkey1を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部132は次なる復号処理の開始に備え、鍵拡張部の内部レジスタに保持されているwkey10を実行鍵Aレジスタにロードする(T27)。

上記のように鍵拡張部132が動作すると、ラウンド処理部136は各サイクルにおいて図11記載の通りに実行鍵を使用することができる。

本第2の実施形態の復号処理期間の動作は以上のようにして行われる。図19のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

第2の実施形態は以上のようにして実施可能である。本第2の実施形態は1サイクル内で実行しなければならない処理の処理時間の最大値をわずかに増やすものの、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

以上の第2の実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態に限ったことではない。

<第3の実施形態>

図20は第3の実施形態において各クロックサイクル内で実行される暗号化処理、復号処理の処理内容を示した図である。同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本第3の実施形態の暗号化処理は、0サイクル目では、AddRoundKey演算、ShiftRows演算、SubBytes演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算を実行する。そして、9サイクル目では、MixColumns演算、第1のAddRoundKey演算、SubBytes演算、ShiftRows演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey0、1サイクル目ではwkey1、…、8サイクル目ではwkey8、9サイクル目では2つの実行鍵とwkey9およびwkey10が用いられる。

本第3の実施形態がトータルで実行している処理は従来例と同じであるが、本第3の実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第3の実施形態において各クロックサイクル内で実行される処理に必要な処理時間について述べる。図21は、第3の実施形態において各クロックサイクル内に実行される暗号化処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第3の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図21に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本第3の実施形態では、第1のAddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、および第2のAddRoundKey演算を行う9サイクル目の処理に必要な処理時間は、AddRoundKey演算、SubBytes演算、ShiftRows演算、およびMixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う0サイクル目の処理に必要な処理時間よりも長い。したがって、本第3の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

本発明はAESの復号処理についても同様に適用可能である。

図20に示すように、本第3の実施形態の復号処理は、0サイクル目では、第1のAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算、および第2のAddRoundKey演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、およびInvMixColumns演算を実行する。そして、9サイクル目ではAddRoundKey演算、InvShiftRows演算、およびInvSubBytes演算を実行する。実行鍵は0サイクル目ではwkey10およびwkey9、1サイクル目ではwkey8、…、9サイクル目ではwkey0が用いられる。

本第3の実施形態がトータルで実行している処理は従来と同じであるが、本実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第3の実施形態において各クロックサイクル内に実行される復号処理に必要な処理時間について述べる。図22は、第3の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間を比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図22に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本第3の実施形態では、第1のAddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算、第2のAddRoundKey演算を行う0サイクル目の処理に必要な処理時間は、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本第3の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

ここまでで説明してきた本第3の実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本第3の実施形態では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。

本第3の実施形態は1サイクル内で実行される処理に必要な処理時間の最大値をわずかに増やすため、従来技術が実施可能な条件下で必ずしも本実施形態が実施可能であるとは限らない。しかし、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理および復号処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。図23は、本実施形態のAES処理回路のブロック図を示したものである。図23において、141はAESの処理を実行するAES処理回路である。142は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。143は鍵拡張部142より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。144はAES処理回路141の外部からの制御信号を受け、鍵拡張部142および暗号化・復号処理部143の動作を制御するための信号を生成し、かつAES処理回路141の外部に対して動作完了を通知するための信号を生成する制御部である。

なお、同図において第1の実施形態および第2の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、暗号化・復号処理部143について説明する。図24は暗号化・復号処理部143のブロック図について示したものである。同図において、145は、選択信号170および選択信号175による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理を行うラウンド処理部である。146は選択信号170および選択信号175による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて復号処理を行うラウンド処理部である。

上記構成において、暗号化・復号処理部143のセレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、ラウンド処理部145について説明する。図25はラウンド処理部145のブロック図について示したものである。同図において、113は入力信号165を入力とし、MixColumns演算を行うところのMixColumns演算部である。137は選択信号175に応じて入力信号165とMixColumns演算部113の出力のいずれか一方を選択し出力するセレクタである。110はセレクタ137の出力および実行鍵A(162)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。111はAddRondKey演算部110の出力を入力としSubBytes演算を行うところのSubBytes演算部である。112はSubBytes演算部111の出力を入力としShiftRows演算を行うところのShiftRows演算部である。114はShiftRows演算部112の出力および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。115は選択信号170に応じてShiftRows演算部112の出力とAddRoundKey演算部114の出力のいずれか一方を選択し出力するセレクタである。セレクタ115の出力信号はラウンド処理部145の出力となる。

上記構成において、セレクタ115は選択信号170がNegateされている時はShiftRows演算部112の出力、Assertされている時はAddRoundKey演算部114の出力を選択し、出力する。セレクタ137は選択信号175がNegateされている時はMixColumns演算部113の出力、Assertされている時は入力信号165を選択し出力する。

次に、ラウンド処理部146について説明する。図26はラウンド処理部146のブロック図について示したものである。同図において、121は入力信号165および実行鍵A(162)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。118は選択信号170に応じて入力信号165とAddRoundKey演算部121の出力のいずれか一方を選択し出力するセレクタである。119はセレクタ118の出力を入力としInvShiftRows演算を行うところのInvShiftRows演算部である。120はInvShiftRows演算部119の出力を入力としInvSubBytes演算を行うところのInvSubBytes演算部である。117はInvSubBytes演算部120および実行鍵B(163)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。116はAddRoundKey演算部117の出力を入力としInvMixColumns演算を行うところのInvMixColumns演算部である。138は選択信号175に応じて、InvMixColumns演算部116の出力かAddRoundKey演算部117の出力のいずれか一方を選択し、出力するセレクタである。セレクタ138の出力はラウンド処理部146の出力となる。

上記構成において、セレクタ118は選択信号170がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部121の出力を選択し出力する。セレクタ138は選択信号175がNegateされている時はInvMixColumns演算部116、Assertされている時はAddRoundKey演算部117の出力を選択し出力する。

次に、上記構成における暗号化処理時の動作について説明する。図27は本実施形態における暗号化処理時のタイミングチャートについて示したものである。図27において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、…、T33とタイミング名が割り当てられている。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図23〜図26で使用されている信号線のナンバと一対一で対応している。

図27のタイミングチャートに示される暗号化処理時の動作は、4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)、そして4つ目は、2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態と同様である。また、鍵準備期間はT06〜T17までであり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。ただし、制御部144は鍵準備期間が終了時(T17)に選択信号175をAssertする。

1ブロック目の暗号化処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部144は選択信号175を暗号化処理の終了時にAssertし、暗号化処理の1サイクル目(T18,T28)にNegateする。そして、選択信号170を暗号化処理の最終サイクル(T16)でAssertし、暗号化処理の終了時(T17)にNegateする。さらに、選択信号171を暗号化処理の1サイクル目にAssertし、暗号化処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時はShiftRows演算部112の出力、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、セレクタ137は選択信号175がNegateされている時はMixColumns演算部113の出力、Assertされている時は入力信号165を選択し出力する。

したがって、ラウンド処理部145は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う。1サイクル目からは1サイクル時間前の結果に対して、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行った結果を出力する。そして、9サイクル目(T26〜T27)ではMixColumns演算、AddRoundKey演算、SubBytes演算、ShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部145は図20記載の通りに暗号化処理を実行可能である。

一方、鍵拡張部142は、鍵準備期間の後、実行鍵A(162)からはwkey0、実行鍵B(163)からはwkey10を出力している。したがって、暗号化処理の開始時(T17)において、ラウンド処理部145に対してwkey0が供給されている。鍵拡張部142は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey0を用いてwkey1を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部145にはwkey1が供給される。以下、T26まで同様にして実行鍵が供給されていく。T26では実行鍵B(163)のwkey10もあわせて供給される。T26においてwkey10を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部142は次なる暗号化処理の開始に備え、共通鍵152として外部より供給されつづけているwkey0を実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部142が動作すると、ラウンド処理部145は各サイクルにおいて図20記載の通りに実行鍵を使用することができる。

本第3の実施形態の暗号化処理期間の動作は以上のようにして行われる。図27のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本実施形態の復号処理の動作について説明する。図28は本実施形態の復号処理時のタイミングチャートについて示したものである。図28において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、…、T33とタイミング名が割り当てられている。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図23〜図26で使用されている信号線のナンバと一対一で対応している。

図28のタイミングチャートに示される復号処理時の動作は、4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の復号処理期間(T17〜T27)、そして、4つ目は2ブロック目の復号処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態と同様である。また、鍵準備期間はT06〜T17までであり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。ただし、鍵準備期間の終了時(T17)に制御部144は選択信号170をAssertする。

1ブロック目の復号処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部144は選択信号170を復号処理の終了時にAssertし、復号処理の1サイクル目(T18,T28)にNegateする。そして、選択信号175を復号処理の最終サイクル(T16)でAssertし、復号処理の終了時(T17)にNegateする。さらに、選択信号171を復号処理の1サイクル目にAssertし、復号処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ118は選択信号170がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部121の出力を選択し出力する。また、セレクタ138は選択信号175がNegateされている時はInvMixColumns演算部116の出力、Assertされている時はAddRoundKey演算部117の出力を選択し出力する。

したがって、ラウンド処理部146は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算、InvMixColumns演算を行う。1サイクル目からは1サイクル前の結果に対して、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算、InvMixColumns演算を行った結果を出力する。また、9サイクル目(T26〜T27)では、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部146は図20に記載された通りに復号処理を実行可能である。

一方、鍵拡張部142は、鍵準備期間の後、実行鍵A(162)からはwkey9、実行鍵B(163)からはwkey10を出力している。したがって、復号処理の開始時(T17)において、ラウンド処理部146に対してwkey10およびwkey9が供給されている。鍵拡張部142は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey9を用いてwkey8を生成し、実行鍵Aレジスタに保持する。これによりT18において、ラウンド処理部146にはwkey8が供給される。以下、T26まで同様にして実行鍵が供給されていく。T26においてwkey0を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部142は次なる復号処理の開始に備え、実行鍵Bレジスタに保持されているwkey10を用いてwkey9を生成し、実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部142が動作すると、ラウンド処理部146は各サイクルにおいて図20記載の通りに実行鍵を使用することができる。

本実施形態の復号処理期間の動作は以上のようにして行われる。図28のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

本第3の実施形態は以上のようにして実施可能である。本第3の実施形態は1サイクル内で実行しなければならない処理の処理時間の最大値をわずかに増やすものの、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理および復号処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

以上説明したように、本発明の考え方を応用することで、基本となる第1の実施形態以外にも多数の実施形態を得ることができる。第2の実施形態および第3の実施形態はその一例である。他にも、図62のような8サイクル目でAddRoundKeyを2回実行する構成のように、暗号化処理の任意のサイクルでAddRoundKeyを2回実行する構成も考えられる。実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態の記載に限ったことではない。

<第4の実施形態>

本第4の実施形態はFIPS197記載のEquivalent Inverse Cipherを用いて復号処理を行う際の実施例を示すものである。

図29は第4の実施形態において各クロックサイクル内に実行される暗号化処理の処理内容を従来例と比較して示したものである。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本実施形態は、0サイクル目から8サイクル目ではAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算を実行する。そして、9サイクル目では、第1のAddRoundKey演算、ShiftRows演算、SubBytes演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey0、1サイクル目ではwkey1、…、8サイクル目ではwkey8が用いられ、9サイクル目では2つの実行鍵wkey9、wkey10が必要となる。

本第4の実施形態は従来技術とトータルで実行している処理は同じであるが、本第4の実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第4の実施形態において各クロックサイクル内に実行される暗号化処理に必要な処理時間について述べる。図31は、第4の実施形態において各クロックサイクル内に実行される暗号化処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第4の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図31に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本第4の実施形態では、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う0〜8サイクル目の処理に必要な処理時間は、第1のAddRoundKey演算、SubBytes演算、ShiftRows演算、第2のAddRoundKey演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本第4の実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態もまた実施可能である。

本発明はAESの復号処理についても同様に適用可能である。

図30は第4の実施形態において各クロックサイクル内で実行される復号処理の処理内容を従来技術と比較して示した図である。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数を示すものである。また、特殊実行鍵wkeyi’(iはラウンド数を示す)はFIPS197記載のEquivalent Inverse Cipherに必要なとなるRound Keyのことを指すものとする。

本第4の実施形態は、0サイクル目から8サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算を実行する。そして、9サイクル目では第1のAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey10、1サイクル目ではwkey9’、…、8サイクル目ではwkey2’が用いられ、9サイクル目では2つの実行鍵wkey1’、wkey0が必要となる。

本第4の実施形態は従来技術とトータルで実行している処理は同じであるが、本第4の実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第4の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間について述べる。図31は、第4の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図31に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本第4の実施形態では、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う0〜8サイクル目の処理に必要な処理時間は、第1のAddRoundKey演算、InvSubBytes演算、InvShiftRows演算、第2のAddRoundKey演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態もまた実施可能である。

ここまでで説明してきた本第4の実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本第4の実施形態では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。本発明は1サイクル内に実行される処理に必要な処理時間を増やすことなく、AESの暗号化処理、復号処理に要するクロックサイクル数を1サイクル削減しており、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

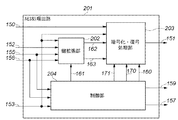

図32は、本第4の実施形態のAES処理回路のブロック図を示したものである。

図32において、201はAESの処理を実行するAES処理回路である。202は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。203は鍵拡張部202より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。204はAES処理回路201の外部からの制御信号を受け、鍵拡張部202および暗号化・復号処理部203の動作を制御するための信号を生成し、かつAES処理回路201の外部に対して動作完了を通知するための信号を生成する制御部である。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、暗号化・復号処理部203について説明する。図33は暗号化・復号処理部203のブロック図を示したものである。同図において、205は選択信号170、暗号化・復号処理選択信号153および選択信号175による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理もしくは復号処理を行うラウンド処理部である。

上記構成において、セレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、ラウンド処理部205について説明する。図34はラウンド処理部205のブロック図を示したものである。同図において、110は入力信号165および実行鍵A(162)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。222はAddRoundKey演算部110の出力を入力とし暗号化・復号処理選択信号153に応じてSubBytes演算とInvSubBytes演算のいずれかを行うところのSubBytes/InvSubBytes演算部である。223はSubBytes/InvSubBytes演算部222の出力を入力とし暗号化・復号処理選択信号153に応じてShiftRows演算とInvShiftRows演算の一方を行うところのShiftRows/InvShiftRows演算部である。224はShiftRows/InvShiftRows演算部223の出力を入力とし暗号化・復号処理選択信号153に応じてMixColumns演算とInvMixColumns演算の一方を行うところのMixColumns/InvMixColumns演算部である。114はShiftRows/InvShiftRows演算部223の出力を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。115は選択信号170に応じてMixColumns/InvMixColumns演算部224の出力とAddRoundKey演算部114の出力のいずれか一方を選択し出力するセレクタである。セレクタ115の出力信号はラウンド処理部205の出力となる。

上記構成において、セレクタ115は選択信号170がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、SubBytes/InvSubBytes演算部222、ShiftRows/InvShiftRows演算部223、およびMixColumns/InvMixColumns演算部224は、暗号化・復号処理選択信号153がNegateされている時はそれぞれSubBytes演算、ShiftRows演算部、MixColumns演算を行い、暗号化・復号処理選択信号153がAssertされている時はそれぞれInvSubBytes演算、InvShiftRows演算部、InvMixColumns演算を行う。

次に、上記構成における暗号化処理時の動作を図9のタイミングチャートに従って説明する。図9において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33とタイミング名が割り当てられている。

同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図32〜図34で使用されている信号線のナンバと一対一で対応している。

図9のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)、そして、4つ目は2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態と同様である。また、鍵準備期間はT06〜T17までである。鍵準備期間の開始条件、終了条件、各回路の動作は第1の実施形態の説明とまったく同様であるため、ここでは省略する。

1ブロック目の暗号化処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部204は選択信号170を暗号化処理の最終サイクル(T16)でAssertし、暗号化処理の終了時(T17)にNegateする。さらに、選択信号171を暗号化処理の1サイクル目にAssertし、暗号化処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、SubBytes/InvSubBytes演算部222、ShiftRows/InvShiftRows演算部223、およびMixColumns/InvMixColumns演算部224は、暗号化・復号処理選択信号153がNegateされている時はそれぞれSubBytes演算、ShiftRows演算部、MixColumns演算を行い、暗号化・復号処理選択信号153がAssertされている時はそれぞれInvSubBytes演算、InvShiftRows演算部、InvMixColumns演算を行う。

したがって、ラウンド処理部205は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う。1サイクル目からは1サイクル時間前の結果に対してAddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行った結果を出力する。そして、9サイクル目(T26〜T27)では、AddRoundKey演算、SubBytes演算、ShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170を先述のようにコントロールすることでラウンド処理部205は図29記載の通りに暗号化処理を実行可能である。

一方、鍵拡張部202は、鍵準備期間の後、実行鍵A(162)からはwkey0、実行鍵B(163)からはwkey10を出力している。したがって、暗号化処理の開始時(T17)において、ラウンド処理部205に対してwkey0が供給されている。鍵拡張部202は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey0を用いてwkey1を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部205にはwkey1が供給される。以下、タイミングT26まで同様にして実行鍵が供給されていく。T26では実行鍵B(163)もあわせ2つの実行鍵wkey9とwkey10が供給される。T26においてwkey9を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部202は次なる暗号化処理の開始に備え、共通鍵152として外部より供給されつづけているwkey0を実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部202が動作すると、ラウンド処理部205は各サイクルにおいて図29記載の通りに実行鍵を使用することができる。

本第4の実施形態の暗号化処理期間の動作は以上のようにして行われる。図9のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本実施形態の復号処理の動作について説明する。図35は本第4の実施形態の復号処理時のタイミングチャートを示したものである。図35において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33とタイミング名が割り当てられている。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図32〜図34で使用されている信号線のナンバと一対一で対応している。

図35のタイミングチャートに示される復号処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の復号処理期間(T17〜T27)、そして、4つ目は2ブロック目の復号処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第1の実施形態の暗号化処理時と同様である。

鍵準備期間はT06〜T17までであり、開始条件および終了条件は本第1の実施形態の暗号化処理時と同様である。各回路の動作も本実施形態の暗号化処理時とほぼ同様である。ただし、タイミングT16における鍵拡張部202の動作、およびタイミングT17における鍵拡張部202と制御部204の動作に、暗号化時とは異なる点があるので、それについて述べる。

タイミングT16において、鍵拡張部202は実行鍵B(163)よりwkey0を出力し、実行鍵A(162)よりwkey10を出力する。ただし、wkey10は鍵拡張部202の内部に設けられたレジスタにも別途保持されている。そして、鍵拡張部202はT16においてwkey10から逆順に鍵拡張を行い、特殊実行鍵をwkey9’を生成する。

タイミングT17において、鍵拡張部202は実行鍵A(162)よりwkey9’を出力する。また、制御部204は選択信号170をAssertする。

1ブロック目の復号処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部204は選択信号170を復号処理の最終サイクル(T16)でAssertし、復号処理の終了時(T17)にNegateする。そして、選択信号171を復号処理の1サイクル目にAssertし、復号処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、SubBytes/InvSubBytes演算部222、ShiftRows/InvShiftRows演算部223、およびMixColumns/InvMixColumns演算部224は、暗号化・復号処理選択信号153がNegateされている時はそれぞれSubBytes演算、ShiftRows演算部、MixColumns演算を行い、暗号化・復号処理選択信号153がAssertされている時はそれぞれInvSubBytes演算、InvShiftRows演算部、InvMixColumns演算を行う。

したがって、ラウンド処理部205は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う。1サイクル目からは1サイクル時間前の結果に対してAddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行った結果を出力する。また、9サイクル目(T26〜T27)では、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170を先述のようにコントロールすることでラウンド処理部205は図30に示した通りに復号処理を実行可能である。

一方、鍵拡張部202は、鍵準備期間の後、実行鍵A(162)からはwkey10、実行鍵B(163)からはwkey0を出力している。したがって、復号処理の開始時(T17)において、ラウンド処理部205に対してwkey10が供給されている。鍵拡張部202は、暗号化・復号処理開始信号158より復号処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey10を用いてwkey9’を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部205にはwkey9’が供給される。以下、タイミングT26まで同様にして実行鍵が供給されていく。タイミングT26では実行鍵B(163)もあわせ2つの実行鍵wkey1’とwkey0が供給される。タイミングT26においてwkey1’を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部202は次なる復号処理の開始に備え、鍵拡張部の内部レジスタに保持されているwkey10を実行鍵Aレジスタにロードする(T27)。

上記のように鍵拡張部202が動作すると、ラウンド処理部205は各サイクルにおいて図30に示した通りに実行鍵を使用することができる。

本第4の実施形態の復号処理期間の動作は以上のようにして行われる。図35のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

本第4の実施形態は以上のようにして実施可能である。本第4の実施形態は、Equivalent Inverse Cipherを用いて復号を行う際の回路構成およびその動作について示したものである。本第4の実施形態は1サイクル内で実行しなければならない処理の処理時間の最大値を増やすことなくAESの暗号化処理に要するクロックサイクル数を1サイクル削減することができる。これにより約10%程度の処理速度の向上が得られる。

以上説明した第4の実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態に限ったことではない。

<第5の実施形態>

本第5の実施形態はFIPS197記載のEquivalent Inverse Cipherを用いて復号処理を行う例を示す。

図36は第5の実施形態において各クロックサイクル内で実行される暗号化処理、復号処理の処理内容を示した図である。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本第5の実施形態の暗号化処理は、0サイクル目では2つの実行鍵を用いて、第1のAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算、第2のAddRoundKey演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、ShiftRows演算、SubBytes演算、MixColumns演算を実行する。そして、9サイクル目では、AddRoundKey演算、ShiftRows演算、SubBytes演算を実行する。実行鍵は0サイクル目ではwkey0とwkey1、1サイクル目ではwkey2、…、9サイクル目ではwkey10が用いられる。

本第5の実施形態がトータルで実行している処理は従来と同じであるが、本実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第5の実施形態において各クロックサイクル内で実行される暗号化処理に必要な処理時間について述べる。図37は、第5の実施形態において各クロックサイクル内で実行される処理に必要な処理時間を比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第5の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図37に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本第5の実施形態では、第1のAddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、第2のAddRoundKey演算を行う0サイクル目の処理必要な処理時間は、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本第5の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

本発明はAESの復号処理についても同様に適用可能である。

図36に示すように、本実施形態の復号処理は、0サイクル目では第1のAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算、第2のAddRoundKey演算を実行する。そして、1サイクル目から8サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算、InvMixColumns演算を実行する。そして、9サイクル目ではAddRoundKey演算、InvShiftRows演算、InvSubBytes演算を実行する。実行鍵は0サイクル目ではwkey10およびwkey9’、1サイクル目ではwkey8’、…、9サイクル目ではwkey0が用いられる。

本第5の実施形態がトータルで実行している処理は従来の実施例と同じであるが、本第5の実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第5の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間について述べる。図37は、第5の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間を従来技術のものと比較した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図37に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本第5の実施形態では、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算、AddRoundKey演算を行う0サイクル目の処理に必要な処理時間は、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算、InvMixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、InvSubBytes演算、InvShiftRows演算を行う9サイクル目の処理に必要な処理時間よりも長い。したがって、本第5の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

ここまでで説明してきた本第5の実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本第5の実施形態では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。

本第5の実施形態は1サイクル内で実行される処理に必要な処理時間の最大値をわずかに増やすため、従来技術が実施可能な条件下で必ずしも本実施形態が実施可能であるとは限らない。しかし、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理および復号処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

図38は本第5の実施形態のAES処理回路のブロック図を示したものである。図38において、231はAESの処理を実行するAES処理回路である。232は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。233は鍵拡張部232より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。234はAES処理回路231の外部からの制御信号を受け、鍵拡張部232および暗号化・復号処理部233の動作を制御するための信号を生成し、かつAES処理回路231の外部に対して動作完了を通知するための信号を生成する制御部である。

なお、同図において第1の実施形態および第2の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略する。

次に、暗号化・復号処理部233について説明する。図39は暗号化・復号処理部233のブロック図について示したものである。同図において、235は選択信号170、選択信号175および暗号化・復号処理選択信号153による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理もしくは復号処理を行うラウンド処理部である。

上記構成において、暗号化・復号処理部233のセレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。

なお、同図において第1の実施形態および第2の実施形態で説明した構成要素および信号線と同一のものに関しては、同じであるものとし、その説明を省略する。

次に、ラウンド処理部235について説明する。図40はラウンド処理部235のブロック図について示したものである。同図において、114は入力信号165および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。137は選択信号175に応じて入力信号165とAddRoundKey演算部114の出力のいずれか一方を選択し出力するセレクタである。222はセレクタ137の出力を入力とし暗号化・復号処理選択信号153に応じてSubBytes演算とInvSubBytes演算のいずれかを行うところのSubBytes/InvSubBytes演算部である。223はSubBytes/InvSubBytes演算部222の出力を入力とし暗号化・復号処理選択信号153に応じてShiftRows演算とInvShiftRows演算の一方を行うところのShiftRows/InvShiftRows演算部である。224はShiftRows/InvShiftRows演算部223の出力を入力とし暗号化・復号処理選択信号153に応じてMixColumns演算とInvMixColumns演算の一方を行うところのMixColumns/InvMixColumns演算部である。115は選択信号170に応じてMixColumns/InvMixColumns演算部224の出力とShiftRows/InvShiftRows演算部223の出力のいずれか一方を選択し出力するセレクタである。110はセレクタ115の出力および実行鍵A(162)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。AddRoundKey演算部110の出力信号はラウンド処理部235の出力となる。

上記構成において、セレクタ115は選択信号170がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はShiftRows/InvShiftRows演算部223の出力を選択し出力する。セレクタ137は選択信号175がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。

次に、上記構成における暗号化処理時の動作を図18のタイミングチャートに従って説明する。同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図38〜図40で使用されている信号線のナンバと一対一で対応している。

図18のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)であり、4つ目は、2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第2の実施形態と同様である。また、鍵準備期間はT06〜T17までの期間である、開始条件、終了条件および各回路の動作も第2の実施形態と同様であるため説明を省略する。1ブロック目の暗号化処理期間はT17からT27までの期間であり、開始条件および終了条件は第2の実施形態と同様である。各回路の動作も第2の実施形態のものと同様である。

制御部234は選択信号175を暗号化処理の終了時にAssertし、暗号化処理の1サイクル目(T18,T28)にNegateする。そして、選択信号170を暗号化処理の最終サイクル(T16)でAssertし、暗号化処理の終了時(T17)にNegateする。さらに、選択信号171を暗号化処理の1サイクル目にAssertし、暗号化処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、セレクタ137は選択信号175がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はShiftRows/InvShiftRows演算部223の出力を選択し出力する。また、SubBytes/InvSubBytes演算部222、ShiftRows/InvShiftRows演算部223、およびMixColumns/InvMixColumns演算部224は、暗号化・復号処理選択信号153がNegateされている時はそれぞれSubBytes演算、ShiftRows演算部、MixColumns演算を行い、暗号化・復号処理選択信号153がAssertされている時はそれぞれInvSubBytes演算、InvShiftRows演算部、InvMixColumns演算を行う。

したがって、ラウンド処理部235は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行う。1サイクル目からは1サイクル時間前の結果に対して、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行った結果を出力する。そして、9サイクル目(T26〜T27)ではSubBytes演算、ShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部235は図36記載の通りに暗号化処理を実行可能である。

一方、鍵拡張部232は、鍵準備期間の後、実行鍵A(162)からはwkey1、実行鍵B(163)からはwkey0を出力している。したがって、暗号化処理の開始時(T17)において、ラウンド処理部235に対してwkey0およびwkey1が供給されている。鍵拡張部232は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey1を用いてwkey2を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部235にはwkey2が供給される。以下、タイミングT26まで同様にして実行鍵が供給されていく。タイミングT26においてwkey10を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部232は次なる暗号化処理の開始に備え、共通鍵152として外部より供給されつづけているwkey0を用いてwkey1を生成し、実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部232が動作すると、ラウンド処理部235は各サイクルにおいて図36に示した通りに実行鍵を使用することができる。

本第5の実施形態の暗号化処理期間の動作は以上のようにして行われる。図18のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本第5の実施形態の復号処理の動作について述べる。図41は本第5の実施形態の復号処理のタイミングチャートを示したものである。図41において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33とタイミング名が割り当てられている。

同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図38〜図40で使用されている信号線のナンバと一対一で対応している。

図41のタイミングチャートに示される復号処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の復号処理期間(T17〜T27)、そして、4つ目は2ブロック目の復号処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は本実施形態の暗号化処理時と同様である。ただし、復号処理時は暗号化・復号処理選択信号153はAssertされる。

鍵準備期間はT06〜T17までであり、開始条件および終了条件は本実施形態の暗号化処理時と同様である。各回路の動作も本実施形態の暗号化処理時とほぼ同様である。ただし、タイミングT16における鍵拡張部232の動作、およびタイミングT17における鍵拡張部232と制御部234の動作に、暗号化時とは異なる点があるので、それについて述べる。

タイミングT16において、鍵拡張部232は実行鍵B(163)よりwkey10を出力し、実行鍵A(162)からはwkey10を出力する。鍵拡張部232はタイミングT16においてwkey10から逆順に鍵拡張を行い、特殊実行鍵wkey9’を生成する。

タイミングT17において、鍵拡張部232は実行鍵A(162)よりwkey9’を出力する。また、制御部234は選択信号175をAssertする。

鍵準備期間の終了時(T17)に制御部234は選択信号175をAssertする。

1ブロック目の復号処理期間はT17からT27までの期間であり、開始条件および終了条件は第1の実施形態と同様である。各回路の動作も第1の実施形態のものとほぼ同様である。

制御部234は選択信号170を復号処理の最終サイクル(T26)にAssertし、復号処理の1サイクル目(T18,T28)にNegateする。そして、選択信号175を復号処理の終了時(T17)でAssertし、復号処理の終了時(T17)にNegateする。さらに、選択信号171を復号処理の1サイクル目にAssertし、復号処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ137は選択信号175がNegateされている時は入力信号165、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、セレクタ115は選択信号170がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時はShiftRows/InvShiftRows演算部223の出力を選択し出力する。

したがって、ラウンド処理部235は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算、InvMixColumns演算を行う。1サイクル目からは1サイクル前の結果に対して、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算、InvMixColumns演算を行った結果を出力する。また、9サイクル目(T26〜T27)ではInvShiftRows演算、InvSubBytes演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部235は図36に示した通りに復号処理を実行可能である。

一方、鍵拡張部232は、鍵準備期間の後、実行鍵A(162)からはwkey9’、実行鍵B(163)からはwkey10を出力している。したがって、復号処理の開始時(T17)において、ラウンド処理部235に対してwkey10およびwkey9’が供給されている。鍵拡張部235は、暗号化・復号処理開始信号158より復号処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey9’を用いてwkey8’を生成し、実行鍵Aレジスタに保持する。これによりT18において、ラウンド処理部235にはwkey8’が供給される。以下、タイミングT26まで同様にして実行鍵が供給されていく。タイミングT26においてwkey0を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部232は次なる復号処理の開始に備え、実行鍵Bレジスタに保持されているwkey10を用いてwkey9’を生成し、実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部232が動作すると、ラウンド処理部235は各サイクルにおいて図36に示した通りに実行鍵を使用することができる。

本第5の実施形態の復号処理期間の動作は以上のようにして行われる。図41のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

第5の実施形態は以上のようにして実施可能である。本第5の実施形態は1サイクル内で実行しなければならない処理の処理時間の最大値をわずかに増やすものの、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

以上説明した第5の実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態に限ったことではない。

<第6の実施形態>

本第6の実施形態はFIPS197記載のEquivalent Inverse Cipherを用いて復号処理を行う例を示す。

図42は第6の実施形態において各クロックサイクル内で実行される暗号化処理、復号処理の処理内容を示した図である。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本第6の実施形態は、0サイクル目では2つの実行鍵を用いて、第1のAddRoundKey演算、SubBytes/InvSubBytes演算、ShiftRows/InvShiftRows演算、MixColumns/InvMixColumns演算、第2のAddRoundKey演算を実行する。そして、1サイクル目から8サイクル目ではSubBytes/InvSubBytes演算、ShiftRows/InvShiftRows演算、MixColumns/InvMixColumns演算、AddRoundKey演算を実行する。そして、9サイクル目ではSubBytes/InvSubBytes演算、ShiftRows/InvShiftRows演算、AddRoundKey演算を実行する。ただし、SubBytes/InvSubBytes演算とは、暗号化時はSubBytes演算、復号時はInvSubBytes演算を実行することを表し、ShiftRows/InvShiftRows演算とは、暗号化時はShiftRows演算、復号時はInvShiftRows演算を実行することを表し、MixColumns/InvMixColumns演算とは、暗号化時はMixColumns演算、復号時はInvMixColumns演算を実行することを表すものとする。

本実施形態の暗号化時に用いられる実行鍵は、0サイクル目はwkey0とwkey1、1サイクル目はwkey2、…、9サイクル目はwkey10である。復号時に用いられる実行鍵は、0サイクル目はwkey10とwkey9’、1サイクル目はwkey8’、…、9サイクル目はwkey0である。

本第6の実施形態がトータルで実行している処理は従来技術と同じであるが、本実施形態ではAESの暗号化処理、復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本実施形態において各クロックサイクル内で実行される暗号化処理に必要な処理時間について述べる。図43は、第6の実施形態において各クロックサイクル内で実行される処理に必要な処理時間を従来技術のものと比較して示した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第6の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図43に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本実施形態では、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行う0サイクル目の処理に必要な処理時間は、AddRoundKey演算、SubBytes演算、ShiftRows演算、MixColumns演算を行う1〜8サイクル目の処理に必要な処理時間や、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う9サイクル目の処理に必要な処理時間よりも長い。図43は復号処理にも対応した図となっており、復号処理に関してもまったく同様のことがいえる。したがって、本第6の実施形態の処理に必要な処理時間の最大値を従来技術のものと比較すると、本第6の実施形態はAddRoundKey演算1回分だけ必要な処理時間が余分にかかる。しかし、AddRoundKey演算1回分の処理時間は、1サイクル内の処理に必要な処理時間全体から見れば非常に小さい。1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、従来技術に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態も多くのケースで実施可能であると想定される。

ここまでで説明してきた本第6の実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、10サイクル目と0サイクル目に実行される処理に必要な処理時間を合わせても、1〜9サイクル目に実行される処理に必要な処理時間に及ばないというように、1サイクル内で実行される処理に必要な処理時間にばらつきがあった。

一方、本第6の実施形態では1サイクル内で実行される処理に必要な処理時間を均等にするよう暗号化処理、復号処理の処理の区切りを変更した。

本第6の実施形態は、1サイクル内で実行される処理に必要な処理時間の最大値をわずかに増やすため、従来技術が実施可能な条件下で必ずしも本第6の実施形態が実施可能であるとは限らない。しかし、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理および復号処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

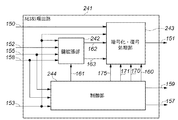

図44は本実施形態のAES処理回路のブロック図を示したものである。図44において、241はAESの処理を実行するAES処理回路である。242は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。243は鍵拡張部242より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。244はAES処理回路241の外部からの制御信号を受け、鍵拡張部242および暗号化・復号処理部243の動作を制御するための信号を生成し、かつAES処理回路241の外部に対して動作完了を通知するための信号を生成する制御部である。

なお、同図において第1の実施形態および第2の実施形態で説明した構成要素および信号線と同一のものに関しては、同じであるものとし、その説明を省略する。

次に、暗号化・復号処理部243について説明する。図45は暗号化・復号処理部243のブロック図を示したものである。同図において、245は選択信号170、選択信号175および暗号化・復号処理選択信号153による制御を受けながら実行鍵A(162)および実行鍵B(163)を用いて1サイクル分の暗号化処理もしくは復号処理を行うラウンド処理部である。

上記構成において、暗号化・復号処理部243のセレクタ109は、選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。

なお、同図において第1実施形態および第2の実施形態で説明した構成要素および信号線と同一のものに関しては、同様であるのでその説明は省略する。

次に、ラウンド処理部245について、図46のブロック図を参照して説明する。同図において、MixColumns/InvMixColumns演算部224には入力信号165および暗号化・復号選択信号153が入力され、セレクタ137にはMixColumns/InvMixColumns演算部224の出力、入力信号165および選択信号175が入力される。AddRoundKey演算部110にはセレクタ137の出力および実行鍵A(162)が入力される。SubBytes/InvSubBytes演算部222にはAddRoundKey演算部110の出力が入力される。ShiftRows/InvShiftRows演算部223にはSubBytes/InvSubBytes演算部222の出力が入力される。AddRoundKey演算部114にはShiftRows/InvShiftRows演算部223の出力および実行鍵B(163)が入力される。セレクタ115にはShiftRows/InvShiftRows演算部223の出力、AddRoundKey演算部114および選択信号170が入力される。セレクタ115の出力はラウンド処理部245の出力信号168に接続されている。なお、同図において、第1の実施形態、第4の実施形態および第5の実施形態で説明した構成要素および信号線と同一のものに関しては説明を省略した。

上記構成において、セレクタ137は選択信号175がNegateされている時はMixColumns/InvMixColumns演算部224の出力を、Assertされている時は入力信号165を選択する。セレクタ115は選択信号170がNegateされている時はShiftRows/InvShiftRows演算部223の出力を、Assertされている時はAddRoundKey演算部114の出力を選択する。

次に、上記構成における暗号化処理時の動作を図27のタイミングチャートを用いて説明する。なお、同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図44〜図46で使用されている信号線のナンバと一対一で対応している。

図27のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の暗号化処理期間(T17〜T27)、そして4つ目は2ブロック目の暗号化処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は第3の実施形態と同様である。また、鍵準備期間はT06〜T17までの期間である、開始条件、終了条件および各回路の動作も第3の実施形態と同様であるためその説明は省略する。

制御部244は選択信号175を暗号化処理の終了時にAssertし、暗号化処理の1サイクル目(T18,T28)にNegateする。そして、選択信号170を暗号化処理の最終サイクル(T16)でAssertし、暗号化処理の終了時(T17)にNegateする。さらに、選択信号171を暗号化処理の1サイクル目にAssertし、暗号化処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ115は選択信号170がNegateされている時はShiftRows/InvShiftRows演算部223の出力、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。また、セレクタ137は選択信号175がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時は入力信号165を選択し出力する。また、SubBytes/InvSubBytes演算部222、ShiftRows/InvShiftRows演算部223、およびMixColumns/InvMixColumns演算部224は、暗号化・復号処理選択信号153がNegateされている時はそれぞれSubBytes演算、ShiftRows演算部、MixColumns演算を行い、暗号化・復号処理選択信号153がAssertされている時はそれぞれInvSubBytes演算、InvShiftRows演算部、InvMixColumns演算を行う。

したがって、ラウンド処理部245は0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、SubBytes演算、ShiftRows演算を行う。1サイクル目からは1サイクル時間前の結果に対して、SubBytes演算、ShiftRows演算、MixColumns演算、AddRoundKey演算を行った結果を出力する。また、9サイクル目(T26〜T27)ではMixColumns演算、AddRoundKey演算、SubBytes演算、ShiftRows演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部245は図42記載の通りに暗号化処理を実行可能である。

一方、鍵拡張部242は、鍵準備期間の後、実行鍵A(162)からはwkey0、実行鍵B(163)からはwkey10を出力している。したがって、暗号化処理の開始時(T17)において、ラウンド処理部245に対してwkey0が供給されている。鍵拡張部242は、暗号化・復号処理開始信号158より暗号化処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey0を用いてwkey1を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部245にはwkey1が供給される。以下、タイミングT26まで同様にして実行鍵が供給されていく。タイミングT26では実行鍵B(163)のwkey10もあわせて供給される。タイミングT26においてwkey10を実行鍵Aレジスタに保持し、実行鍵の供給がすべて完了すると、鍵拡張部242は次なる暗号化処理の開始に備え、共通鍵152として外部より供給されつづけているwkey0を実行鍵Aレジスタに保持する(T27)。

上記のように鍵拡張部242が動作すると、ラウンド処理部245は各サイクルにおいて図42記載の通りに実行鍵を使用することができる。

本実施形態の暗号化処理期間の動作は以上のようにして行われる。図27のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本第6の実施形態の復号処理の動作について述べる。図47は本第6の実施形態の復号処理のタイミングチャートを示したものである。図47において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、・・・、T33のタイミング名を割り当てた。また、同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図44〜図46で使用されている信号線のナンバと一対一で対応している。

図47のタイミングチャートに示される復号処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T17)である。3つ目は、1ブロック目の復号処理期間(T17〜T27)、そして。4つ目は2ブロック目の復号処理期間(T27以降)である。

パラメータ設定期間の役割、開始条件、終了条件は本実施形態の暗号化処理時と同様である。ただし、復号処理時は暗号化・復号処理選択信号153はAssertされる。鍵準備期間はT06〜T17までであり、開始条件および終了条件は本実施形態の暗号化処理時と同様である。各回路の動作も本実施形態の暗号化処理時とほぼ同様である。ただし、タイミングT16において、実行鍵B(163)からはwkey10が出力される。また、鍵準備期間の終了時(T17)に制御部244は選択信号175をAssertする。

1ブロック目の復号処理期間はT17からT27までの期間であり、開始条件および終了条件は本実施形態の暗号化処理時と同様である。各回路の動作もほぼ同様である。

制御部244は選択信号170を復号処理の最終サイクル(T26)にAssertし、復号処理の1サイクル目(T18,T28)にNegateする。そして、選択信号175を復号処理の終了時(T17)にAssertし、復号処理の終了時(T17)にNegateする。さらに、選択信号171を復号処理の1サイクル目にAssertし、復号処理の終了時にNegateする。

回路構成を説明する際に述べたとおり、セレクタ109は選択信号171がNegateされている時は入力信号150、Assertされている時はデータ保持部108の出力を選択する。そして、セレクタ137は選択信号175がNegateされている時はMixColumns/InvMixColumns演算部224の出力、Assertされている時は入力信号165を選択し出力する。また、セレクタ115は選択信号170がNegateされている時はShiftRows/InvShiftRows演算部223、Assertされている時はAddRoundKey演算部114の出力を選択し出力する。

したがって、ラウンド処理部245は、0サイクル目(T17〜T18)では入力信号150に対して、AddRoundKey演算、InvShiftRows演算、InvSubBytes演算を行う。1サイクル目からは1サイクル前の結果に対して、AddRoundKey演算、InvMixColumns演算、InvShiftRows演算、InvSubBytes演算を行った結果を出力する。また、9サイクル目(T26〜T27)ではAddRoundKey演算、InvMixColumns演算、InvShiftRows演算、InvSubBytes演算、AddRoundKey演算を行った結果を出力する。

選択信号171、選択信号170、選択信号175を先述のようにコントロールすることでラウンド処理部245は図42に示した通りに復号処理を実行可能である。

一方、鍵拡張部242は、鍵準備期間の後、実行鍵A(162)からはwkey10、実行鍵B(163)からはwkey0を出力している。したがって、復号処理の開始時(T17)において、ラウンド処理部245に対してwkey10が供給されている。鍵拡張部242は、暗号化・復号処理開始信号158より復号処理の開始を検知すると(T17)、実行鍵Aレジスタに保持されているwkey10’を用いてwkey9’を生成し、実行鍵Aレジスタに保持する。これによりタイミングT18において、ラウンド処理部245にはwkey9’が供給される。以下同様にして、T19ではwkey9’、T20ではwkey8’、…、T26ではwkey1’が供給される。なお、最終サイクルの処理で必要となるwkey0について実行鍵B(163)より供給され続けている。

T26において実行鍵の供給がすべて完了すると、鍵拡張部242は次なる復号処理の開始に備え、次サイクル(T27)にて鍵拡張部242の内部レジスタに保持されているwkey10を用いてwkey9’を生成し、実行鍵Aレジスタに保持する(T27)。

本第6の実施形態の復号処理期間の動作は以上のようにして行われる。図47のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

本第6の実施形態は以上のようにして実施可能である。本第6の実施形態は1サイクル内で実行しなければならない処理の処理時間の最大値をわずかに増やすものの、1サイクル内で実行しなければならない処理の処理時間の最大値は1サイクル時間から余裕をもって設定されていることが多いため、大多数のケースでは問題とはならない。そのため、多くのケースでAESの暗号化処理に要するクロックサイクル数を1サイクル削減することができ、これにより約10%程度の処理速度の向上が得られる。

以上説明した第6の実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態に限ったことではない。

<第7の実施形態>

上記第1乃至第6の実施形態において、各クロックサイクル内で実行される処理の処理時間の最大値が1サイクル時間の半分以下の場合、2クロックサイクルかけて行っていた処理を、1クロックサイクル内で実行するように実装し、高速化することが考えられる。そこで本第7の実施形態では、第1の実施形態を例にして、上記高速化手法の実現例を説明する。

本第7の実施形態における暗号処理回路の暗号化に係る構成は、第1のラウンド処理部と、第2のラウンド処理部と、データ保持部を有する。第1のラウンド処理部は、第1のAddRoundKey演算部、第1のShiftRows演算部、第1のSubBytes演算部、第1のMixColumns演算部、第2のAddRoundKey演算部から構成される。また、第2のラウンド処理部は、第3のAddRoundKey演算部、第2のShiftRows演算部、第2のSubBytes演算部、第2のMixColumns演算部から構成される。

また、第7の実施形態における暗号復号にかかる構成は、第1のラウンド処理部と、第2のラウンド処理部、及び、データ保持部で構成される。ここで、第1のラウンド処理部は、第1のAddRoundKey演算部、第1のInvShiftRows演算部、第1のInvSubBytes演算部、第1のInvMixColumns演算部、第2のAddRoundKey演算部から構成される。また、第2のラウンド処理部は、第3のAddRoundKey演算部、第2のInvShiftRows演算部、第2のInvSubBytes演算部、第2のInvMixColumns演算部から構成される。

上記暗号化、復号における構成は以下の説明から明らかにする。

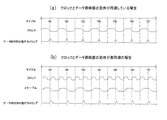

図48は第7の実施形態における各クロックサイクル内で実行される暗号化処理の処理内容を従来技術のものと比較して示したものである。

同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。また、実行鍵wkeyi(iはラウンド数を示す)はFIPS197記載のRound Keyのことである。

本第7の実施形態は、0サイクル目から3サイクル目では第1のAddRoundKey演算、第1のSubBytes演算、第1のShiftRows演算、第1のMixColumns演算、第2のAddRoundKey演算、第2のSubBytes演算、第2のShiftRows演算、第2のMixColumns演算を実行する。そして、4サイクル目では、第1のAddRoundKey演算、第1のSubBytes演算、第1のShiftRows演算、第1のMixColumns演算、第2のAddRoundKey演算、第2のShiftRows演算、第2のSubBytes演算、第3のAddRoundKey演算を実行する。

実行鍵は0サイクル目ではwkey0およびwkey1、1サイクル目ではwkey2およびwkey3、…、4サイクル目ではwkey8、wkey9およびwkey10が用いられる。

本第7の実施形態は従来技術とトータルで実行している処理は同じであるが、本第7の実施形態ではAESの暗号化処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第7の実施形態において各クロックサイクル内で実行される暗号化処理に必要な処理時間について述べる。図49は、第7の実施形態において各クロックサイクル内で実行される暗号化処理に必要な処理時間を従来技術のものと比較して示した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第7の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図49に示すように、各サブブロック演算の処理時間は、SubBytes演算がもっとも長く、次いでMixColumns演算、AddRoundKey演算、ShiftRows演算である。

本第7の実施形態では、第1のAddRoundKey演算、第1のSubBytes演算、第1のShiftRows演算、第1のMixColumns演算、第2のAddRoundKey演算、第2のSubBytes演算、第2のShiftRows演算、第2のMixColumns演算を行う0〜3サイクル目の処理に必要な処理時間は、第1のAddRoundKey演算、第1のSubBytes演算、第1のShiftRows演算、第1のMixColumns演算、第2のAddRoundKey演算、第2のShiftRows演算、第2のSubBytes演算、第3のAddRoundKey演算を行う4サイクル目の処理に必要な処理時間よりも長い。したがって、本第7の実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本第7の実施形態もまた実施可能である。

本発明はAESの復号処理についても同様に適用可能である。

図50は第7の実施形態において各クロックサイクル内で実行される復号処理の処理内容を従来例と比較して示したものである。同図において、サイクル数はAESの処理のスタートを0として、そこから経過したクロックサイクル数のことである。

本第7の実施形態は、0サイクル目では第1のAddRoundKey演算、第1のInvShiftRows演算、第1のInvSubBytes演算、第2のAddRoundKey演算、第1のInvMixColumns演算、第2のInvShiftRows演算、第2のInvSubBytes演算、第3のAddRoundKey演算を行う。そして、1サイクル〜4サイクル目では第1のInvMixColumns演算、第1のInvShiftRows演算、第1のInvSubBytes演算、第1のAddRoundKey演算、第2のInvMixColumns演算、第2のInvShiftRows演算、第2のInvSubBytes演算、第2のAddRoundKey演算を実行する。実行鍵は0サイクル目ではwkey10、wkey9およびwkey8、1サイクル目ではwkey7およびwkey6、2サイクル目ではwkey5およびwkey4、…、4サイクル目ではwkey1およびwkey0が用いられる。

本第7の実施形態は従来技術とトータルで実行している処理は同じであるが、本第7の実施形態ではAESの復号処理を1つ少ないクロックサイクル数で実行することができる。

次に、本第7の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間について述べる。図51は、第7の実施形態において各クロックサイクル内で実行される復号処理に必要な処理時間を従来技術のものと比較して示した図である。縦軸は時間を表しており、棒グラフが長いほど処理時間が長いことを意味する。本第7の実施形態を実現するためには、必要な処理時間の最大値が1サイクル時間を下回っている必要がある。図51に示すように、各サブブロック演算の処理時間は、InvSubBytes演算がもっとも長く、次いでInvMixColumns演算、AddRoundKey演算、InvShiftRows演算である。

本第7の実施形態では、第1のInvMixColumns演算、第1のInvShiftRows演算、第1のInvSubBytes演算、第1のAddRoundKey演算、第2のInvMixColumns演算、第2のInvShiftRows演算、第2のInvSubBytes演算、第2のAddRoundKey演算を行う1〜4サイクル目の処理に必要な処理時間は、第1のAddRoundKey演算、第1のInvShiftRows演算、第1のInvSubBytes演算、第2のAddRoundKey演算、第1のInvMixColumns演算、第2のInvShiftRows演算、第2のInvSubBytes演算、第3のAddRoundKey演算を行う0サイクル目の処理に必要な処理時間よりも長い。したがって、本第7の実施形態において1サイクル内で実行される処理に必要な処理時間の最大値を従来技術のものと比較すると、両者は等しい。従来技術において1サイクル内で実行される処理に必要な処理時間の最大値が1サイクル時間を下回っていれば、本実施形態もまた実施可能である。

ここまでで説明してきた本実施形態の特徴についてまとめる。

従来の一般的な実装方法では、規格にて定義されるラウンド処理を処理の区切りとして、暗号化処理、復号処理を各クロックサイクルごとへ分割していた。そのため、1サイクルあたりの処理に必要な処理時間にばらつきがあった。また、第1の実施形態で示したように処理に要するサイクル数が11と奇数であるため、2サイクル分の処理を1サイクルで行おうとした場合、1サイクル分の処理が半端になってしまい、結果として6サイクルかけて処理を行うこととなる。

一方、本発明では第1の実施形態で示したように1サイクルあたりの処理に必要な処理時間を均等にするよう暗号化処理、復号処理をクロックサイクルごとへ分割した結果、処理に要するサイクル数が10サイクルとなった。したがって、2サイクル分の処理を1サイクルで行う場合にも端数が出ない。本第7の実施形態のように2サイクル分の処理を1サイクルで行った場合、1サイクルの削減効果は、約20%程度の処理速度の向上をもたらす。

次に、上記AESの暗号化処理、復号処理を実現するAES処理回路の回路構成について述べる。

図52は、本第7の実施形態のAES処理回路のブロック図を示したものである。

図52において、401はAESの処理を実行するAES処理回路である。402は共通鍵からAESの暗号化処理、復号処理に必要となる実行鍵を生成し、出力する鍵拡張部である。403は鍵拡張部402より供給される実行鍵を使って128ビットの平文データの暗号化処理または128ビットの暗号文データの復号処理を実行する暗号化・復号処理部である。404はAES処理回路401の外部からの制御信号を受け、鍵拡張部402および暗号化・復号処理部403の動作を制御するための信号を生成し、かつAES処理回路401の外部に対して動作完了を通知するための信号を生成する制御部である。

同図において、462は鍵拡張部402で生成された実行鍵のうちの一つであるところの実行鍵A1、463は鍵拡張部402で生成された実行鍵のうちの一つであるところの実行鍵A2である。

なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては同一参照番号を付し、その説明は省略する。

上記構成において、実行鍵A1(462)は鍵拡張部402から暗号化・復号処理部403に対して入力され、実行鍵A2(463)は鍵拡張部402から暗号化・復号処理部403に対して入力される。

次に、暗号化・復号処理部403について説明する。図53は暗号化・復号処理部403のブロック図を示したものである。同図において、405は実行鍵A1(462)を用いて暗号化処理を行うラウンド処理部である。407は選択信号170による制御を受けながら実行鍵A2(463)および実行鍵B(163)を用いて暗号化処理を行うラウンド処理部である。406は選択信号170による制御を受けながら実行鍵A1(462)および実行鍵B(163)を用いて復号処理を行うラウンド処理部である。408は実行鍵A2(463)を用いて復号処理を行うラウンド処理部である。

同図において、475はラウンド処理部407への入力信号、476はラウンド処理部408への入力信号である。なお、同図において第1の実施形態で説明した構成要素および信号線と同一のものに関しては同一参照番号を付し、その説明は省略する。

図54(a)はラウンド処理部405、図54(b)はラウンド処理部407のブロック構成図である。

まず、ラウンド処理部405について同図(a)を用いて説明する。図示において、110は入力信号165および実行鍵A1(462)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。111はAddRoundKey演算部110の出力を入力としSubBytes演算を行うところのSubBytes演算部である。112はSubBytes演算部111の出力を入力としShiftRows演算を行うところのShiftRows演算部である。113はShiftRows演算部112の出力を入力とし、MixColumns演算を行うところのMixColumns演算部である。MixColumns演算部113の出力信号はラウンド処理部405の出力となる。

次に、ラウンド処理部407について図54(b)を用いて説明する。図示において、110は入力信号475および実行鍵A2(463)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。111はAddRoundKey演算部110の出力を入力としSubBytes演算を行うところのSubBytes演算部である。112はSubBytes演算部111の出力を入力としShiftRows演算を行うところのShiftRows演算部である。113はShiftRows演算部112の出力を入力とし、MixColumns演算を行うところのMixColumns演算部である。114はShiftRows演算部112の出力および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。115は選択信号170に応じてMixColumns演算部113の出力、もしくはAddRoundKey演算部114の出力のいずれか一方を選択し、出力するセレクタである。セレクタ115の出力信号はラウンド処理部407の出力となる。

なお、上述した各演算の名称はFIPS197に記載されるAES処理の各サブブロック演算と同一である。

上記構成において、セレクタ115は選択信号170がNegateされている時はMixColumns演算部113の出力、Assertされている時はAddRoundKey演算部114の出力を選択し、出力する。

次に、ラウンド処理部406、ラウンド処理部408について、図55(a),(b)を参照して説明する。同図(a)はラウンド処理部406のブロック図である。

図示において、116は入力信号165を入力としInvMixColumns演算を行うところのInvMixColumns演算部である。121は入力信号165および実行鍵B(163)を入力とし、AddRoundKey演算を行うところのAddRoundKey演算部である。118は選択信号170に応じて、InvMixColumns演算部116の出力かAddRoundKey演算部121の出力のいずれか一方を選択し、出力するセレクタである。119はセレクタ118の出力を入力としInvShiftRows演算を行うところのInvShiftRows演算部である。120はInvShiftRows演算部119の出力を入力としInvSubBytes演算を行うところのInvSubBytes演算部である。117はInvSubBytes演算部120の出力および実行鍵A1(462)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。AddRoundKey演算部117の出力はラウンド処理部406の出力となる。

なお、上述した各演算の名称は、FIPS197に記載されるAES処理の各サブブロック演算と同一である。

上記構成において、セレクタ118は選択信号170がNegateされている時InvMixColumns演算部116の出力、Assertされている時はAddRoundKey演算部121の出力を選択し、出力する。

次に、ラウンド処理部408について、図55(b)のブロック図を参照して説明する。

同図において、116は入力信号476を入力としInvMixColumns演算を行うところのInvMixColumns演算部である。119はInvMixColumns演算部116の出力を入力としInvShiftRows演算を行うところのInvShiftRows演算部である。120はInvShiftRows演算部119の出力を入力としInvSubBytes演算を行うところのInvSubBytes演算部である。117はInvSubBytes演算部120の出力および実行鍵A2(463)を入力としAddRoundKey演算を行うところのAddRoundKey演算部である。AddRoundKey演算部117の出力はラウンド処理部408の出力となる。

なお、上述した各演算の名称は、FIPS197に記載されるAES処理の各サブブロック演算と同一である。

次に、上記構成における暗号化処理時の動作を図56のタイミングチャートを用いて詳細に説明する。

図56において、横軸は時間を示しており、クロックの立ち上がりエッジに合わせてT01、T02、…、T33のタイミング名を割り当てた。また、同図左端に縦方向に並ぶ3桁のナンバは信号線を示しており、図52〜図55で使用されている信号線の参照番号と一対一で対応している。

図56のタイミングチャートに示される暗号化処理時の動作は4つに大別される。1つ目は、共通鍵等の各種パラメータを設定するパラメータ設定期間(T01〜T06)である。2つ目は、wkey10を生成しレジスタに保持するための鍵準備期間(T06〜T12)である。3つ目は、1ブロック目の暗号化処理期間(T12〜T17)、そして、4つ目は、2ブロック目の暗号化処理期間(T17〜T22)である。

パラメータ設定では、共通鍵152、暗号化・復号選択信号153の他、必要に応じて鍵長や暗号モードなど暗号化・復号処理に必要な各種パラメータが設定される。パラメータ設定期間はリセット直後からの任意長の期間であり、AES処理回路401の外部より鍵準備開始信号155がAssertされると(T06)、パラメータ設定期間が終了する。

パラメータ設定期間が終了すると同時に、次の鍵準備期間が開始される。鍵準備期間は、鍵拡張部において事前に実行鍵を生成するための期間である。鍵準備期間は鍵準備開始信号155がAssertされてから(T06)、最後の実行鍵(wkey10)が生成される6サイクル後(T12)までの期間である。

次に、鍵準備期間における各回路の動作について述べる。鍵拡張部402はパラメータ設定期間中から、共通鍵152より供給されるwkey0を用いてwkey1の生成を行っており、鍵準備開始信号155がAssertされると同時にwkey1が実行鍵A2(463)のレジスタに保持され、出力される。鍵準備開始信号155のAssertにあわせ、制御部404はカウンタ信号161を0から順次カウントアップする。鍵拡張部402はT07において実行鍵A2(463)に保持されているwkey1を用いて鍵拡張を行いwkey2およびwkey3を生成し、それぞれ実行鍵A1(462)、実行鍵A2(463)より出力する。そして、次のサイクル(T08)では実行鍵A2(463)より出力されるwkey3を用いてwkey4およびwkey5を生成し、それぞれ実行鍵A1(462)、実行鍵A2(463)より出力する。以下、同様にして実行鍵が生成され、タイミングT09ではwkey6およびwkey7、タイミングT10ではwkey8およびwkey9、がそれぞれ実行鍵A1(462)、実行鍵A2(463)より出力される。タイミングT11になると、鍵拡張部402は実行鍵A2(463)より出力されるwkey9を用いてwkey10を生成し、実行鍵B(163)より出力する。以後、wkey10は再び鍵準備が実行されるまで実行鍵B(163)より出力され続ける。

鍵準備期間が終了時(T12)、鍵拡張部402は、共通鍵152より供給されるwkey0をを用いてwkey1を生成し、暗号化・復号処理で最初に用いられる実行鍵(wkey0、wkey1)をそれぞれ実行鍵A1(462)、実行鍵A2(463)より出力する。実行鍵A1(462)および実行鍵A2(463)の値は、暗号化・復号処理開始信号158がAssertされるまで保持される。そして、制御部404はカウンタ信号161のカウントアップを停止し、カウンタをゼロクリアする。

また、鍵準備期間の終了に合わせ、制御部404は鍵準備の開始から5サイクル目(T11)において、次サイクル(T12)で鍵準備が終了し、暗号化処理が可能となることを見越し、暗号化・復号処理許可信号157をAssertする。

AES処理回路401の外部にある入力信号供給部は、タイミングT12で暗号化・復号処理許可信号157のAssertを検知すると、入力信号150として平文データP0をAES処理回路401に供給する。そして、入力信号150に対する暗号化処理を開始せしめるため、暗号化・復号処理開始信号158をAssertする(T12)。なお、このタイミングチャートでは最短のサイクルで暗号化・復号処理開始信号158がAssertされているが、そのタイミングはAES処理回路401の外部で自由に決められる。

暗号化処理期間は、入力信号150に対して暗号化処理を行う期間である。暗号化処理期間は、暗号化・復号処理開始信号158がAssert(T12)されてから、その5サイクル後(T17)までの期間である。

制御部404は暗号化・復号処理開始信号158のAssertを検知すると、次サイクル(T13)で暗号化・復号処理許可信号157、有効出力期間信号159、出力保持制御信号160をNegateする。同時に、カウンタ信号161のカウントアップを開始する。

鍵拡張部402は、鍵準備期間と同様に実行鍵の生成を行い、実行鍵A1(462)として、タイミングT12ではwkey0、タイミングT13ではwkey2、…、タイミングT16ではwkey8を出力する。また、実行鍵A2(463)としてタイミングT12ではwkey1、タイミングT13ではwkey3、…、タイミングT16ではwkey9を出力する。

ラウンド処理部405はタイミングT12〜T13では選択信号171がNegateされているため、入力信号150に対して、実行鍵A1として出力されているwkey0を用いて各サブブロック演算を行う。タイミングT13〜T17では選択信号171がAssertされている。そのため、ラウンド処理部405は、データ保持部108の出力信号に対して、T13〜T14ではwkey2、T14〜T15ではwkey4、…、T15〜T16ではwkey6を用いてサブブロック演算を行う。

一方、ラウンド処理部407は入力信号475に対して、T12〜T13ではwkey1、T13〜T14ではwkey3、T14〜T15ではwkey5、…、T15〜T16ではwkey7を用いてサブブロック演算を行う。

暗号化処理の最終サイクルになると(T16)、制御部404は選択信号170をAssertする。それを受け、ラウンド処理部407のセレクタ115は、実行鍵B(163)を用いてAddRoundKey演算を行うAddRoundKey演算部114の出力を選択し、最終サイクルのサブブロック演算を行う。タイミングT16において、ラウンド処理部407の出力信号166は入力信号である平文データP0を暗号化した結果である暗号文データC0を出力しており、その値は1サイクル後(T17)にデータ保持部108よりAES処理回路401の出力として、外部に出力される。同時に、制御部404は暗号化処理が終了し、出力信号151が有効であることをAES処理回路401の外部に対して通知するため、有効出力期間信号159をAssertする(T17)。有効出力期間信号159がAssertされている間、AES処理回路401は出力信号151が有効であることを保証する。

一方、出力保持制御信号160は、タイミングT17において有効出力期間信号159がAssertされているものの、同じくT17において暗号化・復号処理開始信号158もまたAssertされているため、Negateされたままである。もしタイミングT17において暗号化・復号処理開始信号158がAssertされなかった場合、T17において出力保持制御信号160がAssertされ、データ保持部108の値は暗号文データC0に保持される。

また、鍵拡張部402は暗号化処理が終了するT17において、実行鍵A1(462)よりwkey0、実行鍵A2(463)よりwkey1を出力する。そして、実行鍵A1(462)および実行鍵A2(463)の値は、次なる暗号化・復号処理開始信号156がAssertされるまで保持される。

さらに、制御部404は暗号化処理の完了(T17)を見越し、完了の1サイクル前(T16)に暗号化・復号処理許可信号157をAssertする。AES処理回路401の外部は、暗号化・復号処理許可信号157がAssertされていると、入力信号150の値を次なる平文データP1とし、2ブロック目の暗号化処理を開始することが可能となる。図56のタイミングチャートでは、AES処理回路401の外部は、最短のサイクルで次なる暗号化・復号処理開始信号をAssertしている(T17)。2ブロック目の暗号化処理はT17〜T22までであり、1ブロック目と同様の動作が行われる。以降、あらかじめ決められたブロック数の暗号化処理の動作が繰り返し行われる。図56のタイミングチャートでは1ブロック目の暗号化処理の終了後、2ブロック目の暗号化処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの暗号化処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には暗号化処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の暗号化処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

続いて、本第7の実施形態の復号処理の動作について説明する。

図57は本実施形態の復号処理のタイミングチャートを示したものである。同図において横軸は時間を示しており、クロックの立ち上がりごとにT01、T02、…、T33のタイミング名を割り当てた。また、同図左端に縦方向に並ぶ3桁の番号は信号線を示しており、図52〜図55で使用されている信号線の参照番号と一対一で対応している。

復号の場合も4つに大別される。すなわち、パラメータ設定(T01〜T06)、鍵準備(T06〜T12)、1ブロック目の復号処理(T12〜T17)、2ブロック目の復号処理(T17以降)である。

パラメータ設定期間の役割、開始条件、終了条件は本実施形態の暗号化時と同様である。ただし、復号時は暗号化・復号選択信号153がAssertされる必要がある。

鍵準備期間はT06〜T12までであり、開始条件および終了条件は本実施形態の暗号化時と同様である。各回路の動作も暗号化時とほぼ同様である。ただし、鍵準備期間の終了時(T12)において鍵拡張部402は、実行鍵B(163)に保持されているwkey10を用いて逆順に鍵拡張を行い、復号処理で最初に用いられる実行鍵(wkey9、wkey8)を実行鍵A1(462)、実行鍵A2(463)よりそれぞれ出力する。実行鍵A1(462)および実行鍵A2(463)の値は、暗号化・復号処理開始信号158がAssertされるまで保持される。そして、制御部404はカウンタ信号161のカウントアップを停止し、カウンタをゼロクリアする。

また、鍵準備期間の終了に合わせ、制御部404はT11において、T12で鍵準備が終了し、復号処理が可能となることを見越し、暗号化・復号処理許可信号157をAssertする。

AES処理回路401の外部にある入力信号供給部は、T12で暗号化・復号処理許可信号157のAssertを検知すると、入力信号150として暗号文データC0をAES処理回路401に供給する。そして、入力信号150に対する復号処理を開始せしめるため、暗号化・復号処理開始信号158をAssertする(T12)。なお、このタイミングチャートでは最短のサイクルで暗号化・復号処理開始信号158がAssertされているが、そのタイミングはAES処理回路401の外部で自由に決められる。

復号処理期間は、入力信号150に対して復号処理を行う期間である。復号処理期間は、暗号化・復号処理開始信号158がAssert(T12)されてから、その5サイクル後(T17)までの期間である。

制御部404は暗号化・復号処理開始信号158のAssertを検知すると、次サイクル(T13)で暗号化・復号処理許可信号157、有効出力期間信号159、出力保持制御信号160をNegateする。同時に、カウンタ信号161のカウントアップを開始する。

鍵拡張部402はT13において実行鍵A2(463)に保持されているwkey8を用いて鍵拡張を行いwkey7およびwkey6を生成し、それぞれ実行鍵A1(462)、実行鍵A2(463)より出力する。そして、次のサイクル(T14)では実行鍵A2(463)より出力されるwkey6を用いてwkey5およびwkey4を生成し、それぞれ実行鍵A1(462)、実行鍵A2(463)より出力する。以下、同様にして実行鍵が生成され、T15ではwkey3およびwkey2、T16ではwkey1およびwkey0がそれぞれ実行鍵A1(462)、実行鍵A2(463)より出力される。

復号処理の最初のサイクル(T12)では、制御部404により選択信号171がNegateされている。そのため、ラウンド処理部406には入力信号150の平文データP0が入力される。ラウンド処理部406は、選択信号170がAssertされているため、AddRoundKey演算部121の出力を選択するようセレクタ118を切り替え、1サイクル分の復号処理が行われる。ラウンド処理部406の出力はそのままラウンド処理部408に対して入力され、さらにもう1サイクル分の復号処理が行われる。ラウンド処理部408で出力結果はデータ保持部108に保持される。

次サイクル(T13)になると、制御部404により選択信号171がAssertされ、データ保持部の出力がラウンド処理部406に対して入力される。ラウンド処理部406は、選択信号170がNegateされているため、InvMixColumns演算部116の出力を選択するようセレクタ118を切り替え、1サイクル分の復号処理が行われる。ラウンド処理部406の出力はそのままラウンド処理部408に対して入力され、さらにもう1サイクル分の復号処理が行われる。以下、T16まで同様にして処理が行われる。なお、ラウンド処理部406は、実行鍵としてT12ではwkey10およびwkey9、T13ではwkey7、T14ではwkey5、T16ではwkey1を用いる。また、ラウンド処理部408は実行鍵T12ではwkey8、T13ではwkey6、T16ではwkey0を用いる。

T16において、ラウンド処理部408の出力信号167は入力信号である暗号文データC0を復号した結果である平文データP0を出力しており、その値は1サイクル後(T17)にデータ保持部108よりAES処理回路401の出力として、外部に出力される。同時に、制御部404は復号処理が終了し、出力信号151が有効であることをAES処理回路401の外部に対して通知するため、有効出力期間信号159をAssertする(T17)。有効出力期間信号159がAssertされている間、AES処理回路401は出力信号151が有効であることを保証する。

一方、出力保持制御信号160は、T17において有効出力期間信号159がAssertされているものの、同じくT17において暗号化・復号処理開始信号158もまたAssertされているため、Negateされたままである。もしT17において暗号化・復号処理開始信号158がAssertされなかった場合、T17において出力保持制御信号160がAssertされ、データ保持部108の値は平文データP0に保持される。

また、鍵拡張部402は復号処理が終了するT17において、実行鍵A1(462)よりwkey9、実行鍵A2(463)よりwkey8を出力する。そして、実行鍵A1(462)、実行鍵A2(463)の値は、次なる暗号化・復号処理開始信号156がAssertされるまで保持される。

さらに、制御部404は復号処理の完了(T17)を見越し、完了の1サイクル前(T16)に暗号化・復号処理許可信号157をAssertする。AES処理回路401の外部は、暗号化・復号処理許可信号157がAssertされていると、入力信号150の値を次なる暗号文データC1とし、2ブロック目の復号処理を開始することが可能となる。

2ブロック目の復号処理期間はT17〜T22までであり、1ブロック目と同様の動作が行われる。以降、あらかじめ決められたブロック数の復号処理の動作が繰り返し行われる。図57のタイミングチャートでは1ブロック目の復号処理の終了後、2ブロック目の復号処理が最短の間隔で実行されている。このようなタイミングですべてのブロックの復号処理が実行された場合、AES処理回路はピークの性能を発揮する。しかし、基本的には復号処理の間隔は任意の長さとすればよい。

あらかじめ決められたブロック数の復号処理がすべて終了し、次に共通鍵等のパラメータが異なるジョブを実行する際には、再びパラメータ設定から開始される。

本第7の実施形態は以上のようにして実施可能である。第7の実施形態は、1サイクル内で実行しなければならない処理の処理時間の最大値を増やすことなく、AESの暗号化処理、復号処理に要するクロックサイクル数を1サイクル削減しており、これにより約20%程度の処理速度の向上が得られる。

なお、ここでは第1の実施形態を例にとって説明したが、他の実施形態についても同様のことが実現できることはいうまでもない。

以上説明した第7の実施形態はあくまで本発明の一例に過ぎず、本発明の効果は上記実施形態に限ったことではない。

<第8の実施形態>

第7の実施形態の一般形として、第1の実施形態におけるNサイクル分の処理を1クロックサイクルで実行することが考えられる。ただしNは2以上の自然数である。本第8の実施形態では、そのような手法を実現する際の回路構成について述べる。

第1の実施形態におけるNサイクル分の処理を1クロックサイクルで実行する際、処理に要する総サイクル数をNで割り切れる場合と割り切れない場合の2種類に分類することができる。例えば、AES-128では処理に要する総サイクル数が10であるため(図1)、Nの値が2および5の場合は前者に、それ以外は後者に分類される。

まず、総サイクル数をNで割り切れる場合について述べる。このような場合、第7の実施形態でN=2のケースについて行ったのと同様に、暗号化処理、復号処理それぞれについてラウンド処理部をN個(Nは2以上の自然数)ずつ実装し、1クロックサイクルごとにすべてのラウンド処理部を使って処理を行えばよい。このとき、処理に要するクロックサイクル数は10/Nとなる。

第1の実施形態における総サイクル数をNで割り切れる場合の暗号化・復号処理部の回路構成について説明する。図58は本第8の実施形態の暗号化・復号処理部のブロック図を示したものである。同図において、503は暗号化・復号処理部、550は実行鍵A1、551は実行鍵A2である。ただし実行鍵Aは、実行鍵A1(550)、実行鍵A2(551)を含め、N個存在する。なお、第7の実施形態と同一の構成要素および信号線に関しては同一参照番号を付し、その説明は省略する。

上記構成において、セレクタ109の出力はラウンド処理部405に接続されている。ラウンド処理部405がN−1個直列に接続された後、最後に接続されたラウンド処理部405の出力がラウンド処理部407に接続されている。また、セレクタ109の出力はラウンド処理部406にも接続される。また、ラウンド処理部406の出力はラウンド処理部408に接続されており、ラウンド処理部408がN−1個直列に接続された後、最後に接続されたラウンド処理部408の出力がセレクタ107に対して接続されている。ラウンド処理部405には最初に接続されたものから順に実行鍵A1(550)、実行鍵A2(551)、以下別々の実行鍵Aが入力され、ラウンド処理部407にはN個目の実行鍵A、および実行鍵B(163)が入力されている。また、ラウンド処理部406には実行鍵A1(550)および実行鍵B(163)が入力されている。また、ラウンド処理部408には接続された順に実行鍵A2(551)以下別々の実行鍵Aが入力されている。なお、図58において、第7の実施形態と同一の接続関係のものに関しては説明を省略する。