JP4856363B2 - 安定な高次デルタ・シグマ誤差フィードバック変調器およびそのような変調器において使用される雑音伝達関数 - Google Patents

安定な高次デルタ・シグマ誤差フィードバック変調器およびそのような変調器において使用される雑音伝達関数 Download PDFInfo

- Publication number

- JP4856363B2 JP4856363B2 JP2004151328A JP2004151328A JP4856363B2 JP 4856363 B2 JP4856363 B2 JP 4856363B2 JP 2004151328 A JP2004151328 A JP 2004151328A JP 2004151328 A JP2004151328 A JP 2004151328A JP 4856363 B2 JP4856363 B2 JP 4856363B2

- Authority

- JP

- Japan

- Prior art keywords

- modulator

- signal

- output

- input

- transfer function

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000012546 transfer Methods 0.000 title claims description 23

- 238000000034 method Methods 0.000 claims description 9

- 238000010586 diagram Methods 0.000 description 13

- 238000013461 design Methods 0.000 description 8

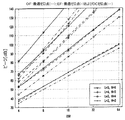

- 238000004088 simulation Methods 0.000 description 8

- 238000001228 spectrum Methods 0.000 description 7

- 230000009471 action Effects 0.000 description 5

- 229920005994 diacetyl cellulose Polymers 0.000 description 5

- 238000013139 quantization Methods 0.000 description 5

- 238000007493 shaping process Methods 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000005070 sampling Methods 0.000 description 4

- 238000013112 stability test Methods 0.000 description 4

- 229920000729 poly(L-lysine) polymer Polymers 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 238000012935 Averaging Methods 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 101100275990 Drosophila melanogaster Naus gene Proteins 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M7/00—Conversion of a code where information is represented by a given sequence or number of digits to a code where the same, similar or subset of information is represented by a different sequence or number of digits

- H03M7/30—Compression; Expansion; Suppression of unnecessary data, e.g. redundancy reduction

- H03M7/3002—Conversion to or from differential modulation

- H03M7/3004—Digital delta-sigma modulation

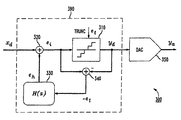

- H03M7/3015—Structural details of digital delta-sigma modulators

- H03M7/3031—Structural details of digital delta-sigma modulators characterised by the order of the loop filter, e.g. having a first order loop filter in the feedforward path

- H03M7/3042—Structural details of digital delta-sigma modulators characterised by the order of the loop filter, e.g. having a first order loop filter in the feedforward path the modulator being of the error feedback type, i.e. having loop filter stages in the feedback path only

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

- Amplifiers (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US47248803P | 2003-05-22 | 2003-05-22 | |

| US60/472488 | 2003-05-22 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004350295A JP2004350295A (ja) | 2004-12-09 |

| JP2004350295A5 JP2004350295A5 (enExample) | 2007-05-10 |

| JP4856363B2 true JP4856363B2 (ja) | 2012-01-18 |

Family

ID=33098336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004151328A Expired - Fee Related JP4856363B2 (ja) | 2003-05-22 | 2004-05-21 | 安定な高次デルタ・シグマ誤差フィードバック変調器およびそのような変調器において使用される雑音伝達関数 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6888484B2 (enExample) |

| EP (1) | EP1480345A3 (enExample) |

| JP (1) | JP4856363B2 (enExample) |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7986932B1 (en) | 2002-11-19 | 2011-07-26 | National Semiconductor Corporation | Fixed point FIR filter with adaptive truncation and clipping and wireless mobile station using same |

| US7084798B2 (en) * | 2004-01-16 | 2006-08-01 | Cirrus Logic, Inc. | Look-ahead delta sigma modulators with quantizer input approximations |

| US7170434B2 (en) * | 2004-01-16 | 2007-01-30 | Cirrus Logic, Inc. | Look-ahead delta sigma modulator with quantization using natural and pattern loop filter responses |

| US7009543B2 (en) * | 2004-01-16 | 2006-03-07 | Cirrus Logic, Inc. | Multiple non-monotonic quantizer regions for noise shaping |

| US7196647B2 (en) * | 2004-01-16 | 2007-03-27 | Cirrus Logic, Inc. | Signal processing with look-ahead modulator noise quantization minimization |

| US7187312B2 (en) * | 2004-01-16 | 2007-03-06 | Cirrus Logic, Inc. | Look-ahead delta sigma modulator having an infinite impulse response filter with multiple look-ahead outputs |

| US7138934B2 (en) * | 2004-01-26 | 2006-11-21 | Cirrus Logic, Inc. | Pattern biasing for look-ahead delta sigma modulators |

| US7148830B2 (en) * | 2004-01-26 | 2006-12-12 | Cirrus Logic, Inc. | Look-ahead delta sigma modulator with pruning of output candidate vectors using quantization error minimization pruning techniques |

| US7081843B2 (en) * | 2004-07-19 | 2006-07-25 | Cirrus Logic, Inc. | Overload protection for look-ahead delta sigma modulators |

| US7577695B2 (en) * | 2004-07-22 | 2009-08-18 | Auburn University | High-order delta-sigma noise shaping in direct digital frequency synthesis |

| EP1624577B1 (en) * | 2004-08-06 | 2008-07-23 | Verigy (Singapore) Pte. Ltd. | Improved analog signal generation using a delta-sigma modulator |

| US6956513B1 (en) * | 2004-10-22 | 2005-10-18 | Broadcom Corporation | Error feedback structure for delta-sigma modulators with improved stability |

| US7321324B2 (en) * | 2005-06-30 | 2008-01-22 | Silicon Laboratories Inc. | Unconditionally stable analog-to-digital converter |

| US7425910B1 (en) * | 2006-02-27 | 2008-09-16 | Marvell International Ltd. | Transmitter digital-to-analog converter with noise shaping |

| US7548178B2 (en) * | 2006-03-10 | 2009-06-16 | Nvidia Corporation | Method and apparatus for ADC size and performance optimization |

| US9300261B2 (en) * | 2006-03-10 | 2016-03-29 | Nvidia Corporation | Method and apparatus for efficient load biasing |

| JP4872439B2 (ja) * | 2006-04-21 | 2012-02-08 | 株式会社Ihi | データ補間方法及びデータ補間装置 |

| GB2438657A (en) * | 2006-06-02 | 2007-12-05 | Ubidyne Inc | Sigma delta modulator utilising systolic array |

| US7317411B1 (en) * | 2006-09-21 | 2008-01-08 | Cirrus Logic, Inc. | Delta-sigma modulator having quantizer code pattern detection controlled dither |

| US7986929B2 (en) * | 2006-12-08 | 2011-07-26 | Silicon Laboratories Inc. | Providing channel filtering in an automatic frequency control path |

| GB2451475B (en) * | 2007-07-31 | 2012-01-11 | Wolfson Microelectronics Plc | Frequency synthesizer |

| GB2451474B (en) * | 2007-07-31 | 2012-03-28 | Wolfson Microelectronics Plc | word length reduction circuit |

| US7495589B1 (en) * | 2007-09-17 | 2009-02-24 | Texas Instruments Incorporated | Circuit and method for gain error correction in ADC |

| US9048865B2 (en) | 2009-12-16 | 2015-06-02 | Syntropy Systems, Llc | Conversion of a discrete time quantized signal into a continuous time, continuously variable signal |

| EP2514098B1 (en) * | 2009-12-16 | 2016-11-09 | Syntropy Systems | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

| US9276602B1 (en) | 2009-12-16 | 2016-03-01 | Syntropy Systems, Llc | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

| US9680497B2 (en) | 2014-03-26 | 2017-06-13 | Syntropy Systems, Llc | Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal |

| JP5700702B2 (ja) * | 2012-07-18 | 2015-04-15 | 旭化成エレクトロニクス株式会社 | デルタシグマ変調器 |

| CN103701465B (zh) * | 2013-12-02 | 2016-09-21 | 苏州上声电子有限公司 | 一种基于多比特△—σ调制的数字扬声器系统实现方法和装置 |

| JP6228832B2 (ja) * | 2013-12-17 | 2017-11-08 | ルネサスエレクトロニクス株式会社 | デルタシグマ変調器 |

| US20150372805A1 (en) * | 2014-06-23 | 2015-12-24 | Qualcomm Incorporated | Asynchronous pulse modulation for threshold-based signal coding |

| US9685975B2 (en) | 2015-01-29 | 2017-06-20 | Syntropy Systems, Llc | Distributed combiner for parallel discrete-to-linear converters |

| US9853654B2 (en) * | 2015-02-25 | 2017-12-26 | Qualcomm Incorporated | Error-feedback digital-to-analog converter (DAC) |

| CN109635393B (zh) * | 2018-11-30 | 2023-04-07 | 上海芯钛信息科技有限公司 | 一种基于分布式算法的sigma-delta调制器设计方法及系统 |

| US11683624B1 (en) | 2020-05-12 | 2023-06-20 | Qualcomm Technologies, Inc. | Transducer with analog and digital modulators |

| CN116318165B (zh) * | 2023-03-02 | 2025-06-17 | 上海交通大学 | 采用二阶噪声耦合技术的两阶段线性-指数型增量型高分辨率模数转换器 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS567346B2 (enExample) * | 1972-10-11 | 1981-02-17 | ||

| DE3021012C2 (de) * | 1980-06-03 | 1985-08-22 | ANT Nachrichtentechnik GmbH, 7150 Backnang | Verallgemeinertes interpolativers Verfahren zur Digital-Analog-Umsetzung von PCM Signalen |

| EP1488336A4 (en) * | 2002-03-04 | 2006-02-15 | St Microelectronics Nv | ENCODER APPARATUS FOR RESONANCE POWER CONVERSION AND METHOD |

-

2004

- 2004-05-21 US US10/851,790 patent/US6888484B2/en not_active Expired - Lifetime

- 2004-05-21 JP JP2004151328A patent/JP4856363B2/ja not_active Expired - Fee Related

- 2004-05-24 EP EP04253046A patent/EP1480345A3/en not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| US6888484B2 (en) | 2005-05-03 |

| EP1480345A3 (en) | 2006-03-22 |

| US20040233086A1 (en) | 2004-11-25 |

| JP2004350295A (ja) | 2004-12-09 |

| EP1480345A2 (en) | 2004-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4856363B2 (ja) | 安定な高次デルタ・シグマ誤差フィードバック変調器およびそのような変調器において使用される雑音伝達関数 | |

| Galton | Spectral shaping of circuit errors in digital-to-analog converters | |

| US7576671B2 (en) | Mismatch-shaping dynamic element matching systems and methods for multi-bit sigma-delta data converters | |

| Hamoui et al. | High-order multibit modulators and pseudo data-weighted-averaging in low-oversampling/spl Delta//spl Sigma/ADCs for broad-band applications | |

| US6304608B1 (en) | Multibit sigma-delta converters employing dynamic element matching with reduced baseband tones | |

| US7969335B2 (en) | Digital correction of nonlinearity errors of multibit delta-sigma digital to analog converters | |

| US6980144B1 (en) | Method for reducing DAC resolution in multi-bit sigma delta analog-to digital converter (ADC) | |

| Kiss et al. | Stable high-order delta-sigma digital-to-analog converters | |

| US20050162296A1 (en) | Method and circuit for reducing quantizer input/output swing in a sigma-delta modulator | |

| Fitzgibbon et al. | Hardware reduction in digital delta-sigma modulators via bus-splitting and error masking—Part II: Non-constant input | |

| Colodro et al. | Continuous-time sigma–delta modulator with an embedded pulsewidth modulation | |

| Sun et al. | Reduced complexity, high performance digital delta-sigma modulator for fractional-N frequency synthesis | |

| Enuchenko et al. | Digital-to-analog converters based on delta-sigma modulators | |

| Zhang et al. | A segmented data-weighted-averaging technique | |

| Lindfors et al. | N‐path dynamic element matching for multibit bandpass ΣΔ modulators | |

| Kiss et al. | Stable high-order delta-sigma DACs | |

| Chiang et al. | Novel noise shaping of cascaded sigma-delta modulator for wide bandwidth applications | |

| Kulka et al. | Implementation of digital sigma-delta modulators for high-resolution audio digital-to-analog converters based on field programmable gate array | |

| Borkowski | Digital Δ-Σ Modulation: variable modulus and tonal behaviour in a fixed-point digital environment | |

| Friedman | Oversampled data conversion techniques | |

| Wisland et al. | A new scalable non-feedback/spl Delta//spl Sigma/digital-to-analog converter | |

| Lindfors et al. | Two-step quantization architectures for multibit/spl Delta//spl Sigma/-modulators | |

| Pelgrom | Time-Discrete Σ Δ Modulation | |

| Schubert | High Order Delta-Sigma Modulation with Positive Integer Coefficients | |

| Fitzgibbon et al. | Hardware reduction in delta-sigma digital-to-analog converters via bus-splitting |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070320 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070320 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090715 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091014 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091224 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111028 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141104 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4856363 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |