JP4713525B2 - Frequency synthesizer - Google Patents

Frequency synthesizer Download PDFInfo

- Publication number

- JP4713525B2 JP4713525B2 JP2007065883A JP2007065883A JP4713525B2 JP 4713525 B2 JP4713525 B2 JP 4713525B2 JP 2007065883 A JP2007065883 A JP 2007065883A JP 2007065883 A JP2007065883 A JP 2007065883A JP 4713525 B2 JP4713525 B2 JP 4713525B2

- Authority

- JP

- Japan

- Prior art keywords

- frequency

- voltage

- vector

- output

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000013598 vector Substances 0.000 claims description 227

- 230000010355 oscillation Effects 0.000 claims description 45

- 230000010354 integration Effects 0.000 claims description 38

- 238000001514 detection method Methods 0.000 claims description 35

- 238000005070 sampling Methods 0.000 claims description 24

- 238000004364 calculation method Methods 0.000 claims description 16

- 238000000605 extraction Methods 0.000 claims description 15

- 238000006243 chemical reaction Methods 0.000 claims description 11

- 238000000034 method Methods 0.000 description 16

- 238000010586 diagram Methods 0.000 description 14

- 230000014509 gene expression Effects 0.000 description 12

- 230000006870 function Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 238000012545 processing Methods 0.000 description 7

- 230000001186 cumulative effect Effects 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 238000013459 approach Methods 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000012067 mathematical method Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 230000002194 synthesizing effect Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Description

本発明は、所望の周波数の発振出力が得られる周波数シンセサイザに関する。 The present invention relates to a frequency synthesizer that can obtain an oscillation output of a desired frequency.

標準信号発生器の一つとしてPLL(Phase Locked Loop)を応用した周波数シンセサイザがある。周波数シンセサイザは図12に示すように、電圧制御発振器201を分周器202により1/Nに分周してその分周出力を位相比較器203の一方の入力端に入力すると共に、基準信号発生器である例えば水晶発振器204の発振出力を分周器200にて1/Mに分周してその分周出力を位相比較器203の他方の入力端に入力し、その比較信号をループフィルタ205を介して電圧制御発振器201にフィードバックし、こうしてPLLを構成している(例えば特許文献1)。PLLがロックすると電圧制御発振器201の発振出力の周波数fvcoと水晶発振器204の発振出力の周波数f0とは、fvco/N=f0/Mの関係にあるので、fvco=(N/M)f0となる。分周器202はプログラマブルカウンタにより構成されていて外部よりディジタルデータで分周比Nを設定できることから、fvcoの周波数を自由に設定できることになる。

As one of standard signal generators, there is a frequency synthesizer applying a PLL (Phase Locked Loop). As shown in FIG. 12, the frequency synthesizer divides the voltage controlled

周波数シンセサイザの応用としては、例えば移動局における局発振部として用いられる。即ち、基地局では所定の周波数帯域を移動局に割り当てるため、移動局側では、割り当てられた周波数帯域の発振出力を生成する必要があり、そのため局発振部に対し周波数を調整できる機能を持たせることが要請される。また無線通信機器の試験用信号源や放送機器などにも使用されている。 As an application of the frequency synthesizer, for example, it is used as a local oscillation unit in a mobile station. In other words, since the base station assigns a predetermined frequency band to the mobile station, the mobile station needs to generate an oscillation output of the assigned frequency band, so that the station oscillator has a function of adjusting the frequency. Is required. It is also used as a test signal source for radio communication equipment and broadcast equipment.

このように例えば通信分野において周波数シンセサイザを適用する場合には、他のチャネルとの混信を避けるためにノイズが少ないことが要求され、また電波が過密化していることから、周波数をできるだけ細かく設定できることが望ましい。周波数を細かく設定するためには、上記の分周比Nを大きくすればよいが、あまり大きくすると、ループに生じる遅延が長くなってノイズが大きくなり、実際にはNは1000程度が上限である。 In this way, for example, when applying a frequency synthesizer in the communication field, it is required to have low noise in order to avoid interference with other channels, and because radio waves are overcrowded, the frequency can be set as fine as possible Is desirable. In order to finely set the frequency, the above-described frequency division ratio N may be increased. However, if the frequency division ratio is increased too much, the delay occurring in the loop becomes longer and the noise becomes larger. .

このため説明の便宜上例えば1000MHz程度の周波数を1Hz単位で調整できる周波数シンセサイザを設計しようとすると、図12の装置を多段化する必要がある。即ち、Nの上限が1000であるとすると、位相比較器に入る基準信号の周波数(M/f0)を1MHzとすることで、1MHzきざみで設定できる1MHz〜1000MHzの周波数シンセサイザを制作できる。同様にして基準信号の周波数を1kHzとすることにより、1kHzきざみで設定できる1kHz〜1MHzの周波数シンセサイザを制作し、同様にして基準信号の周波数を1Hzとすることにより、1Hzきざみで設定できる1Hz〜1kHzの周波数シンセサイザを制作する。そして各周波数シンセサイザを段階的に合成することにより、1Hzきざみで1000Mヘルツまで設定できる周波数シンセサイザが得られることになる。 For this reason, if it is intended to design a frequency synthesizer that can adjust, for example, a frequency of about 1000 MHz in units of 1 Hz, the apparatus shown in FIG. 12 needs to be multistaged. That is, if the upper limit of N is 1000, a frequency synthesizer of 1 MHz to 1000 MHz that can be set in 1 MHz increments can be produced by setting the frequency (M / f0) of the reference signal entering the phase comparator to 1 MHz. Similarly, by setting the frequency of the reference signal to 1 kHz, a frequency synthesizer of 1 kHz to 1 MHz that can be set in steps of 1 kHz is produced. Similarly, by setting the frequency of the reference signal to 1 Hz, it can be set in steps of 1 Hz to 1 Hz. Produces a 1kHz frequency synthesizer. Then, by synthesizing each frequency synthesizer stepwise, a frequency synthesizer that can be set up to 1000 MHz in 1 Hz increments is obtained.

しかしながらこのようにすると、周波数を合成する各合成回路についてPLLを組まなければならないこともあって、回路構成が複雑で部品点数が多くなり、ノイズが多くなるという課題がある。 However, if this is done, a PLL must be assembled for each synthesis circuit that synthesizes the frequency, and there is a problem that the circuit configuration is complicated, the number of parts increases, and noise increases.

そこで本発明者は、従来の周波数シンセサイザとは原理が全く異なる新規な構成を採用することにより、広い帯域に亘って細かく周波数を設定することができる新規な方式の周波数シンセサイザを開発しているが、周波数の引き込み範囲が狭く、電圧制御発振部の製品のばらつきや温度特性などを考慮するとその引き込みを確実に行えないという問題を抱えており、実用化するためにはこの点を克服する必要がある。またこの周波数シンセサイザは、アナログ回路とディジタル回路とからなるが、ディジタル/アナログ変換部内の多数のスイッチング素子の同時スイッチングに基づくノイズを抑えなければならないという問題もある。 Therefore, the present inventor has developed a new type of frequency synthesizer that can set the frequency finely over a wide band by adopting a new configuration that is completely different in principle from the conventional frequency synthesizer. However, there is a problem that the pull-in range of the frequency is narrow and the pull-in cannot be performed reliably considering the variation of the voltage controlled oscillator product and the temperature characteristics, etc., and it is necessary to overcome this point for practical use. is there. This frequency synthesizer is composed of an analog circuit and a digital circuit, but there is also a problem that noise based on simultaneous switching of a large number of switching elements in the digital / analog conversion section must be suppressed.

本発明は、従来の周波数シンセサイザとは原理が全く異なる新規な構成を採用することにより、広い帯域に亘って細かく周波数を設定することができ、しかも低ノイズな周波数信号が得られる周波数シンセサイザであって、周波数の引き込み範囲を広くすることが出きる技術の提供、及びディジタル/アナログ変換部内の多数のスイッチング素子の同時スイッチングに基づくノイズを抑えることのできる技術の提供を目的とする。 The present invention is a frequency synthesizer capable of finely setting frequencies over a wide band and obtaining a low-noise frequency signal by adopting a novel configuration that is completely different in principle from a conventional frequency synthesizer. Thus, it is an object of the present invention to provide a technique capable of widening the frequency pull-in range and a technique capable of suppressing noise based on simultaneous switching of a large number of switching elements in a digital / analog conversion unit.

本発明の周波数シンセサイザは、供給された電圧に応じた周波数の周波数信号を発振する電圧制御発振部と、

前記周波数信号を電圧制御発振部の設定周波数に応じて1/N(Nは整数)に分周する分周手段と、

前記電圧制御発振部の出力周波数の1/Nに相当する周波数の正弦波信号を基準クロック信号に基づいてサンプリングしてそのサンプリング値をディジタル信号として出力するアナログ/ディジタル変換部と、

このアナログ/ディジタル変換部からの出力信号に対応する周波数信号に対して、周波数がω0/2πの正弦波信号のディジタル信号による直交検波を行い、当該周波数信号の周波数とω0/2πとの周波数差に相当する周波数で回転するベクトルを複素表示したときの実数部分及び虚数部分を取り出すベクトル取り出し手段と、

前記電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数を計算するパラメータ出力部と、

前記ベクトルの周波数と前記パラメータ出力部にて計算された周波数との差分を取り出す周波数差取り出し手段と、

この周波数差取り出し手段により取り出された周波数差に対応する電圧信号を積分してディジタル/アナログ変換部を介して制御電圧として前記電圧制御発振部に帰還する手段と、

A)装置の運転開始時に、電圧制御発振部からの出力周波数が小さすぎることに起因して周波数差取り出し手段から電圧信号が得られない間は、第1の定数を積分回路部により積分した立ち上げ用の電圧を電圧制御発振部の制御電圧として出力し、

B)PLLがロックされた後、前記帰還する手段からの制御電圧が予め設定された範囲から外れたときには、当該範囲に収まるように、第1の定数よりも小さく設定された第2の定数を積分回路部により積分した周波数引き込み用の電圧を出力し、

C)前記帰還する手段からの制御電圧が予め設定された範囲に収まった後には、前記積分動作を停止する

周波数引き込み手段と、を備え、

前記電圧制御発振部の制御電圧は、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧との加算値であり、

電圧制御発振部、ベクトル取り出し手段、及び前記電圧信号を電圧制御発振部に帰還する帰還手段によりPLLが形成され、PLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整されることを特徴とする。

The frequency synthesizer of the present invention includes a voltage controlled oscillation unit that oscillates a frequency signal having a frequency according to a supplied voltage,

Frequency dividing means for dividing the frequency signal into 1 / N (N is an integer) according to the set frequency of the voltage controlled oscillation unit;

An analog / digital converter that samples a sine wave signal having a frequency corresponding to 1 / N of the output frequency of the voltage-controlled oscillator based on a reference clock signal and outputs the sampled value as a digital signal;

The frequency signal corresponding to the output signal from the analog / digital converter is subjected to quadrature detection using a digital signal of a sine wave signal having a frequency of ω0 / 2π, and the frequency difference between the frequency signal and ω0 / 2π is detected. Vector extracting means for extracting a real part and an imaginary part when a vector rotating at a frequency corresponding to

A parameter output unit for calculating the frequency of the vector when the output frequency of the voltage controlled oscillation unit reaches a set value;

A frequency difference extracting means for extracting a difference between the frequency of the vector and the frequency calculated by the parameter output unit;

Means for integrating a voltage signal corresponding to the frequency difference extracted by the frequency difference extracting means and feeding it back to the voltage controlled oscillator as a control voltage via a digital / analog converter;

A) At the start of the operation of the apparatus, while the voltage signal cannot be obtained from the frequency difference extracting means due to the output frequency from the voltage controlled oscillation unit being too small, the first constant is integrated by the integrating circuit unit. The voltage for raising is output as the control voltage of the voltage controlled oscillator,

B) After the PLL is locked, when the control voltage from the means for returning deviates from a preset range, a second constant set smaller than the first constant is set so as to fall within the range. Output the frequency pull-in voltage integrated by the integration circuit ,

C) Frequency pulling means for stopping the integration operation after the control voltage from the feedback means falls within a preset range, and

The control voltage of the voltage controlled oscillating unit is an added value of the control voltage from the feedback means and the control voltage from the frequency pulling means,

A PLL is formed by the voltage controlled oscillation unit, the vector extracting unit, and the feedback unit that feeds back the voltage signal to the voltage controlled oscillation unit. When the PLL is locked, the output frequency of the voltage controlled oscillation unit is adjusted to the set frequency. It is characterized by that.

他の発明の周波数シンセサイザは、供給された電圧に応じた周波数の周波数信号を発振する電圧制御発振部と、

前記周波数信号を電圧制御発振部の設定周波数に応じて1/N(Nは整数)に分周する分周手段と、

前記電圧制御発振部の出力周波数の1/Nに相当する周波数の正弦波信号を基準クロック信号に基づいてサンプリングしてそのサンプリング値をディジタル信号として出力するアナログ/ディジタル変換部と、

このアナログ/ディジタル変換部からの出力信号に対応する周波数信号に対して、周波数がω0/2πの正弦波信号のディジタル信号による直交検波を行い、当該周波数信号の周波数とω0/2πとの周波数差に相当する周波数で回転するベクトルを複素表示したときの実数部分及び虚数部分を取り出すベクトル取り出し手段と、

前記電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数を計算するパラメータ出力部と、

前記ベクトルの周波数と前記パラメータ出力部にて計算された周波数との差分を取り出す周波数差取り出し手段と、

この周波数差取り出し手段により取り出された周波数差に対応する電圧信号を積分してディジタル/アナログ変換部を介して制御電圧として前記電圧制御発振部に帰還する手段と、

周波数引き込み手段と、を備え、

前記周波数引き込み手段は、

A)装置の運転開始時に、電圧制御発振部からの出力周波数が小さすぎることに起因して周波数差取り出し手段から電圧信号が得られない間は、立ち上げ用の電圧を電圧制御発振部の制御電圧として出力し、

B)周波数差取り出し手段から電圧信号が出力された後において、当該電圧信号を積分回路部により積分して前記帰還手段より大きい周波数刻みでアナログ信号に変換し、このアナログ信号を電圧制御発振部の制御電圧として出力し、

C)設定周波数と電圧制御発振部からの出力周波数との周波数差が予め設定された範囲に収まった後には、前記積分回路部の積分動作を停止して、前記周波数引き込み手段からの制御電圧を固定値とし、

D)帰還手段におけるディジタル/アナログ変換部の同時スイッチングを減らしてグリッチノイズを低減するために、前記固定値は、前記周波数引き込み手段におけるディジタル/アナログ変換部が設定可能な制御電圧の中で、出力周波数が設定周波数に最も近くなる制御電圧よりも、調整可能な周波数刻みの整数倍に対応する分だけずれた値に設定され、

前記電圧制御発振部、ベクトル取り出し手段、及び前記電圧信号を電圧制御発振部に帰還する帰還手段によりPLLが形成され、PLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整され、

前記電圧制御発振部の制御電圧は、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧の加算値であることを特徴とする。

A frequency synthesizer according to another invention includes a voltage-controlled oscillator that oscillates a frequency signal having a frequency corresponding to a supplied voltage,

Frequency dividing means for dividing the frequency signal into 1 / N (N is an integer) according to the set frequency of the voltage controlled oscillation unit;

An analog / digital converter that samples a sine wave signal having a frequency corresponding to 1 / N of the output frequency of the voltage-controlled oscillator based on a reference clock signal and outputs the sampled value as a digital signal;

The frequency signal corresponding to the output signal from the analog / digital converter is subjected to quadrature detection using a digital signal of a sine wave signal having a frequency of ω0 / 2π, and the frequency difference between the frequency signal and ω0 / 2π is detected. Vector extracting means for extracting a real part and an imaginary part when a vector rotating at a frequency corresponding to

A parameter output unit for calculating the frequency of the vector when the output frequency of the voltage controlled oscillation unit reaches a set value;

A frequency difference extracting means for extracting a difference between the frequency of the vector and the frequency calculated by the parameter output unit;

Means for integrating a voltage signal corresponding to the frequency difference extracted by the frequency difference extracting means and feeding it back to the voltage controlled oscillator as a control voltage via a digital / analog converter;

A frequency pulling means,

The frequency pulling means is

A) At the start of operation of the apparatus, while the voltage signal cannot be obtained from the frequency difference extracting means due to the output frequency from the voltage controlled oscillator being too small , the voltage for starting up is controlled by the voltage controlled oscillator. Output as voltage,

B) After the voltage signal is output from the frequency difference extracting means, the voltage signal is integrated by the integrating circuit section and converted into an analog signal at a frequency step larger than that of the feedback means, and this analog signal is converted into the voltage controlled oscillator section. Output as control voltage,

C) After the frequency difference between the set frequency and the output frequency from the voltage controlled oscillation unit falls within a preset range, the integration operation of the integration circuit unit is stopped, and the control voltage from the frequency pulling means is A fixed value,

D) In order to reduce glitch noise by reducing simultaneous switching of the digital / analog converter in the feedback means, the fixed value is output within a control voltage that can be set by the digital / analog converter in the frequency pull-in means. The frequency is set to a value that deviates from the control voltage closest to the set frequency by an amount corresponding to an integral multiple of the adjustable frequency increment.

A PLL is formed by the voltage controlled oscillation unit, the vector extracting unit, and a feedback unit that feeds back the voltage signal to the voltage controlled oscillation unit. When the PLL is locked, the output frequency of the voltage controlled oscillation unit is adjusted to a set frequency. ,

The control voltage of the voltage controlled oscillator is an added value of the control voltage from the feedback means and the control voltage from the frequency pulling means.

前記分周手段は、N=1の場合も含まれ、この場合実際の装置では分周器が使用されず、電圧制御発振部の出力端とアナログ/ディジタル変換部の入力端との間の導電路が本発明でいう分周手段に相当する。このように本発明では、特許請求の範囲の記載を分かりやすくするために、N=1の場合であっても分周手段という構成を記載している。

電圧制御発振部の制御電圧を、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧の加算値とするためには、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧とを加算して電圧制御発振部に供給するための結合器を備えた構成とすることができる。

The frequency dividing means includes a case where N = 1. In this case, the frequency divider is not used in an actual device, and the conduction between the output terminal of the voltage controlled oscillation unit and the input terminal of the analog / digital conversion unit. The road corresponds to the frequency dividing means in the present invention. Thus, in the present invention, in order to make the description of the scope of claims easy to understand, a configuration of frequency dividing means is described even when N = 1.

In order to set the control voltage of the voltage controlled oscillating unit as the sum of the control voltage from the feedback means and the control voltage from the frequency pulling means, the control voltage from the feedback means and the frequency pulling means from It can be configured to include a coupler for adding the control voltage and supplying the sum to the voltage controlled oscillator.

あるいは、前記電圧制御発振部は、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧とが夫々入力されるポートを備えた構成としてもよい。 Alternatively, the voltage-controlled oscillation unit may include a port to which a control voltage from the feedback unit and a control voltage from the frequency pulling unit are input.

本発明の好ましい態様としては、例えば前記パラメータ出力部は、電圧制御発振部の出力周波数の設定値をNで割ったときに、アナログ/ディジタル変換部で用いる基準クロック信号の周波数とベクトル取り出し手段で用いられるω0/2πとの差に最も近い周波数となるNの値を計算し、分周手段は、この値を用いて電圧制御発振部からの周波数信号を分周する例をあげることができる。 As a preferred aspect of the present invention, for example, the parameter output unit is configured to use a frequency of the reference clock signal used in the analog / digital conversion unit and a vector extraction unit when the set value of the output frequency of the voltage controlled oscillation unit is divided by N. An example can be given in which the value of N that is the frequency closest to the difference from ω0 / 2π used is calculated, and the frequency dividing means uses this value to divide the frequency signal from the voltage controlled oscillator.

更に本発明の好ましい態様を示すと、前記パラメータ出力部は、粗調整のための周波数刻みfaの整数倍の周波数のうち、電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数に最も近い周波数n・fa(nは整数)と、前記周波数刻みfaよりも小さい微調整のための周波数刻みfbの整数倍のうち、電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数と前記周波数n・faとの差に最も近い周波数m・fb(mは整数)と、を計算し、

前記周波数差取り出し手段は、前記ベクトル取り出し手段により得られた前記ベクトルに、周波数n・faで逆回転する逆ベクトルを乗算して、前記ベクトルの周波数から逆ベクトルの周波数を差し引いた周波数の微速ベクトルを取り出す手段と、前記微速ベクトルの周波数を、当該微速ベクトルの各サンプリング時の実数部分及び虚数部分の値から求める微速ベクトルの微速検出手段と、この微速検出手段で検出された微速ベクトルの周波数と周波数m・fbとの差に相当する信号を出力する手段と、を備えている。

Further, according to a preferred aspect of the present invention, the parameter output unit outputs the vector when the output frequency of the voltage controlled oscillation unit reaches a set value out of the frequency that is an integral multiple of the frequency increment fa for coarse adjustment. When the output frequency of the voltage controlled oscillation unit becomes a set value among the frequency n · fa (n is an integer) closest to the frequency and an integer multiple of the frequency step fb for fine adjustment smaller than the frequency step fa A frequency m · fb (m is an integer) closest to the difference between the frequency of the vector and the frequency n · fa;

The frequency difference extraction means multiplies the vector obtained by the vector extraction means by an inverse vector that rotates in reverse at a frequency n · fa, and subtracts the frequency of the inverse vector from the frequency of the vector. Means for taking out the frequency of the slow vector, a slow speed detecting means for the slow vector obtained from the values of the real part and imaginary part at the time of each sampling of the slow vector, and the frequency of the slow vector detected by the slow speed detecting means, And a means for outputting a signal corresponding to the difference between the frequency m · fb.

この場合、微速ベクトルの周波数は、ベクトルを表す複素平面上の位相θをsinθとみなすことができて、その周波数を近似計算により求めることができる程度に低いことが好ましい。

また微速ベクトルの微速検出手段は、あるサンプリング時における微速ベクトルの実数部分及び虚数部分で決まる複素平面上の位置と、次のサンプリング時における微速ベクトルの実数部分及び虚数部分で決まる複素平面上の位置と、の距離を演算して、その演算値を両サンプリング時における微速ベクトルの位相差とみなす手段を含む構成とすることができる。

In this case, the frequency of the slow vector is preferably low enough that the phase θ on the complex plane representing the vector can be regarded as sin θ and the frequency can be obtained by approximate calculation.

In addition, the slow speed detection means for the slow vector is a position on the complex plane determined by the real part and the imaginary part of the slow vector at a certain sampling, and a position on the complex plane determined by the real part and the imaginary part of the slow vector at the next sampling. And a means for considering the calculated value as the phase difference of the slow vector at the time of both samplings.

周波数差に相当する電圧信号を前記電圧制御発振部に帰還する手段は、例えば微速ベクトルの周波数と周波数m・fbとの差に相当する信号を累積する手段を含む。

また逆ベクトルは、複素表面上における逆ベクトルの位置を規定する実数部分及び虚数部分の組を回転方向に沿って順番に配列したデータテーブルと、逆ベクトルの回転方向及び周波数に対応するインクリメント数またはデクリメント数により前記データテーブルのアドレスを発生させる手段とにより生成することができる。

The means for feeding back the voltage signal corresponding to the frequency difference to the voltage-controlled oscillator includes, for example, means for accumulating a signal corresponding to the difference between the frequency of the slow vector and the frequency m · fb.

The inverse vector includes a data table in which a set of a real part and an imaginary part defining the position of the inverse vector on the complex surface is arranged in order along the rotation direction, and an increment number corresponding to the rotation direction and frequency of the inverse vector, or It can be generated by means for generating the address of the data table according to the decrement number.

本発明の周波数シンセサイザは、従来のように周波数の調整単位(いくつ刻みで周波数を調整できるかということ)を分周器の分周比に任せる手法とは全く異なる手法である。即ち、

イ.電圧制御発振部の出力周波数の正弦波信号を直交検波して、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを作成し、

ロ.電圧制御発振部の出力周波数が設定値になったときのベクトルの周波数を予め計算しておいて、

ハ.電圧制御発振部を駆動したときにベクトルの周波数と前記計算された周波数との差分に相当する電圧信号を電圧制御発振部にフィードバックして、その差分がゼロになるようにPLLを形成している。

従ってPLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整されることになるが、電圧制御発振部の出力周波数が設定値になったときのベクトルの周波数を予め計算しておくだけで、そしていわば1段のPLLでありながら、出力周波数を設定できるので、ノイズが小さくしかも広い帯域に亘って細かく周波数を設定することができる。例えば数百MHzの電圧制御発振器を例えば1Hz単位あるいはそれ以下の単位で設定することができ、極めて画期的な周波数シンセサイザが得られる。

The frequency synthesizer of the present invention is a completely different method from the conventional method in which the frequency adjustment unit (how many frequencies can be adjusted) is left to the frequency divider ratio. That is,

I. A quadrature detection is performed on the sine wave signal of the output frequency of the voltage controlled oscillator, and a vector that rotates at the frequency (speed) of the difference from the frequency of the frequency signal used for detection is created.

B. Calculate in advance the frequency of the vector when the output frequency of the voltage-controlled oscillator reaches the set value,

C. When the voltage-controlled oscillator is driven, a voltage signal corresponding to the difference between the vector frequency and the calculated frequency is fed back to the voltage-controlled oscillator, and the PLL is formed so that the difference becomes zero. .

Therefore, when the PLL is locked, the output frequency of the voltage controlled oscillator is adjusted to the set frequency, but the vector frequency when the output frequency of the voltage controlled oscillator reaches the set value is calculated in advance. It is possible to set the output frequency just by setting the output frequency in a so-called PLL, so that the frequency can be set finely over a wide band with less noise. For example, a voltage controlled oscillator of several hundred MHz can be set in units of, for example, 1 Hz or less, and a very innovative frequency synthesizer can be obtained.

そして、本発明では、電圧制御発振部からの出力周波数が小さくて設定周波数に対して大きな開きがある間は、第1の定数を積分回路部により積分して電圧制御発振部の制御電圧として出力することで前記出力周波数を高めている。またPLLがロックされた後、前記帰還する手段からの制御電圧を監視し、この制御電圧が予め設定された範囲から外れたときには、当該範囲に収まるように、周波数引き込み用の電圧を出力している。従って周波数の引き込み範囲が広く、電圧制御発振部の周波数にばらつきがあったり、温度特性などにより周波数が変化しても周波数の引き込みを行うことができるので、安定した動作が得られる。 In the present invention, while the output frequency from the voltage controlled oscillator is small and there is a large difference with respect to the set frequency, the first constant is integrated by the integrating circuit and output as the control voltage of the voltage controlled oscillator. This increases the output frequency. In addition, after the PLL is locked, the control voltage from the feedback means is monitored, and when the control voltage deviates from a preset range, a frequency pull-in voltage is output so that the control voltage falls within the range. Yes. Thus a wide capture range of frequencies, or there are variations in the frequency of the voltage controlled oscillator, it is possible to perform the pull-in frequency even when the frequency is changed due to temperature characteristics, stable operation can be obtained.

また第2の発明では、いわば微調整用の帰還手段のディジタル/アナログ変換部において中心値付近でスイッチングする確率が低くなるので、同時スイッチングするスイッチ数が少なくなり、グリッチノイズの低減化を図ることができる。 In the second invention, since the probability of switching near the center value in the digital / analog converter of the feedback means for fine adjustment is reduced, the number of switches that are simultaneously switched is reduced, and glitch noise is reduced. Can do.

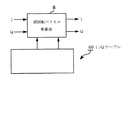

本発明の周波数シンセサイザは、新規な原理に基づいて動作するものであることから、先ず図1を参照しながら本発明の動作原理について簡単に概略的な説明をしておく。図1中1は、電圧制御発振部である電圧制御発振器であり、電圧出力部11から第1の加算部12を経て供給電圧に応じた周波数の矩形波である周波数信号を出力する。電圧制御発振器1からの周波数信号は分周手段2にて1/N(Nは整数)に分周され、更に正弦波に変換され、ディジタル信号に変換されるのであるが、ここではベクトル取り出し手段20により、前記周波数信号の周波数に応じた周波数(速度)で回転するベクトルが取り出されるという説明にとどめる。

Since the frequency synthesizer of the present invention operates based on a novel principle, first, an outline of the operation principle of the present invention will be briefly described with reference to FIG. In FIG. 1,

ベクトル取り出し手段20の後段の周波数差取り出し手段30は、前記ベクトルの周波数と、電圧制御発振器1の出力周波数が設定周波数になったときのベクトルの周波数frと、の差を取り出す。周波数差を取り出す手法としては、例えば電圧制御発振器1の出力周波数が設定周波数になったときにベクトル取り出し手段20にて取り出されるベクトルの回転方向とは逆方向に周波数frで回転する逆ベクトルを作成し、前記ベクトルと逆ベクトルとを乗算してその周波数差を取り出す手法が挙げられる。

The frequency

また逆ベクトルでベクトルの周波数をある程度落としておいて、残りの周波数差分を例えばベクトルの速度を近似式で検出するようにしてもよい。このような例をより具体化した例を挙げると、ベクトルの周波数をfrに一致させる調整(周波数差取り出し手段30により周波数差を取り出す調整工程)を、粗調整と微調整とに分ける。そして粗調整のための周波数刻みfaの整数倍の周波数のうち、電圧制御発振器1の出力周波数が設定値になったときの前記ベクトルの周波数に最も近い周波数n・fa(nは整数)を予め計算して、周波数n・faで逆回転する逆ベクトルを前記ベクトルに乗算して、前記ベクトルの周波数から逆ベクトルの周波数を差し引いた周波数の微速ベクトルを取り出す。そして前記周波数刻みfaよりも小さい微調整のための周波数刻みfbの整数倍のうち、frと前記周波数n・faとの差に最も近い周波数m・fb(mは整数)と、を計算し、前記微速ベクトルの周波数と周波数m・fbとの差を取り出し、こうしてベクトル取り出し手段により得られたベクトルの周波数とfrとの差が求められる。

Alternatively, the vector frequency may be reduced to some extent by using an inverse vector, and the remaining frequency difference may be detected by an approximate expression, for example, the vector speed. As a more specific example, such an adjustment that adjusts the frequency of the vector to fr (adjustment step for extracting the frequency difference by the frequency difference extracting means 30) is divided into rough adjustment and fine adjustment. A frequency n · fa (n is an integer) that is closest to the frequency of the vector when the output frequency of the voltage controlled

以上の一連の計算は、図示しないパラメータ出力部にて計算される。なおこのように周波数差を取り出す調整工程を粗調整と微調整とに分ける場合には、ベクトルの周波数がfrに近付いてきたときに正確な周波数差を得ることができる利点や、周波数の検出の演算が簡単になるという利点などがある。この点は後述の図2の具体例により明らかにされる。 The above series of calculations is performed by a parameter output unit (not shown). When the adjustment process for extracting the frequency difference is divided into rough adjustment and fine adjustment in this way, there is an advantage that an accurate frequency difference can be obtained when the vector frequency approaches fr, There is an advantage that the calculation becomes simple. This point will be clarified by a specific example of FIG. 2 described later.

そして周波数差取り出し手段30により取り出された周波数差に対応する電圧は帰還手段の一部をなす積分手段40により積分され、電圧制御発振器1の入力側に供給される。従って図1のループはPLLを形成しており、前記周波数差がゼロになったときにPLLがロックされ、電圧制御発振器1の出力周波数が設定周波数にロックされることになる。

Then, the voltage corresponding to the frequency difference extracted by the frequency

ところで前記周波数差が大きいときには、一般的には、ディジタル処理を行うベクトル取り出し手段20や周波数差取り出し手段30などを動作させるのに十分な電圧が得られないので、言い換えれば電圧制御発振器1の出力周波数が小さいので、電圧制御発振器1への制御電圧が得られない。このため運転開始初期には、周波数引き込み手段100内の積分回路部から制御電圧を発生させて電圧制御発振器1の出力周波数を引き上げている。そしてPLLの制御範囲に入った後は、周波数引き込み手段100内の積分回路部の積分動作を停止するようにしている。

より具体的には、先ず電圧制御発振器1のスタート時には周波数引き込み手段100から制御電圧が例えば結合器11を介して電圧制御発振器1に供給され、その制御電圧を徐々に大きくしていく。それに伴って電圧制御発振器1の出力周波数が上昇し、ベクトル取り出し手段20や周波数差取り出し手段30が機能し始めると、ベクトル取り出し手段20にて取り出されたベクトルの周波数が高くなっていく。そしてこの周波数がPLLの制御範囲に入ってくると、予め計算された、電圧制御発振器1の出力周波数が設定周波数になったときのベクトルの周波数frと、ベクトル取り出し手段20にて取り出されたベクトルの周波数と、の差(周波数差)が小さくなってくる。

そこで、周波数引き込み手段100からの制御電圧の上昇を止めて固定値とすると共に、前記周波数差に対応する電圧を積分して電圧制御発振器1に制御電圧として加える。その結果電圧制御発振器1の出力周波数の上昇率も小さくなり、前記周波数差の積分値の上昇率も徐々に小さくなる。このため電圧制御発振器1の出力周波数の上昇の仕方が更に緩やかになり、それにつれて前記周波数差に対応する電圧の積分値の上昇の仕方もより緩やかになる。やがて前記出力周波数が設定周波数に落ち着き、PLLループがロックされることになる。

By the way, when the frequency difference is large, generally, a voltage sufficient to operate the vector extraction means 20 or the frequency difference extraction means 30 for performing digital processing cannot be obtained. In other words, the output of the voltage controlled

More specifically, first, when the voltage controlled

Therefore, the control voltage from the frequency pulling means 100 is stopped from increasing to a fixed value, and a voltage corresponding to the frequency difference is integrated and applied to the voltage controlled

しかしながらこの周波数シンセサイザは、原理においては必ずしも周波数引き込み手段100を必要とするものではなく、もしディジタル処理部分において、前記周波数差が大きいときであってもそれに対応する電圧が出力されるとしたら次のように動作する。即ち、運転開始時には、周波数差取り出し手段30により取り出された周波数差に対応する電圧が大きく、この電圧が積分されて電圧制御発振器1の制御電圧として与えられるので、出力周波数が上昇する。その後は、上述のようにしてPLLループがロックされることになる。

However, this frequency synthesizer does not necessarily require the frequency pull-in means 100 in principle, and if the corresponding voltage is output even when the frequency difference is large in the digital processing portion, To work. That is, at the start of operation, the voltage corresponding to the frequency difference extracted by the frequency

実際には、設定周波数の大きさに応じて分周比を選択すればよいことから、ベクトルという発想を取り入れることにより、このように1段のPLLでありながら、広い周波数帯域に亘って細かな周波数設定を行うことができるのである。 In practice, it is only necessary to select a frequency division ratio according to the size of the set frequency. Therefore, by adopting the idea of a vector, a single-stage PLL is used in this way, but it is fine over a wide frequency band. The frequency can be set.

以下に本発明の周波数シンセサイザを具体化した例を図2以降にて説明する。 電圧制御発振器1の後段に設けられた手段について順番に説明すると、2は例えばプログラマブルカウンタからなる分周器であり、この分周器2の分周比N(Nは整数)は後述のパラメータ出力部により決定される。分周器2の後段には、分周器2からの周波数信号である矩形波信号を正弦波信号に変換するための手段としてローパスフィルタ21が設けられている。

3はA/D(アナログ/ディジタル)変換器であり、ローパスフィルタ21からの周が数信号である正弦波信号を基準クロック発生部31からのクロック信号によりサンプリングしてそのサンプリング値をディジタル信号として出力する。基準クロック発生部31は、前記周波数信号をサンプリングするために周波数の安定性が極めて高い周波数信号であるクロック信号を出力する。

An example in which the frequency synthesizer of the present invention is embodied will be described below with reference to FIG. The means provided in the subsequent stage of the voltage-controlled

Reference numeral 3 denotes an A / D (analog / digital) converter, which samples a sine wave signal whose frequency is a few signals from the low-

A/D変換器3で得られるディジタル信号で特定される高周波信号は基本波の他に高調波も含まれている。即ち高調波ひずみを有する正弦波をサンプリングする場合、その高調波成分が折り返しの影響を受けて、場合によっては周波数スペクトルにおける周波数軸上で基本波周波数と高調波の周波数とが重なる場合が想定される。そこでこのような重なりを避けて、電圧制御発振器1の出力周波数に正確に対応するベクトルを後で取り出す必要がある。

The high frequency signal specified by the digital signal obtained by the A / D converter 3 includes harmonics in addition to the fundamental wave. That is, when sampling a sine wave with harmonic distortion, the harmonic component is affected by aliasing, and in some cases, the fundamental frequency and the harmonic frequency may overlap on the frequency axis in the frequency spectrum. The Therefore, it is necessary to avoid the overlap and to later extract a vector that accurately corresponds to the output frequency of the voltage controlled

一般に周波数f1の正弦波信号を周波数fsのクロック信号でサンプリングした場合、その取り込み結果の周波数f2は(1)式で表される。ただしmod(,)はmodulo関数を表している。 In general, when a sine wave signal having a frequency f1 is sampled with a clock signal having a frequency fs, the frequency f2 obtained as a result of the capture is expressed by equation (1). However, mod (,) represents a modulo function.

f2=|mod(f1+fs/2,fs)−fs/2| ……(1)

この取り込み結果において、基本波周波数に対してn次の高調波の周波数はn×(基本波周波数)として表されるので、これをf2と置いて上記の(1)式に代入すれば、高調波がどのような周波数として取り込まれるかを計算することができる。この計算を用いることにより基本波の周波数と高調波の周波数とが重ならないように、分周器2からの高周波信号の周波数fcとサンプリング周波数(クロック信号の周波数)fsとを設定することができ、例えばベクトルが停止するときのfcが36MHzとなるように分周比Nを設定し、fsを40MHzに設定する。この場合、A/D変換器3からのディジタル信号である出力信号で特定される周波数信号の基本波は4MHzの正弦波となる。なおfc/fsを9/10にすれば、基本波の周波数と高調波の周波数とが重ならないが、fc/fsはこの値に限られるものではない。

f2 = | mod (f1 + fs / 2, fs) −fs / 2 | (1)

In this acquisition result, the frequency of the nth-order harmonic with respect to the fundamental frequency is expressed as n × (fundamental frequency). If this is set as f2 and substituted into the above equation (1), the harmonic It can be calculated as to what frequency the wave is captured. By using this calculation, the frequency fc of the high frequency signal from the

A/D変換器3の後段には、キャリアリムーブ4が設けられている。このキャリアリムーブ4は、A/D変換器3からのディジタル信号により特定される正弦波信号に対して周波数がω0t/2π(角速度がω0t)の正弦波信号により直交検波を行い、A/D変換器3のディジタル信号により特定される周波数信号の周波数と検波に用いる正弦波信号の周波数との差の周波数で回転するベクトルを取り出す手段、より詳しくはこのベクトルを複素表示したときの実数部分及び虚数部分を取り出す手段に相当する。 A carrier remove 4 is provided at the subsequent stage of the A / D converter 3. This carrier remove 4 performs quadrature detection on the sine wave signal specified by the digital signal from the A / D converter 3 by a sine wave signal having a frequency of ω0t / 2π (angular velocity is ω0t), and performs A / D conversion. Means for extracting a vector that rotates at the frequency of the difference between the frequency of the frequency signal specified by the digital signal of the device 3 and the frequency of the sine wave signal used for detection; more specifically, a real part and an imaginary number when this vector is complex-displayed It corresponds to the means for taking out the part.

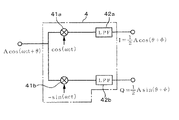

キャリアリムーブ4に関して詳述すると、キャリアリムーブ4は、図3に示すように前記正弦波信号に対してcos(ω0t)を掛け算する掛け算部41aと前記正弦波信号に対して−sin(ω0t)を掛け算する掛け算部41bと、掛け算部41a、41bの後段に夫々設けられたローパスフィルタ42a及び42bと、を備えている。従ってA/D変換器3で得られた正弦波信号をAcos(ω0t+θ)としたとき、掛け算部41aの出力及び掛け算部41bの出力は夫々(2)式及び(3)式により表される。

The carrier remove 4 will be described in detail. The carrier remove 4 has a

Acos(ω0t+θ)・cos(ω0t)

=1/2・Acosθ+1/2{cos(2ω0t)・cosθ+sin(2ω0t)・sinθ}……(2)

Acos(ω0t+θ)・−sin(ω0t)

=1/2・Asinθ−1/2{sin(2ω0t)・cosθ+cos(2ω0t)・sinθ}……(3)

そこで掛け算部41aの出力及び掛け算部41bの出力を夫々ローパスフィルタ42a及び42bを通すことにより、2ω0tの周波数信号は除去されるので、結局ローパスフィルタ42a、42bからは夫々1/2・Acosθと1/2・Asinθとが取り出される。ローパスフィルタ42a、42bにおける実際のディジタル処理は、掛け算部41a、41bから出力される時系列データについて連続する複数個のデータ例えば6個のデータの移動平均を演算している。

Acos (ω0t + θ) ・ cos (ω0t)

= 1/2 · Acosθ + 1/2 {cos (2ω0t) · cosθ + sin (2ω0t) · sinθ} (2)

Acos (ω0t + θ) ・ -sin (ω0t)

= 1/2 · Asinθ-1/2 {sin (2ω0t) · cosθ + cos (2ω0t) · sinθ} (3)

Therefore, by passing the output of the

以上のことは、A/D変換器3で得られた正弦波信号の周波数と直交検波に用いる正弦波信号の周波数が等しいときには、出力に時間関数が含まれないので、キャリアリムーブ4にて得られるベクトルは停止していることになる。一方Acos(ω0t+θ)で表される正弦波信号の周波数が変化すると、Acos(ω0t+θ)はAcos(ω0t+θ+ω1t)となる。従って1/2・Acosθは1/2・Acos(θ+ω1t)となり、1/2・Asinθは1/2・Asin(θ+ω1t)となる。即ち、ローパスフィルタ42a、42bから得られた出力は、正弦波信号[Acos(ω0t+θ)]の周波数の変化分(ω1t)に対応する信号、つまりA/D変換器3で得られた正弦波信号の周波数と直交検波に用いた正弦波信号の周波数との差分(ω1t/2π)の速度で回転するベクトルを複素表示したときの実数部分(I)及び虚数部分(Q)である。なお、この明細書では周波数と角速度とを使い分ける意義はないことから、両者を混在して用いることがある。

As described above, when the frequency of the sine wave signal obtained by the A / D converter 3 is equal to the frequency of the sine wave signal used for quadrature detection, the output does not include a time function. The resulting vector will be stopped. On the other hand, when the frequency of the sine wave signal represented by Acos (ω0t + θ) changes, Acos (ω0t + θ) becomes Acos (ω0t + θ + ω1t). Accordingly, 1/2 · Acosθ is 1/2 · Acos (θ + ω1t), and 1/2 · Asinθ is 1/2 · Asin (θ + ω1t). That is, the output obtained from the low-

図4はこのベクトルVを表した図であり、このベクトルVは長さがAであり、回転速度がω1t(=φ)である(周波数がω1t/2π)。この例では直交検波に用いた周波数は4MHzであり、A/D変換器3で得られた正弦波信号の周波数が4MHzであればベクトルの回転速度はゼロであるが、4MHzからずれていれば、そのずれた周波数差に応じた周波数(回転速度)で回転することになる。 FIG. 4 is a diagram showing the vector V. The vector V has a length A and a rotational speed ω1t (= φ) (frequency is ω1t / 2π). In this example, the frequency used for quadrature detection is 4 MHz. If the frequency of the sine wave signal obtained by the A / D converter 3 is 4 MHz, the vector rotation speed is zero, but if the frequency deviates from 4 MHz. , The motor rotates at a frequency (rotational speed) corresponding to the shifted frequency difference.

キャリアリムーブ4の後段には、逆ベクトル乗算部5が設けられている。この逆ベクトル乗算部5は、キャリアリムーブ4にて得られたベクトルVに対して、パラメータ出力部6にて作成された逆ベクトルV`を乗算するものである。この乗算は、直感的な表現を使えばベクトルVの速度を逆ベクトルV`の速度分だけ減速することになり、言い換えれば、ベクトルVの周波数と逆ベクトルV`の周波数との差で回転するベクトルを得ることになる。

An inverse

逆ベクトル乗算部5における演算について説明すると、キャリアリムーブ4及び逆ベクトル乗算部5は、コンピュータの演算により実行されるものであり、その演算のサンプリングにおいてあるタイミングのサンプリング例えばn回目のベクトルVのサンプリング値がI(n)+jQ(n)であったとすると、n回目の逆ベクトルV`のサンプリング値はI`(n)+jQ`(n)である。両ベクトルを乗算したベクトルI+jQは、{I(n)+jQ(n)}×{I`(n)+jQ`(n)}となる。この式を整理すると、(4)式となる。

I+jQ={I(n)・I`(n)−Q(n)・Q`(n)}+j{I(n)・Q`(n)+I`(n)・Q(n)} ……(4)

図5は、逆ベクトル乗算部5の構成を示しており、(4)式の演算を行っている。

逆ベクトルV`を発生するとは、実際には複素平面上におけるベクトルが逆回転するように当該ベクトルの実数部分及び虚数部分の値つまり逆ベクトルV`の位相をφ`とすると、cosφ`とsinφ`との値を発生させることである。図6は、ベクトルのcosφ`とsinφ`との組がベクトルの回転方向に沿って順番には配列されたI/Qテーブル60を示しており、パラメータ出力部6は、この例では前記I/Qテーブル60を備えていて、指示された電圧制御発振器1の設定周波数に応じて決定されるインクリメント数またはデクリメント数でI/Qテーブル60のアドレスを読み出し、逆ベクトル乗算部5に出力している。例えばアドレスを0番地からk番地までクロックの読み出しのタイミングにより1個づつ読み出すことによりベクトルVがある速度で回転し、インクリメント数を2にして1個おきにアドレスを読み出すと、ベクトルの速度が倍速になる。インクリメントして読み出すかデクリメントして読み出すかは、キャリアリムーブ4にて取り出されたベクトルVの回転方向により決めることができる。こうしてベクトルVに対して逆回転する逆ベクトルV`を生成することができる。

The computation in the inverse

I + jQ = {I (n) .I` (n) -Q (n) .Q` (n)} + j {I (n) .Q` (n) + I` (n) .Q (n)} (4)

FIG. 5 shows the configuration of the inverse

The generation of the inverse vector V ` means that the values of the real part and the imaginary part of the vector, that is, the phase of the inverse vector V `, are φ ` so that the vector on the complex plane is actually rotated in reverse. It is to generate a value with `. FIG. 6 shows an I / Q table 60 in which pairs of vector cosφ ` and sinφ ` are arranged in order along the rotation direction of the vector, and the parameter output unit 6 in this example uses the I / Q table 60 shown in FIG. A Q table 60 is provided, and the address of the I / Q table 60 is read with the increment number or the decrement number determined according to the set frequency of the instructed voltage controlled

図2におけるここまでのブロックについて、具体的な一連の演算に関して述べておく。電圧制御発振器1の出力周波数をfvcoとすると、分周器2にて分周された周波数はfvco/Nとなる。A/D変換部3では、周波数がfsのクロック信号によりサンプリングされるため、A/D変換部3にて得られたディジタル信号により特定される周波数信号の周波数は、fs−(fvco/N)となる。この例ではfsは40MHzであるから、40MHz−(fvco/N)となる。そしてキャリアリムーブ4における検波に用いられる正弦波信号の周波数(ω0t/2π)は4MHzとしているので、キャリアリムーブ4から取り出されるベクトルVの周波数は、40MHz−(fvco/N)−4MHzとなる。

With respect to the blocks so far in FIG. 2, a specific series of operations will be described. If the output frequency of the voltage controlled

ところでこの発明は、電圧制御発振器1の出力周波数fvcoが設定周波数になったときにベクトルVの周波数と前記周波数frとの周波数差がゼロになるように制御される。もし(fvco/N)が36MHzであれば、ベクトルVは停止いるので(周波数がゼロであるので)、この場合は、逆ベクトルV`の周波数をゼロに設定することで、PLLがロックされ、電圧制御発振器1の出力周波数fvcoが設定周波数になる。しかしこのようなケースは1点しかないので、実際にはキャリアリムーブ4から取り出されるベクトルVはある速度で回転している。このため、ベクトルVを止めるための逆ベクトルV`を発生させることが必要になるのであるが、一連の計算はソフトウエアで行われることから、逆ベクトルV`を発生させるためのデータを格納するメモリ容量はできるだけ小さくしたいというのが、設計上の要請である。

By the way, this invention is controlled so that the frequency difference between the frequency of the vector V and the frequency fr becomes zero when the output frequency fvco of the voltage controlled

この観点からすると、電圧制御発振器1の設定周波数をfsetとすると、fset/Nができる限り36MHzに近い方が好ましく、この例では、パラメータ出力部6において、ユーザにより設定された所望の設定周波数fsetに対し、fset/Nが36MHzに最も近くなる整数を演算し、その整数を分周器2の分周比Nとしている。こうすることによってキャリアリムーブ4から取り出されたベクトルVを止めるための逆ベクトルV`の周波数は、4MHzよりも小さい値になり、逆ベクトルV`を発生させるためのデータ量が少なくて済む。

From this point of view, assuming that the set frequency of the voltage controlled

ここで周波数の具体例を挙げると、電圧制御発振器1の設定周波数fsetを例えば520.0001MHzとすると、分周比Nは、例えばfset/36MHzに最も近い整数であるとした場合、N=14となる。この場合、電圧制御発振器の出力周波数が設定周波数fsetであるときの分周後の周波数は、fset/14=37.1428642857143MHzである。既述のように分周後の周波数が36MHzのときに、A/D変換部3にて得られるディジタル値により特定される周波数信号の周波数は、40MHz−36MHz=4MHzであり、4MHzの正弦波信号で直交検波を行うキャリアリムーブ4を通して得られるベクトルVの周波数は4MHz−4MHz=0、つまりベクトルVは停止することになる。従ってfset/14=37.1428642857143MHzの周波数信号がA/D変換部3にてディジタル化され、その周波数信号がキャリアリムーブ4に入力されて得られるベクトルVの周波数は、37.1428642857143MHz−36MHz=1.1428642857143MHzとなる。

このような演算は、周波数シンセサイザに対して設定周波数を入力することにより、電圧制御発振器1を動作させる以前にパラメータ出力部6にて行われる。またパラメータ出力部6は、図示しないメモリを参照して、設定周波数に近い周波数が得られる電圧値を選択し、これにより電圧出力部11の出力電圧がその電圧値に向かって上昇することになる。そして分周比Nを14に設定し、また逆ベクトルV`の周波数を1.1428642857143MHzに設定すれば

A/D変換部3にて得られる周波数信号の周波数が1.1428642857143MHzとなるまで、電圧制御発振器1の出力周波数fvcoが上昇し、やがてベクトルVの周波数と逆ベクトルV`の周波数とが一致したときにPLLがロックされ、fvcoがfsetに収束する。

図7は、ベクトルVが逆ベクトルV`により逆回し処理が行われて停止した状態をイメージ的に示す図である。

As a specific example of the frequency, if the set frequency fset of the voltage controlled

Such calculation is performed by the parameter output unit 6 before the voltage controlled

FIG. 7 is a diagram conceptually showing a state in which the vector V is stopped by performing the reverse rotation process using the reverse vector V `.

ところで上述の動作は、逆ベクトルV`だけに頼ってベクトルVを止める方式の場合の動作であり、この場合には、逆ベクトル乗算部5で得られたベクトルの周波数に対応する信号をループフィルタ8に入力すればよい。しかしながら、このような構成では逆ベクトルV`を発生させるためのデータ量がかなり多くなってしまう。このため図2に示す実施の形態では、逆ベクトルV`によりベクトルVの周波数をある程度まで減速し、残りの減速を後段の位相の時間差検出部71、加算部72及び位相差の累積加算部73の動作に任せている。言い換えれば、逆ベクトル乗算部5ではベクトルVの周波数の粗調整を行い、後段部位においてベクトルVの微調整を行うことで、ベクトルVを停止させている。

By the way, the above-described operation is an operation in the case of a method of stopping the vector V by relying only on the inverse vector V `. In this case, a signal corresponding to the frequency of the vector obtained by the inverse

ベクトルVの周波数の粗調整を行う逆ベクトルV`の周波数は、例えば152.587890625Hz刻みで設定できるようになっている。その理由は、40MHzにてデータをサンプリングする場合、逆ベクトルV`の位相のポイント数を2の18乗に設定すると、40MHz/2の18乗=152.587890625Hzとなるからである。つまりパラメータ出力部6では、最小租調周波数(周波数刻みfa)が152.587890625Hzであり、上記のベクトルVの周波数である1142864.2857143Hz(1.1428642857143MHz)に対して周波数刻みfaを何倍したら最も近くなるかを計算する。

1142864.2857143Hz/152.587890625Hzに最も近い整数は7490であり、パラメータ出力部6はこの整数を求めることにより、電圧制御発振部1の出力周波数が設定値になったときの前記ベクトルVの周波数に最も近い周波数n・fa(nは整数)=7490・152.587890625Hz=1142883.30078125Hzを求める。

The frequency of the inverse vector V ` for coarse adjustment of the frequency of the vector V can be set in increments of 152.5878890625 Hz, for example. The reason is that, when sampling data at 40 MHz, if the number of points of the phase of the inverse vector V 設定 is set to 2 to the 18th power, the 18th power of 40 MHz / 2 = 152.5878890625 Hz. That is, in the parameter output unit 6, the minimum adjustment frequency (frequency step fa) is 152.5878890625 Hz, and the frequency step fa is the most when the frequency step fa is multiplied with respect to the above-mentioned vector V frequency of 1142866.428557143 Hz (1.14282842871433 MHz). Calculate how close you are.

The integer closest to 1142862.2857143 Hz / 152.5878890625 Hz is 7490, and the parameter output unit 6 obtains this integer to obtain the frequency of the vector V when the output frequency of the voltage controlled

そしてパラメータ出力部6は、次の計算を行う。先ずベクトルVの周波数から、逆ベクトルV`により調整される周波数を差し引き、142864.2857143Hz−1142883.30078125Hz=19.0150669664145Hzを求める。

更に粗調整用の前記周波数刻みfaよりも小さい微調整のための周波数刻みfbこの例では周波数刻み1Hzの整数倍のうち、電圧制御発振部1の出力周波数が設定値になったときの前記ベクトルVの周波数と前記周波数n・faとの差である19.0150669664145Hzに最も近い周波数m・fb(mは整数)を計算する。この場合、fbは1Hzであるから、mは19となり、19Hz分の調整が逆ベクトル乗算部5の後段の部分により行われることになる。なおここでいう粗調整と微調整との用語は、この新方式の周波数シンセサイザの改良部分である帰還手段における粗調整と微調整とは異なるものである。

Then, the parameter output unit 6 performs the following calculation. First, the frequency adjusted by the inverse vector V ` is subtracted from the frequency of the vector V to obtain 142864.2857143 Hz-1142883.30078125 Hz = 19.01506669664145 Hz.

Further, the frequency step fb for fine adjustment smaller than the frequency step fa for coarse adjustment. In this example, the vector when the output frequency of the voltage controlled

図2に戻って7は減数処理部、71はローパスフィルタ、71は位相の時間差検出部、72は第2の加算部、73は位相差の累積加算部、8はループフィルタ、80はD/A(ディジタル/アナログ)変換部である。

ベクトルVの回転は逆ベクトルV`により減速されているので、ベクトルVの周波数(速度)を簡単な近似式で求めることができる。図8に示すように複素平面上において、(n−1)番目のサンプリングにより求めたベクトルV(n−1)とn番目のサンプリングにより求めたベクトルV(n)=V(n−1)+ΔVとのなす角度Δφ、即ち両サンプリング時のベクトルVの位相差Δφは、ベクトルVの周波数がサンプリング周波数よりも十分に小さくかつθ=sinθとみなせる程度であれば、ΔVの長さとみなすことができる。

Returning to FIG. 2, 7 is a reduction processing unit, 71 is a low-pass filter, 71 is a phase time difference detection unit, 72 is a second addition unit, 73 is a cumulative addition unit for phase difference, 8 is a loop filter, and 80 is a D / D A (digital / analog) conversion unit.

Since the rotation of the vector V is decelerated by the inverse vector V `, the frequency (speed) of the vector V can be obtained by a simple approximate expression. As shown in FIG. 8, on the complex plane, the vector V (n−1) obtained by the (n−1) th sampling and the vector V (n) = V (n−1) + ΔV obtained by the nth sampling. Can be regarded as the length of ΔV if the frequency of the vector V is sufficiently smaller than the sampling frequency and θ = sin θ. .

ΔVを求める近似式について説明すると、先ず位相差Δφは(5)式で表される。なおimagは虚数部分、conj{V(n)}はV(n)の共役ベクトル、Kは常数である。 The approximate expression for obtaining ΔV will be described. First, the phase difference Δφ is expressed by the equation (5). Here, imag is an imaginary part, conj {V (n)} is a conjugate vector of V (n), and K is a constant.

Δφ=K・imag[ΔV・conj{V(n)}] ……(5)

ここでI値(ベクトルVの実数部分)及びQ値(ベクトルVの虚数部分)についてn番目のサンプリングに対応する値を夫々I(n)及びQ(n)とすれば、ΔV及びconj{V(n)}は複素表示すると夫々(6)式及び(7)式で表される。

Δφ = K · imag [ΔV · conj {V (n)}] (5)

Here, if the values corresponding to the nth sampling are I (n) and Q (n) for the I value (the real part of the vector V) and the Q value (the imaginary part of the vector V), ΔV and conj {V (N)} is represented by the expressions (6) and (7), respectively, in a complex display.

ΔV=ΔI+jΔQ ……(6)

conj{V(n)}=I(n)−jQ(n) ……(7)

ただしΔIはI(n)−I(n−1)であり、ΔQはQ(n)−Q(n−1)である。(6)式及び(7)式を(5)式に代入して整理すると、Δφは(8)式で表されることになる。

ΔV = ΔI + jΔQ (6)

conj {V (n)} = I (n) -jQ (n) (7)

However, ΔI is I (n) −I (n−1), and ΔQ is Q (n) −Q (n−1). If the expressions (6) and (7) are substituted into the expression (5) and rearranged, Δφ is expressed by the expression (8).

Δφ=ΔQ・I(n)−ΔI・Q(n) ……(8)

前記位相の時間差検出部71は、このように近似式を用いてΔφを求める機能を備えている。このΔφは、逆ベクトル乗算部5にて減速されたベクトルVの周波数に対応する値であるから、位相の時間差検出部71は、減速されたベクトルVの周波数を出力する手段(微速ベクトル検出手段)であるといえる。

Δφ = ΔQ · I (n) −ΔI · Q (n) (8)

The phase time

なおベクトルV(n−1)とV(n)とが求まればこの間の角度Δφを求める手法は種々の数学的手法を使うことができ、その一例として(5)式の近似式を挙げたに過ぎない。その数式としてはV(n)とV(n−1)の各終点を結ぶ線の中点と原点とを結ぶベクトルVOである{V(n)+V(n−1)}/2を用い、(5)式においてV(n)に代えてこのベクトルVOを代入してもよい。このような(5)式が近似できる理由は、VOとΔVとが直交しているとみなすことができ、このためΔVの長さは、VOを実軸と見たてたときのΔVの虚数値に相当すると取り扱えることができるからである。 If the vectors V (n−1) and V (n) are obtained, various mathematical methods can be used as a method for obtaining the angle Δφ between them. As an example, the approximate expression (5) is given. Only. As the mathematical formula, {V (n) + V (n-1)} / 2 which is a vector VO connecting the midpoint of the line connecting the end points of V (n) and V (n-1) and the origin is used. In the equation (5), this vector VO may be substituted for V (n). The reason why the equation (5) can be approximated can be considered that VO and ΔV are orthogonal to each other. Therefore, the length of ΔV is the imaginary value of ΔV when VO is regarded as a real axis. This is because it can be handled if it corresponds to a numerical value.

一方パラメータ出力部6は、ベクトルVの周波数微調整分である19Hzの値を計算により求めているため、位相の時間差検出部71にて検出されたベクトルVの周波数と微調整分の19Hzとが加算部72にて突合されて、ベクトルVの周波数と微調整分の19Hzとの差分が取り出され、位相差の累積加算部73に入力される。そして位相差の累積加算部73からの出力値はループフィルタ8に入力される。

On the other hand, since the parameter output unit 6 obtains the value of 19 Hz, which is the fine frequency adjustment of the vector V, by calculation, the frequency of the vector V detected by the phase time

本発明は、図1に示したようにベクトルVを止める処理を行うが、この処理は図2の例ではいわば逆回しすることによるラフな停止処理と微速になったベクトルVを正確に止める処理とに分けており、後半の処理を位相の時間差検出部71と加算部72とに受け持たせていることになる。そして逆ベクトル乗算部5、位相の時間差検出部71及び第2の加算部72は、周波数差取り出し手段に相当する。なおこの例では、電圧制御発振器1の出力周波数が設定周波数よりも低いときには、つまり回転ベクトルの周波数が設定周波数よりも低いときには、位相の時間差検出部71の出力は負の値で出力されるので、この出力に−1を掛け算する掛け算部711を設けている。

The present invention performs the process of stopping the vector V as shown in FIG. 1, but in this example of FIG. 2, this process is a rough stop process by reverse rotation and the process of accurately stopping the vector V that has become slow. The latter half of the processing is assigned to the phase time

位相差の累積加算部73は、図9に示すようにあるサンプリング時における入力値をレジスタ73aに保持し、次のサンプリング時にそれまで保持されていた値を出力すると共に加算部73bに戻して入力値と加算し、その加算値をレジスタ73aに入力するように構成されている。

またループフィルタ8は、図1の積分手段に相当し、図10に示すように入力値を累積加算部8aにて累積加算すると共に、加算部8bにてその累積加算値に入力値を加算するように構成されている。このループフィルタ8の出力電圧は、D/A変換部80にてアナログ電圧とされて、後述の周波数引き込み手段のD/A変換部からの出力電圧と結合器11加算されて電圧制御発振器1に制御電圧として入力される。ループフィルタは信号の変動を抑え、ループの安定化を図る役割も持っている。

この例では、位相差の累積加算部73、ループフィルタ8及びD/A変換部80は帰還手段に相当する。

電圧制御発振部1から周波数差取り出し手段及びループフィルタ8を経て電圧制御発振部1に戻るループはPLLを形成している。またA/D変換器3からループフィルタ8に至るまでの各部位は、FPGAなどのディジタル処理装置により構成される。

As shown in FIG. 9, the phase

The

In this example, the phase difference

A loop returning from the voltage controlled

ここで本発明者は、位相の時間差検出部71の検出値とローパスフィルタ21の出力レベルとの関係を調べたところ、電圧制御発振器1の出力周波数が設定周波数になるポイント)を中心とした所定の周波数領域から外れるとローパスフィルタ21のゲインが落ちてきてしまうことを把握している。これでは、電圧制御発振器1の周波数が温度特性などによりこの範囲以上に変化した場合には、制御系が追従しないので周波数を設定周波数に引き込めなくなってしまう。また装置の運転開始時には電圧制御発振部1には制御電圧が入力されていないので、周波数の引き込み範囲まで制御電圧を立ち上げる必要がある。

Here, the inventor examined the relationship between the detection value of the phase time

そこで周波数引き込み手段100として、スイッチ部101、積分回路部102、加算部103及びD/A変換器104が設けられている。スイッチ部101は、接点a、b、cのいずれかに切り替えられ、aに切り替えられているときには位相の時間差検出部71の出力が、bに切り替えられているときには第2の定数が、cに切り替えられているときには第1の定数が夫々積分回路部102に取り込まれるようになっている。これら第1の定数及び第2の定数は、パラメータ出力部6から出力され、例えば第1の定数(接点cの設定値)よりも第2の定数(接点bの設定値)の方が小さく設定されている。

Therefore, as the frequency pull-in means 100, a switch unit 101, an

積分回路部102は、一つ前のサンプリングで得た値をラッチ部102aでラッチし、この値と今のサンプリングで得た値とを順次加算するように構成されている。またD/A変換器104は、D/A変換器80よりもディジタル側のビット数が少なくなっており、入力信号に対して大きい周波数刻みで出力するように構成されている。

The integrating

スイッチ部101の切り替え動作及び積分回路部102の積分/停止は、動作制御部105により行われる。動作制御部105は、設定周波数に応じて動作制御するためのしきい値となる周波数を決定し、電圧制御発振器1の出力周波数と位相の時間差検出部71に入力されるキャリアレベルとを検出して、検出結果としきい値とに応じてスイッチ部101及び積分回路部102の動作を制御する機能を有する。

Switching operation of the switch unit 101 and integration / stop of the

動作制御部105の動作は、後述の作用説明で図11、図12に示すとおり明らかにするが、ここでその機能をまとめておくと次のとおりである。

A)電圧制御発振器1からの出力周波数が小さすぎて設定周波数と当該出力周波数との周波数差が大きすぎることに起因して加算部72から電圧信号が得られない間は、スイッチ部101をcに設定しかつ積分回路部102をオンにして第1の定数を積分回路部102により積分するようにし、

B)第1の定数を積分回路部102により積分して電圧制御発振器1の制御電圧を出力した後、設定周波数と電圧制御発振器1からの出力周波数との周波数差が小さくなったことにより位相の時間差検出部71から電圧信号(この電圧信号はまだ有効ではない)が出力された後において、スイッチ部101をaに設定しかつ加算部72からの電圧信号を積分するため前記積分回路部102をオンにし、

C)設定周波数と電圧制御発振器1からの出力周波数との周波数差が更に小さくなって当該周波数差に対して位相の時間差検出部71から有効な電圧信号が得られる範囲内であり、かつループフィルタ8の出力が予め設定された範囲に収まった後、前記積分回路部102の積分動作を停止し、

D)前記積分回路部102の積分動作を停止した後に、位相の時間差検出部71から有効な電圧信号が得られる範囲内でありかつループフィルタ8の出力が予め設定された範囲から外れた後には、第2の定数を積分回路部102により積分し、当該ループフィルタ8の出力が予め設定された範囲に収まった後には、前記積分回路部102の積分動作を停止する。

The operation of the

A) While the output frequency from the voltage controlled

B) After the first constant is integrated by the integrating

C) The frequency difference between the set frequency and the output frequency from the voltage controlled

D) After the integration operation of the

次に図2に示す実施の形態の全体の動作について図11及び図12参照しながら説明する。今、上述の具体例で挙げたように、電圧制御発振器1の設定周波数fsetを例えば520.0001MHzとして図示しない入力部から入力したとする(図11のステップS1)。パラメータ出力部6は、電圧制御発振器1の設定周波数と供給電圧との関係を書き込んだテーブルを備えていて、このテーブルにおける520.0001MHzに最も近い設定周波数を選択する。

Next, the overall operation of the embodiment shown in FIG. 2 will be described with reference to FIGS. Now, as described in the above specific example, it is assumed that the set frequency fset of the voltage controlled

また既述のようにしてfset/36MHzに最も近い整数である分周比N=14と、設定周波数が得られるときのベクトルVの周波数を租調整量と微調整量とに分けたときの夫々の量と、を計算する。この場合、周波数の租調整量つまり逆ベクトルの周波数である1142883.30078125Hzと第2の加算器72に入力する微調整量である逆回し処理後のベクトルの周波数19Hzとを計算する。

Further, as described above, the frequency division ratio N = 14, which is the integer closest to fset / 36 MHz, and the frequency of the vector V when the set frequency is obtained are divided into the adjustment amount and the fine adjustment amount, respectively. And calculate the amount. In this case, the frequency adjustment amount, that is, 1142883.30078125 Hz, which is the frequency of the inverse vector, and the vector frequency 19 Hz after the reverse rotation processing, which is the fine adjustment amount input to the

そして周波数引き込み手段である加算部103に加算される初期電圧が設定周波数に見合った値として計算され、更に積分回路部102の積分値がクリアされる(ステップS2、S3)。入力部からスタートの指示を入力すると、前記初期電圧が加算部103に加算されて電圧制御発振器1が立ち上げられるが、この時点では出力周波数が低くて設定周波数との周波数差が大きいのでPLLループは動作しないので即ち加算部72からは電圧信号が出力されず、判断ステップS4を介してステップS5に移り、スイッチ部101が接点cに設定されて第1の定数が積分回路部102にて積分される。

なおキャリアリムーブ4から加算部72に至る演算に関しては既に詳述してある通りであるが、まとめた説明を後で行うことにする。

Then, the initial voltage added to the adding

The calculation from the carrier remove 4 to the

上述の積分の結果、図12に示すように電圧制御発振器1の出力周波数が上昇し、時刻t1にて加算部72から電圧信号が出力され始める。このため判断ステップS4を介してステップS6に移るが、この段階では位相の時間差検出部71から電圧信号が出力されるとはいっても、出力周波数に対応した有効な値ではない。位相の時間差検出部71の入力キャリアが検出できるようになると、ステップS7にてスイッチ部101がaに切り替わる。このため積分回路部102には位相の時間差検出部71からの電圧信号が積分され、この積分値がD/A変換器104を介して結合器11に与えられ、D/A変換器80からの電圧と加算されて制御電圧として電圧制御発振部1に与えられる。

こうして電圧制御発振器1の出力周波数が上昇し、ループフィルタ8の出力値が設定されたしきい値の範囲(第1の設定範囲)内に入ると(時刻t2)、PLLが概ねロックされたものとして、ステップS8に移ってスイッチ部101がbに切り替わり、積分回路部102の積分動作を停止する。

As a result of the integration described above, the output frequency of the voltage controlled

When the output frequency of the voltage controlled

PLLがロックした後、電圧制御発振器1の出力周波数が温度特性などにより変化するおそれがあるので、動作制御部105はステップS9にてD/A変換器80の例えばディジタル値があるしきい値の範囲(例えばフルレンジの1/6〜5/6の範囲である第2の設定範囲)であるか否かを監視して、その範囲から外れるとステップS10により積分回路部102の積分動作を開始する。これにより第2の定数が積分回路部102により積分され、第2の定数は、正の値または負の値として供給される。この積分値はD/A変換器104を介して結合器11に与えられ、D/A変換器80からの電圧と加算されて制御電圧として電圧制御発振部1に与えられる。そしてD/A変換器80のディジタル値が前記しきい値の範囲に収まると、積分回路部102の積分動作を停止する(ステップS9)。

After the PLL is locked, there is a possibility that the output frequency of the voltage controlled

次ぎにキャリアリムーブ4から加算部72に至る演算を含む作用に関して述べておく。装置のスタート時に電圧制御発振器1に電圧が供給されると、周波数信号を出力しその周波数が上昇していく。初めのうちは電圧制御発振器1の出力周波数が低いので、A/D変換部3にて取り出される周波数[40MHz−(出力周波数/N)]が大きく、このためキャリアリムーブ4にて取り出されるベクトルVの周波数が負の大きな値になっており、ローパスフィルタ71にてキャリアが減衰するため、位相の時間差検出部71からは電圧信号が出力されない。電圧制御発振器1の出力周波数がある値まで上昇すると、キャリアリムーブ4からのベクトルVの取り出し演算が有効になってベクトルVの周波数(速度)が落ち始める。

Next, the operation including the calculation from the carrier remove 4 to the

この説明では、40MHz−(出力周波数/N)の値が4MHzよりも小さいとき、つまり出力周波数/Nが36MHzよりも大きいときのベクトルVの回転方向を正の方向と呼ぶとすると、負の方向に回転しているベクトルVの周波数が低くなってきたということである。このとき逆ベクトル乗算部5の出力である、逆回転分が乗算されたベクトルVの周波数も低くなってくる。従って位相の時間差検出部71の出力は、演算が有効になったときは、設定周波数と出力周波数との差がまだ大きいので、大きな値になっているが、徐々に小さくなり(負の速度が小さくなり)、前記出力(位相差)と周波数の微調整量とを加算した第2の加算部72の加算値も小さくなっていく。

In this description, when the value of 40 MHz− (output frequency / N) is smaller than 4 MHz, that is, when the rotation direction of the vector V when the output frequency / N is larger than 36 MHz is called a positive direction, a negative direction is assumed. This means that the frequency of the vector V rotating at a low speed has decreased. At this time, the frequency of the vector V multiplied by the reverse rotation, which is the output of the inverse

更に電圧制御発振器1の出力周波数が上昇して、分周後の周波数が36MHzになり、キャリアリムーブ4から取り出されるベクトルVの速度が停止するタイミングとなる。ここで租調整周波数をΔF(n・fa)とし、微調整周波数をΔf(m・fb)とすると、キャリアリムーブ4から取り出されるベクトルVの周波数が周波数の調整分ΔF+Δfよりも未だ小さく、その周波数差(第2の加算部72の出力)が負の値であることから、ベクトルVの周波数は上昇する。やがてベクトルVの周波数は前記周波数の調整分ΔF+Δfと同じになる。こうしてやがて位相の時間差検出部71の出力がΔf(上述の具体例では19Hz)に収束し、第2の加算部72の出力、即ち周波数差取り出し手段で取り出された周波数差がゼロになる。これによりPLLがロックされ、電圧制御発振器1の出力周波数が設定周波数である520.0001MHzにロックされる。なおループフィルタ8はこの例では完全積分機能を持たせているため、正の直流電圧に収束することになる。またシミュレーションでは、電圧制御発振器1の動作をスタートさせてから、PLLがロックされるに至るまでの時間はおよそ150msecであった。

Further, the output frequency of the voltage controlled

上述の実施の形態によれば、電圧制御発振器1からの出力周波数が小さくて設定周波数に対して大きな開きがある間は、第1の定数を積分回路部102により積分して電圧制御発振器1の制御電圧として出力することで前記出力周波数を高めている。そしてまたPLLがロックされた後、ループフィルタ8からの制御電圧を監視し、この制御電圧が予め設定された範囲から外れたときには、当該範囲に収まるように、第2の定数を積分回路部102により積分して周波数引き込み用の電圧として結合器11に出力している。従って周波数の引き込み範囲が広く、電圧制御発振部の周波数にばらつきがあったり、温度特性などにより周波数が変化しても周波数の引き込みを行うことができるので、安定した動作が得られる。

According to the above-described embodiment, while the output frequency from the voltage controlled

また本発明が採用している周波数シンセサイザの本体の制御方式によれば次のような効果がある。電圧制御発振器1の出力周波数に応じた速度(周波数)で回転するベクトルを取り出し、このベクトルの周波数と出力周波数が設定周波数になったときのベクトルの周波数との差分を取り出して電圧制御発振器1にフィードバックしてPLLを形成しているので、広い周波数帯域に亘って細かな周波数設定を低ノイズで行うことができる。そして周波数差を取り出すにあたって、粗い周波数設定で逆回転する逆ベクトルを用いてベクトルの速度を落とし込み、その微速ベクトルの速度を検出してその検出値と予め計算しておいて微調整分とを付き合わせてその差分を取り出すようにしている。従って既述のようにデータ量を抑えかつ簡単な演算によりベクトルの周波数を検出することができ、従ってメモリ容量が小さくかつ演算の負荷が小さい周波数シンセサイザを提供できる。

Further, according to the control method of the main body of the frequency synthesizer adopted by the present invention, the following effects are obtained. A vector that rotates at a speed (frequency) corresponding to the output frequency of the voltage controlled

なお分周比Nの決め方は、電圧制御発振器1の出力周波数の設定値をNで割ったときに、A/D変換部3で用いる基準クロック信号の周波数とベクトル取り出し手段で用いられるω0/2πとの差に最も近い周波数となるように決めることに限定されるものではない。

The frequency division ratio N is determined by dividing the set value of the output frequency of the voltage controlled

また本発明では、2つのD/A変換部80及び104の各出力を加算した出力が電圧制御発振器1の制御電圧となるが、その構成としては、先の実施の形態のように結合器11を設ける代わりに、図13に示すような2ポートタイプの電圧制御発振器12を用い、D/A変換部80の出力及びD/A変換部104の出力104のを夫々ポート12a及び12bに入力するようにしてもよい。

In the present invention, the output obtained by adding the outputs of the two D /

他の発明の実施の形態について説明する。この実施の形態は、先の実施の形態において、スイッチ部101をaに切り替えた後、PLLロックするときの周波数引き込み手段におけるD/A変換器104について数ビット分だけオフセットをかけるようにしている。この点について詳述する。

Another embodiment of the invention will be described. In this embodiment, after the switch unit 101 is switched to a in the previous embodiment, an offset of several bits is applied to the D /

帰還手段に含まれるD/A変換器80が図14に示すようにラダー抵抗形の場合、内部のスイッチの切り替えによりグリッチノイズが発生し、同時に切り替わるスイッチ数が多くなる程、ノイズ量が増加する。従ってD/A変換器80の入力値がフルレンジの中心値を横切る場合において、同時スイッチングするスイッチ数が最大になり、ノイズ発生量も最大になる。フルレンジの中心値を横切るとは、図14に示す8ビット用の場合例えば「01111111」から「10000000」に切り替わるときである。特に上述の実施の形態のように、大まかな周波数の決定を周波数引き込み手段(スイッチ101からD/A変換器104の部分)により行い、D/A変換器80内に例えばPWM制御を組み込んで細かな諧調表現を行う場合には、周波数引き込み手段のD/A変換器104の設定値を中心付近に設定すると、D/A変換器80がフルレンジの中心値付近で高速にスイッチングする確率が高くなるおそれがある。なおPWM制御を組み込むとは

、入力値であるディジタル値に対応するデューティ比のパルス列がサンプリングのタイミング毎に出力され、これを平滑して制御電圧として出力するという意味である。そしてD/A変換器により細かな諧調表現を行うと、出力変化が小さいのでグリッチノイズが相対的に目立つ結果となる。

When the D /

図15は、電圧制御発振部1の制御電圧と出力周波数との関係を示す特性図であり、黒丸は出力周波数が設定周波数fsに一致するようにPLLロックするときのD/A変換器80の出力電圧である。つまりこの場合、D/A変換器80は内部のPWM信号のデューティ比が50%のときにこの電圧Vsが得られるように設定される。従ってD/A変換器80のフルレンジAD1の中心が黒丸の位置になってしまう。

FIG. 15 is a characteristic diagram showing the relationship between the control voltage of the voltage controlled

そこで、この実施の形態では、PLLロックするときの周波数引き込み手段のD/A変換器104について、設定可能な制御電圧の中で、出力周波数が設定周波数に最も近くなる制御電圧よりも、調整可能な周波数刻みの整数倍に対応する分だけずれた値に設定する(オフセットをかける)ようにする。例えばD/A変換器80のフルレンジに対応する周波数可変量が例えば4.5MHzであり、また周波数引き込み手段のD/A変換器104の1ビットあたりの周波数変化量が約750kHzであるとすると、単純計算では、D/A変換器104を最大±3ビット分オフセットすることができる。

Therefore, in this embodiment, the D /

このようにすれば、図15に示すようにD/A変換器80のフルレンジがAD1からAD2に変わるので、出力周波数が設定周波数fsに一致するときのD/A変換器80の出力値がフルレンジの中心から変位する。この結果、D/A変換器80がフルレンジの中心値付近で高速にスイッチングする確率が低くなり、グリッチノイズを低減できる。

In this way, as shown in FIG. 15, the full range of the D /

1 電圧制御発振器

11 結合器

2 分周器

3 A/D変換部

31 基準クロック発生部

4 キャリアリムーブ

5 逆ベクトル演算部

6 パラメータ出力部

71 位相の時間差検出部

72 加算部

73 位相差の累積加算部

8 ループフィルタ

80 D/A

101 スイッチ

102 積分回路部

104 D/A変換器

105 動作制御部

1

101 switch

102 integration circuit unit 104 D /

Claims (12)

前記周波数信号を電圧制御発振部の設定周波数に応じて1/N(Nは整数)に分周する分周手段と、

前記電圧制御発振部の出力周波数の1/Nに相当する周波数の正弦波信号を基準クロック信号に基づいてサンプリングしてそのサンプリング値をディジタル信号として出力するアナログ/ディジタル変換部と、

このアナログ/ディジタル変換部からの出力信号に対応する周波数信号に対して、周波数がω0/2πの正弦波信号のディジタル信号による直交検波を行い、当該周波数信号の周波数とω0/2πとの周波数差に相当する周波数で回転するベクトルを複素表示したときの実数部分及び虚数部分を取り出すベクトル取り出し手段と、

前記電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数を計算するパラメータ出力部と、

前記ベクトルの周波数と前記パラメータ出力部にて計算された周波数との差分を取り出す周波数差取り出し手段と、

この周波数差取り出し手段により取り出された周波数差に対応する電圧信号を積分してディジタル/アナログ変換部を介して制御電圧として前記電圧制御発振部に帰還する手段と、

A)装置の運転開始時に、電圧制御発振部からの出力周波数が小さすぎることに起因して周波数差取り出し手段から電圧信号が得られない間は、第1の定数を積分回路部により積分した立ち上げ用の電圧を電圧制御発振部の制御電圧として出力し、

B)PLLがロックされた後、前記帰還する手段からの制御電圧が予め設定された範囲から外れたときには、当該範囲に収まるように、第1の定数よりも小さく設定された第2の定数を積分回路部により積分した周波数引き込み用の電圧を出力し、

C)前記帰還する手段からの制御電圧が予め設定された範囲に収まった後には、前記積分動作を停止する

周波数引き込み手段と、を備え、

前記電圧制御発振部の制御電圧は、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧との加算値であり、

電圧制御発振部、ベクトル取り出し手段、及び前記電圧信号を電圧制御発振部に帰還する帰還手段によりPLLが形成され、PLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整されることを特徴とする周波数シンセサイザ。 A voltage-controlled oscillator that oscillates a frequency signal having a frequency corresponding to the supplied voltage;

Frequency dividing means for dividing the frequency signal into 1 / N (N is an integer) according to the set frequency of the voltage controlled oscillation unit;

An analog / digital converter that samples a sine wave signal having a frequency corresponding to 1 / N of the output frequency of the voltage-controlled oscillator based on a reference clock signal and outputs the sampled value as a digital signal;

The frequency signal corresponding to the output signal from the analog / digital converter is subjected to quadrature detection using a digital signal of a sine wave signal having a frequency of ω0 / 2π, and the frequency difference between the frequency signal and ω0 / 2π is detected. Vector extracting means for extracting a real part and an imaginary part when a vector rotating at a frequency corresponding to

A parameter output unit for calculating the frequency of the vector when the output frequency of the voltage controlled oscillation unit reaches a set value;

A frequency difference extracting means for extracting a difference between the frequency of the vector and the frequency calculated by the parameter output unit;

Means for integrating a voltage signal corresponding to the frequency difference extracted by the frequency difference extracting means and feeding it back to the voltage controlled oscillator as a control voltage via a digital / analog converter;

A) At the start of the operation of the apparatus, while the voltage signal cannot be obtained from the frequency difference extracting means due to the output frequency from the voltage controlled oscillator being too low, the first constant is integrated by the integrating circuit. The voltage for raising is output as the control voltage of the voltage controlled oscillator,

B) After the PLL is locked, when the control voltage from the means for returning deviates from a preset range, a second constant set smaller than the first constant is set so as to fall within the range. Output the frequency pull-in voltage integrated by the integration circuit ,

C) Frequency pulling means for stopping the integration operation after the control voltage from the feedback means falls within a preset range, and

The control voltage of the voltage controlled oscillating unit is an added value of the control voltage from the feedback means and the control voltage from the frequency pulling means,

A PLL is formed by the voltage controlled oscillation unit, the vector extracting unit, and the feedback unit that feeds back the voltage signal to the voltage controlled oscillation unit. When the PLL is locked, the output frequency of the voltage controlled oscillation unit is adjusted to the set frequency. This is a frequency synthesizer.

前記周波数信号を電圧制御発振部の設定周波数に応じて1/N(Nは整数)に分周する分周手段と、

前記電圧制御発振部の出力周波数の1/Nに相当する周波数の正弦波信号を基準クロック信号に基づいてサンプリングしてそのサンプリング値をディジタル信号として出力するアナログ/ディジタル変換部と、

このアナログ/ディジタル変換部からの出力信号に対応する周波数信号に対して、周波数がω0/2πの正弦波信号のディジタル信号による直交検波を行い、当該周波数信号の周波数とω0/2πとの周波数差に相当する周波数で回転するベクトルを複素表示したときの実数部分及び虚数部分を取り出すベクトル取り出し手段と、

前記電圧制御発振部の出力周波数が設定値になったときの前記ベクトルの周波数を計算するパラメータ出力部と、

前記ベクトルの周波数と前記パラメータ出力部にて計算された周波数との差分を取り出す周波数差取り出し手段と、

この周波数差取り出し手段により取り出された周波数差に対応する電圧信号を積分してディジタル/アナログ変換部を介して制御電圧として前記電圧制御発振部に帰還する手段と、

周波数引き込み手段と、を備え、

前記周波数引き込み手段は、

A)装置の運転開始時に、電圧制御発振部からの出力周波数が小さすぎることに起因して周波数差取り出し手段から電圧信号が得られない間は、立ち上げ用の電圧を電圧制御発振部の制御電圧として出力し、

B)周波数差取り出し手段から電圧信号が出力された後において、当該電圧信号を積分回路部により積分して前記帰還手段より大きい周波数刻みでアナログ信号に変換し、このアナログ信号を電圧制御発振部の制御電圧として出力し、

C)設定周波数と電圧制御発振部からの出力周波数との周波数差が予め設定された範囲に収まった後には、前記積分回路部の積分動作を停止して、前記周波数引き込み手段からの制御電圧を固定値とし、

D)帰還手段におけるディジタル/アナログ変換部の同時スイッチングを減らしてグリッチノイズを低減するために、前記固定値は、前記周波数引き込み手段におけるディジタル/アナログ変換部が設定可能な制御電圧の中で、出力周波数が設定周波数に最も近くなる制御電圧よりも、調整可能な周波数刻みの整数倍に対応する分だけずれた値に設定され、

前記電圧制御発振部、ベクトル取り出し手段、及び前記電圧信号を電圧制御発振部に帰還する帰還手段によりPLLが形成され、PLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整され、

前記電圧制御発振部の制御電圧は、前記帰還手段からの制御電圧と、前記周波数引き込み手段からの制御電圧の加算値であることを特徴とする周波数シンセサイザ。 A voltage-controlled oscillator that oscillates a frequency signal having a frequency corresponding to the supplied voltage;

Frequency dividing means for dividing the frequency signal into 1 / N (N is an integer) according to the set frequency of the voltage controlled oscillation unit;

An analog / digital converter that samples a sine wave signal having a frequency corresponding to 1 / N of the output frequency of the voltage-controlled oscillator based on a reference clock signal and outputs the sampled value as a digital signal;

The frequency signal corresponding to the output signal from the analog / digital converter is subjected to quadrature detection using a digital signal of a sine wave signal having a frequency of ω0 / 2π, and the frequency difference between the frequency signal and ω0 / 2π is detected. Vector extracting means for extracting a real part and an imaginary part when a vector rotating at a frequency corresponding to

A parameter output unit for calculating the frequency of the vector when the output frequency of the voltage controlled oscillation unit reaches a set value;

A frequency difference extracting means for extracting a difference between the frequency of the vector and the frequency calculated by the parameter output unit;

Means for integrating a voltage signal corresponding to the frequency difference extracted by the frequency difference extracting means and feeding it back to the voltage controlled oscillator as a control voltage via a digital / analog converter;

A frequency pulling means,

The frequency pulling means is

A) At the start of operation of the apparatus, while the voltage signal cannot be obtained from the frequency difference extracting means due to the output frequency from the voltage controlled oscillator being too small, the voltage for starting up is controlled by the voltage controlled oscillator. Output as voltage,

B) After the voltage signal is output from the frequency difference extracting means, the voltage signal is integrated by the integrating circuit section and converted into an analog signal at a frequency step larger than that of the feedback means, and this analog signal is converted into the voltage controlled oscillator section. Output as control voltage,

C) After the frequency difference between the set frequency and the output frequency from the voltage controlled oscillation unit falls within a preset range, the integration operation of the integration circuit unit is stopped, and the control voltage from the frequency pulling means is A fixed value,

D) In order to reduce glitch noise by reducing simultaneous switching of the digital / analog converter in the feedback means, the fixed value is output within a control voltage that can be set by the digital / analog converter in the frequency pull-in means. The frequency is set to a value that deviates from the control voltage closest to the set frequency by an amount corresponding to an integral multiple of the adjustable frequency increment.

A PLL is formed by the voltage controlled oscillation unit, the vector extracting unit, and a feedback unit that feeds back the voltage signal to the voltage controlled oscillation unit. When the PLL is locked, the output frequency of the voltage controlled oscillation unit is adjusted to a set frequency. ,

The frequency synthesizer according to claim 1, wherein the control voltage of the voltage controlled oscillator is an added value of the control voltage from the feedback means and the control voltage from the frequency pulling means.

前記周波数差取り出し手段は、前記ベクトル取り出し手段により得られた前記ベクトルに、周波数n・faで逆回転する逆ベクトルを乗算して、前記ベクトルの周波数から逆ベクトルの周波数を差し引いた周波数の微速ベクトルを取り出す手段と、前記微速ベクトルの周波数を、当該微速ベクトルの各サンプリング時の実数部分及び虚数部分の値から求める微速ベクトルの微速検出手段と、この微速検出手段で検出された微速ベクトルの周波数と周波数m・fbとの差に相当する信号を出力する手段と、を備えていることを特徴とする請求項1ないし7のいずれか一つに記載の周波数シンセサイザ。 The parameter output unit has a frequency n · fa (n) that is closest to the frequency of the vector when the output frequency of the voltage-controlled oscillation unit reaches a set value among frequencies that are integral multiples of the frequency increment fa for coarse adjustment. And an integer multiple of the frequency increment fb for fine adjustment smaller than the frequency increment fa, and the frequency of the vector when the output frequency of the voltage controlled oscillation unit becomes a set value and the frequency n · frequency m · fb (m is an integer) closest to the difference from fa,

The frequency difference extraction means multiplies the vector obtained by the vector extraction means by an inverse vector that rotates in reverse at a frequency n · fa, and subtracts the frequency of the inverse vector from the frequency of the vector. Means for taking out the frequency of the slow vector, a slow speed detecting means for the slow vector obtained from the values of the real part and imaginary part at the time of each sampling of the slow vector, and the frequency of the slow vector detected by the slow speed detecting means, The frequency synthesizer according to claim 1, further comprising: means for outputting a signal corresponding to a difference between the frequency m · fb.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007065883A JP4713525B2 (en) | 2006-03-31 | 2007-03-14 | Frequency synthesizer |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006100935 | 2006-03-31 | ||

| JP2006100935 | 2006-03-31 | ||

| JP2007065883A JP4713525B2 (en) | 2006-03-31 | 2007-03-14 | Frequency synthesizer |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007295537A JP2007295537A (en) | 2007-11-08 |

| JP2007295537A5 JP2007295537A5 (en) | 2010-12-24 |

| JP4713525B2 true JP4713525B2 (en) | 2011-06-29 |

Family

ID=38765658

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007065883A Active JP4713525B2 (en) | 2006-03-31 | 2007-03-14 | Frequency synthesizer |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4713525B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5066466B2 (en) * | 2008-03-12 | 2012-11-07 | 日本電波工業株式会社 | Frequency synthesizer |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002084189A (en) * | 2000-03-21 | 2002-03-22 | Ntt Electornics Corp | Phase synchronization circuit |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04101515A (en) * | 1990-08-21 | 1992-04-03 | Fujitsu Ltd | Control circuit for voltage control oscillator |

| JPH0786925A (en) * | 1993-06-30 | 1995-03-31 | Nec Corp | Frequency controller |

| JP2616701B2 (en) * | 1994-06-29 | 1997-06-04 | 日本電気株式会社 | High-speed pull-in control circuit for clock-dependent synchronizer. |

-

2007

- 2007-03-14 JP JP2007065883A patent/JP4713525B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002084189A (en) * | 2000-03-21 | 2002-03-22 | Ntt Electornics Corp | Phase synchronization circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007295537A (en) | 2007-11-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100995173B1 (en) | Frequency synthesizer | |

| US6891413B2 (en) | Periodic signal controller | |

| JP4397363B2 (en) | Frequency synthesizer | |

| JP4713525B2 (en) | Frequency synthesizer | |

| JP5066466B2 (en) | Frequency synthesizer | |

| JP4299352B2 (en) | Digital processing equipment | |

| CN101416395B (en) | Digital processing apparatus | |

| JP5189436B2 (en) | Frequency synthesizer | |

| WO2007114498A1 (en) | Pll device | |

| JP4874151B2 (en) | Digital processing apparatus and frequency synthesizer | |

| JP6146054B2 (en) | 3-phase rectifier | |

| WO2008126168A1 (en) | Frequency synthesizer | |

| Krieger et al. | Frequency locked phase estimation under harmonically distorted conditions | |

| KR101250571B1 (en) | Frequency synthesizer | |

| Patel et al. | COMPARATIVE ANALYSIS OF DIFFERENT PLL SYNTHESIS TECHNIQUES FOR COMMUNICATION SYSTEM. | |

| BRPI0722377B1 (en) | FREQUENCY SYNTHESIZER |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090227 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090227 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101110 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20101110 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110315 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110324 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4713525 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140401 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |