JP4574821B2 - Semiconductor device and thin film - Google Patents

Semiconductor device and thin film Download PDFInfo

- Publication number

- JP4574821B2 JP4574821B2 JP2000278617A JP2000278617A JP4574821B2 JP 4574821 B2 JP4574821 B2 JP 4574821B2 JP 2000278617 A JP2000278617 A JP 2000278617A JP 2000278617 A JP2000278617 A JP 2000278617A JP 4574821 B2 JP4574821 B2 JP 4574821B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- interlayer insulating

- thin film

- semiconductor device

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、半導体装置及び薄膜に関するもので、特に、多層配線構造の形成における低誘電率層間絶縁膜を有する半導体装置に関するものである。

【0002】

【従来の技術】

従来、多数のトランジスタを1チップに集積し、その集積度を向上させて半導体回路を作製することにより、高機能化が実現されてきた。この半導体集積回路、いわゆるULSIは、トランジスタの微細化技術の開発により進められてきた。しかし、設計寸法が0.25[μm]以下に入ると、配線長の増大から配線遅延がトランジスタの特性であるゲート遅延を上回るようになり、配線の抵抗成分と容量成分とによる遅延の低減、つまり配線のRC時定数の低減を考えることが必要となる。

【0003】

このために、配線用材料はアルミニウム(比抵抗3[μΩcm])から銅(比抵抗2[μΩcm])への変更が試みられ、配線金属の層間絶縁膜もSiO2(比誘電率κ=4)から他の低誘電率を有する材料の導入が検討されている。SiO2に代わる次世代の無機層間絶縁膜材料として、これまでに窒化ホウ素、窒化ホウ素珪素、窒化酸素ホウ素珪素等が検討され、また、有機材料の導入も考えられている。

【0004】

【発明が解決しようとする課題】

次世代の高機能ULSIを実現するためには、配線遅延を低減することが不可欠となる。このため、配線のRC時定数の低減を考えることが必要であり、従来、配線の層間絶縁膜として使用されているSiO2薄膜に代わる低誘電率を有する材料の導入が重要となる。材料の熱的安定性等を考慮すると、有機材料に優る窒化ホウ素などの無機材料の使用が望まれる。

【0005】

窒化ホウ素はSiO2より低誘電率を有し、化学気相成長法やイオンプレーティング法等で合成できることが知られている。しかし、作製された窒化ホウ素膜が水分と反応しやすいことや、薄膜内に蓄積される応力のためにクラックが発生したり、基板材料から剥離するという問題がある。この結果、半導体集積回路の作製プロセスに導入するためには、これらの課題を解決しなければならない。

【0006】

本発明は、前記課題を解決し、ホウ素、炭素、窒素を含有する材料を配線の層間絶縁膜に用いて、高性能半導体装置を提供することを目的とする。

【0007】

前記課題を解決するために、請求項1に記載された発明は、半導体素子の存在する基板上で、ホウ素炭素窒素を主要元素とする絶縁層を介して配線金属が形成され、前記絶縁層内で六方晶の結晶部分とアモルファス部分が混在していることを特徴とする半導体装置である。

【0011】

請求項2に記載された本発明では、請求項1に記載の半導体装置において、前記絶縁層にシリコン、酸素、イオウ、水素、フッ素、塩素の元素が添加されたことを特徴とする。

【0012】

請求項3に記載された本発明では、請求項1又は2に記載の半導体装置において、前記絶縁層と前記配線金属との間に窒化ホウ素、炭化ホウ素以外の窒素化合物層を有することを特徴とする。

【0014】

請求項4に記載された本発明は、前記絶縁層を、それ以外の絶縁層と共に2層以上の構造にして、配線金属間に用いることを特徴とする請求項1〜3のいずれか1項に記載の半導体装置である。

【0015】

請求項5に記載された本発明は、前記絶縁層を、電界効果トランジスタのソースとゲートとの間、および、ゲートとドレインとの間の活性層上に用いることを特徴とする請求項1〜3のいずれか1項に記載の半導体装置である。

請求項6に記載された本発明は、請求項1〜5に記載の半導体装置に用いた前記絶縁層はイオウが添加されたホウ素炭素窒素膜であることを特徴とする薄膜である。

【0016】

本発明の半導体装置は、ホウ素、炭素、窒素の少なくとも1元素を主成分とする薄膜を配線金属間の層間絶縁膜として用いて、配線のRC時定数の低減を図る。絶縁膜内の原子の結合構造や組成比の変化によって、絶縁膜のクラックや剥離を防止して、付着性を向上させ、性能の向上が図られている。

【0017】

【発明の実施の形態】

次に、本発明の実施形態について説明する。ホウ素、炭素、窒素を主要成分とした、本発明に関する材料を配線の層間絶縁膜に用いて、配線遅延の問題を解決することにより、次世代高性能ULSIが作製できる。そして、本発明は、コンピューターをはじめ、それを中心とした高性能情報処理装置、通信装置、制御装置等の様々な用途にキーデバイスとして応用できる。

【0018】

【実施例】

以下に、本発明の半導体装置の実施例について具体的に説明する。

【0019】

[実施例1]

図1は、本発明にかかる半導体装置の実施例1を示す断面図である。実施例1の半導体装置は、シリコン基板1、ゲート2、コンタクト3、酸化膜4、絶縁層としての層間絶縁膜5A〜5C、配線金属としての金属6A〜6Fおよびパシベーション膜7で構成される。

【0020】

シリコン基板1は、p型のシリコン半導体基板である。ゲート2およびコンタクト3からなるMOSFETが半導体素子として設けられ、酸化膜4の形成により素子分離されている。なお、ゲート2は、SiO2膜2Aを介してシリコン基板1に設けられている。

【0021】

多層配線のため、層間絶縁膜5Aが作製された後、フォトリソグラフィー工程を用いて、層間絶縁膜5Aが部分的にエッチング除去され、層間絶縁膜5Aに配線用金属6A、6Bが形成される。さらに、第2層目、第3層目である層間絶縁膜5B、5Cと、配線用金属6C〜6Fとが形成された後、パシベーション膜7が層間絶縁膜5Cの表面に設けられる。

【0022】

この構成の半導体装置を次に示す手順で作製する。つまり、図2(a)に示すp型のシリコン基板1の表面上に、図2(b)に示すように、熱酸化法を用いた従来のプロセスにより、ゲート2、SiO2膜2Aおよびコンタクト3からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜4を形成して、素子分離行う。

【0023】

次に、本発明の層間絶縁膜5Aとして、図2(c)に示すように、プラズマアシスト化学気相成長法によって窒化ホウ素薄膜を形成する。基板温度を390[℃]に保ち、窒素ガスをリアクターへ導入して、窒素プラズマを生成し、三塩化ホウ素ガスを分解して、窒化ホウ素薄膜を合成する。圧力は0.6[Torr]であり、シリコン基板1に150[V]の負バイアスを印加して作製する。その結果、図3に示すように、5[nm]程度の六方晶窒化ホウ素結晶5A1とアモルファス領域5A2とが混在する薄膜が、層間絶縁膜5Aとして得られる。六方晶窒化ホウ素結晶5A1は、ホウ素、窒素の2元素を主要元素とする低誘電率材料である。

【0024】

層間絶縁膜5Aにフォトリソグラフィー工程でパターニングし、三塩化ホウ素と窒素ガスとを用いた反応性イオンエッチング法により、層間絶縁膜5Aを部分的にエッチング除去する。その後、配線用金属6A、6Bとしてメッキ法により銅薄膜を形成し、化学機械研磨により平坦化する(図2(c))。

【0025】

この層間絶縁膜の形成と配線用金属の形成とを繰り返し行い、層間絶縁膜5B、5Cと配線用金属6C〜6Fとを形成し、最後にパシべーション膜7を付ける。

【0026】

層間絶縁膜5A〜5Cとして用いる薄膜を、同じ合成条件で金属基板上に作製し、その上に金属電極を形成して、薄膜の誘電率を評価したところ、比誘電率κ=2.5という値が得られた。この値は、従来のSiO2膜の比誘電率κ=4と比較して非常に低く、また、電気抵抗率も1010[Ωcm]の高い値が得られた。これによって、配線遅延を低減することができる。

【0027】

つまり、低誘電率絶縁体薄膜である層間絶縁膜5A〜5Cを、MOSFETが製作されているシリコン基板1と1層目の配線金属間およびその上の配線金属間に用いて、配線遅延を改善することができる。

【0028】

また、層間絶縁膜5A〜5Cには、六方晶窒化ホウ素結晶5A1とアモルファス領域5A2とが混在するので、剥離やクラックの発生を防止して付着性を向上させることができる。

【0029】

実施例1では、粒子サイズが5[nm]程度の六方晶窒化ホウ素結晶5A1とアモルファス領域5A2とが同程度の割合で作製された薄膜を用いたが、結晶の粒子サイズおよびその占有割合はこれに限定されることはなく、結晶粒子と粒界とからなる多結晶薄膜も含まれる。また、結晶粒子サイズも数原子の結合のものまで含まれる。さらに、層間絶縁膜5A〜5C用の材料として、窒化ホウ素だけではなく、窒化ホウ素炭素、窒化炭素、炭化窒素を用いることができる。

【0030】

なお、前記内容の薄膜作成ができる条件であれば、前記薄膜作成条件に限定されることなく、前記とは異なった作成条件も使用可能である。

【0031】

[実施例2]

図4は、本発明にかかる半導体装置の実施例2を示す断面図である。実施例2の半導体装置は、シリコン基板11、ゲート12、コンタクト13、酸化膜14、層間絶縁膜15A〜15C、配線金属としての金属16A〜16Cおよびパシベーション膜17で構成される。

【0032】

シリコン基板11、ゲート12、コンタクト13、酸化膜14は、図1のシリコン基板1、ゲート2、コンタクト3および酸化膜4と同じであるので、それらの説明を省略する。ゲート12とシリコン基板11との間に設けられているSiO2膜12Aは、図1のSiO2膜2Aと同じであるので、その説明を省略する。

金属16A〜16Cおよびパシベーション膜17については、図1の金属6A〜6Fおよびパシベーション膜7と形状がそれぞれ異なるだけであるので、それらの説明を省略する。

【0033】

実施例2では、層間絶縁膜15A〜15Cの構造が実施例1と異なっている。

この点について、次に示す作成手順の説明の中で詳しく述べる。つまり、図5(a)に示すp型のシリコン基板11の表面上に、図5(b)に示すように、熱酸化法を用いた従来のプロセスにより、ゲート12、SiO2膜12Aおよびコンタクト13からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜14を形成して、素子分離を行う。

【0034】

次に、本発明の層間絶縁膜15Aとして、図5(c)に示すように、窒化ホウ素炭素薄膜500[nm]をプラズマアシスト化学気相成長法によって形成する。層間絶縁膜15Aにフォトリソグラフィー工程でパターニングし、反応性イオンエッチング法により、層間絶縁膜15Aを部分的にエッチング除去する。その後、配線用の金属16Aとして、メッキ法により銅薄膜を形成し、化学機械研磨により平坦化する。

【0035】

層間絶縁膜15Aを形成する場合、基板温度を390[℃]に保ち、窒素ガスをリアクターへ導入して、窒素プラズマを生成し、三塩化ホウ素ガスおよびメタンガスを導入し、分解して炭素を10[%]含んだ窒化ホウ素炭素薄膜を合成する。この際、圧力を0.6[Torr]に保持し、先ず、シリコン基板11に印加する負バイアスを0[V]として、薄膜を5[nm]作製する。その結果、図6に示すように、アモルファス薄膜15A1が得られる。引き続いて、150[V]の負バイアスを印加して、薄膜を500[nm]作製する。これによって、六方晶窒化ホウ素炭素多結晶薄膜15A2が得られる。

第1層目の配線の後、つまり、金属16Aの形成後、層間絶縁膜の形成と配線用金属の形成とを繰り返し行い、層間絶縁膜15B、15Cと金属16B、16Cとを形成し、最後にパシベーション膜17を付ける。

【0036】

2層のアモルファス薄膜15A1と六方晶窒化ホウ素炭素多結晶薄膜15A2を同じ合成条件で金属基板上に作製し、その上に金属電極を形成して、薄膜の誘電率を評価したところ、比誘電率κ=2.8という値が得られた。この値は、従来のSiO2膜の誘電率κ=4と比較して非常に低く、また、電気抵抗率も1010[Ωcm]の高い値が得られた。

【0037】

なお、実施例2では、炭素組成10[%]の層間絶縁膜を用いたが、炭素組成を変化させた絶縁体薄膜も用いることができる。

【0038】

[実施例3]

図7は、本発明にかかる半導体装置の実施例3を示す断面図である。実施例3の半導体装置は、シリコン基板21、ゲート22、コンタクト23、酸化膜24、層間絶縁膜25A〜25C、金属26A〜26C、パシベーション膜27で構成される。

【0039】

シリコン基板21、ゲート22、コンタクト23、酸化膜24は、図1のシリコン基板1、ゲート2、コンタクト3および酸化膜4と同じであるので、それらの説明を省略する。ゲート22とシリコン基板21との間に設けられているSiO2膜22Aは、図1のSiO2膜2Aと同じであるので、その説明を省略する。

金属26A〜26Cおよびパシベーション膜27については、図1の金属6A〜6Fおよびパシベーション膜7と形状がそれぞれ異なるだけであるので、それらの説明を省略する。

【0040】

実施例3では、層間絶縁膜25A〜25Cの構造が実施例1と異なっている。

この点について、次に示す作成手順の説明の中で詳しく述べる。つまり、図8(a)に示すp型のシリコン基板21の表面上に、図8(b)に示すように、熱酸化法を用いた従来プロセスにより、ゲート22、SiO2膜22Aおよびコンタクト23からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜24を形成して、素子分離を行う。

【0041】

次に、本発明の層間絶縁膜25Aとして、図8(c)に示すように、窒化ホウ素炭素薄膜500[nm]をプラズマアシスト化学気相成長法によって形成する。層間絶縁膜25Aにフォトリソグラフィー工程でパターニングし、反応性イオンエッチング法により、層間絶縁膜15Aを部分的にエッチング除去する。その後、配線用金属26Aとして、メッキ法により銅薄膜を形成し、化学機械研磨により平坦化する。

層間絶縁膜25Aを形成する場合、基板温度を390[℃]に保ち、圧力を0.6[Torr]に保持して、シリコン基板21に150[V]の負バイアスを印加する。窒素ガスをリアクターへ導入して窒素プラズマを生成し、先ず、三塩化ホウ素ガスおよびメタンガスを導入して分解し、図9に示すように、炭素を10[%]含んだ六方晶窒化ホウ素炭素薄膜25A1を10[nm]の厚さに合成する。その後、メタンガスの導入を止め、六方晶窒化ホウ素薄膜25A2を100[nm]堆積させる。この工程を4回繰り返し、六方晶窒化ホウ素炭素薄膜25A1および六方晶窒化ホウ素薄膜25A2をそれぞれ4層にし、計8層構成にする。

【0042】

層間絶縁膜25Aに金属26を形成し、層間絶縁膜25Aに配線を行う。配線の後、層間絶縁膜25Aと同じようにして、層間絶縁膜25B、25Cを形成し、配線用金属26B、26Cの形成を繰り返し行い、最後にパシベーション膜27を付ける。

【0043】

8層構成の層間絶縁膜25A〜25Cを同じ合成条件で金属基板上に作製し、その上に金属電極を形成して、薄膜の誘電率を評価したところ、誘電率κ=2.5という値が得られた。この値は、従来のSiO2膜の誘電率κ=4と比較して非常に低く、また、電気抵抗率も1010[Ωcm]の高い値が得られた。

【0044】

なお、実施例3では、層間絶縁膜25A〜25Cとして8層構造を作製したが、これに限定されることはない。また、炭素組成10[%]の層間絶縁膜25A〜25Cを用いたが、炭素組成を変化させた絶縁体薄膜も用いることができる。

【0045】

[実施例4]

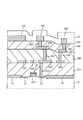

図10は、本発明にかかる半導体装置の実施例4を示す断面図である。実施例4の半導体装置は、シリコン基板31、ゲート32、コンタクト33、酸化膜34、絶縁層としての層間絶縁膜35A〜35C、配線金属としての金属36A〜36Fおよびパシベーション膜37で構成される。

【0046】

シリコン基板31、ゲート32、コンタクト33、酸化膜34、金属36A〜36Fおよびパシベーション膜37については、図1のシリコン基板1、ゲート2、コンタクト3および酸化膜4、金属6A〜6Fおよびパシベーション膜7と同じであるので、それらの説明を省略する。ゲート32とシリコン基板31との間に設けられているSiO2膜32Aは、図1のSiO2膜2Aと同じであるので、その説明を省略する。

【0047】

実施例4では、層間絶縁膜35A〜35Cの構造が実施例1と異なっている。

この点について、次に示す作成手順の説明の中で詳しく述べる。つまり、図11(a)に示すp型のシリコン基板31の表面上に、図11(b)に示すように、熱酸化法を用いた従来プロセスにより、ゲート32、SiO2膜32Aおよびコンタクト33からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜34を形成して、素子分離を行う。

【0048】

次に、本発明の層間絶縁膜35Aとして、図12に示すように、プラズマアシスト化学気相成長法によって、六方晶窒化ホウ素炭素結晶である窒化ホウ素炭素薄膜35A1、窒化ホウ素結晶である窒化ホウ素薄膜35A2、窒化ホウ素炭素薄膜35A3を順次形成する。窒化ホウ素炭素薄膜35A1、35A3は、ホウ素、炭素、窒素を主要元素とする低誘電率材料である。

【0049】

窒化ホウ素炭素薄膜35A1、窒化ホウ素薄膜35A2、窒化ホウ素炭素薄膜35A3の膜厚は、1:8:1の割合で作製する。基板温度を390[℃]に保ち、窒素ガスをリアクターへ導入して、窒素プラズマを生成し、三塩化ホウ素ガスを分解して、窒化ホウ素薄膜を合成する。また、窒化ホウ素炭素薄膜35A1の合成の場合には、メタンガスを窒素ガスと共に供給する。圧力は0.6[Torr]であり、基板に150[V]の負バイアスを印加して作製する。作製された窒素ホウ素炭素薄膜35A1の炭素組成比は0.2とする。その結果、5[nm]程度の窒化ホウ素炭素薄膜35A1または窒化ホウ素薄膜35A2とアモルファス領域が混在する薄膜が得られた。

層間絶縁膜35Aにフォトリソグラフィー工程でパターニングし、三塩化ホウ素と窒素ガスとを用いた反応性イオンエッチング法により、層間絶縁膜35Aを部分的にエッチング除去する。その後、配線用金属36A、36Bとしてメッキ法により銅薄膜を形成し、図11(c)に示すように、化学機械研磨により平坦化する。この層間絶縁膜の形成と配線用金属の形成とを繰り返し行い、層間絶縁膜35B、35Cと配線用金属36C〜36Fとを形成し、最後にパシベーション膜37を付ける。

【0050】

この層間絶縁膜35A〜35Cとして用いる薄膜を、同じ合成条件で金属基板上に作製し、その上に金属電極を形成して、薄膜の誘電率を評価したところ、比誘電率κ=2.8という値が得られた。この値は、従来のSiO2膜の比誘電率κ=4と比較して非常に低く、また、電気抵抗率も108[Ωcm]の高い値が得られた。これによって、配線遅延を低減することができる。

【0051】

また、層間絶縁膜35A〜35Cには、窒化ホウ素炭素薄膜35A1、窒化ホウ素薄膜35A2、窒化ホウ素炭素薄膜35A3が順次形成されているので、剥離やクラックの発生を防止して付着性を向上させることができる。

【0052】

なお、実施例4では、炭素組成比を0.2とした窒化ホウ素炭素薄膜35A1、35A3を用いたが、組成比はこれに限定されることはなく、また、窒化ホウ素薄膜35A2部分にも窒化ホウ素炭素薄膜、炭化ホウ素薄膜、窒化炭素薄膜なども用いることができる。粒子サイズが5[nm]程度の結晶部分とアモルファス領域とが同程度の割合で作製された薄膜を用いたが、結晶の粒子サイズおよびその占有割合はこれに限定されることはなく、結晶粒子と粒界からなる多結晶薄膜も含まれる。結晶粒子サイズも数原子の結合のものまで含まれる。

【0053】

前記内容の薄膜作成ができる条件であれば、前記薄膜作成条件に限定されることなく、前記とは異なった作成条件も使用可能である。

【0054】

[実施例5]

実施例5では、実施例1の層間絶縁膜5A〜5C、実施例2の層間絶縁膜15A〜15C、実施例3の層間絶縁膜25A〜25C、実施例4の層間絶縁膜35A〜35Cに、シリコン、酸素、イオウ、水素、フッ素、塩素等の元素の少なくとも1元素を添加する。元素の添加によって、誘電率の低下、耐吸湿性の向上など、絶縁体薄膜の諸特性を改善することができる。

【0055】

[実施例6]

図13は、本発明にかかる半導体装置の実施例6を示す断面図である。実施例6の半導体装置は、シリコン基板41、ゲート42、コンタクト43、酸化膜44、層間絶縁膜45A〜45C、窒素化合物層46A〜46C、金属47A〜47Cおよびパシベーション膜48で構成される。

【0056】

シリコン基板41は、p型のシリコン半導体基板である。ゲート42およびコンタクト43からなるMOSFETが半導体素子として設けられ、酸化膜44の形成により素子分離されている。なお、ゲート42は、SiO2膜42Aを介してシリコン基板41に設けられている。

【0057】

多層配線のため、層間絶縁膜45Aが作製された後、フォトリソグラフィー工程を用いて、層間絶縁膜45Aが部分的にエッチング除去され、層間絶縁膜45Aの上に窒素化合物層46Aを堆積させる。その後、配線用金属47Aが形成される。さらに、第2層目、第3層目である層間絶縁膜45B、45Cの配線が形成された後、パシベーション膜48が表面に設けられる。

【0058】

この構成の半導体装置を次に示す手順で作製した。つまり、図14(a)に示すp型のシリコン基板41の表面上に、図14(b)に示すように、熱酸化法を用いた従来プロセスにより、ゲート42、SiO2膜42Aおよびコンタクト43からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜44を形成して、素子分離を行う。

【0059】

次に、図14(c)に示すように、層間絶縁膜45Aとして窒化ホウ素炭素薄膜500[nm]をプラズマアシスト化学気相成長法によって形成する。層間絶縁膜45Aにフォトリソグラフィー工程でパターニングし、反応性イオンエッチング法により層間絶縁膜45Aを部分的にエッチング除去する。その後、窒素化合物層46AとしてTiN薄膜を電子ビーム蒸着法により100[nm]形成し、金属47Aとしてメッキ法により銅薄膜を作製して、銅およびTiNを化学機械研磨して平坦化する。

【0060】

本発明の層間絶縁膜45Aを形成する場合、基板温度を390[℃]に保ち、圧力を0.6[Torr]に保持して、シリコン基板41に150[V]の負バイアスを印加する。窒素ガスをリアクターへ導入して、窒素プラズマを生成し、三塩化ホウ素ガスおよびメタンガスを導入し、分解して炭素を10[%]含んだ六方晶窒化ホウ素炭素薄膜を500[nm]の厚さに合成する。第1層目の配線の後、再び層間絶縁膜45B、45Cを前記と同じ方法で形成し、窒素化合物層46B、46Cおよび配線用金属金属47B、47Cの形成を繰り返し行い、最後にパシベーション膜48を付ける。

【0061】

実施例6では、炭素組成10[%]の層間絶縁膜を用いたが、炭素組成を変化させた絶縁体薄膜も用いることができる。また、他の窒素化合物も用いることができる。

【0062】

[実施例7]

図15は、本発明にかかる半導体装置の実施例7を示す断面図である。実施例7の半導体装置は、シリコン基板51、ゲート52、コンタクト53、酸化膜54、第1層間絶縁膜55A〜55C、第2層間絶縁膜56A、56B、金属57A〜57Cおよびパシベーション膜58で構成される。

【0063】

シリコン基板51は、p型のシリコン半導体基板である。ゲート52およびコンタクト53からなるMOSFETが設けられ、酸化膜54の形成により素子分離されている。なお、ゲート52は、SiO2膜52Aを介してシリコン基板51に設けられている。

【0064】

多層配線のため、第1層間絶縁膜55Aが作製された後、フォトリソグラフィー工程を用いて、第1層間絶縁膜55Aが部分的にエッチング除去され、層間絶縁膜55Aの上に配線用金属57Aが形成される。さらに、第2層目、第3層目を作製する場合、第1層間絶縁膜膜55B、55Cおよび第2層間絶縁膜56A、56Bを設け、配線用金属57B、57Cが形成された後、パシベーション膜58が表面に設けられる。

【0065】

この構成の半導体装置を次に示す手順で作製する。つまり、図16(a)に示すp型のシリコン基板51の表面上に、図16(b)に示すように、熱酸化法を用いた従来プロセスにより、ゲート52、SiO2膜52Aおよびコンタクト53からなるMOSFETを作製し、LOCOSプロセスを用いて、酸化膜54を形成して、素子分離を行う。

【0066】

次に、図16(c)に示すように、第1層間絶縁膜55Aとして、プラズマアシスト化学気相成長法によってSiO2薄膜を500[nm]形成する。第1層間絶縁膜55Aにフォトリソグラフィー工程でパターニングし、反応性イオンエッチング法により第1層間絶縁膜55Aを部分的にエッチング除去する。その後、配線用金属57Aとしてメッキ法により銅薄膜を形成し、化学機械研磨により平坦化する。

【0067】

次に、本発明の第2層間絶縁膜56Aとして、プラズマアシスト化学気相成長法によって、窒化ホウ素薄膜を200[nm]の厚さに形成する。基板温度を390[℃]に保ち、窒素ガスをリアクターヘ導入して、窒素プラズマを生成し、三塩化ホウ素ガスを分解して、窒化ホウ素薄膜を合成する。この際、炭素添加のためメタンを導入し、窒化ホウ素薄膜に炭素を10[%]含んだ薄膜を作製する。圧力は0.6[Torr]、シリコン基板51に150[V]の負バイアスを印加して作製する。その結果、5[nm]程度の六方晶窒化ホウ素結晶とアモルファス領域とが混在する薄膜が、第2層間絶縁膜56Aとして得られた。

【0068】

引き続いて、第1層間絶縁膜55Bを堆積して、第2層間絶縁膜56Bを200[nm]堆積する。この後、再びフォトリソグラフィー工程でパターニングし、反応性イオンエッチング法により第1層間絶縁膜55Bおよび第2層間絶縁膜56Bを部分的にエッチング除去し、その後、配線用金属57Bとしてメッキ法により銅薄膜を形成し、化学機械研磨により平坦化する。

【0069】

層間絶縁膜および配線用金属の形成を繰り返し行い、第1層間絶縁膜55Cおよび金属57Cを設ける。そして、最後にパシベーション膜58を付ける。

【0070】

この2層の層間絶縁膜を同じ合成条件で金属基板上に作製し、その上に金属電極を形成して、薄膜の誘電率を評価したところ、誘電率κ=2.8という値が得られた。この値は、従来のSiO2膜の誘電率κ=4と比較して非常に低く、また、電気抵抗率も1010[Ωcm]の高い値が得られた。

【0071】

実施例7では、従来、SiO2とSiN薄膜で構成されている層間絶縁膜をSiO2と窒化ホウ素薄膜で構成したが、本発明の絶縁体薄膜と他の様々な絶縁体薄膜との2層または多層構造を作製することができる。絶縁体薄膜としてSiO2薄膜以外に、ポーラスSiO2薄膜やCF薄膜を始めとする有機物薄膜を用いることができ、2層または多層構造にすることにより、ポーラスSiO2や有機物薄膜の欠点を補うことができる。

【0072】

[実施例8]

図17は、本発明にかかる半導体装置の実施例8を示す断面図である。実施例8の半導体装置は、ガリウム砒素基板61、ガリウム砒素活性層62、ソース63、ドレイン64、ゲート65および絶縁層66で構成される。

【0073】

ガリウム砒素基板61は、半絶縁体基板である。ソース63とドレイン64としてオーミック電極が設けられ、ゲート65としてショットキー接合電極が設けられて、MESFETが作製される。ソース63とゲート65との間およびドレイン64とゲート65との間の、ガリウム砒素活性層62が露出した部分に、絶縁層66が設けられている。

【0074】

この構成の半導体装置を次に示す手順で作製する。つまり、図18(a)に示すように、ガリウム砒素基板61上にn型ガリウム砒素活性層62(電子濃度1×1017[cm-3]、厚さ1[μm])を有機金属気相合成法によって堆積させる。図18(b)に示すように、ソース63およびドレイン64となる電極をオーミック接触によって形成するために、電子ビーム蒸着法によりAuGeNiを500[nm]堆積させる。その後、420[℃]で5分間熱処理を行う。続いて、リセス構造を形成するため、ソース63とドレイン64の間でガリウム砒素活性層62を部分的に薄くする。最後にゲート65を作製する。

【0075】

ゲート65を形成するために、図18(c)に示すように、ソース63とドレイン64の間に先ず絶縁層66を500[nm]堆積させる。絶縁層66は、三塩化ホウ素、窒素およびメタンガスを材料ガスとして、プラズマアシスト気相合成法によって合成される。リセス部分で絶縁層66に0.3[μm]の幅のストライプ窓を三塩化ホウ素と窒素を用いた反応性イオンエッチングによって開ける。その後再び、フォトリソグラフィーによって、レジスト膜67を作製する。この上に、電子ビーム蒸着法によって、TiPtを堆積させ、リフトオフ工程を用いて、図10(d)に示すように、ゲート65を作製する。

【0076】

このように、本発明の絶縁体薄膜を用いて作製したガリウム砒素MESFETは、絶縁体薄膜としてSiNを用いて作製した素子に比べ、明らかに周波数特性の向上が見られた。

【0077】

つまり、本発明は、低誘電率を有する絶縁体薄膜に関するものであり、実施例1〜7までは、シリコン集積回路(LSI)への応用を示している。そして、実施例1〜7では、多層配線が行われるため、MOSFETが製作されているシリコンウエハーと1層目の配線金属間およびその上の配線金属間に低誘電率絶縁体薄膜を用い、配線遅延を改善できることを述べた。

【0078】

LSIの多層配線で起こる遅延現象による周波数特性の改善だけではなく、高周波で動作させる単体のトランジスタまたは多層配線を必要としない低集積回路においても、ゲート電極と活性層表面をカバーする絶縁体薄膜の間で同様の遅延現象が発生し、周波数特性に影響を及ぼす。このために、低誘電率絶縁体薄膜の導入は不可欠であり、本発明の材料を用いることにより、トランジスタの周波数特性の向上を図ることができる。

【0079】

実施例8では、本発明の絶縁体薄膜をガリウム砒素MESFETに用いたが、ガリウム砒素MESFET以外のインジウムリン系MESFETや窒化ガリウム系MESFETにも応用でき、同様の効果を達成することができる。また、実施例8では、本発明の絶縁体層のみを活性層上に有する場合を示したが、他の薄膜との2層または多層構造を形成して使用することもできる。

【0080】

また、実施例8では、リセス構造を有するMESFETを示したが、他のすべての構造のMESFETにおけるソース・ゲート間およびゲート・ドレイン間の活性層上に用いることができ、実施例8と同じ効果を達成することができる。

【0081】

【発明の効果】

以上説明したように、本発明は、ホウ素、炭素、窒素の少なくとも1元素を主要元素とする低誘電率材料を多層配線の層間絶縁膜として用い、絶縁層内の原子の結合構造や組成比の変化を導入することにより、剥離を防止して付着性を向上させ、配線遅延を低減した半導体装置の提供に効果的である。

【0082】

また、本発明の半導体装置をコンピューターを始めそれを中心とした高性能情報処理装置、通信装置、制御装置等のキーデバイスとして提供できることが可能である。

【図面の簡単な説明】

【図1】本発明の半導体装置の実施例1を示す断面図である。

【図2】実施例1の半導体装置の作製手順を説明するための説明図である。

【図3】実施例1の層間絶縁膜を示す断面図である。

【図4】本発明の半導体装置の実施例2を示す断面図である。

【図5】実施例2の半導体装置の作製手順を説明するための説明図である。

【図6】実施例2の層間絶縁膜を示す断面図である。

【図7】本発明の半導体装置の実施例3を示す断面図である。

【図8】実施例3の半導体装置の作製手順を説明するための説明図である。

【図9】実施例3の層間絶縁膜を示す断面図である。

【図10】本発明の半導体装置の実施例4を示す断面図である。

【図11】実施例4の半導体装置の作製手順を説明するための説明図である。

【図12】実施例4の層間絶縁膜を示す断面図である。

【図13】本発明の半導体装置の実施例6を示す断面図である。

【図14】実施例6の半導体装置の作製手順を説明するための説明図である。

【図15】本発明の半導体装置の実施例7を示す断面図である。

【図16】実施例7の半導体装置の作製手順を説明するための説明図である。

【図17】本発明の半導体装置の実施例8を示す断面図である。

【図18】実施例8の半導体装置の作製手順を説明するための説明図である。

【符号の説明】

1、11、21、31、41、51 シリコン基板

2、12、22、32、42、52 ゲート

2A、12A、22A、32A、42A、52A SiO2膜

3、13、23、33、43、53 コンタクト

4、14、24、34、44、54 酸化膜

5A〜5C、15A〜15C、25A〜25C、35A〜35C、45A〜45C 層間絶縁膜

5A1 六方晶窒化ホウ素結晶

5A2 アモルファス領域

6A〜6F、16A〜16C、26A〜26C、36A〜36F、47A〜47C、57A〜57C 金属

7、17、27、37、48、58 パシベーション膜

15A1 アモルファス薄膜

15A2 六方晶窒化ホウ素炭素多結晶薄膜

25A1 六方晶窒化ホウ素炭素薄膜

25A2 六方晶窒化ホウ素薄膜

35A1、35A3 窒化ホウ素炭素薄膜

35A2 窒化ホウ素薄膜

46A〜46C 窒素化合物層

55A〜55C 第1層間絶縁膜

56A、56B 第2層間絶縁膜

61 ガリウム砒素基板

62 ガリウム砒素活性層

63 ソース

64 ドレイン

65 ゲート

66 絶縁層[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor device. And thin film In particular, the present invention relates to a semiconductor device having a low dielectric constant interlayer insulating film in the formation of a multilayer wiring structure.

[0002]

[Prior art]

Conventionally, high functionality has been realized by integrating a large number of transistors on a single chip and improving the degree of integration to fabricate a semiconductor circuit. This semiconductor integrated circuit, so-called ULSI, has been advanced by the development of transistor miniaturization technology. However, when the design dimension enters 0.25 [μm] or less, the wiring delay increases from the gate delay which is a characteristic of the transistor due to the increase in the wiring length, and the delay due to the resistance component and the capacitance component of the wiring is reduced. In other words, it is necessary to consider reducing the RC time constant of the wiring.

[0003]

For this reason, the wiring material has been changed from aluminum (specific resistance 3 [μΩcm]) to copper (specific resistance 2 [μΩcm]), and the interlayer insulating film of the wiring metal is also made of SiO. 2 From the viewpoint of (relative permittivity κ = 4), introduction of other materials having a low permittivity is being studied. SiO 2 Boron nitride, boron nitride silicon, silicon boron oxynitride, etc. have been studied as next-generation inorganic interlayer insulating film materials to replace the above, and introduction of organic materials is also considered.

[0004]

[Problems to be solved by the invention]

In order to realize the next generation high-performance ULSI, it is indispensable to reduce the wiring delay. For this reason, it is necessary to consider the reduction of the RC time constant of the wiring. Conventionally, SiO used as an interlayer insulating film of the wiring 2 It is important to introduce a material having a low dielectric constant instead of a thin film. Considering the thermal stability of the material, it is desirable to use an inorganic material such as boron nitride, which is superior to the organic material.

[0005]

Boron nitride is SiO 2 It is known that it has a lower dielectric constant and can be synthesized by chemical vapor deposition or ion plating. However, there are problems that the produced boron nitride film is likely to react with moisture, cracks are generated due to stress accumulated in the thin film, and peeling from the substrate material. As a result, these problems must be solved in order to introduce the semiconductor integrated circuit into the manufacturing process.

[0006]

An object of the present invention is to solve the above-described problems and provide a high-performance semiconductor device using a material containing boron, carbon, and nitrogen as an interlayer insulating film of wiring.

[0007]

In order to solve the above-mentioned problem, the invention described in

[0011]

[0012]

[0014]

[0015]

Claim 5 The present invention described in Said Insulating layer is used on the active layer between the source and gate of the field effect transistor and between the gate and drain The method according to any one of

Claim 6 The present invention described in

[0016]

The semiconductor device of the present invention uses a thin film containing at least one element of boron, carbon, and nitrogen as a main component as an interlayer insulating film between wiring metals to reduce the RC time constant of the wiring. Changes in the bonding structure and composition ratio of atoms in the insulating film prevent cracking and peeling of the insulating film, improve adhesion, and improve performance.

[0017]

DETAILED DESCRIPTION OF THE INVENTION

Next, an embodiment of the present invention will be described. Next-generation high-performance ULSI can be manufactured by solving the problem of wiring delay by using a material related to the present invention, which mainly contains boron, carbon, and nitrogen, as an interlayer insulating film of wiring. The present invention can be applied as a key device for various uses such as a computer, a high-performance information processing apparatus, a communication apparatus, and a control apparatus centering on the computer.

[0018]

【Example】

Examples of the semiconductor device of the present invention will be specifically described below.

[0019]

[Example 1]

1 is a cross-sectional view showing a first embodiment of a semiconductor device according to the present invention. The semiconductor device according to the first embodiment includes a

[0020]

The

[0021]

After the

[0022]

The semiconductor device having this configuration is manufactured by the following procedure. That is, on the surface of the p-

[0023]

Next, as the

[0024]

The

[0025]

The formation of the interlayer insulating film and the wiring metal are repeatedly performed to form the

[0026]

A thin film used as the

[0027]

In other words, the

[0028]

The

[0029]

In Example 1, hexagonal

[0030]

In addition, as long as it is the conditions which can produce the said thin film, it is not limited to the said thin film production conditions, The production conditions different from the above can also be used.

[0031]

[Example 2]

FIG. 4 is a cross-sectional view showing a semiconductor device according to a second embodiment of the present invention. The semiconductor device according to the second embodiment includes a

[0032]

Since the

The

[0033]

In the second embodiment, the structure of the interlayer insulating

This point will be described in detail in the following description of the creation procedure. That is, on the surface of the p-

[0034]

Next, as an

[0035]

When the

After the first layer wiring, that is, after the formation of the

[0036]

Two layers of amorphous

[0037]

In Example 2, an interlayer insulating film having a carbon composition of 10% was used, but an insulator thin film having a changed carbon composition can also be used.

[0038]

[Example 3]

FIG. 7 is a sectional view showing Example 3 of the semiconductor device according to the present invention. The semiconductor device according to the third embodiment includes a

[0039]

Since the

The

[0040]

In the third embodiment, the structure of the interlayer insulating

This point will be described in detail in the following description of the creation procedure. That is, on the surface of the p-

[0041]

Next, as an

When the

[0042]

A metal 26 is formed on the

[0043]

When the interlayer insulating

[0044]

In Example 3, an eight-layer structure was fabricated as the

[0045]

[Example 4]

FIG. 10 is a sectional view showing a fourth embodiment of the semiconductor device according to the present invention. The semiconductor device of the fourth embodiment includes a

[0046]

Regarding the

[0047]

In the fourth embodiment, the structure of the interlayer insulating

This point will be described in detail in the following description of the creation procedure. That is, on the surface of the p-

[0048]

Next, as an

[0049]

Boron nitride carbon

The

[0050]

A thin film used as the

[0051]

Further, the boron nitride carbon

[0052]

In Example 4, boron nitride carbon

[0053]

As long as the thin film can be formed as described above, the present invention is not limited to the above-described thin film forming conditions, and other forming conditions can be used.

[0054]

[Example 5]

In Example 5, the

[0055]

[Example 6]

FIG. 13 is a sectional view showing a sixth embodiment of the semiconductor device according to the invention. The semiconductor device according to the sixth embodiment includes a

[0056]

The

[0057]

After the

[0058]

The semiconductor device having this configuration was manufactured by the following procedure. That is, on the surface of the p-

[0059]

Next, as shown in FIG. 14C, a boron nitride carbon thin film 500 [nm] is formed as an

[0060]

In the case of forming the

[0061]

In Example 6, an interlayer insulating film having a carbon composition of 10% was used, but an insulator thin film having a changed carbon composition can also be used. Other nitrogen compounds can also be used.

[0062]

[Example 7]

FIG. 15 is a sectional view showing a seventh embodiment of the semiconductor device according to the present invention. The semiconductor device according to the seventh embodiment includes a

[0063]

The

[0064]

For the multilayer wiring, after the first

[0065]

The semiconductor device having this configuration is manufactured by the following procedure. That is, on the surface of the p-

[0066]

Next, as shown in FIG. 16C, the first

[0067]

Next, as the second

[0068]

Subsequently, a first

[0069]

The interlayer insulating film and the wiring metal are repeatedly formed to provide the first

[0070]

When this two-layer interlayer insulating film was produced on a metal substrate under the same synthesis conditions, a metal electrode was formed thereon, and the dielectric constant of the thin film was evaluated, a value of dielectric constant κ = 2.8 was obtained. It was. This value is the same as conventional SiO 2 The dielectric constant κ of the film is very low compared to 4 and the electrical resistivity is 10 Ten A high value of [Ωcm] was obtained.

[0071]

In Example 7, conventionally, SiO 2 And an interlayer insulation film composed of SiN thin film 2 However, a two-layer or multilayer structure of the insulator thin film of the present invention and other various insulator thin films can be manufactured. SiO as an insulator thin film 2 In addition to thin films, porous SiO 2 Organic thin films such as thin films and CF thin films can be used, and

[0072]

[Example 8]

FIG. 17 is a sectional view showing Example 8 of the semiconductor device according to the present invention. The semiconductor device according to the eighth embodiment includes a

[0073]

The

[0074]

The semiconductor device having this configuration is manufactured by the following procedure. That is, as shown in FIG. 18A, an n-type gallium arsenide active layer 62 (

[0075]

In order to form the

[0076]

Thus, the gallium arsenide MESFET fabricated using the insulator thin film of the present invention clearly improved the frequency characteristics as compared with the device fabricated using SiN as the insulator thin film.

[0077]

That is, the present invention relates to an insulator thin film having a low dielectric constant, and Examples 1 to 7 show applications to silicon integrated circuits (LSIs). In Examples 1 to 7, since multilayer wiring is performed, a low dielectric constant insulator thin film is used between the silicon wafer on which the MOSFET is manufactured and the wiring metal on the first layer and between the wiring metals on the wiring. Stated that the delay can be improved.

[0078]

In addition to improving the frequency characteristics due to the delay phenomenon that occurs in the multilayer wiring of LSI, the insulating thin film that covers the gate electrode and the active layer surface also in a low integrated circuit that does not require a single transistor or multilayer wiring that operates at high frequency A similar delay phenomenon occurs between them, affecting the frequency characteristics. For this reason, it is indispensable to introduce a low dielectric constant insulator thin film, and the frequency characteristics of the transistor can be improved by using the material of the present invention.

[0079]

In Example 8, the insulator thin film of the present invention was used for a gallium arsenide MESFET, but it can also be applied to indium phosphide MESFETs and gallium nitride MESFETs other than gallium arsenide MESFETs, and the same effect can be achieved. Further, in Example 8, the case where only the insulator layer of the present invention is provided on the active layer is shown, but a two-layer or multilayer structure with another thin film can be formed and used.

[0080]

Further, although the MESFET having the recess structure is shown in the eighth embodiment, it can be used on the active layer between the source and the gate and between the gate and the drain in the MESFET having any other structure, and the same effect as the eighth embodiment. Can be achieved.

[0081]

【The invention's effect】

As described above, the present invention uses a low dielectric constant material containing at least one element of boron, carbon, and nitrogen as a main element as an interlayer insulating film of a multilayer wiring, and has an atomic bonding structure and composition ratio in the insulating layer. Introducing the change is effective in providing a semiconductor device that prevents peeling and improves adhesion and reduces wiring delay.

[0082]

In addition, the semiconductor device of the present invention can be provided as a key device such as a high-performance information processing device, a communication device, a control device, etc. mainly including a computer.

[Brief description of the drawings]

FIG. 1 is a cross-sectional view showing a first embodiment of a semiconductor device of the present invention.

FIG. 2 is an explanatory diagram for explaining a manufacturing procedure of the semiconductor device of Example 1;

3 is a cross-sectional view showing an interlayer insulating film of Example 1. FIG.

FIG. 4 is a cross-sectional view showing a second embodiment of the semiconductor device of the present invention.

5 is an explanatory diagram for explaining a manufacturing procedure of the semiconductor device of Example 2. FIG.

6 is a cross-sectional view showing an interlayer insulating film of Example 2. FIG.

FIG. 7 is a cross-sectional view showing a third embodiment of the semiconductor device of the present invention.

FIG. 8 is an explanatory diagram for explaining a manufacturing procedure of the semiconductor device of Example 3;

9 is a cross-sectional view showing an interlayer insulating film of Example 3. FIG.

FIG. 10 is a cross-sectional view showing a fourth embodiment of the semiconductor device of the present invention.

11 is an explanatory diagram for describing a manufacturing procedure of the semiconductor device of Example 4. FIG.

12 is a cross-sectional view showing an interlayer insulating film of Example 4. FIG.

13 is a cross-sectional view showing a sixth embodiment of the semiconductor device of the invention. FIG.

14 is an explanatory diagram for describing a manufacturing procedure of the semiconductor device of Example 6. FIG.

FIG. 15 is a cross-sectional view showing a seventh embodiment of the semiconductor device of the present invention.

16 is an explanatory diagram for describing a manufacturing procedure of the semiconductor device of Example 7. FIG.

FIG. 17 is a cross-sectional view showing a semiconductor device according to an eighth embodiment of the present invention.

18 is an explanatory diagram for describing a manufacturing procedure of the semiconductor device of Example 8. FIG.

[Explanation of symbols]

1, 11, 21, 31, 41, 51 Silicon substrate

2, 12, 22, 32, 42, 52 Gate

2A, 12A, 22A, 32A, 42A, 52A SiO 2 film

3, 13, 23, 33, 43, 53 Contact

4, 14, 24, 34, 44, 54 Oxide film

5A-5C, 15A-15C, 25A-25C, 35A-35C, 45A-45C Interlayer insulating film

5A 1 Hexagonal boron nitride crystal

5A 2 Amorphous region

6A-6F, 16A-16C, 26A-26C, 36A-36F, 47A-47C, 57A-57C Metal

7, 17, 27, 37, 48, 58 Passivation film

15A 1 Amorphous thin film

15A 2 Hexagonal boron nitride carbon polycrystalline thin film

25A 1 Hexagonal boron nitride carbon thin film

25A 2 Hexagonal boron nitride thin film

35A 1 , 35A Three Boron nitride carbon thin film

35A 2 Boron nitride thin film

46A-46C Nitrogen compound layer

55A-55C first interlayer insulating film

56A, 56B Second interlayer insulating film

61 Gallium arsenide substrate

62 Gallium arsenide active layer

63 sources

64 drain

65 gate

66 Insulating layer

Claims (6)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000278617A JP4574821B2 (en) | 2000-02-25 | 2000-09-13 | Semiconductor device and thin film |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000049291 | 2000-02-25 | ||

| JP2000-49291 | 2000-02-25 | ||

| JP2000278617A JP4574821B2 (en) | 2000-02-25 | 2000-09-13 | Semiconductor device and thin film |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001313335A JP2001313335A (en) | 2001-11-09 |

| JP2001313335A5 JP2001313335A5 (en) | 2008-05-29 |

| JP4574821B2 true JP4574821B2 (en) | 2010-11-04 |

Family

ID=26586100

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000278617A Expired - Fee Related JP4574821B2 (en) | 2000-02-25 | 2000-09-13 | Semiconductor device and thin film |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4574821B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4497323B2 (en) * | 2006-03-29 | 2010-07-07 | 三菱電機株式会社 | Plasma CVD equipment |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6337637A (en) * | 1986-08-01 | 1988-02-18 | Fujitsu Ltd | Semiconductor device having multilayer interconnection structure and manufacture thereof |

| JPH0499049A (en) * | 1990-08-06 | 1992-03-31 | Kawasaki Steel Corp | Semiconductor device |

| JP2001015595A (en) * | 1999-06-29 | 2001-01-19 | Mitsubishi Electric Corp | Semiconductor device |

-

2000

- 2000-09-13 JP JP2000278617A patent/JP4574821B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6337637A (en) * | 1986-08-01 | 1988-02-18 | Fujitsu Ltd | Semiconductor device having multilayer interconnection structure and manufacture thereof |

| JPH0499049A (en) * | 1990-08-06 | 1992-03-31 | Kawasaki Steel Corp | Semiconductor device |

| JP2001015595A (en) * | 1999-06-29 | 2001-01-19 | Mitsubishi Electric Corp | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001313335A (en) | 2001-11-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR920005320B1 (en) | Capacitor and method for manufacturing thereof | |

| TWI311772B (en) | ||

| US6593656B2 (en) | Multilevel copper interconnects for ultra large scale integration | |

| JP2000003885A (en) | Manufacture of field-effect device and capacitor using improved thin film dielectric substance and device obtained thereby | |

| US5763948A (en) | Semiconductor apparatus including a tin barrier layer having a (III) crystal lattice direction | |

| US5344797A (en) | Method of forming interlevel dielectric for integrated circuits | |

| US9379061B2 (en) | High density dielectric etch-stop layer | |

| KR100596794B1 (en) | Method for forming metal line in semiconductor device | |

| JPH06244185A (en) | Wiring structure and its manufacture | |

| JP4574821B2 (en) | Semiconductor device and thin film | |

| US20170148740A1 (en) | Advanced metallization for damage repair | |

| US20030216052A1 (en) | Method for fabricating semiconductor device | |

| US8334204B2 (en) | Semiconductor device and manufacturing method therefor | |

| KR19990052424A (en) | Wiring Formation Method of Semiconductor Device | |

| JPH1012614A (en) | Wiring for semiconductor device and its fabrication | |

| US20040150108A1 (en) | Low resistance barrier for a microelectronic component and method for fabricating the same | |

| US20050202616A1 (en) | MIM structure and fabrication process with improved capacitance reliability | |

| JP2000114263A (en) | Semiconductor integrated circuit device and its manufacture | |

| JPH04324636A (en) | Semiconductor device and its manufacture | |

| JPH01239940A (en) | Semiconductor device | |

| US20040155348A1 (en) | Barrier structure for copper metallization and method for the manufacture thereof | |

| JPH0346257A (en) | Semiconductor device | |

| JPH06196573A (en) | Fabrication of semiconductor device | |

| JPH0346231A (en) | Semiconductor device | |

| JPH04206741A (en) | Formation of schottky junction |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070213 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080229 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080411 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090520 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090527 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090727 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091125 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100728 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100819 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130827 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |