以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図、図2はパチンコ遊技機1の内部構造を示す全体背面図、図3はパチンコ遊技機1の遊技盤を背面からみた背面図である。なお、ここでは、遊技機の一例としてパチンコ遊技機を示すが、本発明はパチンコ遊技機に限られず、例えばコイン遊技機等であってもよい。また、画像式の遊技機やスロット機に適用することもできる。

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた景品玉を貯留する余剰玉受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部9と7セグメントLEDによる可変表示器10とを含む可変表示装置8が設けられている。この実施の形態では、可変表示部9には、「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、玉出口13を経て始動入賞口14の方に導かれる。通過ゲート11と玉出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。この実施の形態では、開閉板20が大入賞口を開閉する手段となる。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(Vゾーン)に入った入賞球はVカウントスイッチ22で検出される。また、開閉板20からの入賞球はカウントスイッチ23で検出される。可変表示装置8の下部には、始動入賞口14に入った入賞球数を表示する4個の表示部を有する始動入賞記憶表示器18が設けられている。この例では、4個を上限として、始動入賞がある毎に、始動入賞記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示部9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

遊技盤6には、複数の入賞口19,24が設けられ、遊技球の入賞口19,24への入賞は入賞口スイッチ19a,24aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、遊技効果LED28aおよび遊技効果ランプ28b,28cが設けられている。

そして、この例では、一方のスピーカ27の近傍に、景品玉払出時に点灯する賞球ランプ51が設けられ、他方のスピーカ27の近傍に、補給玉が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技台1に隣接して設置され、プリペイドカードが挿入されることによって玉貸しを可能にするカードユニット50も示されている。

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

打球発射装置から発射された打球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が通過ゲート11を通ってゲートスイッチ12で検出されると、可変表示器10の表示数字が連続的に変化する状態になる。また、打球が始動入賞口14に入り始動口スイッチ17で検出されると、図柄の変動を開始できる状態であれば、可変表示部9内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を1増やす。

可変表示部9内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球が特定入賞領域に入賞しVカウントスイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

停止時の可変表示部9内の画像の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、可変表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、可変表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

次に、パチンコ遊技機1の裏面の構造について図2を参照して説明する。

可変表示装置8の背面では、図2に示すように、機構板36の上部に景品玉タンク38が設けられ、パチンコ遊技機1が遊技機設置島に設置された状態でその上方から景品玉が景品玉タンク38に供給される。景品玉タンク38内の景品玉は、誘導樋39を通って玉払出装置に至る。

機構板36には、中継基板30を介して可変表示部9を制御する可変表示制御ユニット29、基板ケース32に覆われ遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31、可変表示制御ユニット29と遊技制御基板31との間の信号を中継するための中継基板33、および景品玉の払出制御を行う賞球制御用マイクロコンピュータ等が搭載された賞球制御基板37が設置されている。さらに、機構板36の下部には、モータの回転力を利用して打球を遊技領域7に発射する打球発射装置34と、遊技効果ランプ・LED28a,28b,28c、賞球ランプ51および球切れランプ52に信号を送るためのランプ制御基板35が設置されている。

また、図3はパチンコ遊技機1の遊技盤を背面からみた背面図である。誘導樋39を通った玉は、図3に示されるように、球切れ検出器187a,187bを通過して玉供給樋186a,186bを経て玉払出装置97に至る。玉払出装置97から払い出された景品玉は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に供給される。連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰玉受皿4に連通する余剰玉通路46が形成されている。入賞にもとづく景品玉が多数払い出されて打球供給皿3が満杯になり、ついには景品玉が連絡口45に到達した後さらに景品玉が払い出されると景品玉は、余剰玉通路46を経て余剰玉受皿4に導かれる。さらに景品玉が払い出されると、感知レバー47が満タンスイッチ48を押圧して満タンスイッチ48がオンする。その状態では、玉払出装置97内のステッピングモータの回転が停止して玉払出装置97の動作が停止するとともに、必要に応じて打球発射装置34の駆動も停止する。なお、この実施の形態では、電気的駆動源の駆動によって遊技球を払い出す玉払出装置として、ステッピングモータの回転によって遊技球が払い出される玉払出装置97を例示するが、その他の駆動源によって遊技球を送り出す構造の玉払出装置を用いてもよいし、電気的駆動源の駆動によってストッパを外し遊技球の自重によって払い出しがなされる構造の玉払出装置を用いてもよい。

賞球払出制御を行うために、入賞口スイッチ19a,24a、始動口スイッチ17およびVカウントスイッチ22からの信号が、主基板31に送られる。主基板31のCPU56は、始動口スイッチ17がオンすると6個の賞球払出に対応した入賞が発生したことを知る。また、カウントスイッチ23がオンすると15個の賞球払出に対応した入賞が発生したことを知る。そして、入賞口スイッチがオンすると10個の賞球払出に対応した入賞が発生したことを知る。なお、この実施の形態では、例えば、入賞口24に入賞した遊技球は、入賞口24からの入賞球流路に設けられている入賞口スイッチ24aで検出され、入賞口19に入賞した遊技球は、入賞口19からの入賞球流路に設けられている入賞口スイッチ19aで検出される。

図4は、主基板31における回路構成の一例を示すブロック図である。なお、図4には、賞球制御基板37、ランプ制御基板35、音制御基板70、発射制御基板91および表示制御基板80も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ12、始動口スイッチ17、Vカウントスイッチ22、カウントスイッチ23および入賞口スイッチ19a,24aからの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16および開閉板20を開閉するソレノイド21を基本回路53からの指令に従って駆動するソレノイド回路59と、始動記憶表示器18の点灯および滅灯を行うとともに7セグメントLEDによる可変表示器10と装飾ランプ25とを駆動するランプ・LED回路60とが搭載されている。

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示部9の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等をホール管理コンピュータ等のホストコンピュータに対して出力する情報出力回路64を含む。

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段の一例であるRAM55、制御用のプログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、マイクロコンピュータにおける情報入出力可能な端子である。

さらに、主基板31には、電源投入時に基本回路53をリセットするための初期リセット回路65と、基本回路53から与えられるアドレス信号をデコードしてI/Oポート部57のうちのいずれかのI/Oポートを選択するための信号を出力するアドレスデコード回路67とが設けられている。

なお、玉払出装置97から主基板31に入力されるスイッチ情報もあるが、図4ではそれらは省略されている。

遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

図5は、電源監視および電源バックアップのためのCPU56周りの一構成例を示すブロック図である。図5に示すように、電源基板に搭載されている第1の電源監視回路(第1の電源監視手段)からの電圧低下信号が、CPU56の割込端子(IRQ端子)に接続されている。第1の電源監視回路は、遊技機が使用する各種直流電源のうちのいずれかの電源の電圧を監視して電源電圧低下を検出する回路である。従って、CPU56は、割込処理によって電源断の発生を確認することができる。

主基板31には、第2の電源監視回路903が搭載されている。この例では、第2の電源監視回路903において、電源監視用IC904が、第1の電源監視回路が監視する電源電圧と等しい電源電圧である+30V電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。そして、例えば、電源基板に搭載される第1の電源監視回路の検出電圧(電圧低下信号を出力することになる電圧)を+16Vとし、第2の電源監視回路903の検出電圧を+8Vとする。そのように構成した場合には、同一の電圧を監視するので、第1の電圧監視回路が電圧低下信号を出力するタイミングと第2の電圧監視回路が電圧低下信号を出力するタイミングの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、第1の電源監視回路からの電圧低下信号に応じて電源断時処理を開始してから電源断時処理が確実に完了するまでの期間である。

第2の電源監視回路903からの電圧低下信号は、初期リセット回路65からの初期リセット信号と論理和をとられた後に、CPU56のリセット端子に入力される。従って、CPU56は、初期リセット回路65からの初期リセット信号がローレベルを呈しているとき、または、第2の電源監視回路903からの電圧低下信号がローレベルを呈しているときに、リセット状態(非動作状態)になる。

なお、初期リセット回路65のリセットIC651は、遊技機に電源が投入され+5V電源の電圧が上昇していくときに、+5V電源電圧が所定値以上になると、出力信号をハイレベルにする。すなわち、初期リセット信号をオフ状態にする。

CPU56等の駆動電源である+5V電源から電力が供給されていない間、RAMの少なくとも一部は、電源基板から供給されるバックアップ電源によってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、初期リセット回路65からリセット信号が発せられるので、CPU56は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップされているので、停電等からの復旧時には停電発生時の遊技状態に復帰することができる。

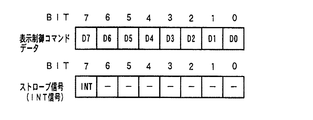

図6は、表示制御基板80内の回路構成を、可変表示部9の一実現例であるCRT82および主基板31の出力ポート(ポートA,B)571,572および出力バッファ回路63とともに示すブロック図である。出力ポート571からは8ビットのデータが出力され、出力ポート572からは1ビットのストローブ信号(INT信号)が出力される。

表示制御用CPU101は、制御データROM102に格納されたプログラムに従って動作し、主基板31からノイズフィルタ107および入力バッファ回路105を介してストローブ信号が入力されると、入力バッファ回路105を介して表示制御コマンドを受信する。入力バッファ回路105として、例えば汎用ICである74HC244を使用することができる。なお、表示制御用CPU101がI/Oポートを内蔵していない場合には、入力バッファ回路105と表示制御用CPU101との間に、I/Oポートが設けられる。

そして、表示制御用CPU101は、受信した表示制御コマンドに従って、CRT82に表示される画面の表示制御を行う。具体的には、表示制御コマンドに応じた指令をVDP103に与える。VDP103は、キャラクタROM86から必要なデータを読み出す。VDP103は、入力したデータに従ってCRT82に表示するための画像データを生成し、その画像データをVRAM87に格納する。そして、VRAM87内の画像データは、R,G,B信号に変換され、D−A変換回路104でアナログ信号に変換されてCRT82に出力される。

なお、図6には、VDP103をリセットするためのリセット回路83、VDP103に動作クロックを与えるための発振回路85、および使用頻度の高い画像データを格納するキャラクタROM86も示されている。キャラクタROM86に格納される使用頻度の高い画像データとは、例えば、CRT82に表示される人物、動物、または、文字、図形もしくは記号等からなる画像などである。

図7は、賞球制御基板37および玉払出装置97の構成要素などの賞球に関連する構成要素を示すブロック図である。図7に示すように、満タンスイッチ48からの検出信号は、中継基板71を介して主基板31のI/Oポート57に入力される。満タンスイッチ48は、余剰玉受皿4の満タンを検出するスイッチである。

球切れ検出スイッチ167および球切れスイッチ187(187a,187b)からの検出信号は、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。球切れ検出スイッチ167は景品玉タンク38内の補給玉の不足を検出するスイッチであり、球切れスイッチ187は、景品玉通路内の景品玉の有無を検出するスイッチである。

主基板31のCPU56は、球切れ検出スイッチ167または球切れスイッチ187からの検出信号が球切れ状態を示しているか、または、満タンスイッチ48からの検出信号が満タン状態を示していると、玉貸し禁止を指示する賞球制御コマンドを送出する。玉貸し禁止を指示する賞球制御コマンドを受信すると、賞球制御基板37の賞球制御用CPU371は、玉貸し処理を停止する。

さらに、賞球カウントスイッチ301Aからの検出信号も、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。また、賞球カウントスイッチ301Aは、玉払出装置97の賞球機構部分に設けられ、実際に払い出された賞球を検出する。

入賞があると、賞球制御基板37には、主基板31の出力ポート(ポートG,H)577,578から賞球個数を示す賞球制御コマンドが入力される。出力ポート577は8ビットのデータを出力し、出力ポート578は1ビットのストローブ信号(INT信号)を出力する。賞球個数を示す賞球制御コマンドは、入力バッファ回路373を介してI/Oポート372aに入力される。賞球制御用CPU371は、I/Oポート372aを介して賞球制御コマンドを入力し、賞球制御コマンドに応じて玉払出装置97を駆動して賞球払出を行う。なお、この実施の形態では、賞球制御用CPU371は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

賞球制御用CPU371は、出力ポート372gを介して、貸し玉数を示す玉貸し個数信号をターミナル基板160に出力し、ブザー駆動信号をブザー基板75に出力する。ブザー基板75にはブザーが搭載されている。さらに、出力ポート372eを介して、エラー表示用LED374にエラー信号を出力する。

さらに、賞球制御基板37の入力ポート372bには、中継基板72を介して、賞球カウントスイッチ301Aの検出信号の検出信号が入力される。賞球制御基板37からの払出モータ289への駆動信号は、出力ポート372cおよび中継基板72を介して玉払出装置97の賞球機構部分における払出モータ289に伝えられる。

カードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、端数表示スイッチ152、連結台方向表示器153、カード投入表示ランプ154およびカード挿入口155が設けられている(図1参照)。残高表示基板74には、打球供給皿3の近傍に設けられている度数表示LED、玉貸しスイッチおよび返却スイッチが接続される。

残高表示基板74からカードユニット50には、遊技者の操作に応じて、玉貸しスイッチ信号および返却スイッチ信号が賞球制御基板37を介して与えられる。また、カードユニット50から残高表示基板74には、プリペイドカードの残高を示すカード残高表示信号および玉貸し可表示信号が賞球制御基板37を介して与えられる。カードユニット50と賞球制御基板37の間では、ユニット操作信号(BRDY信号)、玉貸し要求信号(BRQ信号)、玉貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)がI/Oポート372fを介してやりとりされる。

パチンコ遊技機1の電源が投入されると、賞球制御基板37の賞球制御用CPU371は、カードユニット50にPRDY信号を出力する。カードユニット50においてカードが受け付けられ、玉貸しスイッチが操作され玉貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、賞球制御基板37にBRDY信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、賞球制御基板37にBRQ信号を出力する。そして、賞球制御基板37の賞球制御用CPU371は、払出モータ289を駆動し、所定個の貸し玉を遊技者に払い出す。そして、払出が完了したら、賞球制御用CPU371は、カードユニット50にEXS信号を出力する。

以上のように、カードユニット50からの信号は全て賞球制御基板37に入力される構成になっている。従って、玉貸し制御に関して、カードユニット50から主基板31に信号が入力されることはなく、主基板31の基本回路53にカードユニット50の側から不正に信号が入力される余地はない。なお、主基板31および賞球制御基板37には、ソレノイドおよびモータやランプを駆動するためのドライバ回路が搭載されているが、図7では、それらの回路は省略されている。

図8は、電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、表示制御基板80、音制御基板70、ランプ制御基板35および賞球制御基板37等の遊技装置制御基板と独立して設置され、遊技機内の各遊技装置制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、DC+30V、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、+21V、+12Vおよび+5Vを生成してコネクタ915に出力する。コネクタ915は例えば中継基板に接続され、中継基板から各遊技装置制御基板および機構部品に必要な電圧の電力が供給される。なお、トランス911の入力側には、遊技機に対する電源供給を停止したり開始させたりするための電源スイッチ918が設置されている。

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が遮断されたときの遊技装置制御基板のバックアップRAM(電源バックアップされているRAMすなわち記憶内容保持状態となりうる記憶手段)に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。

なお、バックアップ電源として、+5V電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

また、電源基板910には、上述した第1の電源回路を構成する電源監視用IC902が搭載されている。電源監視用IC902は、+30V電源電圧を導入し、+30V電源電圧を監視することによって電源断の発生を検出する。具体的には、+30V電源電圧が所定値(この例では+16V)以下になったら、電源断が生ずるとして電圧低下信号を出力する。なお、+30V電源電圧は、交流から直流に変換された直後の電圧である。電源監視用IC902からの電圧低下信号は、主基板31や賞球制御基板37等に供給される。

電源監視用IC902が電源断を検知するための所定値は、通常時の電圧より低いが、各遊技装置制御基板上のCPUが暫くの間動作しうる程度の電圧である。また、電源監視用IC902が、CPUを駆動するための電圧(この例では+5V)よりも高く、かつ、交流から直流に変換された直後の電圧を監視するように構成されているので、CPUが必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。さらに、監視電圧として+30Vを用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入ってスイッチ出力を検出しない状態となることができる。

また、電源監視用IC902は、遊技装置制御基板とは別個の電源基板910に搭載されているので、第1の電源監視回路から複数の遊技装置制御基板に電圧低下信号を供給することができる。電圧低下信号を必要とする遊技装置制御基板が幾つあっても第1の電源監視手段は1つ設けられていればよいので、各遊技装置制御基板における各遊技装置制御手段が後述する電源復帰制御を行っても、遊技機のコストはさほど上昇しない。

次に遊技機の動作について説明する。

図9は、主基板31におけるCPU56が実行するメイン処理を示すフローチャートである。遊技機に対する電源が投入されると、メイン処理において、CPU56は、まず、停電からの復旧時であったか否か確認する(ステップS1)。停電からの復旧時であったか否かは、例えば、電源断時にバックアップRAM領域に設定される電源断フラグによって確認される。

すなわち、RAM領域が電源バックアップされている状態で遊技機に電源が再投入されるとRAMには電源断時の状態が保存されているので電源断フラグも正確に保存されている。RAM領域が電源バックアップされていない状態で遊技機に電源が投入されると、RAMの内容は不定になっているので、電源断フラグの値は正しくない。従って、電源断フラグのセット状態に応じて停電からの復旧時であったか否か確認することができる。なお、仮に、電源バックアップされていない状態で遊技機に電源が投入されたときに電源断フラグがセット状態になってしまったとしても、後述するパリティ診断によって、停電からの復旧時であったと誤って判断されてしまうことは防止される。

停電からの復旧時であった場合には、CPU56は、後述する停電復旧処理を実行する(ステップS4)。停電からの復旧時でない場合には、CPU56は、通常の初期化処理を実行する(ステップS1,S2)。その後、メイン処理では、タイマ割込フラグの監視(ステップS6)の確認が行われるループ処理に移行する。なお、ループ内では、表示用乱数更新処理(ステップS5)も実行される。

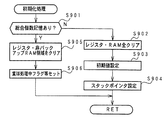

通常の初期化処理では、図10に示すように、レジスタおよびRAMのクリア処理(ステップS2a)と、必要な初期値設定処理(ステップS2b)が行われた後に、2ms毎に定期的にタイマ割込がかかるようにCPU56に設けられているタイマレジスタの初期設定(タイムアウトが2msであることと繰り返しタイマが動作する設定)が行われる(ステップS2c)。すなわち、ステップS2cで、タイマ割込を能動化する処理と、タイマ割込インタバルを設定する処理とが実行される。

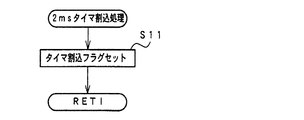

従って、この実施の形態では、CPU56の内部タイマが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、図11に示すように、タイマ割込が発生すると、CPU56は、タイマ割込フラグをセットする(ステップS11)。

CPU56は、ステップS6において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS7)、遊技制御処理を実行する(ステップS9)。以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、遊技制御処理はメイン処理において実行されるが、タイマ割込処理で遊技制御処理を実行してもよい。

図12は、遊技制御処理を示すフローチャートである。遊技制御処理において、CPU56は、まず、表示制御基板80に送出される表示制御コマンドをRAM55の所定の領域に設定する処理を行った後に(表示制御データ設定処理:ステップS21)、表示制御コマンドを出力する処理を行う(表示制御データ出力処理:ステップS22)。

次いで、各種出力データの格納領域の内容を各出力ポートに出力する処理を行う(データ出力処理:ステップS23)。また、ホール管理用コンピュータに出力される大当り情報、始動情報、確率変動情報などの出力データを格納領域に設定する出力データ設定処理を行う(ステップS24)。さらに、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS25)。

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS26)。

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS27)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS28)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

さらに、CPU56は、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17、カウントセンサ23および入賞口スイッチ19a,24aの状態を入力し、各入賞口や入賞装置に対する入賞があったか否か判定する(スイッチ処理:ステップS29)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS30)。

また、CPU56は、賞球制御基板37との間の信号処理を行う(ステップS31)。すなわち、所定の条件が成立すると賞球制御基板37に賞球制御コマンドを出力する。賞球制御基板37に搭載されている賞球制御用CPUは、賞球制御コマンドに応じて玉払出装置97を駆動する。

以上のように、メイン処理には遊技制御処理に移行すべきか否かを判定する処理が含まれ、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理で遊技制御処理に移行すべきか否かを判定するためのフラグがセットされるので、遊技制御処理の全てが確実に実行される。つまり、遊技制御処理の全てが実行されるまでは、次回の遊技制御処理に移行すべきか否かの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することは保証されている。

従来の一般的な遊技制御処理は、定期的に発生する外部割込によって、強制的に最初の状態に戻されていた。図12に示された例に則して説明すると、例えば、ステップS31の処理中であっても、強制的にステップS21の処理に戻されていた。つまり、遊技制御処理中の全ての各処理が実行完了する前に、次回の遊技制御処理が開始されてしまう可能性があった。

なお、ここでは、主基板31のCPU56が実行する遊技制御処理は、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理でセットされるフラグに応じて実行されたが、定期的に(例えば2ms毎)信号を発生するハードウェア回路を設け、その回路からの信号をCPU56の外部割込端子に導入し、割込信号によって遊技制御処理に移行すべきか否かを判定するためのフラグをセットするようにしてもよい。そのように構成した場合にも、遊技制御処理の全てが実行されるまでは、フラグの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することが保証される。

図13は、電源基板910の第1の電源監視回路からの電圧低下信号にもとづく割込に応じて実行される停電発生割込処理の一例を示すフローチャートである。停電発生割込処理において、CPU56は、まず、割込禁止に設定する(ステップS41)。停電割込発生処理ではRAM内容の保存を確実にするためにチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちにCPUが動作し得ない電圧にまで低下してしまうことがことも考えられるので、まず、他の割込が生じないような設定がなされる。

次いで、CPU56は、全ての出力ポートをオフ状態にする(ステップS42)。そして、必要ならば各レジスタの内容をバックアップRAM領域に格納する(ステップS43)。また、電源断フラグをセットする(ステップS44)。さらに、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS45)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとって(ステップS46)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS47)。その後、RAMアクセス禁止状態にする(ステップS48)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

次いで、CPU56は、ホールト命令(HALT命令)を発行する(ステップS49)。すなわち、CPU自身を、リセット解除または割込発生以外では動作しない状態にする。ただし、ステップS41で割込禁止に設定されているので、割込は発生しない。従って、図5に示された電源監視用IC904からのリセット信号によって外部から動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実にCPU56は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生割込処理は、最終部でホールト命令を発行するように構成されるが、プログラムをループ状態にしてもよい。

また、RAMアクセス禁止にする前にセットされる電源断フラグは、上述したように、電源投入時において停電からの復旧か否かを判断する際に使用される。また、ステップS41からS49の処理は、第2の電源監視手段が電圧低下信号を発生する前に完了する。換言すれば、第2の電源監視手段が電圧低下信号を発生する前に完了するように、第1の電圧監視手段および第2の電圧監視手段の検出電圧の設定が行われている。

図14は、停電復旧処理(ステップS4)の一例を示すフローチャートである。停電復旧処理において、CPU56は、まず、バックアップRAM領域のデータチェック(この例ではパリティチェック)を行う(ステップS51)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理(ステップS2)と同様の初期化処理を実行する(ステップS52,S54)。

チェック結果が正常であれば、CPU56は、内部状態を電源断時の状態に戻すための遊技状態復旧処理を行うとともに(ステップS53)、電源断フラグをクリアする(ステップS55)。

なお、ここでは、ステップS1で停電からの復旧か否かを確認し、停電からの復旧時であればパリティチェックを行ったが、最初に、パリティチェックを実行し、チェック結果が正常でなければ停電からの復旧ではないと判断してステップS2の初期化処理を実行し、チェック結果が正常であれば遊技状態復帰処理を行ってもよい。すなわち、パリティチェックの結果をもって停電からの復旧であるか否かを判断してもよい。

図15は、バックアップパリティデータ作成方法を説明するための説明図である。ただし、図15に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図15(A)に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われるが、図15(B)はパリティ診断の例を示す説明図である。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図15(A)に示すようなデータがバックアップ領域に設定されている。

ステップS51の処理において、CPU56は、バックアップRAM領域のバックアップパリティデータ領域に設定されていたデータ(この例では「39H」)を初期データとして、バックアップデータ領域の各データについて順次排他的論理和をとる処理を行う。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「00H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「00H」にならない。

よって、CPU56は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

以上のように、この実施の形態では、遊技制御手段には、遊技機の電源が断しても、所定期間電源バックアップされる記憶手段(この例ではバックアップRAM)が設けられ、電源投入時に、CPU56(具体的にはCPU56が実行するプログラム)は、記憶手段がバックアップ状態にあればバックアップデータにもとづいて遊技状態を回復させる遊技状態復旧処理(ステップS53)を行うように構成される。

この実施の形態では、図8に示されたように電源基板910に第1の電源監視手段が搭載され、図5に示されたように主基板31に第2の電源監視手段が搭載されている。そして、電源電圧が低下していくときに、第2の電源監視手段(この例では電源監視用IC904)が電圧低下信号を発生する時期は、第1の電源監視手段(この例では電源監視用IC902)が電圧低下信号を発生する時期よりも遅くなるように設定されている。さらに、第2の電源監視手段からの電圧低下信号は、CPU56のリセット端子に入力されている。

すると、CPU56は、第1の電源監視手段(電源監視用IC902)からの電圧低下信号にもとづいて停電発生処理(電源断時処理)を実行した後にホールト状態に入るのであるが、ホールト状態において、リセット状態に入ることになる。すなわち、CPU56の動作が完全に停止する。ホールト状態では+5V電源電圧値が徐々に低下するので入出力状態が不定になるが、CPU56はリセット状態になるので、不定データにもとづいて異常動作してしまうことは防止される。

このように、この実施の形態では、CPU56が、第1の電源監視手段からの検出出力の入力に応じてホールト状態に入るとともに、第2の電源監視手段からの検出出力の入力に応じてシステムリセットされるように構成したので、電源断時に確実なデータ保存を行うことができ、遊技者に不利益がもたらされることを防止することができる。

なお、この実施の形態では、電源監視用IC902,904は、同一の電源電圧を監視しているが、異なる電源電圧を監視してもよい。例えば、電源基板910の第1の電源監視回路が+30V電源電圧を監視し、主基板31の第2の電源監視回路が+5V電源電圧を監視してもよい。そして、第2の電源監視回路がローレベルの電圧低下信号を発生するタイミングは第1の電源監視回路が電圧低下信号を発生するタイミングに対して遅くなるように、主基板31の電源監視用IC904のしきい値レベル(電圧低下信号を発生する電圧レベル)が設定される。例えば、しきい値は4.25Vである。4.25Vは、通常時の電圧より低いが、CPU56が暫くの間動作しうる程度の電圧である。

また、上記の実施の形態では、CPU56は、マスク可能外部割込端子(IRQ端子)を介して電源基板からの第1の電圧低下信号(第1の電源監視手段からの電圧低下信号)を検知したが、第1の電圧低下信号をマスク不能割込割込端子(NMI端子)に導入してもよい。その場合には、NMI処理で電源断時処理が実行される。また、入力ポート570を介して電源基板からの第1の電圧低下信号を検知してもよい。その場合には、メイン処理において入力ポートの監視が行われる。

また、IRQ端子を介して電源基板からの第1の電圧低下信号を検知する場合に、メイン処理のステップS10の遊技制御処理の開始時にIRQ割込マスクをセットし、遊技制御処理の終了時にIRQ割込マスクを解除するようにしてもよい。そのようにすれば、遊技制御処理の開始前および終了後に割込がかかることになって、遊技制御処理が中途で中断されることはない。従って、賞球制御コマンドを賞球制御基板37に送出しているときなどにコマンド送出が中断されてしまうようなことはない。よって、停電が発生するようなときでも、賞球制御コマンド等は確実に送出完了する。

次に、可変表示部9の表示制御について説明する。

図16は、8ビットのデータによる表示制御コマンドデータの構成例を示す説明図である。図16に示すように、例えば、8ビットのうちの上位4ビットで制御の種類を指示し、下位4ビットで具体的制御内容を指示する。例えば、この例では、上位4ビットが[0,0,0,1]であれば、下位4ビットの数値で変動種類等が指示される。また、上位4ビットが[1,0,0,0],[1,0,0,1]または[1,0,1,0]であれば、下位4ビットの数値で可変表示部9に可変表示される左図柄、中図柄または右図柄の停止図柄が指示される。

また、上位4ビットが[1,1,0,1]であればデモ画面表示コマンドであることを示す。上位4ビットが[1,1,1,0]であればエラー表示コマンドであることを示す。上位4ビットが[1,1,1,1]であれば全図柄停止コマンド(確定コマンド)であることを示す。なお、それらのコマンドにおいて下位4ビットは例えば0に設定される。

この実施の形態では、主基板31のCPU56は、図柄の変動開始時に、変動種類を示すコマンドと左右中停止図柄を示すコマンドとを表示制御基板80に送出する。表示制御基板80の表示制御用CPU101は、変動種類を示すコマンドによって図柄の変動時間を特定できる。なお、特定された変動時間に対応した複数種類の変動態様が用意されている場合には、表示制御用CPU101が、いずれの変動態様を用いるのかを決定する。このように、図柄変動制御に関して、主基板31のCPU56は、変動開始時に変動時間を特定可能な情報と確定図柄を特定可能な情報とを送出するだけであり、具体的な図柄変動制御は表示制御用CPU101の制御によって実現される。また、主基板31のCPU56は、変動時間が経過したら、表示制御基板80に対して確定コマンドを送出する。

図17は、主基板31から表示制御基板80に送出される表示制御コマンドの構成例を示す説明図である。図17に示すように、表示制御コマンドは、8ビットのデータと、1ビットのストローブ信号(INT信号)とから構成されている。

図18はCPU56が実行する特別図柄プロセス処理のプログラムの一例を示すフローチャートである。図18に示す特別図柄プロセス処理は、図12に示された遊技制御処理におけるステップS27の具体的な処理である。CPU56は、特別図柄プロセス処理を行う際に、特別図柄プロセスフラグの値に応じて、図18に示すステップS300〜S309のうちのいずれかの処理を行う。各処理において、以下のような処理が実行される。

特別図柄変動待ち処理(ステップS300):始動入賞口14(この実施の形態では可変入賞球装置15の入賞口)に打球入賞して始動口センサ17がオンするのを待つ。始動口センサ17がオンすると、始動入賞記憶数が満タンでなければ、始動入賞記憶数が+1される。そして、大当り判定用乱数を抽出する。

特別図柄判定処理(ステップS301):特別図柄の可変表示が開始できる状態になると、始動入賞記憶数を確認する。始動入賞記憶数が0でなければ、抽出されている大当り判定用乱数の値に応じて大当りとするかはずれとするか決定する。

停止図柄設定処理(ステップS302):左右中図柄の停止図柄を決定する。

リーチ動作設定処理(ステップS303):リーチ判定用乱数の値に応じてリーチ動作するか否か決定するとともに、リーチ動作用乱数の値に応じてリーチ動作の変動時間を決定する。

全図柄変動開始処理(ステップS304):可変表示部9において全図柄が変動開始されるように制御する。このとき、表示制御基板80に対して、左右中最終停止図柄と変動時間を特定可能な情報が送信される。

全図柄停止待ち処理(ステップS305):所定時間が経過すると、可変表示部9において表示される全図柄が停止されるように確定コマンドを送出する。

大当り表示処理(ステップS306):停止図柄が大当り図柄の組み合わせである場合には、大当り表示の表示制御コマンドデータが表示制御基板80に送出されるように制御するとともに内部状態(プロセスフラグ)をステップS307に移行するように更新する。そうでない場合には、内部状態をステップS309に移行するように更新する。なお、大当り図柄の組み合わせは、左右中図柄が揃った組み合わせである。また、遊技制御基板80の表示制御用CPU101は表示制御コマンドデータに従って、可変表示部9に大当り表示を行う。大当り表示は遊技者に大当りの発生を報知するためになされるものである。

大入賞口開放開始処理(ステップS307):大入賞口を開放する制御を開始する。具体的には、カウンタやフラグを初期化するとともに、ソレノイド21を駆動して大入賞口を開放する。

大入賞口開放中処理(ステップS308):大入賞口ラウンド表示の表示制御コマンドデータが表示制御基板80に送出する制御や大入賞口の閉成条件の成立を確認する処理等を行う。大入賞口の閉成条件が成立したら、大当り遊技状態の終了条件が成立していなければ内部状態をステップS307に移行するように更新する。大当り遊技状態の終了条件が成立していれば、内部状態をステップS309に移行するように更新する。

大当たり終了処理(ステップS309):大当たり遊技状態が終了したことを遊技者に報知するための表示を行う。その表示が終了したら、内部フラグ等を初期状態に戻し、内部状態をステップS300に移行するように更新する。

上記の各ステップの処理に応じて、遊技制御プログラム中の表示制御コマンドを送出する処理を行うモジュール(図12におけるステップS22)は、対応する表示制御コマンドデータを出力ポートに出力するとともにストローブ信号をオン状態にする。

図19(A)は、可変表示部9における図柄変動に関する各制御コマンドの送出タイミング例を示す説明図である。この実施の形態では、主基板31のCPU56は、図柄変動を開始させるときに、表示制御基板80に対して変動開始コマンドおよび左右中図柄の確定図柄を示す図柄指定コマンドを送出する。

そして、図柄変動を確定させるときに、表示制御基板80に対して変動停止コマンド(確定コマンド)を送出する。表示制御基板80に搭載されている表示制御用CPU101は、変動開始コマンドで指定された変動態様に応じた表示制御を行う。なお、変動開始コマンドには変動時間を示す情報が含まれている。

図19(B)は、可変表示部9の表示結果が所定の大当り図柄であった場合に実行される大当り遊技に関する各制御コマンドの送出タイミング例を示す説明図である。この実施の形態では、主基板31のCPU56は、大当り遊技開始時に、表示制御基板80に対して大当り開始コマンドを送出する。また、所定時間経過後に、1ラウンド(1R)指定コマンドを送出する。表示制御用CPU101は、大当り開始コマンドを受信すると、大当り開始時の表示制御を行う。また、1ラウンド指定コマンドを受信すると、1ラウンド目の表示を行う。

その後、主基板31のCPU56は、表示制御基板80に対して各ラウンドを示すコマンド等を順次送出する。表示制御基板80のCPUは、それらのコマンドに応じて対応する表示制御を行う。

また、大当り遊技終了時に、主基板31のCPU56は、表示制御基板80に対して大当り終了コマンドを送出する。表示制御用CPU101は、大当り終了コマンドを受信すると、所定時間後に制御状態を遊技待ちの状態にする。

図20は、図12に示された遊技制御処理における表示制御データ出力処理(ステップS22)を示すフローチャートである。表示制御データ出力処理において、CPU56は、ポートA出力要求がセットされているか否か判定する(ステップS581)。なお、ポートA出力要求は、表示制御データ設定処理(ステップS21)において、特別図柄プロセス処理等からのコマンド出力要求に応じセットされる。

ポートA出力要求がセットされている場合には、ポートA出力要求をリセットし(ステップS582)、ポートA格納領域の内容を出力ポート(出力ポートA)571に出力する(ステップS583)。また、ポートA出力カウンタを+1するとともに(ステップS584)、出力ポート(ポートB)572のビット7を0にする(ステップS585)。

ポートA出力要求がセットされていない場合には、ポートA出力カウンタの値が0であるか否か判定する(ステップS586)。ポートA出力カウンタの値が0でない場合には、ポートA出力カウンタの値が2であるか否か確認する(ステップS587)。ポートA出力カウンタの値が2ではない、すなわち1である場合には、ポートA出力カウンタの値を1増やす(ステップS588)。

ポートA出力カウンタの値が2である場合には、ポートA出力カウンタの値をクリアするとともに(ステップS589)、出力ポート(出力ポートB)572のビット7を1にする(ステップS590)。

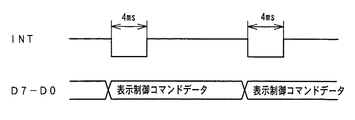

出力ポートBのビット7は、表示制御基板80に与えられるストローブ信号(INT信号)を出力するポートである。また、出力ポートAのビット0〜7は、表示制御コマンドデータを出力するポートである。そして、この実施の形態では、図20に示された表示制御データ出力処理は2msに1回実行される。従って、図20に示されたデータ出力処理によって、図21に示すように、表示制御コマンドデータが出力されるときに、4ms間INT信号がローレベル(オン状態)になる。

なお、INT信号のオン期間の4msは一例であり、オン期間はそれよりも短くてもよく長くてもよい。また、ここでは、1バイトの表示制御コマンドを例示したが、表示制御コマンドの長さも1バイトに限られず、1バイトよりも長い表示制御コマンドを用いてもよい。

次に、遊技状態復旧処理について説明する。

図22は、図14に示された停電復旧処理で行われる遊技状態復旧処理の一例を示すフローチャートである。この例では、CPU56は、レジスタ内容を復元する必要があれば、バックアップRAMに保存されていた値をレジスタに復元する(ステップS61)。そして、バックアップRAMに保存されていたデータにもとづいて停電時の遊技状態を確認する。例えば、特別図柄プロセス処理の進行状況に対応した特別図柄プロセスフラグの値によって遊技状態を確認することができる。

遊技状態が図柄変動中であった場合には(ステップS62)、左右中の停止図柄を示す表示制御コマンドおよび特殊表示コマンドの一例であるエラー表示制御コマンドを表示制御基板80に送出する制御を行う(ステップS63,S64)。遊技状態が図柄変動中でなかった場合には、停電発生前の最後に送出された左右中の停止図柄を示す表示制御コマンドと確定コマンドとを表示制御基板80に送出する制御を行う(ステップS65,S66)。停電発生前の最後に送出された左右中の停止図柄に関する情報は、主基板31のバックアップRAMに保存されている。

図23は、停電が発生した後に復旧した場合の制御状態の一例を示す説明図である。図23において、可変表示の状態は表示制御基板80の表示制御用CPU101によって実現される。

図23(A)は、図柄変動中に停電が生じた後に復旧した場合の例を示す。この場合には、電源復旧時に、主基板31から左右中の停止図柄を示す表示制御コマンドとエラー表示コマンドとが送出される(図22におけるステップS63,S64)。表示制御用CPU101は、エラー表示コマンドを受信すると、可変表示部9に特殊表示としてエラー表示を行う。また、主基板31における遊技制御手段は停電復旧時に図柄変動中の遊技状態、具体的には特別図柄プロセス処理における全図柄停止待ち処理(図18におけるステップS306)の状態に戻るので、変動期間が終了したら確定コマンドを表示制御基板80に送出する。

表示制御用CPU101は、確定コマンドを受信すると、エラー表示を行っている状態で左右中の停止図柄を表示する。そして、次の表示制御コマンドを受信したら、エラー表示を止める。次の表示制御コマンドとは、例えば、大当りとすることに決定されている場合には大当り開始コマンドであり、大当りとしないことに決定されている場合には、次の図柄変動開始時に主基板31から送出される変動開始を示すコマンド(変動時間を特定可能なコマンド)である。また、所定期間継続して始動入賞口14への入賞が発生しなかった場合等に遊技制御手段がデモ画面コマンドを送出するような場合には、デモ画面コマンドを受信したらエラー表示を止めるようにしてもよい。

なお、主基板31において、変動開始時に使用した各種パラメータはバックアップRAMに保存されている。従って、電源復旧後の変動における表示結果(確定図柄)等は、停電によって中断した変動においてなされるはずであった表示結果等と同じである。従って、遊技者に不利益が与えられるということはない。

図23(B)は、大当り遊技中に停電が生じた後に復旧した場合の例を示す。この場合には、電源復旧時に、主基板31から左右中の停止図柄を示す表示制御コマンドと確定コマンドとが送出される(図22におけるステップS65,S66)。

この場合には、遊技制御手段は停電復旧時に大当り遊技中の遊技状態、具体的には特別図柄プロセス処理における大入賞口開放中処理または大入賞口開放開始処理(図18におけるステップS308またはS307)の状態に戻るので、適宜ラウンド回数等を示す大当り遊技に関わる表示制御コマンドを表示制御基板80に送出する。表示制御用CPU101は、大当り遊技に関わるコマンドに応じて、制御状態を大当り遊技中の状態に戻すことができる。

なお、主基板31において、大当り遊技中の各種パラメータ(大入賞口開放回数、大入賞口入賞球数等)はバックアップRAMに保存されている。従って、遊技者にとっての遊技状態も停電前の状態に戻るので、遊技者に不利益が与えられるということはない。

図23(C)は、遊技待ちの状態に停電が生じた後に復旧した場合の例を示す。この場合には、電源復旧時に、主基板31から左右中の停止図柄を示す表示制御コマンドと確定コマンドとが送出される(図22におけるステップS65,S66)。表示制御用CPU101は、左右中の停止図柄を示す表示制御コマンドにもとづいて、停電発生直前に表示されていた左右中図柄を可変表示部9に表示することができる。すなわち、表示状態を停電発生前の状態に戻すことができる。

次に、表示制御用CPU101の動作を説明する。

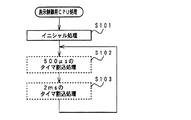

図24は、表示制御基板80における表示制御用CPU101の動作を示すフローチャートである。表示制御用CPU101は、出力ポートやワークエリアの初期化およびタイマセット等のイニシャル処理を行った後に(ステップS101)、ループ状態に入る。イニシャル処理において、500μsおよび2ms毎にタイマ割込が発生するようなタイマ設定がなされている。よって、ループ状態では、500μsのタイマ割込がかかると500μsタイマ割込処理が行われ(ステップS102)、2msのタイマ割込がかかると2msタイマ割込処理が行われる(ステップS103)。なお、500μsタイマ割込処理では表示制御コマンド受信処理が行われ、2msタイマ割込処理では表示制御処理が実行される。

図25は、2msのタイマ割込処理を示すフローチャートである。2msのタイマ割込がかかると、表示制御用CPU101は、次の2ms割込がかかるようにタイマを起動する等のイニシャル処理を行った後に(ステップS111)、表示制御プロセス処理(ステップS112)を実行する。

図26は、500μsタイマ割込処理で実行される表示制御コマンド読込処理を示すフローチャートである。表示制御コマンド読込処理において、表示制御用CPU101は、ストローブ信号(INT信号)に割り当てられている入力ポートのビット7を読み込む。そして、ビット7がオン(ローレベル)しているか否か確認する(ステップS501)。オンしていれば、表示制御コマンドデータの入力に割り当てられている入力ポートから表示制御コマンドデータを読み取る(ステップS502)。なお、上述したように、INT信号は、主基板31のCPU56が新たな表示制御コマンドデータを出力したときにローレベルとされる。

INT信号がオフしている場合には、表示通信カウンタをクリアする(ステップS506)。表示通信カウンタは、INT信号がオンしているときの表示制御コマンドデータ受信回数をカウントするために用いられる。

INT信号がオンしている場合には、受信した表示制御コマンドデータが直前に(500μs前)受信したコマンドデータと同じか否か確認する(ステップS503)。同じでない場合には、表示通信カウンタをクリアする(ステップS506)。同じであった場合には、表示通信カウンタが所定の最大値(MAX)に達しているか否か確認する(ステップS504)。

最大値に達していない場合には、表示通信カウンタの値を+1する(ステップS505)。ここで、最大値とは、表示制御コマンドデータを確実に受信したと判定する値(この例では3)よりも大きい値であり、例えば、4ms間での受信回数をカウントする等の目的で用いられる。

次いで、表示制御用CPU101は、表示通信カウンタ後が「3」になったか否か確認する(ステップS507)。「3」になっている場合には、受信したデータを受信コマンド格納エリアに格納する(ステップS509)。そして、受信したデータをワークエリアに格納する(ステップS510)。なお、ワークエリアに格納されたデータは、次の割込処理において、ステップS503において用いられる。

以上のように、この実施の形態では、表示制御用CPU101は、例えば3回連続して同一の表示制御コマンドデータを受信すると、確かに表示制御コマンドを受信したとして、通信終了フラグをセットする。そして、通信終了フラグがセットされると、受信コマンド格納エリアに格納された表示制御コマンドにもとづいて図柄の変動および背景・キャラクタの表示切替等の処理が行われる。

図27は、図25に示されたタイマ割込処理における表示制御プロセス処理(ステップS112)を示すフローチャートである。表示制御プロセス処理では、表示制御プロセスフラグの値に応じてステップS720〜S870のうちのいずれかの処理が行われる。各処理において、以下のような処理が実行される。

表示制御コマンド受信待ち処理(ステップS720):通信終了フラグのオンに応じて受信コマンドが設定されているワークエリアの内容を読み出して、変動時間を特定可能な表示制御コマンド等を受信したか否か確認する。

リーチ動作設定処理(ステップS750):受信した変動時間を特定可能な表示制御コマンド(例えばリーチ種類を指定するコマンド)に対応した複数の変動態様のうちのいずれのパターンを使用するのかを決定する。

全図柄変動開始処理(ステップS780):左右中図柄の変動が開始されるように制御する。

図柄変動中処理(ステップS810):変動パターンを構成する各変動状態(変動速度や背景、キャラクタ)の切替タイミングを制御するとともに、主基板31から確定コマンドが送出されたか否かを監視する。また、左右図柄の停止制御を行う。

全図柄停止待ち設定処理(ステップS840):変動時間の終了時に、全図柄停止を指示する表示制御コマンドを受信していたら、図柄の変動を停止し最終停止図柄(確定図柄)を表示する制御を行う。

大当り中処理(ステップS870):変動時間の終了後、大当り報知表示、大当たり遊技中のラウンド表示、確変大当り表示または通常大当り表示の制御を行う。

図28は、表示制御コマンド受信待ち処理(ステップS720)の一例を示すフローチャートである。表示制御コマンド受信待ち処理において、表示制御用CPU101は、変動時間を特定可能な表示制御コマンドを受信したか否か確認する(ステップS751)。受信していれば、可変表示部9のエラー表示を消去するとともに(ステップS752)、表示制御プロセスフラグの値をリーチ動作選択処理に対応した値に設定する(ステップS753)。よって、以後、リーチ動作選択処理が実行される。

また、表示制御用CPU101は、左右中の停止図柄を示す表示制御コマンドを受信した場合には(ステップS754)、左右中の停止図柄を示す情報を記憶する(ステップS755)。エラー表示コマンドを受信した場合には(ステップS756)、可変表示部9にエラー表示を行う(ステップS757)。また、確定コマンドを受信した場合には(ステップS758)、記憶されている停止図柄を可変表示部9に表示する(ステップS759)。

大当り遊技中に送出されるコマンドを受信した場合には(ステップS760)、可変表示部9のエラー表示を消去するとともに(ステップS761)、表示制御プロセスフラグの値を大当り中処理に対応した値に設定する(ステップS762)。よって、以後、大当り中処が実行される。大当り遊技中に送出されるコマンドとは、例えば、ラウンド回数を示すコマンドや大入賞口入賞個数を示すコマンドである。

また、デモ画面コマンドを受信した場合にも(ステップS763)、表示制御用CPU101は、エラー表示を消去する(ステップS764)。なお、表示制御用CPU101は、デモ画面コマンドを受信した場合には、エラー表示を消去するとともに、可変表示部9にデモ画面を表示する。

表示制御用CPU101は、通常の電源投入時にも停電からの復旧時にも同じ処理を行うので、停電からの復旧時に、表示制御プロセスフラグは初期化され、表示制御プロセス処理は表示制御コマンド受信待ちの状態となる。図23(A)に示されたように、図柄変動中に停電が発生し停電から復旧した場合には、主基板31からエラー表示コマンドおよび左右中の停止図柄を示す表示制御コマンドが送出される。そして、変動時間が経過すると、確定コマンドが送出される。

表示制御基板80において、表示制御用CPU101は、図28に示されたステップS754で左右中の停止図柄を示す表示制御コマンドを受信したことを確認すると停止図柄を示す情報を記憶し、ステップS756でエラー表示コマンドを受信したことを確認するとエラー表示を行う。そして、ステップS758で確定コマンドを受信したことを確認すると記憶されている停止図柄を表示する。ここでは、エラー表示の消去は行われない。エラー表示は、変動時間を特定可能な表示制御コマンド、大当り遊技中のコマンド等を受信したときに消去される(ステップS752,S761)。

従って、停電が発生し遊技状態が回復した場合には、可変表示部9においてしばらくの間、エラー表示が継続表示される。よって、遊技者等は、停電が発生し遊技状態が回復したことを容易に認識することができる。そして、停電発生前の変動開始時に主基板31から受信した左右中図柄の停止図柄に関する情報は、停電発生によって表示制御基板80において消去されているが、停電からの復旧時にあらためて主基板31から左右中図柄の停止図柄を示すコマンドが送出されるので、所定のタイミングで、正規の左右中停止図柄を可変表示部9に表示することができる。

大当り遊技中に停電が発生し停電から復旧した場合には、図23(B)に示されたように、主基板31から左右中の停止図柄を示す表示制御コマンドおよび確定コマンドが送出される。そして、主基板31における遊技制御手段では、遊技状態が停電発生時の状態に回復するので、大当り遊技中の制御が再開され大当り遊技に関わる表示制御コマンドが送出される。表示制御基板80において、表示制御用CPU101は、大当り遊技に関わる表示制御コマンドを受信すると、表示制御プロセスフラグの値を大当り中処理の値にして、制御状態を大当り中処理に戻す(ステップS762)。なお、停電復旧時に左右中の停止図柄を示す表示制御コマンドが送出されるので、大当り遊技終了時に、表示制御用CPU101は、正規の左右中停止図柄を可変表示部9に表示することができる。

そして、遊技待ち状態で停電が発生し停電から復旧した場合には、図23(C)に示されたように、主基板31から左右中の停止図柄を示す表示制御コマンドおよび確定コマンドが送出される。表示制御用CPU101は、ステップS754で左右中の停止図柄を示す表示制御コマンドを受信したことを確認すると停止図柄を示す情報を記憶し、ステップS758で確定コマンドを受信したことを確認すると停止図柄を可変表示部9に表示する。このように、停電復旧時に左右中の停止図柄を示す表示制御コマンドが送出されるので、表示制御用CPU101は、正規の左右中停止図柄を可変表示部9に表示することができる。

図29は、上述した制御による可変表示部9の表示状態の一例を示す説明図である。図29(A)に示すように図柄が変動していたときに停電が発生しその後復旧すると、可変表示部9には、図29(B)に示すように、エラー表示がなされる。そして、変動期間が終了して主基板31から確定コマンドを受信すると、停止図柄を表示する。その後、この例では、次回の変動開始のための変動開始を示すコマンドを受信するとエラー表示が消去される。

次に、賞球制御手段の停電発生時の動作について説明する。

図30は、電源監視および電源バックアップのための賞球制御用CPU371周りの一構成例を示すブロック図である。図30に示すように、電源基板910に搭載されている第1の電源監視回路(第1の電源監視手段)からの電圧低下信号が、賞球制御用CPU371の割込端子(IRQ端子)に入力されている。従って、賞球制御用CPU371は、割込処理によって電源断の発生を確認することができる。

賞球制御用CPU371等の駆動電源である+5V電源から電力が供給されていない間、賞球制御用CPU371の内蔵RAMの少なくとも一部は、電源基板910から供給されるバックアップ電源がバックアップ端子に接続されることによってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、初期リセット回路935からリセット信号が発せられるので、賞球制御用CPU371は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップされているので、停電等からの復旧時には停電発生時の遊技状態に復帰することができる。

図30に示す構成では、賞球制御基板37には、第2の電源監視回路933が搭載されている。この例では、第2の電源監視回路933において、電源監視用IC934が、電源基板910の第1の電源監視回路が監視する電源電圧と等しい電圧である+30V電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。第2の電源監視回路933が設けられている場合には、第2の電源監視回路933の検出電圧(電圧低下信号を出力することになる電圧)を、電源基板910に搭載されている第1の電源監視回路の検出電圧よりも低くする。

第2の電源監視回路933からの電圧低下信号は、初期リセット回路935からの初期リセット信号と論理和をとられた後に、賞球制御用CPU371のリセット端子に入力される。従って、賞球制御用CPU371は、初期リセット回路935からの初期リセット信号がローレベルを呈しているとき、または、第2の電源監視回路933からの電圧低下信号がローレベルを呈しているときに、リセット状態(非動作状態)になる。

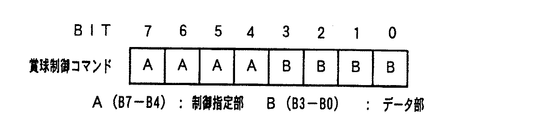

図31は、主基板31から賞球制御基板37に送信される賞球制御コマンドのビット構成の一例を示す説明図である。図31に示すように、1バイト中の上位4ビットが制御指定部として使用され、下位4ビットが賞球数を示す領域として用いられる。

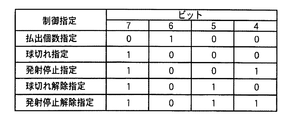

図32に示すように、制御指定部において、ビット7,6,5,4が「0,1,0,0」であれば払出個数指定コマンドであることを示し、「0,1,0,1」であれば払出指定コマンドであることを示す。払出個数指定コマンドは、主基板31のCPU56が入賞を検出すると直ちに賞球制御基板37に送出される。

ビット7,6,5,4が「1,0,0,0」である球切れ指定コマンドは、補給玉がなくなったことが検出されたときに主基板31から送信される。また、ビット7,6,5,4が「1,0,0,1」である発射停止指定コマンドは、余剰玉受皿4が満タンになって満タンスイッチ48がオンしたとき(満タン状態フラグがオンしたとき)に主基板31から送信される。

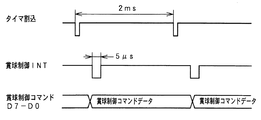

賞球制御コマンドは、主基板31から賞球制御基板37に、1バイト(8ビット:賞球制御コマンドD7〜D0)のデータとして出力される。賞球制御コマンドD7〜D0は正論理で出力される。また、賞球制御コマンドD7〜D0が出力されたときには、負論理の賞球制御INT信号が出力される。

この実施の形態では、図33に示すように、主基板31から賞球制御コマンドD7〜D0が出力されるときに、賞球制御INT信号が5μs以上ローレベルになる。賞球制御INT信号は、賞球制御基板37において、賞球制御用CPU371の割込端子に接続されている。よって、賞球制御用CPU371は、割り込みがあると、賞球制御コマンドD7〜D0が主基板31から送出されたことを認識でき、割込処理において賞球制御コマンド受信処理を行う。

なお、図31に示されたコマンド構成は一例であって、他の構成にしてもよい。例えば、1バイト中の上位下位を、図31に示された構成とは逆にしてもよい。

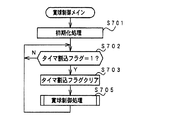

図34は、賞球制御用CPU371のメイン処理を示すフローチャートである。メイン処理では、賞球制御用CPU371は、まず、RAM領域をクリアする等の初期値設定処理を行う(ステップS701)。なお、内蔵RAMの電源バックアップされたRAM領域(バックアップRAM領域)にデータが設定されている場合には、それらの領域のクリア処理はなされない。その後、この実施の形態では、賞球制御用CPU371は、タイマ割込フラグの監視(ステップS702)の確認を行うループ処理に移行する。

ステップS701の初期化処理では、後述する総合個数記憶の値が0でない場合には、非バックアップRAM領域をクリアする。そして、賞球再開のための設定を行う。例えば、賞球中処理中フラグのセット等を行う。なお、バックアップRAM領域であっても、賞球個数に関わらない領域であるならば、それらのアドレスを指定してクリアするようにしてもよい。さらに、それら処理の他に、2ms毎に定期的にタイマ割込がかかるように賞球制御用CPU371に設けられているタイマレジスタの初期設定(タイムアウトが2msであることと繰り返しタイマが動作する設定)が行われる。すなわち、タイマ割込を能動化する処理と、タイマ割込インタバルを設定する処理とが実行される。

従って、この実施の形態では、賞球制御用CPU371の内部タイマが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、図35に示すように、タイマ割込が発生すると、賞球制御用CPU371は、タイマ割込フラグをセットする(ステップS711)。

賞球制御用CPU371は、ステップS702において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS703)、賞球制御処理を実行する(ステップS705)。以上の制御によって、この実施の形態では、賞球制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、賞球制御処理はメイン処理において実行されるが、タイマ割込処理で賞球制御処理を実行してもよい。

図36は、賞球制御用CPU371が内蔵するRAMの使用例を示す説明図である。この例では、バックアップRAM領域に総合個数記憶(例えば2バイト)が形成されている。総合個数記憶は、主基板31の側から指示された払出個数の総数を記憶するものである。

図37は、割込処理による賞球制御コマンド受信処理を示すフローチャートである。主基板31からの賞球制御INT信号は賞球制御用CPU371の割込端子に入力されている。よって、主基板31からの賞球制御INT信号がオン状態になると、賞球制御用CPU371に割込がかかり、図37に示す賞球制御コマンドの受信処理が開始される。

賞球制御コマンドの受信処理において、賞球制御用CPU371は、まず、賞球制御コマンドデータの入力に割り当てられている入力ポートから1バイトのデータを読み込む(ステップS852)。読み込んだデータが払出個数指示コマンドであれば(ステップS853)、払出個数指示コマンドで指示された個数を総合個数記憶に加算する(ステップS855)。そうでなければ、通信終了フラグをセットする(ステップS854)。なお、通信終了フラグは、この例では、払出個数指示コマンド以外のコマンドを受信したことを示すフラグである。

以上のように、賞球制御基板37に搭載された賞球制御用CPU371は、主基板31のCPU56から送られた払出個数指示コマンドに含まれる賞球数をバックアップRAM領域(総合個数記憶)に記憶する。

図38は、賞球制御処理(ステップS711)を示すフローチャートである。賞球制御処理において、賞球制御用CPU371は、総合個数記憶が0でないか否かの確認を行う(ステップS511)。総合個数記憶が0でなければ、賞球制御用CPU371は、賞球払出処理を行う(ステップS512)。賞球払出処理では、払出モータ289がオンしていなければオンするとともに、賞球カウントスイッチ301Aの検出出力によって遊技球の払出がなされたか否かの確認を行う。そして、1個の払出が行われたことを確認したら(ステップS513)、総合個数記憶の値を−1する(ステップS514)。また、総合個数記憶の値が0になったら(ステップS515)、払出モータ289をオフする(ステップS516)。

総合個数記憶の内容は、遊技機の電源が断しても、所定期間電源基板910のバックアップ電源によって保存される。従って、所定期間中に電源が回復すると、賞球制御用CPU371は、総合個数記憶の内容にもとづいて賞球払出処理を継続することができる。

賞球制御用CPU371は、電源投入時に、バックアップRAM領域のデータを確認するだけで、通常の初期設定処理を行うのか賞球中の状態を復元するのか決定できる。すなわち、簡単な判断によって、未払出賞球について賞球処理再開を行うことができる。

なお、賞球制御用CPU371は、主基板31から指示された賞球個数を総合個数記憶で総数として管理したが、賞球数毎(例えば15個、10個、6個)に管理してもよい。例えば、賞球数毎に対応した個数カウンタを設け、払出個数指定コマンドを受信すると、そのコマンドで指定された個数に対応する個数カウンタを+1する。そして、賞球数毎の賞球払出が終了すると、対応する個数カウンタを−1する。その場合にも、各個数カウンタはバックアップRAM領域に形成される。よって、遊技機の電源が断しても、所定期間中に電源が回復すれば、賞球制御用CPU371は、各個数カウンタの内容にもとづいて賞球払出処理を継続することができる。

図39は、賞球制御用CPU371が第1の電源監視手段からの割込に応じて実行される停電発生割込処理を示すフローチャートである。電源基板901の電源監視用IC902が電源電圧の低下を検出すると電圧低下信号が電圧低下を示す状態となり、停電発生割込処理が開始される。停電発生割込処理において、賞球制御用CPU371は、割込禁止に設定し(ステップS801)、RAMアクセス禁止状態に設定して(ステップS802)、ホールト命令(HALT命令)を発行する(ステップS803)。

すなわち、CPU自身を、リセット解除または割込発生以外では動作しない状態にする。従って、図30に示された電源監視用IC934からのリセット信号によって外部から動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実に賞球制御用CPU371は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

図40は、賞球制御用CPU371が電源投入時に実行する初期化処理(ステップS701)の一部を示すフローチャートである。電源が投入され、または、電源が復旧したときには、賞球制御用CPU371は、まず、バックアップRAM領域に形成されている総合個数記憶の値が0でないかどうか確認する(ステップS901)。0である場合には、前回の電源オフ時に未払出賞球はなかったことになるので、通常の初期設定処理を行う。すなわち、レジスタおよび全RAM領域をクリアして(ステップS903)、スタックポインタの初期設定を行う(ステップS904)。

総合個数記憶の値が0でない場合には、アドレスを指定してレジスタと非バックアップRAM領域をクリアする(ステップS905)。そして、賞球再開のための設定を行う。例えば、賞球中処理中フラグのセット等を行う(ステップS906)。なお、バックアップRAM領域であっても、賞球個数に関わらない領域であるならば、それらのアドレスを指定してクリアするようにしてもよい。

このように、賞球制御用CPU371は、電源投入時に、バックアップRAM領域のデータを確認するだけで、通常の初期設定処理を行うのか賞球中の状態を復元するのか決定できる。すなわち、簡単な判断によって、未払出賞球について賞球処理再開を行うことができる。

なお、この実施の形態では、賞球制御用CPU371は、マスク可能外部割込端子(IRQ端子)電源基板からの第1の電圧低下信号(第1の電源監視手段からの電圧低下信号)を検知したが、第1の電圧低下信号をマスク不能割込割込端子(NMI端子)に導入してもよい。その場合には、NMI処理によって図39に示された停電発生処理が実行される。また、入力ポートを介して第1の電圧低下信号を検知してもよい。その場合には、賞球制御用CPU371が実行するメイン処理において、入力ポートの監視が行われる。

上記の実施の形態では、電源基板910からの第1の電圧低下信号が主基板31および賞球制御基板37の割込端子に入力されたが、図41に示すように、賞球制御基板37において、割込端子の前に遅延回路936を設けてもよい。そのように構成した場合には、主基板31のCPU56が、第1の電源監視手段が電圧低下を検出したことを認識するタイミングは、賞球制御基板37の賞球制御用CPU371が認識するタイミングよりも早くなる。

CPU56および賞球制御用CPU371はそれぞれ第1の電圧低下信号に応じて電源断時処理を行うのであるが、CPU56は、賞球制御用CPU371よりも早く電源断時処理を開始する。すなわち、賞球制御用CPU371による賞球制御処理が停止するよりも早くCPU56による遊技制御処理が停止する。すると、遊技制御処理中に送出された賞球制御コマンドは、電源断が生ずるときであっても、確実に賞球制御用CPU371で受信される。賞球制御用CPU371は受信した賞球制御コマンドにもとづく賞球数をバックアップRAM領域に保存するので、賞球数は、停電中でも保持され停電復旧後に処理される。よって、遅延回路936が設けられている場合には、遊技制御手段が検出した入賞にもとづく賞球払出がより確実になされる。よって、遊技者に対して不利益が与えられることをより効果的に防止できる。

また、遅延回路936を設けず、第1の電圧低下信号をソフトウェア的に遅延させてもよい。例えば、賞球制御用CPU371は、第1の電圧低下信号にもとづく割込が発生すると直ちに割込処理を開始するのではなく、タイマをスタートさせてメイン処理を続行する。そして、タイマがタイムアウトしたら、図39に示されたステップS801〜S803の処理を実行する。

なお、上記の実施の形態では、記憶手段としてRAMを用いた場合を示したが、記憶手段として、電気的に書き換えが可能な記憶手段であればRAM以外のものを用いてもよい。

さらに、ここでは、遊技制御手段以外の他の遊技装置制御手段として賞球制御手段を例示したが、表示制御手段、音制御手段およびランプ制御手段についても、第2の電源監視手段を設けてもよい。

上記の各実施の形態のパチンコ遊技機1は、始動入賞にもとづいて可変表示部9に可変表示される特別図柄の停止図柄が所定の図柄の組み合わせになると所定の遊技価値が遊技者に付与可能になる第1種パチンコ遊技機であったが、始動入賞にもとづいて開放する電動役物の所定領域への入賞があると所定の遊技価値が遊技者に付与可能になる第2種パチンコ遊技機や、始動入賞にもとづいて可変表示される図柄の停止図柄が所定の図柄の組み合わせになると開放する所定の電動役物への入賞があると所定の権利が発生または継続する第3種パチンコ遊技機であっても、本発明を適用できる。