以下図面について、本発明の一実施の形態を詳述する。

(1)CBM処理の内容

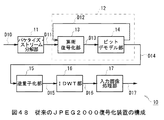

本願発明は上述したJPEG2000規格に準拠した符号化装置1のビットモデル部6(図46)や復号化装置10のビットデモデル部13(図48)において行われるCBM処理に関するものである。そこで、まずCBM処理の具体的処理内容について詳説する。

(1−1)1コードブロックとコードブロックサイズ

図46について上述したように、例えばJPEG2000規格に準拠した符号化装置1の量子化部4では、ウェーブレット係数を量子化したものをコードブロックと呼ばれる単位で切り出してビットモデル部6に与える。そしてビットモデル部6では、図1に示すように、このコードブロック20を単位としてCBM処理を行い、シンボルとコンテクストを生成することになる。

ここでコードブロック20のサイズは、図2に示すように、大枠が定められている。従って、コードブロック20のサイズは、エンコード時にこのルールに従って選択することになる。

この場合、コードブロック20は基本的にはサブバンドの左上境界から始まって位置付けられるので、図3に示すように、画像サイズとコードブロックサイズとの関係によっては不整合を生じる。このようにエンコード時に決定したものを通常サイズと呼び、不整合が生じたものを例外サイズと呼ぶ。

例外サイズは必ず通常サイズよりも小さいものであり、基本的に格納しているデータの量が異なるだけであるので、例外サイズについて触れるのはここだけに留め、以下においては通常サイズのコードブロック20を取り上げて説明する。

(1−2)ビットプレーン

上述のように、CBM処理ではコードブロック20を単位として処理(モデル化、シンボル・コンテクスト出力)を行うわけであるが、この処理はコードブロック20のデータをビットプレーンに分けて順に行われる。ビットプレーンはその名のとおり、『bit(0/1)』を表現するものが集まった平面である。

図4に示すように、コードブロック20に分割されてきたデータは『Sign-Magnitude表現』、すなわち正負符号と絶対値による数値表現により表されている。最上位のビットプレーン22に各画素の正負符号が格納され、これを正負符号ビットプレーン22Sと呼ぶ。そしてこれよりも下位のビットプレーン22に各画素の絶対値データがビットごとに順に格納される。

ここで仮に各画素のデータが16ビットで表現されているとすると、コードブロックデータ20は、各画素の最上位ビット(bit15)が集まって構成するプレーンから最下位ビット(bit0)が集まって構成するプレーンまでの16枚のビットプレーン22に分割されることになる。

上位のビットプレーン22から順に眺めていくと、上述のように最上位ビットが集まって構成するビットプレーン22が正負符号ビットプレーン22Sであり、各画素の正負符号が格納される。

各画素のその次のビットが集まって構成するビットプレーン22から最下位ビットが集まって構成するビットプレーン22までの合計15枚の各ビットプレーン22に、各画素のデータの絶対値がビットごとに分割されて格納されていることになる。この場合、統計的に上位のいくつかのビットプレーン22では全てのビット値が0であるということが多い。このようなものをゼロビットプレーン220と呼ぶ。

かかる15枚のビットプレーン22を上から順に見ていくと、やがて初めてゼロビットプレーン220ではないビットプレーン22にたどりつく。それをトップビットプレーン22Tと呼び、ここではそれが各画素の最下位ビット(bit0)から数えて10番目のビット(bit9)が集まって構成しているビットプレーン22だったとする。これよりも下位のビットプレーン22(それぞれ各画素の9番目以下のビットが集まって構成される各ビットプレーン22)は、データがあったり無かったりしてもここでは特に分類はしない。

ここまでの話しをまとめると、この例では、各画素の最上位ビット(bit15)が集まって構成しているものが正負符号ビットプレーン22S、各画素の次のビット(bit14)が集まって構成しているビットプレーン22から11番目のビット(bit10)が集まって構成しているビットプレーン22がゼロビットプレーン220(10枚)、10番目のビット(bit9)が集まって構成しているビットプレーン22がトップビットプレーン22T、9番目(bit8)のビットが集まって構成しているビットプレーン22から最下位ビットが集まって構成しているビットプレーン22までが残りの処理すべきビットプレーン22(9枚)というビットプレーン構成となっている。

このようなビットプレーン構成のコードブロック20に対し、上述のビットモデル部6(図46)やビットデモデル部13(図48)では次のようにCBM処理を行う。

1. 符号ビットプレーン22Sに対する処理は、後回しにする。

2. ゼロビットプレーン220に対してはCBM処理を行わない。

3. トップビットプレーン22Tで初めてCBM処理を行う。このCBM処理は“Clean-up Pass”(以下、これをCUパスと呼ぶ)と呼ばれる。

4. 残りの処理すべきビットプレーン22に対し、上位のビットプレーン22から順に、“Significance Propagation Pass”(以下、これをSPパスと呼ぶ)、“Magnitude

Refinement Pass”(以下、これをMRパスと呼ぶ)及びCUパスをビットプレーン22ごとにそれぞれ行う。

なお、SPパス、MRパス及びCUパスの詳細については後述する。

(1−3)ビットプレーン内スキャン順序

コードブロック20内の各ビットプレーン22に対するアクセス順序はこれまでに説明した通りであるが、ビットプレーン22内において、各画素のデータにどういう順序でアクセスするかを示したのが図5である。この図5では、ビットプレーン22として8画素×8画素のものを例示している。

ビットプレーン22は、縦4画素ずつ横方向に区切った場合の各行であるストライプ23に分けられる。ストライプ23中の縦1列をストライプカラム23Aと呼ぶ。ビットプレーン22の最上段のストライプ23における左端のストライプカラム23Aから処理を始め、1つのストライプカラム23Aを処理したら隣のストライプカラム23Aに移り、それをそのストライプ23中繰り返す。1ストライプ23の処理が完了したら下段のストライプ23に移動し、ビットプレーン22内の全ての画素を処理し終えるまでこれを繰り返すというのがビットプレーン22内でのスキャン順序(以下、これをビットプレーン内スキャン順序と呼ぶ)である。

さらに、ビットプレーン22内におけるスキャンと3つのパス(SPパス、MRパス及びCUパス)との関係について以下に説明する。

上述のようにトップビットプレーン22Tに対してCUパスのみを行い、それよりも下位のビットプレーン22に対しては、SPパス、MRパス及びCUパスの3つのパスを処理する。これとビットプレーン22内におけるスキャンとの関係を図6〜図9に示す。

まず新たにビットプレーン22をCBM処理しようという場合において、まだひとつのデータも処理されておらずこれから処理を開始しようとしている状態が図6である。SPパスの処理が必要な画素に対して行われ、このSPパス処理の終了した状態が図7となる。SPパスはビットプレーン内スキャン順序を守って行われる。

次のMRパスは、SPパスで処理した画素は避け、該当する画素に対してのみ処理を行う。このMRパスの終了した状態が図8である。このMRパスにおいてもビットプレーン内スキャン順序は守る。

さらに未処理で残った画素に対してもやはりビットプレーン内スキャン順序を守りながらCUパスで処理を行う。このCUパスの完了した状態が図9である。この結果、すべての画素が処理済みになったので、このビットプレーン22のビットモデル化は完了したことになる。

なお『トップビットプレーン22T』については、CUパスの処理のみを全ての画素に対して行う。

(1−4)“Significance”について

次に各コーディング・パス(SPパス、MRパス及びCUパス)の説明に入る前に、“Significance”という状態量について説明する。“Significance”とは該当画素が『有意である(Significant)/有意でない(Insignificant)』ということを意味する。

『有意である(Significant)』とは、「これまでのCBM処理によって該当画素が0ではないとわかっている状態」のことをいい、換言すれば「値が『1』である画素(ビット)をすでにモデル化(符号化)し終えた」ということを意味する。

また『有意でない(Insignificant)』とは、「該当画素の画素値が0であるか、又は0の可能性がある状態」のことをいい、換言すれば「(今のところ)値が『1』である画素(ビット)を未だモデル化(符号化)し終えていない」ということを意味する。

さらに『該当画素』とは、ビットプレーン22上のある着目している画素のことをいう。

なお、“Significance”はコードブロック20(図1)の全体に渡って更新されながら記憶保持される。従ってこれまで例示した8画素×8画素のビットプレーン22が16枚からなるコードブロック20においていえば、64画素(8画素×8画素)分の“Significance”状態量をコードブロック20に渡って記憶保持することになる。

CBM処理では、時間的にトップビットプレーン22Tから順に、ビットプレーン22内ではビットプレーン内スキャン順序に従って3つのコーディング・パス(トップビットプレーン22TではCUパスのみ)を処理(モデル化、シンボル・コンテクスト出力)するが、ある画素の係数(正確にはウェーブレット変換係数を量子化したもの)の状態をこの“Significance”で表していることになる。

因みに、CBM処理が行われていないコードブロック20においては、すべてのSIGプレーン上の値が“Insignificant”で始まり、各ビットプレーン22を処理していく過程において該当するものが“Significant”に転じていく。一度“Significant”になったものがCBM処理の途中で“Insignificant”に戻ることはない。

(1−5)3つのコーディング・パス

次に、SLパス(Significance Propagation Pass)、MRパス(Magnitude Refinement Pass )、CUパス(Clean−up Pass)について説明する。

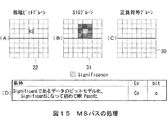

この3つのコーディング・パスに従ってビットモデル化の処理を行う場合には、図10に示すように、これから処理しようとするビットプレーン22(以下、これを処理ビットプレーン22と呼ぶ)以外に、正負符号ビットプレーン22S(図4)のデータを記憶保持するプレーン(以下、これを正負符号プレーンと呼ぶ)30と、“Significance”を記録するプレーン(以下、これをSIGプレーンと呼ぶ31)と、最初の“Refinement pass”であるか否か示すプレーン(以下、これをREFプレーンと呼ぶ)32と、処理ビットプレーン中で着目ビットが処理済みであるか否かを表すプレーン(以下、これをDONEプレーンと呼ぶ)33とを状態量の記録用RAMとして用意するのが一般的である。

これら正負符号プレーン30、SIGプレーン31、REFプレーン32及びDONEプレーン33は、処理ビットプレーン22と同じ大きさを持つ(これまでの例では8画素×8画素)プレーンである。

この場合、正負符号プレーン30は、コードブロック22を処理している間はその値が変化せず記憶保持される。SIGプレーン31は、SPパス、CUパスで値を変化させられる可能性がある。REFプレーン32は、MRパスで値を変化させられる可能性がある。DONEプレーン33は、各コーディング・パスの処理が完了した画素に対応させて処理済のフラグを立てる状態量で、その処理ビットプレーン22に対する処理が完了した段階でリセットされる。

(1−5−1)SPパスの処理

SPパスは、トップビットプレーン22T(図4)を除く処理ビットプレーン22において、最初に実施されるコーディング・パスである。このSPパスは、処理ビットプレーン22上の該当画素と同じ座標位置にあるSIGプレーン31上のデータを参照しながら処理が進められる。

すなわち図11に示すように、例えば処理ビットプレーン22上における該当画素の座標が(2,1)であったとき(図11(B))、SIGプレーン31上のこの該当画素に対応するビット(図11(C)における座標(2,1)のビット)と、その8近傍のビットとを合わせた(1,0)、(2,0)、(3,0)、(1,1)、(2,1)、(3,1)、(1,2)、(2,2)、(3,2)の各座標位置のデータを参照することになる。なお参照する8近傍のビットうち、処理ビットプレーン22の外側に位置してしまったビットはすべて“Insignificant”とされる。

SPパスの処理を行うに際しては、上述したビットプレーン内スキャン順序に従って、処理ビットプレーン22の左上を起点に、当該処理ビットプレーン22上の画素ごとに当該処理を行うことができるかどうかを調べる。具体的には、「『該当画素が“Significant”ではない(Insignificant)』かつ『該当画素の8近傍に“Significant”である画素が少なくともひとつ存在する』」という条件を満たすか否かを調査する。

そしてこの条件を満たすときにその該当画素に対してSPパス

の処理を行い、満たさないときにはSPパスの処理を行わずにビットプレーン内スキャン順序に従って次の画素を評価する。

次に、SPパスの処理に入った場合の流れを説明する。

SPパスに入った場合、シンボルとして図12(A)に示す処理ビットプレーン22の該当画素の値(0/1)を出力する。同時に、処理ビットプレーン22上の該当画素と対応する図12(B)に示すSIGプレーン31上のビットを囲む8近傍のビットのうち、“Significant”であるビットの数を数え、図13に示すルールに従ってコンテクストを出力する。

なおこの図13において、『ΣH』、『ΣV』、『ΣD』及び『ΣH+ΣV』は、それぞれ処理ビットプレーン22上の該当画素と対応するSIGプレーン31上のビットの8近傍における左右2つのビット、上下2つのビット、斜め4つのビット、又は上下左右4つのビットうちの“Significant”であるビットの合計値を表す。

また『CX』は、そのような状態のときのコンテクストを表す。例えば、その処理ビットプレーン22を含むコードブロック20(図1)が画像のLL成分(図47)であり、このとき『ΣH』、『ΣV』及び『ΣD』がそれぞれ0、0及び1であった場合のコンテクストは1となり、『ΣH』、『ΣV』及び『ΣD』がそれぞれ1、0及び0であった場合のコンテクストは5となる。

シンボルの値が0である場合は、その該当画素に対するSPパスの処理がこれで完了し、この該当画素とDONEプレーン33(図10)上の同じ座標位置にビットモデル化が完了した旨のフラグを立てる。

これに対してシンボルの値が1(すなわち該当画素の値が1)だった場合は、この該当画素は初めて1が現れた画素であることになり、いままで“Insignificant”であったが、ここで初めて“Significant”に転じ、SIGプレーン31上の同じ座標位置にフラグを立てる。このときREFプレーン32(図10)上の同座標位置にもフラグを立てる。これは次のMRパスのための処理である。

さらに、その該当画素と同じ座標位置にある正負符号プレーン30上のビット(すなわち該当画素に対応する正負符号)の上下左右4近傍のビットを参照し、図14に示すルールに従ってコンテクストを出力する。

またこれと同時にXOR信号も出力され、これと当該コンテクストの排他的論理和を取ったものを、正負符号のシンボルとして出力することにより該当画素に対応する正負符号のビットモデル化を完了し、この段階でこの該当画素についてのSPパスの処理も完了となる。このときDONEプレーン33(図10)上の該当画素と同じ座標位置にビットモデル化が完了したことを表すフラグを立てる。

なお、上述のことからも明らかなように、スキャン順序によっては、SPパスによって“Significant”に新たに転じたものが他の(近傍)画素のSIGプレーン31上の8近傍参照時に影響を与えることがある。

(1−5−2)MRパスの処理

MRパスは、トップビットプレーン22T(図4)を除く処理ビットプレーン22について、SPパスに続いて実施されるコーディング・パスである。図15に処理の概略を示す。

このMRパスの処理を行うに際しては、上述したビットプレーン内スキャン順序に従って、処理ビットプレーン22の左上を起点に、当該処理を行うことができるかどうかを各画素について調べる。具体的には、「『未処理(DONEプレーン33上の該当画素と同じ座標位置にフラグが立っていない)の処理ビットプレーン22上の該当画素』であって『その該当画素が“Significant”である』」という条件を満たすか否かを調査する。

そしてこの条件を満たすときにその該当画素に対してMRパスの処理を行い、満たさないときにはMRパスの処理を行わずに上述のビットプレーン内スキャン順序に従って処理ビットプレーン22上の次の画素を評価する。

そしてMRパスの処理に入った場合、該当画素とSIGプレーン31上の同じ座標位置にあるビットの8近傍のビットを参照し、図16に示すルールに従ってコンテクストを出力し、同時に該当画素の値(0/1)をシンボル(図16において『X』)として出力する。

図16において、『該当画素を最初に本パス(MRパス)で符号化』しているのかどうかという状態は、REFプレーン32(図10)の該当画素と同じ座標位置のフラグを参照する。このフラグが立っていれば、その該当画素が、SPパスで処理が行われた直後の処理ビットプレーン22上の画素であるということがわかる。ただし、これ以降の下位のビットプレーン22の処理時に誤って参照しないように、参照後にこのフラグをクリアする。

(1−5−3)CUパスの処理

トップビットプレーン22Tに対しては唯一これのみ、トップビットプレーン22Tを除く他の処理対象のビットプレーン22に対しては最後に実施されるコーディング・パスである。

CUパスでは、上述したビットプレーン内スキャン順序に従って、処理ビットプレーン22の左上を起点に、CUパスの処理を行うことができるかどうかを各画素について調べるが、この段階で「未処理(DONEプレーン33上で該当画素と同じ座標位置にフラグが立っていない)の処理ビットプレーン22上の画素」、すなわち処理ビットプレーン22上のSPパス及びMRパスの処理対象とならない残りの画素がすべてCUパスの処理対象となる。

CUパスでは、図17に示すように、上述したSPパスやMRパスのように該当画素と同じ座標位置にあるSIGプレーン31上のビットの8近傍の値を参照するものに加えて、もう少し大きいランレングス符号化を行う。

CUパスの処理は、まず処理ビットプレーン22の左上を起点に、ランレングス処理を行うことができるかどうかを調べる。具体的には、ストライプカラム23A単位で、「『当該ストライプカラム23A内の4画素すべてがCUパスで処理すべき画素である』かつ『当該ストライプカラム23A内の4画素すべてが“Insignificant”である』かつ『当該ストライプカラム23A内の4画素とそれぞれ同じ座標位置にあるSIGプレーン31上の4つのビットの各8近傍に“Significance”が存在しない』」という条件を満たすか否かを調査する。

そしてこの条件を満たすときにランレングス処理に入り、コンテクストとして“run”を出力する。その上で、『当該ストライプカラム23A内の4画素の値がすべて0である』ときにはシンボルとして0を出力し、これに対して『当該ストライプカラム23Aの4画素の値がすべて0ではない』とき、すなわち4画素の中にひとつでも1が存在する場合には、(“run”を出力した上で)シンボルとして1を出力し、それに引き続いて2回“uniform”というコンテクストと対応するシンボルを出力する。

この際“uniform”コンテクストに対応するシンボルは、図18に示すようなルールでエンコードを行う。この図18で説明すると、ストライプカラム23A内の4画素が上から順に0、0、1、0で、初めて1が出てきたその位置を表現する『1、0』なる列がその順でシンボルとなる。“Insignificant”な画素において初めて1が現れたことになるので、その座標は“Significant”に転じ、図17(B)に示すように、かかる値が1の画素と同じSIGプレーン31上の座標位置にフラグを立てる。同時にREFプレーン32(図10)の同じ座標位置にもフラグを立てておくことはいうまでもない。

続いてその該当画素の正負符号をモデル化するが、そのやり方は図14について上述したSPパスにおける正負符号のモデル化のそれと同じものである。さらにこの例ではストライプカラム23A内の4番目の画素がモデル化されずに残っているが、この画素についてはSPパスと同様のモデル化を行うことになる。

(1−6)3つのコーディング・パスの依存関係

CBM処理では3つのコーディング・パスを処理する。一度あるコーディング・パスでモデル化を行った処理ビットプレーン22上の画素がその処理ビットプレーン22中の他のコーディング・パスで再評価されることはない。DONEプレーン33を用いて処理済・未処理を管理しているためである。

しかしながら、上述のように“Significance”は8近傍から影響を受けるため、一般的に “Significance”の依存関係がある。すなわち“Significance”に転じた画素があれば、近傍の画素がモデル化される際にその影響を受ける。

(1−7)従来のCBM処理の問題

これまでCBM処理の概略を示してきたが、ポイントは、

1. ひとつのビットプレーン22について3つのコーディング・パスを処理しなければならない

2. 3つのコーディング・パスにはビットプレーン22内で依存関係がある

3. 上位のビットプレーン22で生成されたSIGプレーン31の値を評価しながら下位のビットプレーン22のビットモデル化が行われる

ということである。

そのような制約のもと、上述した従来手法によるCBM処理では、

1. 上位のビットプレーン22から順番に処理を行う。

2. トップビットプレーン22TではCUパスの処理を行う。このときSIGプレーン31が生成される。

3. トップビットプレーン22Tに対する処理の完了後、ひとつ下のビットプレーン22に移り、SPパスの処理を行いつつSIGプレーン31をアップデートする。

4. SP パスの処理を完了後、MRパスの処理を行う。処理に際してSIGプレーン31を参照する。

5. MRパスの処理を完了後、CUパスの処理を行う。SIGプレーン31を参照しつつ、あらたにモデル化されたビットを取り込みつつSIGプレーン31をアップデートする。これでひとつのビットプレーン22の処理を完了する。

6. 次のビットプレーン22に移る。

7. …

といった流れのシーケンシャルな処理となっていた。

また従来手法におけるビットプレーン22(例えば8画素×8画素)についてのCBM処理では、各コーディング・パスごとにビットプレーン内スキャン順序に従って、1画素ずつ順に評価している。

しかしながら、3つのコーディング・パスを処理するビットプレーン22(主にこれが支配的である)では、64画素を評価するのに少なくともSPパス処理時に64回、MRパス処理時に64回の合わせて192回の係数参照を要する。また実際上は、これに加えて正負符号を評価する分も必要となる。

ところがさらに同時にアクセスするSIGプレーン31に至っては、該当画素と同座標のビット及びその8近傍のビットの値を参照する必要があり、192回×(8+1)=1728回、すなわち処理すべき64画素の27倍のデータアクセスが必要となり、それが回路の動作速度に限界を与えている。

一方、これまでビットプレーン22が8画素×8画素である場合のCBM処理について説明してきたが、ウェーブレット変換して量子化された係数に対してコードブロックを切り出す際に、実際には32画素×32画素や64画素×64画素といったコードブロックサイズが使われることが多い。

この場合、例えば32画素×32画素×16ビットのコードブロックサイズでは、32×32×16=16384〔bit〕=16〔Kbit〕というデータ量となり、64画素×64画素×16ビットのコードブロックサイズでは64×64×16=65536〔bit〕=64〔Kbit〕というデータ量となる。

従って、例えは図46に示すJPEG2000規格に準拠した符号化装置1や図48に示す復号化装置10をIC(Integrated Circuit)化しようと考えた場合、実際上用いられることが多い32画素×32画素×16ビットや64画素×64画素×16ビットのコードブロックサイズは、IC内部のSRAM(Static RAM)に記憶保持するには大きいと言わざるを得ない。

そこで本願特許請求人は、上述した特願2003−130793号において、

1. IC化した符号化装置及び復号化装置の外部にコードブロックデータを記憶保持するDRAM(Dynamic RAM)を設ける一方、係数ビットモデリングに必要な処理ビットプレーンデータを記憶保持するSRAMをIC内部に設け、さらに処理に必要なデータ部分のみを順次切り取りながらSRAMからビットモデル部に読み込んで、CBM処理をした後にSRAMに書き戻すRead−Modify−Write形態をとる

2. 従来1画素ずつ処理していたCBM処理を、処理ビットプレーン22内のストライプカラム23Aの大きさにあたる4画素まとめて演算子として構成し、処理を行う

3. 4画素拡張した演算子をすべてシフトレジスタを用いた演算子として構成することにより、処理ビットプレーンデータ、SIGプレーンデータ、REFプレーンデータ、正負符号プレーンデータ及びDONEプレーンデータの5つの情報が同期したパイプライン処理を行う

などの構成上の工夫を加えることによって、従来のCBM処理において存在した無駄時間を大幅に短縮し、処理時間の低減を図ることを提案している。

しかしながら、この特願2003−130793号において提案した発明では、SIGプレーン31のデータを記憶保持するメモリの構成によっては当該メモリからのSIGプレーン31上の必要なデータの読み出しで処理が待たされ、「4画素拡張演算」の効果を十分に発揮できないことがある。

例えば上述の特願2003−130793号に開示した符号化装置や復号化装置においてSIGプレーン31のデータを記憶保持するメモリの構成として、従来のようにSIGプレーン31上の1ビットについてメモリ語長(1ワード)を割り当てるという構成を採用した場合を考える。

この場合、図19に示すように、処理ビットプレーン22上の1つのストライプカラム(図19(A−1))をCBM処理するためには、SIGプレーン31については18回(図19(A−2))、正負符号プレーン30については14回(図19(A−3))のメモリアクセスが必要となる。

このため例え処理ビットプレーン22の1ストライプカラム23Aを構成する4画素を1クロックで一括してメモリから読み出した場合(図19(B−1))でも、これら4画素をCBM処理するのに必要なSIGプレーン31上のデータや正負符号プレーン30上のデータを読み出し終えるまでCBM処理が待たされることとなる(図19(B−2)、図19(B−3))。

また図20に示すように、処理ビットプレーン22、正負符号プレーン30、SIGプレーン31、REFプレーン32及びDONEプレーン33の各データをひとまとめにマルチプレクスして、ひとつのアドレスを指定することでこれらのデータを一括して取り出せるようなメモリ構成(たて串方式)を採用することも提案されているものの、この手法もメモリアクセス頻度の観点から考えれば上述の手法と全く変わりがない。

そこで本願発明においては、上述のように従来1ビットずつ行っていたメモリからのSIGプレーン31のデータの読み出しを縦4ビットをひとつの単位(語長、ワード)とすることによって、かかる従来手法に比してSIGプレーン31上のデータの読み出しのためのメモリアクセス頻度を低減させようとするものである。以下、本実施の形態について説明する。

(2)第1の実施の形態

(2−1)第1の実施の形態による符号化装置40の構成

(2−1−1)符号化装置40の全体構成

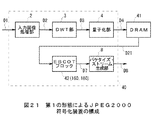

図46との対応部分に同一符号を付して示す図21は、JPEG2000規格に準拠した本実施の形態による符号化装置40を示し、全体として一体にIC化(集積回路化)されて構成されている点と、ICの外部に量子化部4から出力されるコードブロックデータD4を記憶保持するDRAM41が設けられている点と、EBCOTブロック42の構成が異なる点とを除いて図46に示す符号化装置1と同様に構成されている。

実際上、EBCOTブロック42においては、図22に示すように、それぞれSRAMからなる正負符号プレーンバッファ50及び処理ビットプレーンバッファ51A、51Bが入力段に設けられており、DRAM41(図21)に記憶保持されたコードブロックデータD4のうち、正負符号ビットプレーン22Sのデータ(以下、これを単に正負符号プレーンデータと呼ぶ)D20と、必要な処理ビットプレーン22のデータ(以下、これを単に処理ビットプレーンデータと呼ぶ)D21とを読み出し、これらをそれぞれSRAMでなる正負符号バッファ50又はビットプレーンバッファ51A、51Bに記憶保持し得るようになされている。

この場合処理ビットプレーンバッファ51A、51Bは2つ設けられており、これにより一方の処理ビットプレーンバッファ51A、51Bに記憶保持した処理ビットプレーンデータD21をCBM処理しながら、他方の処理ビットプレーンバッファ51B、51Aに次の処理ビットプレーンデータD21を書き込み得るようになされている。

またEBCOTブロック42には、それぞれ少なくとも1ビットプレーン分のデータ及び2ビットプレーン分のデータの記憶容量を有するSRAM52A、52Bが設けられており、これによりCBM処理時に利用するSIGプレーン31(図10)のデータ(以下、これをSIGプレーンデータと呼ぶ)D22をSRAM52Aに記憶保持し、REFプレーン32(図10)のデータ(以下、これをREFプレーンデータと呼ぶ)D23及びDONEプレーン33(図10)のデータ(以下、これをDONEプレーンデータと呼ぶ)D24をSRAM52Bに記憶保持することができるようになされている。

一方、処理ビットプレーンバッファ51A、51Bに記憶保持された処理ビットプレーンデータD21は、スイッチャ53を介してビットモデル部54により所定単位で順次読み出される。そしてビットモデル部54は、この読み出した処理ビットプレーンデータD21を、正負符号プレーンバッファ50に記憶保持された正負符号プレーンデータD20と、SRAM52A、52Bに記憶保持されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを利用しながらCBM処理し、かくして得られたシンボルSB及びコンテクストCXを算術符号化部55に送出する。

算術符号化部55は、供給されるシンボルSB及びコンテクストCXを入力として算術符号化処理を行いながら符号化列を生成し、かくして得られた符号化データD25をコードブロック20ごとに第1又は第2のビットストリームバッファ56A、56Bに順次交互に格納する。

そしてこの第1又は第2のビットストリームバッファ56A、56Bに格納された符号化データD25は、この後スイッチャ57を介して後段のパケッタイズ・ストリーム生成部8(図21)に送出される。

このようにしてこの符号化装置40においては、DRAM41に格納されたコードブロックデータD4から必要な処理ビットプレーンデータD21のみを読み出してビットプレーンバッファ51A、51Bに記憶保持しながら、当該記憶保持した処理ビットプレーンデータD21に対して順次CBM処理を施し得るようになされている。

(2−1−2)ビットモデル部54の構成

ここでビットモデル部54は、図23に示すように、シグナルスイッチャ60、SPパス符号化処理部61、MRパス符号化処理部62、CUパス符号化処理部63、出力スイッチャ64及び制御部65から構成されている。

この場合シグナルスイッチャ60は、トップビットプレーン22T以外の処理ビットプレーン22に対するCBM処理時、シーケンサ及びタイミングジェネレータとしての機能を有する制御部65の制御のもとに、処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをまずSPパス符号化処理部61に送出する。

またシグナルスイッチャ60は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してSPパスによる符号化処理(以下、これをSPパス符号化処理と呼ぶ)をする際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)の正負符号プレーンデータD20を正負符号プレーンバッファ50から順次読み出し、これをSPパス符号化処理部61に送出する。

この場合正負符号プレーンバッファ50は、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(ワード)として正負符号プレーンデータD20を記憶しており、このワード単位で正負符号プレーンデータD20を読書きし得るように構成されている。従って、このときシグナルスイッチャ60は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビットの正負符号プレーンデータD20に対して、図25に示すように、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4画素分の正負符号プレーンデータD20と、その上下のストライプカラム23Aをそれぞれ構成する各4画素分の正負符号プレーンデータD20とを正負符号プレーンバッファ30から3クロックかけて順次読み出し、これをSPパス符号化処理部61に送出することとなる。

さらにシグナルスイッチャ60は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22をSRAM52Aから順次読み出し、これをSPパス符号化処理部61に送出する。

この場合SRAM52Aも、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(ワード)としてSIGプレーンデータD22を記憶しており、このワード単位でSIGプレーンデータD22を読書きし得るように構成されている。従って、このときシグナルスイッチャ60は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビット分のSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットのSIGプレーンデータD22と、その上下の各4ビット分のSGIプレーンデータD22とをSRAM52Aから3クロックかけて順次読み出し(図25)、これをSPパス符号化処理部61に送出することとなる。

さらにシグナルスイッチャ60は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の4ビット(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の4ビット(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから順次読み出し、これをSPパス符号化処理部61に送出する。

この場合SRAM52Bも、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(ワード)としてREFプレーンデータD23及びDONEプレーンデータD23を記憶しており、このワード単位でREFプレーンデータD23やDONEプレーンデータD23を読書きし得るように構成されている。従って、シグナルスイッチャ60は、かかる4ビット分のREFプレーンデータD23又はDONEプレーンデータD24をそれぞれ1クロックでSRAM52Bから読み出し、これをSPパス符号化処理部61に送出することとなる。

このときSPパス符号化処理部61は、シグナルスイッチャ60から順次供給される処理ビットプレーンデータD21と、これと対応する正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、ここでは処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてSPパス符号化処理部61は、シグナルスイッチャ60から次のサンプルの処理ビットプレーンデータD21等が与えられると、その1つ前のサンプルの処理ビットプレーンデータD21(図24(A)において太枠で囲んだ4画素分)について、そのとき記憶保持している図24(B)〜(E)においてそれぞれ太枠で囲まれたSIGプレーンデータD22、正負符号プレーンデータD20、REFプレーンデータD23及びDONEプレーンデータD24を利用して、SPパス符号化処理できるか否かの検出と、できる場合のSPパス符号化処理とを実行する。

そしてSPパス符号化処理部61は、SPパス符号化処理を行った場合、これにより得られたその画素についてのシンボルSB及び正負符号についての各シンボルSBをシンボルデータD26Sとして出力スイッチャ64に送出すると共に、その画素についてのコンテクストCX及び正負符号についてのコンテクストCXをコンテクストデータD27Sとして出力スイッチャ64に送出する。

またSPパス符号化処理部61は、SPパス符号化処理を行ったときは、かかるSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24をこれに応じて更新し、その後これらをシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、これらSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をそれぞれSRAM52A、52Bにおけるもとのアドレス位置に書き戻させる(Read-Modify-Write)。

一方、シグナルスイッチャ60は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するSPパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをMRパス符号化処理部62に送出する。

またシグナルスイッチャ60は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してMRパスによる符号化処理(以下、これをMRパス符号化処理と呼ぶ)をする際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD22をSRAM52Aから順次読み出し、これをMRパス符号化処理部62に送出する。

この際シグナルスイッチャ60は、上述のSPパス符号化処理部61の場合と同様に、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をMRパス符号化処理する際に必要となる合計6ビット分のSIGプレーンデータに対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット分のSIGプレーンデータD22と、その上下の各4ビット分のSIGプレーンデータD22とをSRAM52Aから3クロックかけて順次読み出し(図25)、これをMRパス符号化処理部62に送出することとなる。

さらにシグナルスイッチャ60は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をMRパス符号化処理する際に必要となる、当該4画素と同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから順次読み出し、これをMRパス符号化処理部61に送出する。

このときMRパス符号化処理部62は、シグナルスイッチャ60から順次供給される4画素分の処理ビットプレーンデータD21と、これと対応するSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてMRパス符号化処理部62は、シグナルスイッチャ60から次のサンプルの処理ビットプレーンデータD21等が与えられると、その1つ前のサンプルの処理ビットプレーンデータD21(図24(A)において太枠で囲んだ4画素分)について、そのとき記憶保持している図24(B)、(D)及び(E)においてそれぞれ太枠で囲まれた必要なSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24を利用して、MRパス符号化処理できるか否かの検出と、できる場合のMRパス符号化処理とを実行する。

そしてMRパス符号化処理部62は、MRパス符号化処理を行った場合、これにより得られたその画素についてのシンボルSB及び正負符号についてのシンボルSBをシンボルデータD26Rとして出力スイッチャ64に送出すると共に、その画素についてのコンテクストCX及び正負符号についてのコンテクストCXをコンテクストデータD27Rとして出力スイッチャ64に送出する。

またMRパス符号化処理部62は、MRパス符号化処理を行ったときは、SIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24をこれに応じて更新し、その後これらをシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、これらSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をそれぞれSRAM52A、52Bにおけるもとのアドレス位置に書き戻させる(Read-Modify-Write)。

他方、シグナルスイッチャ60は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するMRパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをCUパス符号化処理部63に送出する。

またシグナルスイッチャ60は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してCUパスによる符号化処理(以下、これをCUパス符号化処理と呼ぶ)をする際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の正負符号プレーンデータD20を正負符号プレーンバッファ50から順次読み出し、これをCUパス符号化処理部63に送出する。

この際シグナルスイッチャ60は、上述のSPパス符号化処理部61と同様に、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる合計6ビットの正負符号プレーンデータD21に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の1ストライプカラム23Aを構成する4ビット分の正負符号プレーンデータD20と、その上下のストライプカラム23Aをそれぞれ構成する各4ビットの正負符号プレーンデータD20とを正負符号プレーンバッファ50から3クロックかけて順次読み出し、これをCUパス符号化処理部62に送出することとなる。

さらにシグナルスイッチャ60は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22をSRAM52Aから順次読み出し、これをCUパス符号化処理部63に送出する。

この場合においても、シグナルスイッチャ60は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる合計6ビット分のSIGプレーンデータに対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットのSIGプレーンデータD22と、その上下の各4ビット分のSIGプレーンデータD22とをSRAM52Aから3クロックかけて順次読み出し(図25)、これをCUパス符号化処理部63に送出することとなる。

さらにシグナルスイッチャ60は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから読み出し、これをCUパス符号化処理部63に送出する。

このときCUパス符号化処理部63は、シグナルスイッチャ60から順次供給される4画素分の処理ビットプレーンデータD21と、これと対応する正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてCUパス符号化処理部63は、シグナルスイッチャ60から次のサンプルの処理ビットプレーンデータD21等が与えられると、その1つ前のサンプルの処理ビットプレーンデータD21(図24(A)において太枠で囲んだ4画素分)について、そのとき記憶保持している図24(B)〜(E)においてそれぞれ太枠で囲まれたSIGプレーンデータD22、正負符号プレーンデータD20、REFプレーンデータD23及びDONEプレーンデータD24を利用して、CUパス符号化処理できるか否かの検出と、できる場合のCUパス符号化処理とを実行する。

そしてCUパス符号化処理部63は、CUパス符号化処理を行った場合、これにより得られたその画素についてのシンボルSB及び正負符号についてのシンボルSBをシンボルデータD26Cとして出力スイッチャ64に送出すると共に、その画素についてのコンテクストCX及び正負符号についてのコンテクストCXをコンテクストデータD27Cとして出力スイッチャ64に送出する。

またCUパス符号化処理部63は、CUパス符号化処理を行ったときは、かかるSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24をこれに応じて更新し、その後これらをシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、これらSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をそれぞれSRAM52A、52Bにおけるもとのアドレス位置に書き戻させる(Read-Modify-Write)。

出力スイッチャ64においては、制御部65の制御のもとに、SPパス符号化処理部61、MRパス符号化処理部62及びCUパス符号化処理部63のそれぞれから与えられるシンボルデータD26S、D26R、D26Cと、コンテクストデータD27S、D27R、D27CとをそれぞれシンボルデータD26及びコンテクストデータD27として算術符号化部55に送出する。

このようにしてこのビットモデル部54においては、処理ビットプレーン22上のストライプカラム23Aを構成する4画素を単位としてSPパス符号化処理、MRパス符号化処理及びCUパス符号化処理を行うと共に、このとき正負符号プレーンデータD20及びSIGプレーンデータD22についても当該ストライプカラム23Aと同位相の1ストライプカラム23Aを構成する4ビットをメモリワードとすることにより、メモリアクセス回数を格段的に低減させて、CBM処理を確実に高速に行い得るようになされている。

(2−1−3)各コーディング・パス処理部の具体的構成

次に、SPパス符号化処理部61、MRパス符号化処理部62及びCUパス符号化処理部63の各構成についてそれぞれ順番に説明する。

(2−1−3−1)SPパス符号化処理部61の構成

SPパス符号化処理部61は、図26に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部70、正符号シフトレジスタ部71、SIGシフトレジスタ部72、REFシフトレジスタ部73、DONEシフトレジスタ部74及びセレクタ75と、後述のようなセレクタ75に対する出力切替え制御等を行う制御部76とから構成されている。

また処理ビットシフトレジスタ部70には3段のシフトレジスタ70Aが設けられると共に、正符号シフトレジスタ部71、SIGシフトレジスタ部72、REFシフトレジスタ部73及びDONEシフトレジスタ部74には、それぞれ4段のシフトレジスタ71A〜74Aが設けられている。

これによりSPパス符号化処理部61は、上述のようにシグナルスイッチャ60(図23)から順次与えられる各1サンプル分の処理ビットプレーンデータD21、正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24を、それぞれ処理ビットシフトレジスタ部70、正符号シフトレジスタ部71、SIGシフトレジスタ部72、REFシフトレジスタ部73及びDONEシフトレジスタ部74の各シフトレジスタ70A〜74Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そして処理ビットシフトレジスタ部70は、シグナルスイッチャ60から1サンプル分の処理ビットプレーンデータD21が与えられると、このとき自己のシフトレジスタ70Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD21をセレクタ75に出力する。

またこのときSIGシフトレジスタ部72は、これと同期して、自己のシフトレジスタ72Aに記憶保持したSIGプレーンデータD22を用いて、このとき処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目にシフトされた4画素について、それぞれ上述のSPパス符号化処理を行うための条件を満たしているか否かの検出処理を画素ごとに並行して行い、検出結果をセレクタ75に出力する。

さらにSIGシフトレジスタ部72は、これと同期して、当該処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目にシフトされた4画素について、図13について上述したルールに従って、当該4画素ごとのコンテクストCXをそれぞれ演算し、演算結果をセレクタ75に出力する。

そして、このときSIGシフトレジスタ部72により検出された、処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目にシフトされた4画素についてのSPパス符号化処理を行うための条件を満たしているか否かの検出結果が全て否定的であった場合には、セレクタ75からは何も出力されず、処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目にシフトされた1サンプル(4画素)分の処理ビットプレーンデータD21に対する処理が終了する。

これに対して、処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目にシフトされた1サンプルのうちのいずれかの画素(以下、これをSPパス符号化処理対象画素と呼ぶ)についての検出結果が肯定的であった場合には、処理ビットシフトレジスタ部70から出力された当該SPパス符号化処理対象画素のデータ値(0/1)と、これに同期してSIGシフトレジスタ部72から出力された当該SPパス符号化処理対象画素についてのコンテクストCXの演算結果とが、それぞれそのSPパス符号化処理対象画素のシンボルSB及びコンテクストCXとしてセレクタ75から出力される。

また、このシンボルSBの値が『0』であった場合、この後セレクタ75からDONEシフトレジスタ部74に与えられる更新情報に基づいて、当該DONEシフトレジスタ部74のシフトレジスタ74Aに記憶保持されたDONEプレーンデータD24のうち、SPパス符号化処理対象画素と同座標のビットの値が、ビットモデル化が完了したことを表す『1』に更新されて、このSPパス符号化処理対象画素に対するSPパス符号化処理が完了する。

これに対して、このシンボルSBの値が『1』であった場合には、その情報がSIGシフトレジスタ部72、REFシフトレジスタ部73及び正負符号シフトレジスタ部71にそれぞれ与えられる。

このときSIGシフトレジスタ部72では、自己のシフトレジスタ72Aに記憶保持されたSIGプレーンデータD22におけるSPパス符号化処理対象画素と同座標のビットの値が“Significant”であることを表す『1』に更新される。またREFシフトレジスタ部73では、自己のシフトレジスタ73Aに記憶保持されたREFプレーンデータD23におけるSPパス符号化処理対象画素と同座標のビットの値が、“Significant”となったことを表す『1』に更新される。

さらにこのとき正負符号シフトレジスタ部71は、このSPパス符号化処理対象画素の正負符号のシンボルSB及びコンテクストCXを図14について上述したルールに従って演算し、その演算結果をセレクタ75に送出する。かくしてこのシンボルSB及びコンテクストCXがセレクタ75を介して出力される。

そして、この後セレクタ75からDONEシフトレジスタ部74に更新情報与えられ、当該更新情報に基づき、DONEシフトレジスタ部74のシフトレジスタ74Aに記憶保持されたDONEプレーンデータD24におけるSPパス符号化処理対象画素と同座標のビットの値が『1』に更新されて、当該SPパス符号化処理対象画素に対するSPパス符号化処理が完了する。

またSPパス符号化処理部61は、この後同じサンプル(このとき処理ビットシフトレジスタ部70のシフトレジスタ70Aの2段目に記憶保持された1サンプル)内の当該SPパス符号化処理対象画素よりもビットプレーン内スキャン順序が後の各画素について、SPパス符号化処理を行うための条件を満たしていない場合にはスキップし、SPパス符号化処理を行うための条件を満たしている場合には上述のSPパス符号化処理対象画素と同様にしてSPパス符号化処理を行う。そしてSPパス符号化処理部61は、このような処理を当該サンプル内の全ての画素に対して行い終えると、当該サンプルに対する処理を終了する。

そして、SPパス符号化処理部61は、この後制御部76から制御部65(図23)に与えられる次の1サンプル分の処理ビットプレーンデータD21等の転送要求に応じて、シグナルスイッチャ60から当該次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに同様の処理を順次繰り返す。

またこの際SPパス符号化処理部61は、次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに、SIGシフトレジスタ部72、REFシフトレジスタ部73及びDONEシフトレジスタ部74の各シフトレジスタ72A〜74Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をそれぞれシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、これらをSRAM52A、52Bのもとの位置に書き戻させる。

このようにしてSPパス符号化処理部61においては、ビットプレーンバッファ51A、51Bに格納された処理ビットプレーンデータD21に対するSPパス符号化処理を行い得るようになされている。

(2−1−3−2)MRパス符号化処理部62の構成

一方、MRパス符号化処理部62は、図27に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部80、SIGシフトレジスタ部82、REFシフトレジスタ部83、DONEシフトレジスタ部84及びセレクタ85と、後述のようなセレクタ85に対する出力切替え制御等を行う制御部86とから構成されている。

また処理ビットシフトレジスタ部80には3段のシフトレジスタ80Aが設けられると共に、SIGシフトレジスタ部82、REFシフトレジスタ部83及びDONEシフトレジスタ部84には、それぞれ4段のシフトレジスタ82A〜84Aが設けられている。

これによりMRパス符号化処理部62は、上述のようにシグナルスイッチャ60(図23)から順次与えられる各1サンプル分の処理ビットプレーンデータD21、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24を、それぞれ処理ビットシフトレジスタ部80、SIGシフトレジスタ部82、REFシフトレジスタ部83及びDONEシフトレジスタ部84のシフトレジスタ80A、82A〜84Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そして処理ビットシフトレジスタ部80は、シグナルスイッチャ60から1サンプル分の処理ビットプレーンデータD21が与えられると、このとき自己のシフトレジスタ80Aの2段目にシフトした1サンプル分の処理ビットプレーンデータD21をセレクタ85に出力する。

またこのときREFシフトレジスタ部83及びDONEシフトレジスタ部84は、これに同期して、自己のシフトレジスタ83A、84Aの2段目にシフトされた1サンプル分のREFプレーンデータD23又はDONEプレーンデータD24をセレクタ85に出力する。

そしてSIGシフトレジスタ部82は、自己のシフトレジスタ82Aに記憶保持したSIGプレーンデータD22を用いて、処理ビットシフトレジスタ部80の2段目にシフトした4画素について、REFシフトレジスタ部83の出力を参照しながら図16について上述したルールに従ってコンテクストCXを演算し、演算結果をセレクタ85に出力する。

そして、このときDONEプレーンデータD24の値が全て『1』(すなわち処理済)であった場合には、セレクタ85からは何も出力されずに、当該処理ビットシフトレジスタ部80のシフトレジスタ80Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD21に対する処理が終了する。

またかかる1サンプル分のDONEプレーンデータD24のうち、いずれかのデータ値が『0』(すなわち未処理)であり、かつそのDONEプレーンデータD24と対応する処理ビットシフトレジスタ部80のシフトレジスタ80Aの2段目にシフトされた画素が“Significant”でなかった場合にも、セレクタ85からは何も出力されずに、当該処理ビットシフトレジスタ部80のシフトレジスタ80Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD21に対する処理が終了する。

これに対して、かかる1サンプル分のDONEプレーンデータD24のうち、いずれかのデータ値が『0』であり、かつそのDONEプレーンデータD24と対応する処理ビットシフトレジスタ部80のシフトレジスタ80Aの2段目にシフトされた画素が“Significant”であった場合には、当該画素(以下、これをMRパス符号化処理対象画素と呼ぶ)がMRパス符号化処理すべき画素であることを意味する。

かくして、このときセレクタ85は、処理ビットシフトレジスタ部80から出力されたこのMRパス符号化処理対象画素のデータ値(0/1)をシンボルSBとして出力する共に、これと併せてSIGシフトレジスタ部82から出力された、このMRパス符号化処理対象画素のコンテクストCXを出力する。

またこのときREFシフトレジスタ部83では、そのMRパス符号化処理対象画素と同座標のビットが『1』である場合(すなわちフラグが立っている場合)にはこれがクリアされ、またDONEシフトレジスタ部84では、そのMRパス符号化処理対象画素と同座標のビットが、当該MRパス符号化処理対象画素が処理済みとなったことを意味する『1』に更新される。

そして、MRパス符号化処理部62は、この後そのとき処理ビットシフトレジスタ部80のシフトレジスタ80Aの2段目にシフトされた残りの画素についても、当該画素がMRパス符号化処理すべき画素であった場合には、上述と同様にMRパス符号化処理する。

さらにMRパス符号化処理部62は、この後制御部86から制御部65(図23)に与えられる次の1サンプル分の処理ビットプレーンデータD21等の転送要求に応じて、シグナルスイッチャ60から当該次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに同様の処理を順次繰り返す。

またこの際MRパス符号化処理部62は、次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに、SIGシフトレジスタ部82、REFシフトレジスタ部83及びDONEシフトレジスタ部84の各シフトレジスタ82A〜84Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、それぞれSRAM52A、52Bのもとの位置に書き戻させる。

このようにしてMRパス符号化処理部62においては、ビットプレーンバッファ51A、51Bに格納された処理ビットプレーンデータD21に対するMRパス符号化処理を行い得るようになされている。

(2−1−3−3)CUパス符号化処理部63の構成

CUパス符号化処理部63は、図28に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部90、正符号シフトレジスタ部91、SIGシフトレジスタ部92、REFシフトレジスタ部93、DONEシフトレジスタ部94及びセレクタ95と、後述のようなセレクタ95に対する出力切替え制御等を行う制御部96とから構成されている。

また処理ビットシフトレジスタ部90には3段のシフトレジスタ90Aが設けられると共に、正符号シフトレジスタ部91、SIGシフトレジスタ部92、REFシフトレジスタ部93及びDONEシフトレジスタ部94には、それぞれ4段のシフトレジスタ91A〜94Aが設けられている。

これによりCUパス符号化処理部63は、上述のようにシグナルスイッチャ60から順次与えられる各1サンプル分の処理ビットプレーンデータD21、正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24を、それぞれ処理ビットシフトレジスタ部90、正符号シフトレジスタ部91、SIGシフトレジスタ部92、REFシフトレジスタ部93及びDONEシフトレジスタ部94の各シフトレジスタ90A〜94Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そして処理ビットシフトレジスタ部90は、シグナルスイッチャ60(図23)から1サンプル分の処理ビットプレーンデータD21が与えられると、このとき自己のシフトレジスタ90Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD21をセレクタ95に出力する。

またこのときSIGシフトレジスタ部92は、これと同期して、自己のシフトレジスタ92Aに記憶保持したSIGプレーンデータD22を用い、DONEシフトレジスタ部94のシフトレジスタ94Aに記憶保持されたDONEプレーンデータD24を参照しながら、処理ビットシフトレジスタ部90のシフトレジスタ90Aの2段目にシフトされた4画素についてランレングス処理を行い得るか否かを検出する。

そしてランレングス処理できない場合には、これら4画素について、それぞれ上述したSPパス符号化処理が順次行われることとなる。

これに対してランレングス処理できる場合、SIGシフトレジスタ部92は、図17及び図18について上述したルールに従って、まずコンテクストとして“run”を出力する。その上でSIGシフトレジスタ部92は、そのサンプル内の4画素の値が全て『0』であるときにはシンボルSBとして0を出力する。かくしてこれらコンテクストCX及びシンボルSBがセレクタ95を介して出力スイッチャ64(図23)に送出される。

またSIGシフトレジスタ部92は、当該サンプル内の4画素の値が全て0ではないとき、すなわち4画素の中にひとつでも値が1の画素が存在する場合には、シンボルSBとして1を出力し、それに引き続いて図18について上述したルールに従って2回“uniform”というコンテクストCXと対応するシンボルSBを出力する。かくしてこれらコンテクストCX及びシンボルSBがセレクタ95を介して出力スイッチャ64(図23)に送出される。

このときSIGシフトレジスタ部92では、自己のシフトレジスタ92Aに記憶保持されたSIGプレーンデータD22における当該値が1の画素と同座標のビットの値が

“Significant”であることを表す『1』に更新される。またREFシフトレジスタ部93では、自己のシフトレジスタ93Aに記憶保持されたREFプレーンデータD23における当該画素と同座標のビットの値が“Significant”となったことを表す『1』に更新される。

さらにこの後正負符号シフトレジスタ部91は、当該画素の正負符号のシンボルSB及びコンテクストCXを図14について上述したルールに従って演算し、その演算結果をセレクタ95に送出する。かくしてこのシンボルSB及びコンテクストCXが上述の“uniform”というコンテクストCX及び当該画素に対応するシンボルSBに続けてセレクタ95を介して出力スイッチャ64(図23)に送出される。

そして、この後セレクタ95からDONEシフトレジスタ部94に更新情報与えられ、当該更新情報に基づき、DONEシフトレジスタ部94のシフトレジスタ94Aに記憶保持されたDONEプレーンデータD24における当該画素と同座標のビットの値が『1』に更新されて、当該画素に対するCUパス符号化処理が完了する。

さらにCUパス符号化処理部63は、この後同じサンプル(このとき処理ビットシフトレジスタ部90のシフトレジスタ90Aの2段目に記憶保持された1サンプル)内の当該画素よりもビットプレーン内スキャン順序が遅い各画素について、それぞれSIGシフトレジスタ部92、REFシフトレジスタ部93及びDONEシフトレジスタ部94の各シフトレジスタ90A〜94Aに記憶保持されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24を必要に応じて順次更新しながら上述したSPパス符号化処理を施す。そしてCUパス符号化処理部63は、このような処理を当該サンプル内の全ての画素に対して行い終えると、当該サンプルに対する処理を終了する。

そして、CUパス符号化処理部63は、この後制御部96から制御部65(図23)に与えられる次の1サンプル分の処理ビットプレーンデータD21等の転送要求に応じて、シグナルスイッチャ60から当該次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに同様の処理を順次繰り返す。

またこの際CUパス符号化処理部63は、次の1サンプル分の処理ビットプレーンデータD21等が与えられるごとに、SIGシフトレジスタ部92、REFシフトレジスタ部93及びDONEシフトレジスタ部94の各シフトレジスタ92A〜94Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をそれぞれシグナルスイッチ60を介して対応するSRAM52A、52Bに与えることにより、これらをSRAM52A、52Bのもとの位置に書き戻させる。

このようにしてCUパス符号化処理部63においては、ビットプレーンバッファ51A、51Bに格納された処理ビットプレーンデータD21に対するCUパス符号化処理を行い得るようになされている。

(2−2)第1の実施の形態による復号化装置100の構成

(2−2−1)復号化装置100の全体構成

図48との対応部分に同一符号を付して示す図29は、JPEG2000規格に準拠した本実施の形態による復号化装置100を示し、全体として一体にIC化(集積回路化)されて構成されている点と、EBCOTブロック101の構成が異なる点と、ICの外部に当該EBCOTブロック101から出力されるコードブロックデータD14を記憶保持するDRAM102が設けられている点とを除いて図48に示す復号化装置10と同様に構成されている。

実際上、EBCOTブロック101においては、図30に示すように、それぞれSRAMからなるストリームバッファ110A、110Bが入力段に設けられており、パケタイズストリーム分解部11から与えられる符号化データD11をこのストリームバッファ110A、110Bに記憶保持し得るようになされている。

この場合ストリームバッファ110A、110Bは2つ設けられており、これにより一方のストリームバッファ110A、110Bに記憶保持したビットプレーン22の1枚分の符号化データD11をCBM処理しながら、他方のストリームバッファ110B、110Aに次のビットプレーン22の1枚分の符号化データD11を書き込み得るようになされている。

またEBCOTブロック101には、それぞれ少なくとも1ビットプレーン分のデータ記憶容量を有するSRAM111Aと、2ビットプレーン分のデータ記憶容量を有するSRAM111Bとが設けられており、これによりCBM処理時に利用するSIGプレーンデータD30をSRAM52Aに記憶保持し、REFプレーンデータD31及びDONEプレーンデータD32をSRAM52Bに記憶保持することができるようになされている。

一方、ストリームバッファ110A、110Bに記憶保持された符号化データD11は、スイッチャ112を介して算術復号化部113により所定単位で順次読み出される。そして算術復号化部113は、この読み出した符号化データD11と後段のビットデモデル部114から与えられるコンテクストデータD33とを入力とした所定の算術復号化演算処理を実行し、かくして得られたシンボルデータD34をビットデモデル部114に送出する。

ビットデモデル部114は、供給されるシンボルデータD34をCBM処理により係数ビットデモデル化する。この際ビットモデル部114は、SPパスによる復号化処理(以下、これをSPパス復号化処理と呼ぶ)、MRパスによる復号化処理(以下、これをMRパス復号化処理と呼ぶ)及びCUパスによる復号化処理(以下、これをCUパス復号化処理と呼ぶ)により順次復号されていく処理ビットプレーンデータD35及び正負符号プレーンデータD36をそれぞれ後段のそれぞれSRAMでなるビットプレーンバッファ116A、116B又は正負符号プレーンバッファ115における対応する位置に順次格納する。

またビットデモデル部114は、これと併せてSRAM111A、111Bに記憶保持されたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を必要に応じて順次更新しつつ、さらにこれら一部が復号等された処理ビットプレーンデータD35、正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を利用しながらCBM処理を進める。さらにこのときビットデモデル部114は、かかる処理ビットプレーンデータD35と併せて得られたコンテクストデータD33を上述のように順次算術復号化部113に送出する。

そしてこのようなCBM処理により最終的に復号された処理ビットプレーンデータD35が第1又は第2のビットプレーンバッファ116A、116Bに記憶保持されると共に、最終的に復号された正負符号プレーンデータD36が正負符号プレーンバッファ115に記憶保持され、これらがその後所定のタイミングで読み出されて、スイッチャ117を介してコードブロックデータD14として上述のDRAM102(図29)に与えられて記憶保持される。

さらにこのDRAM102に記憶保持されたコードブロックデータD14は、この後逆量子化部14(図29)に読み出されて所定の逆量子化処理が施される。

このようにしてこの復号化装置100においては、パケタイズストリーム分解部11から与えられる符号化データD11を順次CBM処理することによりコードブロックデータD35を復号し、これをICの外部に設けられたDRAM41に記憶保持しながら、後段の処理を行い得るようになされている。

(2−2−2)ビットデモデル部114の構成

ここでビットデモデル114部は、図31に示すように、シグナルスイッチャ120、SPパス復号化処理部121、MRパス復号化処理部122、CUパス復号化処理部123、出力スイッチャ124及び制御部125から構成されている。

この場合上述の算術復号化部113(図30)は、ストリームバッファ110A、110Bから読み出した符号化データD11と、SPパス復号化処理部121、MRパス復号化処理部122又はCUパス復号化処理部123から与えられるコンテクストデータD33とに基づいて所定の算術復号化演算処理を実行する。そして算術復号化部113は、この結果として得られたシンボルデータD34のうち、符号化装置40(図19)においてSPパス符号化処理することにより得られた符号化データD11に対して上述のような算術復号化処理を施すことにより得られたものについてはSPパス復号化処理部121に送出する。

このときシグナルスイッチャ120は、シーケンサ及びタイミングジェネレータとしての機能を有する制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている復号前又は一部が復号された処理ビットプレーンデータD35を、図22(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワードずつ順次読み出し、これをまずSPパス復号化処理部121に送出する。

またシグナルスイッチャ120は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の復号前又は一部が復号された正負符号プレーンデータD36を正負符号プレーンバッファ115から順次読み出し、これをSPパス復号化処理部121に送出する。

この場合正負符号プレーンバッファ115は、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(1ワード)として正負符号プレーンデータD36を記憶しており、このワード単位で正負符号プレーンデータD36を読書きし得るように構成されている。従って、このときシグナルスイッチャ120は、かかるビットプレーンバッファ116A、116Bから読み出された4ビット分の処理ビットプレーンデータD35をSPパス復号化処理する際に必要となる合計6ビットの正負符号プレーンデータD36に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン上の1ストライプカラム23Aを構成する4ビットの正負符号プレーンデータD36と、その上下のストライプカラム23Aをそれぞれ構成する各4ビットの正負符号プレーンデータD36とを正負符号プレーンバッファ115から3クロックかけて順次読み出し(図25)、これをSPパス復号化処理部121に送出することとなる。

さらにシグナルスイッチャ120は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図22(B)参照)のSIGプレーンデータD30をSRAM111Aから順次読み出し、これをSPパス復号化処理部121に送出する。

この場合SRAM52Aも、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(ワード)としてSIGプレーンデータD30を記憶しており、このワード単位でSIGプレーンデータD30を読書きし得るように構成されている。従って、このときシグナルスイッチャ120は、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をSPパス復号化処理する際に必要となる合計6ビット分のSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットのSIGプレーンデータD30と、その上下の各4ビットのSGIプレーンデータD30とをSRAM111Aから3クロックかけて順次読み出し、これをSPパス復号化処理部121に送出することとなる。

さらにシグナルスイッチャ120は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の4ビット(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の4ビット(図24(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをSPパス復号化処理部121に送出する。

この場合SRAM111Bも、処理ビットプレーン22の各ストライプカラム23Aとそれぞれ対応する4画素分を単位(ワード)としてREFプレーンデータD31及びDONEプレーンデータD32を記憶しており、このワード単位でREFプレーンデータD31やDONEプレーンデータD32を読書きし得るように構成されている。従って、シグナルスイッチャ120は、かかる4ビット分のREFプレーンデータD31又はDONEプレーンデータD32をそれぞれ1クロックでSRAM111Bから読み出してSPパス復号化処理部121に送出することとなる。

このときSPパス復号化処理部121は、シグナルスイッチャ120から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応する正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードが1サンプルに該当し、正負符号プレーンデータD36及びSIGプレーンデータD30については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてSPパス復号化処理部121は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、図24(A)において太枠で囲んだそのとき記憶保持している1サンプル分のシンボルデータD34(4画素分)について、そのとき記憶保持している図24(B)〜(E)においてそれぞれ太枠で囲まれたSIGプレーンデータD30、正負符号プレーンデータD36、REFプレーンデータD31及びDONEプレーンデータD32とを利用して、SPパス復号化処理できるか否かの検出と、できる場合のSPパス復号化処理とを実行する。

またSPパス復号化処理部121は、SPパス復号化処理を行ったときは、この際に得られたコンテクストCXを上述のように出力スイッチャ124を介してコンテクストデータD33として算術復号化部113(図30)に送出する一方、これと併せて得られた復号された処理ビットプレーンデータD35及び復号された正負符号プレーンデータD36をそれぞれビットプレーンバッファ116A、116B又は正負符号バッファ115における対応する位置に格納する。

さらにSPパス復号化処理部121は、SPパス復号化処理を行ったときには、これに応じてSIGプレーンデータD30、REFプレーンデータD31及び又はDONEプレーンデータD32を更新し、その後これらをシグナルスイッチ120を介して対応するSRAM111A、111Bに与えることにより、これらSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32をそれぞれSRAM111A、111Bのもとの位置に書き戻させる(Read-Modify-Write)。

一方、算術復号化部113(図30)は、ストリームバッファ110A、110Bから読み出した符号化データD11のうち、符号化装置40(図21)においてMRパス符号化処理することにより得られた符号化データD11に対して上述のような算術復号化演算処理を施すことにより得られたシンボルデータD34についてはMRパス復号化処理部122に送出する。

このときシグナルスイッチャ120は、制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている先行するSPパス復号化処理により一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワード分ずつ順次読み出し、これをMRパス復号化処理部122に送出する。

またシグナルスイッチャ120は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をMRパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30をSRAM111Aから順次読み出し、これをMRパス復号化処理部122に送出する。

この際シグナルスイッチャ120は、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をMRパス復号化処理する際に必要となる合計6ビット分のSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット分のSIGプレーンデータD30と、その上下の各4ビット分のSIGプレーンデータD30とをSRAM111Aから3クロックかけて順次読み出し、これをMRパス復号化処理部122に送出することとなる。

さらにシグナルスイッチャ120は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をMRパス復号化処理する際に必要となる、当該4画素と同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図22(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをMRパス復号化処理部122に送出する。

このときMRパス復号化処理部122は、シグナルスイッチャ120から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応するSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードが1サンプルに該当し、正負符号プレーンデータD36及びSIGプレーンデータD30については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてMRパス復号化処理部122は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、図24(A)において太枠で囲んだそのとき記憶保持している1サンプル分のシンボルデータD34(4画素分)について、そのとき記憶保持している図24(B)、(D)及び(E)においてそれぞれ太枠で囲まれたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32と、そのとき算術復号化部113から与えられたシンボルデータD34とを利用して、MRパス復号化処理できるか否かの検出と、できる場合のMRパス復号化処理とを実行する。

またMRパス復号化処理部122は、MRパス復号化処理を行ったときは、この際に得られたコンテクストCXを上述のように出力スイッチャ124を介してコンテクストデータD33として算術復号化部113(図30)に送出する一方、これと併せて得られた復号された処理ビットプレーンデータD35をビットプレーンバッファ116A、116Bの対応する位置に格納する。

さらにMRパス復号化処理部122は、MRパス復号化処理を行ったときには、これに応じてSIGプレーンデータD30、REFプレーンデータD31及び又はDONEプレーンデータD32を更新し、その後これらをシグナルスイッチ120を介して対応するSRAM111A、111Bに与えることにより、これらSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32をそれぞれSRAM111A、111Bのもとの位置に書き戻させる(Read-Modify-Write)。

これと同様にして、算術復号化部113(図30)は、ストリームバッファ110A、110Bから読み出した符号化データD11のうち、符号化装置40(図21)においてCUパス符号化処理することにより得られた符号化データD11に対して所定の算術復号化演算処理を施すことにより得られたシンボルデータD34についてはCUパス復号化処理部123に送出する。

このときシグナルスイッチャ120は、制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている先行するSPパス復号化処理及びMRパス復号化処理(トップビットプレーン22Tに対する復号化処理の場合を除く)により一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワードずつ順次読み出し、これをCUパス復号化処理部123に送出する。

またシグナルスイッチャ120は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の復号前又は一部が復号された正負符号プレーンデータD36を正負符号プレーンバッファ115から順次読み出し、これをCUパス復号化処理部123に送出する。

この際シグナルスイッチャ120は、上述のSPパス復号化処理部121と同様に、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる合計6ビットの正負符号プレーンデータD36に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の1ストライプカラム23Aを構成する4ビットの正負符号プレーンデータD36と、その上下のストライプカラム23Aをそれぞれ構成する各4ビットの正負符号プレーンデータD36とを正負符号プレーンバッファ115から3クロックかけて順次読み出し、これをCUパス復号化処理部123に送出することとなる。

さらにシグナルスイッチャ120は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をCUパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30をSRAM111Aから順次読み出し、これをCUパス復号化処理部123に送出する。

この場合においても、シグナルスイッチャ120は、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる合計6ビット分のSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット分のSIGプレーンデータD30と、その上下の各4ビット分のSIGプレーンデータD30とをSRAM111Aから3クロックかけて順次読み出し、これをCUパス復号化処理部123に送出することとなる。

さらにシグナルスイッチャ120は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをCUパス復号化処理部123に送出する。

このときCUパス復号化処理部123は、シグナルスイッチャ120から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応する正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードが1サンプルに該当し、正負符号プレーンデータD36及びSIGプレーンデータD30については縦方向に並ぶ3ワードが1サンプルに該当する。

そしてCUパス復号化処理部123は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、図24(A)において太枠で囲んだそのとき記憶保持している1サンプル分のシンボルデータD34(4画素分)について、そのとき記憶保持している図24(B)〜(E)においてそれぞれ太枠で囲まれたSIGプレーンデータD30、正負符号プレーンデータD36、REFプレーンデータD31及びDONEプレーンデータD32と、そのとき算術復号化部113からシンボルデータD34が与えられるとを利用して、CUパス復号化処理できるか否かの検出と、できる場合のCUパス復号化処理及びできない場合のSPパス復号化処理とを実行する。

またCUパス復号化処理部123は、CUパス復号化処理又はSPパス復号化処理を行ったときは、この際に得られたコンテクストCXを上述のように出力スイッチャ124を介してコンテクストデータD33として算術復号化部113(図30)に送出する一方、これと併せて得られた復号された処理ビットプレーンデータD35及び復号された正負符号プレーンデータD36をそれぞれビットプレーンバッファ116A、116B又は正負符号バッファ115の対応する位置に格納する。

さらにCUパス復号化処理部123は、CUパス復号化処理又はSPパス復号化処理を行ったときには、これに応じてSIGプレーンデータD30、REFプレーンデータD31及び又はDONEプレーンデータD32を更新し、その後これらをシグナルスイッチ120を介して対応するSRAM111A、111Bに与えることにより、これらSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32をそれぞれSRAM111A、111Bのもとの位置に書き戻させる(Read-Modify-Write)。

このようにしてこのビットデモデル部114においては、上述した符号化装置40(図21)のビットモデル部54(図23)と同様に、復号対象のビットプレーン22上のストライプカラム23Aを構成する4画素を単位としてSPパス復号化処理、MRパス復号化処理及びCUパス復号化処理を行うと共に、このとき正負符号プレーンデータD36及びSIGプレーンデータD30についてもストライプカラム23Aを構成する4ビットをメモリワードとすることにより、メモリアクセス回数を格段的に低減させて、CBM処理を確実に高速に行い得るようになされている。

(2−2−3)各コーディング・パス処理部の具体的構成

次に、SPパス復号化処理部121、MRパス復号化処理部122及びCUパス復号化処理部123の各構成についてそれぞれ順番に説明する。

(2−2−3−1)SPパス復号化処理部121の構成

SPパス復号化処理部121は、図32に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部130、正符号シフトレジスタ部131、SIGシフトレジスタ部132、REFシフトレジスタ部133、DONEシフトレジスタ部134及びセレクタ135と、後述のようなセレクタ135に対する出力切替え制御等を行う制御部136とから構成されている。

また処理ビットシフトレジスタ部130には3段のシフトレジスタ130Aが設けられると共に、正符号シフトレジスタ部131、SIGシフトレジスタ部132、REFシフトレジスタ部133及びDONEシフトレジスタ部134には、それぞれ4段のシフトレジスタ131A〜134Aが設けられている。

これによりSPパス復号化処理部131は、上述のようにシグナルスイッチャ120(図31)から順次与えられる各1サンプル分の処理ビットプレーンデータD35、正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれビットシフトレジスタ部130、正負符号シフトレジスタ部131、SIGシフトレジスタ部132、REFシフトレジスタ部133及びDONEシフトレジスタ部134の各シフトレジスタ130A〜134Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そしてSIGシフトレジスタ部132は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、そのとき自己のシフトレジスタ132Aに記憶保持したSIGプレーンデータD30を用いて、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた4画素について、それぞれ上述のSPパス復号化処理を行うための条件を満たしているか否かの検出処理を画素ごとに並行して行い、検出結果をセレクタ135に出力する。

またSIGシフトレジスタ部132は、これと同期して、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた4画素について、図13について上述したルールに従って、当該4画素ごとのコンテクストCXをそれぞれ演算し、演算結果をセレクタ135に出力する。

そして、このときSIGシフトレジスタ部132により検出された、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた4画素についてのSPパス復号化処理を行うための条件を満たしているか否かの検出結果が全て否定的であった場合には、セレクタ135からは何も出力されず、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた1サンプル(4画素)分の処理ビットプレーンデータD35に対する処理が完了する。

そして、この後制御部136からビットデモデル部114全体の制御部125(図31)に与えられる転送要求に応じて、当該制御部125の制御のもとに、シグナルスイッチャ120(図31)から次の1サンプル分の処理ビットプレーンデータD35等がSPパス復号化処理部121に与えられる。かくしてSPパス復号化処理部121は、これにより新たに処理ビットシフトレジスタ部130の2段目にシフトされた1サンプル(4画素)分の処理ビットプレーンデータD35について、同様の処理を開始する。

これに対して、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた1サンプルのうちのいずれかの画素(以下、これをSPパス復号化処理対象画素と呼ぶ)についての検出結果が肯定的であった場合には、このとき算術復号化部113から与えられたシンボルデータD34のデータ値(0/1)が処理ビットシフトレジスタ部130のシフトジレスタ130Aにおける当該SPパス復号化処理対象画素と対応するビットに格納される。またこれと併せて、SIGシフトレジスタ部132から出力された当該SPパス復号化処理対象画素についてのコンテクストCXの演算結果がセレクタ135から出力されて算術復号化部113に与えられる。

さらに、このときのシンボルデータD34のデータ値(SPパス復号化処理対象画素の復号値)が『0』であった場合、この後セレクタ135からDONEシフトレジスタ部134に与えられる更新情報に基づいて、当該DONEシフトレジスタ部134のシフトレジスタ134Aに記憶保持されたDONEプレーンデータD32のうち、SPパス復号化処理対象画素と同座標のビットの値が、ビットデモデル化が完了したことを表す『1』に更新されて、このSPパス復号化処理対象画素に対するSPパス復号化処理が完了する。

これに対して、このシンボルデータD34のデータ値が『1』であった場合、その情報がSIGシフトレジスタ部132、REFシフトレジスタ部133及び正負符号シフトレジスタ部131にそれぞれ与えられる一方、これに続けて算術復号化部113(図31)から与えられる1シンボル分のシンボルデータD34が正負符号シフトレジスタ部131Aに与えられる。

このときSIGシフトレジスタ部132では、自己のシフトレジスタ132Aに記憶保持されたSIGプレーンデータD30におけるSPパス復号化処理対象画素と同座標のビットの値が“Significant”であることを表す『1』に更新される。またREFシフトレジスタ部133では、自己のシフトレジスタ133Aに記憶保持されたREFプレーンデータD31におけるSPパス復号化処理対象画素と同座標のビットの値が、“Significant”となったことを表す『1』に更新される。

さらにこのとき正負符号シフトレジスタ部131は、供給されるシンボルデータD34のデータ値(0/1)に基づいてSPパス復号化処理対象画素の正負符号を復号化し、得られた正負符号ビットを自己のシフトレジスタ131AにおけるSPパス復号化処理対象画素と対応する位置に格納する一方、当該SPパス復号化処理対象画素の正負符号ビットのコンテクストCXを図14について上述したルールに従って演算し、その演算結果をセレクタ135に送出する。かくしてこのコンテクストCXがセレクタ135を介して算術復号化部113に与えられる。

そして、この後セレクタ135からDONEシフトレジスタ部134に更新情報が与えられ、当該更新情報に基づき、DONEシフトレジスタ部134のシフトレジスタ134Aに記憶保持されたDONEプレーンデータD32におけるSPパス復号化処理対象画素と同座標のビットの値が『1』に更新されて、当該SPパス復号化処理対象画素に対するSPパス復号化処理が完了する。

そして、SPパス復号化処理部121は、この後算術復号化部113から1シンボル分のシンボルデータD34が与えられるごとに同様の処理を順次繰り返す。

またこの際SPパス復号化処理部121は、シグナルスイッチャ120から1サンプル分の処理ビットプレーンデータD35等が与えられるごとに、処理ビットシフトレジスタ部130のシフトレジスタ130Aの3段目に記憶保持されていた処理ビットプレーンデータD35と、正負符号シフトレジスタ部131のシフトレジスタ131Aの4段目に記憶保持されていた正負符号プレーンデータD36とを、それぞれシグナルスイッチャ120を介して対応するビットプレーンバッファ116A、116B又は正負符号バッファ115に与えてもとのアドレス位置に書き戻させる一方、SIGシフトレジスタ部132、REFシフトレジスタ部133及びDONEシフトレジスタ部134の各シフトレジスタ132A〜134Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれシグナルスイッチ120を介して対応するSRAM111A、111Bに与えてもとのアドレス位置に書き戻させる。

このようにしてSPパス復号化処理部121においては、算術復号化部113から順次与えられるシンボルデータD34に基づいて、SPパス復号化処理を行い得るようになされている。

(2−2−3−2)MRパス復号化処理部122の構成

一方、MRパス復号化処理部122は、図33に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部140、SIGシフトレジスタ部142、REFシフトレジスタ部143、DONEシフトレジスタ部144及びセレクタ145と、後述のようなセレクタ145に対する出力切替え制御等を行う制御部146とから構成されている。

また処理ビットシフトレジスタ部140には3段のシフトレジスタ140Aが設けられると共に、SIGシフトレジスタ部142、REFシフトレジスタ部143及びDONEシフトレジスタ部144には、それぞれ4段のシフトレジスタ142A〜144Aが設けられている。

これによりMRパス復号化処理部122は、上述のようにシグナルスイッチャ120(図31)から順次与えられる各1サンプル分の処理ビットプレーンデータD35、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれ処理ビットシフトレジスタ部140、SIGシフトレジスタ部142、REFシフトレジスタ部143及びDONEシフトレジスタ部144のシフトレジスタ140A、142A〜144Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そしてREFシフトレジスタ部143及びDONEシフトレジスタ部144は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、そのとき自己のシフトレジスタ143A、144Aの2段目にシフトされた1サンプル分のREFプレーンデータD31又はDONEプレーンデータD32をセレクタ145に出力する。

またこのときSIGシフトレジスタ部142は、自己のシフトレジスタ142Aに記憶保持したSIGプレーンデータD30を用いて、処理ビットシフトレジスタ部140の2段目にシフトした4画素について、REFシフトレジスタ部143の出力を参照しながら図16について上述したルールに従ってコンテクストCXを演算し、演算結果をセレクタ145に出力する。

そして、このときDONEプレーンデータD32の値が全て『1』(すなわち処理済)であった場合には、セレクタ145からは何も出力されずに、当該処理ビットシフトレジスタ部140のシフトレジスタ140Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD35に対する処理が終了する。

またかかる1サンプル分のDONEプレーンデータD32のうち、いずれかのデータ値が『0』(すなわち未処理)であり、かつそのDONEプレーンデータD32と対応する処理ビットシフトレジスタ部140のシフトレジスタ140Aの2段目にシフトされた画素が“Significant”でなかった場合にも、セレクタ145からは何も出力されずに、当該処理ビットシフトレジスタ部140のシフトレジスタ140Aの2段目にシフトされた1サンプル分の処理ビットプレーンデータD35に対する処理が終了する。

そしてこれらの場合には、この後制御部146からビットデモデル部114全体の制御部125(図31)に与えられる転送要求に応じて、当該制御部125の制御のもとに、シグナルスイッチャ120(図31)から次の1サンプル分の処理ビットプレーンデータD35等がMRパス復号化処理部122に与えられる。かくしてMRパス復号化処理部121は、これにより新たに処理ビットシフトレジスタ部130の2段目にシフトされた1サンプル(4画素)分の処理ビットプレーンデータD35について、同様の処理を開始する。

これに対して、かかる1サンプル分のDONEプレーンデータD32のうち、いずれかのデータ値が『0』であり、かつそのDONEプレーンデータD32と対応する処理ビットシフトレジスタ部140のシフトレジスタ140Aの2段目にシフトされた画素が“Significant”であった場合には、当該画素(以下、これをMRパス復号化処理対象画素と呼ぶ)がMRパス復号化処理すべき画素であることを意味する。

かくして、このとき算術復号化部113(図31)から与えられたシンボルデータD34のデータ値(0/1)が処理ビットシフトレジスタ部140のシフトジレスタ140AにおけるMRパス復号化処理対象画素と対応するビットに格納される一方、SIGシフトレジスタ部142から出力された当該MRパス復号化処理対象画素についてのコンテクストCXの演算結果がセレクタ145から出力されて算術復号化部113に与えられる。

またこのときREFシフトレジスタ部143では、そのMRパス復号化処理対象画素と同座標のビットが『1』である場合(すなわちフラグが立っている場合)にはこれがクリアされ、またDONEシフトレジスタ部144では、そのMRパス復号化処理対象画素と同座標のビットが、当該MRパス復号化処理対象画素が処理済みとなったことを意味する『1』に更新されて、このMRパス復号化処理対象画素に対するMRパス復号化処理が完了する。

そして、MRパス復号化処理部122は、この後そのとき処理ビットシフトレジスタ部140のシフトレジスタ140Aの2段目にシフトされた残りの画素についても、当該画素がMRパス復号化処理すべき画素であった場合には、上述と同様にMRパス復号化処理を実行する。

そして、MRパス復号化処理部122は、この後算術復号化部113から1シンボル分のシンボルデータD34が与えられるごとに同様の処理を順次繰り返す。

またこの際MRパス復号化処理部122は、処理ビットシフトレジスタ部140のシフトレジスタ140Aに新たな4画素分の処理ビットプレーンデータD35が与えられるごとに、処理ビットシフトレジスタ部140のシフトレジスタ140Aの3段目に記憶保持されていた処理ビットプレーンデータD35をシグナルスイッチャ120を介して対応するビットプレーンバッファ116A、116Bに与えてもとのアドレス位置に書き戻させる一方、SIGシフトレジスタ部142、REFシフトレジスタ部143及びDONEシフトレジスタ部144の各シフトレジスタ142A〜144Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれシグナルスイッチ120を介して対応するSRAM111A、111Bに与えてもとのアドレス位置に書き戻させる。

このようにしてMRパス復号化処理部122においては、算術復号化部113から与えられるシンボルデータD34に基づいてMRパス復号化処理を行い得るようになされている。

(2−2−3−3)CUパス復号化処理部123の構成

CUパス復号化処理部123は、図34に示すように、いずれもハードウェア構成の処理ビットシフトレジスタ部150、正符号シフトレジスタ部151、SIGシフトレジスタ部152、REFシフトレジスタ部153、DONEシフトレジスタ部154及びセレクタ155と、後述のようなセレクタ155に対する出力切替え制御等を行う制御部156とから構成されている。

また処理ビットシフトレジスタ部150には3段のシフトレジスタ150Aが設けられると共に、正符号シフトレジスタ部151、SIGシフトレジスタ部152、REFシフトレジスタ部153及びDONEシフトレジスタ部154には、それぞれ4段のシフトレジスタ151A〜154Aが設けられている。

これによりCUパス復号化処理部123は、上述のようにシグナルスイッチャ120(図31)から順次与えられる各1サンプル分の処理ビットプレーンデータD35、正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれ処理ビットシフトレジスタ部150、正符号シフトレジスタ部151、SIGシフトレジスタ部152、REFシフトレジスタ部153及びDONEシフトレジスタ部154の各シフトレジスタ150A〜154Aにおいて順次シフトさせながら3サンプル分又は4サンプル分ずつ記憶保持し得るようになされている。

そしてSIGシフトレジスタ部152は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、そのとき自己のシフトレジスタ152Aに記憶保持したSIGプレーンデータD30と、DONEシフトレジスタ部154のシフトレジスタ154Aに記憶保持されたDONEプレーンデータD32を用いて、処理ビットシフトレジスタ部130のシフトレジスタ130Aの2段目にシフトされた4画素が上述したランレングス処理を行うための条件を満たしているか否かを検出する。

そしてかかる4画素がランレングス処理を行うための条件を満たしていない場合には、これら4画素のそれぞれについて、上述したSPパス復号化処理が順次行われる。

これに対してかかる4画素がランレングス処理を行うための条件を満たしている場合であって、このとき算術復号化部113(図31)から与えられた1シンボル分のシンボルデータD34のデータ値が『0』であったときには、処理ビットシフトレジスタ150のシフトレジスタ150Aにおける2段目の1番目〜4番目の各ビットにそれぞれ『0』が格納される。またこれと併せてSIGシフトレジスタ部152からこれに応じたコンテクストCX(“run”)が出力され、このコンテクストCXがセレクタ155を介して算術復号化部113(図28)に与えられて、この処理ビットシフトレジスタ部150のシフトレジスタ150Aの2段目にシフトされた1サンプル(4画素)分の処理ビットプレーンデータD35に対する処理が完了する。

またかかる4画素がランレングス処理を行うための条件を満たしている場合であって、このとき算術復号化部113から与えられた1シンボル分のシンボルデータD34のデータ値が『1』であったときには、その後算術復号化部113から与えられる2シンボル分のシンボルデータD34のデータ値に応じて、図18について上述した処理と逆の処理が行われる。

具体的には、算術復号化部113から与えられた2シンボル分のシンボルデータD34のデータ値が『0、0』であった場合には、処理ビットシフトレジスタ部150のシフトレジスタ150Aにおける2段目の一番上のビットに『0』が格納され、当該データ値が『0、1』であった場合には、処理ビットシフトレジスタ部150のシフトレジスタ150Aにおける2段目の1番目及び2番目のビットにそれぞれ『0』又は『1』が格納される。また、算術復号化部113から与えられた2シンボル分のシンボルデータD34のデータ値が『1、0』であった場合には、処理ビットシフトレジスタ部150のシフトレジスタ150Aにおける2段目の1番目〜3番目のビットにそれぞれ『0』、『0』又は『1』が格納され、当該データ値が『1、1』であった場合には、処理ビットシフトレジスタ部150のシフトレジスタ150Aにおける2段目の1番目〜4番目のビットにそれぞれ『0』、『0』、『0』又は『1』が格納される。さらに、これと併せてSIGシフトレジスタ部152から2回“uniform”というコンテクストCXが出力され、これがセレクタ155を介して算術復号化部113に与えられる。

さらにこのときSIGシフトレジスタ部152では、自己のシフトレジスタ152Aの2段目における、このとき処理ビットシフトレジスタ部150のシフトレジスタ150Aの『1』が格納された画素(以下、これをCUパス復号化処理対象画素と呼ぶ)と同座標のビットの値が“Significant”であることを表す『1』に更新される。またREFシフトレジスタ部153では、自己のシフトレジスタ153Aに記憶保持されたREFプレーンデータD31における当該CUパス復号化処理対象画素と同座標のビットの値が“Significant”となったことを表す『1』に更新される。

さらにこの後、算術復号化部113から与えられる1シンボル分のシンボルデータD34が正負符号シフトレジスタ部151に与えられる。そして正負符号シフトレジスタ部151では、かかるCUパス復号化処理対象画素の正負符号がこのシンボルデータD34に基づいて演算されると共に当該CUパス復号化処理対象画素のコンテクストCXが図14について上述したルールに従って演算され、算出された正負符号が当該正負符号シフトレジスタ部151のシフトレジスタ151AにおけるCUパス復号化処理対象画素と同座標のビットに格納され、コンテクストCXがセレクタ155を介して算術復号化部113に出力される。

そして、この後セレクタ155からDONEシフトレジスタ部154に更新情報与えられ、当該更新情報に基づき、DONEシフトレジスタ部154のシフトレジスタ154Aに記憶保持されたDONEプレーンデータD32における当該CUパス復号化処理対象画素と同座標のビットの値が『1』に更新されて、当該CUパス復号化処理対象画素に対するCUパス復号化処理が完了する。

さらにCUパス復号化処理部123は、この後同じサンプル(このとき処理ビットシフトレジスタ部150のシフトレジスタ150Aの2段目に記憶保持された1サンプル)内の当該CUパス復号化処理対象画素よりもビットプレーン内スキャン順序が後の各画素について、それぞれSIGシフトレジスタ部152、REFシフトレジスタ部153及びDONEシフトレジスタ部154の各シフトレジスタ150A〜154Aに記憶保持されたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を必要に応じて順次更新しながら上述したCUパス復号化処理を実行する。そしてCUパス復号化処理部123は、このような処理を当該サンプル内の全ての画素に対して行い終えると、当該サンプルに対するCUパス復号化処理を完了する。

そして、CUパス復号化処理部123は、この後算術復号化部113から1シンボル分のシンボルデータD34が与えられるごとに同様の処理を順次繰り返す。

またこの際CUパス復号化処理部123は、シグナルスイッチャ120から1サンプル分の処理ビットプレーンデータD35等が与えられるごとに、処理ビットシフトレジスタ部150のシフトレジスタ150Aの3段目に記憶保持されていた処理ビットプレーンデータD35と、正負符号シフトレジスタ部151のシフトレジスタ151Aの4段目に記憶保持されていた正負符号プレーンデータD36とを、それぞれシグナルスイッチャ120を介して対応するビットプレーンバッファ116A、116B又は正負符号バッファ115に与えてもとのアドレス位置に書き戻させる一方、SIGシフトレジスタ部152、REFシフトレジスタ部153及びDONEシフトレジスタ部154の各シフトレジスタ152A〜154Aの4段目にそれぞれ記憶保持されたSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32を、それぞれシグナルスイッチ120を介して対応するSRAM111A、111Bに与えてもとのアドレス位置に書き戻させる。

このようにしてCUパス復号化処理部123においては、算術復号化部113から順次与えられるシンボルデータD34に基づいて、CUパス復号化処理を行い得るようになされている。

(2−3)第1の実施の形態の動作及び効果

以上の構成において、本実施の形態による符号化装置40及び復号化装置100では、ビットモデル部54又はビットデモデル部114において、処理ビットプレーン22上のストライプカラム23Aを構成する4画素を単位としてCBM処理を行うと共に、このとき正負符号プレーンデータD20、D35及びSIGプレーンデータD22、D30についても処理ビットプレーン22上のストライプカラム23Aと同位相の4ビットを単位(1ワード)として、正負符号プレーンバッファ50、115又はSRAM52A、111Aから読み出す。

従って、この符号化装置40及び復号化装置100では、正負符号プレーンデータD20、D35やSIGプレーンデータD22、D30の1ビットをメモリワードとする従来手法に比して、CBM処理時における正負符号プレーンバッファ50、115やSRAM52A、111Aに対するアクセス回数を格段的に低減させることができる。

実際上、例えば64×64サイズのビットプレーン22を処理する際にメモリからSIGプレーンデータD22、D30を読み出す回数を計算すると、従来の1画素ずつアクセスする手法の場合、直前の画素を処理する際に読み出した流用可能なSIGプレーンデータD22、D30を次の画素を処理する際に利用することなく、画素ごとに必要なSIGプレーンデータD22、D30を1ビットずつ読み出す構成(以下、これをオーバラップ読出し構成と呼ぶ)では36100回のメモリアクセスが必要となり、直前の画素を処理する際に読み出した流用可能なSIGプレーンデータD22、D30を次の画素を処理する際に利用し、足りないSIGプレーンデータD22、D30のみを1ビットずつ読み出す構成(以下、これを更新部分限定読出し構成と呼ぶ)では、17860回のメモリアクセスが必要となる。

これに対してSIGプレーンデータD22、D30を4ビット分ずつ一括して読み出す本実施の形態の手法によれば、オーバラップ読出し構成とした場合であっても8740回のメモリアクセスで足り、また本実施の形態のように更新部分限定読出し構成とした場合に至っては2944回のメモリアクセスで足りる。

よって、かかるJPEG2000規格に準拠した符号化装置40及び復号化装置100におけるビットモデル部54又はビットデモデル部114の構成として上述のような第1の実施の形態の構成を採用することによって、これらビットモデル部54又はビットデモデル部114におけるCBM処理の高速化を図ることができ、またこれに伴ってビットモデル部54又はビットデモデル部114の低消費電力化を図ることもできる。

以上の構成によれば、処理ビットプレーン22上のストライプカラム23Aを構成する4画素を単位としてCBM処理を行うと共に、このとき正負符号プレーンデータD20、D36及びSIGプレーンデータD22、D30についても処理ビットプレーン22上のストライプカラム23Aと同じ位相の4ビットを単位(1ワード)として取り扱うようにしたことにより、CBM処理時における正負符号プレーンバッファ50、115やSRAM52A、111Aに対するアクセス回数を格段的に低減させることができ、かくして符号化処理又は復号化処理を高速化させ得る符号化装置及び復号化装置を実現できる。

(3)第2の実施の形態

(3−1)第2の実施の形態による符号化装置40のEBCOTブロック160の構成

図22との対応部分に同一符号を付して示す図35は、上述したJPEG2000規格に準拠した符号化装置40(図21)に適用される第2の実施の形態によるEBCOTブロック160を示し、処理ビットプレーンデータD22のストライプカラム23Aに対して正負符号プレーンバッファ50又はSRAM52Aにおける正負符号プレーンデータD20及びSIGプレーンデータD22のワードの位相がずれている点を除いて第1の実施の形態による符号化装置40のEBCOTブロック42とほぼ同様に構成されている。

すなわちこのEBCOTブロック160の場合、図36に示すように、正負符号プレーンバッファ161(図35)は、正負符号プレーンデータD20に対する記憶領域が、それぞれ実際の正負符号プレーンデータD20の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ上下に位相がずれた、縦方向に並ぶ4ビット分の正負符号プレーンデータD20を単位(1ワード)として、これらを1クロックで一括して読書きし得るようになされている。

またEBCOTブロック160においては、SRAM162(図35)についても、図36のようにSIGプレーンデータD22に対する記憶領域が、それぞれ実際のSIGプレーンデータD22の記憶に使用する領域に対して、上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素と2ビット分だけ上下方向に位相がずれた、縦方向に並ぶ4ビット分のSIGプレーンデータD22を単位(1ワード)として、これらを1クロックで一括して読書きし得るようになされている。

一方、図37に示すように、このEBCOTブロック160のビットモデル部163は、シグナルスイッチャ164の構成を除いて第1の実施の形態による符号化装置40のビットモデル部54とほぼ同様に構成されている。

そしてシグナルスイッチャ164は、トップビットプレーン22T以外の処理ビットプレーン22に対するCBM処理時、制御部65の制御のもとに、処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをまずSPパス符号化処理部165に送出する。

またシグナルスイッチャ164は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)の正負符号プレーンデータD20を正負符号プレーンバッファ161から順次読み出し、これをSPパス符号化処理部165に送出する。

この際シグナルスイッチャ164は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビットの正負符号プレーンデータD20に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20とを正負符号プレーンバッファ161から2クロックかけて読み出し、これをSPパス符号化処理部165に送出することとなる。

さらにシグナルスイッチャ164は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22をSRAM52Aから順次読み出し、これをSPパス符号化処理部61に送出する。

この場合においても、シグナルスイッチャ164は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビットのSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータと、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD20とをSRAM162から2クロックかけて読み出し、これをSPパス符号化処理部165に送出することとなる。

さらにシグナルスイッチャ164は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の4ビット(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の4ビット(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから順次読み出し、これをSPパス符号化処理部165に送出する。

この場合SRAM52Bは、処理ビットプレーン22上の各ストライプカラム23Aとそれぞれ対応する4ビット分を単位(1ワード)としてREFプレーンデータD31及びDONEプレーンデータD32を記憶しており、このワード単位でREFプレーンデータD31やDONEプレーンデータD32を読書きし得るように構成されている。従って、シグナルスイッチャ164は、かかる4ビット分のREFプレーンデータD31又はDONEプレーンデータD32をそれぞれ1クロックでSRAM52Bから読み出してSPパス符号化処理部165に送出することとなる。

このときSPパス符号化処理部165は、シグナルスイッチャ164から順次供給される4画素分の処理ビットプレーンデータD21と、これと対応する正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、ここでは処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ2ワードが1サンプルに該当する。

そしてSPパス符号化処理部165は、シグナルスイッチャ164から次のサンプルの処理ビットプレーンデータD21等が与えられると、第1の実施の形態による符号化装置40(図21)のSPパス符号化処理部61と同様にして、必要に応じてSPパス符号化処理を実行し、そのとき得られたシンボルSBをシンボルデータD26Sとして出力スイッチャ64に、コンテクストCXをコンテクストデータD27Sとして出力スイッチャ64にそれぞれ送出すると共に、必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24を更新し、さらにこれら更新したSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をSRAM162、SRAM52Bにおけるもとのアドレス位置に書き戻す。

一方、シグナルスイッチャ164は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するSPパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21をビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをMRパス符号化処理部166に送出する。

またシグナルスイッチャ164は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してMRパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD22をSRAM162から順次読み出し、これをMRパス符号化処理部166に送出する。

この際シグナルスイッチャ164は、上述のSPパス符号化処理部の場合と同様に、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をMRパス符号化処理する際に必要となる合計6ビット分のSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22とをSRAM162から2クロックかけて読み出し、これをMRパス符号化処理部166に送出することとなる。

さらにシグナルスイッチャ164は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をMRパス符号化処理する際に必要となる、当該4画素と同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから順次読み出し、これをMRパス符号化処理部166に送出する。

このときMRパス符号化処理部166は、シグナルスイッチャ164から順次供給される4画素分の処理ビットプレーンデータD21と、これと対応するSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ2ワードが1サンプルに該当する。

そしてMRパス符号化処理部166は、シグナルスイッチャ164から次のサンプルの処理ビットプレーンデータD21等が与えられると、第1の実施の形態による符号化装置40(図21)のMRパス符号化処理部62と同様にして、必要に応じてMRパス符号化処理を実行し、そのとき得られたシンボルSBをシンボルデータD26Rとして出力スイッチャ64に、コンテクストCXをコンテクストデータD27Rとして出力スイッチャ64にそれぞれ送出する一方、必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24を更新し、さらにこれら更新したSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をSRAM162、52Bにおけるもとのアドレス位置に書き戻す。

他方、シグナルスイッチャ164は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するMRパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21をビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをCUパス符号化処理部167に送出する。

またシグナルスイッチャ164は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の正負符号プレーンデータD20を正負符号プレーンバッファ161(図35)から順次読み出し、これをCUパス符号化処理部167に送出する。

この際シグナルスイッチャ164は、上述のSPパス符号化処理部165と同様に、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる合計6ビットの正負符号プレーンデータD20に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20とを正負符号プレーンバッファ161から2クロックかけて読み出し、これをCUパス符号化処理部167に送出することとなる。

さらにシグナルスイッチャ164は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22をSRAM162から順次読み出し、これをCUパス符号化処理部167に送出する。

この場合においても、シグナルスイッチャ164は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる合計6ビット分のSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22とをSRAM162から2クロックかけて読み出し、これをCUパス符号化処理部167に送出することとなる。

さらにシグナルスイッチャ164は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とをSRAM52Bから読み出し、これをCUパス符号化処理部167に送出する。

このときCUパス符号化処理部167は、シグナルスイッチャ164から順次供給される4画素分の処理ビットプレーンデータD21と、これと対応する正負符号プレーンデータD20、SIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD21、REFプレーンデータD23及びDONEプレーンデータD24については1ワードが1サンプルに該当し、正負符号プレーンデータD20及びSIGプレーンデータD22については縦方向に並ぶ2ワードが1サンプルに該当する。

そしてCUパス符号化処理部167は、シグナルスイッチャ164から次のサンプルの処理ビットプレーンデータD21等が与えられると、第1の実施の形態による符号化装置40(図21)のCUパス符号化処理部63と同様にして、CUパス符号化処理又はSPパス符号化処理を実行し、そのとき得られたシンボルSBをシンボルデータD26Cとして出力スイッチャ64に、コンテクストCXをコンテクストデータD27Cとして出力スイッチャ64にそれぞれ送出する一方、必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24を更新し、さらにこれら更新したSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をSRAM162、52Bにおけるもとのアドレス位置に書き戻す。

このようにしてこのビットモデル部163においては、CBM処理時における正負符号プレーンデータD20及びSIGプレーンデータD22のアクセス単位(1ワード)の位相を処理ビットプレーン22上のストライプカラム23Aに対して2ビット分ずらすことによって、処理ビットプレーンデータD21の1ストライプカラム23Aを処理する際の正負符号プレーンバッファ161やSRAM162へのアクセス回数を低減させ得るようになされている。

(3−2)第2の実施の形態による復号化装置100のEBCOTブロック170の構成

図30との対応部分に同一符号を付して示す図38は、上述のJPEG2000規格に準拠した復号化装置100(図29)に適用される第2の実施の形態によるEBCOTブロック170を示し、処理ビットプレーンデータD22のストライプカラム23Aに対して正負符号プレーンバッファ171又はSRAM172における正負符号プレーンデータD20及びSIGプレーンデータD22のワードの位相がずれている点を除いて第1の実施の形態による復号化装置100のEBCOTブロック4101とほぼ同様に構成されている。

すなわちこのEBCOTブロック170の場合、図36について上述した正負符号プレーンバッファ161(図35)及びSRAM162(図35)と同様に、正負符号プレーンバッファ171における正負符号プレーンデータD36に対する記憶領域と、SRAM172におけるSIGプレーンデータD30に対する記憶領域とが、それぞれ実際の正負符号プレーンデータD36又はSIGプレーンデータD30の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ位相がずれた、縦方向に並ぶ4ビット分の正負符号プレーンデータD36又はSIGプレーンデータD30をそれぞれ1ワードとして、これらを1クロックで一括して読書きし得るようになされている。

また図39に示すように、このEBCOTブロック170のビットデモデル部173は、シグナルスイッチャ174の構成を除いて第1の実施の形態による復号化装置101のビットデモデル部114とほぼ同様に構成されている。

実際上、シグナルスイッチャ174は、制御部125の制御のもとに、ビットプレーンバッファ116A、116B(図38)に記憶保持されている復号前又は一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワードずつ順次読み出し、これをまずSPパス復号化処理部175に送出する。

またシグナルスイッチャ174は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の復号前又は一部が復号された正負符号プレーンデータD36を正負符号プレーンバッファ171から順次読み出し、これをSPパス復号化処理部175に送出する。

この際シグナルスイッチャ174は、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をSPパス復号化処理する際に必要となる合計6ビットの正負符号プレーンデータD36に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36とを正負符号プレーンバッファ171から2クロックかけて読み出し、これをSPパス復号化処理部175に送出することとなる。

さらにシグナルスイッチャ174は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30をSRAM172から順次読み出し、これをSPパス復号化処理部175に送出する。

この場合においても、シグナルスイッチャ174は、かかるビットプレーンバッファ116A、116B(図38)から読み出された4画素分の処理ビットプレーンデータD21をSPパス復号化処理する際に必要となる合計6ビットのSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30とをSRAM172から2クロックかけて読み出し、これをSPパス復号化処理部175に送出することとなる。

さらにシグナルスイッチャ174は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の4ビット(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の4ビット(図24(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをSPパス復号化処理部175に送出する。

この場合SRAM111Bは、処理ビットプレーン22上の各ストライプカラム23Aとそれぞれ対応する4ビット分を単位(1ワード)としてREFプレーンデータD31及びDONEプレーンデータD32を記憶しており、このワード単位でREFプレーンデータD31やDONEプレーンデータD32を読書きし得るように構成されている。従って、シグナルスイッチャ174は、かかる4ビット分のREFプレーンデータD31又はDONEプレーンデータD32をそれぞれ1クロックでSRAM111Bから読み出してSPパス復号化処理部175に送出することとなる。

このときSPパス復号化処理部175は、シグナルスイッチャ174から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応する正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、ここでは処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードがそれぞれ1サンプルに該当し、正負符号プレーンデータD36及びSIGプレーンデータD30については縦方向に並ぶ2ワードがそれぞれ1サンプルに該当する。

そしてSPパス復号化処理部175は、算術復号化部113から1シンボル分のシンボルデータD34が与えられると、第1の実施の形態による復号化装置101(図29)のSPパス復号化処理部175と同様にして、必要に応じてSPパス復号化処理を実行し、そのとき得られたコンテクストCXを出力スイッチャ124を介してコンテクストデータD33として算術復号部113(図38)に送出すると共に、これと併せて得られた復号された処理ビットプレーンデータD35及び復号された正負符号プレーンデータD36をそれぞれビットプレーンバッファ116A、116B又は正負符号バッファ171の対応する位置に格納する。さらにSPパス復号化処理部175は、必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24を更新すると共に、これら更新したSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24をSRAM172、52Bにおけるもとのアドレス位置に書き戻す。

一方、算術復号化部113(図38)は、ストリームバッファ110A、110Bから読み出した符号化データD11のうち、符号化装置40(図21)においてMRパス符号化処理することにより得られた符号化データD11に対して上述のような算術復号化演算処理を施すことにより得られたシンボルデータD34についてはMRパス復号化処理部176に送出する。

このときシグナルスイッチャ174は、制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている先行するSPパス復号化処理により一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワード分ずつ順次読み出し、これをMRパス復号化処理部176に送出する。

またシグナルスイッチャ174は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をMRパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30をSRAM172から順次読み出し、これをMRパス復号化処理部176に送出する。

この際シグナルスイッチャ174は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をMRパス復号化処理する際に必要となる合計6ビット分のSIGプレーンデータに対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータと、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータとをSRAMから2クロックかけて読み出し、これをMRパス復号化処理部176に送出することとなる。

さらにシグナルスイッチャ174は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をMRパス復号化処理する際に必要となる、当該4画素と同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをMRパス復号化処理部176に送出する。

このときMRパス復号化処理部176は、シグナルスイッチャ174から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応するSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードがそれぞれ1サンプルに該当し、正負符号プレーンデータDD36及びSIGプレーンデータD30については縦方向に並ぶ2ワード分が1サンプルに該当する。

そしてMRパス復号化処理部1176は、算術復号化部113(図38)から1シンボル分のシンボルデータD34が与えられると、第1の実施の形態による復号化装置101(図29)のMRパス復号化処理部122(図31)と同様にして、必要に応じてMRパス復号化処理を実行し、そのとき得られたコンテクストCXを出力スイッチャ124を介してコンテクストデータD33として算術復号部113(図38)に送出すると共に、これと併せて得られた復号された処理ビットプレーンデータD35をビットプレーンバッファ116A、116Bの対応する位置に格納する。さらにMRパス復号化処理部176は、必要に応じてSIGプレーンデータD30、REFプレーンデータD31及び又はDONEプレーンデータD32を更新すると共に、これら更新したSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32をSRAM172、111Bにおけるもとのアドレス位置に書き戻す。

これと同様にして、算術復号化部113(図38)は、ストリームバッファ110A、110Bから読み出した符号化データD11のうち、符号化装置40(図21)においてCUパス符号化処理することにより得られた符号化データD11に対して所定の算術復号化演算処理を施すことにより得られたシンボルデータD34についてはCUパス復号化処理部177に送出する。

このときシグナルスイッチャ174は、制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている先行するSPパス復号化処理及びMRパス復号化処理(トップビットプレーン22Tに対する復号化処理の場合を除く)により一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワードずつ順次読み出し、これをCUパス復号化処理部177に送出する。

またシグナルスイッチャ174は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の復号前又は一部が復号された正負符号プレーンデータD36を正負符号プレーンバッファ171から順次読み出し、これをCUパス復号化処理部177に送出する。

この際シグナルスイッチャ174は、かかるビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる合計6ビットの正負符号プレーンデータD36に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36とを正負符号プレーンバッファ171から2クロックかけて読み出し、これをCUパス復号化処理部177に送出することとなる。

さらにシグナルスイッチャ174は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をCUパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30をSRAM172から順次読み出し、これをCUパス復号化処理部177に送出する。

この場合においても、シグナルスイッチャ174は、かかるビットプレーンバッファ116A、51Bから読み出された4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる合計6ビット分のSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30とをSRAM172から2クロックかけて読み出し、これをCUパス復号化処理部177に送出することとなる。

さらにシグナルスイッチャ174は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をCUパス復号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD32とをSRAM111Bから順次読み出し、これをCUパス復号化処理部177に送出する。

このときCUパス復号化処理部177は、シグナルスイッチャ174から順次供給される4画素分の処理ビットプレーンデータD35と、これと対応する正負符号プレーンデータD36、SIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32とを、それぞれ少なくとも過去3サンプル分だけ記憶保持し得るようになされている。

因みに、この場合も処理ビットプレーンデータD35、REFプレーンデータD31及びDONEプレーンデータD32については1ワードがそれぞれ1サンプルに該当し、正負符号プレーンデータD36及びSIGプレーンデータD30については縦方向に並ぶ2ワード分が1サンプルに該当する。

そしてCUパス復号化処理部177は、算術復号化部113(図38)から1シンボル分のシンボルデータD34が与えられると、第1の実施の形態による復号化装置101(図29)のCUパス復号化処理部123(図31)と同様にして、必要に応じてCUパス復号化処理又はSPパス復号化処理を実行し、そのとき得られたコンテクストCXを出力スイッチャ124を介してコンテクストデータD33として算術復号部113(図38)に送出すると共に、これと併せて得られた復号された処理ビットプレーンデータD35及び復号された正負符号プレーンデータD36をそれぞれビットプレーンバッファ116A、116B又は正負符号バッファ171の対応する位置に格納する。さらにCUパス復号化処理部177は、必要に応じてSIGプレーンデータD30、REFプレーンデータD31及び又はDONEプレーンデータD32を更新すると共に、これら更新したSIGプレーンデータD30、REFプレーンデータD31及びDONEプレーンデータD32をSRAM172、52Bにおけるもとのアドレス位置に書き戻す。

このようにしてこのビットデモデル部173においても、CBM処理時における正負符号プレーンデータ及びSIGプレーンデータのアクセス単位(1ワード)の位相を処理ビットプレーン22上のストライプカラムに対して2ビット分ずらすことによって、処理ビットプレーンデータD35の1ストライプカラム23Aを処理する際のメモリアクセス回数を低減させ得るようになされている。

(3−3)第2の実施の形態の動作及び効果

以上の構成において、本実施の形態によるビットモデル部163及びビットデモデル部173では、処理ビットプレーン22上のストライプカラム2Aを構成する4画素を単位としてCBM処理を行うと共に、このとき正負符号プレーンデータD20、D36及びSIGプレーンデータD22、D30については、ストライプカラム23Aに対して縦方向に2ビットずれた4ビットをアクセス単位(1ワード)として、正負符号プレーンバッファ161、171又はSRAM162、172から読み出す。

従って、図25及び図36を見比べてみても明らかなように、1ストライプカラム23A分の処理ビットプレーンデータD21、D35をCBM処理するに際して、第1の実施の形態のビットモデル部54及びビットデモデル部114によれば、9ワード分の正負符号プレーンデータD20、D36やSIGプレーンデータD22、D30の読み出し(メモリアクセス)が必要であったのに対し、この第2の実施の形態のビットモデル部163及びビットデモデル部173によれば、6ワード分の正負符号プレーンデータD20、D36やSIGプレーンデータD22、D30の読み出し(メモリアクセス)で足りることとなり、より一層とCBM処理時における正負符号プレーンバッファ50、115やSRAM52A、111Aに対するアクセス回数を格段的に低減させることができる。

実際上、例えば64×64サイズのビットプレーン22を処理する際にメモリからSIGプレーンデータD22、D30を読み出す回数を計算すると、第1の実施の形態の手法の場合、上述のようにオーバラップ読出し構成のときには8740回、更新部分限定読出し構成のときには2944回のメモリアクセスが必要となるのに対して、本実施の形態の手法によれば、オーバラップ読出し構成のときには6080回、本実施の形態のように更新部分限定読出し構成のときには2048回のメモリアクセスで足りる。

よって、かかるJPEG2000規格に準拠した符号化装置40及び復号化装置100におけるビットモデル部163又はビットデモデル部173の構成として上述のような第2の実施の形態の構成を採用することによって、これらビットモデル部163又はビットデモデル部173におけるCBM処理のより一層の高速化を図ることができ、またこれに伴ってビットモデル部163又はビットデモデル部173の低消費電力化を図ることもできる。

以上の構成によれば、処理ビットプレーン22上のストライプカラム2Aを構成する4画素を単位としてCBM処理すると共に、このとき正負符号プレーンデータD20、D36及びSIGプレーンデータD22、D30については、ストライプカラム23Aに対して縦方向に2ビットずれた4ビットをアクセス単位(1ワード)として、正負符号プレーンバッファ161、171又はSRAM162、172から読み出すようにしたことにより、第1の実施の形態に比してより一層とCBM処理時における正負符号プレーンバッファ50、115やSRAM52A、111Aに対するアクセス回数を格段的に低減させることができ、かくして符号化処理又は復号化処理をより一層と高速化させ得る符号化装置及び復号化装置を実現できる。

(4)第3の実施の形態

(4−1)第3の実施の形態による符号化装置40のEBCOTブロックの構成

図35との対応部分に同一符号を付して示す図40は、図21について上述のJPEG2000規格に準拠した符号化装置40に適用される第3の実施の形態によるEBCOTブロック180を示し、2ワード分の正負符号プレーンデータD20及びSIGプレーンデータD22を1クロックで読み出し得るようになされた点を除いて第2の実施の形態によるEBCOTブロック160(図35)と同様に構成されている。

すなわちこのEBCOTブロック180の場合、2つの正負符号プレーンバッファ181A、181Bが設けられており、ビットプレーン内スキャン順序に従ってDRAM41(図21)から読み出した正負符号プレーンデータD20のうち、図42に示すように、正負符号プレーン30をストライプ単位で順次交互に分けた場合における一方のグループに属する正負符号プレーンデータD20を一方の正負符号プレーンバッファ(以下、これを第1の正負符号プレーンバッファと呼ぶ)181Aに記憶保持すると共に、他方のグループに属する正負符号プレーンデータD20を他方の正負符号プレーンバッファ(以下、これを第2の正負符号プレーンバッファと呼ぶ)181Bに記憶保持するようになされている。

このときこれら第1及び第2の正負符号プレーンバッファ181A、181Bは、図36について上述したのと同様に、それぞれ自己に割り当てられた正負符号プレーンデータD20に対する記憶領域が、実際の正負符号プレーンデータD20の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ位相がずれた縦方向に並ぶ4ビット分の正負符号プレーンデータD20を1ワードとして、これらを1クロックで一括して読書きし得るようになされている。

またこのEBCOTブロック180では、SIGプレーンデータD22を記憶保持するSRAM182A、182Bも2つ設けられており、SIGプレーンデータD22のうちSIGプレーン31を図41のようにストライプ単位で順次交互に分けた場合における一方のグループに属するSIGプレーンデータD22を一方のSRAM(以下、これを第1のSRAMと呼ぶ)182Aに記憶保持すると共に、他方のグループに属するSIGプレーンデータD22を他方のSRAM(以下、これを第2のSRAMと呼ぶ)182Bに記憶保持するようになされている。

このときこれら第1及び第2のSRAM182A、182Bの場合も、図36について上述したのと同様に、それぞれ自己に割り当てられたSIGプレーンデータD22に対する記憶領域が、実際のSIGプレーンデータD22の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ位相がずれた縦方向に並ぶ4ビット分のSIGプレーンデータD22を1ワードとして、これらを1クロックで一括して読書きし得るようになされている。

一方、図37との対応部分に同一符号を付した図42に示すように、このEBCOTブロック180のビットモデル部183は、シグナルスイッチャ184の構成を除いて第2の実施の形態による符号化装置40(図21)のビットモデル部163と同様に構成されている。

そしてシグナルスイッチャ184は、トップビットプレーン22T以外の処理ビットプレーン22に対するCBM処理時、制御部65の制御のもとに、処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをまずSPパス符号化処理部165に送出する。

またシグナルスイッチャ184は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)の正負符号プレーンデータD20を第1及び第2の正負符号プレーンバッファ181A、181Bから順次読み出し、これをSPパス符号化処理部165に送出する。

この際シグナルスイッチャ184は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビットの正負符号プレーンデータに対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20とをそれぞれ対応する第1又は第2の正負符号プレーンバッファ181A、181Bから同時に1クロックで読み出し、これをSPパス符号化処理部165に送出することとなる。

さらにシグナルスイッチャ184は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22を第1及び第2のSRAM182A、182Bから順次読み出し、これをSPパス符号化処理部165に送出する。

この場合においても、シグナルスイッチャ184は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる合計6ビットのSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22とをそれぞれ対応する第1又は第2のSRAM182A、182Bから同時に1クロックで読み出し、これをSPパス符号化処理部165に送出することとなる。

さらにシグナルスイッチャ184は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をSPパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とを、第2の実施の形態のシグナルスイッチャ164(図37)と同様にしてSRAM52Bから順次読み出し、これをSPパス符号化処理部165に送出する。

かくしてビットモデル部183では、この後SPパス符号化処理部165において、第2の実施の形態と同様にしてSPパス符号化処理が必要に応じて行われ、そのとき得られたシンボルSBがシンボルデータD26Sとして出力スイッチャ64に、コンテクストCXがコンテクストデータとして出力スイッチャにそれぞれ送出される。また必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24が更新され、さらにこれら更新されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24が第1若しくは第2のSRAM182A、182B又はSRAM52Bにおけるもとのアドレス位置に書き戻される。

一方、シグナルスイッチャ184は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するSPパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをMRパス符号化処理部166に送出する。

またシグナルスイッチャ184は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してMRパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD22を第1及び第2のSRAM182A、182Bから順次読み出し、これをMRパス符号化処理部166に送出する。

この際シグナルスイッチャ184は、かかる合計6ビットのSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22とをそれぞれ対応する第1又は第2のSRAM182A、182Bから同時に1クロックで読み出し、これをMRパス符号化処理部166に送出することとなる。

さらにシグナルスイッチャ184は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をMRパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図22(D)参照)分のDONEプレーンデータD24とを、第2の実施の形態のシグナルスイッチャ164(図37)と同様にしてSRAM52Bから順次読み出し、これをMRパス符号化処理部166に送出する。

かくしてビットモデル部183では、この後MRパス符号化処理部166において、第2の実施の形態と同様にしてMRパス符号化処理が必要に応じて行われ、そのとき得られたシンボルSBがシンボルデータD26Sとして出力スイッチャ64に、コンテクストCXがコンテクストデータとして出力スイッチャにそれぞれ送出される。また必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24が更新され、さらにこれら更新されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24が第1若しくは第2のSRAM182A、182B又はSRAM52Bにおけるもとのアドレス位置に書き戻される。

他方、シグナルスイッチャ184は、このようにして処理ビットプレーンバッファ51A、51Bに格納された1ビットプレーン分のデータ(処理ビットプレーンデータD21)に対するMRパス符号化処理を終了すると、この後これと同様にして、制御部65の制御のもとに、同じ処理ビットプレーンデータD21をビットプレーン内スキャン順序に従って処理ビットプレーンバッファ51A、51Bから1ワードずつ順次読み出し、これをCUパス符号化処理部167に送出する。

またシグナルスイッチャ184は、これと同期して、処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21に対してCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の正負符号プレーンデータD20を第1及び第2の正負符号プレーンバッファ181A、181Bから順次読み出し、これをCUパス符号化処理部167に送出する。

この際シグナルスイッチャ184は、上述のSPパス符号化処理部165と同様に、かかる合計6ビットの正負符号プレーンデータD20に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD20とをそれぞれ対応する第1又は第2の正負符号プレーンバッファ181A、181Bから同時に1クロックで読み出し、これをCUパス符号化処理部167に送出することとなる。

さらにシグナルスイッチャ184は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及びその上下の各ビット(合計6ビット、図24(B)参照)分のSIGプレーンデータD22を第1及び第2のSRAM182A、182Bから順次読み出し、これをCUパス符号化処理部167に送出する。

この場合においても、シグナルスイッチャ184は、かかる合計6ビット分のSIGプレーンデータD22に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD22とをそれぞれ対応する第1又は第2のSRAM182A、182Bから同時に1クロックで読み出し、これをCUパス符号化処理部167に送出することとなる。

さらにシグナルスイッチャ185は、これと同期して、かかる4画素分の処理ビットプレーンデータD21をCUパス符号化処理する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD23と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD24とを第2の実施の形態のシグナルスイッチャ164(図37)と同様にしてSRAM52Bから読み出し、これをCUパス符号化処理部167に送出する。

かくしてビットモデル部183では、この後CUパス符号化処理部167において、第2の実施の形態と同様にしてCUパス符号化処理又はSPパス符号化処理が必要に応じて行われ、そのとき得られたシンボルSBがシンボルデータD26Sとして出力スイッチャ64に、コンテクストCXがコンテクストデータとして出力スイッチャにそれぞれ送出される。また必要に応じてSIGプレーンデータD22、REFプレーンデータD23及び又はDONEプレーンデータD24が更新され、さらにこれら更新されたSIGプレーンデータD22、REFプレーンデータD23及びDONEプレーンデータD24が第1若しくは第2のSRAM52A又はSRAM52Bにおけるもとのアドレス位置に書き戻される。

このようにしてこのビットモデル部183においては、正負符号プレーンデータD20を記憶保持するためのメモリとして2つの第1及び第2の正負符号プレーンバッファ181A、181Bを設けると共に、SIGプレーンデータD22を記憶保持するためのメモリとして2つの第1及び第2のSRAM182A、182Bを設けることによって、処理ビットプレーンデータD21の1ストライプカラム23Aを処理する際のメモリアクセス回数をより一層と低減させ得るようになされている。

(4−2)第3の実施の形態による復号化装置100のEBCOTブロック190の構成 図38との対応部分に同一符号を付して示す図43は、図29について上述のJPEG2000規格に準拠した復号化装置100に適用される第3の実施の形態によるEBCOTブロック190を示し、2ワード分の正負符号プレーンデータD36及びSIGプレーンデータD30を1クロックで読み出し得るようになされた点を除いて第2の実施の形態による復号化装置100(図29)のEBCOTブロック170(図37)と同様に構成されている。

すなわちこのEBCOTブロック190の場合、2つの正負符号プレーンバッファ191A、191Bが設けられており、復号した正負符号プレーンデータD36のうち、正負符号プレーン30を図41のようにストライプ単位で順次交互に分けた場合における一方のグループに属する正負符号プレーンデータD36を一方の正負符号プレーンバッファ(以下、これを第1の正負符号プレーンバッファと呼ぶ)191Aに記憶保持すると共に、他方のグループに属する正負符号プレーンデータD36を他方の正負符号プレーンバッファ(以下、これを第2の正負符号プレーンバッファと呼ぶ)191Bに記憶保持するようになされている。

このときこれら第1及び第2の正負符号プレーンバッファ191A、191Bは、図36について上述したのと同様に、それぞれ自己に割り当てられた正負符号プレーンデータD36に対する記憶領域が、実際の正負符号プレーンデータD36の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ位相がずれた縦方向に並ぶ4ビット分の正負符号プレーンデータD36を1ワードとして、これらを1クロックで一括して読書きし得るようになされている。

またこのEBCOTブロック190では、SIGプレーンデータD30を記憶保持するための2つのSRAM192A、192Bが設けられており、SIGプレーンデータD30のうちSIGプレーン31を図41のようにストライプ単位で順次交互に分けた場合における一方のグループに属するSIGプレーンデータD30を一方のSRAM(以下、これを第1のSRAMと呼ぶ)192Aに記憶保持すると共に、他方のグループに属するSIGプレーンデータD30を他方のSRAM(以下、これを第2のSRAMと呼ぶ)192Bに記憶保持するようになされている。

このときこれら第1及び第2のSRAM192A、192Bの場合も、図36について上述したのと同様に、それぞれ自己に割り当てられたSIGプレーンデータD30に対する記憶領域が、実際のSIGプレーンデータD30の記憶に使用する領域に対して上下方向にそれぞれ2ビット分ずつ拡張されており、処理ビットプレーン22上の1ストライプカラム23Aを構成する4画素に対して2ビット分だけ位相がずれた縦方向に並ぶ4ビット分のSIGプレーンデータD30を1ワードとして、これらを1クロックで一括して読書きし得るようになされている。

一方、図39との対応部分に同一符号を付した図44に示すように、このEBCOTブロック190のビットデモデル部193は、シグナルスイッチャ194の構成を除いて第2の実施の形態による復号化装置100(図29)のビットデモデル部173(図39)と同様に構成されている。

そしてシグナルスイッチャ194は、制御部125の制御のもとに、ビットプレーンバッファ116A、116Bに記憶保持されている復号前又は一部が復号された処理ビットプレーンデータD35を、図24(A)に示す1ストライプカラム23Aを構成する4画素分を1ワードとして、ビットプレーン内スキャン順序に従ってビットプレーンバッファ116A、116Bから1ワードずつ順次読み出し、これをまずSPパス復号化処理部175に送出する。

またシグナルスイッチャ194は、これと同期して、ビットプレーンバッファ116A、116Bから読み出された4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビット及びその上下の各ビット(合わせて6ビット、図24(C)参照)分の復号前又は一部が復号された正負符号プレーンデータD36を第1及び第2の正負符号プレーンバッファ191A、191Bから順次読み出し、これをSPパス復号化処理部175に送出する。

この際シグナルスイッチャ194は、上述のように処理ビットプレーン22のストライプカラム23Aに対して正負符号プレーン30上において縦方向に2ビットだけ位相がずれた縦4ビット分の正負符号プレーンデータD36をアクセス単位(1ワード)としているため、かかる合計6ビットの正負符号プレーンデータD36に対して、実際には当該4画素とそれぞれ同座標にある正負符号プレーン30上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36と、下側に2ビットずれた1ワード(4ビット)分の正負符号プレーンデータD36とをそれぞれ対応する第1又は第2の正負符号プレーンバッファ191A、191Bから同時に1クロックで読み出し、これをSPパス復号化処理部175に送出することとなる。

さらにシグナルスイッチャ194は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビット及その上下のビット(合わせて6ビット、図24(B)参照)のSIGプレーンデータD30を第1及び第2のSRAM192A、192Bから順次読み出し、これをSPパス復号化処理部175に送出する。

この場合においても、シグナルスイッチャ194は、かかる処理ビットプレーンバッファ51A、51Bから読み出された4画素分の処理ビットプレーンデータD21をSPパス復号化処理する際に必要となる合計6ビットのSIGプレーンデータD30に対して、実際には当該4画素とそれぞれ同座標にあるSIGプレーン31上の4ビットよりも上側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30と、下側に2ビットずれた1ワード(4ビット)分のSIGプレーンデータD30とをそれぞれ対応する第1又は第2のSRAM192A、192Bから同時に1クロックで読み出し、これをSPパス復号化処理部175に送出することとなる。

さらにシグナルスイッチャ194は、これと同期して、かかる4画素分の処理ビットプレーンデータD35をSPパス復号化処理により復号する際に必要となる、当該4画素とそれぞれ同座標にあるREFプレーン32上の1ワード(図24(E)参照)分のREFプレーンデータD31と、当該4画素と同座標にあるDONEプレーン33上の1ワード(図24(D)参照)分のDONEプレーンデータD32とを、第2の実施の形態のシグナルスイッチャ174(図39)と同様にしてSRAM111Bから順次読み出し、これをSPパス復号化処理部175に送出する。