JP4116067B2 - Liquid crystal display - Google Patents

Liquid crystal display Download PDFInfo

- Publication number

- JP4116067B2 JP4116067B2 JP2007194436A JP2007194436A JP4116067B2 JP 4116067 B2 JP4116067 B2 JP 4116067B2 JP 2007194436 A JP2007194436 A JP 2007194436A JP 2007194436 A JP2007194436 A JP 2007194436A JP 4116067 B2 JP4116067 B2 JP 4116067B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- conductive layer

- liquid crystal

- line

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 37

- 239000010408 film Substances 0.000 claims description 44

- 239000000758 substrate Substances 0.000 claims description 43

- 238000006243 chemical reaction Methods 0.000 claims description 10

- 239000010409 thin film Substances 0.000 claims description 9

- 230000001681 protective effect Effects 0.000 claims description 5

- 239000000463 material Substances 0.000 claims description 3

- 230000005684 electric field Effects 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 10

- 238000000034 method Methods 0.000 description 8

- 239000011651 chromium Substances 0.000 description 7

- 241000519995 Stachys sylvatica Species 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 102100036464 Activated RNA polymerase II transcriptional coactivator p15 Human genes 0.000 description 1

- 101000713904 Homo sapiens Activated RNA polymerase II transcriptional coactivator p15 Proteins 0.000 description 1

- 229910004444 SUB1 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 210000001520 comb Anatomy 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

Description

この発明は、面内応答型液晶表示装置(以下、IPS(in plane switching)パネルと称す)に関する。さらに詳しくは、表示領域のゲート端子近傍の白抜けをなくし表示特性を向上した構造の液晶表示装置に関する。 The present invention relates to an in-plane response type liquid crystal display device (hereinafter referred to as an IPS (in plane switching) panel). More specifically, the present invention relates to a liquid crystal display device having a structure in which white spots in the vicinity of a gate terminal in a display area are eliminated and display characteristics are improved.

従来のIPSパネルにおいては、画素電極PXは、対向電圧信号線CLと接続された対向電極CTとの間に電界を発生させ、この電界によって液晶の光透過率を制御させるようになっている(例えば、特許文献1参照)。

従来のIPSパネルでは、透明基板SUB1上のゲート信号線GLとゲート端子とを結ぶ引き出し配線、詳しくは、表示領域外の隣接するゲート端子間の間隔が隣接するゲート配線間の間隔より狭いためにゲート端子に近いほど配線ピッチが狭くなる引き出し配線群(以下、テーパーゲート配線部と称す)から発生する電界により、対向基板である透明基板SUB2の電位変動を誘発し、ゲート端子近傍の液晶表示部ARに白抜けが生じるという問題点があった。 In the conventional IPS panel, the lead line connecting the gate signal line GL and the gate terminal on the transparent substrate SUB1, more specifically, the distance between adjacent gate terminals outside the display area is narrower than the distance between adjacent gate lines. A liquid crystal display near the gate terminal is induced by an electric field generated from a lead wiring group (hereinafter referred to as a tapered gate wiring portion) in which the wiring pitch becomes narrower as it is closer to the gate terminal. There was a problem that white spots occurred in AR.

この発明は、上述のような課題を解決するためになされたもので、IPSパネルを用いた場合において、テーパーゲート配線部から発生する電界を遮蔽し、対向基板の電位変動を防止することで、ゲート端子近傍の表示領域に白抜けを生じない液晶表示装置を得るものである。 The present invention has been made to solve the above-described problems. When an IPS panel is used, the electric field generated from the tapered gate wiring portion is shielded, and the potential fluctuation of the counter substrate is prevented. A liquid crystal display device that does not cause white spots in the display region near the gate terminal is obtained.

この発明に係る液晶表示装置においては、ゲート配線に電圧を印加するためのゲート端子およびこれに接続するため設置されたテーパーゲート配線部が設けられ、テーパーゲート配線部の上層に絶縁膜を介して導電層を配設したものである。 In the liquid crystal display device according to the present invention, a gate terminal for applying a voltage to the gate wiring and a tapered gate wiring portion installed to connect to the gate terminal are provided, and an insulating film is provided above the tapered gate wiring portion. A conductive layer is provided.

この発明は、テーパーゲート配線部の上層に絶縁膜を介して導電層を配設したことにより、テーパーゲート配線部から発生する電界を導電層が遮蔽し、対向基板の電位変動を防止することで、ゲート端子近傍の表示領域に白抜けを生じず表示品位を向上することが可能となる。 According to the present invention, the conductive layer is disposed on the upper layer of the tapered gate wiring portion with an insulating film interposed therebetween, so that the conductive layer shields the electric field generated from the tapered gate wiring portion and prevents the potential fluctuation of the counter substrate. Thus, it is possible to improve the display quality without causing white spots in the display area near the gate terminal.

実施の形態1.

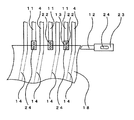

図1はこの発明を実施するための実施の形態1における液晶表示装置の薄膜トランジスタ(以下、TFTと称す)近傍を拡大した平面図、図2は図1に示すTFT近傍の矢視A−A線からみた部分断面の製造工程を示した説明図、図3はこの発明を実施するための実施の形態1における液晶表示装置のゲート端子側の端部を示した平面図、図4は図3に示すテーパーゲート配線部近傍の矢視B−B線からみた部分断面の製造工程を示した説明図、図5はこの発明を実施するための実施の形態1における液晶表示装置のテーパーゲート配線部近傍を拡大した平面図、図6は図5に示すテーパーゲート配線部近傍の矢視C−C線からみた部分断面の製造工程を示した説明図である。

1 is an enlarged plan view of the vicinity of a thin film transistor (hereinafter referred to as TFT) of a liquid crystal display device according to

図1〜図6において、透明な絶縁性基板である第1の基板1a上に表示領域2を形成する画素が配設され、各画素はTFT3を具備している。ゲート配線4はゲート絶縁膜5を介してソース配線6と交差しており、TFT3は複数のゲート配線4と複数のソース配線6の各交差部に対応して形成されている。TFT3のゲート電極4aはゲート配線4の一部であり、ソース電極6aはソース配線6の一部であり、ドレイン電極6bは第1のコンタクトホール7を介して画素電極8に接続されている。

In FIG. 1 to FIG. 6, pixels that form a

TFT3に接続された櫛歯状の画素電極8と、画素電極8の櫛歯とほぼ並行かつ交互に対応して形成され、共通信号線11に第2のコンタクトホール9を介して接続された櫛歯状の対向電極10との間に電圧を印加することによって、第1の基板1a面にほぼ平行な電界を発生させる。画素電極8は、クロム(Cr)等の金属やITO(Indium Tin Oxide)等の透明性導電膜により形成されている。

Comb-

共通信号線11は、一般的に、表示装置全体として同一の電圧が印加されるため、表示領域2の外側に配設された接続線12に変換部13を介して複数の共通信号線11を共通に接続する。共通信号線11は、クロム(Cr)等の金属からなる。

この例では、ソース配線6、画素電極8、対向電極10は、中央部において1回屈曲している。そして、この屈曲点は、共通信号線11に対応する位置に設けられている。このように、屈曲した電極構成により、2方向の液晶の駆動方向を得ることができ、IPSパネルで特定方向におこる視角特性の悪化を改善することができる。

Since the common voltage is generally applied to the

In this example, the source wiring 6, the

各ゲート配線4およびソース配線6は、表示領域2からテーパーゲート配線部14およびテーパーソース配線部15によりそれぞれ引き出され、第1の基板1aの端部近傍に形成されたゲート端子16とソース端子17にそれぞれ接続されている。また、接続線12は、ゲート端子16またはソース端子17と並行に形成された共通信号線端子23に接続されている。

The

ゲート端子16、ソース端子17および共通信号線端子23に、例えば、ACF(Anisotropic Conductive Film:異方性導電膜)などの導電性材料により、フィルム基板に実装された駆動回路などが接続されている。

A drive circuit or the like mounted on a film substrate is connected to the

以下、第1の基板1a上にTFT3を形成した基板をアレイ基板と称す。

第1の基板1aに対向する第2の基板1bと第1の基板1aとの間隙に複数のスペーサを配置し、二枚の基板を等間隔に保持している。また、第1の基板1aと第2の基板1bの周辺部に配置され両基板を貼り合わせるシール材と封止材により液晶を封入させる。第2の基板1b上には、着色層、遮光層、液晶に初期配向をもたせる配向膜および光を偏光させる偏光板などが形成され、アレイ基板に対向することで対向基板と称す。

Hereinafter, a substrate in which the

A plurality of spacers are arranged in the gap between the second substrate 1b and the first substrate 1a facing the first substrate 1a, and the two substrates are held at equal intervals. In addition, liquid crystal is sealed by a sealing material and a sealing material that are arranged around the first substrate 1a and the second substrate 1b and are bonded to each other. On the second substrate 1b, a colored layer, a light-shielding layer, an alignment film for imparting initial alignment to the liquid crystal, a polarizing plate for polarizing light, and the like are formed and referred to as a counter substrate by facing the array substrate.

第1の基板1a上のテーパーゲート配線部14の上層には絶縁膜を介して導電層18を形成するが、この実施の形態1においては、絶縁膜はゲート配線4およびソース配線6を絶縁するゲート絶縁膜5と後述する保護膜21であり、導電層18は画素電極8と同一の製造工程で形成された、すなわち、同一層の導電膜により形成している。

A

なお、この導電層18のパターンは、第2の基板1b側から見てテーパーゲート配線部14をすべて覆うような領域に配設することがテーパーゲート配線部14から発生する電界を漏れなく遮蔽することができ好ましいが、ゲート端子16近傍の表示領域2に白抜けを生じない範囲で導電層18のパターンをゲート端子16から表示領域側に狭めてもよい。

つぎに、本発明の実施の形態1にかかる液晶表示装置の製造方法を図2、図4および図6を用いて説明する。

Note that the pattern of the

Next, a method for manufacturing the liquid crystal display device according to the first embodiment of the present invention will be described with reference to FIGS.

まず、図2(a)、図4(a)および図6(a)に示すように、絶縁性基板上にCr、Al、Ti、Ta、Mo、W、Ni、Cu、Au、Ag等やそれらを主成分とする合金、またはITO等の透光性を有する導電膜、またはそれらの多層膜等をスパッタ法や蒸着法等により成膜し、写真製版・加工により、ゲート配線4、ゲート電極4a、共通信号線11およびテーパーゲート配線部14を形成する。

First, as shown in FIGS. 2 (a), 4 (a) and 6 (a), Cr, Al, Ti, Ta, Mo, W, Ni, Cu, Au, Ag, etc. are formed on an insulating substrate. An alloy containing them as a main component, a light-transmitting conductive film such as ITO, or a multilayer film thereof is formed by sputtering, vapor deposition, etc. 4a, the

次に、図2(b)、図4(b)および図6(b)に示すように、窒化シリコン等よりなるゲート絶縁膜5を形成し、さらに非晶質Si、多結晶poly−Si等よりなる半導体膜19、n型のTFTの場合はP等の不純物を高濃度にドーピングしたn+非晶質Si、n+多結晶poly−Si等よりなるコンタクト膜20を、連続的に例えばプラズマCVD、常圧CVD、減圧CVD法で成膜する。

Next, as shown in FIGS. 2B, 4B, and 6B, a

次いで、半導体膜19およびコンタクト膜20を島状に加工する。

Next, the

次に、図2(c)、図4(c)および図6(c)に示すように、Cr、Al、Ti、Ta、Mo、W、Ni、Cu、Au、Ag等やそれらを主成分とする合金、またはITO等の透光性を有する導電膜、またはそれらの多層膜等をスパッタ法や蒸着法で成膜後、写真製版と微細加工技術により、ソース配線6、ソース電極6a、ドレイン電極6b、テーパーソース配線部15、接続線12および保持容量電極等を形成する。

Next, as shown in FIG. 2 (c), FIG. 4 (c) and FIG. 6 (c), Cr, Al, Ti, Ta, Mo, W, Ni, Cu, Au, Ag, etc. and their main components After forming a light-transmitting conductive film such as ITO or a transparent conductive film such as ITO by a sputtering method or a vapor deposition method, the

さらに、ソース電極6aおよびドレイン電極6bあるいはそれらを形成したホトレジストをマスクとしてコンタクト膜20をエッチングし、チャネル領域から取り除く。

Further, the

次いで、図2(d)、図4(d)および図6(d)に示すように、窒化シリコンや酸化シリコン、無機絶縁膜または有機樹脂等からなる保護膜21を成膜する。

その後、写真製版とそれに続くエッチングにより、第1のコンタクトホール7、第2のコンタクトホール9、テーパーゲート配線部14とゲート端子16および共通信号線11と変換部13とを接続する第3のコンタクトホール22、ならびにテーパーソース配線部15とソース端子17および接続線12と共通信号線端子23または変換部13とを接続する第4のコンタクトホール24を形成する。

Next, as shown in FIGS. 2D, 4D, and 6D, a

Thereafter, a third contact for connecting the

最後に、図2(e)、図4(e)および図6(e)に示すように、Cr、Al、Ti、Ta、Mo、W、Ni、Cu、Au、Ag等やそれらを主成分とする合金、またはITO等の透光性を有する導電膜、またはそれらの多層膜等を成膜後、パターニングすることで、画素電極8、対向電極10、ゲート端子16、ソース端子17、変換部13、導電層18および共通信号線端子23を形成する。

Finally, as shown in FIG. 2 (e), FIG. 4 (e) and FIG. 6 (e), Cr, Al, Ti, Ta, Mo, W, Ni, Cu, Au, Ag, etc. and their main components The

以上の工程により、本実施の形態におけるIPSパネルを構成するアレイ基板を作製することができる。さらに、このアレイ基板と対向基板の間に液晶を挟持し、シール材にて接合する。このときラビング、光配向等の方法により液晶分子を所定の角度で配向させる。なお、液晶を配向させる方法は、既知のどのような方法を用いてもよい。さらに、ゲート配線4、ソース配線6、共通信号線11にそれぞれゲート線駆動回路、ソース線駆動回路、共通信号線用電源を接続することにより液晶表示装置を作製する。

Through the above steps, the array substrate constituting the IPS panel in this embodiment can be manufactured. Further, a liquid crystal is sandwiched between the array substrate and the counter substrate and bonded with a sealing material. At this time, liquid crystal molecules are aligned at a predetermined angle by a method such as rubbing or photo-alignment. Note that any known method may be used as a method of aligning the liquid crystal. Further, a liquid crystal display device is manufactured by connecting a gate line driving circuit, a source line driving circuit, and a common signal line power source to the

以上のように、この実施の形態1においては、導電層18をゲート絶縁膜5および保護膜21を介してテーパーゲート配線部14の上層に配設することで、テーパーゲート配線部14から発生する電界を導電層18によって遮蔽し、対向基板の電位変動を防止することで、ゲート端子16近傍の表示領域2に白抜けを生じさせない液晶表示装置を得ることができる。

As described above, in the first embodiment, the

また、導電層18を画素電極8と同一工程で形成することで、導電層18を形成するための写真製版におけるマスク数の増加による製造工程数の増加や、導電層18の材料を新たに追加することなく、液晶表示装置を得ることができる。

Further, by forming the

なお、この実施の形態1では、導電層18と変換部13とを離間して形成しているが、図7に示すように、変換部13をゲート端子16側に延在させ導電層18を兼用することで、導電層18を共通信号線11と電気的に接続し、固定電位によってシールドさせることができるので好ましい。図7はこの発明を実施するための実施の形態1における他の液晶表示装置のテーパーゲート配線部近傍を拡大した平面図である。

In the first embodiment, the

また、この実施の形態1では、導電層18を画素電極8と同一工程で形成しているが、図8に示すように、ソース配線6、ソース電極6a、ドレイン電極6b、テーパーソース配線部15、接続線12および保持容量電極等と同一工程で形成しても、導電層18がテーパーゲート配線部14から発生する電界を遮蔽することができるので、同様の効果が得られる。図8は図3に示すテーパーゲート配線部近傍の矢視B−B線からみた部分断面の他の製造工程を示した説明図である。

In the first embodiment, the

また、この実施の形態1では、導電層18と接続線12とを離間して形成しているが、図9に示すように、接続線12をゲート端子16側に延在させ導電層18を兼用することで、導電層18を共通信号線11と電気的に接続し、固定電位によってシールドさせることができるので好ましい。図9はこの発明を実施するための実施の形態1における他の液晶表示装置のテーパーゲート配線部近傍を拡大した平面図である。

In the first embodiment, the

また、この実施の形態1では、導電層18をアレイ基板上に形成しているが、対向基板上のテーパーゲート配線部14に対応する領域に導電層18を形成しても、導電層18がテーパーゲート配線部14から発生する電界を遮蔽することができるので、同様の効果が得られる。

In the first embodiment, the

1a 第1の基板、1b 第2の基板、2 表示領域、3 TFT、4 ゲート配線、4aゲート電極、5 ゲート絶縁膜、6 ソース配線、6a ソース電極、6b ドレイン電極、7 第1のコンタクトホール、8 画素電極、9 第2のコンタクトホール、10 対向電極、11 共通信号線、12 接続線、13 変換部、14 テーパーゲート配線部、15 テーパーソース配線部、16 ゲート端子、17 ソース端子、18 導電層、19 半導体層、20 コンタクト膜、21 保護膜、22 第3のコンタクトホール、23 共通信号線、24 第4のコンタクトホール DESCRIPTION OF SYMBOLS 1a 1st board | substrate, 1b 2nd board | substrate, 2 Display area, 3 TFT, 4 Gate wiring, 4a gate electrode, 5 Gate insulating film, 6 Source wiring, 6a Source electrode, 6b Drain electrode, 7 1st contact hole , 8 Pixel electrode, 9 Second contact hole, 10 Counter electrode, 11 Common signal line, 12 Connection line, 13 Conversion part, 14 Tapered gate wiring part, 15 Tapered source wiring part, 16 Gate terminal, 17 Source terminal, 18 Conductive layer, 19 semiconductor layer, 20 contact film, 21 protective film, 22 third contact hole, 23 common signal line, 24 fourth contact hole

Claims (10)

前記薄膜トランジスタに接続された画素電極、

前記画素電極に対向して形成された対向電極、

複数の前記対向電極に共通の電位を与える接続線、

前記ゲート配線に電圧を印加するためのゲート端子、

前記ゲート配線と前記ゲート端子とを接続する表示領域外にある引き出し配線

を有するアレイ基板と、

前記アレイ基板に対向する対向基板とを備え、

前記引き出し配線の上層に、絶縁膜を介して導電層を配設し、

前記導電層は、透光性を有する導電膜で形成されると共に、

前記接続線上に設けられたコンタクトホールを介して前記接続線と接続されたことを特徴とする液晶表示装置。 A thin film transistor formed corresponding to each intersection of a plurality of gate lines and a plurality of source lines;

A pixel electrode connected to the thin film transistor;

A counter electrode formed to face the pixel electrode;

A connection line for applying a common potential to the plurality of counter electrodes;

A gate terminal for applying a voltage to the gate wiring;

An array substrate having a lead-out line outside the display region connecting the gate line and the gate terminal;

A counter substrate facing the array substrate,

A conductive layer is disposed above the lead-out wiring via an insulating film,

The conductive layer is formed of a light-transmitting conductive film,

A liquid crystal display device connected to the connection line via a contact hole provided on the connection line .

前記薄膜トランジスタに接続された画素電極、

前記画素電極に対向して形成され、共通信号線に接続された対向電極、

複数の前記共通信号線を共通に接続する接続線、

前記ゲート配線に電圧を印加するためのゲート端子、

前記ゲート配線と前記ゲート端子とを接続する表示領域外にある引き出し配線

を有するアレイ基板と、

前記アレイ基板に対向する対向基板とを備え、

前記接続線以外に、前記引き出し配線の上層に絶縁膜を介して導電層を配設し、

前記導電層は、透光性を有する導電膜で形成されると共に、

前記接続線上に設けられたコンタクトホールを介して前記接続線と接続されたことを特徴とする液晶表示装置。 A thin film transistor formed corresponding to each intersection of a plurality of gate lines and a plurality of source lines;

A pixel electrode connected to the thin film transistor;

A counter electrode formed facing the pixel electrode and connected to a common signal line;

A connection line for commonly connecting a plurality of the common signal lines;

A gate terminal for applying a voltage to the gate wiring;

An array substrate having a lead-out line outside the display region connecting the gate line and the gate terminal;

A counter substrate facing the array substrate,

In addition to the connection line, a conductive layer is disposed on the lead wiring via an insulating film,

The conductive layer is formed of a light-transmitting conductive film,

A liquid crystal display device connected to the connection line via a contact hole provided on the connection line .

前記薄膜トランジスタに接続された画素電極、

前記画素電極に対向して形成され、共通信号線に接続された対向電極、

複数の前記共通信号線を共通に接続する接続線、

前記ゲート配線に電圧を印加するためのゲート端子、

前記ゲート配線と前記ゲート端子とを接続する表示領域外にある引き出し配線

を有するアレイ基板と、

前記アレイ基板に対向する対向基板とを備え、

前記引き出し配線の上層に、絶縁膜を介して前記接続線を前記ゲート端子側に延在させて形成した導電層を配設し、

前記導電層は、透光性を有する導電膜で形成されると共に、

前記接続線上に設けられたコンタクトホールを介して前記接続線と接続されたことを特徴とする液晶表示装置。 A thin film transistor formed corresponding to each intersection of a plurality of gate lines and a plurality of source lines;

A pixel electrode connected to the thin film transistor;

A counter electrode formed facing the pixel electrode and connected to a common signal line;

A connection line for commonly connecting a plurality of the common signal lines;

A gate terminal for applying a voltage to the gate wiring;

An array substrate having a lead-out line outside the display region connecting the gate line and the gate terminal;

A counter substrate facing the array substrate,

A conductive layer formed by extending the connection line to the gate terminal side through an insulating film is disposed on the lead wiring,

The conductive layer is formed of a light-transmitting conductive film,

A liquid crystal display device connected to the connection line via a contact hole provided on the connection line .

前記薄膜トランジスタに接続された画素電極、

前記画素電極に対向して形成され、共通信号線に接続された対向電極、

複数の前記共通信号線を変換部によって共通に接続する接続線、

前記ゲート配線に電圧を印加するためのゲート端子、

前記ゲート配線と前記ゲート端子とを接続する表示領域外にある引き出し配線

を有するアレイ基板と、

前記アレイ基板に対向する対向基板とを備え、

前記引き出し線の上層に、絶縁膜を介して前記変換部と同一層で形成した導電層を配設し、

前記導電層は、透光性を有する導電膜で形成されると共に、

前記変換部は、前記接続線上に設けられたコンタクトホールを介して前記接続線と接続されたことを特徴とする液晶表示装置。 A thin film transistor formed corresponding to each intersection of a plurality of gate lines and a plurality of source lines;

A pixel electrode connected to the thin film transistor;

A counter electrode formed facing the pixel electrode and connected to a common signal line;

A plurality of common signal lines connected in common by the converter,

A gate terminal for applying a voltage to the gate wiring;

An array substrate having a lead-out line outside the display region connecting the gate line and the gate terminal;

A counter substrate facing the array substrate,

A conductive layer formed in the same layer as the conversion part via an insulating film is disposed on the lead line,

The conductive layer is formed of a light-transmitting conductive film,

The liquid crystal display device , wherein the conversion unit is connected to the connection line through a contact hole provided on the connection line .

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007194436A JP4116067B2 (en) | 2007-07-26 | 2007-07-26 | Liquid crystal display |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007194436A JP4116067B2 (en) | 2007-07-26 | 2007-07-26 | Liquid crystal display |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004089053A Division JP4011557B2 (en) | 2004-03-25 | 2004-03-25 | Liquid crystal display device and method of manufacturing liquid crystal display device |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008025316A Division JP4829260B2 (en) | 2008-02-05 | 2008-02-05 | Liquid crystal display |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007272255A JP2007272255A (en) | 2007-10-18 |

| JP2007272255A5 JP2007272255A5 (en) | 2008-04-03 |

| JP4116067B2 true JP4116067B2 (en) | 2008-07-09 |

Family

ID=38675045

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007194436A Expired - Lifetime JP4116067B2 (en) | 2007-07-26 | 2007-07-26 | Liquid crystal display |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4116067B2 (en) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5429776B2 (en) * | 2008-12-10 | 2014-02-26 | 株式会社ジャパンディスプレイ | LCD panel |

| JP2012155090A (en) * | 2011-01-25 | 2012-08-16 | Seiko Instruments Inc | Display device |

| JP5901007B2 (en) | 2011-09-12 | 2016-04-06 | 株式会社ジャパンディスプレイ | Display device |

| JP5681269B2 (en) * | 2013-11-27 | 2015-03-04 | 株式会社ジャパンディスプレイ | LCD panel |

-

2007

- 2007-07-26 JP JP2007194436A patent/JP4116067B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007272255A (en) | 2007-10-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5456980B2 (en) | Liquid crystal display device and manufacturing method thereof | |

| CN101539701B (en) | Liquid crystal display device | |

| JP6747068B2 (en) | Liquid crystal display panel and liquid crystal display device including the liquid crystal display panel | |

| JP4385993B2 (en) | Liquid crystal display device and manufacturing method thereof | |

| JP5907697B2 (en) | Wiring structure, thin film transistor array substrate including the same, and display device | |

| KR20130054780A (en) | Array substrate for fringe field switching mode liquid crystal display device and method for fabricating the same | |

| CN103091915B (en) | Wiring structure, the thin-film transistor array base-plate comprising it and display device | |

| CN103309101B (en) | Wiring structure and possess its thin-film transistor array base-plate and display device | |

| US7751012B2 (en) | Array substrate for in-plane switching mode liquid crystal display device and method of fabricating the same | |

| CN108508661B (en) | Liquid crystal display panel and liquid crystal display device | |

| JP4011557B2 (en) | Liquid crystal display device and method of manufacturing liquid crystal display device | |

| JP5117893B2 (en) | Liquid crystal display device and manufacturing method thereof | |

| JP4116067B2 (en) | Liquid crystal display | |

| JP5090133B2 (en) | Liquid crystal display | |

| JP2015145907A (en) | Manufacturing method of display device | |

| JP4829260B2 (en) | Liquid crystal display | |

| JP4593161B2 (en) | Liquid crystal display | |

| JP3367821B2 (en) | Active matrix substrate | |

| JP5560227B2 (en) | Method for manufacturing liquid crystal display device and liquid crystal display device | |

| JP5286438B2 (en) | Liquid crystal display | |

| KR101147267B1 (en) | Thin Film Transistor Substrate of Horizontal Electronic Fileld and Method of Fabricating the same | |

| KR20150024992A (en) | Display substrate and method of manufacturing the same | |

| JP2018146923A (en) | Liquid crystal display | |

| KR20080061826A (en) | Array substrate for liquid crystal display device and manufacturing method thereof | |

| KR20170049725A (en) | Thin film transistor and method of the same, and display divice having the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070726 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080219 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20080219 |

|

| TRDD | Decision of grant or rejection written | ||

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20080404 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080415 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080416 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4116067 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130425 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130425 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140425 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |