JP4114915B2 - Data processing apparatus and data processing system - Google Patents

Data processing apparatus and data processing system Download PDFInfo

- Publication number

- JP4114915B2 JP4114915B2 JP2002150389A JP2002150389A JP4114915B2 JP 4114915 B2 JP4114915 B2 JP 4114915B2 JP 2002150389 A JP2002150389 A JP 2002150389A JP 2002150389 A JP2002150389 A JP 2002150389A JP 4114915 B2 JP4114915 B2 JP 4114915B2

- Authority

- JP

- Japan

- Prior art keywords

- external

- access

- memory

- bus

- data processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Memory System Of A Hierarchy Structure (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、キャッシュメモリを有するデータ処理装置におけるキャッシュコヒーレンシに関し、例えば外部バスマスタがデータプロセッサのローカルメモリをアクセス可能なとき、外部バスマスタによるローカルメモリアクセス時のキャッシュコヒーレンシの維持に適用して有効な技術に関する。

【0002】

【従来の技術】

データプロセッサのローカルバスに接続されたローカルメモリをローカルバスとは別のバスに接続された外部バスマスタにアクセス可能にする技術について記載された文献として、特開2000−282704、特開2001−306486の公報がある。前者には、CPUの外部バスとして汎用バスとSDRAMバスとがあり、その汎用バスに接続されるバスマスタがCPU内に設けられている透過制御部を介してSDRAMをアクセスできるデータ処理システムについて記載される。後者には、CPUチップに外部システムバスを介してバスマスタが、また、専用インタフェースを介してRDRAM(SDRAM)が接続されるシステムにおいて、バスマスタがCPUチップ内を介してRDRAM(SDRAM)をアクセスできるようにした制御方式が記載される。

【0003】

【発明が解決しようとする課題】

データプロセッサがキャッシュメモリを内蔵するとき、外部バスマスタとデータプロセッサがキャッシュ対象領域(キャッシャブルエリア)を共有するとき、前記ローカルメモリとキャッシュメモリのコヒーレンシを取る必要がある。このコヒーレンシ維持のためには、例えば、外部バスマスタが上記キャッシャブルエリアをアクセスするとき、アクセス前にデータプロセッサに割り込みを入れ、その割込みハンドラでデータプロセッサのキャッシュメモリをパージし、パージ完了後、該エリアをアクセスする。しかしながら、外部バスマスタがデータプロセッサに割り込みを入れ、そのハンドラでキャッシュメモリをパージする操作を介在させると、性能低下を招く虞がある。特に、外部バスマスタによるデータ転送量が小さい場合、実際の転送より、上記割込みハンドラによるコヒーレンシ実現用の前処理が長い時間を要することになり、オーバヘッドとして無視できない。

【0004】

また、キャッシュメモリそれ自体が能動的にバスアクセス状態を監視し、キャッシュコヒーレンシを維持するように能動的に動作するスヌープ方式のキャッシュ制御を採用することも可能であるが、この制御方式は、キャッシュメモリによる能動的な制御故に回路の物理的及び論理的な規模が増大し、コストの増大を招いてしまう。

【0005】

本発明の目的は、外部バスマスタとキャッシャブルエリアを共有可能なときにキャッシュコヒーレンシを維持する処理に移行するための前処理によるオーバーヘッドを低減することができるデータ処理装置、更にはデータ処理システムを提供することにある。

【0006】

本発明の別の目的は、外部バスマスタとキャッシャブルエリアを共有可能なときにキャッシュコヒーレンシの維持を行なうための物理的及び論理的な規模を小さくすることができるデータ処理装置、更にはデータ処理システムを提供することにある。

【0007】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【0008】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0009】

〔1〕本発明に係るデータ処理装置は、外部に第1バスと第2バスが別々に接続可能であって、前記第1バスに接続する外部バスマスタに前記第2バスに接続する外部メモリのアクセスを許容するバス権を与えることが可能なデータプロセッサであって、前記外部メモリをキャッシュ対象とすることが可能なキャッシュメモリを含む。このデータプロセッサは、外部バスマスタからのアクセス要求の条件が特定の条件を満たすとき、キャッシュメモリの状態をチェックし、外部バスマスタからのメモリアクセスアドレスに対してキャッシュメモリにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを保つ操作を行なって、前記外部バスマスタからのアクセス要求に応答する外部メモリアクセスを開始可能にする。

【0010】

上記した手段によれば、データ処理装置が外部バスマスタとキャッシャブルエリアを共有可能なときにキャッシュコヒーレンシを維持する処理に移行するための前処理では、外部バスマスタからのアクセス要求の条件が特定の条件を満たすか否かを判定すればよく、CPUへの割り込み処理に必要な状態保存などの前処理を要しない。外部バスマスタにデータプロセッサ内のバス権を与えることによってCPU動作との間の関係は整合する。また、キャッシュコヒーレンシを保つ操作はキャッシュメモリがバス状態を監視して能動的に行なうものではないから、従来のバススヌープ方式のキャッシュ制御を採用する場合に比べて、キャッシュコヒーレンシの維持を行なうための物理的及び論理的な規模を小さくすることが可能である。

【0011】

本発明の一つの具体的な態様として、データ処理装置は、前記特定の条件をプログラマブルに指定するための制御レジスタを有する。前記制御レジスタは、アクセスアドレスとの比較に用いられる特定のアドレスを指定するための第1記憶領域を有する。アクセスアドレスがキャッシャブルエリアであるか否かの判定に用いられる。

【0012】

前記制御レジスタは、アドレス比較のアドレスレンジを指定する第2記憶領域を有する。キャッシャブルエリアのサイズを任意に指定可能になる。

【0013】

前記制御レジスタは、アドレス比較結果の一致又は不一致の何れを特定の条件成立とするかを指定するための第3記憶領域を有する。第1記憶領域及び第2記憶領域を用いてキャッシャブルエリアを直接指定するときは、アドレス比較結果の一致を特定の条件成立とすればよい。第1記憶領域及び第2記憶領域を用いてノンキャッシャブルエリアを指定するときは、アドレス比較結果の不一致を特定の条件成立とすればよい。キャッシャブルエリアがノンキャッシャブルエリアに分断されている状態を指定するのに便利である。

【0014】

前記制御レジスタは、前記特定の条件が不成立であることを選択的に指定するための第4記憶領域を有してよい。要するに、キャッシュコヒーレンシを保つための一連の処理について選択/非選択が可能になる。

【0015】

前記キャッシュコヒーレンシを保つ操作は、例えば、外部バスマスタによるメモリアクセスアドレスに基づいたキャッシュのヒットしたブロックがダーティであってライトアクセスに応答するときは当該ブロックをライトバックし且つ無効化し、キャッシュのヒットするブロックがダーティであってリードアクセスに応答するときは当該ブロックをライトバックし且つクリーン化し、キャッシュのヒットするブロックがクリーンであってライトアクセスに応答するときはヒットブロックを無効化し、キャッシュにヒットするブロックがクリーンであってリードアクセスに応答するとき及びヒットするブロックが存在しない時は、何もしない操作である。

【0016】

〔2〕更に具体的な観点による本発明に係るデータ処理装置は、キャッシュメモリを内蔵するCPU、外部バスマスタを接続可能な外部インタフェース回路、外部メモリを接続可能なメモリインタフェース回路、及びそれらが共通接続される内部バスを有する。前記外部インタフェース回路は、外部バスマスタからの要求に応答してバス権を委譲することが可能であり、バス権を委譲したとき、外部バスマスタからの要求に応じて、前記内部バスから前記メモリインタフェース回路を介して外部メモリをアクセス可能とする。更に前記外部インタフェース回路は、前記メモリインタフェース回路を介して外部メモリをアクセスするときのアクセス条件が特定の条件を満たすとき、前記CPUに所定のキャッシュ制御コマンドを発行し、それに対する所定の応答を待って前記メモリインタフェース回路を介する外部メモリアクセスを開始可能する。前記CPUは、前記キャッシュ制御コマンドを受理したとき、キャッシュメモリの状態をチェックし、メモリアクセスアドレスに対してキャッシュメモリにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを保つ操作を行なって、前記所定の応答を前記外部インタフェース回路に返すことが可能である。

【0017】

この発明においても上記同様に、データ処理装置が外部バスマスタとキャッシャブルエリアを共有可能なときにキャッシュコヒーレンシを維持する処理に移行するには、CPUへの割り込み処理に必要な状態保存などの前処理を要せず、また、従来のバススヌープ方式のキャッシュ制御を採用する場合に比べて、キャッシュコヒーレンシの維持を行なうための物理的及び論理的な規模を小さくすることが可能である。

【0018】

前記外部インタフェース回路には、上記同様に、第1乃至第4記憶領域が割当てられた制御レジスタを設け、前記特定の条件をプログラマブルに指定可能にするのが望ましい。

【0019】

前記外部インタフェース回路は、外部にバス権を与えた状態で前記所定の応答を待っているとき、前記外部インタフェース回路の状態が所定の状態であることを条件に、前記外部に対してバス権の解放とリトライを要求する機能を有することが望ましい。前記所定の状態は、前記外部インタフェース回路が新たなアクセス要求を受付け不可能な状態である。例えば、CPUが外部インタフェース回路に外部リードアクセスを指示して、CPUがデータリードを待っているとき、外部バスマスタが外部インタフェース回路からバス権を獲得して外部メモリアクセス可能にされることがある。このとき、キャッシュコヒーレント維持のためにCPUがキャッシュメモリのライトバックを行なおうとしても、CPUは先に発行したリードアクセスに対するリードデータを待っているためにライトバックのための外部メモリアクセスを行なうことができずにデッドロックになってしまう可能性がある。前記外部インタフェース回路が新たなアクセス要求を受付け不可能な状態にあるとき、そのようなデッドロックを生ずる可能性があるので、前記バス権の解放とリトライの要求機能により、外部バスマスタにバス権を放棄させれば、先のリードアクセスが処理されてCPUは新たなアクセス要求を発行可能になる。この状態で外部バスマスタは、バス権放棄により中断若しくは中止した外部メモリアクセスをリトライすればよい。これにより、デッドロックの虞を未然に防止することができる。

【0020】

〔3〕本発明に係るデータ処理システムは、データプロセッサと、前記データプロセッサに接続されたローカルバスと、前記ローカルバスに接続された外部メモリと、前記データプロセッサに接続されたシステムバスと、前記システムバスに接続された外部バスマスタと、前記システムバスに接続されたその他の回路と、を有する。前記データプロセッサは、前記外部バスマスタに前記外部メモリのアクセスを許容するバス権を与えることが可能であって、前記外部メモリをキャッシュ対象とすることが可能なキャッシュメモリを含み、外部バスマスタからのアクセス要求の条件が特定の条件を満たすとき、前記キャッシュメモリの状態をチェックし、メモリアクセスアドレスに対してキャッシュメモリにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを保つ操作を行なって、前記外部バスマスタからのアクセス要求に応答する外部メモリアクセスを開始可能にする。

【0021】

前記外部バスマスタによる前記アクセス要求には、外部バスマスタが接続されるアドレス空間情報を含むとよい。これにより、データプロセッサは、バス幅やウェイトサイクル数等の外部バスマスタのアクセス能力に合わせて外部バスマスタとインタフェースを行なうことができる。

【0022】

前記データプロセッサには、上記同様に、第1乃至第4記憶領域が割当てられた制御レジスタを設け、前記特定の条件をプログラマブルに指定可能にするのが望ましい。更に、複数の外部バスマスタがシステムバスに接続される場合には、夫々の外部バスマスタに応じて前記制御レジスタを夫々有し、前記特定の条件をプログラマブルに指定可能にしても良い。

【0023】

【発明の実施の形態】

図1には本発明に係るデータ処理システムが例示される。同図に示されるデータ処理システムは、データプロセッサ1、前記データプロセッサ1に接続されたローカルバス2、前記ローカルバス2に接続された外部メモリ例えばダブルデータレートの大容量のSDRAM(Synchronous Dynamic Random Access Memory)3、前記データプロセッサ1に接続されたシステムバス4、前記システムバス4に接続された外部バスマスタ5、前記システムバス4に接続されたその他の回路例えばフラッシュメモリ(FLASH)6及びSRAM(Static Random Access Memory)7、そしてデータプロセッサ1に接続されたPCI(Peripheral Component Interconnect)バス8を備えて成る。前記ローカルバス2はSDRAM3に専用化され、例えばメモリモジュール向け小振幅高速インタフェースであるSSTL(Stub Series Terminated Transceiver Logic)2のバス仕様に準拠する。システムバス4はLVTTL(Low Voltage TTL)に準拠するバスであり、共有バスとして利用される。前記外部バスマスタ5はグラフィックコントローラ又はハードディスクコントローラなどのバスマスタモジュールを意味する。図示は省略するが、システムバス4には複数の外部バスマスタ及び複数のASICを接続することも可能である。

【0024】

前記データプロセッサ1は、キャッシュメモリ10を内蔵したCPU11、DMAC12(Direct Memory Access Controller)、PCIインタフェース回路13、SDRAMインタフェース回路14、外部バスインタフェース回路15、周辺ブリッジインタフェース回路16、デバッグインタフェース回路17、それらの回路ジュールを接続する内部バス(オンチップバス)18から成る。周辺ブリッジインタフェース回路16は、オンチップバス18と周辺バス20との間のブリッジを構成する。周辺バス20には適宜の内部周辺回路(IP)21が接続される。SDRAMインタフェース回路14はデータプロセッサ1のローカルメモリである前記SDRAM3がローカルバス2経由で接続される。外部バスインタフェース回路15は、前記システムバス4とオンチップバス18に接続される。

【0025】

前記SDRAM3はキャッシュメモリ10によるキャッシャブル領域を含む。外部バスインタフェース回路15は、オンチップバス18側のバスマスタモジュールであるCPU11からのバス権要求、DMAC12からのバス権要求、そしてシステムバス4側のバスマスタモジュールである外部バスマスタ5からのバス権要求を調停する。図1においてBREQは外部バスマスタ5から外部バスインタフェース回路15へのバス権要求信号、BACKは外部バスインタフェース回路15から外部バスマスタ5へのバス権承認信号である。

【0026】

CPU11又はDMAC12がバス権を獲得すれば、そのバス権を獲得したバスマスタモジュールが外部バスインタフェース回路15を介してシステムバス4の回路モジュールをアクセスすることができる。

【0027】

一方、システムバス4側の外部バスマスタ5がバス権を獲得したときは、外部バスマスタ5はシステムバス4の回路モジュールをアクセスすることができ、更に、外部バスインタフェース回路15を介してSDRAM3のアクセスが可能にされる。これは、図1のシステムではSSTL2の高速バス仕様を用いて高速大容量メモリであるSDRAM3をシステムバス4から切り離したローカルメモリとし、このSDRAM3をCPU11のワークメモリとして、更には外部バスバスマスタのテンポラリメモリ或はフレームバッファメモリとしても利用可能にするためである。外部バスマスタ5がSDRAM3をアクセスする場合の経路は、外部バスマスタ5、外部バスインタフェース回路15、オンチップバス18、SDRAMインタフェース回路14及びSDRAM3に通ずる経路となる。尚、システムバス側の外部バスマスタ5がバス権を獲得したときは、外部バスマスタ5はオンチップバス18上のその他の回路モジュールをアクセスすることも可能である。要するに外部バスマスタ5はローカルメモリ(SDRAM3)も含めてデータプロセッサ1をアクセスすることができる。

【0028】

図2にはデータプロセッサのオンチップバス18に接続された回路モジュールに割当てられる物理アドレスマップが例示される。4ギガバイト(GB)のアドレス空間に、夫々の回路モジュールがマッピングされる。例えば図中、FEMI_dbは前記外部バスインタフェース回路15をメモリマップドI/Oとみなしたとき当該回路15に割当てられるアドレス空間、EMI_DRAMはSDRAM3のアドレス空間である。

【0029】

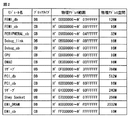

図3には外部バスインタフェース回路15に割当てられるアドレスマップが例示される。ここでは128メガバイト(MB)のアドレス空間がエリア0〜エリア4までの5個のエリアに分割される。図の例からも明らかなように、外部バスインタフェース回路15には外部バスマスタ5が複数個接続される場合もある。図示は省略するが、更にASICも複数接続することが可能である。

【0030】

外部バスマスタ5がシステムバス4上の回路モジュールをアクセスするときは、どの回路モジュールをアクセスするかを示すために対応する回路モジュールのモジュール選択信号(チップ選択信号)をアサートする。外部バスマスタ5がデータプロセッサ1をアクセスするときは、全てのモジュール選択信号をネゲートする。このとき外部バスマスタ5は、自分自身が図3のどのエリアに接続されているかを通知するためにアドレス空間情報26(図1参照)を外部バスインタフェース回路15に出力する。外部バスインタフェース回路15は、制御レジスタ27として、図3のエリア0〜4毎に図4のメモリ制御レジスタAnMCR(n=0〜4)を有し、外部バスマスタ5が通知するアドレス空間情報により制御レジスタAnMCR(n=0〜4)の中から一つを選択し、それによって外部バスインタフェース回路15は外部バスマスタ5との通信に必要なウェイトサイクル数などの制御情報を認識する。

【0031】

図4のメモリ制御レジスタAnMCR(n=0〜4)は、前述のようにエリア0〜エリア4の夫々に対応して存在し、各エリアに接続されるデバイスと外部インタフェース回路15との間のアクセスを規定するパラメータを指定する。外部バスマスタ5が外部インタフェース回路15をアクセスするとき、それがどのアドレスエリアに接続されているかは、前記アドレス空間情報26により通知される。 外部インタフェース回路15は通知されたエリアのメモリ制御レジスタAnMCR(n=0〜4)の内容に従って、外部バスマスタ5とハンドシェイクで情報のインタフェース制御を行なう。

【0032】

図5に外部バスマスタ5と外部インタフェース回路15との間のバスアービトレーションシーケンスが例示される。期間T1ではオンチップバス18側のCPU11などにより外部インタフェース回路15を介してシステムバス4がアクセスされている状態を示す。期間T2では外部バスマスタ5がバス権を取ってデータプロセッサ1をアクセスするときのシステムバス4の状態を示している。外部バスインタフェース回路15はバス権を取っていないためハイインピーダンス状態となり、システムバス4上ではバス権を取っている外部バスマスタ5よりアドレス等の情報が出力されている。期間T3はその後、再度オンチップバス18側のCPU11などにより外部インタフェース回路15を介してシステムバス4がアクセスされている状態を示す。尚、図5では前記信号BREQ,BACKを負論理信号として図示している。

【0033】

図6には外部バスマスタ5がローカルメモリをアクセスするときの処理フローが例示される。先ず、外部バスマスタ5が外部インタフェース回路15にバス権要求信号BREQをアサートしてオンチップバス18のバス権を要求する(ST1)。オンチップバス18側との競合が無ければバス権承認信号BACKがアサートされて外部バスマスタ5にバス権が与えられる(ST2)。これにより、外部バスマスタ5はデータプロセッサ1をアクセスする。続いて外部バスマスタ5が外部インタフェース回路15にアドレス、データ(ライト時)、コマンドを送る(ST3)。外部インタフェース回路15は、そのメモリアクセスアドレスがキャッシュコヒーレンシ(単にコヒーレンシとも称する)対象アドレスか否かを判定し(ST4)、コヒーレンシ対象アドレスであるという特定の条件を満たすとき、CPU11にコヒーレンシコマンドを送る。コヒーレンシコマンドを受取ったときCPU11の動作については詳細を後述するが、概略的には、前記キャッシュメモリ10の状態をチェックし、メモリアクセスアドレスに対してキャッシュにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを保つ操作を行なって、コヒーレンシコマンドに対する応答を外部インタフェース回路15に返す。外部インタフェース回路15はコヒーレンシコマンドに対する応答の受領を確認すると(ST6)、今度はSDRAMインタフェース回路14にアクセスコマンドを供給して、SDRAM3のアクセス動作を開始させる(ST7)。

【0034】

図7にはコヒーレンシコマンド受理後のCPU11によるコヒーレンシ処理フローが例示される。コヒーレンシコマンドを受理し(ST10)、キャッシュメモリ10をチェックし(ST11)、キャッシュヒットか否かを判定し(ST12)、キャッシュミスであれば当該コヒーレンシコマンドに対する応答を外部インタフェース回路15に返す(ST19)。キャッシュヒットであればダーティーブロックにヒットしたか否かを判定し(ST13)、次にライトアクセスに応答するアクセスであったか、換言すればライトアクセス時のコヒーレンシ維持かリードアクセス時のコヒーレンシ維持かを判別する(ST14,ST15)。ステップST12〜ST15の判定により、キャッシュのヒットするブロックがダーティであってライトアクセスに応答するアクセスのときはヒットするブロックをライトバックし且つ当該ブロックを無効化し(ST16)、キャッシュのヒットするブロックがダーティであってリードアクセスに応答するときはヒットするブロックをライトバックし且つ当該ブロックをクリーン化し(ST17)、キャッシュのヒットするブロックがクリーンであってライトアクセスに応答するときはヒットするブロックを無効化する操作を行なって(ST18)、当該コヒーレンシコマンドに対する応答を外部インタフェース回路15に返す(ST19)。

【0035】

コヒーレンシ対象アドレスという特定の条件をプログラマブルに指定する為の制御レジスタ28について説明する。外部インタフェース回路15は、その制御レジスタ28として、例えば図8に例示されるスヌープアドレスレジスタSNPARn(n=0,1)と、図9に例示されるスヌープ制御レジスタSNPCRn(n=0,1)を有する。

【0036】

図8にはスヌープアドレスレジスタSNPARn(n=0,1)の一例が示される。スヌープアドレスレジスタSNPARnのビット31〜0(CADR:第1記憶領域)には、CPU11により32ビットの物理アドレス(アクセスアドレスとの比較に用いられるアドレス情報)が任意に指定可能にされる。

【0037】

図9にはスヌープ制御レジスタSNPCRn(n=0,1)の一例が示される。ビット1〜0(SNPMD:第3記憶領域及び第4記憶領域)は、外部インタフェース回路15がコヒーレンシコマンドを発行する機能をイネーブルにするか否か、またコヒーレンシコマンドを発行する場合には、スヌープアドレスレジスタSNPARnのアドレスと、外部バスマスタ5のアクセスアドレスの比較結果が一致したとき発行するのか、不一致のとき発行するのかを指定する。ビット4〜2(RANGE:第2記憶領域)は、アドレス比較を行なうアドレス長を指定する。ビット7〜4は、スヌープアドレスレジスタSNPARn及びスヌープ制御レジスタSNPCRnをどのエリアに接続された外部バスマスタからのアクセスに用いるかを指定する。この例では、スヌープアドレスレジスタSNPARn及びスヌープ制御レジスタSNPCRnがともに2本実装されており、外部バスマスタ5が最大2つのエリアに接続された場合までをサポートすることができる。また複数の外部バスマスタが接続される場合には夫々に対応した前記スヌープアドレスレジスタSNPARn及びスヌープ制御レジスタSNPCRnを外部バスインタフェース15内に持たせることにより任意に制御することが可能となる。

【0038】

前記スヌープアドレスレジスタSNPARnの第1記憶領域と前記スヌープ制御レジスタSNPCRnの第2記憶領域を用いて図10のキャッシャブルエリアCE1を直接指定するときは、アドレス比較結果の一致をコヒーレンシコマンド発行の条件成立とすればよい。前記スヌープアドレスレジスタSNPARnの第1記憶領域と前記スヌープ制御レジスタSNPCRnの第2記憶領域を用いて図10のノンキャッシャブルエリアNCE2を指定するときは、アドレス比較結果の不一致をコヒーレンシコマンド発行の条件成立とすればよい。この設定はキャッシャブルエリアCE2がノンキャッシャブルエリアNCE2に分断されている状態を指定するのに便利である。

【0039】

次に、外部インタフェース回路15の内蔵バッファのフル状態によるデッドロック条件とその解消方法について図6を参照しながら説明する。

【0040】

前記外部インタフェース回路15は、外部バスマスタ5にバス権を与えた状態で前記キャッシュコヒーレンシコマンドに対するCPU11からの応答を待っているとき(図6のST6)、前記外部インタフェース回路15の状態が所定の状態、例えば前記外部インタフェース回路15のリクエスト受付バッファ(図1の30)がフル状態で新たなアクセス要求を受付け不可能な状態、であることを条件に(図6のST8)、前記外部インタフェース回路15は前記外部バスマスタに対してバス権の解放とリトライを要求する機能を有する(図6のST9)。例えば、CPU11が外部インタフェース回路15に外部接続されたSRAM7などに対する外部リードアクセスを指示して、CPU11がデータリードを待っているとき、外部バスマスタ5が外部インタフェース回路15からバス権を獲得してSDRAM3をアクセス可能にされることがある。このとき、キャッシュコヒーレントコマンドが発行されて例えばCPU11がキャッシュメモリ10のライトバックを行なおうとしても、CPU15は先に発行したリードアクセスに対するリードデータを待っているためにライトバックのための外部メモリアクセスを行なうことができずにデッドロックになってしまう可能性がある。そこで前記外部インタフェース回路15が新たなアクセス要求を受付け不可能な状態にあるとき、そのようなデッドロックを生ずる可能性があるので、前記バス権の解放とリトライを要求機能により外部バスマスタ5にバス権を放棄させれば、先のリードアクセスが処理されてCPU11は新たなアクセス要求を発行可能になる。この状態で外部バスマスタ5は、バス権放棄により中断若しくは中止したSDRAM3のアクセスをリトライすればよい。これにより、デッドロックの虞を未然に防止することができる。

【0041】

以上説明したデータプロセッサ1及びこれを適用したデータ処理システムによれば以下の作用効果を得る。

【0042】

外部バスマスタ5がデータプロセッサ1のキャッシャブルローカルメモリとしてのSDRAM3をアクセスするとき、キャッシュメモリ10のキャッシュコヒーレンシを維持させる処理を行うのにデータプロセッサ1への割り込み処理が不要になり、その処理のオーバーヘッドを低減でき、そのメモリアクセスを高速化することができる。外部バスマスタ5のデータ転送処理とデータプロセッサ1の演算処理を並列に実行できるようになり、データ処理性能も向上させることが可能になる。これに対し、そのようなキャッシュコヒーレンシを維持させるのにデータプロセッサへの割り込み処理を介在させる場合には、その割り込みハンドラ実行中に、データプロセッサは他の処理を実行できず、また割り込み処理のオーバーヘッド(割り込み開始、レジスタ待避、回復など)にプロセッサマシンサイクルで50〜100サイクル程度必要になる。本発明の場合にはオーバーヘッドはプロセッササイクルで10サイクル程度であり、データ転送とプロセッサ処理の並列実行も可能である。

【0043】

更に、外部バスマスタ5のドライバソフトを簡略化でき、その開発工数も低減可能になる。外部バスマスタ5のドライバから、コヒーレンシ用の割り込みハンドラを除くことができるからである。

【0044】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0045】

例えば、外部バスマスタがリードアクセスする時のコヒーレンシチェックに伴うキャッシュ操作を下記のようにすることも可能である。即ち、キャッシュメモリのリードヒットするブロックがダーティであるとき、ヒットするブロックをライトバックすると共にクリーン化し、更にそのデータを外部インタフェース回路15に直接供給する。キャッシュメモリのリードヒットするブロックがクリーンなとき、ヒットするブロックのデータを外部インタフェース回路15に供給する。このように、キャッシュメモリのリードヒット時には、外部バスマスタ5が所望とするデータはCPU11のキャッシュメモリ10内に存在しているから、そのデータをCPU11から直接外部インタフェース回路15に転送することにより、前述したところの外部インタフェース回路15がコヒーレンシコマンドの完了通知を受理した後にSDRAMインタフェース回路14を改めてアクセスする場合に比べて、高速アクセスが可能になる。

【0046】

また、データプロセッサのオンチップ回路モジュールは前記説明に限定されず適宜変更可能である。ローカルメモリとしての外部メモリはダブルデータレートのSDRAMに限定されず、シングルデータレート、或はその他記憶形式のメモリであってもよい。また、システムバスとローカルバスの仕様はLVTTLとSSTL2に限定されず適宜変更可能である。また、本発明は複数のキャッシュ内蔵のプロセッサで構成される、マルチプロセッサシステムにも適用可能である。

【0047】

【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0048】

外部バスマスタがデータ処理装置のキャッシャブルメモリをアクセスするとき、キャッシュメモリのキャッシュコヒーレンシを維持させるのにデータ処理装置への割り込み処理が不要になり、キャッシュコヒーレンシを維持させる処理のオーバーヘッドが小さくなり、そのアクセスを高速化することができる。外部バスマスタのデータ転送処理とデータ処理装置の演算処理を並列に実行できるようになり、データ処理性能も向上させることが可能になる。更に、外部バスマスタのドライバソフトを簡略化でき、その開発工数も低減可能になる。

【図面の簡単な説明】

【図1】本発明に係るデータ処理システムを例示するブロック図である。

【図2】データプロセッサのオンチップバスに接続された回路モジュールに割当てられるも物理アドレスマップを例示する説明図である。

【図3】外部バスインタフェース回路に割当てられるアドレスマップを例示する説明図である。

【図4】メモリ制御レジスタAnMCRの説明図である。

【図5】外部バスマスタと外部インタフェース回路との間のバスアービトレーションシーケンスを例示するタイミングチャートである。

【図6】外部バスマスタがローカルメモリをアクセスするときの処理を例示するフローチャートである。

【図7】コヒーレンシコマンド受理後のCPUによるコヒーレンシ処理を例示するフローチャートである。

【図8】スヌープアドレスレジスタSNPARnの一例が示す説明図である。

【図9】スヌープ制御レジスタSNPCRnの一例が示す説明図である。

【図10】スヌープアドレスレジスタの第1記憶領域と前記スヌープ制御レジスタの第2記憶領域を用いてキャッシャブルエリアを直接指定した状態とノンキャッシャブルエリアを指定した状態とを対比した説明図である。

【符号の説明】

1 データプロセッサ

2 ローカルバス

3 SDRAM

4 システムバス

5 外部バスマスタ

10 キャッシュメモリ

11 CPU

15 外部インタフェース回路

27,28 制御レジスタ

AnMCR メモリ制御レジスタ

SNPARn スヌープアドレスレジスタ

SNPCRn スヌープコントロールレジスタ

CADR 第1領域

SNPMD 第3記憶領域及び第4記憶領域

RANGE 第2領域[0001]

BACKGROUND OF THE INVENTION

The present invention relates to cache coherency in a data processing apparatus having a cache memory. For example, when an external bus master can access a local memory of a data processor, the present invention is effective when applied to maintenance of cache coherency when an external bus master accesses a local memory. About.

[0002]

[Prior art]

Japanese Patent Laid-Open No. 2000-282704 and Japanese Patent Laid-Open No. 2001-306486 are documents that describe a technique for making a local memory connected to a local bus of a data processor accessible to an external bus master connected to a bus different from the local bus. There is a publication. The former describes a data processing system in which a general-purpose bus and an SDRAM bus are provided as external buses for a CPU, and a bus master connected to the general-purpose bus can access the SDRAM via a transparent control unit provided in the CPU. The In the latter, in a system in which a bus master is connected to the CPU chip via an external system bus and an RDRAM (SDRAM) is connected via a dedicated interface, the bus master can access the RDRAM (SDRAM) via the CPU chip. The control method is described.

[0003]

[Problems to be solved by the invention]

When the data processor incorporates the cache memory, when the external bus master and the data processor share the cache target area (cacheable area), it is necessary to take coherency between the local memory and the cache memory. In order to maintain this coherency, for example, when an external bus master accesses the cacheable area, an interrupt is input to the data processor before the access, and the cache memory of the data processor is purged by the interrupt handler. Access the area. However, if an external bus master interrupts the data processor and the handler purges the cache memory, the performance may be degraded. In particular, when the amount of data transferred by the external bus master is small, preprocessing for realizing coherency by the interrupt handler takes longer than actual transfer, and cannot be ignored as overhead.

[0004]

In addition, the cache memory itself can actively monitor the bus access state, and can adopt a snoop cache control that operates actively so as to maintain cache coherency. The active control by the memory increases the physical and logical scale of the circuit, resulting in an increase in cost.

[0005]

An object of the present invention is to provide a data processing apparatus and further a data processing system capable of reducing overhead due to preprocessing for shifting to processing for maintaining cache coherency when a cacheable area can be shared with an external bus master. There is to do.

[0006]

Another object of the present invention is to provide a data processing apparatus and a data processing system capable of reducing the physical and logical scale for maintaining cache coherency when a cacheable area can be shared with an external bus master. Is to provide.

[0007]

The above and other objects and novel features of the present invention will be apparent from the description of this specification and the accompanying drawings.

[0008]

[Means for Solving the Problems]

The following is a brief description of an outline of typical inventions disclosed in the present application.

[0009]

[1] In the data processing device according to the present invention, the first bus and the second bus can be connected to the outside separately, and the external bus master connected to the first bus is connected to the second bus. A data processor capable of giving a bus right allowing access, and includes a cache memory capable of caching the external memory. This data processor checks the state of the cache memory when the condition of the access request from the external bus master satisfies a specific condition, and if there is a block that hits the cache memory for the memory access address from the external bus master, An operation for maintaining cache coherency with the data of the access address is performed, and external memory access in response to an access request from the external bus master can be started.

[0010]

According to the above-described means, in the preprocessing for shifting to the processing for maintaining the cache coherency when the data processing apparatus can share the cacheable area with the external bus master, the condition of the access request from the external bus master is a specific condition. What is necessary is just to determine whether it satisfy | fills, and preprocessing, such as a state preservation | save required for interruption processing to CPU, is not required. The relationship between CPU operations is matched by giving the external bus master the bus rights in the data processor. Further, since the cache memory does not actively perform the operation for maintaining the cache coherency by monitoring the bus state, the cache coherency is maintained as compared with the case where the conventional bus snoop cache control is employed. It is possible to reduce the physical and logical scale.

[0011]

As one specific aspect of the present invention, the data processing apparatus includes a control register for programmably specifying the specific condition. The control register has a first storage area for designating a specific address used for comparison with an access address. This is used to determine whether the access address is a cacheable area.

[0012]

The control register has a second storage area for designating an address range for address comparison. The size of the cacheable area can be specified arbitrarily.

[0013]

The control register includes a third storage area for designating whether a specific condition is satisfied when the address comparison result matches or does not match. When the cacheable area is directly specified using the first storage area and the second storage area, it is only necessary that the address comparison result coincides with a specific condition. When a non-cacheable area is designated using the first storage area and the second storage area, a mismatch between address comparison results may be satisfied as a specific condition. This is useful for specifying a state in which the cacheable area is divided into non-cacheable areas.

[0014]

The control register may have a fourth storage area for selectively designating that the specific condition is not satisfied. In short, it is possible to select / deselect a series of processes for maintaining cache coherency.

[0015]

For example, when the cache hit block in the cache based on the memory access address by the external bus master is dirty and responds to the write access, the cache coherency maintaining operation writes back the block and invalidates the cache hit. When a block is dirty and responds to a read access, the block is written back and cleaned, and when the cache hit block is clean and responds to a write access, the hit block is invalidated and the cache is hit When the block is clean and responds to read access, and when there is no block to hit, nothing is done.

[0016]

[2] A data processing apparatus according to the present invention from a more specific viewpoint includes a CPU incorporating a cache memory, an external interface circuit to which an external bus master can be connected, a memory interface circuit to which an external memory can be connected, and a common connection therebetween Having an internal bus. The external interface circuit can delegate the bus right in response to a request from the external bus master, and when the bus right is delegated, the memory interface circuit from the internal bus in response to a request from the external bus master The external memory can be accessed via Furthermore, the external interface circuit issues a predetermined cache control command to the CPU and waits for a predetermined response to the CPU when an access condition when accessing the external memory through the memory interface circuit satisfies a specific condition. Thus, external memory access via the memory interface circuit can be started. When the CPU receives the cache control command, the CPU checks the state of the cache memory, and if there is a block hitting the cache memory with respect to the memory access address, maintains the cache coherency with the data at the memory access address. It is possible to perform an operation and return the predetermined response to the external interface circuit.

[0017]

Also in the present invention, as described above, in order to shift to processing for maintaining cache coherency when the data processing apparatus can share a cacheable area with an external bus master, preprocessing such as state saving necessary for interrupt processing to the CPU is performed. In addition, the physical and logical scales for maintaining cache coherency can be reduced as compared with the case where the conventional bus snoop cache control is employed.

[0018]

Similarly to the above, the external interface circuit is preferably provided with a control register to which the first to fourth storage areas are allocated so that the specific condition can be specified in a programmable manner.

[0019]

When the external interface circuit is waiting for the predetermined response in a state in which the bus right is given to the outside, the external interface circuit has the bus right to the outside on condition that the state of the external interface circuit is the predetermined state. It is desirable to have a function that requests release and retry. The predetermined state is a state in which the external interface circuit cannot accept a new access request. For example, when the CPU instructs the external interface circuit to perform external read access and the CPU is waiting for data read, the external bus master may acquire the bus right from the external interface circuit and be able to access the external memory. At this time, even if the CPU attempts to write back the cache memory in order to maintain cache coherency, the CPU waits for read data for the previously issued read access, and therefore performs external memory access for write back. You couldn't do it and you could end up deadlocking. When the external interface circuit is in a state where it cannot accept a new access request, such a deadlock may occur. Therefore, the bus right is granted to the external bus master by the function of releasing the bus right and retrying. If abandoned, the previous read access is processed and the CPU can issue a new access request. In this state, the external bus master may retry the external memory access suspended or canceled due to the bus right abandonment. Thereby, the possibility of deadlock can be prevented in advance.

[0020]

[3] A data processing system according to the present invention includes a data processor, a local bus connected to the data processor, an external memory connected to the local bus, a system bus connected to the data processor, An external bus master connected to the system bus; and other circuits connected to the system bus. The data processor includes a cache memory that can give the external bus master a bus right that allows access to the external memory and that can cache the external memory, and access from the external bus master When the request condition satisfies a specific condition, an operation of checking the state of the cache memory and maintaining cache coherency with the data at the memory access address if there is a block hitting the cache memory with respect to the memory access address The external memory access in response to the access request from the external bus master can be started.

[0021]

The access request by the external bus master may include address space information to which the external bus master is connected. Thus, the data processor can interface with the external bus master in accordance with the access capability of the external bus master such as the bus width and the number of wait cycles.

[0022]

As described above, the data processor is preferably provided with a control register to which the first to fourth storage areas are allocated, so that the specific condition can be specified in a programmable manner. Further, when a plurality of external bus masters are connected to the system bus, the control registers may be provided according to the respective external bus masters so that the specific conditions can be specified in a programmable manner.

[0023]

DETAILED DESCRIPTION OF THE INVENTION

FIG. 1 illustrates a data processing system according to the present invention. The data processing system shown in FIG. 1 includes a

[0024]

The

[0025]

The

[0026]

If the

[0027]

On the other hand, when the

[0028]

FIG. 2 illustrates a physical address map assigned to a circuit module connected to the on-chip bus 18 of the data processor. Each circuit module is mapped to a 4-gigabyte (GB) address space. For example, in the figure, FEMI_db is an address space allocated to the external bus interface circuit 15 when the external bus interface circuit 15 is regarded as a memory mapped I / O, and EMI_DRAM is an address space of the

[0029]

FIG. 3 illustrates an address map assigned to the external bus interface circuit 15. Here, a 128 megabyte (MB) address space is divided into five areas from

[0030]

When the

[0031]

The memory control register AnMCR (n = 0 to 4) in FIG. 4 exists corresponding to each of the

[0032]

FIG. 5 illustrates a bus arbitration sequence between the

[0033]

FIG. 6 illustrates a processing flow when the

[0034]

FIG. 7 illustrates a coherency processing flow by the

[0035]

The control register 28 for programmably specifying a specific condition called a coherency target address will be described. As the

[0036]

FIG. 8 shows an example of the snoop address register SNPARn (n = 0, 1). In

[0037]

FIG. 9 shows an example of the snoop control register SNPCRn (n = 0, 1).

[0038]

When directly specifying the cacheable area CE1 of FIG. 10 using the first storage area of the snoop address register SNPARn and the second storage area of the snoop control register SNPCRn, a condition for issuing a coherency command is satisfied when the address comparison result matches. And it is sufficient. When the non-cacheable area NCE2 of FIG. 10 is designated using the first storage area of the snoop address register SNPARn and the second storage area of the snoop control register SNPCRn, the condition for issuing the coherency command is satisfied when the address comparison result does not match. And it is sufficient. This setting is convenient for designating a state where the cacheable area CE2 is divided into the non-cacheable area NCE2.

[0039]

Next, a deadlock condition caused by the full state of the internal buffer of the external interface circuit 15 and a method for solving it will be described with reference to FIG.

[0040]

When the external interface circuit 15 waits for a response from the

[0041]

According to the

[0042]

When the

[0043]

Furthermore, the driver software for the

[0044]

Although the invention made by the present inventor has been specifically described based on the embodiments, it is needless to say that the present invention is not limited thereto and can be variously modified without departing from the gist thereof.

[0045]

For example, the cache operation associated with the coherency check when the external bus master performs read access can be performed as follows. That is, when the block in which the read hit of the cache memory is dirty, the hit block is written back and cleaned, and the data is directly supplied to the external interface circuit 15. When the read hit block of the cache memory is clean, the data of the hit block is supplied to the external interface circuit 15. As described above, since the data desired by the

[0046]

The on-chip circuit module of the data processor is not limited to the above description, and can be changed as appropriate. The external memory as the local memory is not limited to the double data rate SDRAM, but may be a single data rate or other storage type memory. The specifications of the system bus and the local bus are not limited to LVTTL and SSTL2, and can be changed as appropriate. The present invention can also be applied to a multiprocessor system composed of a plurality of cache built-in processors.

[0047]

【The invention's effect】

The effects obtained by the representative ones of the inventions disclosed in the present application will be briefly described as follows.

[0048]

When the external bus master accesses the cacheable memory of the data processing device, interrupt processing to the data processing device is not required to maintain cache coherency of the cache memory, and processing overhead for maintaining cache coherency is reduced. Access can be speeded up. The data transfer processing of the external bus master and the arithmetic processing of the data processing device can be executed in parallel, and the data processing performance can be improved. Furthermore, the driver software for the external bus master can be simplified and the development man-hours can be reduced.

[Brief description of the drawings]

FIG. 1 is a block diagram illustrating a data processing system according to the present invention.

FIG. 2 is an explanatory diagram exemplifying a physical address map assigned to a circuit module connected to an on-chip bus of a data processor;

FIG. 3 is an explanatory diagram illustrating an address map assigned to an external bus interface circuit;

FIG. 4 is an explanatory diagram of a memory control register AnMCR.

FIG. 5 is a timing chart illustrating a bus arbitration sequence between an external bus master and an external interface circuit.

FIG. 6 is a flowchart illustrating a process when an external bus master accesses a local memory.

FIG. 7 is a flowchart illustrating coherency processing by the CPU after receiving a coherency command.

FIG. 8 is an explanatory diagram illustrating an example of a snoop address register SNPARn.

FIG. 9 is an explanatory diagram illustrating an example of a snoop control register SNPCRn.

FIG. 10 is an explanatory diagram comparing a state in which a cacheable area is directly designated and a state in which a non-cacheable area is designated using the first storage area of the snoop address register and the second storage area of the snoop control register. .

[Explanation of symbols]

1 Data processor

2 Local bus

3 SDRAM

4 System bus

5 External bus master

10 Cache memory

11 CPU

15 External interface circuit

27, 28 Control register

AnMCR memory control register

SNPARn snoop address register

SNPCRn Snoop control register

CADR first area

SNPMD third storage area and fourth storage area

RANGE 2nd area

Claims (20)

前記外部バスマスタからのアクセス要求の条件が特定の条件を満たすとき、前記キャッシュメモリの状態をチェックし、メモリアクセスアドレスに対して前記キャッシュメモリにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを維持する処理を行なった後に、前記外部バスマスタからのアクセス要求に応答する外部メモリアクセスを開始可能にするものであり、

前記キャッシュコヒーレンシを維持する処理は、

前記ヒットしたブロックがダーティであるかを判定する第1処理と、

前記外部バスマスタからのアクセスがライトアクセスであるか、リードアクセスであるかを判別する第2処理と、

前記ヒットしたブロックがダーティで且つ、前記ライトアクセスであるときに、上記ヒットしたブロックに含まれるデータを前記外部メモリにライトバックし、且つ、前記キャッシュメモリのブロックを無効化する第3処理と、を含むことを特徴とするデータ処理装置。The first bus and the second bus can be separately connected to the outside, and a bus right allowing access to the external memory connected to the second bus can be given to the external bus master connected to the first bus A data processing device comprising a cache memory capable of caching the external memory;

When the condition of the access request from the external bus master satisfies a specific condition, the state of the cache memory is checked, and if there is a block hitting the cache memory with respect to the memory access address, the data of the memory access address After performing the process of maintaining cache coherency between them, it is possible to start external memory access in response to an access request from the external bus master ,

The process of maintaining the cache coherency is:

A first process for determining whether the hit block is dirty;

A second process for determining whether the access from the external bus master is a write access or a read access;

A third process for writing back data contained in the hit block to the external memory and invalidating the cache memory block when the hit block is dirty and the write access; data processing apparatus comprising a.

前記外部インタフェース回路は、外部バスマスタからの要求に応答してバス権を委譲することが可能であり、バス権を委譲したとき、外部バスマスタからの要求に応じて、前記内部バスから前記メモリインタフェース回路を介して外部メモリをアクセス可能とし、

前記メモリインタフェース回路を介して外部メモリをアクセスするときのアクセス条件が特定の条件を満たすとき、前記CPUに所定のキャッシュ制御コマンドを発行し、それに対する所定の応答を待って前記メモリインタフェース回路を介する外部メモリアクセスを開始可能とし、

前記CPUは、前記キャッシュ制御コマンドを受理したとき、キャッシュメモリの状態をチェックし、メモリアクセスアドレスに対してキャッシュヒットブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを維持する処理を行なって、前記所定の応答を前記外部インタフェース回路に返すことが可能であり、

前記キャッシュコヒーレンシを維持する処理は、

前記ヒットしたブロックがダーティであるかを判定する第1処理と、

前記外部バスマスタからのアクセスがライトアクセスであるか、リードアクセスであるかを判別する第2処理と、

前記ヒットしたブロックがダーティで且つ、前記ライトアクセスであるときに、上記ヒットしたブロックに含まれるデータを前記外部メモリにライトバックし、且つ、前記キャッシュメモリのブロックを無効化する第3処理と、を含むことを特徴とするデータ処理装置。A data processing device having a CPU incorporating a cache memory, an external interface circuit to which an external bus master can be connected, a memory interface circuit to which an external memory can be connected, and an internal bus to which they are commonly connected,

The external interface circuit can delegate the bus right in response to a request from the external bus master, and when the bus right is delegated, the memory interface circuit from the internal bus in response to a request from the external bus master The external memory can be accessed via

When an access condition for accessing the external memory through the memory interface circuit satisfies a specific condition, a predetermined cache control command is issued to the CPU, and a predetermined response is waited for the CPU to pass through the memory interface circuit. External memory access can be started,

When the CPU receives the cache control command, the CPU checks the state of the cache memory, and if there is a cache hit block for the memory access address, the CPU maintains cache coherency with the data at the memory access address. The predetermined response can be returned to the external interface circuit ,

The process of maintaining the cache coherency is:

A first process for determining whether the hit block is dirty;

A second process for determining whether the access from the external bus master is a write access or a read access;

A third process for writing back data contained in the hit block to the external memory and invalidating the cache memory block when the hit block is dirty and the write access; data processing apparatus comprising a.

前記データプロセッサは、前記外部バスマスタに前記外部メモリのアクセスを許容するバス権を与えることが可能であって、前記外部メモリをキャッシュ対象とすることが可能なキャッシュメモリを含み、外部バスマスタからのアクセス要求の条件が特定の条件を満たすとき、前記キャッシュメモリの状態をチェックし、メモリアクセスアドレスに対してキャッシュにヒットするブロックがあれば前記メモリアクセスアドレスのデータとの間のキャッシュコヒーレンシを維持する処理を行なって、前記外部バスマスタからのアクセス要求に応答する外部メモリアクセスを開始可能にするものであり、

前記キャッシュコヒーレンシを維持する処理は、

前記ヒットするブロックがダーティであるかを判定する第1処理と、

前記外部バスマスタからのアクセスがライトアクセスであるか、リードアクセスである かを判別する第2処理と、

前記ヒットするブロックがダーティで且つ、前記ライトアクセスであるときに、上記ヒットするブロックに含まれるデータを前記外部メモリにライトバックし、且つ、前記キャッシュメモリのブロックを無効化する第3処理と、を含むことを特徴とするデータ処理システム。A data processor, a local bus connected to the data processor, an external memory connected to the local bus, a system bus connected to the data processor, an external bus master connected to the system bus, and the system A data processing system having other circuits connected to the bus,

The data processor includes a cache memory that can give the external bus master a bus right that allows access to the external memory and that can cache the external memory, and access from the external bus master A process of checking the state of the cache memory when a request condition satisfies a specific condition, and maintaining cache coherency with data at the memory access address if there is a block hitting the cache for the memory access address To enable external memory access in response to an access request from the external bus master ,

The process of maintaining the cache coherency is:

A first process for determining whether the hit block is dirty;

A second process for determining whether the access from the external bus master is a write access or a read access ;

When the hit block is dirty and the write access, the third process of writing back the data contained in the hit block to the external memory and invalidating the cache memory block; data processing system which comprises a.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002150389A JP4114915B2 (en) | 2002-05-24 | 2002-05-24 | Data processing apparatus and data processing system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002150389A JP4114915B2 (en) | 2002-05-24 | 2002-05-24 | Data processing apparatus and data processing system |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003345653A JP2003345653A (en) | 2003-12-05 |

| JP2003345653A5 JP2003345653A5 (en) | 2005-09-29 |

| JP4114915B2 true JP4114915B2 (en) | 2008-07-09 |

Family

ID=29768259

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002150389A Expired - Fee Related JP4114915B2 (en) | 2002-05-24 | 2002-05-24 | Data processing apparatus and data processing system |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4114915B2 (en) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5056487B2 (en) * | 2008-03-06 | 2012-10-24 | 富士通株式会社 | Debugging support mechanism and processor system |

| TW201017421A (en) * | 2008-09-24 | 2010-05-01 | Panasonic Corp | Cache memory, memory system and control method therefor |

| CN104932989B (en) * | 2014-03-21 | 2020-05-19 | 三星电子株式会社 | Opportunistic cache injection of data into a low latency level of a cache hierarchy |

| US10216640B2 (en) * | 2014-03-21 | 2019-02-26 | Samsung Electronics Co., Ltd. | Opportunistic cache injection of data into lower latency levels of the cache hierarchy |

| CN114328311B (en) * | 2021-12-15 | 2024-09-06 | 珠海一微半导体股份有限公司 | Memory controller architecture, data processing circuit and data processing method |

-

2002

- 2002-05-24 JP JP2002150389A patent/JP4114915B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003345653A (en) | 2003-12-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5353415A (en) | Method and apparatus for concurrency of bus operations | |

| US6032231A (en) | Multiprocessor with split transaction bus architecture providing cache tag and address compare for sending retry direction to other bus module upon a match of subsequent address bus cycles to content of cache tag | |

| US5561779A (en) | Processor board having a second level writeback cache system and a third level writethrough cache system which stores exclusive state information for use in a multiprocessor computer system | |

| US6295582B1 (en) | System and method for managing data in an asynchronous I/O cache memory to maintain a predetermined amount of storage space that is readily available | |

| US6321296B1 (en) | SDRAM L3 cache using speculative loads with command aborts to lower latency | |

| US6571321B2 (en) | Read exclusive for fast, simple invalidate | |

| US5909699A (en) | Method and apparatus for supporting read, write, and invalidation operations to memory which maintain cache consistency | |

| US6681293B1 (en) | Method and cache-coherence system allowing purging of mid-level cache entries without purging lower-level cache entries | |

| US7991928B2 (en) | Retry mechanism | |

| US8037253B2 (en) | Method and apparatus for global ordering to insure latency independent coherence | |

| US5659709A (en) | Write-back and snoop write-back buffer to prevent deadlock and to enhance performance in an in-order protocol multiprocessing bus | |

| KR100371844B1 (en) | Queue-based predictive flow control mechanism | |

| WO1994008297A9 (en) | Method and apparatus for concurrency of bus operations | |

| US6751705B1 (en) | Cache line converter | |

| JPH05181745A (en) | Secondary-level cache controller | |

| CN101430664A (en) | Multiprocessor system and Cache consistency message transmission method | |

| US12056051B2 (en) | Tag update bus for updated coherence state | |

| US5918069A (en) | System for simultaneously writing back cached data via first bus and transferring cached data to second bus when read request is cached and dirty | |

| US5829027A (en) | Removable processor board having first, second and third level cache system for use in a multiprocessor computer system | |

| US5704058A (en) | Cache bus snoop protocol for optimized multiprocessor computer system | |

| JP3723700B2 (en) | Method and apparatus for transferring data over a processor interface bus | |

| US5987544A (en) | System interface protocol with optional module cache | |

| US6336169B1 (en) | Background kill system bus transaction to optimize coherency transactions on a multiprocessor system bus | |

| EP0681241A1 (en) | Processor board having a second level writeback cache system and a third level writethrough cache system which stores exclusive state information for use in a multiprocessor computer system | |

| JP4114915B2 (en) | Data processing apparatus and data processing system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20050315 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050425 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050425 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080317 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080408 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080414 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130425 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |