JP2012242585A - Display device, electronic apparatus, and driving method for display device - Google Patents

Display device, electronic apparatus, and driving method for display device Download PDFInfo

- Publication number

- JP2012242585A JP2012242585A JP2011112280A JP2011112280A JP2012242585A JP 2012242585 A JP2012242585 A JP 2012242585A JP 2011112280 A JP2011112280 A JP 2011112280A JP 2011112280 A JP2011112280 A JP 2011112280A JP 2012242585 A JP2012242585 A JP 2012242585A

- Authority

- JP

- Japan

- Prior art keywords

- drive

- pulse

- unit

- transistor

- display device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Abstract

Description

本明細書で開示する技術は、表示装置、電子機器、及び、表示装置の駆動方法に関する。 The technology disclosed in this specification relates to a display device, an electronic apparatus, and a method for driving the display device.

今日、表示素子(電気光学素子とも称される)を具備する画素回路(画素とも称される)を有する表示装置、表示装置を具備する電子機器が広く利用されている。画素の表示素子として、印加される電圧や流れる電流によって輝度が変化する電気光学素子を用いた表示装置がある。例えば、印加される電圧によって輝度が変化する電気光学素子としては液晶表示素子が代表例であり、流れる電流によって輝度が変化する電気光学素子としては、有機エレクトロルミネッセンス(Organic Electro Luminescence, 有機EL, Organic Light Emitting Diode, OLED;以下、有機ELと記す) 素子が代表例である。後者の有機EL素子を用いた有機EL表示装置は、画素の表示素子として、自発光素子である電気光学素子を用いたいわゆる自発光型の表示装置である。 Today, display devices including pixel circuits (also referred to as pixels) including display elements (also referred to as electro-optical elements) and electronic devices including the display devices are widely used. As a display element of a pixel, there is a display device using an electro-optical element whose luminance changes depending on an applied voltage or a flowing current. For example, a liquid crystal display element is a typical example of an electro-optical element whose luminance changes depending on an applied voltage, and an organic electroluminescence (Organic Electro Luminescence, Organic EL, Organic) (Light Emitting Diode, OLED; hereinafter referred to as “organic EL”) A typical example is an element. The organic EL display device using the latter organic EL element is a so-called self-luminous display device using an electro-optic element which is a self-luminous element as a pixel display element.

ところで、表示素子を用いた表示装置においては、その駆動方式として、単純(パッシブ)マトリクス方式とアクティブマトリクス方式とを採ることができる。但し、単純マトリクス方式の表示装置は、構造が単純であるものの、大型でかつ高精細の表示装置の実現が難しい等の問題がある。 By the way, in a display device using a display element, a simple (passive) matrix method and an active matrix method can be adopted as the driving method. However, although a simple matrix display device has a simple structure, there is a problem that it is difficult to realize a large and high-definition display device.

このため、近年、画素内部の表示素子に供給する画素信号を、同様に画素内部に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタ(一般には、薄膜トランジスタ(Thin Film Transistor ;TFT)等のトランジスタをスイッチングトランジスタとして使用して制御するアクティブマトリクス方式の開発が盛んに行なわれている。 For this reason, in recent years, a pixel signal supplied to a display element in a pixel has been changed to an active element similarly provided in the pixel, for example, an insulated gate field effect transistor (generally a transistor such as a thin film transistor (TFT)). Active matrix systems that are used and controlled as switching transistors have been actively developed.

従来のアクティブマトリクス方式の表示装置は、プロセス変動により表示素子を駆動するトランジスタの閾値電圧や移動度がばらついてしまう。又、表示素子の特性が経時的に変動する。このような駆動用のトランジスタの特性ばらつきや表示素子等の画素回路を構成する素子の特性変動は、発光輝度に影響を与えてしまう。即ち、各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性(ユニフォーミティ)が得られるはずであるが、駆動用のトランジスタの特性ばらつきや表示素子の特性変動により、画面のユニフォーミティが損なわれる。そこで、表示装置の画面全体に亘って発光輝度を均一に制御するため、各画素回路内でトランジスタや表示素子等の画素回路を構成する素子の特性ばらつき等に起因する表示むらを補正する技術が、例えば特許第4240059号公報や特許第4240068号公報に提案されている。 In a conventional active matrix display device, the threshold voltage and mobility of a transistor that drives a display element vary due to process variations. Further, the characteristics of the display element change with time. Such variations in the characteristics of the driving transistors and fluctuations in the characteristics of the elements constituting the pixel circuit, such as the display elements, affect the light emission luminance. In other words, if video signals of the same level are supplied to each pixel, all pixels should emit light with the same luminance and screen uniformity (uniformity) should be obtained. However, the characteristics of the driving transistors vary. Also, the uniformity of the screen is impaired due to the characteristic variation of the display element. Therefore, in order to uniformly control the light emission luminance over the entire screen of the display device, there is a technique for correcting display unevenness caused by characteristic variations of elements constituting a pixel circuit such as a transistor or a display element in each pixel circuit. For example, it is proposed in Japanese Patent No. 4240059 and Japanese Patent No. 4240068.

ここで、素子の特性むら(ばらつき及び経時変動の双方を含む)に起因する表示むらを改善する技術においては、各種の駆動パルスのタイミングによってトランジスタを制御して表示輝度を制御する。このため、駆動パルスの形状(幅、変化特性等)がばらつくと表示むらの原因となってしまう。 Here, in a technique for improving display unevenness due to element characteristic unevenness (including both variation and temporal variation), display luminance is controlled by controlling transistors according to timings of various drive pulses. For this reason, if the shape (width, change characteristics, etc.) of the drive pulse varies, it causes display unevenness.

したがって本開示の目的は、駆動パルスの形状(幅、変化特性等)がばらつくことに起因する表示むら現象を抑制することのできる技術を提供することにある。 Accordingly, an object of the present disclosure is to provide a technique capable of suppressing the display unevenness phenomenon caused by variations in the shape (width, change characteristics, etc.) of the drive pulse.

本開示の第1の態様に係る表示装置は、表示部と、保持容量と、映像信号と対応する駆動電圧を保持容量に書き込む書込トランジスタと、保持容量に書き込まれた駆動電圧に基づいて表示部を駆動する駆動トランジスタ、とを有する画素回路が所定の方向に配列されている画素部を備える。ここで、画素部には、所定の方向に配列されている各書込トランジスタと各駆動トランジスタの少なくとも一方を駆動するために駆動パルスを供給する駆動線が配されている。本開示の第1の態様に係る表示装置は、駆動線を選択する選択部と、駆動パルスの元になるパルス信号を生成するパルス生成部、とを更に備え、選択部は、パルス生成部で生成されたパルス信号に基づいて、複数の駆動線へ駆動パルスを供給する。本開示の第1の態様に係る表示装置の従属項に記載された各表示装置は、本開示の第1の態様に係る表示装置のさらなる有利な具体例を規定する。 The display device according to the first aspect of the present disclosure includes a display unit, a storage capacitor, a write transistor that writes a drive voltage corresponding to a video signal in the storage capacitor, and a display based on the drive voltage written in the storage capacitor. A pixel portion having a driving transistor for driving the portion and a pixel circuit arranged in a predetermined direction. Here, the pixel portion is provided with a drive line for supplying a drive pulse to drive at least one of the write transistors and the drive transistors arranged in a predetermined direction. The display device according to the first aspect of the present disclosure further includes a selection unit that selects a drive line and a pulse generation unit that generates a pulse signal that is a source of the drive pulse, and the selection unit is a pulse generation unit. Based on the generated pulse signal, a drive pulse is supplied to a plurality of drive lines. Each display device described in the dependent claims of the display device according to the first aspect of the present disclosure defines a further advantageous specific example of the display device according to the first aspect of the present disclosure.

本開示の第2の態様に係る電子機器は、表示部、保持容量、映像信号と対応する駆動電圧を保持容量に書き込む書込トランジスタ、及び、保持容量に書き込まれた駆動電圧に基づいて表示部を駆動する駆動トランジスタを具備した表示素子が配列された画素部と、画素部に供給される映像信号を生成する信号生成部、とを備える。ここで、画素部には、所定の方向に配列されている各書込トランジスタと各駆動トランジスタの少なくとも一方を駆動するために駆動パルスを供給する駆動線が配されている。本開示の第2の態様に係る電子機器は、駆動線を選択する選択部と、駆動パルスの元になるパルス信号を生成するパルス生成部、とを更に備え、選択部は、パルス生成部で生成されたパルス信号に基づいて、複数の駆動線へ駆動パルスを供給する。第2の態様に係る電子機器は、第1の態様に係る表示装置の従属項に記載された各技術・手法が同様に適用可能であり、それが適用された構成は、第2の態様に係る電子機器のさらなる有利な具体例を規定する。 An electronic apparatus according to a second aspect of the present disclosure includes a display unit, a storage capacitor, a write transistor that writes a drive voltage corresponding to a video signal to the storage capacitor, and a display unit based on the drive voltage written to the storage capacitor A pixel unit in which display elements each including a driving transistor for driving the pixel unit are arranged, and a signal generation unit that generates a video signal supplied to the pixel unit. Here, the pixel portion is provided with a drive line for supplying a drive pulse to drive at least one of the write transistors and the drive transistors arranged in a predetermined direction. The electronic device according to the second aspect of the present disclosure further includes a selection unit that selects a drive line and a pulse generation unit that generates a pulse signal that is a source of the drive pulse, and the selection unit is a pulse generation unit. Based on the generated pulse signal, a drive pulse is supplied to a plurality of drive lines. In the electronic device according to the second aspect, each technique and method described in the dependent claims of the display device according to the first aspect can be similarly applied, and the configuration to which the technique / method is applied is similar to the second aspect. Further advantageous specific examples of such electronic devices will be defined.

本開示の第3の態様に係る表示装置の駆動方法は、表示部、保持容量、映像信号と対応する駆動電圧を保持容量に書き込む書込トランジスタ、及び、保持容量に書き込まれた駆動電圧に基づいて表示部を駆動する駆動トランジスタを具備した画素回路が配列された画素部の各画素回路を駆動する方法であって、駆動パルスの元になるパルス信号を生成し、生成されたパルス信号に基づいて、複数の駆動線へ駆動パルスを供給する。第3の態様に係る表示装置の駆動方法は、第1の態様に係る表示装置の従属項に記載された各技術・手法が同様に適用可能であり、それが適用された構成は、第3の態様に係る表示装置の駆動方法のさらなる有利な具体例を規定する。 A display device driving method according to a third aspect of the present disclosure is based on a display unit, a storage capacitor, a writing transistor that writes a driving voltage corresponding to a video signal to the storage capacitor, and a driving voltage written in the storage capacitor. A method of driving each pixel circuit of a pixel portion in which a pixel circuit having a driving transistor for driving a display portion is arranged, generating a pulse signal that is a source of a driving pulse, and based on the generated pulse signal Then, a drive pulse is supplied to a plurality of drive lines. The technology and method described in the dependent claims of the display device according to the first aspect can be similarly applied to the driving method of the display device according to the third aspect. Further advantageous specific examples of the driving method of the display device according to the aspect will be defined.

要するに、本明細書で開示する技術では、駆動パルスの元になるパルス信号を駆動部とは別の箇所に設けられたパルス生成部で生成し、駆動部では、パルス生成部で生成されたパルス信号に基づいて、複数の駆動線へ駆動パルスを供給する。複数の駆動線に供給された駆動信号は同じパルス生成部で生成されたパルス信号に基づくので、各駆動パルスの間にはパルス形状(幅、変化特性等)のばらつきがないと云ってよく、駆動パルスの形状(幅、変化特性等)がばらつくことに起因する表示むら現象が抑制される。 In short, in the technology disclosed in this specification, a pulse signal that is a source of a drive pulse is generated by a pulse generation unit provided at a location different from the drive unit, and the drive unit generates a pulse generated by the pulse generation unit. Based on the signal, a drive pulse is supplied to a plurality of drive lines. Since drive signals supplied to a plurality of drive lines are based on pulse signals generated by the same pulse generation unit, it can be said that there is no variation in pulse shape (width, change characteristics, etc.) between the drive pulses. The display unevenness phenomenon due to the variation in the shape (width, change characteristics, etc.) of the drive pulse is suppressed.

第1の態様に係る表示装置、第2の態様に係る電子機器、第3の態様に係る表示装置の駆動方法によれば、駆動パルスの形状(幅、変化特性等)がばらつくことに起因する表示むら現象を抑制することができる。 According to the display device according to the first aspect, the electronic device according to the second aspect, and the driving method of the display device according to the third aspect, the shape (width, change characteristics, etc.) of the drive pulse varies. The display unevenness phenomenon can be suppressed.

以下、図面を参照して、本明細書で開示する技術の実施形態について詳細に説明する。各機能要素について形態別に区別する際にはアルファベット或いは“_n”(nは数字)或いはこれらの組合せの参照子を付して記載し、特に区別しないで説明する際にはこの参照子を割愛して記載する。図面においても同様である。 Hereinafter, embodiments of the technology disclosed in this specification will be described in detail with reference to the drawings. When distinguishing each functional element according to its form, an alphabet or “_n” (n is a number) or a combination of these is given as a reference, and this reference is omitted when it is not particularly distinguished. To be described. The same applies to the drawings.

説明は以下の順序で行なう。

1.全体概要

2.表示装置の概要

3.発光素子

4.駆動方法:基本

5.具体的な適用例:

駆動パルスの形状がばらつくことに起因する表示むら現象の対処

実施例1:同じパルス信号をスイッチ選択、走査線の最外部にパルス生成部

実施例2:同じパルス信号をスイッチ選択、走査線配列方向中間にパルス生成部

実施例3:パルス生成部で生成されたパルス信号を順次シフト

実施例4:電子機器への適用事例

The description will be made in the following order.

1.

Coping with display unevenness phenomenon due to variation in shape of drive pulse Example 1: Switch selection of same pulse signal, pulse generation unit at outermost part of scanning line Example 2: Switch selection of same pulse signal, direction of scanning line arrangement Pulse generator in the middle Example 3: Sequentially shifting the pulse signal generated in the pulse generator Example 4: Application example to electronic equipment

<全体概要>

本実施形態の構成において、表示装置、或いは、電子機器は、表示部と、保持容量と、映像信号と対応する駆動電圧を保持容量に書き込む書込トランジスタと、保持容量に書き込まれた駆動電圧に基づいて表示部を駆動する駆動トランジスタとを有する画素回路が所定の方向に配列されている画素部を備える。画素部には、所定の方向に配列されている各書込トランジスタと各駆動トランジスタの少なくとも一方を駆動するために駆動パルスを供給する駆動線(走査線)が配されており、この駆動線を選択する選択部を更に備える。又、表示装置、或いは、電子機器は、駆動パルスの元になるパルス信号を生成するパルス生成部を備えており、パルス生成部で生成されたパルス信号に基づいて選択部が複数の駆動線へ駆動パルスを供給する。駆動パルスの元になるパルス信号を駆動部とは別の箇所に設けられたパルス生成部で生成し、パルス生成部で生成されたパルス信号に基づいて駆動部が複数の駆動線へ駆動パルスを供給する。したがって、複数の駆動線に供給された駆動信号は同じパルス生成部で生成されたパルス信号に基づくので、各駆動パルスの間にはパルス形状(幅、変化特性等)のばらつきは実質的に発生せず、駆動パルスの形状(幅、変化特性等)がばらつくことに起因する表示むら現象を抑制することができる。

<Overview>

In the configuration of this embodiment, the display device or the electronic device uses the display unit, the storage capacitor, the write transistor that writes the drive voltage corresponding to the video signal in the storage capacitor, and the drive voltage written in the storage capacitor. A pixel portion having a driving transistor for driving the display portion based on the pixel portion is arranged in a predetermined direction. The pixel portion is provided with a drive line (scanning line) for supplying a drive pulse to drive at least one of the write transistors and the drive transistors arranged in a predetermined direction. A selection unit for selecting is further provided. In addition, the display device or the electronic apparatus includes a pulse generation unit that generates a pulse signal that is a source of the drive pulse, and the selection unit transfers the drive signal to a plurality of drive lines based on the pulse signal generated by the pulse generation unit. Supply drive pulses. A pulse signal that is the source of the drive pulse is generated by a pulse generation unit provided at a location different from the drive unit, and the drive unit sends drive pulses to a plurality of drive lines based on the pulse signal generated by the pulse generation unit. Supply. Therefore, since the drive signals supplied to a plurality of drive lines are based on the pulse signals generated by the same pulse generation unit, variations in pulse shape (width, change characteristics, etc.) are substantially generated between the drive pulses. In addition, the display unevenness phenomenon caused by the variation in the shape (width, change characteristics, etc.) of the drive pulse can be suppressed.

パルス生成部で生成されたパルス信号に基づいて複数の駆動線へ駆動部が駆動パルスを供給するので、パルス生成部の数は駆動線の総数よりも少なくてよい。この場合、全駆動線について1つのパルス生成部を設けることができるし、全駆動線の内の一部の複数の駆動線を一単位として、一単位ごとにパルス生成部を設けることもできる。 Since the drive unit supplies drive pulses to the plurality of drive lines based on the pulse signal generated by the pulse generation unit, the number of pulse generation units may be smaller than the total number of drive lines. In this case, one pulse generation unit can be provided for all the drive lines, and a pulse generation unit can be provided for each unit, with some of the drive lines as a unit.

パルス生成部の配置箇所としては、走査線の最外部に配置することもできるが、好ましくは、走査線の配列方向の中間部に配置する方がよい。パルス生成部から出力されるパルス信号の遅延量の差による弊害を小さくできるからである。因みに、全駆動線の内の一部の複数の駆動線の一単位ごとにパルス生成部を設ける場合には、その一単位ごとに、駆動線の配列方向における中間部にパルス生成部を配置すればよい。 The pulse generation unit may be arranged at the outermost part of the scanning line, but is preferably arranged at an intermediate part in the arrangement direction of the scanning line. This is because the adverse effects caused by the difference in the delay amount of the pulse signal output from the pulse generator can be reduced. Incidentally, when a pulse generator is provided for each unit of a plurality of drive lines of all the drive lines, the pulse generator is arranged in the intermediate part in the drive line arrangement direction for each unit. That's fine.

パルス生成部は、画素部の内部に設けることもできるし、画素部の外部に設けることもできる。画素部の外部に設けた方が、選択部(走査部)とパルス生成部とを一体的に造り込むことができる利点がある。画素部と選択部(走査部)とが別体とされる場合に好適な構成である。 The pulse generation unit can be provided inside the pixel unit or can be provided outside the pixel unit. Providing outside the pixel portion has an advantage that the selection portion (scanning portion) and the pulse generation portion can be integrally formed. This configuration is suitable when the pixel portion and the selection portion (scanning portion) are separated.

本実施形態の構成において、表示装置、或いは、電子機器は、選択部の駆動線の選択に基づき、パルス生成部で生成されたパルス信号を取り込んで、駆動線に供給するスイッチ回路、を駆動線ごとに有するスイッチ部を更に備える構成にすることができる。スイッチ回路としては、CMOSスイッチ等のトランスファーゲート構造を利用したものであるとよい。この場合、画素回路に入力される駆動パルスに関し、パネル内或いはパネル外で一括でパルス信号を生成した後に各CMOSスイッチ等で抜き出して走査線に供給する。「パネル内或いはパネル外で一括」であるので、パルス生成部は、各駆動線について、同じタイミングのパルス信号を生成するのがよい。仮に、各駆動線について異なるタイミングのパルス信号を生成する場合、スイッチ回路にパルスシフト機構等の対処が必要になる。スイッチ回路は、画素部の内部に設けることもできるし、画素部の外部に設けることもできる。画素部の外部に設けた方が、選択部(走査部)とスイッチ回路(更にはパルス生成部も)とを一体的に造り込むことができる利点がある。画素部と選択部(走査部)とが別体とされる場合に好適な構成である。 In the configuration of this embodiment, the display device or the electronic device uses a switching circuit that takes in the pulse signal generated by the pulse generation unit based on selection of the driving line of the selection unit and supplies the pulse signal to the driving line. It can be set as the structure further provided with the switch part which has for every. The switch circuit preferably uses a transfer gate structure such as a CMOS switch. In this case, regarding the drive pulses input to the pixel circuit, pulse signals are generated in a lump in the panel or outside the panel, and then extracted by each CMOS switch or the like and supplied to the scanning lines. Since it is “collectively within the panel or outside the panel”, the pulse generation unit may generate a pulse signal of the same timing for each drive line. If a pulse signal with different timing is generated for each drive line, a countermeasure such as a pulse shift mechanism is required for the switch circuit. The switch circuit can be provided inside the pixel portion or can be provided outside the pixel portion. Providing outside the pixel portion has an advantage that the selection portion (scanning portion) and the switch circuit (and also the pulse generation portion) can be integrally formed. This configuration is suitable when the pixel portion and the selection portion (scanning portion) are separated.

本実施形態の構成において、表示装置、或いは、電子機器は、選択部が、パルス生成部で生成されたパルス信号を一単位期間分ずつシフトして順に駆動線に供給するシフトレジスタ部を有する構成にすることもできる。これにより、一連の処理が一単位期間で完結される場合に限らず、一連の処理が複数の単位期間に亘る場合においても、駆動パルスの形状(幅、変化特性等)が行ごと或いは列ごとにばらつく度合いを緩和できる。論理回路を構成するトランジスタの特性ばらつきに起因する駆動パルスの形状のばらつきによる処理期間のばらつきが輝度むら(カラー表示の場合は色むら)として現れる現象を改善することができる。 In the configuration of the present embodiment, the display device or the electronic apparatus includes a shift register unit in which the selection unit shifts the pulse signal generated by the pulse generation unit by one unit period and sequentially supplies it to the drive line. It can also be. As a result, not only when a series of processing is completed in one unit period, but also when a series of processing spans a plurality of unit periods, the shape (width, change characteristics, etc.) of the drive pulse is set for each row or column. The degree of variation can be reduced. It is possible to improve a phenomenon in which variation in the processing period due to variation in the shape of the drive pulse due to variation in characteristics of the transistors forming the logic circuit appears as luminance unevenness (color unevenness in the case of color display).

駆動パルスは、例えば、書込トランジスタを介して映像信号を保持容量の一端に供給しつつ駆動トランジスタを介して保持容量に電流を供給する処理にも使用される。この処理は、書込トランジスタを介して映像信号を保持容量の一端に供給しつつ駆動トランジスタを介して保持容量に電流を供給する処理は、駆動トランジスタの移動度を補正する移動度補正処理に使用される。 The drive pulse is also used, for example, for a process of supplying a current to the storage capacitor via the drive transistor while supplying a video signal to one end of the storage capacitor via the write transistor. In this process, the process of supplying the current to the holding capacitor via the driving transistor while supplying the video signal to one end of the holding capacitor via the writing transistor is used for the mobility correction process for correcting the mobility of the driving transistor. Is done.

駆動パルスは、例えば、駆動トランジスタの閾値電圧のばらつきを補正するためにも使用される。前述の移動度補正との併用もあり得る。 The drive pulse is also used, for example, to correct variations in the threshold voltage of the drive transistor. A combination with the mobility correction described above is also possible.

デバイス構成としては、表示部がライン状或いは2次元マトリクス状に配列された画素部を備えるものでもよい。 As a device configuration, the display unit may include a pixel unit arranged in a line or a two-dimensional matrix.

表示部としては、例えば、有機エレクトロルミネッセンス発光部、無機エレクトロルミネッセンス発光部、LED発光部、半導体レーザー発光部等の自発光型の発光部を具備した発光素子を用いることができ、特に、有機エレクトロルミネッセンス発光部であるとよい。 As the display unit, for example, a light emitting element including a self-emitting type light emitting unit such as an organic electroluminescent light emitting unit, an inorganic electroluminescent light emitting unit, an LED light emitting unit, a semiconductor laser light emitting unit, etc. can be used. It is good that it is a luminescence light emitting part.

<表示装置の概要>

以下の説明においては、対応関係の理解を容易にするため、回路構成部材の抵抗値や容量値(静電容量、キャパシタンス)等は、その部材に付されている符号と同一符号で示すことがある。

<Outline of display device>

In the following description, in order to facilitate understanding of the correspondence relationship, the resistance value and the capacitance value (capacitance, capacitance), etc., of the circuit constituent member may be indicated by the same reference numerals as those attached to the member. is there.

[基本]

先ず、発光素子を備えた表示装置の概要について説明する。以下の回路構成の説明においては、「電気的に接続」を単に「接続」と記載するし、この「電気的に接続」は、特段の明示のない限り、直接に接続されることに限らず、他のトランジスタ(スイッチングトランジスタが典型例である)その他の電気素子(能動素子に限らず受動素子でもよい)を介して接続されることも含む。

[Basic]

First, an outline of a display device including a light emitting element will be described. In the following description of the circuit configuration, “electrically connected” is simply referred to as “connected”, and this “electrically connected” is not limited to being directly connected unless otherwise specified. It is also included that they are connected via other transistors (a switching transistor is a typical example) or other electrical elements (not limited to active elements but may be passive elements).

表示装置は、複数の画素回路(或いは単に画素とも称することもある)を備えている。各画素回路は、発光部と発光部を駆動する駆動回路とを具備する表示素子(電気光学素子)を有する。表示部としては、例えば、有機エレクトロルミネッセンス発光部、無機エレクトロルミネッセンス発光部、LED発光部、半導体レーザー発光部等の自発光型の発光部を具備した発光素子を用いることができる。尚、表示素子の発光部を駆動する方式としては定電流駆動型を採用するが、原理的には、定電流駆動型に限らず定電圧駆動型でもよい。 The display device includes a plurality of pixel circuits (or simply referred to as pixels). Each pixel circuit includes a display element (electro-optical element) including a light emitting unit and a drive circuit that drives the light emitting unit. As the display unit, for example, a light emitting element including a self-luminous light emitting unit such as an organic electroluminescence light emitting unit, an inorganic electroluminescence light emitting unit, an LED light emitting unit, a semiconductor laser light emitting unit, or the like can be used. Note that a constant current drive type is adopted as a method for driving the light emitting portion of the display element, but in principle, the constant current drive type is not limited to the constant current drive type.

以下に説明する例においては、発光素子として、有機エレクトロルミネッセンス発光部を備えている場合で説明する。より詳細には、発光素子は、駆動回路と、駆動回路に接続された有機エレクトロルミネッセンス発光部(発光部ELP)とが積層された構造を有する有機エレクトロルミネッセンス素子(有機EL素子)である。 In the example described below, a case where an organic electroluminescence light emitting unit is provided as a light emitting element will be described. More specifically, the light emitting element is an organic electroluminescent element (organic EL element) having a structure in which a driving circuit and an organic electroluminescent light emitting part (light emitting part ELP) connected to the driving circuit are stacked.

発光部ELPを駆動するための駆動回路として各種の回路があるが、画素回路としては、5Tr/1C型、4Tr/1C型、3Tr/1C型、或いは2Tr/1C型等の駆動回路を備えた構成にすることができる。「αTr/1C型」におけるαはトランジスタの数を意味し、「1C」は容量部が1つの保持容量Ccs(キャパシタ)を具備することを意味する。駆動回路を構成する各トランジスタは、好適には、全てがnチャネル型のトランジスタから構成されているのが好ましいが、これには限らず、場合によっては、一部のトランジスタをpチャネル型としてもよい。尚、半導体基板等にトランジスタを形成した構成とすることもできる。駆動回路を構成するトランジスタの構造は、特に限定するものではなく、MOS型FETを代表例とする絶縁ゲート型電界効果トランジスタ(一般には、薄膜トランジスタ(Thin Film Transistor ;TFT))を使用できる。更には、駆動回路を構成するトランジスタはエンハンスメント型とデプレッション型の何れでもよいし、又、シングルゲート型とデュアルゲート型の何れでもよい。 There are various types of driving circuits for driving the light emitting unit ELP, and the pixel circuit includes a driving circuit of 5Tr / 1C type, 4Tr / 1C type, 3Tr / 1C type, or 2Tr / 1C type. Can be configured. In the “αTr / 1C type”, α means the number of transistors, and “1C” means that the capacitor portion has one holding capacitor C cs (capacitor). The transistors constituting the drive circuit are preferably all n-channel transistors. However, the present invention is not limited to this, and in some cases, some transistors may be p-channel transistors. Good. Note that a transistor may be formed on a semiconductor substrate or the like. The structure of the transistor constituting the drive circuit is not particularly limited, and an insulated gate field effect transistor (typically, a thin film transistor (TFT)) typified by a MOS FET can be used. Further, the transistor constituting the driver circuit may be either an enhancement type or a depletion type, and may be either a single gate type or a dual gate type.

何れの構成においても、表示装置は、基本的には、最小の構成要素として2Tr/1C型と同様に、発光部ELP、駆動トランジスタTRD、書込トランジスタTRW(サンプリングトランジスタとも称される)、少なくとも書込走査部を具備する垂直走査部、信号出力部の機能を持つ水平駆動部、保持容量Ccsを備える。各走査部は、駆動線(走査線)を選択する選択部の一例である。好ましくは、ブートストラップ回路を構成するべく、駆動トランジスタTRDの制御入力端(ゲート端)と主電極端(ソース/ドレイン領域)の一方(典型的にはソース端)との間に保持容量Ccsが接続される。駆動トランジスタTRDは、主電極端の一方が発光部ELPと接続され、主電極端の他方は電源線PWLと接続される。電源線PWLには、電源回路或いは電源電圧用の走査回路等から電源電圧(定常電圧或いはパルス状の電圧)が供給される。 In any configuration, the display device basically has a light emitting unit ELP, a drive transistor TR D , and a write transistor TR W (also referred to as a sampling transistor) as in the 2Tr / 1C type as the minimum components. A vertical scanning unit including at least a writing scanning unit, a horizontal driving unit having a function of a signal output unit, and a holding capacitor C cs . Each scanning unit is an example of a selection unit that selects a drive line (scanning line). Preferably, in order to form a bootstrap circuit, a storage capacitor C is provided between the control input terminal (gate terminal) of the driving transistor TR D and one (typically the source terminal) of the main electrode terminal (source / drain region). cs is connected. Driving transistor TR D, one main electrode terminal is connected to the light emitting unit ELP, the other main electrode terminal is connected to the power supply line PWL. A power supply voltage (steady voltage or pulsed voltage) is supplied to the power supply line PWL from a power supply circuit or a scanning circuit for power supply voltage.

水平駆動部は、発光部ELPにおける輝度を制御するための映像信号Vsigや閾値補正等に使用される基準電位(1種とは限らない)を表す広義の映像信号VSを映像信号線DTL(データ線とも称される)に供給する。書込トランジスタTRWは、主電極端の一方が映像信号線DTLに接続され、主電極端の他方が駆動トランジスタTRDの制御入力端に接続される。書込走査部は書込トランジスタTRWをオン/オフ制御する制御パルス(書込駆動パルスWS)を書込走査線WSLを介して書込トランジスタTRWの制御入力端に供給する。書込トランジスタTRWの主電極端の他端と駆動トランジスタTRDの制御入力端と保持容量Ccsの一端との接続点を第1ノードND1と称し、駆動トランジスタTRDの主電極端の一方と保持容量Ccsの他端との接続点を第2ノードND2と称する。各走査線は、駆動パルスを画素回路を構成するトランジスタに供給する駆動線の一例である。 The horizontal drive unit displays a video signal V sig for controlling the luminance in the light emitting unit ELP, a video signal VS in a broad sense representing a reference potential (not limited to one type) used for threshold correction, and the like as a video signal line DTL ( Data line). Write transistor TR W is one of the main electrode terminal connected to the video signal line DTL, the other main electrode terminal connected to the control input terminal of the drive transistor TR D. Write scanner supplies a control input terminal of the write transistor TR W control pulse for turning on / off control of the write transistor TR W (write drive pulse WS) via a writing scanning line WSL. A connection point between the other end of the main electrode end of the write transistor TR W , the control input end of the drive transistor TR D , and one end of the storage capacitor C cs is referred to as a first node ND 1 , and is connected to the main electrode end of the drive transistor TR D. A connection point between one end and the other end of the storage capacitor C cs is referred to as a second node ND 2 . Each scanning line is an example of a driving line that supplies a driving pulse to a transistor included in the pixel circuit.

[構成例]

図1及び図2は、本開示に係る表示装置の一実施形態であるアクティブマトリクス型表示装置の一構成例の概略を示すブロック図である。図1は、一般的なアクティブマトリクス型表示装置の構成の概略を示すブロック図であり、図2は、そのカラー画像表示対応の場合の概略を示すブロック図である。

[Configuration example]

1 and 2 are block diagrams illustrating an outline of a configuration example of an active matrix display device that is an embodiment of a display device according to the present disclosure. FIG. 1 is a block diagram showing an outline of the configuration of a general active matrix display device, and FIG. 2 is a block diagram showing an outline in the case of color image display.

図1に示すように、表示装置1は、複数の表示素子としての有機EL素子(図示せず)を持った画素回路10(画素とも称される)が表示アスペクト比である縦横比がX:Y(例えば9:16)の有効映像領域を構成するように配置された表示パネル部100と、この表示パネル部100を駆動制御する種々のパルス信号を発するパネル制御部の一例である駆動信号生成部200(いわゆるタイミングジェネレータ)と、映像信号処理部220を備えている。駆動信号生成部200と映像信号処理部220とは、1チップのIC(Integrated Circuit;半導体集積回路)に内蔵され、本例では、表示パネル部100の外部に配置されている。

As shown in FIG. 1, the

尚、製品形態としては、図示のように、表示パネル部100、駆動信号生成部200、及び映像信号処理部220の全てを備えたモジュール(複合部品)形態の表示装置1として提供されることに限らず、例えば、表示パネル部100のみで表示装置1として提供すしてもよい。又、表示装置1は、封止された構成のモジュール形状のものをも含む。例えば、画素アレイ部102に透明なガラス等の対向部に貼り付けられて形成された表示モジュールが該当する。透明な対向部には、カラーフィルタ、保護膜、遮光膜等が設けられてもよい。表示モジュールには、外部から画素アレイ部102への映像信号Vsigや各種の駆動パルスを入出力するための回路部やFPC(フレキシブルプリントサーキット)等が設けられていてもよい。

As shown in the figure, the product form is provided as a

このような表示装置1は、様々な電子機器、例えば半導体メモリやミニディスク(MD)やカセットテープ等の記録媒体を利用した携帯型の音楽プレイヤー、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置、ビデオカメラ等、電子機器に入力された映像信号や電子機器内で生成した映像信号を、静止画像や動画像(映像)として表示するあらゆる分野の電子機器の表示部に利用できる。

Such a

表示パネル部100は、基板101の上に、画素回路10がM行×N列のマトリクス状に配列された画素アレイ部102と、画素回路10を垂直方向に走査する垂直駆動部103と、画素回路10を水平方向に走査する水平駆動部106(水平セレクタ或いはデータ線駆動部とも称される)と、各駆動部(垂直駆動部103及び水平駆動部106)と外部回路とのインタフェースをとるインタフェース部130(IF)と、外部接続用の端子部108(パッド部)等が集積形成されている。即ち、垂直駆動部103や水平駆動部106やインタフェース部130等の周辺駆動回路が、画素アレイ部102と同一の基板101上に形成された構成となっている。第m行目(m=1、2、3、…、M)、第n列(n=1、2、3、…、N)に位置する発光素子(画素回路10)を、図では10_n,mで示している。

The display panel unit 100 includes a

インタフェース部130は、垂直駆動部103と外部回路とのインタフェースをとる垂直IF部133と、水平駆動部106と外部回路とのインタフェースをとる水平IF部136を有する。

The interface unit 130 includes a vertical IF

垂直駆動部103と水平駆動部106とで、信号電位の保持容量への書込みや、閾値補正動作や、移動度補正動作や、ブートストラップ動作を制御する制御部109が構成される。この制御部109とインタフェース部130(垂直IF部133や水平IF部136)を含めて、画素アレイ部102の画素回路10を駆動制御する駆動制御回路を構成している。

The

2Tr/1C型とする場合であれば、垂直駆動部103は、書込走査部(ライトスキャナWS;Write Scan)や電源供給能力を有する電源スキャナとして機能する駆動走査部(ドライブスキャナDS;Drive Scan)を有する。画素アレイ部102は、一例として、図示する左右方向の一方側もしくは両側から垂直駆動部103で駆動され、かつ図示する上下方向の一方側もしくは両側から水平駆動部106で駆動されるようになっている。

In the case of the 2Tr / 1C type, the

端子部108には、表示装置1の外部に配された駆動信号生成部200から、種々のパルス信号が供給される。同様に、映像信号処理部220から映像信号Vsigが供給される。カラー表示対応の場合には、色別(本例ではR(赤)、G(緑)、B(青)の3原色)の映像信号Vsig_R、映像信号Vsig_G、映像信号Vsig_Bが供給される。

Various pulse signals are supplied to the

一例としては、垂直駆動用のパルス信号として、垂直方向の走査開始パルスの一例であるシフトスタートパルスSP(図はSPDS、SPWSの2種)や垂直走査クロックCK(図はCKDS、CKWSの2種)、必要に応じて位相反転した垂直走査クロックxCK(図はxCKDS、xCKWSの2種)、並びに特定タイミングのパルス出力を指示するイネーブルパルス等の必要なパルス信号が供給される。水平駆動用のパルス信号として、水平方向の走査開始パルスの一例である水平スタートパルスSPHや水平走査クロックCKH、必要に応じて位相反転した水平走査クロックxCKH、並びに特定タイミングのパルス出力を指示するイネーブルパルス等の必要なパルス信号が供給される。 As an example, as a pulse signal for vertical driving, a shift start pulse SP (two types of SPDS and SPWS in the figure) and a vertical scanning clock CK (two types of CKDS and CKWS in the figure) are examples of a vertical scanning start pulse. ), Necessary pulse signals such as a vertical scanning clock xCK (two types of xCKDS and xCKWS in the figure) whose phases are inverted as necessary, and an enable pulse for instructing a pulse output at a specific timing are supplied. As horizontal drive pulse signals, horizontal start pulse SPH, which is an example of a horizontal scan start pulse, horizontal scan clock CKH, horizontal scan clock xCKH whose phase is reversed as necessary, and enable to instruct pulse output at a specific timing Necessary pulse signals such as pulses are supplied.

端子部108の各端子は、配線109を介して、垂直駆動部103や水平駆動部106に接続される。例えば、端子部108に供給された各パルスは、必要に応じて図示を割愛したレベルシフタ部で電圧レベルを内部的に調整した後、バッファを介して垂直駆動部103の各部や水平駆動部106に供給される。

Each terminal of the

画素アレイ部102は、図示を割愛するが(詳細は後述する)、表示素子としての有機EL素子に対して画素トランジスタが設けられた画素回路10が行列状に2次元配置され、画素配列に対して行ごとに垂直走査線SCLが配線されるとともに、列ごとに映像信号線DTLが配線された構成となっている。つまり、画素回路10は、垂直走査線SCLを介して直駆動部103と接続され、又、映像信号線DTLを介して水平駆動部106と接続されている。具体的には、マトリクス状に配列された各画素回路10に対しては、垂直駆動部103によって駆動パルスで駆動されるn行分の垂直走査線SCL_1〜SCL_nが画素行ごとに配線される。垂直駆動部103は、論理ゲートの組合せ(ラッチやシフトレジスタ等も含む)によって構成され、画素アレイ部102の各画素回路10を行単位で選択する、即ち、駆動信号生成部200から供給される垂直駆動系のパルス信号に基づき、垂直走査線SCLを介して各画素回路10を順次選択する。水平駆動部106は、論理ゲートの組合せ(ラッチやシフトレジスタ等も含む)によって構成され、画素アレイ部102の各画素回路10を列単位で選択する、即ち、駆動信号生成部200から供給される水平駆動系のパルス信号に基づき、選択された画素回路10に対し映像信号線DTLを介して映像信号VSの内の所定電位(例えば映像信号Vsigレベル)をサンプリングして保持容量Ccsに書き込ませる。

Although the

本実施形態の表示装置1は、線順次駆動や点順次駆動が可能になっており、垂直駆動部103の書込走査部104及び駆動走査部105は線順次で(つまり行単位で)で画素アレイ部102を走査するとともに、これに同期して水平駆動部106が、画像信号を、1水平ライン分を同時に(線順次の場合)、或いは画素単位で(点順次の場合)、画素アレイ部102に書き込む。

The

カラー画像表示対応をとるには、画素アレイ部102には、例えば図2に示すように、色別(本例ではR(赤)、G(緑)、B(青)の3原色)のサブピクセルとして画素回路10_R、画素回路10_G、画素回路10_Bを所定の配列順で縦ストライプ状に設ける。1組の色別のサブピクセルによりカラーの1画素が構成される。ここでは、サブピクセルレイアウトの一例として縦ストライプ状に各色のサブピクセルを配置したストライプ構造のものを示しているが、サブピクセルレイアウトはこのような配列例に限定されるものではない。サブピクセルを垂直方向にシフトさせた形態を採用してもよい。

In order to achieve color image display, the

尚、図1及び図2では、画素アレイ部102の一方側にのみ垂直駆動部103(詳しくはその構成要素)を配置する構成を示しているが、垂直駆動部103の各要素を画素アレイ部102を挟んで左右両側に配置する構成を採ることもできる。又、垂直駆動部103の各要素の一方と他方を左右の各別に配置する構成を採ることもできる。同様に、図1及び図2では、画素アレイ部102の一方側にのみ水平駆動部106を配置する構成を示しているが、画素アレイ部102を挟んで上下両側に水平駆動部106を配置する構成を採ることもできる。本例では、垂直シフトスタートパルス、垂直走査クロック、水平スタートパルス、水平走査クロック等のパルス信号を表示パネル部100の外部から入力する構成としているが、これらの各種のタイミングパルスを生成する駆動信号生成部200を表示パネル部100上に搭載することもできる。

1 and 2 show a configuration in which the vertical drive unit 103 (specifically, its constituent elements) is arranged only on one side of the

図示した構成は、表示装置の一形態を示したに過ぎず、製品形態としては、その他の形態をとることができる。即ち、表示装置は、画素回路10を構成する素子を行列状に配置した画素アレイ部と、画素アレイ部の周辺に配置され、各画素を駆動するための走査線と接続された走査部を主要部とする制御部と、制御部を動作させるための各種の信号を生成する駆動信号生成部や映像信号処理部を備えて装置の全体が構成されていればよい。製品形態としては、画素アレイ部と制御部とを同一の基体(例えばガラス基板)上に搭載した表示パネル部と駆動信号生成部や映像信号処理部を別体とする図示のような形態(パネル上配置構成と称する)の他に、表示パネル部には画素アレイ部を搭載し、それとは別基板(例えばフレキシブル基板)上に制御部や駆動信号生成部や映像信号処理部等の周辺回路を搭載する形態(周辺回路パネル外配置構成と称する)を採ることができる。又、画素アレイ部と制御部とを同一の基体上に搭載して表示パネル部を構成するパネル上配置構成の場合、画素アレイ部のTFTを生成する工程にて同時に制御部(必要に応じて駆動信号生成部や映像信号処理部も)用の各トランジスタを生成する形態(トランジスタ一体構成と称する)と、COG(Chip On Glass)実装技術により画素アレイ部が搭載された基体上に制御部(必要に応じて駆動信号生成部や映像信号処理部も)用の半導体チップを直接実装する形態(COG搭載構成と称する)を採ることもできる。或いは又、表示パネル部(少なくとも画素アレイ部を備える)のみで表示装置として提供することもできる。

The illustrated configuration only shows one form of the display device, and the product form can take other forms. That is, the display device mainly includes a pixel array unit in which elements constituting the

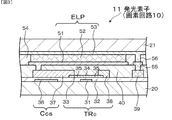

<発光素子>

図3は、駆動回路を備えた発光素子11(実質的には画素回路10)を説明する図である。ここで、図3は、発光素子11(画素回路10)の一部分の模式的な一部断面図である。図3では、絶縁ゲート型電界効果トランジスタは薄膜トランジスタ(TFT)であるとする。図示しないが、いわゆるバックゲート型の薄膜トランジスタ或いはMOS型のトランジスタを使用してもよい。

<Light emitting element>

FIG. 3 is a diagram for explaining the light emitting element 11 (substantially the pixel circuit 10) provided with a drive circuit. Here, FIG. 3 is a schematic partial cross-sectional view of a part of the light emitting element 11 (pixel circuit 10). In FIG. 3, it is assumed that the insulated gate field effect transistor is a thin film transistor (TFT). Although not shown, a so-called back gate type thin film transistor or MOS type transistor may be used.

発光素子11の駆動回路を構成する各トランジスタ及び容量部(保持容量Ccs)は支持体20上に形成され、発光部ELPは、例えば、層間絶縁層40を介して、駆動回路を構成する各トランジスタ及び保持容量Ccsの上方に形成されている。駆動トランジスタTRDの一方のソース/ドレイン領域は、発光部ELPに備えられたアノード電極に、コンタクトホールを介して接続されている。図3においては、駆動トランジスタTRDのみを図示する。書込トランジスタTRWやその他のトランジスタは隠れて見えない。発光部ELPは、例えば、アノード電極、正孔輸送層、発光層、電子輸送層、カソード電極等の周知の構成、構造を有する。

Each transistor and capacitor (retention capacitor C cs ) constituting the drive circuit of the light-emitting element 11 are formed on the

具体的には、駆動トランジスタTRDは、ゲート電極31、ゲート絶縁層32、半導体層33、半導体層33に設けられたソース/ドレイン領域35、及び、ソース/ドレイン領域35の間の半導体層33の部分が該当するチャネル形成領域34から構成されている。保持容量Ccsは、他方の電極36、ゲート絶縁層32の延在部から構成された誘電体層、及び、一方の電極37(第2ノードND2に相当する)から成る。ゲート電極31、ゲート絶縁層32の一部、及び、保持容量Ccsを構成する他方の電極36は、支持体20上に形成されている。駆動トランジスタTRDの一方のソース/ドレイン領域35は配線38に接続され、一方のソース/ドレイン領域35は一方の電極37に接続されている。駆動トランジスタTRD及び保持容量Ccs等は、層間絶縁層40で覆われており、層間絶縁層40上に、アノード電極51、正孔輸送層、発光層、電子輸送層、及び、カソード電極53から成る発光部ELPが設けられている。図3においては、正孔輸送層、発光層、及び、電子輸送層を1層52で表した。発光部ELPが設けられていない層間絶縁層40の部分の上には、第2層間絶縁層54が設けられ、第2層間絶縁層54及びカソード電極53上には透明な基板21が配置されており、発光層にて発光した光は、基板21を通過して、外部に出射される。一方の電極37とアノード電極51とは、層間絶縁層40に設けられたコンタクトホールによって接続されている。カソード電極53は、第2層間絶縁層54、層間絶縁層40に設けられたコンタクトホール56、コンタクトホール55を介して、ゲート絶縁層32の延在部上に設けられた配線39に接続されている。

Specifically, the drive transistor TR D includes a

[駆動方法]

発光部の駆動方法に関して、以下に説明する。理解を容易にするべく、画素回路10を構成する各トランジスタは、nチャネル型のトランジスタから構成されているとして説明する。又、発光部ELPは、アノード端が第2ノードND2に接続され、カソード端はカソード配線cath(その電位をカソード電位Vcathとする)に接続されるものとする。更には、ドレイン電流Idsの値の大小によって、発光部ELPにおける発光状態(輝度)が制御される。発光素子の発光状態においては、駆動トランジスタTRDの2つの主電極端(ソース/ドレイン領域)は、一方(発光部ELPのアノード側)がソース端(ソース領域)として働き、他方がドレイン端(ドレイン領域)として働く。表示装置は、カラー表示対応のものであり、(N/3)×M個の2次元マトリクス状に配列された画素回路10から構成され、カラー表示の一単位を成す1つの画素回路は、3つの副画素回路(赤色を発光する赤色発光画素回路10_R、緑色を発光する緑色発光画素回路10_G、青色を発光する青色発光画素回路10_B)から構成されているとする。各画素回路10を構成する発光素子は、線順次駆動されるとし、表示フレームレートをFR(回/秒)とする。即ち、第m行目(但し、m=1、2、3、…、M)に配列された(N/3)個の画素回路10、より具体的には、N個の画素回路10のそれぞれを構成する発光素子が同時に駆動される。換言すれば、1つの行を構成する各発光素子にあっては、その発光/非発光のタイミングは、それらが属する行単位で制御される。尚、1つの行を構成する各画素回路10について映像信号を書き込む処理は、全ての画素回路10について同時に映像信号を書き込む処理(同時書込み処理とも称する)でもよいし、画素回路10毎に順次映像信号を書き込む処理(順次書込み処理とも称する)でもよい。何れの書込み処理とするかは、駆動回路の構成に応じて適宜選択すればよい。

[Driving method]

A method for driving the light emitting unit will be described below. In order to facilitate understanding, each transistor constituting the

ここで、第m行目、第n列(但し、n=1、2、3、…、N)に位置する発光素子(画素回路10)に関する駆動動作を説明する。因みに、第m行目、第n列に位置する発光素子を、第(n、m)番目の発光素子或いは第(n、m)番目の発光素子画素回路と称する。第m行目に配列された各発光素子の水平走査期間(第m番目の水平走査期間)が終了するまでに、各種の処理(閾値補正処理、書込み処理、移動度補正処理、等)が行なわれる。尚、書込み処理や移動度補正処理は、第m番目の水平走査期間内に行なわれる必要がある。一方、駆動回路の種類によっては、閾値補正処理やこれに伴う前処理を第m番目の水平走査期間より先行して行なうことができる。 Here, a driving operation related to the light emitting element (pixel circuit 10) located in the m-th row and the n-th column (where n = 1, 2, 3,..., N) will be described. Incidentally, the light emitting element located in the mth row and the nth column is referred to as the (n, m) th light emitting element or the (n, m) th light emitting element pixel circuit. Various processes (threshold correction process, writing process, mobility correction process, etc.) are performed before the horizontal scanning period (m-th horizontal scanning period) of each light emitting element arranged in the m-th row is completed. It is. Note that the writing process and the mobility correction process need to be performed within the m-th horizontal scanning period. On the other hand, depending on the type of the drive circuit, the threshold correction processing and the preprocessing associated therewith can be performed prior to the mth horizontal scanning period.

前述の各種の処理が全て終了した後、第m行目に配列された各発光素子を構成する発光部を発光させる。尚、各種の処理が全て終了した後、直ちに発光部を発光させてもよいし、所定の期間(例えば、所定の行数分の水平走査期間)が経過した後に発光部を発光させてもよい。「所定の期間」は、表示装置の仕様や画素回路10(つまり駆動回路)の構成等に応じて、適宜設定すればよい。以下では説明の便宜のため、各種の処理終了後、直ちに発光部を発光させるものとする。第m行目に配列された各発光素子を構成する発光部の発光は、第(m+m’)行目に配列された各発光素子の水平走査期間の開始直前まで継続される。「m’」は、表示装置の設計仕様によって決定すればよい。即ち、或る表示フレームの第m行目に配列された各発光素子を構成する発光部の発光は、第(m+m’−1)番目の水平走査期間まで継続される。一方、第(m+m’)番目の水平走査期間の始期から、次の表示フレームにおける第m番目の水平走査期間内において書込み処理や移動度補正処理が完了するまで、第m行目に配列された各発光素子を構成する発光部は、原則として非発光状態を維持する。非発光状態の期間(非発光期間とも称する)を設けることにより、アクティブマトリクス駆動に伴う残像ボケが低減され、動画品位をより良好にすることができる。但し、各画素回路10(発光素子)の発光状態/非発光状態は、以上に説明した状態には限定されない。水平走査期間の時間長は、(1/FR)×(1/M)秒未満の時間長である。(m+m’)の値がMを越える場合、越えた分の水平走査期間は、次の表示フレームにおいて処理される。 After all the above-described various processes are completed, the light emitting units constituting the light emitting elements arranged in the m-th row are caused to emit light. In addition, after all the various processes are completed, the light emitting unit may emit light immediately, or the light emitting unit may emit light after a predetermined period (for example, a horizontal scanning period for a predetermined number of rows) has elapsed. . The “predetermined period” may be appropriately set according to the specifications of the display device, the configuration of the pixel circuit 10 (that is, the drive circuit), and the like. In the following, for convenience of explanation, it is assumed that the light emitting unit emits light immediately after completion of various processes. The light emission of the light emitting units constituting the light emitting elements arranged in the mth row is continued until just before the start of the horizontal scanning period of the light emitting elements arranged in the (m + m ′) th row. “M ′” may be determined according to the design specifications of the display device. That is, the light emission of the light emitting units constituting the light emitting elements arranged in the mth row of a certain display frame is continued until the (m + m′−1) th horizontal scanning period. On the other hand, from the beginning of the (m + m ′) th horizontal scanning period to the mth horizontal scanning period in the next display frame until the writing process and the mobility correction process are completed, they are arranged in the mth row. As a general rule, the light-emitting portion constituting each light-emitting element maintains a non-light-emitting state. By providing a non-light emitting period (also referred to as a non-light emitting period), afterimage blur caused by active matrix driving is reduced, and the quality of moving images can be improved. However, the light emission state / non-light emission state of each pixel circuit 10 (light emitting element) is not limited to the state described above. The time length of the horizontal scanning period is a time length of less than (1 / FR) × (1 / M) seconds. When the value of (m + m ′) exceeds M, the excess horizontal scanning period is processed in the next display frame.

トランジスタがオン状態(導通状態)にあるとは、主電極端間(ソース/ドレイン領域間)にチャネルが形成されている状態を意味し、一方の主電極端から他方の主電極端に電流が流れているか否かは問わない。トランジスタがオフ状態(非導通状態)にあるとは、主電極端間にチャネルが形成されていない状態を意味する。或るトランジスタの主電極端が他のトランジスタの主電極端に接続されているとは、或るトランジスタのソース/ドレイン領域と他のトランジスタのソース/ドレイン領域とが同じ領域を占めている形態を包含する。更には、ソース/ドレイン領域は、不純物を含有したポリシリコンやアモルファスシリコン等の導電性物質から構成することができるだけでなく、金属、合金、導電性粒子、これらの積層構造、有機材料(導電性高分子)から成る層から構成することができる。又、以下の説明で用いるタイミングチャートにおいて、各期間を示す横軸の長さ(時間長)は模式的なものであり、各期間の時間長の割合を示すものではない。 A transistor in an on state (conducting state) means a state in which a channel is formed between the main electrode ends (between the source / drain regions), and a current flows from one main electrode end to the other main electrode end. It doesn't matter whether it is flowing or not. The transistor being in an off state (non-conducting state) means a state in which no channel is formed between the main electrode ends. The main electrode end of a certain transistor is connected to the main electrode end of another transistor means that the source / drain region of a certain transistor and the source / drain region of another transistor occupy the same region. Includes. Furthermore, the source / drain regions can be composed not only of conductive materials such as polysilicon or amorphous silicon containing impurities, but also metals, alloys, conductive particles, their laminated structures, organic materials (conductive Polymer). In the timing chart used in the following description, the length of the horizontal axis (time length) indicating each period is a schematic one and does not indicate the ratio of the time length of each period.

画素回路10の駆動方法においては、前処理工程、閾値補正処理工程、映像信号書込み処理工程、移動度補正工程、発光工程を有する。前処理工程、閾値補正処理工程、映像信号書込み処理工程、及び、移動度補正工程を纏めて非発光工程とも称する。画素回路10の構成によっては映像信号書込み処理工程と移動度補正工程とを同時に行なうこともある。各工程について概説する。

The driving method of the

因みに、駆動トランジスタTRDは、発光素子の発光状態においては、以下の式(1)に従ってドレイン電流Idsを流すように駆動される。ドレイン電流Idsが発光部ELPを流れることで発光部ELPが発光する。更には、ドレイン電流Idsの値の大小によって、発光部ELPにおける発光状態(輝度)が制御される。発光素子の発光状態においては、駆動トランジスタTRDの2つの主電極端(ソース/ドレイン領域)は、一方(発光部ELPのアノード端側)がソース端(ソース領域)として働き、他方がドレイン端(ドレイン領域)として働く。説明の便宜のため、以下の説明において、駆動トランジスタTRDの一方の主電極端を単にソース端と称し、他方の主電極端を単にドレイン端と呼ぶ場合がある。尚、実効的な移動度μ、チャネル長L、チャネル幅W、制御電極端の電位(ゲート電位Vg)とソース端の電位(ソース電位Vs)との電位差(ゲート・ソース間電圧)Vgs、閾値電圧Vth、等価容量Cox((ゲート絶縁層の比誘電率)×(真空の誘電率)/(ゲート絶縁層の厚さ))、係数k≡(1/2)・(W/L)・Coxとする。 Incidentally, the drive transistor TR D is driven so that the drain current I ds flows according to the following formula (1) in the light emitting state of the light emitting element. When the drain current I ds flows through the light emitting unit ELP, the light emitting unit ELP emits light. Furthermore, the light emission state (luminance) in the light emitting unit ELP is controlled by the magnitude of the value of the drain current I ds . In the light emitting state of the light emitting element, one of the two main electrode ends (source / drain regions) of the driving transistor TR D serves as a source end (source region) while the other serves as a drain end. Work as (drain region). For convenience of description, in the following description, one main electrode end of the drive transistor TR D may be simply referred to as a source end, and the other main electrode end may be simply referred to as a drain end. Effective mobility μ, channel length L, channel width W, potential difference (gate-source voltage) V between control electrode end potential (gate potential V g ) and source end potential (source potential V s ) V gs , threshold voltage V th , equivalent capacitance C ox ((dielectric constant of gate insulating layer) × (dielectric constant of vacuum) / (thickness of gate insulating layer)), coefficient k≡ (1/2) · (W / L) · C ox .

Ids=k・μ・(Vgs−Vth)2 (1) I ds = k · μ · (V gs −V th ) 2 (1)

以下の説明では、特段の断りのない限り、発光部ELPの寄生容量の静電容量Celは、保持容量Ccsの静電容量Ccs及び駆動トランジスタTRDの寄生容量の一例であるゲート・ソース間の静電容量Cgsと比較して十分に大きな値であるとし、駆動トランジスタTRDのゲート端の電位(ゲート電位Vg)の変化に基づく駆動トランジスタTRDのソース領域(第2ノードND2)の電位(ソース電位Vs)の変化を考慮しない。 In the following description, unless otherwise specified, the capacitance C el of the parasitic capacitance of the light emitting unit ELP is an example of the capacitance C cs of the holding capacitor C cs and the parasitic capacitance of the driving transistor TR D. A source region (second node) of the drive transistor TR D based on a change in the potential (gate potential V g ) of the gate end of the drive transistor TR D is assumed to be a sufficiently large value compared with the capacitance C gs between the sources. ND 2 ) potential (source potential V s ) is not considered.

〔前処理工程〕

第1ノードND1と第2ノードND2との間の電位差が、駆動トランジスタTRDの閾値電圧Vthを越え、且つ、第2ノードND2と発光部ELPに備えられたカソード電極との間の電位差が、発光部ELPの閾値電圧VthELを越えないように、第1ノードND1に第1ノード初期化電圧(Vofs)を印加し、第2ノードND2に第2ノード初期化電圧(Vini)を印加する。例えば、発光部ELPにおける輝度を制御するための映像信号Vsigを0〜10ボルト、電源電圧Vccを20ボルト、駆動トランジスタTRDの閾値電圧Vthを3V、カソード電位Vcathを0ボルト、発光部ELPの閾値電圧VthELを3ボルトとする。この場合、駆動トランジスタTRDの制御入力端の電位(ゲート電位Vg、つまり第1ノードND1の電位)を初期化するための電位Vofsは0ボルト、駆動トランジスタTRDのソース端の電位(ソース電位Vsつまり第2ノードND2の電位)を初期化するための電位Viniは−10ボルトとする。

[Pretreatment process]

The potential difference between the first node ND 1 and the second node ND 2 exceeds the threshold voltage V th of the driving transistor TR D , and between the second node ND 2 and the cathode electrode provided in the light emitting unit ELP. The first node initialization voltage (V ofs ) is applied to the first node ND 1 and the second node initialization voltage is applied to the second node ND 2 so that the potential difference between the first node ND 1 and the threshold voltage V thEL does not exceed the threshold voltage V thEL. (V ini ) is applied. For example, the video signal V sig for controlling the luminance in the light emitting unit ELP is 0 to 10 volts, the power supply voltage V cc is 20 volts, the threshold voltage V th of the driving transistor TR D is 3 V, the cathode potential V cath is 0 volts, The threshold voltage V thEL of the light emitting unit ELP is 3 volts. In this case, the potential V ofs for initializing the potential of the control input terminal of the drive transistor TR D (gate potential V g , that is, the potential of the first node ND 1 ) is 0 volts, and the potential of the source terminal of the drive transistor TR D The potential V ini for initializing (the source potential V s, that is, the potential of the second node ND 2 ) is −10 volts.

〔閾値補正処理工程〕

第1ノードND1の電位を保った状態で、駆動トランジスタTRDにドレイン電流Idsを流して、第1ノードND1の電位から駆動トランジスタTRDの閾値電圧Vthを減じた電位に向かって第2ノードND2の電位を変化させる。この際には、前処理工程後の第2ノードND2の電位に駆動トランジスタTRDの閾値電圧Vthを加えた電圧を超える電圧(例えば発光時の電源電圧)を、駆動トランジスタTRDの主電極端の他方(第2ノードND2とは反対側)に印加する。この閾値補正処理工程において、第1ノードND1と第2ノードND2との間の電位差(換言すれば、駆動トランジスタTRDのゲート・ソース間電圧Vgs)が駆動トランジスタTRDの閾値電圧Vthに近づく程度は閾値補正処理の時間により左右される。よって、例えば閾値補正処理の時間を充分長く確保すれば第2ノードND2の電位は第1ノードND1の電位から駆動トランジスタTRDの閾値電圧Vthを減じた電位に達し、駆動トランジスタTRDはオフ状態となる。一方、例えば閾値補正処理の時間を短く設定せざるを得ない場合は、第1ノードND1と第2ノードND2との間の電位差が駆動トランジスタTRDの閾値電圧Vthより大きく、駆動トランジスタTRDはオフ状態とはならない場合がある。閾値補正処理の結果として、必ずしも駆動トランジスタTRDがオフ状態となることを要しない。尚、閾値補正処理工程においては、好ましくは、式(2)を満足するように電位を選択、決定しておくことで、発光部ELPが発光しないようにする。

[Threshold correction processing step]

While maintaining the potential of the first node ND 1, by supplying a drain current I ds to the drive transistor TR D, toward an electric potential obtained by subtracting the threshold voltage V th of the driving transistor TR D from the first node potential of ND 1 The potential of the second node ND 2 is changed. At this time, the pretreatment step after the second node ND 2 in a voltage exceeding the threshold voltage V th of the voltage obtained by adding the driving transistor TR D to the potential (e.g., power supply voltage during light emission), a main driving transistor TR D It is applied to the other electrode end (the side opposite to the second node ND 2 ). In the threshold value correction process, (in other words, the driving transistor TR gate-source voltage of the D V gs) the potential difference between the first node ND 1 and the second node ND 2 is the threshold voltage V of the drive transistor TR D The degree of approaching th depends on the threshold correction processing time. Thus, for example, if the threshold correction processing time is sufficiently long, the potential of the second node ND 2 reaches the potential obtained by subtracting the threshold voltage V th of the drive transistor TR D from the potential of the first node ND 1 , and the drive transistor TR D Is turned off. On the other hand, for example, when the threshold correction processing time must be set short, the potential difference between the first node ND 1 and the second node ND 2 is larger than the threshold voltage V th of the drive transistor TR D , and the drive transistor TR D may not be off. As a result of the threshold correction process, the drive transistor TR D does not necessarily have to be turned off. In the threshold value correction processing step, preferably, the light emitting unit ELP does not emit light by selecting and determining a potential so as to satisfy Expression (2).

(Vofs−Vth)<(VthEL+Vcath) (2) (V ofs -V th) <( V thEL + V cath) (2)

〔映像信号書込み処理工程〕

書込走査線WSLからの書込駆動パルスWSによりオン状態とされた書込トランジスタTRWを介して、映像信号線DTLから映像信号Vsigを第1ノードND1に印加し、第1ノードND1の電位をVsigへと上昇させる。この電第1ノードND1の電位変化分(ΔVin=Vsig−Vofs)に基づく電荷が、保持容量Ccs、発光部ELPの寄生容量Cel、駆動トランジスタTRDの寄生容量(例えばゲート・ソース間容量Cgs等)に振り分けられる。静電容量Celが、静電容量Ccs及びゲート・ソース間容量Cgsの静電容量Cgsと比較して十分に大きな値であれば、電位変化分(Vsig−Vofs)に基づく第2ノードND2の電位の変化は小さい。一般に、発光部ELPの寄生容量Celの静電容量Celは、保持容量Ccsの静電容量Ccs及びゲート・ソース間容量Cgsの静電容量Cgsよりも大きい。この点を勘案して、特段の必要がある場合を除き、第1ノードND1の電位変化により生ずる第2ノードND2の電位変化は考慮しない。この場合、ゲート・ソース間電圧Vgsは、式(3)で表すことができる。

[Video signal writing process]

The video signal V sig is applied from the video signal line DTL to the first node ND 1 via the write transistor TR W that is turned on by the write drive pulse WS from the write scanning line WSL, and the first node ND 1 Increase the potential of 1 to V sig . Charges based on the potential change (ΔV in = V sig −V ofs ) of the electric first node ND 1 are the holding capacitor C cs , the parasitic capacitance C el of the light emitting unit ELP, and the parasitic capacitance (eg, gate) of the driving transistor TR D. -The capacity between sources C gs etc.). Capacitance C el is, if sufficiently large value as compared with the capacitance C gs of the electrostatic capacitance C cs and the gate-source capacitance C gs, based on the potential variation (V sig -V ofs) The change in potential of the second node ND 2 is small. In general, the capacitance C el of the parasitic capacitance C el of the light emitting section ELP is larger than the capacitance C gs of the storage capacitor C cs of the electrostatic capacitance C cs and the gate-source capacitance C gs. In consideration of this point, the potential change of the second node ND 2 caused by the potential change of the first node ND 1 is not taken into account, unless otherwise required. In this case, the gate-source voltage V gs can be expressed by Equation (3).

Vg=Vsig

Vs ≒Vofs−Vth

Vgs≒Vsig−(Vofs−Vth) (3)

V g = V sig

V s ≒ V ofs -V th

V gs ≈ V sig − (V ofs −V th ) (3)

〔移動度補正処理工程〕

書込トランジスタTRWを介して映像信号Vsigを保持容量Ccsの一端に供給しつつ(つまり映像信号Vsigと対応する駆動電圧を保持容量Ccsに書き込みつつ)、駆動トランジスタTRDを介して保持容量Ccsに電流を供給する。例えば、書込走査線WSLからの書込駆動パルスWSによりオン状態とされた書込トランジスタTRWを介して映像信号線DTLから映像信号Vsigを第1ノードND1に供給した状態で、駆動トランジスタTRDに電源を供給しドレイン電流Idsを流して、第2ノードND2の電位を変化させ、所定期間経過後、書込トランジスタTRWをオフ状態にする。このときの第2ノードND2の電位変化分をΔV(=電位補正値、負帰還量)とする。移動度補正処理を実行するための所定期間は、表示装置の設計の際、設計値として予め決定しておけばよい。尚、この際には、好ましくは、式(2A)を満足するように移動度補正期間を決定する。こうすることで、移動度補正期間に発光部ELPが発光することはない。

[Mobility correction process]

While supplying the video signal V sig to one end of the holding capacitor C cs via the write transistor TR W (that is, while writing the drive voltage corresponding to the video signal V sig to the holding capacitor C cs ), via the drive transistor TR D Current is supplied to the holding capacitor C cs . For example, the drive is performed in a state where the video signal V sig is supplied from the video signal line DTL to the first node ND 1 via the write transistor TR W turned on by the write drive pulse WS from the write scanning line WSL. Power is supplied to the transistor TR D and the drain current I ds flows to change the potential of the second node ND 2 , and after a predetermined period, the write transistor TR W is turned off. The change in potential of the second node ND 2 at this time is represented by ΔV (= potential correction value, negative feedback amount). The predetermined period for executing the mobility correction process may be determined in advance as a design value when designing the display device. In this case, the mobility correction period is preferably determined so as to satisfy the formula (2A). By doing so, the light emitting unit ELP does not emit light during the mobility correction period.

(Vofs−Vth+ΔV)<(VthEL+Vcath) (2A) (V ofs −V th + ΔV) <(V thEL + V cath ) (2A)

駆動トランジスタTRDの移動度μの値が大きい場合は電位補正値ΔVは大きくなり、移動度μの値が小さい場合は電位補正値ΔVは小さくなる。このときの駆動トランジスタTRDのゲート・ソース間電圧Vgs(つまり第1ノードND1と第2ノードND2との電位差)は、式(4)で表すことができる。ゲート・ソース間電圧Vgsは発光時の輝度を規定するが、電位補正値ΔVは駆動トランジスタTRDのドレイン電流Idsに比例し、ドレイン電流Idsは移動度μに比例するので、結果的には、移動度μが大きいほど電位補正値ΔVが大きくなるので、画素回路10ごとの移動度μのばらつきを取り除くことができる。

When the value of mobility μ of the driving transistor TR D is large, the potential correction value ΔV is large, and when the value of mobility μ is small, the potential correction value ΔV is small. The gate-source voltage V gs (that is, the potential difference between the first node ND 1 and the second node ND 2 ) of the driving transistor TR D at this time can be expressed by Expression (4). Although the gate-source voltage V gs defines the luminance at the time of light emission, the potential correction value ΔV is proportional to the drain current I ds of the driving transistor TR D and the drain current I ds is proportional to the mobility μ. Since the potential correction value ΔV increases as the mobility μ increases, variations in the mobility μ for each

Vgs≒Vsig−(Vofs−Vth)−ΔV (4) V gs ≈ V sig − (V ofs −V th ) −ΔV (4)

〔発光工程〕

書込走査線WSLからの書込駆動パルスWSにより書込トランジスタTRWをオフ状態とすることにより第1ノードND1を浮遊状態とし、駆動トランジスタTRDに電源を供給して駆動トランジスタTRDを介して、駆動トランジスタTRDのゲート・ソース間電圧Vgs(第1ノードND1と第2ノードND2との間の電位差)に応じた電流Idsを発光部ELPに流すことにより発光部ELPを駆動して発光させる。

[Light emission process]

The first node ND 1 in a floating state by the OFF state of the writing transistor TR W by the write drive pulse WS from the write scanning line WSL, a driving transistor TR D to supply power to the driving transistor TR D The current I ds corresponding to the gate-source voltage V gs (potential difference between the first node ND 1 and the second node ND 2 ) of the driving transistor TR D is caused to flow through the light emitting unit ELP. To emit light.

〔駆動回路の構成による相違点〕

ここで、それぞれ典型的な、5Tr/1C型、4Tr/1C型、3Tr/1C型、2Tr/1C型での相違点は以下の通りである。5Tr/1C型では、駆動トランジスタTRDの電源側の主電極端と電源回路(電源部)との間に接続された第1トランジスタTR1(発光制御トランジスタ)と、第2ノード初期化電圧を印加する第2トランジスタTR2と、第1ノード初期化電圧を印加する第3トランジスタTR3とを設ける。第1トランジスタTR1、第2トランジスタTR2、第3トランジスタTR3は何れもスイッチングトランジスタである。第1トランジスタTR1は、発光期間にオン状態としておき、オフ状態にして非発光期間に入り、その後の閾値補正期間に一度オン状態にし、更に移動度補正期間以降(次の発光期間も)オン状態とする。第2トランジスタTR2は、第2ノードの初期化期間にのみオン状態としそれ以外はオフ状態とする。第3トランジスタTR3は、第1ノードの初期化期間から閾値補正期間に亘ってのみオン状態としそれ以外はオフ状態とする。書込トランジスタTRWは、映像信号書込み処理期間から移動度補正処理期間に亘ってオン状態とされ、それ以外はオフ状態とされる。

[Differences due to drive circuit configuration]

Here, the differences between the typical 5Tr / 1C type, 4Tr / 1C type, 3Tr / 1C type, and 2Tr / 1C type are as follows. In the 5Tr / 1C type, a first transistor TR 1 (light emission control transistor) connected between the main electrode end on the power supply side of the drive transistor TR D and the power supply circuit (power supply unit), and a second node initialization voltage A second transistor TR 2 to be applied and a third transistor TR 3 to apply a first node initialization voltage are provided. The first transistor TR 1 , the second transistor TR 2 , and the third transistor TR 3 are all switching transistors. The first transistor TR 1 is turned on during the light emission period, is turned off, enters the non-light emission period, is turned on once during the subsequent threshold correction period, and is turned on after the mobility correction period (also in the next light emission period). State. The second transistor TR 2 is turned on only during the initialization period of the second node, and is turned off otherwise. The third transistor TR 3 is turned on only during the threshold correction period from the initialization period of the first node, and is otherwise turned off. The writing transistor TR W is turned on from the video signal writing processing period to the mobility correction processing period, and is otherwise turned off.

4Tr/1C型では、5Tr/1C型から、第1ノード初期化電圧を印加する第3トランジスタTR3が省略され、第1ノード初期化電圧は映像信号線DTLから映像信号Vsigと時分割で供給される。第1ノードの初期化期間に第1ノード初期化電圧を映像信号線DTLから第1ノードに供給するべく、書込トランジスタTRWは第1ノードの初期化期間にもオン状態とされる。典型的には、書込トランジスタTRWは、第1ノードの初期化期間から移動度補正処理期間に亘ってオン状態とされ、それ以外はオフ状態とされる。 In the 4Tr / 1C type, the third transistor TR 3 for applying the first node initialization voltage is omitted from the 5Tr / 1C type, and the first node initialization voltage is time-divisionally divided from the video signal line DTL to the video signal V sig. Supplied. In order to supply the first node initialization voltage from the video signal line DTL to the first node during the initialization period of the first node, the write transistor TR W is also turned on during the initialization period of the first node. Typically, the write transistor TR W is turned on from the initializing period of the first node to the mobility correction processing period, and is otherwise turned off.

3Tr/1C型では、5Tr/1C型から、第2トランジスタTR2と第3トランジスタTR3が省略され、第1ノード初期化電圧及び第2ノード初期化電圧は映像信号線DTLから映像信号Vsigと時分割で供給される。映像信号線DTLの電位は、第2ノードの初期化期間に第2ノードを第2ノード初期化電圧に設定し、その後の第1ノードの初期化期間に第1ノードを第1ノード初期化電圧に設定するべく、第2ノード初期化電圧と対応した電圧Vofs_Hを供給しその後に第1ノード初期化電圧Vofs_L(=Vofs)にする。そして、これと対応して、書込トランジスタTRWは第1ノードの初期化期間及び第2ノードの初期化期間にもオン状態とされる。典型的には、書込トランジスタTRWは、第2ノードの初期化期間から移動度補正処理期間に亘ってオン状態とされ、それ以外はオフ状態とされる。 In the 3Tr / 1C type, the second transistor TR 2 and the third transistor TR 3 are omitted from the 5Tr / 1C type, and the first node initialization voltage and the second node initialization voltage are supplied from the video signal line DTL to the video signal V sig. And supplied in a time-sharing manner. The potential of the video signal line DTL is set such that the second node is set to the second node initialization voltage during the initialization period of the second node, and the first node is set to the first node initialization voltage during the subsequent initialization period of the first node. in order to set, to the first node initialization voltage V Ofs_L thereafter supplies a voltage V Ofs_H corresponding to the second node initialization voltage (= V ofs). Correspondingly, the write transistor TR W is also turned on in the initializing period of the first node and the initializing period of the second node. Typically, the write transistor TR W is turned on from the initialization period of the second node to the mobility correction processing period, and is otherwise turned off.

因みに、3Tr/1C型では、映像信号線DTLを利用して第2ノードND2の電位を変化させる。このため、保持容量Ccsの静電容量Ccsを、設計上、他の駆動回路よりも大きい値(例えば、静電容量Ccsを静電容量Celの約1/4〜1/3程度)に設定する。したがって、他の駆動回路よりも、第1ノードND1の電位変化により生ずる第2ノードND2の電位変化の程度が大きい点を考慮する。 Incidentally, in the 3Tr / 1C type, the potential of the second node ND 2 is changed using the video signal line DTL. Therefore, the capacitance C cs of the storage capacitor C cs, design, larger than the other driving circuits (for example, about 1 / 4-1 / 3 of about capacitance C cs of the electrostatic capacitance C el ). Therefore, it is considered that the potential change of the second node ND 2 caused by the potential change of the first node ND 1 is larger than that of the other driving circuits.

2Tr/1C型では、5Tr/1C型から、第1トランジスタTR1と第2トランジスタTR2と第3トランジスタTR3が省略され、第1ノード初期化電圧は映像信号線DTLから映像信号Vsigと時分割で供給され、第2ノード初期化電圧は駆動トランジスタTRDの電源側の主電極端を、第1電位Vcc_H(=5Tr/1C型のVcc)と第2電位Vcc_L(=5Tr/1C型のVini)でパルス駆動することで与えられる。駆動トランジスタTRDの電源側の主電極端は、発光期間に第1電位Vcc_Hにされ、第2電位Vcc_Lにされることで非発光期間に入り、その後の閾値補正期間以降(次の発光期間も)に第1電位Vcc_Hにされる。第1ノードの初期化期間に第1ノード初期化電圧を映像信号線DTLから第1ノードに供給するべく、書込トランジスタTRWは第1ノードの初期化期間にもオン状態とされる。典型的には、書込トランジスタTRWは、第1ノードの初期化期間から移動度補正処理期間に亘ってオン状態とされ、それ以外はオフ状態とされる。 In the 2Tr / 1C type, the first transistor TR 1 , the second transistor TR 2, and the third transistor TR 3 are omitted from the 5Tr / 1C type, and the first node initialization voltage is obtained from the video signal line DTL and the video signal V sig . The second node initialization voltage is supplied in a time-sharing manner, and the second node initialization voltage is applied to the main electrode end on the power source side of the driving transistor TR D by the first potential V cc — H (= 5Tr / 1C type V cc ) and the second potential V cc — L (= 5Tr / 1C type V ini ). The main electrode end on the power supply side of the driving transistor TR D is set to the first potential V cc_H during the light emission period and enters the non-light emission period by being set to the second potential V cc_L , and after the subsequent threshold correction period (next light emission) The first potential V cc — H is also set during the period). In order to supply the first node initialization voltage from the video signal line DTL to the first node during the initialization period of the first node, the write transistor TR W is also turned on during the initialization period of the first node. Typically, the write transistor TR W is turned on from the initializing period of the first node to the mobility correction processing period, and is otherwise turned off.

尚、ここでは、駆動トランジスタの特性ばらつきとして、閾値電圧及び移動度の双方について補正処理を行なう場合で説明したが、何れか一方のみについて補正処理を行なうようにしてもよい。 Here, the case where correction processing is performed for both the threshold voltage and the mobility as the characteristic variation of the drive transistor has been described, but correction processing may be performed for only one of them.

以上、好ましい例に基づき説明したが、これらの例に限定されるものではない。各例において説明した表示装置、表示素子、駆動回路を構成する各種の構成要素の構成、構造、発光部の駆動方法における工程は例示であり、適宜、変更することができる。 Although the description has been given based on the preferred examples, the invention is not limited to these examples. The structure and structure of various components constituting the display device, the display element, and the drive circuit described in each example, and the steps in the method for driving the light emitting unit are examples, and can be changed as appropriate.

又、5Tr/1C型、4Tr/1C型、及び、3Tr/1C型の動作においては、書込み処理と移動度補正を別個に行なってもよいし、2Tr/1C型と同様に、書込み処理において移動度補正処理を併せて行なってもよい。具体的には、第1トランジスタTR1(発光制御トランジスタ)をオン状態とした状態で、書込トランジスタTRWを介して、データ線DTLから映像信号VSigを第1ノードに印加すればよい。 In the 5Tr / 1C type, 4Tr / 1C type, and 3Tr / 1C type operations, the writing process and the mobility correction may be performed separately, and the movement is performed in the writing process as in the case of the 2Tr / 1C type. The degree correction process may be performed together. Specifically, the video signal V Sig may be applied from the data line DTL to the first node via the write transistor TR W with the first transistor TR 1 (light emission control transistor) turned on.

<具体的な適用例>

以下に、駆動パルスの形状(幅、変化特性等)がばらつくことに起因する表示むら現象が抑制する本実施形態の技術の具体的な適用例について説明する。尚、アクティブマトリクス型の有機ELパネルを使用する表示装置においては、例えば、パネル両側或いは片側に配置されている垂直走査部によってトランジスタの制御入力端に供給する各種のゲート信号(制御パルス)を作り、画素回路10へ当該信号を印加する。更にはこのような有機ELパネルを使用する表示装置においては、素子数削減及び高精細化のため、2Tr/1C型の画素回路10を用いることがある。この点を勘案して、以下では、代表的に2Tr/1C型の構成への適用例で説明する。

<Specific application examples>

Hereinafter, a specific application example of the technique of the present embodiment that suppresses the display unevenness phenomenon caused by the variation in the shape (width, change characteristics, etc.) of the drive pulse will be described. In a display device using an active matrix organic EL panel, for example, various gate signals (control pulses) to be supplied to the control input terminal of the transistor are generated by vertical scanning units arranged on both sides or one side of the panel. Then, the signal is applied to the

[画素回路]

図4及び図5は、画素回路10と、当該画素回路10を備えた表示装置の一形態を示す図である。図4は基本構成(1画素分)を示し、図5は具体的な構成(表示装置の全体)を示す。尚、表示パネル部100の基板101上において画素回路10の周辺部に設けられた垂直駆動部103と水平駆動部106も合わせて示している。

[Pixel circuit]

4 and 5 are diagrams illustrating one mode of the

表示装置1は、映像信号Vsig(詳しくは信号振幅ΔVin)に基づいて画素回路10内の電気光学素子(本例では発光部ELPとして有機EL素子127を使用する)を発光させる。このため、表示装置1は、画素アレイ部102に行列状に配される画素回路10内に、少なくとも、駆動電流を生成する駆動トランジスタ121(駆動トランジスタTRD)、駆動トランジスタ121の制御入力端(ゲート端が典型例)と出力端(ソース端が典型例)の間に接続された保持容量120(保持容量Ccs)、駆動トランジスタ121の出力端に接続された電気光学素子の一例である有機EL素子127(発光部ELP)、及び、保持容量120に信号振幅ΔVinに応じた情報を書き込むサンプリングトランジスタ125(書込トランジスタTRW)を備える。この画素回路10においては、保持容量120に保持された情報に基づく駆動電流Idsを駆動トランジスタ121で生成して電気光学素子の一例である有機EL素子127に流すことで有機EL素子127を発光させる。

The

サンプリングトランジスタ125で保持容量120に信号振幅ΔVinに応じた情報を書き込むので、サンプリングトランジスタ125は、その入力端(ソース端もしくはドレイン端の一方)に信号電位(Vofs+ΔVin)を取り込み、その出力端(ソース端もしくはドレイン端の他方)に接続された保持容量120に信号振幅ΔVinに応じた情報を書き込む。もちろん、サンプリングトランジスタ125の出力端は、駆動トランジスタ121の制御入力端にも接続されている。

Since the

尚、ここで示した画素回路10の接続構成は、最も基本的な構成を示したもので、画素回路10は、少なくとも前述の各構成要素を含むものであればよく、これらの構成要素以外(つまり他の構成要素)が含まれていてもよい。又、「接続」は、直接に接続されている場合に限らず、他の構成要素を介在して接続されている場合でもよい。例えば、接続間には、必要に応じて更に、スイッチング用のトランジスタや、ある機能を持った機能部等を介在させる等の変更が加えられることがある。典型的には、表示期間(換言すれば非発光時間)を動的に制御するためにスイッチング用のトランジスタを、駆動トランジスタ121の出力端と電気光学素子(有機EL素子127)と間に、もしくは駆動トランジスタ121の電源供給端(ドレイン端が典型例)と電源供給用の配線である電源線PWL(本例では電源供給線105DSL)との間に配することがある。このような変形態様の画素回路であっても、実施例1(或いはその他の実施例)で説明する構成や作用を実現し得るものである限り、それらの変形態様も、本開示に係る表示装置の一実施形態を実現する画素回路10である。

Note that the connection configuration of the

又、画素回路10を駆動するための周辺部には、例えば、サンプリングトランジスタ125を水平周期で順次制御することで画素回路10を線順次走査して、1行分の各保持容量120に映像信号Vsigの信号振幅ΔVinに応じた情報を書き込む書込走査部104、及び、書込走査部104での線順次走査に合わせて1行分の各駆動トランジスタ121の電源供給端に印加される電源供給を制御するための走査駆動パルス(電源駆動パルスDSL)を出力する駆動走査部105を具備する制御部109を設ける。又、制御部109には、書込走査部104での線順次走査に合わせて各水平周期内で基準電位(Vofs)と信号電位(Vofs+ΔVin)で切り替わる映像信号Vsigがサンプリングトランジスタ125に供給されるように制御する水平駆動部106を設ける。

Further, in the peripheral portion for driving the

制御部109は、好ましくは、保持容量120に信号振幅ΔVinに対応する情報が書き込まれた時点でサンプリングトランジスタ125を非導通状態にして駆動トランジスタ121の制御入力端への映像信号Vsigの供給を停止させ、駆動トランジスタ121の出力端の電位変動に制御入力端の電位が連動するブートストラップ動作を行なうように制御するのがよい。制御部109は、好ましくは、ブートストラップ動作を、サンプリング動作の終了後の発光開始の初期でも実行するようにする。即ち、信号電位(Vofs+ΔVin)がサンプリングトランジスタ125に供給されている状態でサンプリングトランジスタ125を導通状態にした後にサンプリングトランジスタ125を非導通状態にすることで、駆動トランジスタ121の制御入力端と出力端の電位差が一定に維持されるようにする。

The

又、制御部109は、好ましくはブートストラップ動作を、発光期間において電気光学素子(有機EL素子127)の経時変動補正動作を実現するように制御する。このため、制御部109は、保持容量120に保持された情報に基づく駆動電流Idsが電気光学素子(有機EL素子127)に流れている期間は継続的にサンプリングトランジスタ125を非導通状態にしておくことで、制御入力端と出力端の電圧を一定に維持可能にして電気光学素子の経時変動補正動作を実現するとよい。発光時における保持容量120のブートストラップ動作により有機EL素子127の電流−電圧特性が経時変動しても駆動トランジスタ121の制御入力端と出力端の電位差をブートストラップした保持容量120により一定に保つことで、常に一定の発光輝度を保つようにする。又、好ましくは、制御部109は、基準電位(=第1ノード初期化電圧Vofs)がサンプリングトランジスタ125の入力端(ソース端が典型例)に供給されている時間帯でサンプリングトランジスタ125を導通させることで駆動トランジスタ121の閾値電圧Vthに対応する電圧を保持容量120に保持するための閾値補正動作を行なうように制御する。

Further, the

この閾値補正動作は、必要に応じて、信号振幅ΔVinに対応する情報の保持容量120への書込みに先行する複数の水平周期で繰り返し実行するとよい。ここで「必要に応じて」とは、1水平周期内の閾値補正期間では駆動トランジスタ121の閾値電圧に相当する電圧を十分に保持容量120へ保持させることができない場合を意味する。閾値補正動作の複数回の実行により、確実に駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持させる。閾値補正を複数回行なう処理を分割閾値補正とも称する。

This threshold value correcting operation may be repeatedly executed at a plurality of horizontal periods preceding the writing of information corresponding to the signal amplitude ΔV in to the

又、更に好ましくは、制御部109は、閾値補正動作に先立って、サンプリングトランジスタ125の入力端に基準電位(Vofs)が供給されている時間帯でサンプリングトランジスタ125を導通させて閾値補正用の準備動作(放電動作や初期化動作)を実行するように制御する。閾値補正動作前に駆動トランジスタ121の制御入力端と出力端の電位を初期化しておく。より詳しくは、制御入力端と出力端と間に保持容量120を接続しておくことで、保持容量120の両端の電位差が閾値電圧Vth以上になるように設定する。

More preferably, prior to the threshold value correcting operation, the

尚、2Tr/1C駆動構成における閾値補正に当たっては、制御部109には、書込走査部104での線順次走査に合わせて1行分の各画素回路10に、駆動電流Idsを電気光学素子(有機EL素子127)に流すために使用される第1電位Vcc_Hと第1電位Vcc_Hとは異なる第2電位Vcc_Lとを切り替えて出力する駆動走査部105を設け、駆動トランジスタ121の電源供給端子に第1電位Vcc_Hに対応する電圧が供給され、かつサンプリングトランジスタ121に信号電位(Vofs+ΔVin)が供給されている時間帯でサンプリングトランジスタ125を導通させることで閾値補正動作を行なうように制御するのがよい。又、2TR駆動構成における閾値補正の準備動作に当たっては、駆動トランジスタ121の電源供給端に第2電位Vcc_L(=第2ノード初期化電圧Vini)に対応する電圧が供給され、かつサンプリングトランジスタ125に基準電位(Vofs)が供給されている時間帯でサンプリングトランジスタ125を導通させて、駆動トランジスタ121の制御入力端(つまり第1ノードND1)の電位を基準電位(Vofs)に、又出力端(つまり第2ノードND2)の電位を第2電位Vcc_Lに初期化するのがよい。

In the threshold correction in the 2Tr / 1C driving configuration, the

更に好ましくは、制御部109は、閾値補正動作の後、駆動トランジスタ121に第1電位Vcc_Hに対応する電圧が供給され、サンプリングトランジスタ125に信号電位(Vofs+ΔVin)が供給されている時間帯でサンプリングトランジスタ125を導通させることで保持容量120に信号振幅ΔVinの情報を書き込む際、駆動トランジスタ121の移動度μに対する補正分を保持容量120に書き込まれる情報に加えるように制御する。この際には、サンプリングトランジスタ125に信号電位(Vofs+ΔVin)が供給されている時間帯内の所定位置で、その時間帯より短い期間だけサンプリングトランジスタ125を導通させるとよい。以下2Tr/1C駆動構成での画素回路10の一例について具体的に説明する。

More preferably, after the threshold correction operation, the

画素回路10は、基本的にnチャネル型の薄膜電界効果トランジスタで駆動トランジスタが構成されている。又、有機EL素子の経時劣化による当該有機EL素子への駆動電流Idsの変動を抑制するための回路、即ち電気光学素子の一例である有機EL素子の電流−電圧特性の変化を補正して駆動電流Idsを一定に維持する駆動信号一定化回路(その1)を備え、又駆動トランジスタの特性変動(閾値電圧ばらつきや移動度ばらつき)による駆動電流変動を防ぐ閾値補正機能や移動度補正機能を実現して駆動電流Idsを一定に維持する駆動方式を採用した点に特徴を有する。

The

駆動トランジスタ121の特性変動(例えば閾値電圧や移動度等のばらつきや変動)による駆動電流Idsに与える影響を抑制する方法としては、2TR構成の駆動回路をそのまま駆動信号一定化回路(その1)として採用しつつ、各トランジスタ(駆動トランジスタ121及びサンプリングトランジスタ125)の駆動タイミングを工夫することで対処する。画素回路10は、2TR駆動の構成であり、素子数や配線数が少ないため、高精細化が可能であることに加えて、映像信号Vsigの劣化なくサンプリングできるため、良好な画質を得ることができる。

As a method of suppressing the influence on the drive current I ds due to the characteristic variation of the drive transistor 121 (for example, variation or fluctuation in threshold voltage, mobility, etc.), the drive circuit of the 2TR configuration is used as it is as a drive signal stabilization circuit (part 1). This is dealt with by devising the drive timing of each transistor (

又、画素回路10は、保持容量120の接続態様に特徴を有し、有機EL素子127の経時劣化による駆動電流変動を防ぐ回路として、駆動信号一定化回路(その2)の一例であるブートストラップ回路を構成している。有機EL素子の電流−電圧特性に経時変化があった場合でも駆動電流を一定にする(駆動電流変動を防ぐ)ブートストラップ機能を実現する駆動信号一定化回路(その2)を備えた点に特徴を有する。

The

駆動トランジスタを始めとする各トランジスタとしてはFET(電界効果トランジスタ)を使用する。この場合、駆動トランジスタについては、ゲート端を制御入力端として取り扱い、ソース端及びドレイン端の何れか一方(ここではソース端とする)を出力端として取り扱い、他方を電源供給端(ここではドレイン端とする)として取り扱う。 FETs (field effect transistors) are used as the transistors including the driving transistor. In this case, for the drive transistor, the gate end is handled as a control input end, either the source end or the drain end (here, the source end) is handled as the output end, and the other is the power supply end (here the drain end). ).

具体的には図4及び図5に示すように、画素回路10は、それぞれnチャネル型の駆動トランジスタ121及びサンプリングトランジスタ125と、電流が流れることで発光する電気光学素子の一例である有機EL素子127とを有する。一般に、有機EL素子127は整流性があるためダイオードの記号で表している。尚、有機EL素子127には、寄生容量Celが存在する。図では、この寄生容量Celを有機EL素子127(ダイオード状のもの)と並列に示す。

Specifically, as illustrated in FIGS. 4 and 5, the

駆動トランジスタ121は、ドレイン端Dが第1電位Vcc_H或いは第2電位Vcc_Lを供給する電源供給線105DSLに接続され、ソース端Sが、有機EL素子127のアノード端Aに接続され(その接続点は第2ノードND2でありノードND122とする)、有機EL素子127のカソード端Kが基準電位を供給する全画素回路10共通のカソード配線cath(電位はカソード電位Vcath、例えばGND)に接続されている。尚、カソード配線cathは、それ用の単一層の配線(上層配線)のみとしてもよいし、例えばアノード用の配線が形成されるアノード層に、カソード配線用の補助配線を設けてカソード配線の抵抗値を低減するようにしてもよい。この補助配線は、画素アレイ部102(表示エリア)内に格子状又は列又は行状に配線され、上層配線と同電位で固定電位である。

The

サンプリングトランジスタ125は、ゲート端Gが書込走査部104からの書込走査線104WSに接続され、ドレイン端Dが映像信号線106HS(映像信号線DTL)に接続され、ソース端Sが駆動トランジスタ121のゲート端Gに接続されている(その接続点は第1ノードND1でありノードND121とする)。サンプリングトランジスタ125のゲート端Gには、書込走査部104からアクティブHの書込駆動パルスWSが供給される。サンプリングトランジスタ125は、ソース端Sとドレイン端Dとを逆転させた接続態様とすることもできる。

The

駆動トランジスタ121のドレイン端Dは、電源スキャナとして機能する駆動走査部105からの電源供給線105DSLに接続されている。電源供給線105DSLは、この電源供給線105DSLそのものが、駆動トランジスタ121に対しての電源供給能力を備える点に特徴を有する。駆動走査部105は、駆動トランジスタ121のドレイン端Dに対して、それぞれ電源電圧に相当する高電圧側の第1電位Vcc_Hと閾値補正に先立つ準備動作に利用される低電圧側の第2電位Vcc_L(初期化電圧もしくはイニシャル電圧とも称される)とを切り替えて供給する。

The drain terminal D of the

駆動トランジスタ121のドレイン端D側(電源回路側)を第1電位Vcc_Hと第2電位Vcc_Lの2値をとる電源駆動パルスDSLで駆動することで、閾値補正に先立つ準備動作を行なうことを可能にしている。第2電位Vcc_Lとしては、映像信号線106HSにおける映像信号Vsigの基準電位(Vofs)より十分低い電位とする。具体的には、駆動トランジスタ121のゲート・ソース間電圧Vgs(ゲート電位Vgとソース電位Vsの差)が駆動トランジスタ121の閾値電圧Vthより大きくなるように、電源供給線105DSLの低電位側の第2電位Vcc_Lを設定する。尚、基準電位(Vofs)は、閾値補正動作に先立つ初期化動作に利用するとともに映像信号線106HSを予めプリチャージにしておくためにも利用する。

By driving the drain end D side (power supply circuit side) of the

このような画素回路10では、有機EL素子127を駆動するときには、駆動トランジスタ121のドレイン端Dに第1電位Vcc_Hが供給され、ソース端Sが有機EL素子127のアノード端A側に接続されることで、全体としてソースフォロワ回路を形成するようになっている。

In such a

このような画素回路10を採用する場合、駆動トランジスタ121の他に走査用に1つのスイッチングトランジスタ(サンプリングトランジスタ125)を使用する2TR駆動の構成を採るとともに、各スイッチングトランジスタを制御する電源駆動パルスDSL及び書込駆動パルスWSのオン/オフタイミングの設定により、有機EL素子127の経時劣化や駆動トランジスタ121の特性変動(例えば閾値電圧や移動度等のばらつきや変動)による駆動電流Idsに与える影響を防ぐ。

When such a

[画素回路の動作]

図6は、画素回路10に関する駆動タイミングの一例として、線順次方式で信号振幅Vinの情報を保持容量120に書き込む際の動作を説明するタイミングチャート(理想状態)である。図7は、図6に示したタイミングチャートの主要な期間における等価回路と動作状態を説明する図である。図6においては、時間軸を共通にして、書込走査線104WSの電位変化、電源供給線105DSLの電位変化、映像信号線106HSの電位変化を表してある。これらの電位変化と並行に、駆動トランジスタ121のゲート電位Vg及びソース電位Vsの変化も表してある。基本的には、書込走査線104WSや電源供給線105DSLの1行ごとに、1水平走査期間だけ遅れて同じような駆動を行なう。

[Operation of pixel circuit]

Figure 6 is an example of a driving timing regarding the

図6中の信号のように各パルスのタイミングによって有機EL素子127に流れる電流値をコントロールする。図6のタイミング例では、電源駆動パルスDSLを第2電位Vcc_Lとすることで消光及びノードND122を初期化した後に、第1ノード初期化電圧Vofsを映像信号線106HSに印加している際にサンプリングトランジスタ125をオン状態としてノードND121を初期化し、その状態で電源駆動パルスDSLを第1電位Vcc_Hとすることで閾値補正を行なう。その後、サンプリングトランジスタ125をオフ状態とし、映像信号線106HSに映像信号Vsigを印加する。その状態でサンプリングトランジスタ125をオン状態とすることにより信号を書き込むと同時に移動度補正を行なう。信号を書き込んだ後、サンプリングトランジスタ125をオフ状態にすると発光を開始する。このように移動度補正や閾値補正等、パルスの位相差によって駆動をコントロールする。

The value of the current flowing through the

以下、閾値補正及び移動度補正に着目して動作を詳しく説明する。画素回路10において、駆動タイミングとしては、先ず、サンプリングトランジスタ125は、書込走査線104WSから供給された書込駆動パルスWSに応じて導通し、映像信号線106HSから供給された映像信号Vsigをサンプリングして保持容量120に保持する。最初に、以下では、説明や理解を容易にするため、特段の断りのない限り、書込みゲインが1(理想値)であると仮定して、保持容量120に信号振幅Vinの情報を、書き込む、保持する、あるいはサンプリングする等と簡潔に記して説明する。書込みゲインが1未満の場合、保持容量120には信号振幅Vinの大きさそのものではなく、信号振幅Vinの大きさに対応するゲイン倍された情報が保持されることになる。

Hereinafter, the operation will be described in detail focusing on threshold correction and mobility correction. In the

画素回路10に対する駆動タイミングは、映像信号Vsigの信号振幅Vinの情報を保持容量120に書き込む際に、順次走査の観点からは、1行分の映像信号を同時に各列の映像信号線106HSに伝達する線順次駆動を行なう。特に、2TR構成の画素回路10における駆動タイミングでの閾値補正と移動度補正を行なう際の基本的な考え方においては、先ず、映像信号Vsigを基準電位(Vofs)と信号電位(Vofs+Vin)とを1H期間内において時分割で有するものとする。具体的には、映像信号Vsigが非有効期間である基準電位(Vofs)にある期間を1水平期間の前半部とし、有効期間である信号電位(Vsig=Vofs+Vin)にある期間を1水平期間の後半部とする。1水平期間を前半部と後半部に分ける際は、典型的にはほぼ1/2期間ずつ分けるがこのことは必須でなく、前半部よりも後半部の方をより長くしてもよいし、逆に、前半部よりも後半部の方をより短くしてもよい。

The drive timing for the

信号書込みに用いる書込駆動パルスWSを閾値補正や移動度補正にも用いることとし、1H期間内に2回、書込駆動パルスWSをアクティブにしてサンプリングトランジスタ125をオンする。そして、1回目のオンタイミングにて閾値補正を行ない、2回目のオンタイミングにて信号電圧書込みと移動度補正を同時に行なう。その後、駆動トランジスタ121は、第1電位(高電位側)にある電源供給線105DSLから電流の供給を受け保持容量120に保持された信号電位(映像信号Vsigの有効期間の電位に対応する電位)に応じて駆動電流Idsを有機EL素子127に流す。尚、1H期間内に2回、書込駆動パルスWSをアクティブにするのではなく、サンプリングトランジスタ125のオン状態を維持したまま、映像信号線106HSの電位を、有機EL素子127における輝度を制御するための信号電位(=Vofs+Vin)としてもよい。

The writing drive pulse WS used for signal writing is also used for threshold correction and mobility correction, and the

例えば、有機EL素子127の発光状態は、電源供給線105DSLが第1電位Vcc_Hであり、サンプリングトランジスタ125がオフ状態である(図6(A)を参照)。このとき、駆動トランジスタ121は飽和領域で動作するように設定されているため、有機EL素子127に流れる電流Idsは駆動トランジスタ121のゲート・ソース間電圧Vgs(ノードND121とノードND122との間の電圧)に応じて決まる式(1)に示される値となる。その後、垂直駆動部103は、電源供給線105DSLが第1電位Vcc_Hにありかつ映像信号線106HSが映像信号Vsigの非有効期間である基準電位(Vofs)にある時間帯でサンプリングトランジスタ125を導通させる制御信号として書込駆動パルスWSを出力して、駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持しておく(図6(D)を参照)。この動作が閾値補正機能を実現する。この閾値補正機能により、画素回路10ごとにばらつく駆動トランジスタ121の閾値電圧Vthの影響をキャンセルすることができる。

For example, the light emission state of the

垂直駆動部103は、信号振幅Vinのサンプリングに先行する複数の水平期間で閾値補正動作を繰り返し実行して確実に駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持するようにするのがよい。閾値補正動作を複数回実行することで、十分に長い書込み時間を確保する。こうすることで、駆動トランジスタ121の閾値電圧Vthに相当する電圧を確実に保持容量120に予め保持することができる。

The

保持された閾値電圧Vthに相当する電圧は駆動トランジスタ121の閾値電圧Vthのキャンセルに用いられる。したがって、画素回路10ごとに駆動トランジスタ121の閾値電圧Vthがばらついていても、画素回路10ごとに完全にキャンセルされるため、画像のユニフォーミティすなわち表示装置の画面全体に亘る発光輝度の均一性が高まる。特に信号電位が低階調のときに現れがちな輝度むらを防ぐことができる。

Voltage corresponding to the held threshold voltage V th is used to cancel the threshold voltage V th of the

好ましくは、垂直駆動部103は、閾値補正動作に先立って、電源供給線105DSLが第2電位にありかつ映像信号線106HSが映像信号Vsigの非有効期間である基準電位(Vofs)にある時間帯で、書込駆動パルスWSをアクティブ(本例ではHレベル)にしてサンプリングトランジスタ125を導通させ、その後に書込駆動パルスWSをアクティブHにしたままで電源供給線105DSLを第1電位に設定する。

Preferably, prior to the threshold correction operation, the