JP2010114711A - Power-amplifying device - Google Patents

Power-amplifying device Download PDFInfo

- Publication number

- JP2010114711A JP2010114711A JP2008286223A JP2008286223A JP2010114711A JP 2010114711 A JP2010114711 A JP 2010114711A JP 2008286223 A JP2008286223 A JP 2008286223A JP 2008286223 A JP2008286223 A JP 2008286223A JP 2010114711 A JP2010114711 A JP 2010114711A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- pulse

- modulation

- circuit

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Landscapes

- Particle Formation And Scattering Control In Inkjet Printers (AREA)

- Amplifiers (AREA)

Abstract

Description

本発明は、例えばアクチュエータを駆動するための駆動信号の基準となる駆動波形信号をパルス変調し、その変調信号を電力増幅して駆動信号として出力する電力増幅装置に関するものである。 The present invention relates to a power amplifying apparatus that pulse-modulates a drive waveform signal that becomes a reference of a drive signal for driving an actuator, for example, and amplifies the modulated signal to output it as a drive signal.

プッシュプル接続されたトランジスタ対をリニア駆動するアナログ電力増幅器に比べて、プッシュプル接続されたスイッチング素子をスイッチ動作、つまりデジタル駆動させて電力増幅するデジタル電力増幅器、所謂D級アンプは、効率に優れ、広い範囲で使用されている。例えば、このデジタル電力増幅器を用いて駆動信号を出力する場合、駆動信号の基準となる駆動波形信号の振幅値を変調回路でパルスデューティからなる変調信号にパルス変調し、その変調信号をデジタル電力増幅器で電力増幅し、その電力増幅された電力増幅変調信号を平滑フィルタで平滑化して、駆動信号として出力する。平滑フィルタは、パルス変調の周波数成分を減衰する。パルス変調には、周知のパルス幅変調を始めとして、種々の変調方法があるが、下記特許文献1に記載される電力増幅装置では、ΔΣ変調方式によるパルス密度変調、所謂PDM(Pulse Density Modulation)を用いてパルス変調を行っている。周知のように、パルス密度変調を用いると、パルス幅変調に比して、少し波形精度が高くなる。

しかしながら、パルス密度変調では、パルスデューティ比が50%付近で、変調信号の周波数が高くなるため、高速スイッチングによって駆動信号に歪みが生じる恐れがある上に、シュートスルーなどのスイッチングロスの増大にも繋がる。

本発明は、これらの諸問題に着目して開発されたものであり、駆動信号の歪みを抑制防止すると共に、スイッチングロスも低減可能な電力増幅装置を提供することを目的とするものである。

However, in pulse density modulation, the frequency of the modulation signal becomes high when the pulse duty ratio is around 50%, so that the drive signal may be distorted by high-speed switching, and the switching loss such as shoot-through may increase. Connected.

The present invention has been developed by paying attention to these problems, and an object of the present invention is to provide a power amplifying device that can suppress and prevent distortion of a drive signal and reduce switching loss.

上記諸問題を解決するため、本発明の電力増幅装置は、出力する駆動信号の基準となる駆動波形信号の振幅値をパルスデューティからなる変調信号にパルス変調する変調回路と、前記変調回路でパルス変調された変調信号を電力増幅するデジタル電力増幅回路と、前記デジタル電力増幅回路で電力増幅された電力増幅変調信号を平滑化し、前記駆動信号として出力する平滑フィルタと、前記変調回路による変調信号のパルス幅を調整するパルス幅調整回路とを備えたことを特徴とするものである。

この電力増幅装置によれば、変調回路による変調信号のパルス幅を調整する構成としたため、例えば変調回路がΔΣ変調回路などのパルス密度変調回路である場合に、パルスデューティ比が50%付近で周波数が高くなるとき、変調信号のパルス幅を所定の時間長さ以上に制御することで、変調信号の周波数が低下し、駆動信号の歪みを抑制防止することができると共に、スイッチングロスも低減することが可能となる。

In order to solve the above problems, a power amplifying apparatus according to the present invention includes a modulation circuit that pulse-modulates an amplitude value of a drive waveform signal serving as a reference of an output drive signal into a modulation signal having a pulse duty, and a pulse generated by the modulation circuit. A digital power amplifier circuit that amplifies the modulated modulation signal; a smoothing filter that smoothes the power amplification modulation signal that has been power amplified by the digital power amplification circuit; and outputs the modulated signal as the drive signal; and a modulation signal generated by the modulation circuit And a pulse width adjusting circuit for adjusting the pulse width.

According to this power amplifying apparatus, since the pulse width of the modulation signal by the modulation circuit is adjusted, for example, when the modulation circuit is a pulse density modulation circuit such as a ΔΣ modulation circuit, the frequency is about 50% in the pulse duty ratio. When the signal becomes high, the modulation signal pulse width is controlled to a predetermined time length or more, so that the frequency of the modulation signal can be reduced, distortion of the drive signal can be suppressed and switching loss can be reduced. Is possible.

また、本発明の電力増幅装置は、前記パルス幅調整回路は、前記パルス変調された変調信号のパルス幅を所定の時間長さ以上に制御する制御信号を変調回路に入力することを特徴とするものである。

この電力増幅装置によれば、駆動信号の歪みを抑制防止すると共に、スイッチングロスも低減することができる。

また、本発明の電力増幅装置は、前記変調回路が、ΔΣ変調回路であることを特徴とするものである。

この電力増幅装置によれば、変調回路にΔΣ変調回路を用いることにより、駆動信号の波形精度を向上することができる。

In the power amplifying device of the present invention, the pulse width adjustment circuit inputs a control signal for controlling a pulse width of the pulse-modulated modulation signal to a predetermined time length or more to the modulation circuit. Is.

According to this power amplification device, it is possible to suppress and prevent distortion of the drive signal and reduce switching loss.

In the power amplifying apparatus of the present invention, the modulation circuit is a ΔΣ modulation circuit.

According to this power amplifying device, the waveform accuracy of the drive signal can be improved by using the ΔΣ modulation circuit as the modulation circuit.

次に、本発明の電力増幅装置の一実施形態として、液体噴射型印刷装置に用いられたものについて説明する。

図1は、本実施形態の印刷装置の概略構成図であり、図において、印刷媒体1は、図の左から右に向けて矢印方向に搬送され、その搬送途中の印刷領域で印刷される、ラインヘッド型印刷装置である。

液体噴射型印刷装置のうち、液体噴射ノズルの形成された液体噴射ヘッドをキャリッジと呼ばれる移動体に載せて印刷媒体の搬送方向と交差する方向に移動させるものを一般に「マルチパス型印刷装置」と呼んでいる。これに対し、印刷媒体の搬送方向と交差する方向に長尺な液体噴射ヘッドを配置して、所謂1パスでの印刷が可能なものを一般に「ラインヘッド型印刷装置」と呼んでいる。

Next, an embodiment used in a liquid jet printing apparatus will be described as an embodiment of the power amplification apparatus of the present invention.

FIG. 1 is a schematic configuration diagram of a printing apparatus according to the present embodiment. In the drawing, a

Among liquid ejecting printing apparatuses, a liquid ejecting head on which a liquid ejecting nozzle is formed is placed on a moving body called a carriage and moved in a direction crossing the transport direction of the print medium, and generally called a “multi-pass printing apparatus”. I'm calling. On the other hand, what is capable of printing in a so-called one pass by arranging a long liquid jet head in a direction crossing the conveyance direction of the printing medium is generally called a “line head type printing apparatus”.

図1中の符号2は、印刷媒体1の搬送ライン上方に設けられた複数の液体噴射ヘッドであり、印刷媒体搬送方向に2列になるように且つ印刷媒体搬送方向と交差する方向に並べて配設されて、夫々、ヘッド固定プレート11に固定されている。各液体噴射ヘッド2の最下面には、多数のノズルが形成されており、この面がノズル面と呼ばれている。ノズルは、図2に示すように、噴射する液体の色毎に、印刷媒体搬送方向と交差する方向に列状に配設されており、その列をノズル列と呼んだり、その列方向をノズル列方向と呼んだりする。そして、印刷媒体搬送方向と交差する方向に配設された全ての液体噴射ヘッド2のノズル列によって、印刷媒体1の搬送方向と交差する方向の幅全長に及ぶラインヘッドが形成されている。印刷媒体1は、これらの液体噴射ヘッド2のノズル面の下方を通過するときに、ノズル面に形成されている多数のノズルから液体が噴射され、印刷が行われる。

液体噴射ヘッド2には、例えばイエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(K)の4色のインクなどの液体が、図示しない各色の液体タンクから液体供給チューブを介して供給される。そして、各液体噴射ヘッド2に形成されているノズルから同時に必要箇所に必要量の液体を噴射することにより、印刷媒体1上に微小なドットを出力する。これを各色毎に行うことにより、搬送部4で搬送される印刷媒体1を一度通過させるだけで、所謂1パスによる印刷を行うことができる。

液体噴射ヘッドの各ノズルから液体を噴射する方法としては、静電方式、ピエゾ方式、膜沸騰液体噴射方式などがあり、本実施形態ではピエゾ方式を用いた。ピエゾ方式は、ノズルアクチュエータである圧電素子に駆動信号を与えると、キャビティ内の振動板が変位してキャビティ内に圧力変化を生じ、その圧力変化によって液滴がノズルから噴射されるというものである。そして、駆動信号の波高値や電圧増減傾きを調整することで液滴の噴射量を調整することが可能となる。なお、本発明は、ピエゾ方式以外の液体噴射方法にも、同様に適用可能である。

For example, liquids such as yellow (Y), magenta (M), cyan (C), and black (K) inks are supplied to the liquid ejecting

As a method of ejecting liquid from each nozzle of the liquid ejecting head, there are an electrostatic method, a piezo method, a film boiling liquid ejecting method, and the like. In this embodiment, the piezo method is used. In the piezo method, when a drive signal is given to a piezoelectric element that is a nozzle actuator, the diaphragm in the cavity is displaced to cause a pressure change in the cavity, and a droplet is ejected from the nozzle by the pressure change. . The droplet ejection amount can be adjusted by adjusting the peak value of the drive signal and the voltage increase / decrease slope. Note that the present invention can be similarly applied to liquid ejection methods other than the piezo method.

液体噴射ヘッド2の下方には、印刷媒体1を搬送方向に搬送するための搬送部4が設けられている。搬送部4は、駆動ローラ8及び従動ローラ9に搬送ベルト6を巻回して構成され、駆動ローラ8には図示しない電動モータが接続されている。また、搬送ベルト6の内側には、当該搬送ベルト6の表面に印刷媒体1を吸着するための図示しない吸着装置が設けられている。この吸着装置には、例えば負圧によって印刷媒体1を搬送ベルト6に吸着する空気吸引装置や、静電気力で印刷媒体1を搬送ベルト6に吸着する静電吸着装置などが用いられる。従って、給紙ローラ5によって給紙部3から印刷媒体1を一枚だけ搬送ベルト6上に送給し、電動モータによって駆動ローラ8を回転駆動すると、搬送ベルト6が印刷媒体搬送方向に回転され、吸着装置によって搬送ベルト6に印刷媒体1が吸着されて搬送される。この印刷媒体1の搬送中に、液体噴射ヘッド2から液体を噴射して印刷を行う。印刷の終了した印刷媒体1は、搬送方向下流側の排紙部10に排紙される。なお、前記搬送ベルト6には、例えばリニアエンコーダなどで構成される印刷基準信号出力装置が取付けられている。この印刷基準信号出力装置は、例えば搬送ベルト6とそれに吸着されて搬送される印刷媒体1とが同期して移動されることに着目し、印刷媒体1が搬送経路中の所定位置を通過した後は、搬送ベルト6の移動に伴って要求される印刷解像度相当のパルス信号を出力し、このパルス信号に応じて、後述する駆動回路から駆動信号をノズルアクチュエータに出力することで印刷媒体1上の所定位置に所定の色の液体を噴射し、そのドットによって印刷媒体1上に所定の画像を描画する。

Below the

この印刷装置内には、自身を制御するための制御装置が設けられている。この制御装置は、例えば図3に示すように、例えばパーソナルコンピュータ、デジタルカメラ等のホストコンピュータ60から入力された印刷データに基づいて、印刷装置や給紙装置等を制御することにより印刷媒体に印刷処理を行うものである。そして、ホストコンピュータ60から入力された印刷データ読込むための入力インタフェース61と、この入力インタフェース61から入力された印刷データに基づいて印刷処理等の演算処理を実行する例えばマイクロコンピュータで構成される制御部62と、前記給紙ローラ5に接続されている給紙ローラモータ17を駆動制御する給紙ローラモータドライバ63と、各液体噴射ヘッド2を駆動制御するヘッドドライバ65と、前記駆動ローラ8に接続されている電動モータ7を駆動制御する電動モータドライバ66と、各ドライバ63、65、66と外部の給紙ローラモータ17、液体噴射ヘッド2,3、電動モータ7とを接続するインタフェース67とを備えて構成される。

A control device for controlling itself is provided in the printing apparatus. For example, as shown in FIG. 3, the control device prints on a print medium by controlling a printing device, a paper feeding device, and the like based on print data input from a

制御部62は、印刷処理等の各種処理を実行するCPU(Central Processing Unit)62aと、入力インタフェース61を介して入力された印刷データ或いは当該印刷データ印刷処理等を実行する際の各種データを一時的に格納し、或いは印刷処理等のプログラムを一時的に展開するRAM(Random Access Memory)62cと、CPU62aで実行する制御プログラム等を格納する不揮発性半導体メモリで構成されるROM(Read-Only Memory)62dを備えている。この制御部62は、インタフェース61を介してホストコンピュータ60から印刷データ(画像データ)を入手すると、CPU62aが、この印刷データに所定の処理を実行して、何れの液体噴射ヘッド2の何れのノズルから液体を噴射するか或いはどの程度の液体を噴射するかというノズル選択データ(駆動信号選択データ)を算出し、この印刷データや駆動信号選択データ及び各種センサからの入力データに基づいて、各ドライバ63、65、66に制御信号を出力する。各ドライバ63、65、66からはアクチュエータを駆動するための駆動信号が出力され、給紙ローラモータ17、電動モータ7、液体噴射ヘッド2内のノズルアクチュエータなどが夫々作動して、印刷媒体1の給紙及び搬送及び排紙、並びに印刷媒体1への印刷処理が実行される。なお、制御部62内の各構成要素は、図示しないバスを介して電気的に接続されている。

The

図4には、本実施形態の印刷装置の制御装置から液体噴射ヘッド2に供給され、圧電素子からなるノズルアクチュエータを駆動するための駆動信号COMの一例を示す。本実施形態では、中間電位を中心に電位が変化する信号とした。この駆動信号COMは、ノズルアクチュエータを駆動して液体を噴射する単位駆動信号としての駆動パルスPCOMを時系列的に接続したものであり、各駆動パルスPCOMの立上がり部分がノズルに連通するキャビティ(圧力室)の容積を拡大して液体を引込む(液体の噴射面を考えればメニスカスを引き込むとも言える)段階であり、駆動パルスPCOMの立下がり部分がキャビティの容積を縮小して液体を押出す(液体の噴射面を考えればメニスカスを押出すとも言える)段階であり、液体を押出した結果、液滴がノズルから噴射される。

FIG. 4 shows an example of a drive signal COM that is supplied from the control device of the printing apparatus of the present embodiment to the

この電圧台形波からなる駆動パルスPCOMの電圧増減傾きや波高値を種々に変更することにより、液体の引込量や引込速度、液体の押出量や押出速度を変化させることができ、これにより液滴の噴射量を変化させて異なる大きさのドットを得ることができる。従って、複数の駆動パルスPCOMを時系列的に連結する場合でも、そのうちから単独の駆動パルスPCOMを選択してアクチュエータに供給し、液滴を噴射したり、複数の駆動パルスPCOMを選択してアクチュエータに供給し、液滴を複数回噴射したりすることで種々の大きさのドットを得ることができる。即ち、液体が乾かないうちに複数の液滴を同じ位置に着弾すると、実質的に大きな液滴を噴射するのと同じことになり、ドットの大きさを大きくすることができるのである。このような技術の組合せによって多階調化を図ることが可能となる。なお、図4の左端の駆動パルスPCOM1は、液体を引込むだけで押出していない。これは、微振動と呼ばれ、液滴を噴射せずに、例えばノズルの増粘を抑制防止したりするのに用いられる。 By variously changing the voltage increase / decrease slope and peak value of the driving pulse PCOM composed of this voltage trapezoidal wave, the liquid drawing amount and drawing speed, the liquid pushing amount and the pushing speed can be changed. It is possible to obtain dots of different sizes by changing the amount of injection. Therefore, even when a plurality of drive pulses PCOM are connected in time series, a single drive pulse PCOM is selected and supplied to the actuator, and droplets are ejected or a plurality of drive pulses PCOM are selected and the actuator is selected. In this way, dots of various sizes can be obtained by ejecting droplets a plurality of times. That is, if a plurality of droplets land on the same position before the liquid dries, it is substantially the same as ejecting a large droplet, and the size of the dot can be increased. By combining such techniques, it is possible to increase the number of gradations. Note that the driving pulse PCOM1 at the left end in FIG. This is called microvibration, and is used, for example, to suppress or prevent thickening of the nozzle without ejecting droplets.

各液体噴射ヘッド2には、前記駆動信号COMの他、前記図3の制御装置から制御信号として、印刷データに基づいて噴射するノズルを選択すると共に圧電素子などのノズルアクチュエータの駆動信号COMへの接続タイミングを決定する駆動信号選択データSI&SP、全ノズルにノズル選択データが入力された後、駆動信号選択データSI&SPに基づいて駆動信号COMと液体噴射ヘッド2のノズルアクチュエータとを接続させるラッチ信号LAT及びチャンネル信号CH、駆動信号選択データSI&SPをシリアル信号として液体噴射ヘッド2に送信するためのクロック信号CLKが入力されている。なお、これ以後、ノズルアクチュエータを駆動する駆動信号の最小単位を駆動パルスPCOMとし、駆動パルスPCOMが時系列的に連結された信号全体を駆動信号COMと記す。即ち、ラッチ信号LATで一連の駆動信号COMが出力され始め、チャンネル信号CH毎に駆動パルスPCOMが出力されることになる。

In addition to the drive signal COM, each

図5には、駆動信号COM(駆動パルスPCOM)をノズルアクチュエータ22に供給するために各液体噴射ヘッド2内に構築されたスイッチングコントローラの具体的な構成を示す。このスイッチングコントローラは、液体を噴射させるべきノズルに対応した圧電素子などのノズルアクチュエータ22を指定するための駆動信号選択データSI&SPを保存するシフトレジスタ211と、シフトレジスタ211のデータを一時的に保存するラッチ回路212と、ラッチ回路212の出力をレベル変換して選択スイッチ201に供給することにより、駆動信号COMをピエゾ素子などのノズルアクチュエータ22に接続するレベルシフタ213を備えて構成されている。

FIG. 5 shows a specific configuration of the switching controller constructed in each

シフトレジスタ211には、駆動信号選択データ信号SI&SPが順次入力されると共に、クロック信号CLKの入力パルスに応じて記憶領域が初段から順次後段にシフトする。ラッチ回路212は、ノズル数分の駆動信号選択データSI&SPがシフトレジスタ211に格納された後、入力されるラッチ信号LATによってシフトレジスタ211の各出力信号をラッチする。ラッチ回路212に保存された信号は、レベルシフタ213によって次段の選択スイッチ201をオンオフできる電圧レベルに変換される。これは、駆動信号COMが、ラッチ回路212の出力電圧に比べて高い電圧であり、これに合わせて選択スイッチ201の動作電圧範囲も高く設定されているためである。従って、レベルシフタ213によって選択スイッチ201が閉じられる圧電素子などのノズルアクチュエータは駆動信号選択データSI&SPの接続タイミングで駆動信号COM(駆動パルスPCOM)に接続される。また、シフトレジスタ211の駆動信号選択データSI&SPがラッチ回路212に保存された後、次の印刷情報をシフトレジスタ211に入力し、液体の噴射タイミングに合わせてラッチ回路212の保存データを順次更新する。なお、図中の符号HGNDは、圧電素子などのノズルアクチュエータのグランド端である。また、この選択スイッチ201によれば、圧電素子などのノズルアクチュエータを駆動信号COM(駆動パルスPCOM)から切り離した後も、当該ノズルアクチュエータ22の入力電圧は、切り離す直前の電圧に維持される。

The drive signal selection data signal SI & SP is sequentially input to the

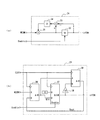

図6には、ノズルアクチュエータの駆動回路の具体的な構成を示す。本実施形態の駆動回路は、予め記憶されている駆動波形データDWCOMに基づいて、駆動信号COMの元、つまりノズルアクチュエータ22の駆動を制御する信号の基準となる駆動波形信号WCOMを生成する駆動波形信号発生回路25と、駆動波形信号発生回路25で生成された駆動波形信号WCOMをパルス変調する変調回路26と、変調回路26でパルス変調された変調信号を電力増幅するデジタル電力増幅器、所謂D級アンプ28と、デジタル電力増幅器28で電力増幅された電力増幅変調信号を平滑化して、駆動信号COM(駆動パルスPCOM)として選択スイッチ201からノズルアクチュエータ22に供給する平滑フィルタ29と、変調回路26からの変調信号を読込んで当該変調回路26による変調信号のパルス幅を調整するパルス幅調整回路31を備えて構成される。

FIG. 6 shows a specific configuration of the drive circuit of the nozzle actuator. The drive circuit according to the present embodiment generates a drive waveform signal WCOM that serves as a reference of a signal for controlling the drive of the

駆動波形信号発生回路25は、CPU62aから出力された駆動波形データDWCOMを電圧信号に変換して所定サンプリング周期分ホールドすると共に、それをD/A変換器でアナログ変換して駆動波形信号WCOMとして出力する。本実施形態では、この駆動波形信号WCOMをパルス変調する変調回路26にパルス密度変調(PDM)回路としてΣΔ変調回路を用いた。ΣΔ変調を行うパルス密度変調は、入力信号の量子化誤差を遅延させて入力側にフィードバックし、それを再び量子化して、パルスデューティとして出力する。パルス密度変調回路の詳細は、後段に説明する。デジタル電力増幅器28は、実質的に電力を増幅するためのハイサイドのスイッチング素子Q1及びローサイドのスイッチング素子Q2からなるハーフブリッジD級出力段21と、変調回路26からの変調信号に基づいて、それらのスイッチング素子Q1、Q2のゲート−ソース間信号GH、GLを調整するためのゲート駆動回路30とを備えて構成されている。また、平滑フィルタ29は例えばコイルLとコンデンサCの組合せからなるローパスフィルタ(低域通過フィルタ)で構成され、このローパスフィルタによって電力増幅変調信号の変調周期成分、この場合は基準信号の周波数成分が除去される。

The drive waveform

デジタル電力増幅器28では、変調信号がハイレベルであるとき、ハイサイド側スイッチング素子Q1のゲート−ソース間信号GHはハイレベルとなり、ローサイド側スイッチング素子Q2のゲート−ソース間信号GLはローレベルとなるので、ハイサイド側スイッチング素子Q1はオン状態となり、ローサイド側スイッチング素子Q2はオフ状態となり、その結果、ハーフブリッジD級出力段21の出力は、供給電圧VDDとなる。一方、変調信号がローレベルであるとき、ハイサイド側スイッチング素子Q1のゲート−ソース間信号GHはローレベルとなり、ローサイド側スイッチング素子Q2のゲート−ソース間信号GLはハイレベルとなるので、ハイサイド側スイッチング素子Q1はオフ状態となり、ローサイド側スイッチング素子Q2はオン状態となり、その結果、ハーフブリッジ出力段21の出力は0となる。

In the

このようにハイサイド及びローサイドのスイッチング素子がデジタル駆動される場合には、オン状態のスイッチング素子に電流が流れるが、ドレイン−ソース間の抵抗値は非常に小さく、損失は殆ど発生しない。また、オフ状態のスイッチング素子には電流が流れないので損失は発生しない。従って、このデジタル電力増幅器28の損失そのものは極めて小さく、小型のMOSFET等のスイッチング素子を使用することができる。

In this way, when the high-side and low-side switching elements are digitally driven, a current flows through the on-state switching elements, but the resistance value between the drain and source is very small and almost no loss occurs. Further, since no current flows through the switching element in the off state, no loss occurs. Therefore, the loss of the

図7aには、前記変調回路26として用いられたパルス密度変調回路の機能ブロック図を、図7bには、当該パルス密度変調回路の論理回路図を示す。このパルス密度変調回路は、所謂ΔΣ変調回路であり、機能回路としては、入力信号である駆動波形信号WCOMを量子化する量子化器32、原信号である駆動波形信号WCOMから量子化信号を減じて量子化誤差を算出する加減算器33、量子化誤差を遅延する遅延器34、遅延された量子化誤差を原信号である駆動波形信号WCOMに加算する加算器35を備えて構成される。具体的な論理回路としては、クロック信号CLKの反転値の立上がり時に前記遅延された量子化誤差Doutを原信号である駆動波形信号WCOMに加算する加算器36、クロック信号CLKの立上がり時に加算器36の出力Qinと例えば“10”に設定された定数Aを比較し、出力Qinが定数A以上であるときにハイレベルとなるパルス密度変調信号PDMを出力する比較器37、比較器37の出力であるパルス密度変調信号PDMを例えば10倍の値にレベルシフトするレベルシフタ38、クロック信号CLKの立上がり時にレベルシフタ38の出力を加算器36の出力Qinから減じて遅延された量子化誤差を出力する遅延・加減算器39を備えて構成される。なお、本実施形態では、前記機能回路としての量子化器32、論理回路としての比較器37は、後述する制御信号Enable信号がハイレベルにあるときだけ、量子化、或いは比較を行う。

FIG. 7a shows a functional block diagram of a pulse density modulation circuit used as the

図8aには、前記パルス幅調整回路31の機能ブロック図を、図8bには、当該パルス幅調整回路31の論理回路図を示す。このパルス幅調整回路31は、機能回路としては、パルス密度変調信号PDMのエッジ、即ちローレベルからハイレベルへの転換期及びハイレベルからローレベルへの転換期を検出してクロック信号の周期分のリセット信号resetを出力するエッジ検出部40、リセット信号resetの立上がり時にリセットされ、クロック信号CLKをカウントするカウンタ41、カウンタ41の出力と例えば“1”に設定された定数constを比較し、カウンタ41の出力が定数constよりも大きいときにハイレベルとなる制御信号Enableを出力する比較器42とを備えて構成される。論理回路としては、パルス密度変調信号PDMにクロック信号CLKの周期分の遅れを与える遅延器43、遅延器43で遅延された遅延クロック信号dCLKとクロック信号CLKの排他的論理和を算出し、遅延クロック信号dCLK又は通常のクロック信号CLKの何れか一方のみがハイレベルにあるときにハイレベルとなる、つまりパルス密度変調信号PDMの立上がり及び立下がりのエッジ検出からクロック信号CLKの周期分のリセット信号resetを出力する排他的論理和器44、リセット信号resetの立上がり時にリセットされ、クロック信号CLKの立上がり時にカウントアップするカウンタ45と、クロック信号CLKの反転値の立上がり時にカウンタ45の出力と例えば“1”に設定された定数constを比較し、カウンタ45の出力が定数const以上であるときにハイレベルとなる制御信号Enableを出力する比較器46を備えて構成される。

FIG. 8 a shows a functional block diagram of the pulse

本実施形態のパルス密度変調回路26、パルス幅調整回路31によれば、図9aに示すように、パルス幅調整回路31のカウンタ45の初期値が“0”であり、制御信号Enableはローレベルにあり、パルス密度変調信号PDMの初期値がローレベルにあり、例えば入力信号である駆動波形信号WCOMが“4”一定であるとすると、クロック信号CLKの立下がり時に出力されるパルス密度変調回路26の加算器36の出力Qinは“4”であるが、制御信号Enableがローレベルにあるので、比較器37は“10”である定数Aと出力Qinとの比較演算を行わず、次のクロック信号の立上がりで出力されるパルス密度変調信号PDMはローレベルのままとなり、遅延・加減算器39の入力Bは“0”、一方の入力Aは“4”であるから当該遅延・加減算器39の出力Doutは“4”となる。

According to the pulse

同じクロック信号CLKの立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“8”となるが、パルス幅調整回路31のカウンタ45がインクリメントされて“1”となるので、そのタイミングで比較器46から出力される制御信号Enableはハイレベルとなり、次のクロック信号の立上がり時に比較器37は定数Aと出力Qinを比較するが、出力Qinが“10”より小さいのでパルス密度変調信号PDMはローレベルのままとなり、遅延・加減算器39の出力Doutは“8”となる。

同じクロック信号CLKの立下がり時には、パルス幅調整回路31のカウンタ45がインクリメントされて“2”となると共に、パルス密度変調回路26の加算器36の出力Qinは“12”となり、制御信号Enableはハイレベルのままであるから、次のクロック信号の立上がりで比較器37の出力、つまりパルス密度変調信号PDMがハイレベルとなり、遅延・加減算器39の入力Bは“10”となり、一方の入力Aは“12”なので、出力Doutは“2”となる。

At the fall of the same clock signal CLK, the output Qin of the

When the same clock signal CLK falls, the

前記パルス密度変調信号PDMの立上がりと共にリセット信号resetも立上がるため、パルス幅調整回路31のカウンタ45がリセットされて“0”となり、比較器46から出力される制御信号Enableがローレベルになると共に、パルス密度変調回路26の加算器36の出力Qinは“6”となるが、制御信号Enableがローレベルであるから比較器37は比較演算を行わず、パルス密度変調信号PDMはハイレベルのままとなる。従って、遅延・加減算器39の入力Bは“10”のままであり、一方の入力Aが“6”であるから、次のクロック信号CLKの立上がりでの出力Doutは“−4”となると共に、リセット信号resetもローレベルとなる。

Since the reset signal reset rises with the rise of the pulse density modulation signal PDM, the

同じクロック信号CLKの立下がり時には、パルス幅調整回路31のカウンタ45がインクリメントされて“1”となり、比較器46から出力される制御信号Enableがハイレベルになると共に、パルス密度変調回路26の加算器36の出力Qinは“0”となり、次のクロック信号CLKの立上がりで比較器37から出力されるパルス密度変調信号PDMはローレベルに変化する。従って、遅延・加減算器39の入力Bは“0”となり、一方の入力Aも“0”であるから、出力Doutは“0”となる。

At the fall of the same clock signal CLK, the

前記パルス密度変調信号PDMの立下がりと共にリセット信号resetも立上がるため、パルス幅調整回路31のカウンタ45がリセットされて“0”となり、比較器46から出力される制御信号Enableがローレベルになると共に、パルス密度変調回路26の加算器36の出力Qinは“4”となるが、制御信号Enableがローレベルであるから比較器37は比較演算を行わず、パルス密度変調信号PDMはローレベルのままとなる。従って、遅延・加減算器39の入力Bは“0”のままであり、一方の入力Aが“4”であるから、次のクロック信号CLKの立上がりでの出力Doutは“4”となると共に、リセット信号resetもローレベルとなる。

Since the reset signal reset rises with the fall of the pulse density modulation signal PDM, the

このように、パルス密度変調信号PDMのエッジ検出時には、制御信号Enableをローレベルにするため、この制御信号Enableがローレベルにあるときには、比較器37による比較演算が停止され、パルス密度変調信号PDMのパルス幅が時間軸方向に長くなる、換言すればパルス密度変調信号PDMのパルス幅を所定の時間長さ以上に制御することができる。周知のように、パルス密度変調では、パルスデューティ比が50%でパルス周波数が高くなるので、本実施形態のパルス幅調整回路31の機能を図に表すと、図9bに示すように、パルスデューティ比50%近傍でのパルス周波数をあるレベルで規制することができ、そのようにすることで駆動信号COM(駆動パルスPCOM)の歪みを抑制防止することができると共に、スイッチングロスも低減することが可能となる。

Thus, when the edge of the pulse density modulation signal PDM is detected, the control signal Enable is set to the low level. Therefore, when the control signal Enable is at the low level, the comparison operation by the

図10aは、パルス密度変調のパルス幅を制御しない、通常のパルス密度変調のタイミングチャートであり、図6のパルス幅調整回路がなく、図7の制御信号Enableがない場合を示している。このタイミングチャートで、図9aと同様に、パルス密度変調信号PDMの初期値がローレベルにあり、例えば入力信号である駆動波形信号WCOMが“4”一定であるとすると、クロック信号CLKの立下がり時に出力されるパルス密度変調回路26の加算器36の出力Qinは“4”であり、定数Aと出力Qinの比較結果に基づいて、次のクロック信号の立上がりで比較器37から出力されるパルス密度変調信号PDMはローレベルのままとなり、遅延・加減算器39の入力Bは“0”、一方の入力Aは“4”であるから当該遅延・加減算器39の出力Doutは“4”となる。

FIG. 10a is a timing chart of normal pulse density modulation in which the pulse width of pulse density modulation is not controlled, and shows a case where the pulse width adjustment circuit of FIG. 6 is not provided and the control signal Enable of FIG. 7 is not provided. In this timing chart, as in FIG. 9a, if the initial value of the pulse density modulation signal PDM is at a low level, for example, if the drive waveform signal WCOM that is an input signal is “4” constant, the falling edge of the clock signal CLK The output Qin of the

同じクロック信号CLKの立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“8”となり、次のクロック信号の立上がり時に比較器37は定数Aと出力Qinを比較するが、出力Qinが“10”より小さいのでパルス密度変調信号PDMはローレベルのままとなり、遅延・加減算器39の出力Doutは“8”となる。

同じクロック信号CLKの立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“12”となり、次のクロック信号の立上がりで比較器37の出力、つまりパルス密度変調信号PDMがハイレベルとなり、遅延・加減算器39の入力Bは“10”となり、一方の入力Aは“12”なので、出力Doutは“2”となる。

When the same clock signal CLK falls, the output Qin of the

When the same clock signal CLK falls, the output Qin of the

同じクロック信号の立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“6”となり、次のクロック信号の立上がりで比較器37の出力、つまりパルス密度変調信号PDMがローレベルとなり、遅延・加減算器39の入力Bは“0”となり、一方の入力Aが“6”であるから、出力Doutは“6”となる。

同じクロック信号CLKの立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“10”となり、次のクロック信号CLKの立上がりで比較器37から出力されるパルス密度変調信号PDMはハイレベルに変化し、遅延・加減算器39の入力Bは“10”となり、一方の入力Aも“10”であるから、出力Doutは“0”となる。

At the fall of the same clock signal, the output Qin of the

At the fall of the same clock signal CLK, the output Qin of the

同じクロック信号の立下がり時には、パルス密度変調回路26の加算器36の出力Qinは“4”となり、次のクロック信号CLKの立上がりで比較器37から出力されるパルス密度変調信号PDMはローレベルに変化し、遅延・加減算器39の入力Bは“0”となり、一方の入力Aが“4”であるから、出力Doutは“4”となる。

このように、制御信号Enableを用いない通常のパルス密度変調では、出力であるパルス密度変調信号PDMが頻繁にハイレベルとローレベルに変化する場合がある。時間当たりの変化が多いということは、周波数が高いということであり、図10bに示すように、パルスデューティ比が50%のときにピークになる。パルス周波数が高いと、パルス幅が狭くなり、高速スイッチングによって駆動信号に歪みが生じる恐れがある上に、シュートスルーなどのスイッチングロスの増大にも繋がる。

At the fall of the same clock signal, the output Qin of the

As described above, in normal pulse density modulation that does not use the control signal Enable, the output pulse density modulation signal PDM may frequently change between a high level and a low level. A large change per time means that the frequency is high, and peaks as shown in FIG. 10b when the pulse duty ratio is 50%. When the pulse frequency is high, the pulse width is narrowed, the drive signal may be distorted by high-speed switching, and the switching loss such as shoot-through is increased.

このように、本実施形態の電力増幅装置によれば、出力する駆動信号COM(駆動パルスPCOM)の基準となる駆動波形信号WCOMの振幅値をパルスデューティからなる変調信号PDMにパルス変調し、そのパルス変調された変調信号PDMをデジタル電力増幅回路28で電力増幅し、その電力増幅された電力増幅変調信号APWMを平滑化して駆動信号COM(駆動パルスPCOM)として出力するにあたり、変調回路26による変調信号PDMのパルス幅を調整することとしたため、変調回路26がΔΣ変調回路などのパルス密度変調回路である場合に、パルスデューティ比が50%付近で周波数が高くなるとき、変調信号PDMのパルス幅を所定の時間長さ以上に制御することで、変調信号PDMの周波数が低下し、駆動信号COM(駆動パルスPCOM)の歪みを抑制防止することができると共に、スイッチングロスも低減することが可能となる。

As described above, according to the power amplifying apparatus of the present embodiment, the amplitude value of the drive waveform signal WCOM serving as a reference of the output drive signal COM (drive pulse PCOM) is pulse-modulated to the modulation signal PDM having the pulse duty, The modulation by the

また、パルス変調された変調信号PDMのパルス幅を所定の時間長さ以上に制御する制御信号Enableを変調回路26に入力することとしたため、駆動信号COM(駆動パルスPCOM)の歪みを抑制防止すると共に、スイッチングロスも低減することができる。

また、変調回路26が、ΔΣ変調回路であることとしたため、駆動信号COM(駆動パルスPCOM)の波形精度を向上することができる。

なお、前記実施形態では、本発明の電力増幅装置をラインヘッド型の液体噴射型印刷装置に用いた場合についてのみ詳述したが、本発明の電力増幅装置は、マルチパス型の液体噴射型印刷装置にも同様に適用可能である。

Further, since the control signal Enable for controlling the pulse width of the pulse-modulated modulation signal PDM to be equal to or longer than a predetermined time length is input to the

In addition, since the

In the above-described embodiment, only the case where the power amplifying apparatus of the present invention is used in a line head type liquid jet printing apparatus has been described in detail. However, the power amplifying apparatus of the present invention is a multi-pass type liquid jet printing apparatus. The same applies to the apparatus.

また、前記実施形態では、本発明の電力増幅装置を液体噴射型印刷装置のデジタル電力増幅器の駆動回路に具体化したが、この限りではなく、インク以外の他の液体(液体以外にも、機能材料の粒子が分散されている液状体、ジェルなどの流状体を含む)や液体以外の流体(流体として流して噴射できる固体など)を噴射したり吐出したりする液体噴射装置に具体化することもできる。例えば、液晶ディスプレイ、EL(エレクトロルミネッサンス)ディスプレイ、面発光ディスプレイ、カラーフィルタの製造などに用いられる電極材や色材などの材料を分散又は溶解の形態で含む液状体を噴射する液状体噴射装置、バイオチップ製造に用いられる生体有機物を噴射する液体噴射装置、精密ピペットとして用いられて試料となる液体を噴射する液体噴射装置であってもよい。更に、時計やカメラなどの精密機械にピンポイントで潤滑油を噴射する液体噴射装置、光通信素子などに用いられる微小半球レンズ(光学レンズ)などを形成するための紫外線硬化樹脂などの透明樹脂液を基板上に噴射する液体噴射装置、基板などをエッチングするために酸又はアルカリなどのエッチング液を噴射する液体噴射装置、ジェルを噴射する流状体噴射装置、トナーなどの粉体を例とする固体を噴射する流体噴射式記録装置であってもよい。そして、これらのうち何れか一種の噴射装置に本発明を適用することができる。 In the above embodiment, the power amplifying device of the present invention is embodied in the drive circuit of the digital power amplifier of the liquid jet printing apparatus. However, the present invention is not limited to this. The present invention is embodied in a liquid ejecting apparatus that ejects or ejects a fluid other than a liquid (including a liquid material in which particles of material are dispersed, a fluid such as a gel), or a fluid other than a liquid (such as a solid that can be ejected as a fluid). You can also. For example, a liquid material ejecting apparatus that ejects a liquid material that contains materials such as electrode materials and color materials used in the manufacture of liquid crystal displays, EL (electroluminescence) displays, surface-emitting displays, color filters, and the like in a dispersed or dissolved form. Further, it may be a liquid ejecting apparatus that ejects a bio-organic matter used for biochip manufacturing, or a liquid ejecting apparatus that ejects a liquid that is used as a precision pipette to become a sample. In addition, transparent resin liquids such as UV curable resins for forming liquid injection devices that inject lubricating oil onto precision machines such as watches and cameras, micro hemispherical lenses (optical lenses) used in optical communication elements, etc. Examples include a liquid ejecting apparatus that ejects a liquid onto a substrate, a liquid ejecting apparatus that ejects an etching solution such as acid or alkali to etch the substrate, a fluid ejecting apparatus that ejects a gel, and a powder such as toner. It may be a fluid ejection recording apparatus that ejects a solid. The present invention can be applied to any one of these injection devices.

1は印刷媒体、2は液体噴射ヘッド、3は給紙部、4は搬送部、5は給紙ローラ、6は搬送ベルト、7は電動モータ、8は駆動ローラ、9は従動ローラ、10は排紙部、11は固定プレート、21はハーフブリッジD級出力段、22はノズルアクチュエータ、25は駆動波形信号発生回路、26は変調回路、28はデジタル電力増幅器、29は平滑フィルタ、30はゲート駆動回路、31はパルス幅調整回路、32は量子化器、33は加減算器、34は遅延器、35は加算器、36は加算器、37比較器、38はレベルシフタ、39は遅延・加減算器、40はエッジ検出部、41はカウンタ、42は比較器、43は遅延器、44は排他的論理和器、45はカウンタ、46は比較器、65はヘッドドライバ 1 is a print medium, 2 is a liquid ejecting head, 3 is a paper feed unit, 4 is a transport unit, 5 is a paper feed roller, 6 is a transport belt, 7 is an electric motor, 8 is a drive roller, 9 is a driven roller, 10 is A paper discharge unit, 11 is a fixed plate, 21 is a half bridge class D output stage, 22 is a nozzle actuator, 25 is a drive waveform signal generation circuit, 26 is a modulation circuit, 28 is a digital power amplifier, 29 is a smoothing filter, 30 is a gate Drive circuit, 31 pulse width adjustment circuit, 32 quantizer, 33 adder / subtractor, 34 delay device, 35 adder, 36 adder, 37 comparator, 38 level shifter, 39 delay / adder / subtractor , 40 is an edge detector, 41 is a counter, 42 is a comparator, 43 is a delay unit, 44 is an exclusive OR, 45 is a counter, 46 is a comparator, and 65 is a head driver.

Claims (3)

前記変調回路でパルス変調された変調信号を電力増幅するデジタル電力増幅回路と、

前記デジタル電力増幅回路で電力増幅された電力増幅変調信号を平滑化し、前記駆動信号として出力する平滑フィルタと、

前記変調回路による変調信号のパルス幅を調整するパルス幅調整回路と、

を備えたことを特徴とする電力増幅装置。 A modulation circuit for pulse-modulating the amplitude value of the drive waveform signal serving as a reference of the drive signal to be output into a modulation signal comprising a pulse duty;

A digital power amplifier circuit for power-amplifying the modulation signal pulse-modulated by the modulation circuit;

A smoothing filter that smoothes the power amplification modulation signal that has been power amplified by the digital power amplification circuit, and outputs the smoothed output as the drive signal;

A pulse width adjustment circuit for adjusting a pulse width of a modulation signal by the modulation circuit;

A power amplifying device comprising:

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008286223A JP2010114711A (en) | 2008-11-07 | 2008-11-07 | Power-amplifying device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008286223A JP2010114711A (en) | 2008-11-07 | 2008-11-07 | Power-amplifying device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010114711A true JP2010114711A (en) | 2010-05-20 |

| JP2010114711A5 JP2010114711A5 (en) | 2011-11-17 |

Family

ID=42302914

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008286223A Withdrawn JP2010114711A (en) | 2008-11-07 | 2008-11-07 | Power-amplifying device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010114711A (en) |

Cited By (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013031960A (en) * | 2011-08-02 | 2013-02-14 | Seiko Epson Corp | Drive circuit and drive method for driving liquid ejection head |

| CN103722882A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus and liquid ejecting method |

| CN103722883A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus and liquid ejecting method |

| CN103722881A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus |

| JP2014076562A (en) * | 2012-10-10 | 2014-05-01 | Seiko Epson Corp | Printer and printing method |

| JP2014184587A (en) * | 2013-03-22 | 2014-10-02 | Seiko Epson Corp | Liquid discharge apparatus and method of discharging liquid |

| JP2014184569A (en) * | 2013-03-22 | 2014-10-02 | Seiko Epson Corp | Liquid discharge apparatus and capacitive load drive circuit |

| US8974024B2 (en) | 2013-03-22 | 2015-03-10 | Seiko Epson Corporation | Liquid discharge apparatus |

| JP2015164779A (en) * | 2014-03-03 | 2015-09-17 | セイコーエプソン株式会社 | Liquid discharge device, head unit, and liquid discharge device control method |

| US9156250B2 (en) | 2014-03-03 | 2015-10-13 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| US9186888B2 (en) | 2013-08-20 | 2015-11-17 | Seiko Epson Corporation | Liquid discharging apparatus, control method thereof, and program |

| US9254645B2 (en) | 2013-08-30 | 2016-02-09 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US9259919B2 (en) | 2014-05-02 | 2016-02-16 | Seiko Epson Corporation | Liquid discharge apparatus and control method of liquid discharge apparatus |

| JP2016040085A (en) * | 2014-08-12 | 2016-03-24 | セイコーエプソン株式会社 | Liquid emission device and head unit |

| US9302473B2 (en) | 2014-01-16 | 2016-04-05 | Seiko Epson Corporation | Liquid discharge apparatus, head unit, and control method of liquid discharge apparatus |

| JP2016074227A (en) * | 2015-12-24 | 2016-05-12 | セイコーエプソン株式会社 | Driving circuit and driving method for driving liquid discharge head |

| US9352557B2 (en) | 2014-08-12 | 2016-05-31 | Seiko Epson Corporation | Liquid discharge apparatus and head unit |

| US9358781B2 (en) | 2014-03-03 | 2016-06-07 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| US9358782B2 (en) | 2014-05-26 | 2016-06-07 | Seiko Epson Corporation | Liquid discharge apparatus |

| US9375917B2 (en) | 2014-08-12 | 2016-06-28 | Seiko Epson Corporation | Liquid discharge apparatus and head unit |

| US9399341B2 (en) | 2014-11-25 | 2016-07-26 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9421762B1 (en) | 2015-03-20 | 2016-08-23 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9427957B2 (en) | 2014-03-25 | 2016-08-30 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, and method of controlling liquid ejecting apparatus |

| US9434157B2 (en) | 2014-12-10 | 2016-09-06 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9475284B2 (en) | 2015-02-04 | 2016-10-25 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9475282B2 (en) | 2013-08-30 | 2016-10-25 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US9475283B2 (en) | 2015-02-17 | 2016-10-25 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9522528B2 (en) | 2014-12-11 | 2016-12-20 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, integrated circuit device for capacitive load driving, and capacitive load driving circuit |

| US9527277B2 (en) | 2014-12-10 | 2016-12-27 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9533493B2 (en) | 2014-12-11 | 2017-01-03 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, integrated circuit device for capacitive load driving, and capacitive load driving circuit |

| EP3112159A2 (en) | 2015-07-01 | 2017-01-04 | Seiko Epson Corporation | Liquid discharge device and head unit |

| US9539805B2 (en) | 2014-12-11 | 2017-01-10 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9539804B2 (en) | 2014-12-15 | 2017-01-10 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9545789B2 (en) | 2014-11-25 | 2017-01-17 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9550356B2 (en) | 2015-01-28 | 2017-01-24 | Seiko Epson Corporation | Liquid discharge apparatus, head unit, capacitive load drive circuit, and integrated circuit device for capacitive load drive |

| JP2017019295A (en) * | 2016-11-04 | 2017-01-26 | セイコーエプソン株式会社 | Printing device and printing method |

| JP2017019296A (en) * | 2016-11-04 | 2017-01-26 | セイコーエプソン株式会社 | Printing device and printing method |

| US9555624B2 (en) | 2015-02-03 | 2017-01-31 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9555625B2 (en) | 2015-03-20 | 2017-01-31 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9573367B2 (en) | 2014-12-10 | 2017-02-21 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device |

| US9579886B2 (en) | 2015-02-04 | 2017-02-28 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| JP2017043007A (en) * | 2015-08-27 | 2017-03-02 | セイコーエプソン株式会社 | Liquid discharge device and head unit |

| US9656462B2 (en) | 2015-08-26 | 2017-05-23 | Seiko Epson Corporation | Liquid ejecting apparatus |

| US9849670B2 (en) | 2016-03-18 | 2017-12-26 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US9862184B2 (en) | 2015-10-26 | 2018-01-09 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9908329B2 (en) | 2016-02-26 | 2018-03-06 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US9925766B2 (en) | 2016-02-26 | 2018-03-27 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9956767B2 (en) | 2016-02-26 | 2018-05-01 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9981466B2 (en) | 2016-08-08 | 2018-05-29 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10000058B2 (en) | 2016-03-18 | 2018-06-19 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US10022960B2 (en) | 2016-03-18 | 2018-07-17 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10035342B2 (en) | 2016-07-08 | 2018-07-31 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US10044343B2 (en) | 2016-02-26 | 2018-08-07 | Seiko Epson Corporation | Drive circuit, and control method of drive circuit |

| EP3372406A1 (en) | 2017-03-06 | 2018-09-12 | Seiko Epson Corporation | Liquid ejecting apparatus and capacitive load drive circuit |

| US10086605B2 (en) | 2016-09-26 | 2018-10-02 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and driving method |

| CN108621563A (en) * | 2017-03-23 | 2018-10-09 | 精工爱普生株式会社 | Printing equipment and printing equipment power supply unit |

| US10179449B2 (en) | 2015-10-09 | 2019-01-15 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US10245827B2 (en) | 2015-03-20 | 2019-04-02 | Seiko Epson Corporation | Liquid ejecting device, driver circuit, and head unit |

| US10265948B2 (en) | 2016-02-26 | 2019-04-23 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US10457041B2 (en) | 2017-07-06 | 2019-10-29 | Seiko Epson Corporation | Liquid discharge apparatus, circuit substrate, and integrated circuit device |

| US10464316B2 (en) | 2017-07-06 | 2019-11-05 | Seiko Epson Corporation | Liquid discharge apparatus, circuit substrate, and integrated circuit device |

| US10821727B2 (en) | 2017-11-30 | 2020-11-03 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10875294B2 (en) | 2018-02-26 | 2020-12-29 | Seiko Epson Corporation | Liquid ejecting apparatus |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007312258A (en) * | 2006-05-22 | 2007-11-29 | Sharp Corp | Pulse signal generating apparatus |

| JP2008113424A (en) * | 2006-10-03 | 2008-05-15 | Seiko Epson Corp | Control method of class-d amplifier, control circuit for class-d amplifier, driving circuit for capacitive load, transducer, ultrasonic speaker, display device, directional acoustic system, and printer |

-

2008

- 2008-11-07 JP JP2008286223A patent/JP2010114711A/en not_active Withdrawn

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007312258A (en) * | 2006-05-22 | 2007-11-29 | Sharp Corp | Pulse signal generating apparatus |

| JP2008113424A (en) * | 2006-10-03 | 2008-05-15 | Seiko Epson Corp | Control method of class-d amplifier, control circuit for class-d amplifier, driving circuit for capacitive load, transducer, ultrasonic speaker, display device, directional acoustic system, and printer |

Cited By (101)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013031960A (en) * | 2011-08-02 | 2013-02-14 | Seiko Epson Corp | Drive circuit and drive method for driving liquid ejection head |

| CN103722881A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus |

| CN103722883A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus and liquid ejecting method |

| CN103722881B (en) * | 2012-10-10 | 2015-11-18 | 精工爱普生株式会社 | Liquid ejection apparatus |

| JP2014076562A (en) * | 2012-10-10 | 2014-05-01 | Seiko Epson Corp | Printer and printing method |

| US8833890B2 (en) | 2012-10-10 | 2014-09-16 | Seiko Epson Corporation | Liquid ejecting apparatus |

| CN103722882A (en) * | 2012-10-10 | 2014-04-16 | 精工爱普生株式会社 | Liquid ejecting apparatus and liquid ejecting method |

| CN105398219A (en) * | 2012-10-10 | 2016-03-16 | 精工爱普生株式会社 | Liquid Ejecting Apparatus And Liquid Ejecting Method |

| US8857935B2 (en) | 2012-10-10 | 2014-10-14 | Seiko Epson Corporation | Liquid ejecting apparatus and liquid ejecting method |

| US8894171B2 (en) | 2012-10-10 | 2014-11-25 | Seiko Epson Corporation | Liquid ejecting apparatus and liquid ejecting method |

| CN105235389A (en) * | 2012-10-10 | 2016-01-13 | 精工爱普生株式会社 | liquid ejecting apparatus |

| CN103722882B (en) * | 2012-10-10 | 2015-11-25 | 精工爱普生株式会社 | Liquid ejection apparatus and liquid ejection method |

| CN103722883B (en) * | 2012-10-10 | 2015-11-18 | 精工爱普生株式会社 | Liquid ejection apparatus and liquid ejection method |

| JP2014184587A (en) * | 2013-03-22 | 2014-10-02 | Seiko Epson Corp | Liquid discharge apparatus and method of discharging liquid |

| JP2014184569A (en) * | 2013-03-22 | 2014-10-02 | Seiko Epson Corp | Liquid discharge apparatus and capacitive load drive circuit |

| US9168738B2 (en) | 2013-03-22 | 2015-10-27 | Seiko Epson Corporation | Liquid discharge apparatus and method of discharging liquid |

| US9346264B2 (en) | 2013-03-22 | 2016-05-24 | Seiko Epson Corporation | Liquid discharge apparatus and capacitive load driving circuit |

| US8974024B2 (en) | 2013-03-22 | 2015-03-10 | Seiko Epson Corporation | Liquid discharge apparatus |

| US9735774B2 (en) | 2013-03-22 | 2017-08-15 | Seiko Epson Corporation | Capacitive load driving circuit |

| US9539806B2 (en) | 2013-03-22 | 2017-01-10 | Seiko Epson Corporation | Liquid discharge apparatus and method of discharging liquid |

| US9186888B2 (en) | 2013-08-20 | 2015-11-17 | Seiko Epson Corporation | Liquid discharging apparatus, control method thereof, and program |

| US9475282B2 (en) | 2013-08-30 | 2016-10-25 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US10035341B2 (en) | 2013-08-30 | 2018-07-31 | Seiko Epson Corporation | Driving circuit for driving capacitive load |

| US9254645B2 (en) | 2013-08-30 | 2016-02-09 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US9446584B2 (en) | 2013-08-30 | 2016-09-20 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US9302473B2 (en) | 2014-01-16 | 2016-04-05 | Seiko Epson Corporation | Liquid discharge apparatus, head unit, and control method of liquid discharge apparatus |

| US9673810B2 (en) | 2014-01-16 | 2017-06-06 | Seiko Epson Corporation | Driving circuit for driving a capacitive load, and control method of a driving circuit for driving a capacitive load |

| US9654099B2 (en) | 2014-03-03 | 2017-05-16 | Seiko Epson Corporation | Driving circuit for driving a capacitive load |

| US9358781B2 (en) | 2014-03-03 | 2016-06-07 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| US9586397B2 (en) | 2014-03-03 | 2017-03-07 | Seiko Epson Corporation | Driving circuit for driving a capacitive load |

| US9427958B2 (en) | 2014-03-03 | 2016-08-30 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| US9440433B2 (en) | 2014-03-03 | 2016-09-13 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| US9156250B2 (en) | 2014-03-03 | 2015-10-13 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, and control method of liquid discharging apparatus |

| JP2015164779A (en) * | 2014-03-03 | 2015-09-17 | セイコーエプソン株式会社 | Liquid discharge device, head unit, and liquid discharge device control method |

| US9656461B2 (en) | 2014-03-25 | 2017-05-23 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, and method of controlling liquid ejecting apparatus |

| US9427957B2 (en) | 2014-03-25 | 2016-08-30 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, and method of controlling liquid ejecting apparatus |

| US9522531B2 (en) | 2014-05-02 | 2016-12-20 | Seiko Epson Corporation | Liquid discharge apparatus and control method of liquid discharge apparatus |

| US9259919B2 (en) | 2014-05-02 | 2016-02-16 | Seiko Epson Corporation | Liquid discharge apparatus and control method of liquid discharge apparatus |

| US9358782B2 (en) | 2014-05-26 | 2016-06-07 | Seiko Epson Corporation | Liquid discharge apparatus |

| US9831868B2 (en) | 2014-05-26 | 2017-11-28 | Seiko Epson Corporation | Driving circuit for driving a piezoelectric element |

| US9375917B2 (en) | 2014-08-12 | 2016-06-28 | Seiko Epson Corporation | Liquid discharge apparatus and head unit |

| US9352559B2 (en) | 2014-08-12 | 2016-05-31 | Seiko Epson Corporation | Liquid discharge apparatus and head unit |

| US9623653B2 (en) | 2014-08-12 | 2017-04-18 | Seiko Epson Corporation | Driving circuit for driving a capacitive load |

| US9352557B2 (en) | 2014-08-12 | 2016-05-31 | Seiko Epson Corporation | Liquid discharge apparatus and head unit |

| US9586396B2 (en) | 2014-08-12 | 2017-03-07 | Seiko Epson Corporation | Drive circuit for driving a capacitive load |

| JP2016040085A (en) * | 2014-08-12 | 2016-03-24 | セイコーエプソン株式会社 | Liquid emission device and head unit |

| US9793891B2 (en) | 2014-08-12 | 2017-10-17 | Seiko Epson Corporation | Drive circuit for driving a capacitive load |

| US10434767B2 (en) | 2014-11-25 | 2019-10-08 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9545789B2 (en) | 2014-11-25 | 2017-01-17 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9399341B2 (en) | 2014-11-25 | 2016-07-26 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9731501B2 (en) | 2014-11-25 | 2017-08-15 | Seiko Epson Corporation | Liquid ejecting apparatus, head unit, integrated circuit device for driving capacitive load, and capacitive load driving circuit |

| US9434157B2 (en) | 2014-12-10 | 2016-09-06 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9573367B2 (en) | 2014-12-10 | 2017-02-21 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device |

| US9527277B2 (en) | 2014-12-10 | 2016-12-27 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9539805B2 (en) | 2014-12-11 | 2017-01-10 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9751303B2 (en) | 2014-12-11 | 2017-09-05 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, integrated circuit device for capacitive load driving, and capacitive load driving circuit |

| US9764548B2 (en) | 2014-12-11 | 2017-09-19 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9533493B2 (en) | 2014-12-11 | 2017-01-03 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, integrated circuit device for capacitive load driving, and capacitive load driving circuit |

| US9522528B2 (en) | 2014-12-11 | 2016-12-20 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, integrated circuit device for capacitive load driving, and capacitive load driving circuit |

| US9713922B2 (en) | 2014-12-15 | 2017-07-25 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9539804B2 (en) | 2014-12-15 | 2017-01-10 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and integrated circuit device for capacitive load driving |

| US9550356B2 (en) | 2015-01-28 | 2017-01-24 | Seiko Epson Corporation | Liquid discharge apparatus, head unit, capacitive load drive circuit, and integrated circuit device for capacitive load drive |

| US9862185B2 (en) | 2015-01-28 | 2018-01-09 | Seiko Epson Corporation | Liquid discharge apparatus, head unit, capacitive load drive circuit, and integrated circuit device for capacitive load drive |

| US9555624B2 (en) | 2015-02-03 | 2017-01-31 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9475284B2 (en) | 2015-02-04 | 2016-10-25 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9579886B2 (en) | 2015-02-04 | 2017-02-28 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US9475283B2 (en) | 2015-02-17 | 2016-10-25 | Seiko Epson Corporation | Liquid discharging apparatus, head unit, capacitive load driving circuit, and control method of capacitive load driving circuit |

| US10245827B2 (en) | 2015-03-20 | 2019-04-02 | Seiko Epson Corporation | Liquid ejecting device, driver circuit, and head unit |

| US9555625B2 (en) | 2015-03-20 | 2017-01-31 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9421762B1 (en) | 2015-03-20 | 2016-08-23 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9975332B2 (en) | 2015-03-20 | 2018-05-22 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| EP3112159A2 (en) | 2015-07-01 | 2017-01-04 | Seiko Epson Corporation | Liquid discharge device and head unit |

| US9744761B2 (en) | 2015-07-01 | 2017-08-29 | Seiko Epson Corporation | Liquid discharge device and head unit |

| US9656462B2 (en) | 2015-08-26 | 2017-05-23 | Seiko Epson Corporation | Liquid ejecting apparatus |

| US9669621B2 (en) | 2015-08-27 | 2017-06-06 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| JP2017043007A (en) * | 2015-08-27 | 2017-03-02 | セイコーエプソン株式会社 | Liquid discharge device and head unit |

| US9937712B2 (en) | 2015-08-27 | 2018-04-10 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US10493755B2 (en) | 2015-10-09 | 2019-12-03 | Seiko Epson Corporation | Driving circuit for capacitive load |

| US10179449B2 (en) | 2015-10-09 | 2019-01-15 | Seiko Epson Corporation | Liquid ejecting apparatus and head unit |

| US9862184B2 (en) | 2015-10-26 | 2018-01-09 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| JP2016074227A (en) * | 2015-12-24 | 2016-05-12 | セイコーエプソン株式会社 | Driving circuit and driving method for driving liquid discharge head |

| US9956767B2 (en) | 2016-02-26 | 2018-05-01 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US9925766B2 (en) | 2016-02-26 | 2018-03-27 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US10044343B2 (en) | 2016-02-26 | 2018-08-07 | Seiko Epson Corporation | Drive circuit, and control method of drive circuit |

| US9908329B2 (en) | 2016-02-26 | 2018-03-06 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10265948B2 (en) | 2016-02-26 | 2019-04-23 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and head unit |

| US10000058B2 (en) | 2016-03-18 | 2018-06-19 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US10022960B2 (en) | 2016-03-18 | 2018-07-17 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US9849670B2 (en) | 2016-03-18 | 2017-12-26 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US10035342B2 (en) | 2016-07-08 | 2018-07-31 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and integrated circuit |

| US9981466B2 (en) | 2016-08-08 | 2018-05-29 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10086605B2 (en) | 2016-09-26 | 2018-10-02 | Seiko Epson Corporation | Liquid ejecting apparatus, drive circuit, and driving method |

| JP2017019296A (en) * | 2016-11-04 | 2017-01-26 | セイコーエプソン株式会社 | Printing device and printing method |

| JP2017019295A (en) * | 2016-11-04 | 2017-01-26 | セイコーエプソン株式会社 | Printing device and printing method |

| US10286655B2 (en) | 2017-03-06 | 2019-05-14 | Seiko Epson Corporation | Liquid ejecting apparatus and capacitive load drive circuit |

| EP3372406A1 (en) | 2017-03-06 | 2018-09-12 | Seiko Epson Corporation | Liquid ejecting apparatus and capacitive load drive circuit |

| CN108621563A (en) * | 2017-03-23 | 2018-10-09 | 精工爱普生株式会社 | Printing equipment and printing equipment power supply unit |

| US10457041B2 (en) | 2017-07-06 | 2019-10-29 | Seiko Epson Corporation | Liquid discharge apparatus, circuit substrate, and integrated circuit device |

| US10464316B2 (en) | 2017-07-06 | 2019-11-05 | Seiko Epson Corporation | Liquid discharge apparatus, circuit substrate, and integrated circuit device |

| US10821727B2 (en) | 2017-11-30 | 2020-11-03 | Seiko Epson Corporation | Liquid ejecting apparatus and drive circuit |

| US10875294B2 (en) | 2018-02-26 | 2020-12-29 | Seiko Epson Corporation | Liquid ejecting apparatus |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010114711A (en) | Power-amplifying device | |

| JP5245767B2 (en) | Actuator driving method and power amplifier | |

| JP5471325B2 (en) | Liquid ejecting apparatus, printing apparatus, and surgical tool | |

| JP5256768B2 (en) | Liquid ejector | |

| JP5320975B2 (en) | Pulse width modulation circuit and fluid ejection device | |

| JP6187756B2 (en) | Liquid ejection device | |

| JP5212336B2 (en) | Liquid ejecting apparatus, liquid ejecting printing apparatus, and driving method of liquid ejecting apparatus | |

| JP2011005733A (en) | Fluid ejection device and fluid ejection printer | |

| JP2009154477A (en) | Liquid jet device and its drive method | |

| JP4811501B2 (en) | Capacitive load driving circuit, liquid ejecting apparatus, and printing apparatus | |

| JP2010114500A (en) | Power amplifying device | |

| JP5163207B2 (en) | Liquid ejecting apparatus and printing apparatus | |

| JP2011088294A (en) | Power amplifying circuit, liquid jet apparatus, and liquid jet type printer | |

| JP5521315B2 (en) | Power amplifier, liquid ejecting apparatus, and liquid ejecting printing apparatus | |

| JP2009196197A (en) | Liquid jet device | |

| JP2009178950A (en) | Liquid jetting apparatus | |

| JP5585700B2 (en) | Drive circuit and liquid ejecting apparatus | |

| JP5024145B2 (en) | Liquid ejector | |

| JP5440684B2 (en) | Driving circuit | |

| JP2010125741A (en) | Liquid jet type printing apparatus | |

| JP2011025622A (en) | Liquid jetting apparatus and liquid jetting type printer | |

| JP5790801B2 (en) | Surgical tool | |

| JP2010124040A (en) | Power amplifying device | |

| JP2011093104A (en) | Liquid jet device and liquid jet type printer | |

| JP2013151164A (en) | Liquid jetting device, printing apparatus and method for driving liquid jetting device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111004 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111004 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120828 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120924 |