JP2010026607A - 情報処理装置および仮想回路書き込み方法 - Google Patents

情報処理装置および仮想回路書き込み方法 Download PDFInfo

- Publication number

- JP2010026607A JP2010026607A JP2008184301A JP2008184301A JP2010026607A JP 2010026607 A JP2010026607 A JP 2010026607A JP 2008184301 A JP2008184301 A JP 2008184301A JP 2008184301 A JP2008184301 A JP 2008184301A JP 2010026607 A JP2010026607 A JP 2010026607A

- Authority

- JP

- Japan

- Prior art keywords

- arithmetic

- circuit

- calculation

- data

- writing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 title claims description 28

- 238000004364 calculation method Methods 0.000 claims abstract description 186

- 230000015654 memory Effects 0.000 claims abstract description 82

- 238000012546 transfer Methods 0.000 claims description 54

- 238000012545 processing Methods 0.000 claims description 41

- 230000010365 information processing Effects 0.000 claims description 37

- 238000004891 communication Methods 0.000 claims description 31

- 230000000737 periodic effect Effects 0.000 claims description 10

- 230000005540 biological transmission Effects 0.000 claims description 3

- 230000008569 process Effects 0.000 description 14

- 238000010586 diagram Methods 0.000 description 11

- 230000006870 function Effects 0.000 description 7

- 238000004088 simulation Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 230000006872 improvement Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000004549 pulsed laser deposition Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 238000012800 visualization Methods 0.000 description 2

- 241001093575 Alma Species 0.000 description 1

- PEDCQBHIVMGVHV-UHFFFAOYSA-N Glycerine Chemical compound OCC(O)CO PEDCQBHIVMGVHV-UHFFFAOYSA-N 0.000 description 1

- 229920002153 Hydroxypropyl cellulose Polymers 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000012217 deletion Methods 0.000 description 1

- 230000037430 deletion Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 230000004927 fusion Effects 0.000 description 1

- 235000010977 hydroxypropyl cellulose Nutrition 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

- 239000002918 waste heat Substances 0.000 description 1

Images

Landscapes

- Multi Processors (AREA)

- Stored Programmes (AREA)

Abstract

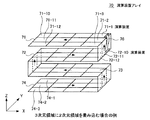

【解決手段】演算対象について所定の演算を行うアプリケーション・プログラムを記憶するメモリと、演算対象の各々の問題領域に対応して隣接する演算装置間で直接データ通信可能に接続されて配置され、またアプリケーション・プログラムの実行に用いられ各々の問題領域に対応した演算を行う演算回路が再構成され、隣接する演算装置間で問題領域についての演算結果データを送受信する複数の演算装置からなる演算装置アレイ40と、アプリケーション・プログラムを実行し、演算装置アレイ40を構成する各演算装置から各問題領域についての演算結果データを取得し、演算対象について演算結果を算出するホストプロセッサと、メモリ、ホストプロセッサおよび演算装置アレイ40との間で、データを通信するバスを備える。

【選択図】図4

Description

具体的には、本発明の一側面の情報処理装置は、メモリと、演算装置アレイと、ホストプロセッサと、バスを備えるように構成する。

メモリは、演算対象について所定の演算を行うアプリケーション・プログラムを記憶する。

演算装置アレイは、複数の演算装置から構成される。この複数の演算装置は、前記演算対象の各々の問題領域に対応して隣接する演算装置間で直接データ通信可能に接続されて配置され、また前記アプリケーション・プログラムの実行に用いられ前記各々の問題領域に対応した演算を行う演算回路が再構成され、隣接する演算装置間で前記問題領域についての演算結果データを送受信する。

ホストプロセッサは、前記アプリケーション・プログラムを実行し、前記演算装置アレイを構成する各演算装置から各問題領域についての演算結果データを取得し、前記演算対象について演算結果を算出する。

前記バスは、前記メモリ、前記ホストプロセッサおよび前記演算装置アレイとの間で、データを通信する。

1.本発明の一実施の形態に係る演算装置アレイの概念

2.隣接する演算装置との接続

3.情報処理装置の概要

4.情報処理装置の全体構成

5.ホストプロセッサの構成

6.演算装置(演算ボード、書き込み・入出力ボード)の構成

7.演算装置アレイによる演算処理

8.演算装置への書き込み処理

9.本発明の他の実施の形態に係る演算装置アレイ

10.本発明のさらに他の実施の形態に係る演算装置アレイ

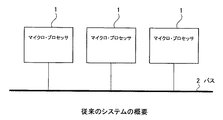

本発明に係る情報処理装置は、特許文献1(特開2003−208311号公報)に記載の技術をスーパーコンピュータ等のHPCに適用し、大規模演算をスケーラブルに行える基盤として、演算対象(対象問題)の構造を反映させて多数のPLD同士を相互接続したPLDアレイ(演算装置アレイ)を構成したものである。演算装置アレイは、PLDとして例えば大規模FPGAを搭載し、外部IO(入出力部)を大量に装備した小型のFPGAカード(演算装置)を、格子状に並べた構成を取る。

演算対象6は、流体モデルや液体モデルなどであり、1次元、2次元および3次元の任意の構造を取り得る。演算対象の具体例としては、例えば天文学や物理学分野において現在進められているALMAプロジェクトや重力波検出、さらには、次世代核融合実証炉等における炉設計、高エネルギー物理学分野においては、次世代加速器の内部反応予測シミュレーション、地球科学分野における様々な可視化シミュレーション(具体的には断層モデルの可視化等)、気象学的には中長期予報のためのシミュレーション分野の拡充等が要望として上がってきている。また、宇宙航空分野においては、人工衛星の機能設計や国際宇宙ステーションにおけるシミュレーション、将来の月への基地建設、有人火星探査におけるリスクシミュレーション等の分野からの要望も生じている。

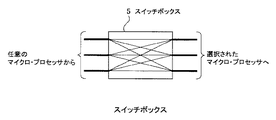

本発明の情報処理装置においては、上記のとおり隣接する演算装置間で直接データ転送できるように構成している。以下、この隣接する演算装置との接続の形態について、図5〜図7を参照して説明する。

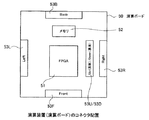

演算ボード50は、主に演算処理を担当する演算回路等(特許請求の範囲に記載された演算回路に相当)が書き込まれるFPGA51、主記憶装置として機能するメモリ52、および複数のコネクタ(接続端子)が設置された基板50Aを備える。また、書き込み・入出力ボード60は、演算ボード50のFPGAに演算回路等を書き込むための書き込み回路およびデータ転送用の入出力回路等が書き込まれるFPGA61、主記憶装置として機能するメモリ62、および複数のコネクタ(接続端子)が設置された基板60Aを備える。各コネクタは、演算ボード50の基板50Aおよび書き込み・入出力ボード60の基板60A上の各辺の所定位置に設けられる。演算ボード50と書き込み・入出力ボード60の機能等の詳細については後述する。

次に、上述のような構成の演算装置アレイを用いた情報処理装置の概要について説明する。

本実施の形態における情報処理装置は、例えば、CPUなどからなるホストプロセッサ11と、実際のメモリ空間を構築するメモリ12と、仮想回路空間を構築するPLD13とを備える。

ここでは、ハードウェア・オブジェクト26に対する読み書きの要求がアプリケーション21から、順次、要求を伝えてハードウェア・ネット29にまで伝えて応答を返すまで処理が続く。この時、ハードウェア・ネット29は並列動作を行う。アプリケーション21はハードウェア・オブジェクト26に実行を命令して、返答を待たずに、次の処理、例えば、別のハードウェア・オブジェクト26の実行を行っていく。ハードウェア・ネット29の処理が終了したかどうかを調べる処理を行いハードウェア・オブジェクト26のメンバー変数の値を読み取る。このように、アプリケーション21のレベルでの並列処理にあった形で、ハードウェア・オブジェクト26すなわち演算回路を含む組み込み回路の並列性を適切に利用することができる。

まず、アプリケーション21が起動されると、OSはアプリケーション21の実行に必要な領域をアプリケーション21が排他的に使用できるように確保して制御をアプリケーション21に渡す。アプリケーション21の起動・初期化プログラムは、プログラムで使用されるイベント管理、メッセージ管理等のOSとの通信やアプリケーション21内での管理に必要な基盤部分の立ち上げを行う。なお、ハードウェア・オブジェクト26の管理に必要な管理制御部分もこの時にアプリケーション部に組み込まれる。

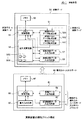

図10は、情報処理装置の全体構成を示す図である。

本実施の形態における情報処理装置は、例えば、ホストプロセッサ11と、主記憶装置としてのメモリ12と、仮想回路空間であるハードウェア・モジュール30と、演算対象の各問題領域について演算を行う演算装置アレイ40とを備える。

演算装置アレイ40はハードウェア・モジュールの一種であり、図4に示した例では3次元構造であるが、ここでは説明の便宜のため2次元構造で表現してある。また、ホストプロセッサ11、メモリ12、およびハードウェア・モジュール30は、所定の規格(PCI規格等)のバス14を通じて高速なデータ転送が可能となっている。

図11に、ホストプロセッサの階層構成図を示す。

ホストプロセッサ11は、アプリケーション21、オブジェクト・マネジャー22、ハードウェア・モジュール・ドライバ23、OS24、バス25を備える。この例では、アプリケーション21を3つ含む例を示しているが、適宜の数のアプリケーションを有することができる。各アプリケーション21は、ひとつ又は複数のハードウェア・オブジェクト26、ハードウェア・ドライバ27、アプリケーション21とハードウェア・ドライバ27との入出力を制御するインターフェース28の組を有する。

図12は、演算装置(演算ボード、書き込み・入出力ボード)の仮想回路書き込み後の機能を示すブロック図である。以下、図12を参照して、演算ボード50、書き込み・入出力ボード60の順に説明する。

f(i, j, k) = F(i-1, j-1, k-1, i, j, k, i+1, j+1, k+1)

次に、図10に示した演算装置アレイ40を例に演算処理の概要を説明する。

前提として、演算装置アレイ40を構成する各演算装置40−1の演算ボード50および書き込み・入出力ボード60に、各々が担当する演算対象の問題領域に合わせてhwNet29である仮想回路(図12参照)が書き込まれた状態であるとする。演算を行う順番は、演算対象の物理現象や特性等に基づいて決定される。ここでは演算装置「00」,演算装置「10」,演算装置「20」から演算を開始して横方向へ順に移動していき、末端の演算装置「03」,演算装置「13」,演算装置「23」で演算を終了する場合を想定する。

このように構成したことにより、隣接する演算装置40−1間のデータ転送処理が情報処理装置の処理能力のボトルネックになることを回避することができる。

次に、図13および図14を参照して、演算装置アレイを構成する各演算装置に対する演算回路等の書き込み処理を説明する。図13は、演算回路等書き込み処理を示すフローチャートである。図14は、演算回路等書き込み処理時の状態遷移を示すものである。

この例では、第1の演算装置の演算ボード50−1と隣接する第2の演算装置の演算ボード50−2が接続し、第1の演算装置の書き込み・入出力ボード60−1と隣接する第2の演算装置の書き込み・入出力ボード60−2が接続している。第1の演算装置はハードウェア・モジュールを介してハードウェア・モジュール30(ホストプロセッサ11側)と接続しているとする。

3次元構造の演算装置アレイ40において、図12に示したように、一つの演算装置40−1の演算ボード50には、隣接FPGAデータ転送回路が3対ある。この隣接FPGAデータ転送回路の接続先を電気的に変えることで、3次元領域の中に2次元領域を畳み込むことができる。すなわち、3次元に構成した演算装置アレイの各演算装置を電気的に制御することにより、2次元または3次元の演算装置アレイとして使用することが可能になる。

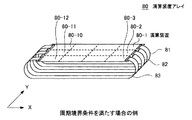

次に、演算対象が周期境界条件を満たす場合の演算装置アレイについて説明する。

演算対象が周期境界条件を満たす場合、演算装置アレイを構成する複数のハードウェア・ネットすなわち演算装置のうち周期境界に位置する演算装置同士を電気的に接続し、トーラス状(円環)を形成する。

Claims (10)

- 演算対象について所定の演算を行うアプリケーション・プログラムを記憶するメモリと、

前記演算対象の各々の問題領域に対応して隣接する演算装置間で直接データ通信可能に接続されて配置され、また前記アプリケーション・プログラムの実行に用いられ前記各々の問題領域に対応した演算を行う演算回路が再構成され、隣接する演算装置間で前記問題領域についての演算結果データを送受信する複数の演算装置からなる演算装置アレイと、

前記アプリケーション・プログラムを実行し、前記演算装置アレイを構成する各演算装置から各問題領域についての演算結果データを取得し、前記演算対象について演算結果を算出するホストプロセッサと、

前記メモリ、前記ホストプロセッサおよび前記演算装置アレイとの間で、データを通信するバスと、を含む

情報処理装置。 - 前記複数の演算装置は、ホストプロセッサによって予め決められた演算結果の転送先に従い、当該演算装置の演算結果データを隣接する所定の演算装置に転送する

請求項1に記載の情報処理装置。 - 前記演算装置アレイを構成する前記複数の演算装置に対して、前記ホストプロセッサの指示に基づいて、前記演算回路を書き込むための仮想回路データ書き込み回路を所定の順序で書き込む

請求項2に記載の情報処理装置。 - 前記演算装置アレイを構成する前記複数の演算装置において、全ての演算装置について前記仮想回路データ書き込み回路の書き込みが終了後、前記仮想回路データ書き込み回路が最後に書き込まれた演算装置から最初に書き込まれた演算装置まで前記全ての演算装置について前記演算回路を書き込む

請求項3に記載の情報処理装置。 - 前記演算装置は、前記演算回路が書き込まれる演算ボードと、前記仮想回路データ書き込み回路が書き込まれる書き込みボードから一対の演算装置が構成される

請求項4に記載の情報処理装置。 - 前記演算装置アレイを構成する前記複数の演算装置において、前記演算回路の書き込みとともに、前記ホストプロセッサと送受信するデータを転送するためのデータ入出力回路を書き込む

請求項5に記載の情報処理装置。 - 前記演算装置の前記演算ボードは、上下左右前後の隣接する演算ボードと接続するための第1のコネクタおよび対をなす前記書き込みボードと接続するための第2のコネクタを備え、また前記書き込みボードは、対をなす前記演算ボードと接続するための第3のコネクタを備え、

前記演算ボードの演算回路は、第1のコネクタを介して隣接する演算ボードの演算回路と前記演算結果データの送受信を行うとともに、第2および第3のコネクタを介して前記書き込みボードの前記書き込み回路および前記データ入出力回路とデータの送受信を行う

請求項6に記載の情報処理装置。 - 前記ホストプロセッサは、前記演算装置アレイを構成する複数の演算ボードのうち所定の演算ボード同士を第1のコネクタを介して電気的に接続するように制御する

請求項7に記載の情報処理装置。 - 前記演算対象が周期境界条件を満たす場合、前記ホストプロセッサは、前記演算装置アレイを構成する複数の演算装置のうち周期境界に該当する演算装置同士を第1のコネクタを介して電気的に接続するように制御する

請求項7に記載の情報処理装置。 - 演算対象の各々の問題領域に対応して隣接する演算装置間で直接データ通信可能に接続されて配置された複数の演算装置の各々に対して、ホストプロセッサの指示に基づき演算回路を書き込むための仮想回路データ書き込み回路を所定の順序で書き込むステップと、

全ての演算装置について前記仮想回路データ書き込み回路の書き込みが終了後、前記仮想回路データ書き込み回路が最後に書き込まれた演算装置から最初に書き込まれた演算装置まで前記全ての演算装置について前記演算回路を書き込むステップと、

を含む仮想回路書き込み方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008184301A JP5315517B2 (ja) | 2008-07-15 | 2008-07-15 | 情報処理装置および仮想回路書き込み方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008184301A JP5315517B2 (ja) | 2008-07-15 | 2008-07-15 | 情報処理装置および仮想回路書き込み方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010026607A true JP2010026607A (ja) | 2010-02-04 |

| JP5315517B2 JP5315517B2 (ja) | 2013-10-16 |

Family

ID=41732412

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008184301A Expired - Fee Related JP5315517B2 (ja) | 2008-07-15 | 2008-07-15 | 情報処理装置および仮想回路書き込み方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5315517B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2014185462A1 (ja) * | 2013-05-17 | 2017-02-23 | 日本電気株式会社 | 基板と基板装置及び基板接続方法 |

| CN111859829A (zh) * | 2019-04-04 | 2020-10-30 | 北京比特大陆科技有限公司 | 控制算力板的方法、装置和设备以及介质、程序产品 |

| US10884794B2 (en) | 2016-08-09 | 2021-01-05 | Fujitsu Limited | Control apparatus for information processing system, computer-readable non-transitory recording medium having program stored therein, and information processing method which allocate processes executed to acquire desired result to processing apparatus to perform for pipeline processing |

| JP2023517172A (ja) * | 2020-03-06 | 2023-04-24 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 3次元メッシュ・トポロジにおけるコンピューティング・ノードの構成 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09282295A (ja) * | 1996-04-11 | 1997-10-31 | Sanyo Electric Co Ltd | 並列計算機のためのプロセサ間データ転送方法 |

| JP2003208311A (ja) * | 2002-01-15 | 2003-07-25 | Japan Science & Technology Corp | 半導体回路制御装置及び半導体回路制御プログラム |

-

2008

- 2008-07-15 JP JP2008184301A patent/JP5315517B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09282295A (ja) * | 1996-04-11 | 1997-10-31 | Sanyo Electric Co Ltd | 並列計算機のためのプロセサ間データ転送方法 |

| JP2003208311A (ja) * | 2002-01-15 | 2003-07-25 | Japan Science & Technology Corp | 半導体回路制御装置及び半導体回路制御プログラム |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2014185462A1 (ja) * | 2013-05-17 | 2017-02-23 | 日本電気株式会社 | 基板と基板装置及び基板接続方法 |

| US10884794B2 (en) | 2016-08-09 | 2021-01-05 | Fujitsu Limited | Control apparatus for information processing system, computer-readable non-transitory recording medium having program stored therein, and information processing method which allocate processes executed to acquire desired result to processing apparatus to perform for pipeline processing |

| CN111859829A (zh) * | 2019-04-04 | 2020-10-30 | 北京比特大陆科技有限公司 | 控制算力板的方法、装置和设备以及介质、程序产品 |

| CN111859829B (zh) * | 2019-04-04 | 2024-04-16 | 北京比特大陆科技有限公司 | 控制算力板的方法、装置和设备以及介质、程序产品 |

| JP2023517172A (ja) * | 2020-03-06 | 2023-04-24 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 3次元メッシュ・トポロジにおけるコンピューティング・ノードの構成 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5315517B2 (ja) | 2013-10-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12346729B2 (en) | Runtime virtualization of reconfigurable data flow resources | |

| JP7377852B2 (ja) | プログラマブル集積回路のための階層型部分的再構成 | |

| US11782729B2 (en) | Runtime patching of configuration files | |

| US7412586B1 (en) | Switch memory architectures | |

| US20190057060A1 (en) | Reconfigurable fabric data routing | |

| US11171652B2 (en) | Method and apparatus for implementing configurable streaming networks | |

| Iskandar et al. | Near-memory computing on fpgas with 3d-stacked memories: Applications, architectures, and optimizations | |

| JP5315517B2 (ja) | 情報処理装置および仮想回路書き込み方法 | |

| US20250251967A1 (en) | Multiple contexts for a compute unit in a reconfigurable data processor | |

| Nyboe et al. | Mpsoc4drones: An open framework for ros2, px4, and fpga integration | |

| CN1842762A (zh) | 数据处理装置 | |

| CN112748876A (zh) | 存储装置、存储控制器和操作神经处理器的方法 | |

| US20250328328A1 (en) | Operation Fusion in Reconfigurable Dataflow Processors | |

| Williams | Adaptive parallel meshes with complex geometry | |

| US12487965B2 (en) | All reduce across multiple reconfigurable dataflow processors | |

| Christodoulis et al. | An FPGA target for the StarPU heterogeneous runtime system | |

| Cicuttin et al. | HyperFPGA: A possible general purpose reconfigurable hardware for custom supercomputing | |

| Mohiyuddin | Tuning hardware and software for multiprocessors | |

| Nazar Shahsavani et al. | Efficient compilation and mapping of fixed function combinational logic onto digital signal processors targeting neural network inference and utilizing high-level synthesis | |

| Bellocchi et al. | RICHIE: a Framework for Agile Design and Exploration of RISC-V-Based Accelerator-Rich Heterogeneous SoCs | |

| Russo | Adaptation of High Performance and High Capacity Reconfigurable Systems to OpenCL Programming Environments | |

| US20250217125A1 (en) | Compiling and executing a high-level program based on a pre-segmented computational graph | |

| Glinskiy et al. | Supercomputer technologies for solving problems of computational physics | |

| US20240338340A1 (en) | Intelligent graph execution and orchestration engine for a reconfigurable data processor | |

| Melber | Fluid: Raising the Level of Abstraction for FPGA Accelerator Development without Compromising Performance |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20100414 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110707 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130314 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130604 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130613 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |