JP2010021637A - データ処理装置 - Google Patents

データ処理装置 Download PDFInfo

- Publication number

- JP2010021637A JP2010021637A JP2008178084A JP2008178084A JP2010021637A JP 2010021637 A JP2010021637 A JP 2010021637A JP 2008178084 A JP2008178084 A JP 2008178084A JP 2008178084 A JP2008178084 A JP 2008178084A JP 2010021637 A JP2010021637 A JP 2010021637A

- Authority

- JP

- Japan

- Prior art keywords

- encryption

- decryption

- encryption key

- key

- data processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000012545 processing Methods 0.000 claims description 125

- 238000000034 method Methods 0.000 claims description 99

- 230000008569 process Effects 0.000 claims description 92

- 238000012795 verification Methods 0.000 claims description 27

- 239000004065 semiconductor Substances 0.000 claims description 4

- 239000000758 substrate Substances 0.000 claims description 3

- 238000004364 calculation method Methods 0.000 description 69

- 238000004458 analytical method Methods 0.000 description 13

- 238000010586 diagram Methods 0.000 description 11

- 230000006870 function Effects 0.000 description 5

- 238000002347 injection Methods 0.000 description 5

- 239000007924 injection Substances 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 238000013478 data encryption standard Methods 0.000 description 4

- 238000001514 detection method Methods 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 230000005856 abnormality Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000003745 diagnosis Methods 0.000 description 1

- 230000036541 health Effects 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Abstract

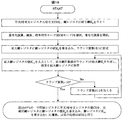

【解決手段】データ処理装置は、暗号鍵を用いて平文の暗号化と暗号文の復号を行うプロセッサ(7)を備える。前記プロセッサは、前記暗号化又は復号を当初の演算として行ったとき、当該当初の演算の逆算を行い、この逆算において最終的に用いた暗号鍵を外部からアクセス可能に保持する記憶回路(24)を有する。これにより、前記当初の演算で最初に用いた暗号鍵がデータ処理装置内で管理されているとき、その管理主体は、記憶回路が保有する前記逆算において最終的に用いた暗号鍵をアクセスする事によって、双方が一致するか否かによって、単なる逆算では検出不可能な故障攻撃の検出が可能になる。

【選択図】図1

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

実施の形態について更に詳述する。以下、本発明を実施するための形態を図面に基づいて詳細に説明する。なお、発明を実施するための形態を説明するための全図において、同一の機能を有する要素には同一の符号を付して、その繰り返しの説明を省略する。

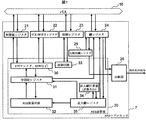

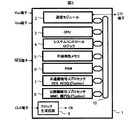

図2には本発明の一例に係るICカード用マイコンのブロックダイヤグラムが例示される。ICカード用マイコン1は、非接触又は接触インタフェースを行うための通信モジュール2、ICカード用マイコン1の全体的な制御を行う中央処理装置(CPU)3、ICカード用マイコンの割込みやリセット等の例外処理制御及び動作モードの制御等を行うシステムコントロールロジック4、CPU3の動作プログラムやデータテーブル等を保有する不揮発性メモリ5、CPU3のワーク領域等に用いられるRAM6、DEA又はAES等に準拠する共通鍵暗号プロセッサ7、べき乗剰余乗算や楕円暗号演算等を行う公開鍵暗号プロセッサ8、及びICカード用マイコン1の動作基準クロックとされるクロック信号CKを生成するクロック生成回路9等を有する。10は内部バスである。不揮発性メモリ5にはマスクROM、EEPROM、又はフラッシュメモリ等を採用すればよい。このICカード用マイコン1は、例えば単結晶シリコン等の1個の半導体基板にCMOS等の集積回路製造技術によって構成される。

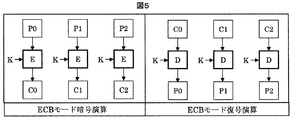

図1では暗号モードとして例えば図5のECBモードを用いる。図5の標記から明らかなように、ECBモードにおいてEで示される暗号化演算とDで示される復号演算とはその処理内容が相違される。図7にはECBモードにおいける暗号化と復号の演算手法が例示される。ここでは、図5の一つのEで示される暗号化演算は図7のEncに示されるSe0〜Se10の複数ステップの繰り返しによって実現される。与えられた鍵Kは、ステップSe0〜Se10の各ステップにおいて順次K0〜K10に自律的に更新演算されて用いられる。K0=Kであり、K1〜K10を拡大鍵と称する。Se0〜Se10のサフィックス1〜10をラウンド数と称する。すなわちラウンドiのステップはSeiとなる。ステップSe0〜Se10の各ラウンドで符号化演算が行われ、PがM1に符号化され、M1がM2に符号化され、M2がM3に符号化され、最後にM10がCに符号化される事によって、平文Pが暗号文Cに暗号化される。図5の一つのDで示される復号演算は図7のDecに示されるSd0〜Sd10の複数ステップの繰り返しによって実現される。ステップSd0〜Sd10の各ステップにおいて鍵はK10〜K0に順次自律的に更新演算されて用いられる。復号においてもステップSd0〜Sd10のサフィックスをラウンド数と称する。ステップSd0〜Sd10の各ラウンドで復号演算が行われ、CがM10に復号され、M10がM9に復号され、M9がM8に復号され、最後にM1がPに復号される事によって、暗号文Cが平文Pに復号される。各ラウンドの暗号化、復号演算には例えば第1文献及び第2文献に記載の具体的な処理を適用すればよく、ここではその詳細な説明は省略する。

OFBモードにおける暗号化復号処理では図6に示されるように、暗号化も復号もEで示される“暗号処理”のアルゴリズムを共通に用いる。図8にはこの点が更に詳細に示される、Encの符号化もDecの復号も、入力IVに対して鍵Kを用いた暗号化処理(E)を共通に行い、暗号化ではその暗号化処理(E)結果Rに対して平文P0との排他的論理和を採って暗号文C0を生成し、復号ではその暗号化処理(E)結果Rに対して暗号文C0との排他的論理和を採って平文P0を生成する。したがって暗号化に際して復号の逆演算を単純に行っても暗号化処理(E)が共通化されるので故障攻撃に対する検出の実効性は低い。暗号化処理(E)は例えば今までで説明したECBモードにおけるEの暗号化処理と同じである。

2 通信モジュール

3 中央処理装置(CPU)

4 システムコントロールロジック

5 不揮発性メモリ

6 RAM

7,7A,7B,7C 共通鍵暗号プロセッサ

8 公開鍵暗号プロセッサ

9 クロック生成回路

10 内部バス

20,20A,20B,20C AES演算部

21 初期値レジスタ

22 平文/暗号文レジスタ

23 制御レジスタ

24 鍵レジスタ

25 比較用鍵レジスタ

26,41,51,52 比較器

30 インタフェース回路(I/F)

31,31a,31b 中間値レジスタ

32 AES演算回路

33,33A,33B,33C 制御回路

34 拡大鍵計算回路

35,35a,35b 拡大鍵レジスタ

40 拡大鍵保管レジスタ

50 比較用レジスタ

Claims (21)

- 暗号鍵を用いて平文の暗号化と暗号文の復号を行うプロセッサを備えたデータ処理装置であって、

前記プロセッサは、前記暗号化又は復号を当初の演算として行ったとき、当該当初の演算の逆算を行い、この逆算において最終的に用いた暗号鍵を外部からアクセス可能に保持する記憶回路を有する、データ処理装置。 - 暗号鍵を用いて平文の暗号化と暗号文の復号を行うプロセッサを備えたデータ処理装置であって、

前記プロセッサは、前記暗号化又は復号を当初の演算として行ったとき、当該当初の演算の逆算を行い、この逆算において最終的に用いた暗号鍵が当初の演算で最初に用いた暗号鍵に一致すか否かを検証する、データ処理装置。 - プロセッサを備えたデータ処理装置であって、

前記プロセッサは、その外部から入力した暗号鍵の初期値に基づいて順次更新した暗号鍵を用いた演算を順次複数回繰り返して暗号化を行い、また、外部から入力した暗号鍵に基づいて順次更新した暗号鍵を用いた演算を順次複数回繰り返して復号を行い、暗号化の演算又は復号の演算に用いた最新の前記更新した暗号鍵を外部からアクセス可能に保持する記憶回路を有する、データ処理装置。 - 前記プロセッサを制御する中央処理装置を更に有し、前記記憶回路は前記中央処理措置のアドレス空間に配置される、請求項3記載のデータ処理装置。

- 前記記憶回路は、前記暗号鍵の初期値が中央処理装置によって書き込まれる領域であって、その後、暗号鍵の初期値に基づいて順次更新した最新の暗号鍵によって書き換えられる領域である、請求項4記載のデータ処理装置。

- 前記プロセッサは平文の暗号化に際して、その暗号化の結果に対し、当該暗号化の最後の暗号化演算で用いた暗号鍵を初期値とする復号を逆演算として行い、当該復号の最後に用いた暗号鍵を前記記憶回路に書き込む、請求項3記載のデータ処理装置。

- 前記プロセッサは暗号文の復号に際して、前記暗号鍵の初期値を暗号化の場合と同様に繰り返し更新して暗号化の最後に用いる暗号鍵を生成し、生成した当該暗号鍵を初期値に用いた復号演算を順次複数回繰り返して復号を行い、復号の最後に用いた暗号鍵を前記記憶回路に書き込む、請求項3記載のデータ処理装置。

- 前記記憶回路に書き込まれた前記復号の最後に用いた暗号鍵と、前記暗号化の最初に用いた暗号鍵とが一致するか否かを判別する比較器を更に有する、請求項6又は7記載のデータ処理装置。

- 前記比較器による不一致の判別結果は例外処理を要求する信号であり、

前記例外処理が要求される中央処理装置を更に有する、請求項8記載のデータ処理装置。 - 前記例外処理は前記中央処理装置のリセット例外処理である、請求項9記載のデータ処理装置。

- プロセッサを備えたデータ処理装置であって、

前記プロセッサは、その外部から入力した暗号鍵の初期値に基づいて順次更新した暗号鍵を用いた演算を順次複数回繰り返す単位暗号化を複数単位分だけ直列的に実行して暗号化を行い、また、外部から入力した暗号鍵に基づいて順次更新した暗号鍵を用いた演算を順次複数回繰り返す単位復号を複数単位分だけ直列的に実行して復号を行い、

前記単位暗号化は、外部から入力した暗号鍵の初期値に基づいて順次更新した暗号鍵を用いた暗号化演算を順次複数回繰り返す暗号化処理とその暗号化処理による処理結果を用いる暗号化論理演算とから成り、

前記単位復号は、外部から入力した暗号鍵の初期値に基づいて順次更新した暗号鍵を用いた前記暗号化演算を順次複数回繰り返す暗号化処理とその暗号化処理による処理結果を用いる復号論理演算とから成り、

前記プロセッサは、前記暗号化において前ブロックの単位暗号化の暗号化処理の結果を受ける次ブロックの単位暗号化の暗号化処理に並行して、前記前ブロックの単位暗号化の暗号化処理の結果を用いて単位暗号化の暗号化処理の逆演算として復号処理を行い、前記逆演算に用いた最新の前記更新した暗号鍵を外部からアクセス可能に保持する記憶回路を有する、データ処理装置。 - 前記プロセッサは、前記復号において前ブロックの単位復号の暗号化処理の結果を受ける次ブロックの単位復号の暗号化処理に並行して、前記前ブロックの単位復号の暗号化処理の結果を用いて単位暗号化の暗号化処理の逆演算として復号処理を行い、

前記記憶回路は、前記逆演算に用いた最新の前記更新した暗号鍵を外部からアクセス可能に保持する、請求項11記載のデータ処理装置。 - 前記プロセッサを制御する中央処理装置を更に有し、前記記憶回路は前記中央処理措置のアドレス空間に配置される、請求項12記載のデータ処理装置。

- 前記記憶回路は、前記暗号鍵の初期値が中央処理装置によって書き込まれる領域であって、その後、暗号鍵の初期値に基づいて順次更新した最新の暗号鍵によって書き換えられる領域である、請求項13記載のデータ処理装置。

- 前記暗号化論理演算及び前記復号論理演算は排他的論理和演算である、請求項12記載のデータ処理装置。

- 前記記憶回路に書き込まれた前記復号の最後に用いた暗号鍵と、前記暗号化の最初に用いた暗号鍵とが一致するか否かを判別する比較器を更に有する、請求項12記載のデータ処理装置。

- 前記比較器による不一致の判別結果は例外処理を要求する信号であり、

前記例外処理が要求される中央処理装置を更に有する、請求項16記載のデータ処理装置。 - 前記例外処理は前記中央処理装置のリセット例外処理である、請求項17記載のデータ処理装置。

- 前記プロセッサはAESに準拠する、請求項3又は12記載のデータ処理装置。

- データ処理装置は半導体基板に形成されたICカード用のマイクロコンピュータである、請求項3又は12記載のデータ処理装置。

- 前記プロセッサは、暗号アルゴリズムの暗号化機能のみを用いる暗号利用モードにおいて、復号処理による検算を処理する機能を備える請求項3又は11記載のデータ処理装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008178084A JP5483838B2 (ja) | 2008-07-08 | 2008-07-08 | データ処理装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008178084A JP5483838B2 (ja) | 2008-07-08 | 2008-07-08 | データ処理装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010021637A true JP2010021637A (ja) | 2010-01-28 |

| JP5483838B2 JP5483838B2 (ja) | 2014-05-07 |

Family

ID=41706136

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008178084A Expired - Fee Related JP5483838B2 (ja) | 2008-07-08 | 2008-07-08 | データ処理装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5483838B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019124713A (ja) * | 2018-01-11 | 2019-07-25 | Necプラットフォームズ株式会社 | 暗号化装置、復号装置、回線暗号システム、暗号化方法およびプログラム |

| JP2020109967A (ja) * | 2019-01-06 | 2020-07-16 | 新唐科技股▲ふん▼有限公司 | 被保護システム及び保護方法 |

| CN114830093A (zh) * | 2020-02-27 | 2022-07-29 | 三垦电气株式会社 | 异常检测电路以及异常检测方法 |

| JP2024513723A (ja) * | 2021-04-06 | 2024-03-27 | グーグル エルエルシー | 安全な暗号化コプロセッサ |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10154976A (ja) * | 1996-11-22 | 1998-06-09 | Toshiba Corp | タンパーフリー装置 |

| JP2005503069A (ja) * | 2001-09-04 | 2005-01-27 | エステーミクロエレクトロニクス ソシエテ アノニム | 秘密の量を保護する方法 |

| JP2005522912A (ja) * | 2002-04-08 | 2005-07-28 | オベルトゥル カード システムズ ソシエテ アノニム | 暗号化されたアクセスを使う電子的エンティティのセキュリティ化方法 |

-

2008

- 2008-07-08 JP JP2008178084A patent/JP5483838B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10154976A (ja) * | 1996-11-22 | 1998-06-09 | Toshiba Corp | タンパーフリー装置 |

| JP2005503069A (ja) * | 2001-09-04 | 2005-01-27 | エステーミクロエレクトロニクス ソシエテ アノニム | 秘密の量を保護する方法 |

| JP2005522912A (ja) * | 2002-04-08 | 2005-07-28 | オベルトゥル カード システムズ ソシエテ アノニム | 暗号化されたアクセスを使う電子的エンティティのセキュリティ化方法 |

Non-Patent Citations (3)

| Title |

|---|

| R. KARRI ET AL.: "Concurrent error detection schemes for fault-based side-channel cryptanalysis of symmetric block cip", IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, vol. 21, no. 12, JPN6013017180, December 2002 (2002-12-01), pages 1509 - 1517, XP002587894, ISSN: 0002520325, DOI: 10.1109/tcad.2002.804378 * |

| 佐藤証,他: "ブロック暗号AESの高性能エラー検出回路方式", マルチメディア,分散,協調とモバイル(DICOMO2008)シンポジウム論文集, JPN6013017182, 2 July 2008 (2008-07-02), pages 498 - 505, ISSN: 0002736006 * |

| 盛合志帆: "故障利用暗号攻撃によるブロック暗号の解読", 1997年暗号と情報セキュリティ・シンポジウム予稿集, vol. 6A, JPN6009029788, 30 January 1997 (1997-01-30), ISSN: 0002736007 * |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019124713A (ja) * | 2018-01-11 | 2019-07-25 | Necプラットフォームズ株式会社 | 暗号化装置、復号装置、回線暗号システム、暗号化方法およびプログラム |

| JP7063628B2 (ja) | 2018-01-11 | 2022-05-09 | Necプラットフォームズ株式会社 | 暗号化装置、暗号化方法およびプログラム |

| JP2020109967A (ja) * | 2019-01-06 | 2020-07-16 | 新唐科技股▲ふん▼有限公司 | 被保護システム及び保護方法 |

| CN114830093A (zh) * | 2020-02-27 | 2022-07-29 | 三垦电气株式会社 | 异常检测电路以及异常检测方法 |

| JP2024513723A (ja) * | 2021-04-06 | 2024-03-27 | グーグル エルエルシー | 安全な暗号化コプロセッサ |

| JP7699664B2 (ja) | 2021-04-06 | 2025-06-27 | グーグル エルエルシー | 安全な暗号化コプロセッサ |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5483838B2 (ja) | 2014-05-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN111095213B (zh) | 嵌入式程序的安全引导方法、装置、设备及存储介质 | |

| TWI822783B (zh) | 包括具有改善記憶體使用效率的安全處理器的系統晶片與記憶體系統以及操作系統晶片的方法 | |

| CN102737202B (zh) | 利用迭代加密/解密密钥更新的指令加密/解密设备和方法 | |

| CN101256613B (zh) | 无需制造者和用户知道彼此的加密信息的安全处理器系统 | |

| CN112699383B (zh) | 数据密码设备、存储器系统及其操作方法 | |

| US9418246B2 (en) | Decryption systems and related methods for on-the-fly decryption within integrated circuits | |

| US10650151B2 (en) | Method of execution of a binary code of a secure function by a microprocessor | |

| KR101546204B1 (ko) | 호스트 디바이스, 반도체 메모리 디바이스, 및 인증 방법 | |

| JP6182371B2 (ja) | 半導体集積回路を含むシステム | |

| CN101231622B (zh) | 基于闪存的数据存储方法和设备、及数据读取方法和设备 | |

| CN107408192A (zh) | 保护存储器 | |

| EP2831800B1 (en) | Method for protecting data | |

| US10862682B2 (en) | Nonce generation for encryption and decryption | |

| US9842214B2 (en) | System and method to secure on-board bus transactions | |

| US20210319143A1 (en) | Memory bus link authentication and encryption mechanisms for hardware-based replay protection | |

| CN105678173A (zh) | 基于硬件事务内存的vTPM安全保护方法 | |

| CN113343215A (zh) | 嵌入式软件的授权和认证方法及电子设备 | |

| TW201723804A (zh) | 安全模指數處理器、方法、系統、及指令 | |

| US9251098B2 (en) | Apparatus and method for accessing an encrypted memory portion | |

| JP5483838B2 (ja) | データ処理装置 | |

| US11442738B2 (en) | Method for executing a machine code of a secure function | |

| Sepulveda et al. | SEPUFSoC: Using PUFs for memory integrity and authentication in multi-processors system-on-chip | |

| US8311212B2 (en) | Method of processing data protected against attacks by generating errors and associated device | |

| KR101656092B1 (ko) | 비동기적인 인증을 갖는 보안 컴퓨팅 시스템 | |

| US9213864B2 (en) | Data processing apparatus and validity verification method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110701 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130419 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130502 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130625 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131114 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140107 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140130 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140218 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5483838 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |