JP2010015275A - データ処理システム及びプログラム開発システム - Google Patents

データ処理システム及びプログラム開発システム Download PDFInfo

- Publication number

- JP2010015275A JP2010015275A JP2008172955A JP2008172955A JP2010015275A JP 2010015275 A JP2010015275 A JP 2010015275A JP 2008172955 A JP2008172955 A JP 2008172955A JP 2008172955 A JP2008172955 A JP 2008172955A JP 2010015275 A JP2010015275 A JP 2010015275A

- Authority

- JP

- Japan

- Prior art keywords

- program

- cpu

- target device

- bus

- bus load

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Bus Control (AREA)

Abstract

【解決手段】メモリへのアクセスにおいてCPU又はDMA制御装置の間でバス占有権を調停するバス調停回路は、前記CPUからの前記メモリに対するアクセスによるバス負荷を定期的に計測してそのバス負荷情報を前記DMA制御装置へ送信する。前記DMA制御装置は、バス調停装置から受取ったバス負荷情報に基づいて、データ転送制御のデータ転送量を少なくする制御を行う。これによれば、定期的に計測されたバス負荷に従ってDMA制御装置によるバス占有時間を動的に変更することができる。

【選択図】図1

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

実施の形態について更に詳述する。以下、本発明を実施するための形態を図面に基づいて詳細に説明する。なお、発明を実施するための形態を説明するための全図において、同一の機能を有する要素には同一の符号を付して、その繰り返しの説明を省略する。

図1は本発明の第1の実施形態に係るデータ処理システムが例示される。データ処理システム1はデータプロセッサ若しくはマイクロコンピュータのような1チップであってもよいし、オンボードのマルチチップシステムであってもよい。データ処理システム1はそのプログラム開発システムとしての開発環境2と共に図示され、データ処理システム1を便宜上ターゲット機器1とも称する。

n=ceil(N×dT/T) (N<T−T/dT)

n=dT−1 (N≧T−T/dT)

ここで、関数ceil (x)は、xの小数点切り上げ関数とする。n=0のときは完全にCPU優先、n=dTのときは完全にDMA優先になってしまい、DMA転送サイズ切り替えの意味がなくなってしまうため、1≦n≦dT-1とする。

図7は本発明の第2の実施形態における、バス調停回路13の詳細図である。本発明においては、第1の実施形態とはバス負荷監視回路131におけるバス監視方式が相違される。CPUアクセス要求側のキューバッファ133はバッファ空き容量S20を出力し、バス負荷監視回路131はクロック信号S12とバッファ空き容量S20からDMA転送サイズ指定要求S03を出力する。バス負荷監視回路131はCPUアクセス要求S01の代わりに、CPUアクセス要求S01を蓄積するキューバッファ133の空き容量S20を用いることで、CPUアクセスに関するバス負荷を監視している。例えばキューバッファ133のライトポインタとリードポインタは空(記憶データ無し)の状態で値が一致され、書き込み毎にライトポインタがインクリメントされ、読出し毎にリードポインタがインクリメントされ、リードポインタはライトポインタの値を追い抜くことはないとすると、前記バッファ空き容量S20はライトポインタの値に対するリードポインタの値の差になる。

n=dtx - dT (dT<dtx<M(dT+1))

ここで、dtxはCPUからのDRAMアクセスの最長バスサイクル数として希望する値、Mはバッファ最大容量とする。n=0のときは完全にCPU優先、n=MdTのときは完全にDMA優先になってしまい、DMA転送サイズ切り替えの意味がなくなってしまうため、1≦n<MdTとする。

図9には本発明の第3の実施形態に係るデータ処理システム(ターゲット機器)1がその開発環境2と共に示される。第1及び第2の実施形態と異なる点は、CPU11がCPUアクセス要求S01のほかにキャッシュミス信号S24をバス調停回路13内のバス負荷監視回路131へ出力し、バス負荷監視回路131はキャッシュミス信号S24からバス負荷を計算してDMA転送サイズ指定要求S03を出力するところである。バス負荷監視回路131は、CPUアクセス要求S01の代わりにキャッシュミス信号S24を用いることで、CPUアクセスに関するバス負荷を監視している。

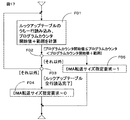

図13には本発明の第4の実施形態に係るデータ処理システム(ターゲット機器)1がその開発環境2と共に例示される。第1ないし第3の実施形態と異なる点は、CPU11がCPUアクセス要求S01のほかにプログラムカウンタの値S31をバス調停回路13内のバス負荷監視回路131へ出力し、バス負荷監視回路131はプログラムカウンタの値S31からバス負荷を計算してDMA転送サイズ指定要求S03を出力することである。バス負荷監視回路131は、CPUアクセス要求S01の代わりにプログラムカウンタの値S31を用いることで、CPUアクセスに関するバス負荷を監視している。

図21には本発明の第5の実施形態に係るデータ処理システム(ターゲット機器)1がその開発環境2と共に例示される。第1ないし第4の実施形態と異なる点は、DMA転送効率を上げるために、バス負荷監視回路131がDMA転送サイズ指定要求S03の代わりにDMA転送モード指定要求S33を出力し、DMA制御装置12におけるDMA転送モードを変更することである。要するに、CPUアクセスが少なければ、即ち所定の閾値を超えなければDMA転送モードをバーストモードとし、CPUアクセスが多ければ、即ち所定の閾値を超えればDMA転送モードをサイクルスチールモードとする。この場合の制御手法は前述の説明から極めて容易に類することができる内容であるからその詳細な説明は省略する。

図22には本発明の第6の実施形態に係るデータ処理システム(ターゲット機器)1がその開発環境2と共に例示される。第1ないし第5の実施形態と異なる点は、DMA転送効率を上げるために、バス負荷監視回路131がDMA転送サイズ指定要求S03およびDMA転送モード指定要求S33の両方を出力し、DMA制御装置12におけるDMA転送サイズおよびDMA転送モードを変更することである。

図24には本発明の第7の実施形態に係るデータ処理システム(ターゲット機器)1がその開発環境2と共に例示される。第1ないし第6の実施形態と異なる点は、CPUがCPUアクセス要求S01のほかにプログラムカウンタ値S31を出力しており、かつバス負荷監視回路がDMA転送サイズ指定要求S03およびDMA転送モード指定要求S33の両方を出力し、DMA制御装置12におけるDMA転送サイズおよびDMA転送モードを変更することである。

11 CPU

111 CPUコア

112 キャッシュ

113 キャッシュ用デマルチプレクサ

114 キャッシュ用マルチプレクサ

115 CPUコア用デマルチプレクサ

116 CPUコア用マルチプレクサ

12 DMA制御装置(DMAC)

121 レジスタ制御回路

1211 レジスタ書込内容生成部

1212 従来のレジスタ制御回路

1213 デマルチプレクサ

1214 マルチプレクサ

122 各種制御回路

123 バスI/F

124 各種レジスタ類

125 DMA制御装置内部バス

13 バス調停回路

131 バス負荷監視回路

13101 条件付カウンタ

13102 タイマ用カウンタ

13103 DMA転送サイズ判定用比較器

13104 タイマ信号生成用比較器

13105 サンプル&ホールド回路

13106 CPUアクセス要求数閾値格納メモリ

13107 CPUアクセス要求数計測周期格納メモリ

13108 バッファ空き容量時間積分器

13109 バッファ空き容量時間積分閾値格納メモリ

13110 バッファ空き容量時間積分値計測周期格納メモリ

13111 キャッシュミス信号数用条件付カウンタ

13112 キャッシュミス信号数閾値格納メモリ

13113 キャッシュミス信号計測周期格納メモリ

13114 ルックアップテーブル

131141 プログラムカウンタ開始値

131151 プログラムカウンタ範囲

132 DMA用キューバッファ

133 CPU用キューバッファ

134 優先順位判定回路

135 セレクタ

14 DRAM

15 プログラム専用RAM

16 プログラムI/F

17 バス

2 開発環境

21 プログラム

22 ビルダ

221 コンパイラ

222 リンカ

223 シミュレータ

224 プロファイラ

23 アップローダ

24 OS

25 PC

S01 CPUアクセス要求

S02 DMAアクセス要求

S03 DMA転送サイズ指定要求

S04 DRAMアクセス

S041 アクセス要求元識別子

S042 アクセス先アドレス

S043 アクセスサイズ

S044 リード/ライト判別子

S045 書き込みデータ

S05 プログラム実行形式

S06 プログラム内命令

S07 レジスタ書込内容

S071 DMA転送サイズ指定ビット

S08 各種信号

S09 レジスタ書込内容(DMA転送サイズ指定要求反映後)

S10 各種レジスタ初期化信号

S11 レジスタ内容

S12 クロック信号

S13 選択信号

S14 CPUアクセス要求数

S15 タイマ用カウンタ信号

S16 DMA転送サイズ指定要求連続値

S17 タイマ信号

S18 CPUアクセス要求数閾値信号

S19 CPUアクセス要求数計測周期信号

S20 CPU用キューバッファ空き容量

S21 CPU用キューバッファ空き容量時間積分値

S22 CPU用キューバッファ空き容量時間積分閾値

S23 CPU用キューバッファ空き容量時間積分値計測周期

S24 キャッシュミス信号

S25 キャッシュアクセス要求

S26 キャッシュ内データ

S27 キャッシュ関連デバッグ用データ

S28 キャッシュミス信号数

S29 キャッシュミス信号数閾値

S30 キャッシュミス信号数計測周期

S31 プログラムカウンタ値

S32 CPU関連デバッグ用データ

S33 DMA転送モード指定要求

C1 DMA転送サイズ32バイト設定

C2 DMA転送サイズ64バイト設定

C3 DMA転送サイズ32バイト/64バイト自動切換設定

C4 DMA転送サイクルスチールモード設定

C5 DMA転送バーストモード設定

C6 DMA転送サイクルスチール/バースト自動切換モード設定

C7 DMA転送量・転送方法自動切換モード設定

F01 プログラムカウンタ開始値+範囲計算処理

F02 プログラムカウンタ値判定処理

F03 ルックアップテーブル全文読込完了判定処理

F04 DMA転送サイズ0指定処理

F05 DMA転送サイズ1指定処理

F06 プログラムのコンパイル処理

F07 プログラムのリンク処理

F08 DMAアクセス間隔判定処理

F09 レジスタ設定値からDMAアクセス間隔を求める処理

F10 シミュレーション実行処理

F11 プロファイラ計測結果からDMAアクセス間隔を求める処理

F12 CPUアクセス計測間隔算出処理

F13 CPUアクセス要求数平均値算出処理

F14 CPUアクセス要求閾値計算処理

F15 プログラム再コンパイル処理

F16 プログラム再リンク処理

F17 プログラムアップロード処理

F18 ルックアップテーブル作成処理

F19 ルックアップテーブル順位判定処理

F20 DMA転送モード0設定処理

F21 DMA転送モード1設定処理

F22 CPUアクセス回数計算処理

T01 DMA転送サイズ32バイト固定時タイムチャート

T02 DMA転送サイズ自動切換時タイムチャート

T03 DRAMアクセスのオーバーヘッド時間

T04 DMAによる32バイトDRAMアクセスにかかる時間

T05 DMAによる64バイトDRAMアクセスにかかる時間

T06 DMA転送量切換タイミング境界線

T07 DMA転送量切換タイミング境界印

T08 DMA転送サイズ自動切換時の転送完了を示す境界線

T09 DMA転送サイズ32バイト固定時の転送完了を示す境界線

T10 CPUアクセス計測期間を示す矢印

T11 DMA転送サイズ自動切換時と固定時とのアクセス時間差

T12 CPUからのDRAMアクセスにかかる時間

T13 DMA転送サイズ自動切換時のCPUアクセス完了を示す境界線

T14 DMA転送サイズ固定時のCPUアクセス完了を示す境界線

T15 DMA転送サイズ自動切換時と固定時とのCPUアクセス時間差

T16 DMA転送サイズ64バイト固定時タイムチャート

Claims (11)

- データ転送量およびデータ転送方法が設定されるレジスタを有するDMA制御装置と、メモリへのアクセスにおいてCPU又は前記DMA制御装置の間でバス占有権を調停するバス調停回路とを有するデータ処理システムにおいて、

前記バス調停装置は、前記CPUからの前記メモリに対するアクセスによるバス負荷を定期的に計測してそのバス負荷情報を前記DMA制御装置へ送信するバス負荷監視回路を有し、

前記DMA制御装置は、前記バス負荷監視回路から受取ったバス負荷情報が所定のバス負荷を超えているときデータ転送制御によるデータ転送量を少なくする制御を行う、データ処理システム。 - 前記データ転送制御によるデータ転送量を少なくする制御は、サイクルスチールモードにおける1回のデータ転送量を減らす制御である、請求項1記載のデータ処理システム。

- 前記データ転送制御によるデータ転送量を少なくする制御は、データ転送制御モードをバーストモードからサイクルスチールモードに変更する制御である、請求項1記載のデータ処理システム。

- 前記バス負荷監視回路は、一定時間における前記CPUからのメモリアクセス回数を計測し、アクセス回数が閾値以上かどうかを表す信号を前記バス負荷情報として求める、請求項1項記載のデータ処理システム。

- 前記バス調停装置は、前記CPUからのメモリアクセス要求を一時的に蓄積し、空き記憶容量を前記バス監視回路へ送信するバッファを更に有し、

前記バス負荷監視回路は、一定時間における前記バッファのバッファ空き容量の積分値が閾値以上か否かを表す情報を前記バス負荷情報として前記DMA制御装置へ送信する、請求項1記載のデータ処理システム。 - 前記CPUは、キャッシュミスヒットが発生した際にキャッシュミス信号をバス調停回路へ送信するキャッシュメモリを有し、

前記バス負荷監視回路は、一定時間におけるキャッシュミス信号発生回数を計測し、キャッシュミス信号発生回数が閾値以上かどうかを表す情報を前記バス負荷情報として前記DMA制御装置へ送信する、請求項1記載のデータ処理システム。 - 前記CPUは実行すべき命令のアドレスを示すプログラムカウンタの値をバス調停回路へ出力し、

前記バス負荷監視回路は、前記CPUからのメモリアクセス回数の少ないルーチンまたはタスクにおけるプログラムカウンタの開始値および範囲をルックアップテーブルとして記憶し、入力した前記プログラムカウンタの値がテーブル内にヒットしたかどうかに関する情報を前記バス負荷として前記DMA制御装置へ送信する、請求項1記載のデータ処理システム。 - 請求項4記載のデータ処理システムをターゲット機器としてそのプログラムの開発を支援するプログラム開発システムであって、

前記ターゲット機器上で動作するプログラムのソースコードを実行形式に変換するビルダと、

該プログラム実行形式を前記ターゲット機器上へ転送するアップローダとを有し、

前記ビルダは、ターゲット機器を模擬しプログラムを実行するシミュレータと、

前記シミュレータによる実行結果に基づいて、前記ターゲット機器におけるメモリアクセス回数を複数回計測し、前記ターゲット機器のバス負荷監視回路におけるCPUからのメモリアクセス回数の閾値および計測周期を、プログラム実行時間が最短になるように求めるプロファイラと、を有し、

前記アップローダは、前記プロファイラで求められた前記CPUからのメモリアクセス回数の閾値および計測周期をプログラムと一緒に出力する、プログラム開発システム。 - 請求項5記載のデータ処理システムをターゲット機器としてそのプログラムの開発を支援するプログラム開発システムであって、

前記ターゲット機器上で動作するプログラムのソースコードを実行形式に変換するビルダと、

該プログラム実行形式を前記ターゲット機器上へ転送するアップローダとを有し、

前記ビルダは、ターゲット機器を模擬しプログラムを実行するシミュレータと、

前記シミュレータによる実行結果に基づいて、前記ターゲット機器におけるメモリアクセス回数を複数回計測し、前記ターゲット機器のバス負荷監視回路におけるバッファ空き容量の積分値の閾値および計測周期を、プログラム実行時間が最短になるように求めるプロファイラと、を有し、

前記アップローダは、前記プロファイラで求められた前記バッファ空き容量の積分値の閾値および計測周期をプログラムと一緒に出力する、プログラム開発システム。 - 請求項6記載のデータ処理システムをターゲット機器としてそのプログラムの開発を支援するプログラム開発システムであって、

前記ターゲット機器上で動作するプログラムのソースコードを実行形式に変換するビルダと、

該プログラム実行形式を前記ターゲット機器上へ転送するアップローダとを有し、

前記ビルダは、ターゲット機器を模擬しプログラムを実行するシミュレータと、

前記シミュレータによる実行結果に基づいて、前記ターゲット機器におけるメモリアクセス回数を複数回計測し、前記ターゲット機器のバス負荷監視回路におけるキャッシュミス回数の閾値および計測周期を、プログラム実行時間が最短になるように求めるプロファイラと、を有し、

前記アップローダは、前記プロファイラで求められた前記キャッシュミス回数の閾値および計測周期をプログラムと一緒に出力する、プログラム開発システム。 - 請求項7記載のデータ処理システムをターゲット機器としてそのプログラムの開発を支援するプログラム開発システムであって、

前記ターゲット機器上で動作するプログラムのソースコードを実行形式に変換するビルダと、

該プログラム実行形式を前記ターゲット機器上へ転送するアップローダとを有し、

前記ビルダは、ターゲット機器を模擬しプログラムを実行するシミュレータと、

前記シミュレータによる実行結果に基づいて、前記ターゲット機器におけるメモリアクセス回数を複数回計測し、前記ターゲット機器のバス負荷監視回路におけるCPUからのメモリアクセス回数の少ないルーチンまたはタスクにおけるプログラムカウンタの開始値および範囲を示すルックアップテーブルを求めるプロファイラと、を有し、

前記アップローダは、前記プロファイラで求められたルックアップテーブルをプログラムと一緒に出力するプログラム開発システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008172955A JP4871921B2 (ja) | 2008-07-02 | 2008-07-02 | データ処理システム及びプログラム開発システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008172955A JP4871921B2 (ja) | 2008-07-02 | 2008-07-02 | データ処理システム及びプログラム開発システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010015275A true JP2010015275A (ja) | 2010-01-21 |

| JP4871921B2 JP4871921B2 (ja) | 2012-02-08 |

Family

ID=41701354

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008172955A Expired - Fee Related JP4871921B2 (ja) | 2008-07-02 | 2008-07-02 | データ処理システム及びプログラム開発システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4871921B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012066621A1 (ja) | 2010-11-15 | 2012-05-24 | 富士通株式会社 | 情報処理システム |

| US10565152B2 (en) | 2017-04-27 | 2020-02-18 | Canon Kabushiki Kaisha | Transfer device, control device, transfer method, and multifunction peripheral |

| CN113590512A (zh) * | 2021-07-30 | 2021-11-02 | 眸芯科技(上海)有限公司 | 可直连外设设备的自启动dma装置及应用 |

-

2008

- 2008-07-02 JP JP2008172955A patent/JP4871921B2/ja not_active Expired - Fee Related

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012066621A1 (ja) | 2010-11-15 | 2012-05-24 | 富士通株式会社 | 情報処理システム |

| US9043507B2 (en) | 2010-11-15 | 2015-05-26 | Fujitsu Limited | Information processing system |

| US10565152B2 (en) | 2017-04-27 | 2020-02-18 | Canon Kabushiki Kaisha | Transfer device, control device, transfer method, and multifunction peripheral |

| CN113590512A (zh) * | 2021-07-30 | 2021-11-02 | 眸芯科技(上海)有限公司 | 可直连外设设备的自启动dma装置及应用 |

| CN113590512B (zh) * | 2021-07-30 | 2023-09-29 | 眸芯科技(上海)有限公司 | 可直连外设设备的自启动dma装置及应用 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4871921B2 (ja) | 2012-02-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102668599B1 (ko) | 하드웨어 가속을 위한 하드웨어 리소스들의 임베디드 스케줄링 | |

| EP1899828B1 (en) | Device and method for arbitrating between direct memory access task requests | |

| US7437618B2 (en) | Method in a processor for dynamically during runtime allocating memory for in-memory hardware tracing | |

| US8527812B2 (en) | Information processing device | |

| EP1899825B1 (en) | Device and method for controlling multiple dma tasks | |

| US7421619B2 (en) | Method in a processor for performing in-memory tracing using existing communication paths | |

| US7913123B2 (en) | Concurrently sharing a memory controller among a tracing process and non-tracing processes using a programmable variable number of shared memory write buffers | |

| US20090007076A1 (en) | Synchronizing Triggering of Multiple Hardware Trace Facilities Using an Existing System Bus | |

| JP4813485B2 (ja) | バーストリードライト動作による処理装置 | |

| US9009368B2 (en) | Interrupt latency performance counters | |

| US20060184837A1 (en) | Method, apparatus, and computer program product in a processor for balancing hardware trace collection among different hardware trace facilities | |

| JP2007241918A (ja) | プロセッサ装置 | |

| US20140129784A1 (en) | Methods and systems for polling memory outside a processor thread | |

| US8190924B2 (en) | Computer system, processor device, and method for controlling computer system | |

| JP4871921B2 (ja) | データ処理システム及びプログラム開発システム | |

| EP1899827A1 (en) | Device and method for executing a dma task | |

| US8812783B2 (en) | Operation apparatus, cache apparatus, and control method thereof | |

| CN112559403B (zh) | 一种处理器及其中的中断控制器 | |

| CN114514504A (zh) | 管理上游资源的同时进行的限流 | |

| EP3066559B1 (en) | Logic analyzer for detecting hangs | |

| US7761280B2 (en) | Data processing apparatus simulation by generating anticipated timing information for bus data transfers | |

| US8667233B2 (en) | Competition testing device | |

| JP2010134584A (ja) | メモリ管理装置、メモリ管理方法およびプログラム | |

| EP4339776A1 (en) | Task scheduling method, system, and hardware task scheduler | |

| JP2008171436A (ja) | データ転送装置および方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100326 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111025 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111110 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111121 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141125 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |