JP2008021968A - Method of operating non-volatile memory element - Google Patents

Method of operating non-volatile memory element Download PDFInfo

- Publication number

- JP2008021968A JP2008021968A JP2007121187A JP2007121187A JP2008021968A JP 2008021968 A JP2008021968 A JP 2008021968A JP 2007121187 A JP2007121187 A JP 2007121187A JP 2007121187 A JP2007121187 A JP 2007121187A JP 2008021968 A JP2008021968 A JP 2008021968A

- Authority

- JP

- Japan

- Prior art keywords

- resistance

- resistance layer

- layers

- bit line

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 33

- 239000004065 semiconductor Substances 0.000 claims description 42

- 239000000758 substrate Substances 0.000 claims description 39

- 230000008859 change Effects 0.000 claims description 23

- 230000002457 bidirectional effect Effects 0.000 claims description 5

- 229910002367 SrTiO Inorganic materials 0.000 claims description 3

- 229910005872 GeSb Inorganic materials 0.000 claims description 2

- 229910010413 TiO 2 Inorganic materials 0.000 claims description 2

- 238000011017 operating method Methods 0.000 claims 2

- 229910003134 ZrOx Inorganic materials 0.000 claims 1

- 230000010354 integration Effects 0.000 abstract description 4

- 239000010410 layer Substances 0.000 description 183

- 239000000463 material Substances 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 239000011651 chromium Substances 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 230000006872 improvement Effects 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- -1 V 2 O 5 Inorganic materials 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 229910000314 transition metal oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Landscapes

- Semiconductor Memories (AREA)

Abstract

Description

本発明は、半導体素子に係り、特に、抵抗ノードを利用した不揮発性メモリ素子の動作方法に関する。 The present invention relates to a semiconductor device, and more particularly, to a method for operating a nonvolatile memory device using a resistance node.

不揮発性メモリ素子、例えば、相転移メモリ素子(Phase−change Random Access Memory:PRAM) または抵抗メモリ素子(Resistive Random Access Memory:RRAM)は、抵抗ノードの可変抵抗状態を利用して動作する。最近、高容量のデータ処理を要する半導体製品の増加によって、このような不揮発性メモリ素子の集積度の向上または動作ビットの向上が要求されている。例えば、マルチビットで動作可能な不揮発性メモリ素子への必要性が増大しつつある。 A non-volatile memory device, for example, a phase-change memory device (PRAM) or a resistive memory device (Resistive Random Access Memory: RRAM) operates using a variable resistance state of a resistance node. Recently, with the increase in semiconductor products that require high-capacity data processing, improvement in the degree of integration of such nonvolatile memory elements or improvement in operation bits has been demanded. For example, there is an increasing need for non-volatile memory devices that can operate in multiple bits.

一方、不揮発性メモリ素子は、前述のように、高容量化されると同時に高速度化されている。すなわち、高容量のデータを処理するためには、データの高速処理が要求されている。したがって、不揮発性メモリ素子の動作速度の上昇、例えば、フラッシュメモリ素子のようなブロック消去またはフラッシュ消去特性が要求されている。 On the other hand, as described above, the capacity of the nonvolatile memory element is increased at the same time as the capacity is increased. That is, in order to process high-capacity data, high-speed data processing is required. Therefore, an increase in the operation speed of the non-volatile memory device, for example, a block erase or flash erase characteristic like a flash memory device is required.

また、不揮発性メモリ素子の集積度の向上によって、動作電流を減少させるための努力が行われている。しかし、抵抗ノードを利用した不揮発性メモリ素子は、比較的に高い動作電流を必要としている。動作電流の減少は、抵抗ノードの可変抵抗の状態に影響を及ぼしうる。したがって、従来の不揮発性メモリ素子は、動作電流を減少させるのに当って限界を有している。 In addition, efforts have been made to reduce the operating current by improving the degree of integration of nonvolatile memory elements. However, a nonvolatile memory element using a resistance node requires a relatively high operating current. The decrease in operating current can affect the state of the variable resistance of the resistance node. Therefore, the conventional nonvolatile memory device has a limit in reducing the operating current.

例えば、PRAMは、相転移抵抗体の結晶状態の変化による抵抗変化を利用してデータを保存する。しかし、PRAMの結晶状態を変化させるためには、高い電流密度が必要であり、これにより、動作電流が増加するという問題がある。このような動作電流の増加は、短チャンネル効果を誘発して、PRAM素子の集積度の向上に障害となりうる。したがって、相転移抵抗体の結晶状態の変化領域を縮小させて、少ない動作電流で高い電流密度を得ようとする努力が行われている。 For example, the PRAM stores data using a resistance change caused by a change in the crystal state of the phase transition resistor. However, in order to change the crystal state of the PRAM, a high current density is required, which increases the operating current. Such an increase in the operating current induces a short channel effect and may hinder the improvement of the integration degree of the PRAM device. Therefore, efforts are being made to obtain a high current density with a small operating current by reducing the change region of the crystalline state of the phase change resistor.

本発明が解決しようとする技術的課題は、前述の問題点を克服するためのものであって、低い動作電流で動作し、高集積化の可能な不揮発性メモリ素子のマルチビット動作方法を提供するところにある。 The technical problem to be solved by the present invention is to overcome the above-mentioned problems, and provides a multi-bit operation method of a non-volatile memory device that operates at a low operating current and can be highly integrated. There is a place to do.

前記技術的課題を解決するための本発明の一形態に係る不揮発性メモリ素子の動作方法が提供される。前記不揮発性メモリ素子は、半導体基板と、前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する第1抵抗層及び第2抵抗層と、前記第1抵抗層の下側の前記半導体基板の部分に形成され、前記第1抵抗層と連結された第1埋め込み電極と、前記第2抵抗層の下側の前記半導体基板の部分に形成され、前記第2抵抗層と連結された第2埋め込み電極と、前記半導体基板上に形成され、前記第1抵抗層及び第2抵抗層上を横切って延びるゲート電極と、前記半導体基板と前記ゲート電極との間のゲート絶縁膜とを備える。前記不揮発性メモリ素子の動作方法は、前記第1埋め込み電極を第1ビットラインとして利用し、前記第2埋め込み電極を第2ビットラインとして利用し、前記ゲート電極をワードラインとして利用する。そして、前記不揮発性メモリ素子の動作方法は、前記第1抵抗層及び第2抵抗層に2ビットのデータをプログラムするステップと、前記第1抵抗層及び第2抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含む。 A method for operating a nonvolatile memory device according to an aspect of the present invention for solving the technical problem is provided. The nonvolatile memory element is formed in the vicinity of a semiconductor substrate, a surface of the semiconductor substrate, and a first resistance layer and a second resistance layer that store a variable resistance state, and the lower side of the first resistance layer. A first embedded electrode formed on a portion of the semiconductor substrate and connected to the first resistance layer; and formed on a portion of the semiconductor substrate below the second resistance layer and connected to the second resistance layer. A second buried electrode; a gate electrode formed on the semiconductor substrate, extending across the first resistance layer and the second resistance layer; and a gate insulating film between the semiconductor substrate and the gate electrode. . The operation method of the nonvolatile memory device uses the first embedded electrode as a first bit line, the second embedded electrode as a second bit line, and the gate electrode as a word line. The non-volatile memory device may be operated by programming 2-bit data in the first resistance layer and the second resistance layer, and 2-bit data programmed in the first resistance layer and the second resistance layer. Reading data.

前記本発明の一側面によれば、前記2ビットのデータをプログラムするステップは、前記第1抵抗層及び第2抵抗層の抵抗をそれぞれ二つの状態に変化させて行える。 According to one aspect of the present invention, the step of programming the 2-bit data can be performed by changing the resistances of the first resistance layer and the second resistance layer in two states.

前記本発明の他の側面によれば、前記2ビットのデータを読み取るステップは、前記第1抵抗層及び前記第2抵抗層の抵抗値の変化による前記第1ビットラインと前記第2ビットラインとの間の電流の変化を測定して行える。 According to another aspect of the present invention, the step of reading the 2-bit data includes the first bit line and the second bit line according to changes in resistance values of the first resistance layer and the second resistance layer. This can be done by measuring the change in current during

前記本発明のさらに他の側面によれば、前記2ビットのデータを読み取るステップは、前記埋め込み電極の一つと隣接した抵抗層の一つとを連結するように深いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の両方向電流値を順次に測定するステップを含みうる。 According to still another aspect of the present invention, the step of reading the 2-bit data forms a deep channel to connect one of the buried electrodes and one of the adjacent resistance layers, and the first bit. The method may include sequentially measuring a bidirectional current value between a line and the second bit line.

前記本発明のさらに他の側面によれば、前記不揮発性メモリ素子の動作方法は、前記第1抵抗層及び前記第2抵抗層に保存されたデータを同時に消去するステップをさらに含みうる。 According to another aspect of the present invention, the method of operating the nonvolatile memory device may further include simultaneously erasing data stored in the first resistance layer and the second resistance layer.

前記技術的課題を解決するための本発明の他の形態に係る不揮発性メモリ素子の動作方法が提供される。前記不揮発性メモリ素子は、半導体基板と、前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、前記複数の抵抗層の下側の前記半導体基板の部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、前記複数の抵抗層上を横切って延びるゲート電極と、前記半導体基板と前記ゲート電極との間のゲート絶縁膜とを備える。前記不揮発性メモリ素子の動作方法は、前記複数の埋め込み電極を複数のビットラインとして利用し、前記ゲート電極をワードラインとして利用する。そして、前記不揮発性メモリ素子の動作方法は、前記複数の抵抗層のうち、隣接する二つの抵抗層に2ビットのデータをプログラムするステップと、前記隣接する二つの抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含む。 A method for operating a nonvolatile memory device according to another aspect of the present invention for solving the technical problem is provided. The nonvolatile memory element is formed in the vicinity of a semiconductor substrate, a surface of the semiconductor substrate, a plurality of resistance layers for storing a variable resistance state, and a portion of the semiconductor substrate below the plurality of resistance layers. A plurality of buried electrodes respectively formed and connected to the plurality of resistance layers; a gate electrode extending across the plurality of resistance layers; and a gate insulating film between the semiconductor substrate and the gate electrode. Prepare. The operation method of the nonvolatile memory device uses the plurality of embedded electrodes as a plurality of bit lines and the gate electrode as a word line. The non-volatile memory device may be operated by programming 2-bit data in two adjacent resistance layers of the plurality of resistance layers, and 2-bit programmed in the two adjacent resistance layers. Reading the data.

本発明に係る不揮発性メモリ素子の動作方法によれば、動作電流、例えば、プログラム電流を低くすることができる。 According to the operation method of the nonvolatile memory element according to the present invention, the operating current, for example, the program current can be lowered.

また、本発明に係る不揮発性メモリ素子の動作方法によれば、一つの単位セルで2ビットのデータを処理できる。 In addition, according to the operation method of the nonvolatile memory device according to the present invention, 2-bit data can be processed in one unit cell.

また、本発明に係る不揮発性メモリ素子の動作方法によれば、ブロック消去またはフラッシュ消去が可能であり、したがって、動作速度が向上しうる。 In addition, according to the operation method of the nonvolatile memory device according to the present invention, block erasure or flash erasure is possible, and thus the operation speed can be improved.

以下、添付した図面を参照して、本発明に係る望ましい実施形態を説明することによって本発明を詳細に説明する。しかし、本発明は、以下で開示される実施形態に限定されるものではなく、相異なる多様な形態で具現され、単に、本実施形態は、本発明の開示を完全にし、当業者に発明の範疇を完全に知らせるために提供されるものである。図面における構成要素は、説明の便宜のために、その大きさが誇張されている。 Hereinafter, exemplary embodiments of the present invention will be described in detail with reference to the accompanying drawings. However, the present invention is not limited to the embodiments disclosed below, and may be embodied in various different forms. The embodiments are merely a complete disclosure of the present invention and are disclosed to those skilled in the art. It is provided to fully inform the category. The components in the drawings are exaggerated in size for convenience of explanation.

本発明の実施形態に係る不揮発性メモリ素子は、抵抗ノードまたは抵抗層を利用してデータを保存できる。したがって、本発明の実施形態に係る不揮発性メモリ素子は、その抵抗ノードまたは抵抗層の種類によって、他の名称で呼ばれうる。例えば、本発明の実施形態に係る不揮発性メモリ素子は、PRAMまたはRRAMを備えうるが、本発明の範囲は、このような名称に制限されない。 The nonvolatile memory device according to the embodiment of the present invention can store data using a resistance node or a resistance layer. Therefore, the nonvolatile memory device according to the embodiment of the present invention may be referred to by other names depending on the type of the resistance node or the resistance layer. For example, the nonvolatile memory device according to the embodiment of the present invention may include a PRAM or an RRAM, but the scope of the present invention is not limited to such names.

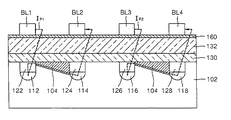

図1は、本発明の一実施形態に係る不揮発性メモリ素子を示す概略的な斜視図であり、図2は、図1の不揮発性メモリ素子のIII−III線による断面図である。 FIG. 1 is a schematic perspective view illustrating a nonvolatile memory device according to an embodiment of the present invention, and FIG. 2 is a cross-sectional view taken along line III-III of the nonvolatile memory device of FIG.

図1及び図2に示すように、不揮発性メモリ素子は、半導体基板102を備える。ただし、図1には、説明の便宜のために、半導体基板102が示されていない。半導体基板102は、シリコン(Si)ウェーハ、ゲルマニウム(Ge)ウェーハまたは金属−絶縁体遷移(Metal−Insulator Transition;MIT)物質を含みうる。例えば、MIT物質は、遷移金属酸化物、例えば、V2O5、TiOxを含みうる。このようなMIT物質は、所定の臨界電圧以上の電圧が印加されれば、絶縁体から金属に変化しうる。このようなMIT物質は、複数層の半導体素子の形成に利用されうる。

As shown in FIGS. 1 and 2, the nonvolatile memory element includes a

複数の抵抗層122、124、126、128は、半導体基板102の表面の付近にそれぞれ形成される。複数の埋め込み電極112、114、116、118は、抵抗層122、124、126、128の下側の半導体基板102の部分にそれぞれ形成される。ゲート電極132は、半導体基板102上に形成され、抵抗層122、124、126、128を横切って延びるように配置されうる。ゲート絶縁膜130は、半導体基板102とゲート電極132との間に介在されうる。選択的に、ビットラインBL1、BL2、BL3、BL4が半導体基板102上に更に形成されうる。

The plurality of

例えば、埋め込み電極112、114、116、118は、半導体基板102内に埋め込まれた形態で提供されうる。埋め込み電極112、114、116、118は、その機能または配置によって多様な形態として呼ばれ、その名称によって本発明の範囲が制限されない。例えば、埋め込み電極112、114、116、118は、順次にソースS及びドレインDと呼ばれてもよく、または埋め込み電極112、114、116、118は、その位置上の配置によって下部電極と呼ばれてもよい。

For example, the embedded

例えば、埋め込み電極112、114、116、118は、半導体基板102に不純物をドーピングして形成されうる。この場合、半導体基板102が第1導電型の不純物でドーピングされた場合、埋め込み電極112、114、116、118は、第1導電型と逆である第2導電型の不純物でドーピングされうる。これにより、埋め込み電極112、114、116、118及び半導体基板102は、ダイオード接合を形成できる。第1導電型及び第2導電型は、n型及びp型からそれぞれ選択された何れか一つでありうる。

For example, the buried

他の例として、埋め込み電極112、114、116、118は、金属層または金属シリサイド層を備えうる。この場合、埋め込み電極112、114、116、118は、半導体基板102とショットキー接合を形成できる。このようなショットキー接合により、埋め込み電極112、114、116、118と半導体基板102との間の電流の流れは、整流の特性を有しうる。

As another example, the buried

ゲート絶縁膜130は、ゲート電極132を半導体基板102と絶縁させる役割が行える。さらに、ゲート絶縁膜130が抵抗層122、124、126、128上にさらに延びることによって、抵抗層122、124、126、128をゲート電極132とさらに絶縁させる役割が行える。ゲート絶縁膜130の厚さは、動作電圧によって適切に選択され、図1及び図2に示すサイズにより制限されない。例えば、ゲート電極132は、導電性物質、例えば、ポリシリコン層、または金属層を備えうる。

The

ビットラインBL1、BL2、BL3、BL4は、層間絶縁膜160を介在してゲート電極132上に形成される。ビットラインBL1、BL2、BL3、BL4は、埋め込み電極112、114、116、118のそれぞれとプラグ135を介して連結される。例えば、ビットラインBL1、BL2、BL3、BL4は、ゲート電極132の延長方向とは異なる方向、例えば、埋め込み電極112、114、116、118と平行な方向に延びうる。例えば、ビットラインBL1、BL2、BL3、BL4は、金属層を備えうる。

Bit lines BL1, BL2, BL3, and BL4 are formed on

複数の抵抗層122、124、126、128は、可変抵抗状態を保存し、このような可変抵抗状態は、データビットとして保存されうる。例えば、抵抗層122、124、126、128は、低抵抗状態及び高抵抗状態を有し、このような低抵抗状態及び高抵抗状態は、それぞれデータ状態“0”または“1”に対応しうる。抵抗層122、124、126、128を二つ以上組合せば、2ビット以上のデータ状態を形成することもある。例えば、二つの抵抗層を利用すれば、(0,0)、(0,1)、(1,0)及び(1,1)状態の2ビットのデータ状態が形成されうる。 The plurality of resistance layers 122, 124, 126, 128 store variable resistance states, and such variable resistance states can be stored as data bits. For example, the resistance layers 122, 124, 126, and 128 have a low resistance state and a high resistance state, and the low resistance state and the high resistance state may correspond to the data state “0” or “1”, respectively. . If two or more resistance layers 122, 124, 126, 128 are combined, a data state of 2 bits or more may be formed. For example, if two resistance layers are used, a 2-bit data state of (0, 0), (0, 1), (1, 0) and (1, 1) states can be formed.

例えば、抵抗層122、124、126、128は、両端に印加された電圧によって、その抵抗状態が変わる物質を含み、例えば、Nb2O5、クロム(Cr)がドーピングされたSrTiO3、ZrOx、GST(GeSbxTey)、NiO、ZnO、TiO2及びHfOからなる群から選択された少なくとも一つ以上をそれぞれ含みうる。例えば、GSTは、その結晶状態の変化によってその抵抗が変わるという点でPRAMに利用されうる。他の例として、Nb2O5、クロム(Cr)がドーピングされたSrTiO3、NiOまたはZnOは、結晶状態の変化なしにその抵抗が変わるという点でRRAMに利用されうる。 For example, the resistance layers 122, 124, 126, and 128 include a material whose resistance state changes depending on a voltage applied to both ends, for example, SrTiO 3 or ZrO x doped with Nb 2 O 5 or chromium (Cr). , GST (GeSb x Te y) , may include NiO, ZnO, selected from the group consisting of TiO 2 and HfO the at least one, respectively. For example, GST can be used in a PRAM in that its resistance changes with changes in its crystalline state. As another example, SrTiO 3 , NiO, or ZnO doped with Nb 2 O 5 , chromium (Cr) can be used for RRAM in that its resistance changes without changing its crystalline state.

図3に示すように、RRAM素子に利用される抵抗層の電圧−電流特性を例示的に更に詳細に説明する。図3は、抵抗層としてNiOを例としたグラフであって、抵抗層の物質によっては、他の形状のグラフが形成されうる。ただし、印加された電圧によって抵抗が変わりうるという点では共通する。 As shown in FIG. 3, the voltage-current characteristics of the resistance layer used in the RRAM element will be described in more detail by way of example. FIG. 3 is a graph illustrating NiO as an example of the resistance layer. Depending on the material of the resistance layer, graphs having other shapes can be formed. However, this is common in that the resistance can be changed depending on the applied voltage.

図3に示すように、抵抗層に初期電圧が印加されれば(P10)、セット電圧、例えば、NiOの場合、4.5Vまでは電流がほとんど流れない。すなわち、抵抗層は、高い抵抗値を表す(リセット状態)。しかし、セット電圧を超えれば、電流が急増する。一旦、セット電圧以上の電圧が加えられた後、再び0から電圧を印加すれば(P20)、高い電流が流れる。すなわち、抵抗層は、低い抵抗値を表す(セット状態)。しかし、再びリセット電圧以上に電圧が増加すれば、電流は急減する(P30)。すなわち、抵抗層の抵抗が再びリセット状態の高い抵抗値に還元される。以後、セット電圧に至る前まで電圧を上昇させ続ければ(P40)、初期リセット状態と同じ経路を示す。 As shown in FIG. 3, when an initial voltage is applied to the resistance layer (P10), in the case of a set voltage, for example, NiO, current hardly flows up to 4.5V. That is, the resistance layer exhibits a high resistance value (reset state). However, if the set voltage is exceeded, the current increases rapidly. Once a voltage equal to or higher than the set voltage is applied, if a voltage is applied again from 0 (P20), a high current flows. That is, the resistance layer exhibits a low resistance value (set state). However, if the voltage increases again above the reset voltage, the current rapidly decreases (P30). That is, the resistance of the resistance layer is reduced again to a high resistance value in the reset state. Thereafter, if the voltage is continuously raised before reaching the set voltage (P40), the same path as in the initial reset state is shown.

すなわち、抵抗層は、臨界電圧、例えば、セット電圧またはリセット電圧を境界として比抵抗が変わり、このような比抵抗の変化は、印加電圧がなくなった後にも、一定の範囲の電圧区間内では維持される。したがって、抵抗層は、不揮発性メモリ素子の記録媒体として利用されうる。 That is, the resistivity of the resistive layer changes with a critical voltage, for example, a set voltage or a reset voltage as a boundary, and such a change in specific resistance is maintained within a voltage range of a certain range even after the applied voltage disappears. Is done. Therefore, the resistance layer can be used as a recording medium for a nonvolatile memory element.

図3の抵抗層に関する説明は、RRAMに利用されるものを例として説明したものであり、PRAMに利用される抵抗層は、他の方式で抵抗変化を経験できる。PRAMに利用される抵抗層は、相転移抵抗体と呼ばれ、このような相転移抵抗体は、構造の変化、例えば、非晶質状態及び結晶質状態への遷移を通じて抵抗状態が変化しうる。このような相転移抵抗体の抵抗変化の特性は、当業者には周知のものであるので、その詳細な説明を省略する。 The description relating to the resistance layer in FIG. 3 is an example of what is used in the RRAM, and the resistance layer used in the PRAM can experience a resistance change in other ways. A resistance layer used in PRAM is called a phase change resistor, and such a phase change resistor can change its resistance state through a structural change, for example, a transition to an amorphous state and a crystalline state. . Such resistance change characteristics of the phase change resistor are well known to those skilled in the art, and a detailed description thereof will be omitted.

一方、前述の実施形態で、抵抗層122、124、126、128のうち、隣接した一対、例えば、第1抵抗層122及び第2抵抗層124が単位セルの構造を形成できる。この場合、第1埋め込み電極112、第2埋め込み電極114、第1ビットラインBL1及び第2ビットラインBL2が、このような単位セルの構造の一部となりうる。

On the other hand, in the above-described embodiment, a pair of adjacent ones of the resistance layers 122, 124, 126, and 128, for example, the

本発明の実施形態に係る不揮発性メモリ素子は、図1及び図2に示す配置に制限されない。したがって、不揮発性メモリ素子は、一つの単位セルの構造を含んでもよく、または複数の単位セルの構造を含んでもよい。すなわち、抵抗層122、124、126、128、埋め込み電極112、114、116、118、及びビットラインBL1、BL2、BL3、BL4は、単に対として提供され、その数が本発明の範囲を制限しない。

The nonvolatile memory device according to the embodiment of the present invention is not limited to the arrangement shown in FIGS. Therefore, the nonvolatile memory device may include a single unit cell structure or a plurality of unit cell structures. That is, the resistance layers 122, 124, 126, 128, the buried

以下では、前述の不揮発性メモリ素子の動作特性を説明する。 Hereinafter, operation characteristics of the nonvolatile memory device will be described.

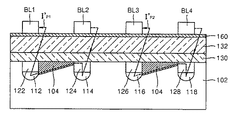

図4及び図5は、本発明の一実施形態に係る不揮発性メモリ素子のプログラム動作を示す断面図である。 4 and 5 are cross-sectional views illustrating a program operation of the nonvolatile memory device according to the embodiment of the present invention.

図4及び図5に示すように、この実施形態で、第1抵抗層122及び第2抵抗層124が一つの単位セルを形成し、第3抵抗層126及び第4抵抗層128が他の単位セルを形成する。図4及び図5には、二つの単位セルが同時に動作するものとして図示されているが、二つの単位セルが別途に動作してもよい。さらに、単位セルの構成は他の形態で提供され、例えば、第2抵抗層124及び第3抵抗層126が一つの単位セルを形成するように提供されてもよい。一方、ゲート電極132は、ワードラインとして利用されうる。

As shown in FIGS. 4 and 5, in this embodiment, the

図4に示すように、二つの単位セルからそれぞれ選択された一つの抵抗層、例えば、第1抵抗層122及び第3抵抗層126のプログラム動作が例示的に説明される。このプログラム動作で、第1抵抗層122の右側部分及び第3抵抗層126の右側部分にデータが保存されうる。このようなデータプログラムは、前述のように、第1抵抗層122及び第3抵抗層126の抵抗をそれぞれ二つの状態に変化させて行える。

As shown in FIG. 4, a program operation of one resistance layer selected from two unit cells, for example, the

例えば、第1ビットラインBL1にプログラム電圧を印加し、第2埋め込み電極114と第1抵抗層122とを連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。深いチャンネル104は、第1ビットラインB1の付近より第2ビットラインBL2の付近で更に深く形成される。例えば、深いチャンネル104の深さは、ゲート電極132に加えられるターンオン電圧または半導体基板102の不純物の濃度を調節して制御できる。

For example, the program voltage is applied to the first bit line BL1, and the turn-on voltage is applied to the word line, that is, the

これにより、プログラム電流IP1は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、深いチャンネル104及び第2埋め込み電極114を経て、第2ビットラインBL2の方向に流れる。深いチャンネル104が、第1抵抗層122と第2埋め込み電極114とを連結するために、相対的に抵抗の高い第2抵抗層124を経るプログラム電流IP1の量は無視できる。

Accordingly, the program current I P1 flows from the first bit line BL1 through the first buried

同様に、第3ビットラインBL3にプログラム電圧を印加し、第4埋め込み電極118と第3抵抗層126とを連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。これにより、プログラム電流IP2は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、深いチャンネル104及び第4埋め込み電極118を経て第4ビットラインBL4の方向に流れる。

Similarly, a program voltage is applied to the third bit line BL3 to turn on the word line, that is, the

したがって、第1抵抗層122及び第3抵抗層126にプログラム電流が流れ、第1抵抗層122及び第3抵抗層126の抵抗が変わりうる。例えば、プログラム以前を低抵抗状態、例えば“0”状態とすれば、プログラムによって第1抵抗層122及び第3抵抗層126は、高抵抗状態、例えば“1”状態になりうる。例えば、プログラム電圧は、相転移抵抗体を非晶質状態にするための電圧でありうる。しかし、データ状態“0”及び“1”は、その逆に表示されてもよい。

Therefore, a program current flows through the

結果的に、図4のプログラム動作により、二つの単位セルは、それぞれ(0,0)状態から(1,0)状態に変換しうる。例えば、(0,0)状態は、単位セル内の二つの抵抗層、例えば、第1抵抗層122及び第2抵抗層124または第3抵抗層126及び第4抵抗層128が何れも低抵抗状態である場合を表す。(1,0)状態は、単位セル内の左側抵抗層、例えば、第1抵抗層122または第3抵抗層126が高抵抗状態であり、右側抵抗層、例えば、第2抵抗層124または第4抵抗層128が低抵抗状態である場合を表す。

As a result, the two unit cells can be converted from the (0, 0) state to the (1, 0) state by the program operation of FIG. For example, in the (0, 0) state, two resistance layers in the unit cell, for example, the

図5に示すように、二つの単位セルからそれぞれ選択された異なる抵抗層、例えば、第2抵抗層124及び第4抵抗層128のプログラム動作が例示的に説明される。このプログラム動作で、第2抵抗層124の左側部分及び第4抵抗層128の左側部分にデータが保存されうる。図5のプログラム動作は、図4のプログラム動作で電流方向を逆方向にすることによって行える。

As shown in FIG. 5, the program operation of different resistance layers selected from two unit cells, for example, the

例えば、第2ビットラインBL2及び第4ビットラインBL4にプログラム電圧を印加し、第1埋め込み電極112と第2抵抗層124、または第3埋め込み電極116と第4抵抗層128、をそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。

For example, a program voltage is applied to the second bit line BL2 and the fourth bit line BL4 to deeply connect the first buried

これにより、プログラム電流I’P1は、第2ビットラインBL2から第1ビットラインBL1の方向に流れ、プログラム電流I’P2は、第4ビットラインBL4から第3ビットラインBL3の方向に流れる。これにより、第2抵抗層124及び第4抵抗層128にプログラム電流が流れ、第2抵抗層124及び第4抵抗層128の抵抗が変わりうる。

Accordingly, the program current I ′ P1 flows from the second bit line BL2 to the first bit line BL1, and the program current I ′ P2 flows from the fourth bit line BL4 to the third bit line BL3. Accordingly, a program current flows through the

結果的に、図5のプログラム動作により、二つの単位セルは、それぞれ(0,0)状態から(0,1)状態に変換しうる。(0,1)状態は、単位セル内の右側抵抗層、例えば、第2抵抗層124または第4抵抗層128が高抵抗状態であり、左側抵抗層、例えば、第1抵抗層122または第3抵抗層126が低抵抗状態である場合を表す。

As a result, the two unit cells can be converted from the (0, 0) state to the (0, 1) state by the program operation of FIG. In the (0, 1) state, the right resistance layer in the unit cell, for example, the

一方、二つの単位セルに図4及び図5のプログラム動作を順次に行えば、二つの単位セルは、それぞれ(0,0)状態から、(1,0)状態を経て(1,1)状態に変換しうる。(1,1)状態は、単位セル内の二つの抵抗層、例えば、第1抵抗層122及び第2抵抗層124、または第3抵抗層126及び第4抵抗層128が何れも高抵抗状態である場合を表す。したがって、図4及び/または図5のプログラム動作を利用すれば、単位セルは、それぞれ四つの状態、すなわち(0,0)、(1,0)、(0,1)及び(1,1)の状態を有し、したがって、2ビットのデータを保存できる。

On the other hand, if the program operation of FIG. 4 and FIG. 5 is sequentially performed on the two unit cells, the two unit cells change from the (0,0) state to the (1,1) state via the (1,0) state, respectively. Can be converted to In the (1, 1) state, two resistance layers in the unit cell, for example, the

前述のプログラム動作で、抵抗層の抵抗変化領域は、深いチャンネル104と接する局部的な部分になる。したがって、低いプログラム電流IP1、IP2、I’P1、I’P2のみでプログラム動作が行われうる。

With the above-described program operation, the resistance change region of the resistance layer becomes a local portion in contact with the

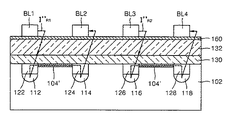

図6及び図7は、本発明の一実施形態に係る読み取り動作を示す断面図である。 6 and 7 are cross-sectional views illustrating a reading operation according to an embodiment of the present invention.

図6に示すように、第1ビットラインBL1及び第3ビットラインBL3に読み取り電圧をそれぞれ印加し、第2埋め込み電極114と第1抵抗層122、または第4埋め込み電極118と第3抵抗層126とをそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。読み取り電圧は、抵抗層122、124、126、128の抵抗変化を招かないように低い電圧であってもよく、したがって、プログラム電圧より低くてもよい。

As shown in FIG. 6, a read voltage is applied to the first bit line BL1 and the third bit line BL3, respectively, and the second embedded

これにより、読み取り電流IR1は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、深いチャンネル104及び第2埋め込み電極114を経て、第2ビットラインBL2の方向に流れる。読み取り電流IR2は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、深いチャンネル104及び第4埋め込み電極118を経て、第4ビットラインBL4の方向に流れる。

Thus, the read current I R1, the first buried

したがって、読み取り電流IR1、IR2のレベルから、それぞれ第1抵抗層122及び第3抵抗層126の抵抗レベルが求められうる。前述のように、第2抵抗層124及び第4抵抗層128にはほとんど読み取り電流IR1、IR2が流れないため、第1抵抗層122及び第3抵抗層126の抵抗レベルがそれぞれ求められうる。これにより、第1抵抗層122及び第3抵抗層126のそれぞれのデータ状態、すなわち、“0”または“1”状態が読み取られうる。

Therefore, the resistance levels of the

図7に示すように、第2ビットラインBL2及び第4ビットラインBL4に読み取り電圧をそれぞれ印加し、第1埋め込み電極112と第2抵抗層124、または第3埋め込み電極116と第4抵抗層128とをそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。

As shown in FIG. 7, read voltages are applied to the second bit line BL2 and the fourth bit line BL4, respectively, and the first embedded

これにより、読み取り電流I’R1は、第2ビットラインBL2から第2埋め込み電極114、第2抵抗層124、深いチャンネル104及び第1埋め込み電極112を経て、第1ビットラインBL1の方向に流れる。読み取り電流I’R2は、第4ビットラインBL4から第4埋め込み電極118、第4抵抗層128、深いチャンネル104及び第3埋め込み電極116を経て、第3ビットラインBL3の方向に流れる。したがって、読み取り電流I’R1、I’R2のレベルから、それぞれ第2抵抗層124及び第4抵抗層128の抵抗レベルが求められうる。これにより、第2抵抗層124及び第4抵抗層128のそれぞれのデータ状態、すなわち、“0”または“1”状態が読み取られうる。

Accordingly, the read current I ′ R1 flows in the direction of the first bit line BL1 from the second bit line BL2 through the second embedded

したがって、図6及び図7に示すように、深いチャンネル104を形成し、第1ビットラインBL1と第2ビットラインBL2との間の両方向電流IR1、I’R1を測定することによって、単位セルの第1抵抗層122及び第2抵抗層124にプログラムされた2ビットのデータを読み取ることができる。同様に、深いチャンネル104を形成し、第3ビットラインBL3と第4ビットラインBL4との間の両方向電流IR2、I’R2を測定することによって、単位セルの第3抵抗層126及び第4抵抗層128にプログラムされた2ビットのデータを読み取ることができる。

Accordingly, as shown in FIGS. 6 and 7, the

図8は、本発明の他の実施形態に係る不揮発性メモリ素子の読み取り動作を示す断面図である。 FIG. 8 is a cross-sectional view illustrating a read operation of a nonvolatile memory device according to another embodiment of the present invention.

図8に示すように、第1ビットラインBL1に読み取り電圧を印加し、第1抵抗層122と第2抵抗層124とを連結するように、半導体基板102に浅いチャンネル104’を形成する。これにより、読み取り電流I”R1は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、浅いチャンネル104’、第2抵抗層124及び第2埋め込み電極114を経て、第2ビットラインBL2に流れる。浅いチャンネル104’は、抵抗層122、124を直接連結し、埋め込み電極112、114を直接連結しないように浅く形成される。例えば、ワードライン、すなわち、ゲート電極132に加えられるターンオン電圧を高めることによって、浅いチャンネル104’を形成できる。

As shown in FIG. 8, a read voltage is applied to the first bit line BL1, and a

同様に、第3ビットラインBL3に読み取り電圧を印加し、第3抵抗層126と第4抵抗層128とを連結するように、半導体基板102に浅いチャンネル104’を形成する。これにより、読み取り電流I”R2は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、浅いチャンネル104’、第4抵抗層128及び第4埋め込み電極118を経て、第4ビットラインBL4に流れる。

Similarly, a read voltage is applied to the third bit line BL3 to form a

読み取り電流I”R1を測定することによって、第1抵抗層122及び第2抵抗層124の抵抗レベル、すなわち、データ状態が同時に求められ、読み取り電流I”R2を測定することによって、第3抵抗層126及び第4抵抗層128の抵抗レベル、すなわち、データ状態が同時に求められうる。なぜなら、第1抵抗層122及び第2抵抗層124のそれぞれの抵抗レベルによって、読み取り電流I”R1が変わり、第3抵抗層126及び第4抵抗層128のそれぞれの抵抗レベルによって、読み取り電流I”R2が変わるためである。

By measuring the read current I ″ R1 , the resistance levels, that is, the data states of the

このような読み取り電流I”R1、I”R2の差は、浅いチャンネル104’を形成するための閾電圧が半導体基板102に対するソースの電位に依存するためである。ここで、ソースは、浅いチャンネル104’と接する第2埋め込み電極114及び/または第2抵抗層124の端部、または第4埋め込み電極118及び/または第4抵抗層128の端部となりうる。ソースの電位は、第1抵抗層122及び第2抵抗層124の抵抗レベル、または第3抵抗層126及び第4抵抗層128の抵抗レベルによって変わる。

The difference between the read currents I ″ R1 and I ″ R2 is because the threshold voltage for forming the

図10は、図8の不揮発性メモリ素子の読み取り動作のシミュレーション結果を示すグラフである。このシミュレーションで、抵抗層の“0”状態の抵抗は、1kΩとし、“1”状態の抵抗は、1MΩとした。 FIG. 10 is a graph showing a simulation result of the read operation of the nonvolatile memory element of FIG. In this simulation, the resistance of the resistance layer in the “0” state is 1 kΩ, and the resistance in the “1” state is 1 MΩ.

図10に示すように、読み取り電圧がVbであるとき、読み取り電流は、(1,1)、(1,0)、(0,1)及び(0,0)状態の順に増大した。ただし、(1,0)及び(1,1)状態をさらに確実に区分するために、Vaで読み取り電流をさらに比較できる。例えば、Vaは、約0.6Vであり、Vbは、約1Vでありうる。このように、一つまたは二つの読み取り電流を比較することによって、単位セルの抵抗層のデータ状態を読み取ることができる。例えば、データ状態は、測定された読み取り電流値と、既に知られたデータ状態の読み取り電流とを比較することによって分かる。 As shown in FIG. 10, when the read voltage was Vb , the read current increased in the order of (1, 1), (1, 0), (0, 1), and (0, 0). However, in order to further partitioned reliably (1,0) and (1,1) state, can be further compares a read current V a. For example, V a can be about 0.6V and V b can be about 1V. In this way, the data state of the resistance layer of the unit cell can be read by comparing one or two read currents. For example, the data state can be found by comparing the measured read current value with the read current of the already known data state.

図9は、本発明の一実施形態に係る不揮発性メモリ素子の消去動作を示す断面図である。 FIG. 9 is a cross-sectional view illustrating the erase operation of the nonvolatile memory device according to the embodiment.

図9に示すように、所定数の抵抗層、例えば、抵抗層122、124、126、128のデータが同時に消去されうる。このような消去動作は、ブロック消去またはフラッシュ消去とも呼ばれる。 As shown in FIG. 9, data of a predetermined number of resistance layers, for example, the resistance layers 122, 124, 126, and 128 can be simultaneously erased. Such an erase operation is also called block erase or flash erase.

例えば、抵抗層122、124、126、128を連結するように、浅いチャンネル104’を形成し、抵抗層122、124、126、128のエッジに位置したビットライン、すなわち、第1ビットラインBL1と第4ビットラインBL4との間に消去電圧を印加する。これにより、第1ビットラインBL1から抵抗層122、124、126、128を経て、第4ビットラインBL4に消去電流IEが流れる。

For example, the

消去電流IEにより、抵抗層122、124、126、128のデータは、何れも同時に消去されうる。例えば、抵抗層122、124、126、128の抵抗は、低いレベルに変更され、そのデータ状態は、何れも“0”状態になりうる。消去電圧は、選択された抵抗層122、124、126、128の数によって変わりうる。

The data of the resistance layers 122, 124, 126, and 128 can be erased simultaneously by the erase current IE . For example, the resistance of the resistance layers 122, 124, 126, and 128 may be changed to a low level, and the data state may be “0”. The erase voltage can vary depending on the number of selected

この実施形態で、抵抗層122、124、126、128のデータは、一時に消去され、したがって、非常に速い消去速度を有しうる。

In this embodiment, the data in the

以上、本発明の特定の実施形態に関する説明は、例示及び説明を目的として提供された。本発明は、前記実施形態に限定されず、当業者によって、本発明の技術的思想の範囲内で前記実施形態を組み合わせて実施するなど、多様な修正及び変更が可能であるということは言うまでもない。 The foregoing descriptions of specific embodiments of the present invention have been presented for purposes of illustration and description. The present invention is not limited to the above-described embodiments, and it goes without saying that various modifications and changes can be made by those skilled in the art, for example, by combining the embodiments within the scope of the technical idea of the present invention. .

本発明は、不揮発性メモリ素子関連の技術分野に好適に利用されうる。 The present invention can be suitably used in technical fields related to nonvolatile memory elements.

112、114、116、118 埋め込み電極

122、124、126、128 抵抗層

130 ゲート絶縁膜

132 ゲート電極

135 プラグ

BL1、BL2、BL3、BL4 ビットライン

112, 114, 116, 118 Embedded

Claims (18)

前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する第1抵抗層及び第2抵抗層と、

前記第1抵抗層の下側の前記半導体基板の部分に形成され、前記第1抵抗層と連結された第1埋め込み電極と、

前記第2抵抗層の下側の前記半導体基板の部分に形成され、前記第2抵抗層と連結された第2埋め込み電極と、

前記半導体基板上に形成され、前記第1抵抗層及び第2抵抗層上を横切って延びるゲート電極と、

前記半導体基板と前記ゲート電極との間のゲート絶縁膜と、を備える不揮発性メモリ素子の動作方法であって、

前記第1埋め込み電極を第1ビットラインとして利用し、前記第2埋め込み電極を第2ビットラインとして利用し、前記ゲート電極をワードラインとして利用して、前記第1抵抗層及び第2抵抗層に2ビットのデータをプログラムするステップと、前記第1抵抗層及び第2抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含むことを特徴とする不揮発性メモリ素子の動作方法。 A semiconductor substrate;

A first resistance layer and a second resistance layer, each formed near the surface of the semiconductor substrate and storing a variable resistance state;

A first embedded electrode formed on a portion of the semiconductor substrate below the first resistance layer and connected to the first resistance layer;

A second embedded electrode formed in a portion of the semiconductor substrate below the second resistance layer and connected to the second resistance layer;

A gate electrode formed on the semiconductor substrate and extending across the first resistance layer and the second resistance layer;

A non-volatile memory device operating method comprising: a gate insulating film between the semiconductor substrate and the gate electrode;

The first buried layer is used as a first bit line, the second buried electrode is used as a second bit line, and the gate electrode is used as a word line to form the first resistance layer and the second resistance layer. A method for operating a nonvolatile memory device, comprising: programming 2-bit data; and reading 2-bit data programmed in the first resistance layer and the second resistance layer.

前記第1ビットラインにプログラム電圧を印加し、前記第2埋め込み電極と前記第1抵抗層とを連結する深いチャンネルが形成されるように、前記ワードラインにターンオン電圧を印加して行うことを特徴とする請求項2に記載の不揮発性メモリ素子の動作方法。 In the programming step, the resistance change of the first resistance layer is:

A program voltage is applied to the first bit line, and a turn-on voltage is applied to the word line so that a deep channel connecting the second buried electrode and the first resistance layer is formed. The method of operating a nonvolatile memory device according to claim 2.

前記第2ビットラインにプログラム電圧を印加し、前記第1埋め込み電極と前記第2抵抗層とを連結する深いチャンネルが形成されるように、前記ワードラインにターンオン電圧を印加して行うことを特徴とする請求項2に記載の不揮発性メモリ素子の動作方法。 In the programming step, the resistance change of the second resistance layer is:

A program voltage is applied to the second bit line, and a turn-on voltage is applied to the word line so as to form a deep channel connecting the first buried electrode and the second resistance layer. The method of operating a nonvolatile memory device according to claim 2.

前記埋め込み電極の一つと隣接した抵抗層の一つとを連結するように深いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の両方向電流値を順次に測定するステップを含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。 The step of reading the 2-bit data includes:

Forming a deep channel to connect one of the buried electrodes and one of the adjacent resistance layers, and sequentially measuring a bidirectional current value between the first bit line and the second bit line. The method of operating a non-volatile memory device according to claim 1.

前記第1抵抗層と前記第2抵抗層とを連結するように浅いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の少なくとも一方向電流値を測定するステップを含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。 The step of reading the 2-bit data includes:

Forming a shallow channel to connect the first resistance layer and the second resistance layer, and measuring at least a one-way current value between the first bit line and the second bit line. The method of operating a non-volatile memory device according to claim 1.

前記第1抵抗層と前記第2抵抗層とを連結するように浅いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間に消去電圧を印加するステップを含むことを特徴とする請求項8に記載の不揮発性メモリ素子の動作方法。 The step of simultaneously erasing the data comprises:

Forming a shallow channel to connect the first resistance layer and the second resistance layer, and applying an erase voltage between the first bit line and the second bit line. The method of operating a nonvolatile memory device according to claim 8.

前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、

前記複数の抵抗層の下側の前記半導体基板の部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、

前記複数の抵抗層上を横切って延びるゲート電極と、

前記半導体基板と前記ゲート電極との間のゲート絶縁膜と、を備える不揮発性メモリ素子の動作方法であって、

前記複数の埋め込み電極を複数のビットラインとして利用し、前記ゲート電極をワードラインとして利用して、前記複数の抵抗層のうち、隣接する二つの抵抗層に2ビットのデータをプログラムするステップと、前記隣接する二つの抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含むことを特徴とする不揮発性メモリ素子の動作方法。 A semiconductor substrate;

A plurality of resistance layers formed respectively near the surface of the semiconductor substrate and storing a variable resistance state;

A plurality of embedded electrodes respectively formed on portions of the semiconductor substrate below the plurality of resistance layers and connected to the plurality of resistance layers;

A gate electrode extending across the plurality of resistive layers;

A non-volatile memory device operating method comprising: a gate insulating film between the semiconductor substrate and the gate electrode;

Using the plurality of buried electrodes as a plurality of bit lines and using the gate electrode as a word line, and programming 2-bit data in two adjacent resistance layers of the plurality of resistance layers; And reading the 2-bit data programmed in the two adjacent resistance layers.

前記二つの抵抗層のうちの一つと隣接した前記埋め込み電極の一つとを連結する深いチャンネルを形成し、前記二つの抵抗層のうちの一つに連結されたビットラインにプログラム電圧を印加するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。 In the programming step, one resistance change of the two adjacent resistance layers is:

Forming a deep channel connecting one of the two resistance layers and one of the adjacent buried electrodes, and applying a program voltage to a bit line connected to one of the two resistance layers; The method according to claim 12, further comprising:

前記隣接した二つの抵抗層のうちの一つと隣接した前記埋め込み電極の一つとを連結するように深いチャンネルを形成し、前記隣接した二つの抵抗層に連結されたビットライン間の両方向電流値を順次に測定するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。 The step of reading the 2-bit data includes:

A deep channel is formed to connect one of the two adjacent resistance layers and one of the adjacent buried electrodes, and a bidirectional current value between bit lines connected to the two adjacent resistance layers is obtained. The method of claim 12, further comprising a step of sequentially measuring.

前記隣接した二つの抵抗層を連結するように浅いチャンネルを形成し、前記隣接した二つの抵抗層に連結されたビットライン間の少なくとも一方向電流値を測定するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。 The step of reading the 2-bit data includes:

The method includes forming a shallow channel to connect the two adjacent resistance layers and measuring at least one-way current value between bit lines connected to the two adjacent resistance layers. Item 13. A method for operating a nonvolatile memory element according to Item 12.

前記連続した所定数の抵抗層を連結するように浅いチャンネルを形成し、前記連続した所定数の抵抗層の両端部の抵抗層に連結されたビットラインに消去電圧を印加するステップを含むことを特徴とする請求項15に記載の不揮発性メモリ素子の動作方法。 The step of simultaneously erasing the data comprises:

Forming a shallow channel so as to connect the predetermined number of consecutive resistance layers, and applying an erase voltage to bit lines connected to the resistance layers at both ends of the predetermined number of consecutive resistance layers. 16. The method of operating a nonvolatile memory device according to claim 15, wherein:

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060065469A KR20080006358A (en) | 2006-07-12 | 2006-07-12 | Method for operating a non-volatile memory device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008021968A true JP2008021968A (en) | 2008-01-31 |

| JP2008021968A5 JP2008021968A5 (en) | 2010-06-17 |

Family

ID=38999940

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007121187A Pending JP2008021968A (en) | 2006-07-12 | 2007-05-01 | Method of operating non-volatile memory element |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2008021968A (en) |

| KR (1) | KR20080006358A (en) |

| CN (1) | CN101106135A (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013200923A (en) * | 2012-03-26 | 2013-10-03 | Toshiba Corp | Nonvolatile semiconductor memory device |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100946179B1 (en) * | 2008-05-29 | 2010-03-09 | 한국과학기술원 | Nonvolatile semiconductor memory device and manufacturing method thereof |

| US8194441B2 (en) * | 2010-09-23 | 2012-06-05 | Micron Technology, Inc. | Phase change memory state determination using threshold edge detection |

-

2006

- 2006-07-12 KR KR1020060065469A patent/KR20080006358A/en not_active Application Discontinuation

-

2007

- 2007-04-23 CN CNA2007101010388A patent/CN101106135A/en active Pending

- 2007-05-01 JP JP2007121187A patent/JP2008021968A/en active Pending

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013200923A (en) * | 2012-03-26 | 2013-10-03 | Toshiba Corp | Nonvolatile semiconductor memory device |

| US8817523B2 (en) | 2012-03-26 | 2014-08-26 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

| US9245623B2 (en) | 2012-03-26 | 2016-01-26 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101106135A (en) | 2008-01-16 |

| KR20080006358A (en) | 2008-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5160116B2 (en) | Nonvolatile memory device | |

| US9136468B2 (en) | Nonvolatile semiconductor memory device | |

| JP4684297B2 (en) | Writing method for nonvolatile semiconductor memory device | |

| US8427865B2 (en) | Semiconductor storage device | |

| JP5722180B2 (en) | Nonvolatile memory device | |

| US9025369B2 (en) | Resistance change nonvolatile semiconductor memory device | |

| US7742331B2 (en) | Nonvolatile semiconductor memory device and data erase/write method thereof | |

| JP4981302B2 (en) | Nonvolatile memory element, nonvolatile memory element array, and method of operating nonvolatile memory element array | |

| EP1710840B1 (en) | Multi-bit memory device having resistive material layers as storage node and methods of manufacturing and operating the same | |

| US9570169B1 (en) | Resistive memory device | |

| JP4088324B1 (en) | Nonvolatile semiconductor memory device | |

| US20150255511A1 (en) | Nonvolatile memory device | |

| JPWO2006137111A1 (en) | Nonvolatile semiconductor memory device and writing method thereof | |

| WO2008068801A1 (en) | Nonvolatile semiconductor storage device, and writing method, reading method and erasing method of the same | |

| JPWO2007023569A1 (en) | Nonvolatile semiconductor memory device and writing method thereof | |

| KR20060070694A (en) | Nonvolitile memory device comprising two resistance material layer | |

| JP2006295157A (en) | Memory device having serially connected resistance node | |

| TWI570722B (en) | Semiconductor memory device | |

| KR100624463B1 (en) | Nor-type hybrid multi-bit non-volatile memory device and method of operating the same | |

| US10115819B2 (en) | Recessed high voltage metal oxide semiconductor transistor for RRAM cell | |

| US7636251B2 (en) | Methods of operating a non-volatile memory device | |

| JP2008021968A (en) | Method of operating non-volatile memory element | |

| JP2014063549A (en) | Semiconductor storage device | |

| CN106133841B (en) | One-time programmable memory, electronic system, method for operating one-time programmable memory and method for programming one-time programmable memory | |

| CN102185108A (en) | Semiconductor memory structure and control method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100427 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110325 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120719 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120731 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121221 |