JP2007535760A - 開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキング - Google Patents

開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキング Download PDFInfo

- Publication number

- JP2007535760A JP2007535760A JP2007510746A JP2007510746A JP2007535760A JP 2007535760 A JP2007535760 A JP 2007535760A JP 2007510746 A JP2007510746 A JP 2007510746A JP 2007510746 A JP2007510746 A JP 2007510746A JP 2007535760 A JP2007535760 A JP 2007535760A

- Authority

- JP

- Japan

- Prior art keywords

- data

- field

- mask

- debug

- message

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/28—Error detection; Error correction; Monitoring by checking the correct order of processing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/36—Preventing errors by testing or debugging software

- G06F11/362—Software debugging

- G06F11/3636—Software debugging by tracing the execution of the program

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/36—Preventing errors by testing or debugging software

- G06F11/362—Software debugging

- G06F11/3648—Software debugging using additional hardware

Abstract

Description

本出願は、2000年11月7日に発行され、発明の名称が「データ・プロセッサのための開発インターフェース(Development Interface For A Data Processor)」である米国特許No.6,145,122に関連し、当該特許は、本明細書に援用される。

本発明は、一般的に、データ処理システムに関し、より詳細には、開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキングに関する。

現在のリアルタイム・デバッグ・システムにおいては、デバッグ・メッセージは、制限された帯域幅ポートを介して集積回路から外部の開発システムに送信される。メッセージを発生することが可能である多重バス・マスタ及び/又は多重バスが集積回路に更に一層高密度に詰め込まれるようになるにつれ、当該制限された帯域幅ポートが集積回路から外部の開発システムへ送信されることになるデバッグ・メッセージの量を十分にサポートすることが益々難しくなりつつある。

本発明が、添付図面により一例としてであって限定するものとしてではなく説明され、そこにおいては、類似の参照番号は、類似の構成要素を示す。

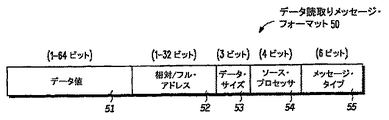

図14は、マスキングを用いて、端末装置18上に送信される出力ビットの数(即ち、帯域幅)を低減する仕方の例200を記載する。図14は、メモリの中の2つの制御変数(変数1及び変数2)がプログラムの流れを追跡している間にモニタリングされる例200を示す。図14に中のボックス201を参照すると、変数1は、アドレス0x1300D3C3に配置され、そして8ビットの変数タイプを有する。変数2は、アドレス0x81001BF4に配置され、そして16ビットの変数タイプを有する。図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージが変数1に関して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、52ビットが要求される(ボックス202参照)。同様に、図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージが変数2に関して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、60ビットが要求される(ボックス202参照)。

図15は、マスキングを用いて、端末装置18上に送信される出力ビットの数(即ち、帯域幅)を低減する仕方を記載する。図15は、メモリの中の混合型の単精度及び倍精度の浮動小数点制御変数のアレイが、プログラムの流れを追跡する間にモニタリングされる例300を示す。外部開発システム25が、制御変数が当該変数のデータ・タイプによりサポートされた大きさのほぼ12.5%(即ち、1/8)を超えたときを決定するためモニタリングしている。図15の中のボックス301を参照すると、アレイ1は、アドレス0x1300D300−0x1300D3FFに配置され、そしてランダムにアクセスすることができる16個の倍精度変数及び32個の単精度変数から成る。図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージがアレイ1の中の倍精度変数に対して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、85ビットが要求される(ボックス302を参照)。同様に、図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージがアレイ1の中の単精度変数に対して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、53ビットが要求される(ボックス302を参照)。

図16は、マスキングを用いて、端末装置18上に送信される出力ビットの数(即ち、帯域幅)を低減する仕方の例400を記載する。図16は、メモリの中の混合型の単精度及び倍精度の浮動小数点制御変数のアレイが、プログラムの流れを追跡する間にモニタリングされる例400を示す。外部開発システム25は、有界の制御変数の近似値をモニタリングしている。図16の中のボックス401を参照すると、アレイ1は、アドレス0x1300D300−0x1300D3FFに配置され、そしてランダムにアクセスすることができる16個の倍精度変数及び32個の単精度変数から成る。図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージがアレイ1の中の倍精度変数に対して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、85ビットが要求される(ボックス402を参照)。同様に、図3及び図4に示されるデータ・メッセージ・フォーマット(書き込みに対して40、読み出しに対して50)を用いたデバッグ・メッセージがアレイ1の中の単精度変数に対して用いられる場合、開発インターフェース14から外部開発システム25へ送られるため、53ビットが要求される(ボックス402を参照)。

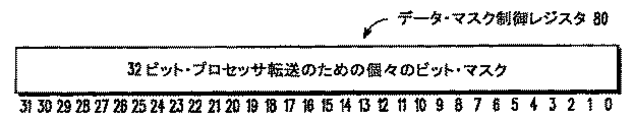

データ・サイズ・フィールド43(図3を参照)の中の1ビットが、変数が単精度か倍精度かを決定するため要求される。例400においては、唯1つのソース・プロセッサが存在し、その結果、ソース・プロセッサ・フィールド44(図3を参照)からのビットは、外部開発システム25により要求されない。例400においては、メッセージ・タイプ・フィールド45(図3を参照)により与えられる唯一の有効な情報は、エラーが生じたか否かを指示する個々のビットである。その結果、メッセージ・タイプ・フィールド45からの唯1つのビットが、外部開発システム25により要求される。

Claims (45)

- デバッグ・メッセージをマスキングする方法であって、

デバッグ・メッセージを発生するステップと、

少なくとも1つのユーザが構成可能なマスクを前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生するステップと

を備える方法。 - 前記デバッグ・メッセージが、複数のフィールドを備える請求項1記載の方法。

- 前記少なくとも1つのユーザが構成可能なマスクを前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生する前記ステップが、前記少なくとも1つのユーザが構成可能なマスクを適用して、前記複数のフィールドのうちの少なくとも1つをマスキングするステップを備える請求項2記載の方法。

- 前記少なくとも1つのユーザが構成可能なマスクを前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生する前記ステップが、前記少なくとも1つのユーザが構成可能なマスクを適用して、前記複数のフィールドのうちの少なくとも1つのフィールドの一部をマスキングするステップを備え、

前記少なくとも1つのフィールドの前記一部が、前記少なくとも1つのフィールドの全部より小さい

請求項2記載の方法。 - 前記複数のフィールドが、データ・フィールド及びアドレス・フィールドを備える請求項4記載の方法。

- 前記複数のフィールドが、データ・サイズ・フィールド、ソース・フィールド及びメッセージ・タイプ・フィールドを備える請求項5記載の方法。

- 前記少なくとも1つのユーザが構成可能なマスクを複数のユーザが構成可能なマスクから選択するステップを更に備え、

前記複数のユーザが構成可能なマスクのそれぞれが、前記デバッグ・メッセージ内の前記複数のフィールドのうちの1つのフィールドに対応する

請求項2記載の方法。 - 少なくとも1つのユーザが構成可能なマスクを前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生する前記ステップが、前記少なくとも1つのユーザが構成可能なマスクを適用して、前記複数のフィールドのうちの少なくとも1つのフィールドの一部をマスキングするステップを備え、

前記少なくとも1つのフィールドの前記一部が、前記少なくとも1つのフィールドの全部より小さい

請求項7記載の方法。 - 前記複数のフィールドが、データ・フィールド、アドレス・フィールド、データ・サイズ・フィールド、ソース・フィールド及びメッセージ・タイプ・フィールドを備える請求項8記載の方法。

- 前記デバッグ・メッセージが、データ・フィールドを備え、

前記少なくとも1つのユーザが構成可能なマスクが、前記データ・フィールドに対応する複数のユーザが構成可能なマスクから選択され、

前記少なくとも1つのユーザが構成可能なマスクが、前記データ・フィールドのデータ・タイプに基づいて選択される

請求項1記載の方法。 - 前記データ・タイプが、前記データ・フィールド内のデータのサイズを指示する請求項10記載の方法。

- 前記デバッグ・メッセージが、アドレス・フィールドを備え、

前記少なくとも1つのユーザが構成可能なマスクが、前記アドレス・フィールドに対応する複数のユーザが構成可能なマスクから選択され、

前記少なくとも1つのユーザが構成可能なマスクが、フル・アドレス又は相対アドレスのいずれが転送されるかに基づいて選択される

請求項1記載の方法。 - デバッグ機能を実行し、当該デバッグ機能に対応するデバッグ・メッセージを発生するデバッグ回路と、

ユーザが構成可能なマスキング情報を格納するマスク記憶回路と、

前記マスク記憶回路に結合されたマスキング回路であって、前記ユーザが構成可能なマスキング情報を前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生するマスキング回路と

を備える装置。 - 前記デバッグ回路に結合されたソース回路を更に備え、

前記デバッグ回路が、前記デバッグ機能を前記ソース回路の少なくとも一部について実行する

請求項13記載の装置。 - 前記ソース回路が、プロセッサを備える請求項14記載の装置。

- 前記ユーザが構成可能なマスキング情報が、複数のユーザが構成可能なマスクとして格納される請求項13記載の装置。

- 前記マスキング回路が、前記複数のユーザが構成可能なマスクのうちの少なくとも1つを選択して、前記デバッグ・メッセージを適用して、前記のマスキングされたデバッグ・メッセージを発生する請求項16記載の装置。

- 前記複数のユーザが構成可能なマスクのそれぞれが、前記マスク記憶回路内のユーザが構成可能なレジスタに格納される請求項16記載の装置。

- 前記デバッグ・メッセージが、複数のフィールドを備え、

前記マスキング回路が、前記マスキング情報を適用して、前記複数のフィールドのうちの少なくとも1つのフィールドの一部をマスキングし、

前記少なくとも1つのフィールドの前記一部が、前記少なくとも1つのフィールドの全部より小さい

請求項13記載の装置。 - 前記複数のフィールドが、データ・フィールド、アドレス・フィールド、データ・サイズ・フィールド、ソース・フィールド及びメッセージ・タイプ・フィールドを備える請求項19記載の装置。

- 前記ユーザが構成可能なマスキング情報が、複数のユーザが構成可能なマスクとして格納され、

前記ユーザが構成可能なマスクのそれぞれが、前記複数のフィールドの少なくとも1つに対応する

請求項20記載の装置。 - 前記マスキング回路が、前記複数のユーザが構成可能なマスクのうちの少なくとも1つを選択して、前記デバッグ・メッセージの前記複数のフィールドのうちの少なくとも1つフィールドに適用して、前記のマスキングされたデバッグ・メッセージを発生する請求項21記載の装置。

- 前記ユーザが構成可能なマスクのうちの少なくとも2つが、前記データ・フィールドに対応し、

前記マスキング回路が、前記ユーザが構成可能なマスクのうちの前記少なくとも2つのうちの1つを、前記データ・フィールド内のデータのデータ・タイプに基づいて選択する

請求項21記載の装置。 - 前記マスキング回路が、前記のマスキングされたデバッグ・メッセージをデバッグ端末装置を介して与える請求項13記載の装置。

- 前記デバッグ回路及び前記マスキング回路に結合されたデバッグ・メッセージ記憶回路であって、前記の発生されたデバッグ・メッセージを格納するデバッグ・メッセージ記憶回路を更に備える請求項13記載の装置。

- 前記マスキング回路に結合されたデバッグ・メッセージ記憶回路であって、前記の発生されたマスキングされたデバッグ・メッセージを格納するデバッグ・メッセージ記憶回路を更に備える請求項13記載の装置。

- 前記デバッグ・メッセージ記憶回路が、前記のマスキングされたデバッグ・メッセージをデバッグ端末装置を介して与える請求項26記載の装置。

- デバッグ・メッセージを発生するデバッグ手段と、

少なくとも1つのユーザが構成可能なマスクを前記デバッグ・メッセージに適用して、マスキングされたデバッグ・メッセージを発生するマスキング手段と

を備える装置。 - 前記デバッグ・メッセージが、複数のフィールドを備える請求項28記載の装置。

- 前記マスキング手段が、前記少なくとも1つのユーザが構成可能なマスクを適用して、前記複数のフィールドのうちの少なくとも1つフィールドの一部をマスキングし、

前記少なくとも1つフィールドの前記一部が、前記少なくとも1つのフィールドの全部より小さい

請求項29記載の装置。 - 前記複数のフィールドが、データ・フィールド及びアドレス・フィールドを備える請求項30記載の装置。

- 前記複数のフィールドが、データ・サイズ・フィールド、ソース・フィールド及びメッセージ・タイプ・フィールドを備える請求項31記載の装置。

- 前記少なくとも1つのユーザが構成可能なマスクを複数のユーザが構成可能なマスクから選択する選択手段を更に備え、

前記複数のユーザが構成可能なマスクのそれぞれが、前記デバッグ・メッセージ内の前記複数のフィールドのうちの1つのフィールドに対応する

請求項29記載の装置。 - 前記マスキング手段が、前記少なくとも1つのユーザが構成可能なマスクを適用して、前記複数のフィールドのうちの少なくとも1つフィールドの一部をマスキングし、

前記少なくとも1つフィールドの前記一部が、前記少なくとも1つフィールドの全部より小さい

請求項33記載の装置。 - 前記複数のフィールドが、データ・フィールド、アドレス・フィールド、データ・サイズ・フィールド、ソース・フィールド及びメッセージ・タイプ・フィールドを備える請求項34記載の装置。

- マスキングする方法であって、

複数のマスクを設けるステップと、

前記複数のマスクのうちの1つマスクを、転送されるべきデータのデータ・タイプに基づいて選択するステップと、

前記複数のマスクのうちの前記の選択された1つのマスクを前記転送されるべきデータに適用して、転送されるべきマスキングされたデータを発生するステップと

を備える方法。 - 前記データ・タイプが、前記転送されるべきデータのサイズを指示する請求項36記載の方法。

- 前記転送されるべきデータが、デバッグ・メッセージ内の1つのフィールドである請求項36記載の方法。

- 前記複数のマスクのうちの前記の選択された1つのマスクを前記転送されるべきデータに適用した後では、前記転送されるべきデータは、マスキングされたデバッグ・メッセージ内の1つのフィールドである請求項38記載の方法。

- 前記の転送されるべきマスキングされたデータが、前記転送されるべきデータより小さい請求項36記載の方法。

- 複数のマスクを格納するマスク記憶回路と、

転送されるべきデータを格納するデータ記憶回路と、

前記マスク記憶回路及びデータ記憶回路に結合されたマスキング回路であって、前記複数のマスクのうちの1つを、前記転送されるべきデータのデータ・タイプに基づいて選択し、前記複数のマスクのうちの前記の選択された1つのマスクを前記転送されるべきデータに適用するマスキング回路と

を備える装置。 - 前記データ・タイプが、前記転送されるべきデータのサイズを指示する請求項41記載の装置。

- 前記マスキング回路が、前記複数のマスクのうちの前記の選択された1つのマスクを前記転送されるべきデータに適用して、転送されるべきマスキングされたデータを発生し、前記の転送されるべきマスキングされたデータを端末装置を介して与える請求項41記載の装置。

- 前記転送されるべきデータが、デバッグ回路によりデバッグ機能に応答して発生される請求項41記載の装置。

- 前記複数のマスクのそれぞれが、前記転送されるべきデータに対応し、

前記転送されるべきデータが、前記デバッグ回路により発生されたデバッグ・メッセージのフィールドとして与えられる請求項44記載の装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/836,173 US7434108B2 (en) | 2004-04-30 | 2004-04-30 | Masking within a data processing system having applicability for a development interface |

| PCT/US2005/011277 WO2005111800A2 (en) | 2004-04-30 | 2005-04-06 | Masking within a data processing system having applicability for a development interface |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007535760A true JP2007535760A (ja) | 2007-12-06 |

| JP2007535760A5 JP2007535760A5 (ja) | 2008-05-22 |

Family

ID=35310740

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007510746A Pending JP2007535760A (ja) | 2004-04-30 | 2005-04-06 | 開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキング |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7434108B2 (ja) |

| EP (1) | EP1756716A4 (ja) |

| JP (1) | JP2007535760A (ja) |

| KR (1) | KR101050554B1 (ja) |

| CN (1) | CN100568187C (ja) |

| TW (1) | TWI374357B (ja) |

| WO (1) | WO2005111800A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010505195A (ja) * | 2006-09-28 | 2010-02-18 | フリースケール セミコンダクター インコーポレイテッド | キャッシュ・メモリ・デバッグ・サポートを有するデータ処理システムおよびそのための方法 |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9020854B2 (en) | 2004-03-08 | 2015-04-28 | Proxense, Llc | Linked account system using personal digital key (PDK-LAS) |

| US8433919B2 (en) | 2005-11-30 | 2013-04-30 | Proxense, Llc | Two-level authentication for secure transactions |

| US8036152B2 (en) | 2006-01-06 | 2011-10-11 | Proxense, Llc | Integrated power management of a client device via system time slot assignment |

| US11206664B2 (en) | 2006-01-06 | 2021-12-21 | Proxense, Llc | Wireless network synchronization of cells and client devices on a network |

| US8086904B2 (en) * | 2006-07-28 | 2011-12-27 | Apple Inc. | Event-based setting of process tracing scope |

| US8116179B2 (en) * | 2006-07-28 | 2012-02-14 | Apple Inc. | Simultaneous viewing of multiple tool execution results |

| US9269221B2 (en) | 2006-11-13 | 2016-02-23 | John J. Gobbi | Configuration of interfaces for a location detection system and application |

| WO2009062194A1 (en) | 2007-11-09 | 2009-05-14 | Proxense, Llc | Proximity-sensor supporting multiple application services |

| US8171528B1 (en) | 2007-12-06 | 2012-05-01 | Proxense, Llc | Hybrid device having a personal digital key and receiver-decoder circuit and methods of use |

| WO2009079666A1 (en) | 2007-12-19 | 2009-06-25 | Proxense, Llc | Security system and method for controlling access to computing resources |

| US8508336B2 (en) | 2008-02-14 | 2013-08-13 | Proxense, Llc | Proximity-based healthcare management system with automatic access to private information |

| US11120449B2 (en) | 2008-04-08 | 2021-09-14 | Proxense, Llc | Automated service-based order processing |

| US7958401B2 (en) * | 2008-07-25 | 2011-06-07 | Freescale Semiconductor, Inc. | Debug trace messaging with one or more characteristic indicators |

| US8024620B2 (en) * | 2008-07-25 | 2011-09-20 | Freescale Semiconductor, Inc. | Dynamic address-type selection control in a data processing system |

| US8402258B2 (en) | 2008-07-25 | 2013-03-19 | Freescale Semiconductor, Inc. | Debug message generation using a selected address type |

| US7984206B2 (en) * | 2008-08-06 | 2011-07-19 | Texas Instruments Incorporated | System for debugging throughput deficiency in an architecture using on-chip throughput computations |

| US20100042975A1 (en) * | 2008-08-13 | 2010-02-18 | Honeywell International Inc. | Message logging for software applications |

| US8589738B2 (en) * | 2009-05-05 | 2013-11-19 | Freescale Semiconductor, Inc. | Program trace message generation for page crossing events for debug |

| US8438547B2 (en) * | 2009-05-05 | 2013-05-07 | Freescale Semiconductor, Inc. | Address translation trace message generation for debug |

| US9418205B2 (en) | 2010-03-15 | 2016-08-16 | Proxense, Llc | Proximity-based system for automatic application or data access and item tracking |

| US8918854B1 (en) | 2010-07-15 | 2014-12-23 | Proxense, Llc | Proximity-based system for automatic application initialization |

| US9265450B1 (en) | 2011-02-21 | 2016-02-23 | Proxense, Llc | Proximity-based system for object tracking and automatic application initialization |

| WO2014183106A2 (en) | 2013-05-10 | 2014-11-13 | Proxense, Llc | Secure element as a digital pocket |

| US9552279B2 (en) * | 2013-08-16 | 2017-01-24 | Nxp Usa, Inc. | Data bus network interface module and method therefor |

| GB2520724A (en) * | 2013-11-29 | 2015-06-03 | St Microelectronics Res & Dev | Debug circuitry |

| CN115934449B (zh) * | 2023-02-08 | 2023-06-02 | 合肥智芯半导体有限公司 | 一种寄存器的校验方法、装置及设备 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000112783A (ja) * | 1998-09-30 | 2000-04-21 | Nec Corp | プログラム検査方法、プログラム検査装置及びプログラム検査プログラムを記憶した記憶媒体 |

| JP2003271416A (ja) * | 2002-03-12 | 2003-09-26 | Seiko Epson Corp | 情報処理装置及び電子機器 |

| JP2003280941A (ja) * | 2002-03-26 | 2003-10-03 | Toshiba Corp | トレースデータ圧縮装置、トレースデータ圧縮方法及びトレースデータ圧縮回路を内蔵したマイクロコンピュータ |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4598364A (en) * | 1983-06-29 | 1986-07-01 | International Business Machines Corporation | Efficient trace method adaptable to multiprocessors |

| US5513317A (en) * | 1992-09-10 | 1996-04-30 | International Business Machines Corporation | System and method for permitting rapid refinement of data output from a debugger |

| US5826058A (en) * | 1995-06-02 | 1998-10-20 | Motorola, Inc. | Method and apparatus for providing an external indication of internal cycles in a data processing system |

| US6513155B1 (en) * | 1997-12-12 | 2003-01-28 | International Business Machines Corporation | Method and system for merging event-based data and sampled data into postprocessed trace output |

| US6145122A (en) | 1998-04-27 | 2000-11-07 | Motorola, Inc. | Development interface for a data processor |

| US6611924B1 (en) * | 1999-07-16 | 2003-08-26 | Lucent Technologies Inc. | Reducing code size of debug output statements |

| US6918065B1 (en) * | 1999-10-01 | 2005-07-12 | Hitachi, Ltd. | Method for compressing and decompressing trace information |

| US6732311B1 (en) * | 2000-05-04 | 2004-05-04 | Agere Systems Inc. | On-chip debugger |

| DE10132313A1 (de) * | 2001-07-06 | 2003-01-23 | Infineon Technologies Ag | Programmgesteuerte Einheit |

| WO2003034225A2 (en) | 2001-10-12 | 2003-04-24 | Pts Corporation | Debugging of processors |

| US6816989B2 (en) * | 2001-12-28 | 2004-11-09 | Hewlett-Packard Development Company, L.P. | Method and apparatus for efficiently managing bandwidth of a debug data output port or buffer |

| GB2389432B (en) * | 2002-06-07 | 2005-09-07 | Advanced Risc Mach Ltd | Instruction tracing in data processing systems |

| US7149926B2 (en) * | 2003-05-22 | 2006-12-12 | Infineon Technologies Ag | Configurable real-time trace port for embedded processors |

-

2004

- 2004-04-30 US US10/836,173 patent/US7434108B2/en not_active Expired - Fee Related

-

2005

- 2005-04-06 KR KR1020067025142A patent/KR101050554B1/ko not_active IP Right Cessation

- 2005-04-06 EP EP05732055A patent/EP1756716A4/en not_active Withdrawn

- 2005-04-06 CN CNB2005800137003A patent/CN100568187C/zh not_active Expired - Fee Related

- 2005-04-06 JP JP2007510746A patent/JP2007535760A/ja active Pending

- 2005-04-06 WO PCT/US2005/011277 patent/WO2005111800A2/en active Application Filing

- 2005-04-28 TW TW094113758A patent/TWI374357B/zh not_active IP Right Cessation

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000112783A (ja) * | 1998-09-30 | 2000-04-21 | Nec Corp | プログラム検査方法、プログラム検査装置及びプログラム検査プログラムを記憶した記憶媒体 |

| JP2003271416A (ja) * | 2002-03-12 | 2003-09-26 | Seiko Epson Corp | 情報処理装置及び電子機器 |

| JP2003280941A (ja) * | 2002-03-26 | 2003-10-03 | Toshiba Corp | トレースデータ圧縮装置、トレースデータ圧縮方法及びトレースデータ圧縮回路を内蔵したマイクロコンピュータ |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010505195A (ja) * | 2006-09-28 | 2010-02-18 | フリースケール セミコンダクター インコーポレイテッド | キャッシュ・メモリ・デバッグ・サポートを有するデータ処理システムおよびそのための方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050257102A1 (en) | 2005-11-17 |

| EP1756716A2 (en) | 2007-02-28 |

| CN100568187C (zh) | 2009-12-09 |

| WO2005111800A2 (en) | 2005-11-24 |

| TW200606630A (en) | 2006-02-16 |

| EP1756716A4 (en) | 2010-08-04 |

| CN101036125A (zh) | 2007-09-12 |

| TWI374357B (en) | 2012-10-11 |

| KR20070012845A (ko) | 2007-01-29 |

| WO2005111800A3 (en) | 2007-04-26 |

| US7434108B2 (en) | 2008-10-07 |

| KR101050554B1 (ko) | 2011-07-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2007535760A (ja) | 開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキング | |

| JP4225851B2 (ja) | データ処理装置用トレース要素生成システム | |

| EP1723532B1 (en) | Multiple burst protocol device controller | |

| US8201025B2 (en) | Debug messaging with selective timestamp control | |

| US8825922B2 (en) | Arrangement for processing trace data information, integrated circuits and a method for processing trace data information | |

| US5862148A (en) | Microcontroller with improved debug capability for internal memory | |

| US20100095038A1 (en) | Driver Transparent Message Signaled Interrupts | |

| EP2324419B1 (en) | Debug message generation using a selected address type | |

| CN107636630B (zh) | 中断控制器 | |

| US20130173837A1 (en) | Methods and apparatus for implementing pci express lightweight notification protocols in a cpu/memory complex | |

| US6484273B1 (en) | Integrated EJTAG external bus interface | |

| US6092219A (en) | Method for use of bus parking states to communicate diagnostic information | |

| US7783809B2 (en) | Virtualization of pin functionality in a point-to-point interface | |

| KR100288670B1 (ko) | 데이터세그먼트처리방법및정보처리시스템 | |

| US8312331B2 (en) | Memory testing with snoop capabilities in a data processing system | |

| US6473814B1 (en) | System for optimally tuning a burst length by setting a maximum burst length based on a latency timer value and adjusting the maximum burst length based on a cache line size | |

| US7080191B2 (en) | Method and system for accessing memory devices | |

| WO2008024336A2 (en) | Write data mask method and system | |

| CN106940684B (zh) | 一种按比特写数据的方法及装置 | |

| US20050081015A1 (en) | Method and apparatus for adapting write instructions for an expansion bus | |

| US20030200401A1 (en) | Microcomputer system automatically backing-up data written in storage medium in transceiver, and transceiver connected thereto | |

| JP2591514B2 (ja) | 1チップメモリデバイス | |

| US9442788B2 (en) | Bus protocol checker, system on chip including the same, bus protocol checking method | |

| CN116700795B (zh) | 一种位操作控制系统及控制方法 | |

| US8862770B1 (en) | Processor architecture verification |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080404 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110411 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110621 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110628 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110912 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111024 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120315 |