JP2006236105A - アクセス制御装置及びその制御方法 - Google Patents

アクセス制御装置及びその制御方法 Download PDFInfo

- Publication number

- JP2006236105A JP2006236105A JP2005051369A JP2005051369A JP2006236105A JP 2006236105 A JP2006236105 A JP 2006236105A JP 2005051369 A JP2005051369 A JP 2005051369A JP 2005051369 A JP2005051369 A JP 2005051369A JP 2006236105 A JP2006236105 A JP 2006236105A

- Authority

- JP

- Japan

- Prior art keywords

- memory

- access

- memory module

- address

- area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0646—Configuration or reconfiguration

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0215—Addressing or allocation; Relocation with look ahead addressing means

Abstract

【課題】高速動作可能なメモリモジュールに対するアクセス性能の低下を防止する。

【解決手段】複数のメモリモジュール106,107,108,109に対するアクセスを制御するアクセス制御装置であって、複数のメモリモジュールへのアクセス状況を判定する判定手段と、判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更手段とを有する。また、複数のメモリモジュールに対するアクセスを制御するアクセス制御装置の制御方法であって、複数のメモリモジュールへのアクセス状況を判定する判定工程と、判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更工程とを有する。

【選択図】図1

【解決手段】複数のメモリモジュール106,107,108,109に対するアクセスを制御するアクセス制御装置であって、複数のメモリモジュールへのアクセス状況を判定する判定手段と、判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更手段とを有する。また、複数のメモリモジュールに対するアクセスを制御するアクセス制御装置の制御方法であって、複数のメモリモジュールへのアクセス状況を判定する判定工程と、判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更工程とを有する。

【選択図】図1

Description

本発明は、複数のメモリモジュールに対するアクセスを制御する技術に関する。

一般的に、主記憶メモリとして使用されているDRAM内のメモリセルはバンク、行、列に分割されており、バンクと行を組み合わせたページ単位でページの活性化を行い(ページオープン、オープン)、活性化を行った後に、列アドレスに対してRead/Writeのコマンドを発行する。そして、ページオープンされているページに対して、プリチャージコマンドを発行することでページの非活性化(ページクローズ、クローズ)を行う(例えば、特許文献1)。

また、あるページがページオープンの状態では、そのページ内の列アドレスに対してはページオープンすることなくアクセスを行うことが可能であり、高速なメモリアクセスが可能となる。

尚、バンク毎に活性化されるページは1つであり、同一バンクで別の行にアクセスする場合は、活性化されているページをクローズし、アクセスを発行するページを活性化してからアクセスを行う列にRead/Writeコマンドを発行する。

また、クローズ状態のページに対してアクセスを発行する場合、ページをオープンした後に、アクセスする列に対してRead/Writeコマンドを発行する。

同一バンクで異なるページにアクセスする際に、ページオープンされていないページに対してアクセスする場合を「ページミス」といい、その際に要する時間、即ち、ページをクローズしてアクセスするページをオープンするまでの時間を「ページミスペナルティ」と呼んでいる。

ところで、近年の半導体技術の向上に伴い、プロセッサやLSIの内部の動作周波数が飛躍的に高速化しており、LSIの外部に接続されるメモリ、特にDRAMを使用した主記憶メモリに対しても動作周波数の向上が要求され、近年メモリモジュールの高速化が進んでいる。

このような状況下において、DRAMを使用したメモリモジュールも高速化に応じて構造、構成の変更が必要となり、従来PC133(133MHzのクロック周波数で動作するSDRAMと、それを差し込むためのDIMMの規格)等のメモリモジュールではUnbufferedの構成(バッファ・チップが接続(使用)されない構成)でコマンド、データ共にコントローラから出力された信号をそのままモジュール内のメモリモジュールに分配しても問題は生じなかったが、DDR400(DDR SDRAM規格の一つで、400MHz(200MHzのDDR)までのメモリクロックに対応する仕様)等のメモリモジュールでは問題が生じている。

即ち、DDR400等のメモリモジュールを複数、構成する際に、コマンド系の信号が多くのメモリモジュールに分配されて供給されると、基板上の信号の負荷が大きくなることから信号の伝播遅延が大きくなり、Unbufferedの構成では高速動作が保証できなくなる。

そこで、コマンド系の信号を各メモリモジュール内に実装されたレジスタにてラッチし、各メモリモジュールに分配することにより基板上の信号負荷を低減し、高速動作を保証している。

このときデータはコマンド系の信号と比較し基板上の信号負荷が小さいため、高速動作に対する影響は小さかった。

しかしながら、DDR2/DDR3といった更なる高速化の実現を可能とするメモリモジュールを複数用いて構成したシステムを構築すると、各データ信号の分配による基板上の負荷が無視できなくなり、高速動作に影響してしまう。

この高速動作を保証する仕組みとして、例えば図14に示すような、Point to Pointの高速シリアルインターフェース技術を用いてコマンド、データの伝送を行い、それぞれのメモリモジュール内のバッファでコマンド、データを一旦バッファリングして、伝送する仕組みが実現に向けて検討されている。以下、図14を用いて本構成のメモリモジュールの動作を説明する。

メモリ制御回路1401から発行されるメモリコマンドは、メモリモジュール1406〜1409内のバッファ1411へ伝達される。各バッファ1411は自モジュールへのアクセスか、或いは他のモジュールへのアクセスかを判定する。ここで、自モジュールへのアクセスであった場合は、モジュール内のDRAM1410へそのコマンドを分配し、他のモジュールへのアクセスであった場合は、次のモジュールへそのコマンドを伝達する。

また、書き込みデータに関しては、メモリコマンドと一緒に伝達される。尚、読み込みデータに関しては、バッファ1411を介してメモリコマンドとは逆に、メモリ制御回路1401側へとデータを伝播する。

図14に示す構成では、接続されるモジュール間でコマンド、データがシリアルに伝送されることになり、コマンドや書き込みデータはLSIからの距離の遠いモジュールへの到達サイクルが遅れる。また、読み込みデータはLSIからの距離の遠いモジュールからのレイテンシが長くなる傾向にある。

例えば、図14に示すメモリ制御回路1401に一番近いメモリモジュール1406に対するメモリアクセスはコマンド、書き込みデータに対してはバッファ1411一段分、また読み出しデータは更に一段分のメモリアクセスレイテンシとなる。

一方、メモリ制御回路1401から一番遠いメモリモジュール1409に対するメモリアクセスはコマンド、書き込みデータに対してはバッファ1411四段分、また読み出しデータは更に四段分のメモリアクセスレイテンシとなるため、メモリモジュールの物理的位置によりアクセスレイテンシが大幅に異なる。

特開平10−3785号公報

上述した図14に示すシステムに対して、従来のメモリモジュールを使用したシステムの場合、図15に示すように、各メモリモジュール1506〜1509に対してコマンド、データが分配されるため、それぞれのDRAM1510に対するアクセスレイテンシは均一であり、如何なる領域にメモリアクセスを発行してもアクセス性能は均一であった。

しかし、図14に示すようなメモリモジュールを使用した場合、アクセスされる対象のメモリモジュールに依存してアクセスレイテンシが大幅に異なることになる。

例えば、図14においてアクセスレイテンシの一番小さいメモリモジュール1406に対してメモリアクセスが多く発行された場合と、アクセスレイテンシの一番大きいメモリモジュール1409に対してメモリアクセスが多く発行された場合とでは、そのアクセス応答性が大きく異なっているため、メモリアクセスに依存したシステム性能に大きな影響を与えてしまう。

即ち、図14に示すようなメモリモジュールを搭載したシステムにおいて、例えばアクセスレイテンシの少ないメモリモジュール1406に対するメモリアクセス数が少なく、アクセスレイテンシの大きいメモリモジュール1409に対するメモリアクセスが多数発行される場合と、アクセスレイテンシの少ないメモリモジュール1406に対するメモリアクセスが多数発行され、アクセスレイテンシの大きいメモリモジュール1409に対するメモリアクセス数が少ない場合とでは、後者に対して前者のメモリアクセス性能が悪くなる、という問題がある。

この場合、メモリアクセスが多数発行されるメモリ空間をアクセスレイテンシの少ないメモリモジュール1406にアドレス割り当てを行うことによって性能の低下を防ぐことができる。

しかしながら、システムに複数の機能やアプリケーションが動作している場合、各々のメモリ空間に対するアクセス頻度は時系列的に変化するため、ある時点でメモリアクセス性能の低下を防ぐメモリ空間の割り当てを行っても、機能及びアプリケーションの変化によりアクセスパターンが変化し、アクセス頻度が高いメモリ空間がアクセスレイテンシの大きいメモリモジュールが割り当てられている空間に遷移した場合、メモリアクセス性能が低下してしまう、という問題がある。

本発明は上記課題を解決するためになされたもので、高速動作可能なメモリモジュールに対するアクセス性能の低下を防止することを目的とする。

本発明は、複数のメモリモジュールに対するアクセスを制御するアクセス制御装置であって、複数のメモリモジュールへのアクセス状況を判定する判定手段と、前記判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更手段とを有することを特徴とする。

また、本発明は、複数のメモリモジュールに対するアクセスを制御するアクセス制御装置の制御方法であって、複数のメモリモジュールへのアクセス状況を判定する判定工程と、前記判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更工程とを有することを特徴とする。

本発明によれば、高速動作可能なメモリモジュールに対するアクセス性能の低下を防止することができる。

以下、図面を参照しながら発明を実施するための最良の形態について詳細に説明する。本実施形態として、図11に示したメモリ制御回路1101から4組のメモリモジュール1106〜1109が鎖状に接続され、各メモリモジュールはコマンド、データを受け取り、下流へと伝達するバッファ1111と複数のDRAM1110とを有するシステムを例に説明する。

尚、ここではメモリ制御回路1101から物理的距離が一番近いメモリモジュール1106に対するアクセスレイテンシが一番小さく、物理的距離が一番遠いメモリモジュール1109に対するアクセスレイテンシが一番大きいものとする。

[第1の実施形態]

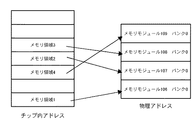

図1は、第1の実施形態におけるメモリシステムの構成の一例を示す図である。図1に示すように、メモリモジュール部102は図11に示したメモリモジュール部1102に相当するものである。そして、第1の実施形態では、メモリ制御回路101がメモリ情報レジスタ103、アクセスパターン判定・設定部104、メモリインタフェース105を含むものである。

図1は、第1の実施形態におけるメモリシステムの構成の一例を示す図である。図1に示すように、メモリモジュール部102は図11に示したメモリモジュール部1102に相当するものである。そして、第1の実施形態では、メモリ制御回路101がメモリ情報レジスタ103、アクセスパターン判定・設定部104、メモリインタフェース105を含むものである。

ここで、図2を用いて第1の実施形態におけるメモリ制御回路101の構成及び制御について説明する。

図2は、第1の実施形態におけるメモリ制御回路101の構成の一例を示す図である。図2において、202はメモリアクセスインタフェースであり、201のメモリアクセスバスを介してメモリモジュール部102の各メモリモジュール106〜109とアクセスコマンド、データの授受を行う。205はメモリ情報レジスタであり、203のレジスタアクセスバスを介してメモリモジュール部102の各メモリモジュール106〜109への動作設定や状態を保持する。

このメモリ情報レジスタ205は、各メモリモジュール106〜109へのリード時のアクセスレイテンシを指定して保持するメモリ構成情報レジスタ209と、メモリ空間と各メモリモジュール106〜109のアドレス割り当てとを指定するメモリアドレス設定レジスタ210とから構成されている。

204はアクセスパターン判定・設定部であり、各メモリモジュール106〜109に対して行われたアクセスの内容をアクセスパターン211として入力し、その解析の結果に基づいてメモリ情報レジスタ205に設定を行う。このアクセスパターン判定・設定部204は、メモリへのアクセスパターン211を判定するメモリアクセスパターン判定部207と、メモリアドレス設定部208とから構成されている。

アクセスパターン判定部207では、入力されたアクセスパターン211からメモリへアクセスしたアクセス内容の解析を行う。そして、メモリアドレス設定部208が、その解析の結果に基づいてチップ上のメモリ空間と各メモリモジュール106〜109の物理アドレスとの割り当てを決定する。

212はメモリ制御コア部であり、各メモリモジュール106〜109の各DRAM110へのメモリアクセス内容を制御する。また、メモリ制御コア部212は、不図示のCPUからのアクセス指示により、メモリモジュール部102に書き込むメモリ書き込みデータ213を受信し、メモリモジュール部102から読み出したメモリ読み出しデータ214を送信する。

ここで、図3を用いてメモリ情報レジスタ205の構成について説明する。尚、第1の実施形態では、メモリ制御回路101に4組のメモリモジュール106、107、108、109が接続されるため、メモリ情報レジスタ205のメモリ構成情報レジスタ209及びメモリアドレス設定レジスタ210は4組の対応するレジスタ領域を有する。

図3は、第1の実施形態におけるメモリ情報レジスタ205の構成及び設定例を示す図である。図3に示す(A)はメモリ構成情報レジスタ209の構成及び設定例を示す図、同(B)はメモリアドレス設定レジスタ210の構成及び設定例を示す図である。

まず、メモリ構成情報レジスタ209は、接続するメモリモジュールの構成情報としてメモリモジュールが有効か無効かを表すフラグ301、メモリバンクの個数302を設定する領域と、アドレス情報として行アドレス個数303、列アドレス個数304を設定する領域と、メモリモジュール毎のレイテンシとして物理的距離情報305を設定する領域とを有する。

例えば、メモリバンクの個数302の設定はフラグにより行われ、「0」は4バンクのモジュールが接続され、「1」は8バンクのモジュールが接続されることを示している。また、メモリモジュール毎の物理的距離情報305は、メモリ制御回路101と各メモリモジュール106〜109との物理的距離が近いものから順に「0」、「1」、「2」、「3」と設定する。

次に、メモリアドレス設定レジスタ210は、メモリ領域下位アドレスレジスタフィールド306と、メモリ領域上位アドレスレジスタフィールド307とを有する。アドレス領域の指定はメモリモジュール毎に、下限領域の開始アドレスのMSB8ビットと、上限領域の終了アドレスのMSB8ビットを指定する。

例えば、メモリモジュールの構成として、バンク個数が4、行アドレス個数が13、列アドレス個数が10の場合、図3に示す(A)のように、バンク個数4の情報からメモリバンクの個数302のレジスタ設定値が「0」、行アドレス個数303のレジスタ設定値が「0xd」、列アドレス個数304のレジスタ設定値が「0xa」に設定される。

また、メモリアドレスマップが図4に示す401〜404のように構成されている場合、図3に示す(B)のように、メモリアドレス設定レジスタ210の各メモリモジュール106〜109に対応するメモリ領域下位アドレスレジスタフィールド306及びメモリ領域上位アドレスレジスタフィールド307には、「0x00」及び「0x10」、「0x10」及び「0x20」、「0x20」及び「0x30」、「0x30」及び「0x40」が設定される。

ここで、アクセスパターン判定・設定部204が入力されたアクセスパターン211に基づいてメモリ情報レジスタ205に設定を行う処理について説明する。

アクセスパターン判定・設定部204は、メモリモジュール106〜109のどの領域のアドレスを読み書きしているかといったアクセス内容をアクセスパターン211として入力し、そのアクセス内容を解析した結果に基づいてメモリ情報レジスタ205のメモリ構成情報レジスタ209及びメモリアドレス設定レジスタ210に書き込む値を生成して設定する。

具体的には、アクセスパターン判定部207が入力されたアクセスパターン211からメモリモジュール106よりもメモリモジュール108を物理的に距離が近い方が良いと判定すると、メモリアドレス設定部208がメモリアドレスの変更対象となるメモリモジュール106の物理的距離情報305に書き込む値「2」を生成し、メモリモジュール108の物理的距離情報305に書き込む値「0」を生成し、新たなメモリアドレス設定値としてメモリ構成情報レジスタ209に設定する。

従って、アクセスパターン211を解析することにより、メモリへのアクセス頻度情報に応じてチップ上のメモリ空間と各メモリモジュールを割り当てるアドレスとを変更することにより、メモリモジュール毎にリード時のアクセスレイテンシが異なるメモリシステムでメモリ制御回路101のレイテンシ増加を抑えることができ、メモリアクセス性能の低下を防ぐことができる。

尚、第1の実施形態は、アクセスパターン判定部207、メモリアドレス設定部208をソフトウェアによって実現することも可能である。

例えば、アクセスパターン判定部207、メモリアドレス設定部208を図2に示すようなハードウェア回路ではなく、プログラム等のソフトウェアで実現する場合には、アクセスパターン判定部207、メモリアドレス設定部208の処理内容はプロセッサで実現する。

また、ソフトウェアで処理する場合は、メモリアドレス設定部208の実行結果である新しいメモリアドレス値を直接メモリアドレス設定レジスタ210に書き込むことで構成できる。特に、ソフトウェアで回路を実現する場合、ハードウェアの回路規模を削減することが可能であり、ハードウェアで構成した場合と同様に、アクセスレイテンシが異なるメモリシステムでメモリアドレスの割り当てを変更することができ、メモリアクセス性能の低下を防ぐことができる。

第1の実施形態によれば、メモリモジュール毎にアクセスレイテンシが異なるメモリに対するメモリ制御回路において、アクセスパターンに応じてメモリ空間と各メモリモジュールのアドレス割り当てを変更することにより、レイテンシの増加によるメモリアクセス性能の低下を防ぐことができる。

[第2の実施形態]

次に、図面を参照しながら本発明に係る第2の実施形態について詳細に説明する。

次に、図面を参照しながら本発明に係る第2の実施形態について詳細に説明する。

図5は、第2の実施形態におけるメモリ制御回路501の構成の一例を示す図である。尚、第1の実施形態で用いた図1と同様な機能を有するものには同一の符号を付し、その説明は省略する。

図5において、502は第2の実施形態におけるアクセスパターン判定・設定部であり、図1に示したアクセスパターン判定部207、メモリアドレス設定部208に対応するアクセスパターン判定部503、メモリアドレス設定部504と、更にメモリモジュールへのアクセス頻度を検出するアクセスカウンタ505とを備えている。

ここで、第2の実施形態におけるアクセスカウンタ505の構成及び動作について説明する。アクセスカウンタ505は、Nビット(Nは任意の自然数)のカウンタで、メモリアクセス要求をメモリ制御コア部212で受け取る毎に1加算(インクリメント)され、カウント値が最大値になると再度0から計数を開始する。尚、カウント値が0から最大値になる間をアクセス計測単位とする。

尚、このアクセスカウンタ505は、メモリモジュールの個数及ぶ各メモリモジュールのバンクの数による領域分割個数に対応したメモリアクセスカウンタを有する。

即ち、図6に示すように、アクセスカウンタ505は複数のメモリアクセスカウンタで構成され、メモリアクセスカウンタ601はメモリモジュール106のバンク0、メモリアクセスカウンタ602はメモリモジュール107のバンク0、メモリアクセスカウンタ603はメモリモジュール108のバンク0、メモリアクセスカウンタ604はメモリモジュール109のバンク0といったように、メモリモジュール及びバンクにそれぞれ対応するものである。

従って、本実施形態のように、メモリモジュールが4個でそれぞれ4バンク構成である場合には、メモリアクセスカウンタ505として合計16個のカウンタが用意されることになる。

そして、各メモリモジュールのバンク毎にメモリアクセス頻度を計測することで、より物理的距離が近い場所に配置すべきメモリモジュールの領域を検出し、メモリ領域に割り当てるメモリアドレスを変更するための情報として利用する。

図7は、メモリ領域毎に対応するメモリモジュール及びバンクとメモリアクセス回数の具体例を示す図である。図7は、説明を簡単にするために、各メモリモジュール106〜109のバンク0のみを示している。

図7に示すように、チップ内のメモリ領域として、メモリ領域1〜メモリ領域4が定義され、物理アドレスとして、メモリモジュール106のバンク0領域〜メモリモジュール109のバンク0領域に対応するものである。また、各メモリアドレスにおけるメモリが活性化したメモリアクセス回数701が示されている。

即ち、図7に示す例では、メモリ領域1に対応するメモリモジュール106のバンク0領域に対するメモリアクセスが15回であったことを示している。

また、チップ内アドレスと物理アドレスとが、例えば図8に示すような対応関係にあるとすれば、チップ内アドレスのメモリ領域1は物理アドレスのメモリモジュール106のバンク0領域を、メモリ領域2はメモリモジュール107のバンク0領域を、メモリ領域3はメモリモジュール108のバンク0領域を、メモリ領域4はメモリモジュール109のバンク0領域を、それぞれアクセスすることになる。

そこで、第2の実施形態では、図7に示すメモリモジュールのバンク領域へのアクセス回数701からアクセスの多いメモリ領域を物理的に近いメモリアドレス領域に変換することでアクセスレイテンシの改善を図るものである。

即ち、メモリアクセス回数により、メモリモジュールへのアクセスが多い場合には物理的距離が近いメモリモジュールにチップ内アドレスを変更し、またメモリモジュールへのアクセスが少ない場合には物理的距離が遠いメモリモジュールにチップ内アドレスを変更する。

具体的には、図7に示したようなメモリアクセス回数701の場合、図8に示すチップ内アドレスと物理アドレスの対応は、図9に示すチップ内アドレスと物理アドレスの対応に変換される。従って、チップ内アドレスのメモリ領域2及びメモリ領域4は、変換前後で変らず、物理アドレスのメモリモジュール107のバンク0領域及びメモリモジュール109のバンク0領域をそれぞれ参照するが、メモリ領域1はメモリモジュール106のバンク0領域からメモリモジュール108のバンク0領域へと変更され、メモリ領域3はメモリモジュール108のバンク0領域からメモリモジュール106のバンク0領域へと変更される(図9に示す破線)。

このように、メモリアクセスの回数に応じて適宜チップ内アドレスの物理アドレスへのアドレス割り当てを変更することで、アクセスレイテンシによる性能低下を削減することができる。

第2の実施形態によれば、メモリ制御回路が実際に発行された分割された各メモリ空間毎のメモリアクセスの回数を計数し、メモリアクセスが多数発行されているメモリ空間をレイテンシの少ないメモリモジュールへとアドレス割り当て変更を行うことにより、動作状況に応じてレイテンシ増加によるメモリアクセス性能の低下を防ぐことができる。

[第3の実施形態]

次に、図面を参照しながら本発明に係る第3の実施形態について詳細に説明する。

次に、図面を参照しながら本発明に係る第3の実施形態について詳細に説明する。

図10は、第3の実施形態におけるメモリ制御回路1001の構成の一例を示す図である。尚、第1の実施形態で用いた図1と同様な機能を有するものには同一の符号を付し、その説明は省略する。

図10において、1002は第3の実施形態におけるアクセスパターン判定・設定部であり、図1に示したアクセスパターン判定部207、メモリアドレス設定部208に対応するアクセスパターン判定部1003、メモリアドレス設定部1004と、更にメモリモジュールにおけるページ遷移を計数するページ遷移カウンタ1005とを備えている。

ここで、第3の実施形態におけるページ遷移カウンタ1005の構成及び動作について説明する。ページ遷移カウンタ1005は、Nビット(Nは任意の自然数)のカウンタで、メモリモジュールの各領域のページ遷移回数をカウントする。具体的には、メモリ制御コア部212でメモリアクセス要求を受けると、該当アドレスのページが活性化されているか、非活性化されているかを判定し、非活性化されている場合には、ページ遷移と判定してページ遷移回数として1加算(インクリメント)され、カウント値が最大値になると再度0から計数を開始する。尚、カウント値が0から最大値になる間をアクセス計測単位とする。

尚、このページ遷移カウンタ1005は、メモリモジュールの個数及び各メモリモジュールのバンクの数による領域分割個数に対応したページ遷移カウンタを有する。

即ち、図11に示すように、ページ遷移カウンタ1005は複数のページ遷移アクセスカウンタで構成され、ページ遷移カウンタ1101はメモリモジュール106のバンク0、ページ遷移カウンタ1102はメモリモジュール107のバンク0、ページ遷移カウンタ1103はメモリモジュール108のバンク0、ページ遷移カウンタ1104はメモリモジュール109のバンク0といったように、メモリモジュール及びバンクにそれぞれ対応するものである。

従って、本実施形態のように、メモリモジュールが4個でそれぞれ4バンク構成である場合には、ページ遷移カウンタ1005として合計16個のカウンタが用意されることになる。

そして、各メモリモジュールのバンク毎にページ遷移回数を計数することで、より物理的距離が近い場所に配置すべきメモリモジュールの領域を検出し、メモリ領域に割り当てるメモリアドレスを変更するための情報として利用する。

図12は、メモリ領域毎に対応するメモリモジュール及びバンクと、ページ遷移回数の具体例を示す図である。図12は、説明を簡単にするために、各メモリモジュール106〜109のバンク0のみを示している。

図12に示すように、チップ内のメモリ領域として、メモリ領域1〜メモリ領域4が定義され、物理アドレスとして、メモリモジュール106のバンク0領域〜メモリモジュール109のバンク0領域に対応するものである。また、各メモリアドレスにおけるメモリのページ遷移回数1201が示されている。

即ち、図12に示す例では、メモリ領域1に対応するメモリモジュール106のバンク0領域に対するページ遷移が15回であったことを示している。

また、チップ内アドレスと物理アドレスとが、第2の実施形態で用いた図8に示すような対応関係にあるとすれば、チップ内アドレスのメモリ領域1は物理アドレスのメモリモジュール106のバンク0領域を、メモリ領域2はメモリモジュール107のバンク0領域を、メモリ領域3はメモリモジュール108のバンク0領域を、メモリ領域4はメモリモジュール109のバンク0領域を、それぞれアクセスすることになる。

そこで、第3の実施形態では、図12に示すメモリモジュールのバンク領域へのページ遷移回数1201からページ遷移の多いメモリ領域を物理的に近いメモリアドレス領域に変換することでアクセスレイテンシの改善を図るものである。

即ち、ページ遷移回数により、メモリモジュールのページ遷移が多い場合には物理的距離が近いメモリモジュールにチップ内アドレスを変更し、またメモリモジュールのページ遷移が少ない場合には物理的距離が遠いメモリモジュールにチップ内アドレスを変更する。

具体的には、図12に示したようなページ遷移回数1201の場合、図8に示すチップ内アドレスと物理アドレスの対応は、図9に示すチップ内アドレスと物理アドレスの対応に変換される。従って、チップ内アドレスのメモリ領域2及びメモリ領域4は、変換前後で変らず、物理アドレスのメモリモジュール107のバンク0領域及びメモリモジュール109のバンク0領域をそれぞれ参照するが、メモリ領域1はメモリモジュール106のバンク0領域からメモリモジュール108のバンク0領域へと変更され、メモリ領域3はメモリモジュール108のバンク0領域からメモリモジュール106のバンク0領域へと変更される(図9に示す破線)。

尚、各メモリモジュールが複数のバンク(複数のページ)で構成されている場合には、複数のページにおけるページ遷移を考慮して上述したチップ内アドレスを変更することは言うまでもない。

また、ページ管理について詳細な説明は省略するが、従来のメモリモジュールに対して行われるページ管理方法をそのまま適用し、高速アクセスと低消費電力を実現するようにしても良い。

第3の実施形態では、複数のページに対するメモリ制御回路101からの距離に応じてページ非活性化時に距離の遠いページの優先度を下げ、また距離の近いページを優先的に非活性化するように制御する。具体的には、以下のように制御する。

・常に距離の近いページをクローズする

・重み付けを行い、距離の近いページをクローズする優先度を上げる(距離の遠いページをクローズする場合の条件(アクセス回数や頻度)を設定する

・距離の遠いメモリモジュールをオープンページモードとする

このように、メモリの活性化領域、非活性化領域のページ遷移回数に応じて適宜チップ内アドレスの物理アドレスへのアドレス割り当てを変更することで、アクセスレイテンシによる性能低下を削減することができる。

・常に距離の近いページをクローズする

・重み付けを行い、距離の近いページをクローズする優先度を上げる(距離の遠いページをクローズする場合の条件(アクセス回数や頻度)を設定する

・距離の遠いメモリモジュールをオープンページモードとする

このように、メモリの活性化領域、非活性化領域のページ遷移回数に応じて適宜チップ内アドレスの物理アドレスへのアドレス割り当てを変更することで、アクセスレイテンシによる性能低下を削減することができる。

第3の実施形態によれば、メモリ制御回路が実際に発行された分割された各メモリ空間毎のページ遷移数を計数し、ページ遷移数の多いメモリ空間をレイテンシの少ないメモリモジュールへとアドレス割り当て変更を行うことにより、レイテンシ増によるページミスペナルティの影響を削減すると共に、ページ遷移の少ないメモリ空間の転送幅を維持し、メモリアクセス性能の最適化を実現することができる。

[第4の実施形態]

次に、図面を参照しながら本発明に係る第4の実施形態について詳細に説明する。

次に、図面を参照しながら本発明に係る第4の実施形態について詳細に説明する。

第1乃至第3の実施形態では、アクセスパターン判定部がアクセスパターン、アクセス回数、ページ遷移回数に基づいてメモリアドレスの変更が必要と判定した場合に、メモリ制御コア部212でメモリへのアクセスを停止させ、チップ内アドレスの物理アドレスへのアドレス割り当てを変更したが、第4の実施形態では更にメモリモジュールのデータの複写動作を行うものである。

図7に示すように、メモリモジュール毎にメモリへのアクセス回数が計数され、メモリアクセス回数701によりメモリ領域1とメモリ領域3のメモリデータを入れ替える必要が発生した場合、メモリ情報レジスタ205におけるメモリアドレス設定レジスタ210のメモリ領域下位アドレスレジスタフィールド306とメモリ領域上位アドレスレジスタフィールド307で決定させるメモリモジュールの特定の領域に入っているメモリデータの置き換えを実行する。

図13は、第4の実施形態におけるメモリデータの複写を示す図である。図13に示すように、メモリモジュール108のバンク0領域と、メモリモジュール106のバンク0領域との割り当てを変更する場合、メモリデータを一時的に保持するための任意バッファ領域1301を設け、メモリモジュール108のバンク0領域1302及びメモリモジュール106のバンク0領域1303のメモリデータを一時的に複写し、新しく割り当てたメモリモジュールの変更先メモリアドレスへ複写することにより、メモリデータの互換性を保つようにしている。

従って、メモリアドレスの置き換え対象となったメモリアドレスへのデータ複写作業が終了した段階で、メモリ制御コア部212がメモリモジュールへのアクセスを再開させることにより、問題なく新しいメモリアドレスでメモリデータの読み書きが可能となる。

第4の実施形態によれば、メモリ空間とメモリモジュールのアドレス割り当て変更時に、メモリ複写を行うことにより、割り当て変更後も変更以前に該空間に保持されたメモリデータを使用することが可能となる。

尚、本発明は複数の機器(例えば、ホストコンピュータ,インターフェース機器,リーダ,プリンタなど)から構成されるシステムに適用しても、1つの機器からなる装置(例えば、複写機,ファクシミリ装置など)に適用しても良い。

また、本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ(CPU若しくはMPU)が記録媒体に格納されたプログラムコードを読出し実行することによっても、達成されることは言うまでもない。

この場合、記録媒体から読出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記録媒体は本発明を構成することになる。

このプログラムコードを供給するための記録媒体としては、例えばフロッピー(登録商標)ディスク,ハードディスク,光ディスク,光磁気ディスク,CD−ROM,CD−R,磁気テープ,不揮発性のメモリカード,ROMなどを用いることができる。

また、コンピュータが読出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているOS(オペレーティングシステム)などが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

更に、記録媒体から読出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

101 メモリ制御回路

102 メモリモジュール部

103 メモリ情報レジスタ

104 アクセスパターン判定・設定部

105 メモリインタフェース

106 メモリモジュール

107 メモリモジュール

108 メモリモジュール

109 メモリモジュール

110 DRAM

111 buffer

201 メモリアクセスバス

202 メモリアクセスインタフェース

203 レジスタアクセスバス

204 アクセスパターン判定・設定部

205 メモリ情報レジスタ

207 アクセスパターン判定部

208 メモリアドレス設定部

209 メモリ構成情報レジスタ

210 メモリアドレス設定レジスタ

211 アクセスパターン

212 メモリ制御コア部

213 メモリ書き込みデータ

214 メモリ読み出しデータ

301 メモリモジュール有効フラグ

302 メモリバンク個数

303 行アドレス個数

304 列アドレス個数

305 物理的距離情報

306 メモリ領域下位アドレスレジスタフィールド

307 メモリ領域上位アドレスレジスタフィールド

401 メモリモジュール106領域

402 メモリモジュール107領域

403 メモリモジュール108領域

404 メモリモジュール109領域

505 アクセスカウンタ

601 メモリアクセスカウンタ(メモリ領域1)

602 メモリアクセスカウンタ(メモリ領域2)

603 メモリアクセスカウンタ(メモリ領域3)

604 メモリアクセスカウンタ(メモリ領域4)

701 メモリアクセス回数

1005 ページ遷移カウンタ

1101 ページ遷移カウンタ(メモリ領域1)

1102 ページ遷移カウンタ(メモリ領域2)

1103 ページ遷移カウンタ(メモリ領域3)

1104 ページ遷移カウンタ(メモリ領域4)

1201 ページ遷移回数

1301 バッファ領域

1302 メモリモジュール108のバンク0

1303 メモリモジュール106のバンク0

102 メモリモジュール部

103 メモリ情報レジスタ

104 アクセスパターン判定・設定部

105 メモリインタフェース

106 メモリモジュール

107 メモリモジュール

108 メモリモジュール

109 メモリモジュール

110 DRAM

111 buffer

201 メモリアクセスバス

202 メモリアクセスインタフェース

203 レジスタアクセスバス

204 アクセスパターン判定・設定部

205 メモリ情報レジスタ

207 アクセスパターン判定部

208 メモリアドレス設定部

209 メモリ構成情報レジスタ

210 メモリアドレス設定レジスタ

211 アクセスパターン

212 メモリ制御コア部

213 メモリ書き込みデータ

214 メモリ読み出しデータ

301 メモリモジュール有効フラグ

302 メモリバンク個数

303 行アドレス個数

304 列アドレス個数

305 物理的距離情報

306 メモリ領域下位アドレスレジスタフィールド

307 メモリ領域上位アドレスレジスタフィールド

401 メモリモジュール106領域

402 メモリモジュール107領域

403 メモリモジュール108領域

404 メモリモジュール109領域

505 アクセスカウンタ

601 メモリアクセスカウンタ(メモリ領域1)

602 メモリアクセスカウンタ(メモリ領域2)

603 メモリアクセスカウンタ(メモリ領域3)

604 メモリアクセスカウンタ(メモリ領域4)

701 メモリアクセス回数

1005 ページ遷移カウンタ

1101 ページ遷移カウンタ(メモリ領域1)

1102 ページ遷移カウンタ(メモリ領域2)

1103 ページ遷移カウンタ(メモリ領域3)

1104 ページ遷移カウンタ(メモリ領域4)

1201 ページ遷移回数

1301 バッファ領域

1302 メモリモジュール108のバンク0

1303 メモリモジュール106のバンク0

Claims (8)

- 複数のメモリモジュールに対するアクセスを制御するアクセス制御装置であって、

複数のメモリモジュールへのアクセス状況を判定する判定手段と、

前記判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更手段とを有することを特徴とするアクセス制御装置。 - 前記判定手段は、前記アクセス状況として各メモリモジュールへのアクセスパターンを判定し、前記アドレス設定変更手段は、前記アクセスパターンに基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更することを特徴とする請求項1記載のアクセス制御装置。

- 前記判定手段は、前記アクセス状況として各メモリモジュールへのアクセス回数を計数し、前記アドレス設定変更手段は、前記アクセス回数に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更することを特徴とする請求項1記載のアクセス制御装置。

- 前記判定手段は、前記アクセス状況として各メモリモジュールのページに対するページ遷移数を計数し、前記アドレス設定変更手段は、前記ページ遷移数に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更することを特徴とする請求項1記載のアクセス制御装置。

- 前記アドレス設定変更手段で前記アドレス設定を変更する際に、前記メモリモジュールのデータを変更されたメモリモジュールに複写することを特徴とする請求項3又は請求項4記載のアクセス制御装置。

- 複数のメモリモジュールに対するアクセスを制御するアクセス制御装置の制御方法であって、

複数のメモリモジュールへのアクセス状況を判定する判定工程と、

前記判定の結果に基づいて各メモリモジュールに対応するメモリ空間上のアドレス設定を変更するアドレス設定変更工程とを有することを特徴とするアクセス制御装置の制御方法。 - 請求項6記載のアクセス制御装置の制御方法をコンピュータに実行させるためのプログラム。

- 請求項7記載のプログラムを記録したコンピュータ読み取り可能な記録媒体。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005051369A JP2006236105A (ja) | 2005-02-25 | 2005-02-25 | アクセス制御装置及びその制御方法 |

| US11/345,388 US20060195665A1 (en) | 2005-02-25 | 2006-02-02 | Access control device, method for changing memory addresses, and memory system |

| CNA2006100078923A CN1825473A (zh) | 2005-02-25 | 2006-02-23 | 存储器控制装置、改变存储器地址的方法以及存储系统 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005051369A JP2006236105A (ja) | 2005-02-25 | 2005-02-25 | アクセス制御装置及びその制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006236105A true JP2006236105A (ja) | 2006-09-07 |

| JP2006236105A5 JP2006236105A5 (ja) | 2008-04-10 |

Family

ID=36933127

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005051369A Withdrawn JP2006236105A (ja) | 2005-02-25 | 2005-02-25 | アクセス制御装置及びその制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20060195665A1 (ja) |

| JP (1) | JP2006236105A (ja) |

| CN (1) | CN1825473A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011530734A (ja) * | 2008-08-08 | 2011-12-22 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | 標準メモリモジュールとピン互換性のあるメモリモジュール内における独立制御可能且つ再構成可能な仮想メモリデバイス |

| US8867294B2 (en) | 2010-03-12 | 2014-10-21 | Ps4 Luxco S.A.R.L. | Semiconductor device, refresh control method thereof and computer system |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7904639B2 (en) * | 2006-08-22 | 2011-03-08 | Mosaid Technologies Incorporated | Modular command structure for memory and memory system |

| JP2008242731A (ja) * | 2007-03-27 | 2008-10-09 | Oki Electric Ind Co Ltd | マイクロプロセッサ設計プログラム、マイクロプロセッサ設計装置及びマイクロプロセッサ |

| JP5171448B2 (ja) * | 2007-07-31 | 2013-03-27 | キヤノン株式会社 | 画像形成装置及びその制御方法 |

| JP2011081732A (ja) * | 2009-10-09 | 2011-04-21 | Elpida Memory Inc | 半導体装置及びその調整方法並びにデータ処理システム |

| CN111158600B (zh) * | 2019-12-30 | 2023-10-27 | 中国人民解放军国防科技大学 | 一种提升高带宽存储器(hbm)访问效率的装置和方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6571325B1 (en) * | 1999-09-23 | 2003-05-27 | Rambus Inc. | Pipelined memory controller and method of controlling access to memory devices in a memory system |

| JP4159415B2 (ja) * | 2002-08-23 | 2008-10-01 | エルピーダメモリ株式会社 | メモリモジュール及びメモリシステム |

| US7222224B2 (en) * | 2004-05-21 | 2007-05-22 | Rambus Inc. | System and method for improving performance in computer memory systems supporting multiple memory access latencies |

-

2005

- 2005-02-25 JP JP2005051369A patent/JP2006236105A/ja not_active Withdrawn

-

2006

- 2006-02-02 US US11/345,388 patent/US20060195665A1/en not_active Abandoned

- 2006-02-23 CN CNA2006100078923A patent/CN1825473A/zh active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011530734A (ja) * | 2008-08-08 | 2011-12-22 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | 標準メモリモジュールとピン互換性のあるメモリモジュール内における独立制御可能且つ再構成可能な仮想メモリデバイス |

| KR101477849B1 (ko) * | 2008-08-08 | 2014-12-30 | 휴렛-팩커드 디벨롭먼트 컴퍼니, 엘.피. | 메모리 모듈 및 메모리 모듈 제어 방법 |

| US8924639B2 (en) | 2008-08-08 | 2014-12-30 | Hewlett-Packard Development Company, L.P. | Independently controllable and reconfigurable virtual memory devices in memory modules that are pin-compatible with standard memory modules |

| US8867294B2 (en) | 2010-03-12 | 2014-10-21 | Ps4 Luxco S.A.R.L. | Semiconductor device, refresh control method thereof and computer system |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060195665A1 (en) | 2006-08-31 |

| CN1825473A (zh) | 2006-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5835435A (en) | Method and apparatus for dynamically placing portions of a memory in a reduced power consumtion state | |

| US9343127B1 (en) | Memory device having an adaptable number of open rows | |

| US20180275921A1 (en) | Storage device | |

| JP2006236105A (ja) | アクセス制御装置及びその制御方法 | |

| JP2006313538A (ja) | メモリモジュール及びメモリシステム | |

| JP2007220110A (ja) | 埋め込み型コンピュータシステムの各構成部材のための共通化インターフェース | |

| JP2008305350A (ja) | メモリシステム、メモリ装置、およびメモリ装置の制御方法 | |

| US11042304B2 (en) | Determining a transfer rate for channels of a memory system | |

| CN101140792A (zh) | 同步半导体存储器件 | |

| US8433835B2 (en) | Information processing system and control method thereof | |

| JP5188134B2 (ja) | メモリアクセス制御装置及びメモリアクセス制御方法 | |

| CN108139994B (zh) | 内存访问方法及内存控制器 | |

| JP2014154119A (ja) | メモリ制御装置及び半導体記憶装置 | |

| US11829640B2 (en) | Asynchronous arbitration across clock domains for register writes in an integrated circuit chip | |

| JP5349775B2 (ja) | メモリコントローラ及びその制御方法 | |

| US20180181335A1 (en) | Apparatus and method to speed up memory frequency switch flow | |

| US20210157389A1 (en) | Standby current reduction in memory devices | |

| JP6170363B2 (ja) | 制御装置、コンピュータシステム、制御方法、及びプログラム | |

| JP2004127305A (ja) | メモリ制御装置 | |

| US8074096B2 (en) | Semiconductor integrated circuit, memory system, memory controller and memory control method | |

| CN112965816B (zh) | 内存管理技术及计算机系统 | |

| JP2007334835A (ja) | メモリ制御装置及びその制御方法 | |

| JP2006146340A (ja) | メモリ制御装置及びメモリ制御方法 | |

| JP2008040896A (ja) | メモリ制御装置及びメモリ制御方法 | |

| JP2008117242A (ja) | データ転送制御装置、及び、データ転送制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080221 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090821 |