JP2006105997A - 電子デバイスにスキャンパターンを提供する方法および装置 - Google Patents

電子デバイスにスキャンパターンを提供する方法および装置 Download PDFInfo

- Publication number

- JP2006105997A JP2006105997A JP2005292299A JP2005292299A JP2006105997A JP 2006105997 A JP2006105997 A JP 2006105997A JP 2005292299 A JP2005292299 A JP 2005292299A JP 2005292299 A JP2005292299 A JP 2005292299A JP 2006105997 A JP2006105997 A JP 2006105997A

- Authority

- JP

- Japan

- Prior art keywords

- test

- scan

- scan test

- series

- patterns

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims description 32

- 238000012360 testing method Methods 0.000 claims abstract description 142

- 230000004044 response Effects 0.000 claims abstract description 50

- 238000002405 diagnostic procedure Methods 0.000 claims abstract description 32

- 238000004519 manufacturing process Methods 0.000 claims abstract description 30

- 230000007547 defect Effects 0.000 claims abstract description 23

- 239000013598 vector Substances 0.000 claims description 22

- 230000002950 deficient Effects 0.000 description 7

- 230000006870 function Effects 0.000 description 5

- 238000012029 structural testing Methods 0.000 description 2

- 230000006378 damage Effects 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000011990 functional testing Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/319—Tester hardware, i.e. output processing circuits

- G01R31/31917—Stimuli generation or application of test patterns to the device under test [DUT]

- G01R31/31919—Storing and outputting test patterns

- G01R31/31921—Storing and outputting test patterns using compression techniques, e.g. patterns sequencer

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318533—Reconfiguring for testing, e.g. LSSD, partitioning using scanning techniques, e.g. LSSD, Boundary Scan, JTAG

- G01R31/318544—Scanning methods, algorithms and patterns

- G01R31/318547—Data generators or compressors

Abstract

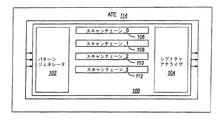

【解決手段】 電子デバイス(100)は、生産テストモードと診断テストモードを備えたBISTハードウェア(102、104)を有し、スキャンパターンを提供すると、生産テストモードで応答シグネチャを出力し、診断テストモードで生応答データを出力する。生産テストモードで、ATE(114)から、i)第1のスキャンテストパターンをBISTハードウェア(102,104)に提供し、ii)応答シグネチャと予想応答シグネチャとを比較して、欠陥スキャンテストパターンを識別する。次に、ATE(114)により、欠陥スキャンテストパターンと関連した固有ラベルを識別し、診断テストモードで、i)第2のスキャンテストパターンをBISTハードウェア(102,104)に提供し、ii)生応答データを捕捉する。第2のスキャンテストパターンは、識別されたラベルに対応する。

【選択図】 図2

Description

102 パターンジェネレータ

104 シグナチャアナライザ

106、108、110、112 スキャンチェーン

114 ATE

Claims (10)

- 組み込み自己テストハードウェアを有する電子デバイスにスキャンパターンを提供する方法であって、前記自己テストハードウェアが、生産テストモードと診断テストモードを有し、前記電子デバイスが、前記生産テストモードで1つまたは複数の応答シグネチャを出力し、前記診断テストモードで生応答データを出力し、

生産テストモードにおいて、自動テスト機器を使用して、i)第1の一連のスキャンテストパターンを前記自己テストハードウェアに提供し、ii)応答シグネチャを捕捉し予想応答シグネチャと比較して、いくつかの欠陥スキャンテストパターンを識別するステップと、

前記自動テスト機器を使用して、前記欠陥スキャンテストパターンと関連したいくつかの固有ラベルを識別すると、

診断テストモードにおいて、前記自動テスト機器を使用して、i)第2の一連のスキャンテストパターンを前記自己テスハードウェアに提供し、前記第2の一連のスキャンテストパターンにおけるスキャンテストパターンが前記識別されたラベルに対応し、ii)生応答データを捕捉するステップと、

を含むことを特徴とする方法。 - それぞれの一連のスキャンテストパターンが、スキャンテストパターンの複数の区間を含み、前記いくつかの欠陥スキャンテストパターンが、スキャンテストパターンのいくつかの欠陥区間に対応するラベルを識別することによって識別されることを特徴とする請求項1に記載の方法。

- 前記第1の一連のスキャンテストパターンが、単一の生産テストベクトル内で実行されることを特徴とする請求項1に記載の方法。

- 前記ATE(114)が、前記識別したラベルを単一の診断テストベクトルに動的にコンパイルすることを特徴とする請求項1に記載の方法(200)。

- 前記自動テスト機器が、前記第2の一連のスキャンテストパターンにおける前記スキャンテストパターンを前記自己テストハードウェアに提供するときに複数の診断テストベクトルを動的に生成し実行することを特徴とする請求項1に記載の方法。

- コンピュータ可読媒体と、

前記コンピュータ可読媒体に記憶され、自動テスト機器に、

電子デバイスの組み込み自己テストハードウェアを生産テストモードにする動作、

第1の一連のスキャンテストパターンを前記自己テストハードウェアに提供する動作、

前記スキャンテストパターンに対応する応答シグネチャを捕捉する動作、

前記捕捉した応答シグネチャを予想応答シグネチャと比較して、いくつかの欠陥スキャンテストパターンを識別する動作、

前記欠陥スキャンテストパターンと関連した固有ラベルの数を識別する動作、

前記自己テストハードウェアを診断テストモードにする動作、

前記自己テストハードウェアに第2の一連のスキャンテストパターンを提供する動作であって、前記第2の一連のスキャンテストパターンにおける前記スキャンテストパターンが前記識別したラベルに対応する動作、および、

前記スキャンテストパターンに対応する生応答データを捕捉する動作、

を実行させるプログラムコードと、

を有することを特徴とする装置。 - それぞれの一連のスキャンテストパターンが、スキャンテストパターンの複数の区間を含み、前記プログラムコードが、スキャンテストパターンのいくつかの欠陥区間を識別することによっていくつかの欠陥スキャンテストパターンを識別することを特徴とする請求項6に記載の装置。

- 前記プログラムコードが、前記第1の一連のスキャンテストパターンを単一の生産テストベクトル内で実行させることを特徴とする請求項6に記載の装置。

- 前記プログラムコードが、前記自動テスト機器に、前記識別したラベルを単一の診断テストベクトルに動的にコンパイルさせることを特徴とする請求項6に記載の装置。

- 前記第2の一連のスキャンテストパターンにおけるスキャンテストパターンを前記自己テストハードウェアに提供するときに、前記プログラムコードが前記自動テスト機器に複数の診断テストベクトルを動的に生成させ実行させることを特徴とする請求項6に記載の装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/959,856 US7254760B2 (en) | 2004-10-05 | 2004-10-05 | Methods and apparatus for providing scan patterns to an electronic device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006105997A true JP2006105997A (ja) | 2006-04-20 |

| JP2006105997A5 JP2006105997A5 (ja) | 2008-11-13 |

Family

ID=36120724

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005292299A Pending JP2006105997A (ja) | 2004-10-05 | 2005-10-05 | 電子デバイスにスキャンパターンを提供する方法および装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7254760B2 (ja) |

| JP (1) | JP2006105997A (ja) |

| DE (1) | DE102005026403B4 (ja) |

| TW (1) | TWI370261B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7685487B1 (en) * | 2005-03-22 | 2010-03-23 | Advanced Micro Devices, Inc. | Simultaneous core testing in multi-core integrated circuits |

| US7526694B1 (en) * | 2006-08-03 | 2009-04-28 | Xilinx, Inc. | Integrated circuit internal test circuit and method of testing therewith |

| US20080077835A1 (en) * | 2006-09-27 | 2008-03-27 | Khoche A Jay | Automatic Test Equipment Receiving Diagnostic Information from Devices with Built-in Self Test |

| US7650547B2 (en) * | 2007-02-28 | 2010-01-19 | Verigy (Singapore) Pte. Ltd. | Apparatus for locating a defect in a scan chain while testing digital logic |

| US8127186B2 (en) | 2007-02-28 | 2012-02-28 | Verigy (Singapore) Pte. Ltd. | Methods and apparatus for estimating a position of a stuck-at defect in a scan chain of a device under test |

| US20080235545A1 (en) * | 2007-03-06 | 2008-09-25 | Vinay Burjinroppa Jayaram | Re-using production test scan paths for system test of an integrated circuit |

| US9183105B2 (en) * | 2013-02-04 | 2015-11-10 | Alcatel Lucent | Systems and methods for dynamic scan scheduling |

| CN108508352B (zh) * | 2018-04-19 | 2020-11-24 | 中国电子科技集团公司第五十八研究所 | 一种测试码生成电路 |

| US11156660B1 (en) * | 2019-12-19 | 2021-10-26 | Cadence Design Systems, Inc. | In-system scan test of electronic devices |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11202026A (ja) * | 1998-01-13 | 1999-07-30 | Hitachi Ltd | 不良解析手法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5790562A (en) * | 1996-05-06 | 1998-08-04 | General Motors Corporation | Circuit with built-in test and method thereof |

| US6393594B1 (en) * | 1999-08-11 | 2002-05-21 | International Business Machines Corporation | Method and system for performing pseudo-random testing of an integrated circuit |

| US6591211B1 (en) * | 1999-08-27 | 2003-07-08 | Intel Corporation | Testing unit and self-evaluating device |

| US6557129B1 (en) | 1999-11-23 | 2003-04-29 | Janusz Rajski | Method and apparatus for selectively compacting test responses |

| US6424926B1 (en) * | 2000-03-31 | 2002-07-23 | Intel Corporation | Bus signature analyzer and behavioral functional test method |

| DE10122619C1 (de) * | 2001-05-10 | 2003-02-13 | Infineon Technologies Ag | Testschaltung zum Testen einer synchronen Schaltung |

| US7159145B2 (en) * | 2003-05-12 | 2007-01-02 | Infineon Technologies Ag | Built-in self test system and method |

| US7321999B2 (en) * | 2004-10-05 | 2008-01-22 | Verigy (Singapore) Pte. Ltd. | Methods and apparatus for programming and operating automated test equipment |

-

2004

- 2004-10-05 US US10/959,856 patent/US7254760B2/en active Active

-

2005

- 2005-04-14 TW TW094111829A patent/TWI370261B/zh active

- 2005-06-08 DE DE102005026403A patent/DE102005026403B4/de not_active Expired - Fee Related

- 2005-10-05 JP JP2005292299A patent/JP2006105997A/ja active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11202026A (ja) * | 1998-01-13 | 1999-07-30 | Hitachi Ltd | 不良解析手法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7254760B2 (en) | 2007-08-07 |

| TW200612239A (en) | 2006-04-16 |

| US20060075316A1 (en) | 2006-04-06 |

| DE102005026403B4 (de) | 2007-12-13 |

| DE102005026403A1 (de) | 2006-04-20 |

| TWI370261B (en) | 2012-08-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7908532B2 (en) | Automated system and processing for expedient diagnosis of broken shift registers latch chains | |

| US7774662B2 (en) | Method and structure for picosecond-imaging-circuit-analysis based built-in-self-test diagnostic | |

| JP2006105997A (ja) | 電子デバイスにスキャンパターンを提供する方法および装置 | |

| US8522097B2 (en) | Logic built-in self-test programmable pattern bit mask | |

| US7475308B2 (en) | implementing deterministic based broken scan chain diagnostics | |

| US7010735B2 (en) | Stuck-at fault scan chain diagnostic method | |

| US10509072B2 (en) | Test application time reduction using capture-per-cycle test points | |

| US20090132882A1 (en) | Scan-load-based dynamic scan configuration | |

| TWI781634B (zh) | 用以測試一或多個受測裝置之自動化測試裝備、方法及電腦程式,其中不同測試活動使用受測裝置資源之子集 | |

| US7921346B2 (en) | Verification of array built-in self-test (ABIST) design-for-test/design-for-diagnostics (DFT/DFD) | |

| US6557132B2 (en) | Method and system for determining common failure modes for integrated circuits | |

| US11815555B2 (en) | Universal compactor architecture for testing circuits | |

| US7607057B2 (en) | Test wrapper including integrated scan chain for testing embedded hard macro in an integrated circuit chip | |

| US8423845B2 (en) | On-chip logic to log failures during production testing and enable debugging for failure diagnosis | |

| US10963612B2 (en) | Scan cell architecture for improving test coverage and reducing test application time | |

| US6314540B1 (en) | Partitioned pseudo-random logic test for improved manufacturability of semiconductor chips | |

| JP2006105996A (ja) | 自動テスト機器をプログラミングし操作する方法および装置 | |

| US10247776B2 (en) | Structurally assisted functional test and diagnostics for integrated circuits | |

| US6865704B2 (en) | Scan multiplexing for increasing the effective scan data exchange rate | |

| Cook et al. | Diagnosis of multiple faults with highly compacted test responses | |

| US20090210761A1 (en) | AC Scan Diagnostic Method and Apparatus Utilizing Functional Architecture Verification Patterns | |

| US11092645B2 (en) | Chain testing and diagnosis using two-dimensional scan architecture | |

| US10613142B2 (en) | Non-destructive recirculation test support for integrated circuits | |

| Parker et al. | Boundary-Scan Testing | |

| JP2004333370A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20071025 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080929 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110819 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120131 |