-

GEBIET

-

Die vorliegende Erfindung betrifft das Gebiet der Computerprozessoren und insbesondere das Optimieren von Anweisungen für die Ausführung während der Anweisungs-Decodierzeit in einem Prozessor.

-

HINTERGRUND

-

US-Patentanmeldung Nr. 2011/0087865 ”Intermediate Register Mapper”, veröffentlicht am 14.4.2011 durch Barrick et al. und durch Verweis hierin einbezogen, erläutert ”ein Verfahren, einen Prozessor und ein Computerprogramm-Produkt, welche eine temporäre Registerzuordnungsfunktion in einem Registerumbenennungs-Mechanismus verwenden. Eine Suche in den logischen Registern ermittelt, ob bei einem mit der abgefertigten Anweisung verknüpften logischen Register ein Treffer aufgetreten ist. In dieser Hinsicht durchläuft die Suche in den logischen Registern mindestens eine Registerzuordnungsfunktion aus einer Gruppe von Registerzuordnungsfunktionen, die eine Zuordnungsfunktion für architekturdefinierte Register, eine vereinheitlichte Hauptzuordnungsfunktion und eine temporäre Registerzuordnungsfunktion beinhaltet. Ein einzelner Treffer beim logischen Register wird aus der Gruppe von Registerzuordnungsfunktionen ausgewählt. Wenn eine Anweisung mit einem Zuordnungsfunktions-Eintrag in der vereinheitlichten Hauptzuordnungsfunktion beendet, aber nicht abgeschlossen ist, wird der Zuordnungsinhalt des Registerzuordnungsfunktions-Eintrags in der vereinheitlichten Hauptzuordnungsfunktion zur temporären Registerzuordnungsfunktion verschoben und wird der Eintrag der vereinheitlichten Registerzuordnungsfunktion freigegeben, was eine Anzahl von für die Wiederverwendung verfügbaren Einträgen der vereinheitlichten Hauptzuordnungsfunktion erhöht.”

-

Die am 2. April 1998 eingereichte

US-Patentschrift Nr. 6 314 511 ”Mechanism for freeing registers on processors that perform dynamic out-of-order execution of instructions using renaming registers” von Levy et al., durch Verweis hierin einbezogen, erläutert das ”Freigeben von Umbenennungsregistern, die architekturdefinierten Registern zugeordnet wurden, bevor eine andere Anweisung das architekturdefinierte Register neu definierte. Umbenennungsregister werden von einem Prozessor verwendet, um Anweisungen entweder in einem Einzel- oder in einem Multithread-Prozessor, der Anweisungen ”out-of-order” (unter Missachtung der Reihenfolge) ausführt, dynamisch ”out-of-order” auszuführen. Ein Mechanismus zum Freigeben von Umbenennungsregistern wird beschrieben, der aus einem Satz von Anweisungen besteht, die von einem Compiler verwendet werden, um dem Prozessor anzuzeigen, wann er das physische (Umbenennungs-)Register, das einem bestimmten architekturdefinierten Register zugeordnet ist, freigeben kann. Durch diesen Mechanismus kann das Umbenennungsregister neu zugewiesen oder neu zugeordnet werden, um einen anderen Wert zu speichern, sobald das Umbenennungsregister nicht mehr für das Zuordnen zum architekturdefinierten Register benötigt wird. Es gibt mindestens drei Arten und Weisen, den Prozessor mit einer Anweisung, die das vom Zuordnen zu befreiende Umbenennungsregister identifiziert, zu aktivieren: (1) ein Benutzer kann die Anweisung, die sich auf ein bestimmtes Umbenennungsregister bezieht, explizit an den Prozessor bereitstellen; (2) ein Betriebssystem kann die Anweisung bereitstellen, wenn ein Thread inaktiv ist, der sich auf einen mit dem Thread verknüpften Satz von Registern bezieht; und (3) ein Compiler kann die Anweisung in die Vielzahl von an den Prozessor gerichteten Anweisungen einschließen. Es gibt mindestens fünf Ausführungsformen der an den Prozessor bereitgestellten Anweisung, um architekturdefinierten Registern zugeordnete Umbenennungsregister freizugeben: (1) Register-Bit freigeben; (2) Register freigeben; (3) Maske freigeben; (4) Opcode freigeben; und (5) Opcode/Maske freigeben. Die Anweisung ”Register-Bit freigeben” bewirkt die größte Beschleunigung für einen ”Out-of-Order”-Prozessor, und die Anweisung ”Register freigeben” bewirkt die geringste Beschleunigung.”

-

”Power ISATM Version 2.06 Revision B”, veröffentlicht am 23. Juli 2010, von IBM® und durch Verweis hierin einbezogen, erläutert eine beispielhafte RISC-(reduced instruction set computer)Anweisungssatz-Architektur. Power ISA wird hierin verwendet, um beispielhafte Ausführungsformen darzulegen, jedoch ist die Erfindung nicht auf Power ISA oder RISC-Architekturen beschränkt. Der Fachmann wird den Nutzen von Aspekten der Erfindung in einer Vielzahl von Architekturen ohne weiteres erkennen.

-

”z/Architecture Principles of Operation” SA22-7832-08, Neunte Ausgabe (August 2010) von IBM® und durch Verweis hierin einbezogen, erläutert eine beispielhafte CISC-(complex instruction set computer)Anweisungssatz-Architektur.

-

KURZBESCHREIBUNG

-

In einer Ausführungsform geht eine Präfixanweisung einer nächsten Anweisung voraus, wobei die Präfixanweisung einen vom Prozessor beim Ausführen der nächsten Anweisung zu verwendenden Wert bereitstellt. Der Prozessor erhält eine erste Anweisung (Präfixanweisung) und eine zweite Anweisung (nächste Anweisung) zur Ausführung, wobei die erste Anweisung der zweiten Anweisung in Programmreihenfolge vorausgeht. Der Prozessor ermittelt, dass die erste Anweisung eine Präfixanweisung ist, wobei die Präfixanweisung einen beim Ausführen der zweiten Anweisung zu verwendenden ersten Wert angibt, wobei die zweite Anweisung einen beim Ausführen der zweiten Anweisung zu verwendenden zweiten Wert angibt. Der Prozessor führt die erste Anweisung ohne Speichern des ersten Werts auf einer von der Anweisung angegebenen Position erfolgreich aus und führt die zweite Anweisung unter Verwendung des ersten Werts ohne Abrufen des ersten Werts auf einer zweiten von der Anweisung angegebenen Position erfolgreich aus.

-

In einer Ausführungsform beinhaltet das Ermitteln außerdem das Ermitteln, dass es kein eingreifendes Unterbrechungsereignis zwischen der erfolgreichen Ausführung der ersten Anweisung und der zweiten Anweisung gibt.

-

In einer Ausführungsform wird der beim Ausführen der zweiten Anweisung zu verwendende Wert als ein Ergebnisregister der ersten Anweisung identifiziert, wobei das Ergebnisregister der ersten Anweisung ein Quellenregister der zweiten Anweisung ist.

-

In einer Ausführungsform ist das Ergebnisregister ein mit einem architekturdefinierten Anweisungssatz verknüpftes architekturdefiniertes Register, das entweder aus einem Allgemeinregister oder aus einem Gleitkommaregister besteht.

-

In einer Ausführungsform wird der beim Ausführen der zweiten Anweisung zu verwendende Wert als ein Hauptspeicheroperand der ersten Anweisung identifiziert, wobei der Hauptspeicheroperand der ersten Anweisung ein Quellen-Speicheroperand der zweiten Anweisung ist.

-

In einer Ausführungsform beinhaltet der zu verwendende Wert ein Ergebnis des Ausführens der ersten Anweisung und ein Direktfeld der ersten Anweisung, wobei das erfolgreiche Ausführen außerdem das Verwenden eines verketteten Werts aus mindestens einem Teil des Direktfelds der ersten Anweisung und einem Direktfeld der zweiten Anweisung beinhaltet.

-

In einer Ausführungsform wird eine einzige interne Anweisung auf Grundlage der ersten Anweisung und der zweiten Anweisung formatiert, wobei das erfolgreiche Ausführen das Ausführen der einzigen internen Anweisung beinhaltet.

-

Ebenso werden hierin System und Computerprogramm-Produkte entsprechend den oben zusammengefassten Verfahren beschrieben und beansprucht.

-

Zusätzliche Funktionsmerkmale und Vorteile werden durch die Verfahren der vorliegenden Erfindung realisiert. Weitere Ausführungsformen und Aspekte der Erfindung sind hierin ausführlich beschrieben und werden als Bestandteil der beanspruchten Erfindung betrachtet.

-

KURZBESCHREIBUNG DER ZEICHNUNGEN

-

Der Gegenstand, welcher als die Erfindung angesehen wird, wird in den Ansprüchen am Ende der Beschreibung genau dargelegt und klar beansprucht. Die vorerwähnten und weitere Aufgaben, Merkmale und Vorteile der Erfindung sind aus der folgenden ausführlichen Beschreibung in Verbindung mit den folgenden beigefügten Zeichnungen ersichtlich:

-

1 veranschaulicht eine beispielhafte Prozessor-Systemkonfiguration;

-

2 veranschaulicht eine erste beispielhafte Prozessor-Pipeline;

-

3 veranschaulicht eine zweite beispielhafte Prozessor-Pipeline;

-

4A veranschaulicht eine beispielhafte Optimierungsanalyse-Steuerkomponentenumgebung;

-

Die 4B bis 4E veranschaulichen eine beispielhafte Optimierung;

-

5 ist ein beispielhafter Ablaufplan, der Aspekte einer Ausführungsform der Erfindung veranschaulicht; und

-

6 ist ein beispielhafter Ablaufplan, der Aspekte einer Ausführungsform der Erfindung veranschaulicht.

-

AUSFÜHRLICHE BESCHREIBUNG

-

Ein ”Out-of-Order”-(OoO-)Prozessor enthält üblicherweise mehrere Ausführungs-Pipelines, die in opportunistischer Weise Anweisungen in einer anderen Reihenfolge als der von der Programmsequenz (oder ”Programmreihenfolge”) angegebenen ausführen können, um durch Verringern von Datenabhängigkeiten und Maximieren der Auslastung der für verschiedene Anweisungsarten zugeordneten Ausführungs-Pipelines die mittlere Anzahl von Anweisungen pro Zyklus zu maximieren. Die Ergebnisse der Anweisungsausführung werden üblicherweise vorübergehend in den physischen Registern einer oder mehrerer Registerdateien begrenzter Tiefe untergebracht. Ein OoO-Prozessor verwendet üblicherweise Registerumbenennung, um eine unnötige Durchnummerierung von Anweisungen wegen der Wiederverwendung eines gegebenen architekturdefinierten Registers durch nachfolgende Anweisungen in der Programmreihenfolge zu vermeiden.

-

Nach

US 2011/0087865 (Barrick) wird während Registerumbenennungsoperationen jedes durch eine Anweisung angesprochene architekturdefinierte (d. h. logische) Register einem eindeutigen physischen Register in einer Registerdatei zugeordnet. In aktuellen Hochleistungs-OoO-Prozessoren wird eine vereinheitlichte Hauptzuordnungsfunktion genutzt, um die physischen Register in mehreren Registerdateien zu verwalten. Neben dem Speichern der logisch-zu-physischen Registerumsetzung (d. h. in Zuordnungsfunktions-Einträgen) ist die vereinheitlichte Hauptzuordnungsfunktion auch für das Speichern von Abhängigkeitsdaten (d. h. Warteschlangen-Positionsdaten) zuständig, was für das Ordnen der Anweisungen bei Abschluss wichtig ist.

-

In einem auf vereinheitlichten Hauptzuordnungsfunktionen beruhenden Umbenennungsschema ist es erwünscht, Zuordnungsfunktions-Einträge so bald wie möglich für die Wiederverwendung durch den OoO-Prozessor freizugeben. Jedoch kann nach Stand der Technik ein Eintrag der vereinheitlichten Hauptzuordnungsfunktion nicht freigegeben werden, bis die Anweisung, die in ein durch den Zuordnungsfunktions-Eintrag zugeordnetes Register schreibt, abgeschlossen ist. Diese Einschränkung wird durchgesetzt, weil bis zum Abschluss eine Möglichkeit besteht, dass eine Anweisung, die ”beendet” ist (d. h. die bestimmte Ausführungseinheit (EU – execution unit) hat die Anweisung erfolgreich ausgeführt), noch gelöscht wird, bevor die Anweisung ”abgeschlossen” werden kann und bevor der architekturdefinierte, kohärente Zustand der Register aktualisiert wird.

-

In aktuellen Implementierungen wurde Ressourcenengpässen bei der vereinheitlichten Hauptzuordnungsfunktion gewöhnlich durch Erhöhen der Anzahl der Einträge der vereinheitlichten Hauptzuordnungsfunktion begegnet. Jedoch ist das Erhöhen der Größe der vereinheitlichten Hauptzuordnungsfunktion hinsichtlich Chipfläche, Komplexität, Energieverbrauch und Zugriffszeit mit einem Nachteil verbunden.

-

Bei Barrick wird ein Verfahren zum Verwalten eines Satzes von einem oder mehreren physischen Registern in einem Datenverarbeitungssystem bereitgestellt. Das Datenverarbeitungssystem hat einen Prozessor, der Anweisungen unter Missachtung der Reihenfolge verarbeitet, wobei die Anweisungen auf logische Register verweisen und wobei jedes der logischen Register dem Satz aus einem oder mehreren physischen Registern zugeordnet wird. In Reaktion auf die Abfertigung einer oder mehrerer der Anweisungen führt eine Registerverwaltungseinheit eine Suche in den logischen Registern durch, welche ermittelt, ob bei einem mit der abgefertigten Anweisung verknüpften logischen Register in einer oder mehreren Registerzuordnungsfunktionen ein Treffer aufgetreten ist. In dieser Hinsicht durchläuft die Suche in den logischen Registern mindestens eine Registerzuordnungsfunktion aus einer Gruppe von Registerzuordnungsfunktionen, die eine Zuordnungsfunktion für architekturdefinierte Register, eine vereinheitlichte Hauptzuordnungsfunktion und eine temporäre Registerzuordnungsfunktion beinhaltet. Die Registerverwaltungseinheit wählt einen einzelnen Treffer beim logischen Register aus der Gruppe von Registerzuordnungsfunktionen aus. Wenn eine Anweisung mit einem Zuordnungsfunktions-Eintrag in der vereinheitlichten Hauptzuordnungsfunktion beendet, aber nicht abgeschlossen ist, verschiebt die Registerverwaltungseinheit logisch-zu-physische Registerumbenennungsdaten des Eintrags der vereinheitlichten Hauptzuordnung in der vereinheitlichten Hauptzuordnungsfunktion zur temporären Registerzuordnungsfunktion und gibt die vereinheitlichte Hauptzuordnungsfunktion den Eintrag der vereinheitlichten Hauptzuordnung vor Abschluss der Anweisung frei. Die Freigabe des Eintrags der vereinheitlichten Hauptzuordnung erhöht eine Anzahl von für die Wiederverwendung verfügbaren Einträgen der vereinheitlichten Hauptzuordnung.

-

Die Figuren und insbesondere 1 zeigen ein Beispiel eines Datenverarbeitungssystems 100, welches einen OoO-Prozessor enthalten kann, der eine temporäre Registerzuordnungsfunktion wie unten anhand 2 beschrieben verwendet. Wie in 1 gezeigt, verfügt das Datenverarbeitungssystem 100 über eine Zentraleinheit (CPU) 110, welche mit Prozessor 200 in 2 implementiert sein kann. Die CPU 110 ist durch eine Verschaltung 112 mit verschiedenen weiteren Komponenten verbunden. Ein Nur-Lese-Speicher (ROM – read-only memory) 116 ist mit der Verschaltung 112 verbunden und enthält ein ”Basic Input/Output System” (BIOS), das bestimmte grundlegende Funktionen des Datenverarbeitungssystems 100 steuert. Ein Direktzugriffsspeicher (RAM – random access memory) 114, ein E/A-Adapter 118 und ein DFV-Adapter 134 sind ebenfalls mit dem Systembus 112 verbunden. Der E/A-Adapter 118 kann ein Small-Computer-System-Interface-(”SCSI”-)Adapter sein, der mit einer Speichereinheit 120 Daten austauscht. Der DFV-Adapter 134 verbindet die Verschaltung 112 mit dem Netz 140, was dem Datenverarbeitungssystem 100 ermöglicht, mit anderen solchen Systemen wie einem fernen Computer 142 Daten auszutauschen. Ein/Ausgabe-Einheiten sind außerdem über einen Benutzerschnittstellenadapter 122 und einen Bildschirmadapter 136 mit der Verschaltung 112 verbunden. Eine Tastatur 124, ein Trackball 132, eine Maus 126 und ein Lautsprecher 128 sind alle über den Benutzerschnittstellenadapter 122 mit dem Bus 112 verbunden. Ein Bildschirm 138 ist über einen Bildschirmadapter 136 mit dem Systembus 112 verbunden. Auf diese Weise empfängt das Datenverarbeitungssystem 100 Eingaben zum Beispiel über die Tastatur 124, den Trackball 132 und/oder die Maus 126 und liefert es Ausgaben zum Beispiel über das Netz 140 auf die Speichereinheit 120, den Lautsprecher 128 und/oder den Bildschirm 138. Die im Datenverarbeitungssystem 100 veranschaulichten Hardware-Elemente sollen nicht erschöpfend sein, sondern vielmehr Hauptkomponenten eines Datenverarbeitungssystems in einer einzigen Ausführungsform darstellen.

-

Der Betrieb des Datenverarbeitungssystems 100 kann durch Programmcode wie Firmware und/oder Software gesteuert werden, welcher üblicherweise zum Beispiel ein Betriebssystem wie AIX® (”AIX” ist ein Warenzeichen der IBM Corporation) und ein oder mehrere Anwendungs- oder Middleware-Programme enthält. Ein solcher Programmcode weist die unten im Zusammenhang mit 2 erörterten Anweisungen auf.

-

In 2 ist ein superskalarer Prozessor 200 dargestellt. Anweisungen werden aus einem Speicher (z. B. RAM 114 in 1) abgerufen und in eine Anweisungssequenzbildungslogik (ISL – instruction sequencing logic) 204 geladen, welche einen Level-1-Anweisungs-Cachespeicher (L1-I-Cachespeicher) 206, eine Abruf-Decodier-Einheit 208, eine Anweisungswarteschlange 210 und eine Abfertigungseinheit 212 enthält. Speziell werden die Anweisungen in einen L1-I-Cachespeicher 206 von ISL 204 geladen. Die Anweisungen werden im L1-I-Cachespeicher 206 aufbewahrt, bis sie benötigt werden, oder ersetzt, wenn sie nicht benötigt werden. Die Anweisungen werden aus dem L1-I-Cachespeicher 206 abgerufen und durch die Abruf-Decodier-Einheit 208 decodiert. Nach Decodieren einer aktuellen Anweisung wird die aktuelle Anweisung in die Anweisungswarteschlange 210 geladen. Die Abfertigungseinheit 212 fertigt Anweisungen aus der Anweisungswarteschlange 210 an eine Registerverwaltungseinheit 214 sowie eine Abschlusseinheit 240 ab. Die Abschlusseinheit 240 ist mit einer allgemeinen Ausführungseinheit 224 und der Registerverwaltungseinheit 214 verbunden und überwacht, wann eine ausgegebene Anweisung abgeschlossen ist.

-

Wenn die Abfertigungseinheit 212 eine aktuelle Anweisung abfertigt, ordnet die vereinheitlichte Hauptzuordnungsfunktion 218 der Registerverwaltungseinheit 214 einem physischen Register in den Physische-Register-Dateien 232a bis 232n, das gerade keinem logischen Register zugewiesen ist, die Nummer eines logischen Zielregisters zu. Bei dem Ziel wird davon ausgegangen, dass es zu dem bezeichneten physischen Register aus den Physische-Register-Dateien 232a bis 232n umbenannt wird. Die vereinheitlichte Hauptzuordnungsfunktion 218 entfernt das zugewiesene physische Register aus einer in der vereinheitlichten Hauptzuordnungsfunktion 218 gespeicherten Liste 219 freier physischer Register. Alle nachfolgenden Verweise auf dieses logische Zielregister werden auf dasselbe physische Register verweisen, bis die Abruf-Decodier-Einheit 208 eine weitere Anweisung decodiert, die in dasselbe logische Register schreibt. Dann benennt die vereinheitlichte Hauptzuordnungsfunktion 218 das logische Register in eine andere, aus der Frei-Liste 219 ausgewählte physische Position um und wird die Zuordnungsfunktion aktualisiert, um die neuen logisch-zu-physischen Registerzuordnungsfunktionsdaten einzugeben. Wenn die logisch-zu-physischen Registerzuordnungsfunktionsdaten nicht mehr benötigt werden, werden die physischen Register alter Zuordnungen an die Frei-Liste 219 zurückgegeben. Wenn die Liste freier physischer Register 219 nicht genug physische Register enthält, setzt die Abfertigungseinheit 212 die Anweisungsabfertigung aus, bis die benötigten physischen Register verfügbar werden.

-

Nachdem die Registerverwaltungseinheit 214 die aktuelle Anweisung zugeordnet hat, gibt eine Ausgabewarteschlange 222 die aktuelle Anweisung an eine Steuerkomponente für die allgemeine Ausführung 224 aus, welche Ausführungseinheiten (EUs – execution units) 230a bis 230n enthält. Die Ausführungseinheiten 230a bis 230n sind von verschiedenen Typen wie Gleitkomma (FP – floating-point), Festkomma (FX – fixed-point) und Laden/Speichern (LS – load/store). Die Steuerkomponente für die allgemeine Ausführung 224 tauscht über einen Daten-Cachespeicher 234 mit einem Datenspeicher (z. B. RAM 114, ROM 116 in 1) Daten aus. Außerdem kann die Ausgabewarteschlange 222 Anweisungen des Typs FP, des Typs FX sowie LS-Anweisungen enthalten. Jedoch sollte man erkennen, dass jede beliebige Anzahl und Art von Anweisungen verwendet werden kann. Während der Ausführung erhalten die Ausführungseinheiten (EUs) 230a bis 230n die Quellenoperandenwerte von physischen Positionen in den Registerdateien 232a bis 232n und speichern sie Ergebnisdaten, falls vorhanden, in den Registerdateien 232a bis 232n und/oder im Daten-Cachespeicher 234.

-

Wie weiter durch 2 veranschaulicht, enthält die Registerverwaltungseinheit 214 Folgendes: (i) einen Zuordnungsfunktions-Cluster 215, welcher eine Zuordnungsfunktion für architekturdefinierte Register 216, eine vereinheitlichte Hauptzuordnungsfunktion 218, eine temporäre Registerzuordnungsfunktion 220 und eine (ii) Ausgabewarteschlange 222 enthält. Der Zuordnungsfunktions-Cluster 215 verfolgt die den logischen Registern verschiedener Anweisungen zugewiesenen physischen Register. In einer beispielhaften Ausführungsform verfügt die Zuordnungsfunktion für architekturdefinierte Register 216 über 16 logische (d. h. nicht physisch zugeordnete) Register jedes Typs, welche den letzten gültigen (d. h. mit Prüfpunkt versehenen) Zustand der logisch-zu-physischen Registerzuordnungsfunktionsdaten speichern. Jedoch sollte man erkennen, dass verschiedene Prozessorarchitekturen mehr oder weniger logische Register haben können, wie in der beispielhaften Ausführungsform beschrieben. Die Zuordnungsfunktion für architekturdefinierte Register 216 enthält eine Zeigerliste, die ein physisches Register identifiziert, welches den mit Prüfpunkt versehenen Zustand beschreibt. Die Physische-Register-Dateien 232a bis 232n enthalten üblicherweise mehr Register als die Anzahl von Einträgen in der Zuordnungsfunktion für architekturdefinierte Register 216. Es ist zu beachten, dass die spezielle Anzahl von physischen und logischen Registern, die in einem Umbenennungszuordnungsschema verwendet werden, schwanken kann.

-

Im Gegensatz dazu ist die vereinheitlichte Hauptzuordnungsfunktion 218 üblicherweise größer (sie enthält üblicherweise bis zu 20 Einträge) als die Zuordnungsfunktion für architekturdefinierte Register 216. Die vereinheitlichte Hauptzuordnungsfunktion 218 erleichtert das Verfolgen des transienten Zustands von logisch-zu-physischen Registerzuordnungen. Der Begriff ”transient” bezieht sich auf die Tatsache, dass die vereinheitlichte Hauptzuordnungsfunktion 218 versuchsweise logisch-zu-physische Registerzuordnungsdaten verfolgt, während die Anweisungen unter Missachtung der Reihenfolge (”out-of-order”) ausgeführt werden. Zu OoO-Ausführung kommt es üblicherweise, wenn in der Pipeline ältere Anweisungen vorliegen, die länger für die Ausführung brauchen (d. h. mehr Taktzyklen benötigen) würden als neuere Anweisungen. Jedoch wenn das Ergebnis nach dem Ausführen einer OoO-Anweisung erfordern sollte, dass es aus einem bestimmten Grund (z. B. wegen einer falschen Verzweigungsvorhersage) gelöscht wird, kann der Prozessor in den durch die Zuordnungsfunktion für architekturdefinierte Register 216 bewahrten, mit Prüfpunkt versehenen Zustand zurückkehren und die Ausführung ab dem letzten gültigen Zustand wiederaufnehmen.

-

Die vereinheitlichte Hauptzuordnungsfunktion 218 nimmt die Verknüpfung zwischen den physischen Registern in den Physische-Register-Dateien 232a bis 232n und der Zuordnungsfunktion für architekturdefinierte Register 216 vor. Der qualifizierende Begriff ”vereinheitlicht” bezieht sich auf die Tatsache, dass die vereinheitlichte Hauptzuordnungsfunktion 218 die Komplexität des Erstellens einer dedizierten Zuordnungsfunktion nach Kundenwünschen für jede der Registerdateien 232 (z. B. Allgemeinregister (GPRs – general-purpose registers), Gleitkommaregister (FPRs – floating-point registers), Festkommaregister (FXPs – fixed-point registers), Ausnahmebedingungsregister (XERs – exception registers), Bedingungsregister (CRs – condition registers) usw.) erübrigt.

-

Neben dem Erstellen eines transienten logisch-zu-physischen Registerzuordnungsfunktions-Eintrags einer OoO-Anweisung verfolgt die vereinheitlichte Hauptzuordnungsfunktion 218 auch Abhängigkeitsdaten (d. h. Anweisungen, die von der Beendigung einer älteren Anweisung in der Pipeline abhängig sind), was für das Ordnen der Anweisungen wichtig ist. Herkömmlicherweise reiht sich die Anweisung in die Ausgabewarteschlange 222 ein, sobald die vereinheitlichte Hauptzuordnungsfunktion 218 in die logisch-zu-physische Registerumsetzung einer Anweisung eingetreten ist. Die Ausgabewarteschlange 222 dient als Gatekeeper, bevor die Anweisung zur Ausführung an die Ausführungseinheit 230 ausgegeben wird. Meistens kann eine Anweisung die Ausgabewarteschlange 222 nicht verlassen, wenn sie davon abhängig ist, dass eine ältere Anweisung beendet wird. Aus diesem Grund verfolgt die vereinheitlichte Hauptzuordnungsfunktion 218 Abhängigkeitsdaten durch Speichern der Ausgabewarteschlangen-Positionsdaten für jede Anweisung, die zugeordnet wird. Nachdem die Anweisung durch die Steuerkomponente für die allgemeine Ausführung 224 ausgeführt wurde, wird die Anweisung für ”beendet” erklärt und aus der Ausgabewarteschlange 222 zurückgezogen.

-

Die Registerverwaltungseinheit 214 kann in einem einzigen Zyklus mehrere Anweisungen von der Abfertigungseinheit 212 empfangen, um eine gefüllte Einzelausgabe-Pipeline aufrechtzuerhalten. Das Abfertigen von Anweisungen wird durch die Anzahl verfügbarer Einträge in der vereinheitlichten Hauptzuordnungsfunktion 218 begrenzt. In herkömmlichen Zuordnungssystemen, welchen die temporäre Registerzuordnungsfunktion 220 fehlt, gibt es, wenn die vereinheitlichte Hauptzuordnungsfunktion 218 insgesamt 20 Zuordnungsfunktions-Einträge aufweist, ein Maximum von 20 Anweisungen, die sofort in Ausführung befindlich (d. h. prüfpunktlos) sein können. Demgemäß kann die Abfertigungseinheit 212 eines herkömmlichen Zuordnungssystems denkbar mehr Anweisungen ”abfertigen” als die Anzahl, welche tatsächlich aus der vereinheitlichten Hauptzuordnungsfunktion 218 zurückgezogen werden kann. Die Ursache dieses Engpasses bei der vereinheitlichten Hauptzuordnungsfunktion 218 ist die Tatsache, dass der Zuordnungsfunktions-Eintrag einer Anweisung herkömmlicherweise nicht aus der vereinheitlichten Hauptzuordnungsfunktion 218 zurückgezogen werden konnte, bis die Anweisung ”abgeschlossen” wurde (d. h. alle älteren Anweisungen die Ausführung ”beendet” haben).

-

Gemäß einer Ausführungsform dient die temporäre Registerzuordnungsfunktion 220 als ein nicht zeitkritisches Register, für welches eine ”beendete”, aber ”nicht abgeschlossene” Anweisung vor dem letztendlichen Abschluss der Anweisung aus der vereinheitlichten Hauptzuordnungsfunktion 218 zurückgezogen (d. h. aus der vereinheitlichten Hauptzuordnungsfunktion 218 entfernt) werden könnte. Sobald die Anweisung ”abgeschlossen” wird, benachrichtigt die Abschlusseinheit 240 die temporäre Registerzuordnungsfunktion 220 über den Abschluss. Der Zuordnungsfunktions-Eintrag in der temporären Registerzuordnungsfunktion 220 kann dann den architekturdefinierten kohärenten Zustand der Zuordnungsfunktion für architekturdefinierte Register 216 durch Ersetzen des entsprechenden Eintrags, der jetzt in der Zuordnungsfunktion für architekturdefinierte Register 216 gespeichert war, aktualisieren.

-

Wenn die Abfertigungseinheit 212 eine Anweisung abfertigt, vergleicht die Registerverwaltungseinheit 214 die zu der Anweisung gehörige(n) Nummer(n) logischer Register mit den Zuordnungen in der Zuordnungsfunktion für architekturdefinierte Register 216, der vereinheitlichten Hauptzuordnungsfunktion 218 und der temporären Registerzuordnungsfunktion 220, um zu ermitteln, ob eine Übereinstimmung (gewöhnlich als ”Treffer” bezeichnet) in der Zuordnungsfunktion für architekturdefinierte Register 216, der vereinheitlichten Hauptzuordnungsfunktion 218 und/oder der temporären Registerzuordnungsfunktion 220 vorliegt. Diese Auswertung wird als eine Suche in den logischen Registern bezeichnet. Wenn die Suche gleichzeitig bei mehr als einer Registerzuordnungsfunktion (d. h. der Zuordnungsfunktion für architekturdefinierte Register 216, der vereinheitlichten Hauptzuordnungsfunktion 218 und/oder der temporären Registerzuordnungsfunktion 220) erfolgt, wird die Suche als eine parallele Suche in den logischen Registern bezeichnet.

-

Jede Anweisung, die den Wert eines bestimmten logischen Zielregisters aktualisiert, wird einem neuen physischen Register zugeordnet. Jedes Mal, wenn diese neue Ausprägung des logischen Registers von einer anderen Anweisung als eine Quelle verwendet wird, muss dasselbe physische Register verwendet werden. Da es eine Vielzahl von Ausprägungen eine logischen Registers geben kann, kann es auch eine Vielzahl von dem logischen Register entsprechenden physischen Registern geben. Die Registerverwaltungseinheit 214 führt die Tasks des (i) Analysierens, welches physische Register einem durch eine bestimmte Anweisung verwendeten logischen Register entspricht, des (ii) Ersetzens des Verweises auf das logische Register durch einen Verweis auf das entsprechende physische Register (d. h. Registerumbenennung) und des (iii) Zuordnens eines neuen physischen Registers jedes Mal, wenn eine neue Ausprägung irgendeines logischen Registers erstellt wird (d. h. Zuordnung des physischen Registers), aus.

-

Anfangs, bevor Anweisungen abgefertigt werden, empfängt die vereinheitlichte Hauptzuordnungsfunktion 218 keinen Treffer/keine Übereinstimmung, da es keine gerade in Ausführung befindlichen Anweisungen gibt. In einem solchen Fall erstellt die vereinheitlichte Hauptzuordnungsfunktion 218 einen Zuordnungseintrag. Da nachfolgende Anweisungen abgefertigt werden, wenn eine Übereinstimmung mit einem logischen Register für dieselbe Nummer eines logischen Registers sowohl in der Zuordnungsfunktion für architekturdefinierte Register 216 als auch in der vereinheitlichten Hauptzuordnungsfunktion 218 gefunden wird, erhält das Auswählen der logisch-zu-physischen Registerzuordnung der vereinheitlichten Hauptzuordnungsfunktion 218 Priorität, da die Möglichkeit besteht, dass es Anweisungen gibt, die gerade unter Missachtung der Reihenfolge ausgeführt werden (d. h., dass die Zuordnung in einem transienten Zustand ist).

-

Nachdem die vereinheitlichte Hauptzuordnungsfunktion 218 einen Treffer/eine Übereinstimmung in ihrer Zuordnungsfunktion gefunden hat, reiht sich die Anweisung in die Ausgabewarteschlange 222 ein, um auf die Ausgabe zur Ausführung durch eine der Ausführungseinheiten 230 zu warten. Nachdem die Steuerkomponente für die allgemeine Ausführung 224 die Anweisung ausgeführt und ”beendet” hat, aber bevor die Anweisung ”abgeschlossen” wird, zieht die Registerverwaltungseinheit 214 den in der vereinheitlichten Hauptzuordnungsfunktion 218 jetzt gefundenen Zuordnungseintrag aus der vereinheitlichten Hauptzuordnungsfunktion 218 zurück und verschiebt sie den Zuordnungseintrag zur temporären Registerzuordnungsfunktion 220. Daraufhin wird ein Zeitfenster in der vereinheitlichten Hauptzuordnungsfunktion 218 verfügbar gemacht, um eine anschließend abgefertigte Anweisung zuzuordnen. Im Gegensatz zur vereinheitlichten Hauptzuordnungsfunktion 218 speichert die temporäre Registerzuordnungsfunktion 220 keine Abhängigkeitsdaten. Somit hängt die Zuordnung, die zur temporären Registerzuordnungsfunktion 220 übertragen wird, nicht von den Warteschlangenpositionen der mit ihren Quellenzuordnungen verknüpften Anweisungen ab (und verfolgt sie diese nicht). Dies ist so, weil die Ausgabewarteschlange 222 die ”beendete, aber nicht abgeschlossene” Anweisung nach einer erfolgreichen Ausführung zurückzieht. Im Gegensatz dazu speichert eine vereinheitlichte Hauptzuordnungsfunktion bei herkömmlichen Umbenennungszuordnungsschemas, welchen eine temporäre Registerzuordnungsfunktion fehlt, weiter den Quellenumbenennungs-Eintrag, bis die Anweisung abgeschlossen wird. Bei der vorliegenden Ausführungsform kann die temporäre Registerzuordnungsfunktion 220 weiter weg von anderen kritischen Pfadelementen angeordnet werden, weil die Ausführung der vereinheitlichten Hauptzuordnungsfunktion 218 nicht zeitkritisch ist.

-

Sobald die vereinheitlichte Hauptzuordnungsfunktion 218 einen Zuordnungseintrag aus der vereinheitlichten Hauptzuordnungsfunktion 218 zurückzieht und zur temporären Registerzuordnungsfunktion 220 verschiebt, führt der Zuordnungsfunktions-Cluster 215 an einer anschließend abgefertigten Anweisung eine parallele Suche in den logischen Registern durch, um zu ermitteln, ob die nachfolgende Anweisung einen Treffer/eine Übereinstimmung in der Zuordnungsfunktion für architekturdefinierte Register 216, der vereinheitlichten Hauptzuordnungsfunktion 218 und/oder der temporären Registerzuordnungsfunktion 220 enthält. Wenn in mindestens zwei Zuordnungsfunktionen aus der Gruppe der Zuordnungsfunktion für architekturdefinierte Register 216, der vereinheitlichten Hauptzuordnungsfunktion 218 und der temporären Registerzuordnungsfunktion 220 ein Treffer bei/eine Übereinstimmung mit derselben Nummer eines logischen Zielregisters gefunden wird, verleiht der Multiplexer 223 in Ausgabewarteschlange 222 durch Auswählen der logisch-zu-physischen Registerzuordnung der vereinheitlichten Hauptzuordnungsfunktion 218 Priorität vor derjenigen der temporären Registerzuordnungsfunktion 220, welche wiederum Auswahlpriorität vor der Zuordnungsfunktion für architekturdefinierte Register 216 genießt.

-

Der von Barrick vorgeschlagene Mechanismus, durch welchen die Auswahlpriorität ermittelt wird, wird nachfolgend erörtert. Ein logischer Übersichts-Ablaufplan eines beispielhaften Verfahrens zur Ermittlung, welche Zuordnungsdatenwerte beim Ausführen einer Anweisung zu verwenden sind, gemäß einer Ausführungsform. In einer Ausführungsform fertigt eine Abfertigungseinheit 212 eine oder mehrere Anweisungen an eine Registerverwaltungseinheit 214 ab. In Reaktion auf die Abfertigung der Anweisung(en) ermittelt die Registerverwaltungseinheit 214 durch eine parallele Suche in den logischen Registern, ob ein ”Treffer” bei einem zu jeder abgefertigten Anweisung gehörigen logischen Register (zusätzlich zu einem ”Treffer” bei einer Zuordnungsfunktion für architekturdefinierte Register 216) aufgetreten ist. In dieser Hinsicht versteht es sich von selbst, dass vorausgesetzt wird, dass die Zuordnungsfunktion für architekturdefinierte Register 216 immer einen Treffer/eine Übereinstimmung hat, da die Zuordnungsfunktion für architekturdefinierte Register 216 den mit Prüfpunkt versehenen Zustand der logisch-zu-physischen Registerzuordnungsfunktionsdaten speichert. Wenn die Registerverwaltungseinheit 214 keine Übereinstimmung/keinen Treffer in einer vereinheitlichten Hauptzuordnungsfunktion 218 und/oder einer temporären Registerzuordnungsfunktion 220 erkennt, wählt ein Multiplexer 223 die logisch-zu-physischen Registerumbenennungsdaten aus der Zuordnungsfunktion für architekturdefinierte Register 216 aus. Wenn die Registerverwaltungseinheit 214 eine Übereinstimmung/einen Treffer in der vereinheitlichten Hauptzuordnungsfunktion 218 und/oder der temporären Registerzuordnungsfunktion 220 erkennt, ermittelt die Registerverwaltungseinheit 214 in einem Entscheidungsblock, ob sowohl in der vereinheitlichten Hauptzuordnungsfunktion 218 als auch in der temporären Registerzuordnungsfunktion 220 eine Übereinstimmung/ein Treffer auftritt. Wenn in beiden Zuordnungsfunktionen 218 und 220 ein Treffer/eine Übereinstimmung festgestellt wird, ermittelt die Registerverwaltungseinheit 214, ob der Zuordnungseintrag in der vereinheitlichten Hauptzuordnungsfunktion 218 ”jünger” als der Zuordnungseintrag in der temporären Registerzuordnungsfunktion 220 ist (d. h., ob die Erstellung des Zuordnungseintrags kürzer zurückliegt). Wenn der Eintrag in der vereinheitlichten Hauptzuordnungsfunktion 218 jünger als der Eintrag in der temporären Registerzuordnungsfunktion 220 ist, wählt der Multiplexer 223 die logisch-zu-physischen Registerumbenennungsdaten aus der vereinheitlichten Hauptzuordnungsfunktion 218 aus. Wenn der Eintrag in der vereinheitlichten Hauptzuordnungsfunktion 218 nicht jünger als der Eintrag in der temporären Registerzuordnungsfunktion 220 ist, wählt der Multiplexer 223 die logisch-zu-physischen Registerumbenennungsdaten aus der temporären Registerzuordnungsfunktion 220 aus.

-

Wenn weder in der vereinheitlichten Hauptzuordnungsfunktion 218 noch in der temporären Registerzuordnungsfunktion 220 eine Übereinstimmung/ein Treffer auftritt, wird ermittelt, ob in der vereinheitlichten Hauptzuordnungsfunktion 218 ein ausschließlicher Treffer/eine ausschließliche Übereinstimmung auftritt. Wenn ein ausschließlicher Treffer bei der vereinheitlichten Hauptzuordnungsfunktion 218 auftritt, wählt der Multiplexer 223 die logisch-zu-physischen Registerumbenennungsdaten aus der vereinheitlichten Hauptzuordnungsfunktion 218 aus. Jedoch wenn kein Treffer/keine Übereinstimmung bei der vereinheitlichten Hauptzuordnungsfunktion 218 auftritt (und somit der Treffer/die Übereinstimmung ausschließlich bei der temporären Registerzuordnungsfunktion 220 auftritt), wählt der Multiplexer 223 die logisch-zu-physischen Registerumbenennungsdaten aus der temporären Registerzuordnungsfunktion 220 (Block 320) aus. Eine Steuerkomponente für die allgemeine Ausführung 224 verwendet die Ausgabedaten der Suche in den logischen Registern zur Ausführung.

-

In einer beispielhaften Ausführungsform fertigt eine Abfertigungseinheit 212 eine oder mehrere Anweisungen an die Registerverwaltungseinheit 214 ab. Eine vereinheitlichte Hauptzuordnungsfunktion erstellt einen neuen Eintrag der logisch-zu-physischen Registerzuordnung. Eine Ausgabewarteschlange 222 bewahrt die Ausgabewarteschlangen-Positionsdaten der abgefertigten Anweisung, welche den Zuordnungseintrag verwendet, der über die Suche in den logischen Registern (in 3 beschrieben) ausgewählt wird. Eine Steuerkomponente für die allgemeine Ausführung 224 erkennt, ob eine der in Ausführung befindlichen Anweisungen beendet wurde (d. h. ob eine der Einheiten 130 die Ausführung einer Anweisung beendet hat). Wenn die ausgegebene Anweisung nicht beendet wurde, wartet das Verfahren darauf, dass eine Anweisung beendet wird. In Reaktion auf das Erkennen durch die Steuerkomponente für die allgemeine Ausführung 224, dass eine Anweisung beendet ist, verschiebt die vereinheitlichte Hauptzuordnungsfunktion 218 die logisch-zu-physischen Registerumbenennungsdaten von der vereinheitlichten Hauptzuordnungsfunktion 218 zur temporären Registerzuordnungsfunktion 220. Die vereinheitlichte Hauptzuordnungsfunktion 218 zieht den zur beendeten Anweisung gehörigen Eintrag der vereinheitlichten Hauptzuordnung zurück. Eine Abschlusseinheit 240 ermittelt, ob die beendete Anweisung abgeschlossen ist. Wenn die beendete Anweisung nicht abgeschlossen ist, wartet die Abschlusseinheit 240 weiter, bis sie erkennt, dass die allgemeine Ausführungseinheit 224 alle älteren Anweisungen beendet hat. Jedoch wenn die Abschlusseinheit 240 erkennt, dass die beendete Anweisung abgeschlossen ist, aktualisiert die temporäre Registerzuordnungsfunktion 220 den architekturdefinierten kohärenten Zustand der Zuordnungsfunktion für architekturdefinierte Register 216 und zieht die temporäre Registerzuordnungsfunktion 220 ihren Zuordnungseintrag zurück.

-

US-Patentschrift Nr. 6 189 088 ”Forwarding stored data fetched for out-of-order load/read operation to over-taken operation read-accessing same memory location” von Gschwind, erteilt am 13. Februar 2001 und durch Verweis hierin einbezogen, beschreibt einen beispielhaften ”Out-of-Order”-(OoO-)Prozessor.

-

Bei Gschwind ist 3 ein funktionales Blockschaltbild eines herkömmlichen Computer-Verarbeitungssystems (das z. B. einen superskalaren Prozessor enthält), welches dynamisches Umordnen von Speicheroperationen und hardwaregestützte Implementierungen der Kollisionsprüfungs- und Datenumgehungssequenz unterstützt. Das heißt, das System in 3 enthält die zur Unterstützung des Umordnens von Anweisungen mittels der oben aufgeführten Mechanismen erforderlichen Hardware-Ressourcen, aber es enthält nicht die zur Unterstützung der Ausführung von „Out-of-Order”-Ladeoperationen vor reihenfolgegemäßen Ladeoperationen erforderlichen Hardware-Ressourcen. Das System besteht aus: einem Speicher-Teilsystem 301; einem Daten-Cachespeicher 302; einem Anweisungs-Cachespeicher 304; und einer Prozessoreinheit 300. Die Prozessoreinheit 300 enthält: eine Anweisungswarteschlange 303; mehrere Speichereinheiten (MUs – memory units) 305 zum Durchführen von Lade- und Speicheroperationen; mehrere Funktionseinheiten (FUs – functional units) 307 zum Durchführen von Ganzzahl-, logischen und Gleitkommaoperationen; eine Verzweigungseinheit (BU – branch unit) 309; eine Registerdatei 311; eine Registerzuordnungstabelle 320; eine Warteschlange für freie Register 322; eine Abfertigungstabelle 324; eine Zurückziehungs-Warteschlange 326; und eine reihenfolgegemäße Zuordnungstabelle 328.

-

Im in 3 veranschaulichten Prozessor werden Anweisungen aus dem Anweisungs-Cachespeicher 304 (oder aus dem Speicher-Teilsystem 301, wenn die Anweisungen sich nicht im Anweisungs-Cachespeicher 304 befinden) unter der Steuerung von Verzweigungseinheit 309 abgerufen, in die Anweisungswarteschlange 303 gestellt und anschließend aus der Anweisungswarteschlange 303 abgefertigt. Die von den Anweisungen zur Angabe von Operanden verwendeten Registernamen werden entsprechend dem Inhalt der Registerzuordnungstabelle 320 umbenannt, welche die aktuelle Zuordnung von Namen architekturdefinierter Register zu physischen Registern angibt. Die von den Anweisungen zur Angabe der Ziele für die Ergebnisse verwendeten Namen der architekturdefinierten Register werden aus der Warteschlange für freie Register 322, welche die Namen von physischen Registern enthält, die der Prozessor gerade nicht verwendet, entnommenen physischen Registern zugewiesen. Die Registerzuordnungstabelle 320 wird mit den durch die Anweisungen angegebenen Zuweisungen physischer Register zu den Namen der architekturdefinierten Zielregister aktualisiert. Anweisungen mit allen ihren umbenannten Registern werden in die Abfertigungstabelle 324 gestellt. Anweisungen werden außerdem einschließlich ihrer Adressen und der Namen ihrer physischen und architekturdefinierten Register in Programmreihenfolge in die Zurückziehungs-Warteschlange 326 gestellt. Anweisungen werden aus der Abfertigungstabelle 324 abgefertigt, wenn alle durch solche Anweisungen zu verwendenden Ressourcen verfügbar sind (physische Register wurden den erwarteten Operanden zugewiesen, und Funktionseinheiten sind frei). Die von der Anweisung verwendeten Operanden werden aus der Registerdatei 311 gelesen, welche üblicherweise Allgemeinregister (GPRs), Gleitkommaregister (FPRs) und Bedingungsregister (CRs) enthält. Anweisungen werden, möglicherweise unter Missachtung der Reihenfolge, in einer entsprechenden Speichereinheit 305, Funktionseinheit 307 oder Verzweigungseinheit 309 ausgeführt. Bei Abschluss der Ausführung werden die Ergebnisse aus den Anweisungen in die Registerdatei 311 gestellt. Anweisungen in der Abfertigungstabelle 324, die darauf warten, dass die physischen Register durch die ihre Ausführung abschließenden Anweisungen gesetzt werden, werden benachrichtigt. Die Zurückziehungs-Warteschlange 326 wird über die ihre Ausführung abschließenden Anweisungen sowie darüber, ob sie irgendwelche Ausnahmebedingungen ausgelöst haben, benachrichtigt. Abgeschlossene Anweisungen werden in Programmreihenfolge (ab dem Anfang der Warteschlange) aus der Zurückziehungs-Warteschlange 326 entfernt. Zum Zeitpunkt des Zurückziehens wird, wenn keine Ausnahmebedingungen durch eine Anweisung ausgelöst wurden, die reihenfolgegemäße Zuordnungstabelle 328 aktualisiert, so dass die Namen architekturdefinierter Register auf die physischen Register in Registerdatei 311, welche die Ergebnisse aus der zurückgezogen werdenden Anweisung enthalten, verweisen; die früheren Registernamen aus der reihenfolgegemäßen Zuordnungstabelle 328 werden in die Warteschlange für freie Register 322 zurückgegeben.

-

Andererseits wird, wenn eine Anweisung eine Ausnahmebedingung ausgelöst hat, die Programmsteuerung auf die Adresse der Anweisung gesetzt, die gerade aus der Zurückziehungs-Warteschlange 326 zurückgezogen wird. Ferner wird die Zurückziehungs-Warteschlange 326 gelöscht, wodurch alle nicht zurückgezogenen Anweisungen abgebrochen werden. Ferner wird die Registerzuordnungstabelle 320 auf den Inhalt der reihenfolgegemäßen Zuordnungstabelle 328 gesetzt und wird jedes nicht in der reihenfolgegemäßen Zuordnungstabelle 328 enthaltene Register zur Warteschlange für freie Register 322 hinzugefügt.

-

Ein herkömmlicher superskalarer Prozessor, welcher das Umordnen von Ladeanweisungen bezüglich vorausgehender Ladeanweisungen unterstützt (wie in 3 gezeigt), kann um Folgendes erweitert werden:

- 1. einen Mechanismus zum Kennzeichnen von Ladeanweisungen, welche bezüglich vorausgehender Ladeanweisungen unter Missachtung der Reihenfolge ausgegeben werden;

- 2. einen Mechanismus zum Nummerieren von Anweisungen, wie sie abgerufen werden, und zum Feststellen, ob eine Anweisung im Anweisungsstrom früher oder später auftrat. Stattdessen kann ein alternativer Mechanismus verwendet werden, um zu ermitteln, ob eine Anweisung bezüglich einer anderen Anweisung früher oder später auftrat;

- 3. einen Mechanismus zum Speichern von Informationen über Ladeoperationen, welche unter Missachtung der Reihenfolge ausgeführt wurden, einschließlich ihrer Adresse in der Programmreihenfolge, der Adresse ihres Zugriffs und des für die größte garantierte, das geladene Datenelement enthaltende atomare Einheit gelesenen Datenwerts;

- 4. einen Mechanismus zum Durchführen einer Kollisionsprüfung, wenn eine Ladeanweisung bezüglich einer oder mehrerer „Out-of-Order”-Ladeanweisungen reihenfolgegemäß ausgeführt wird, und zum Durchführen von Prioritätscodierung, wenn mehrere Anweisungen mit einer Ladeoperation kollidieren;

- 5. einen Mechanismus zum Umgehen des mit einer kollidierenden Ladeoperation verknüpften Datenelements; und

- 6. einen Mechanismus zum Löschen des in Schritt (3) erzeugten Datensatzes an der Stelle, wo der ”Out-of-Order”-Zustand in Programmreihenfolge aus der Zurückziehungs-Warteschlange 326 in die Registerdatei 311 zurückgezogen wird.

-

Die durch Gschwind offenbarten Mechanismen werden zusammen mit den im herkömmlichen, in 3 dargestellten ”Out-of-Order”-Prozessor verfügbaren Mechanismen verwendet wie folgt. Jede Anweisung wird mit einer Anweisungsnummer nummeriert, wenn sie in die Anweisungswarteschlange 303 kommt. Eine Ladeanweisung kann früher aus Abfertigungstabelle 324 abgefertigt werden als eine vorausgehende Ladeanweisung. Eine solche Ladeanweisung wird im Folgenden als eine ”Out-of-Order”-Ladeoperation bezeichnet. In einem solchen Fall wird der der Ladeanweisung entsprechende Eintrag in der Zurückziehungs-Warteschlange 326 als ein ”Out-of-Order”-Ladevorgang gekennzeichnet.

-

Das Erkennen der Abfertigung einer ”Out-of-Order”-Ladeoperation aus einer Abfertigungstabelle 324 an eine Speichereinheit 305 zur Ausführung erfolgt vorzugsweise mit zwei Zählern, einem Zähler ”Abgerufene Ladevorgänge” und einem Zähler ”Abgefertigte Ladevorgänge”. Der Zähler ”Abgerufene Ladevorgänge” wird hochgezählt, wenn ein Ladeoperation zur Abfertigungstabelle 324 hinzugefügt wird. Der Zähler ”Abgefertigte Ladevorgänge” wird hochgezählt, wenn eine Ladeoperation zur Ausführung an eine Speichereinheit 305 gesendet wird. Der aktuelle Inhalt des Zählers ”Abgerufene Ladevorgänge” wird an eine Ladeanweisung angehängt, wenn die Ladeanweisung zur Abfertigungstabelle 324 hinzugefügt wird. Wenn die Ladeanweisung zur Ausführung aus der Abfertigungstabelle 324 an eine Speichereinheit 305 abgefertigt wird, wird die Ladeanweisung als eine ”Out-of-Order”-Ladeoperation identifiziert, falls der an die Ladeanweisung in der Abfertigungstabelle 324 angehängte Wert zu diesem Zeitpunkt vom Inhalt des Zählers ”Abgefertigte Ladevorgänge” verschieden ist. Es ist zu beachten, dass die Differenz zwischen den beiden Zählerwerten der genauen Anzahl von Ladeoperationen entspricht, je nachdem, welche Ladeanweisung unter Missachtung der Reihenfolge (”out of order”) ausgegeben wird. ”Out-of-Order”-Ladeanweisungen werden nur dann an eine Speichereinheit 305 abgefertigt, wenn in der Ladereihenfolgetabelle Platz für das Hinzufügen von Einträgen verfügbar ist.

-

Die Ladereihenfolgetabelle ist eine einzelne Tabelle, auf welche alle Speichereinheiten 305 gleichzeitig zugreifen (d. h. es wird nur eine einzige logische Kopie aufrechterhalten, obwohl mehrere physische Kopien aufrechterhalten werden können, um die Verarbeitung zu beschleunigen). Es ist zu beachten, dass bei Verwendung mehrerer physischer Kopien der logische Inhalt der mehreren Kopien für alle Speichereinheiten 305 immer denselben Zustand widerspiegeln muss.

-

Die Anweisungsnummer der in Ausführung befindlichen Anweisung und die Tatsache, ob eine Anweisung spekulativ ausgeführt wird, werden der Speichereinheit 305 für jede ausgegebene Ladeoperation mitgeteilt.

-

Eine durch einen Prozessor implementierte Anweisungssatz-Architektur (ISA) definiert üblicherweise eine feste Anzahl von architekturdefinierten Allgemeinregistern, die zugänglich sind, auf Grundlage von Registerfeldern von Anweisungen der ISA. In Prozessoren für ”Out-of-Order”-Ausführung werden Umbenennungsregister zugewiesen, um Registerergebnisse spekulativ ausgeführter Anweisungen darin unterzubringen. Der Wert des Umbenennungsregisters wird als ein Wert eines architekturdefinierten Registers übergeben, wenn die entsprechende spekulative Anweisungsausführung ”übergeben” oder ”abgeschlossen” ist. Folglich gibt es in einer Registerumbenennungs-Ausführungsform zu jedem Zeitpunkt und wie es von einem im Prozessor ausgeführt werdenden Programm wahrgenommen wird, viel mehr Umbenennungsregister als architekturdefinierte Register.

-

In einer Ausführungsform von Umbenennungsregistern werden architekturdefinierten Registern und Umbenennungsregistern separate Register zugewiesen. In einer weiteren Ausführungsform sind Umbenennungsregister und architekturdefinierte Register zusammengeführte Register. Die zusammengeführten Register enthalten eine Markierung (Tag) zum Anzeigen des Zustands des zusammengeführten Registers, wobei in einem Zustand das zusammengeführte Register ein Umbenennungsregister ist und in einem anderen Zustand das zusammengeführte Register ein architekturdefiniertes Register ist.

-

In einer Ausführungsform mit zusammengeführten Registern werden die ersten n physischen Register als Teil der Initialisierung (zum Beispiel während eines Kontextwechsels oder beim Initialisieren einer Partition) als die architekturdefinierten Register zugewiesen, wobei n die Anzahl der durch die Anweisungssatz-Architektur (ISA) vereinbarten Register ist. Diese Register werden auf den Zustand ”architekturdefiniertes Register” (AR) gesetzt; die übrigen physischen Register nehmen den Zustand ”verfügbar” an. Wenn eine ausgegebene Anweisung ein Zielregister enthält, wird ein neuer Umbenennungspuffer benötigt. Aus diesem Grund wird ein physisches Register aus dem Pool der verfügbaren Register ausgewählt und dem Zielregister zugeordnet. Demgemäß wird der ausgewählte Registerzustand auf den Zustand ”Umbenennungspuffer nicht gültig” (NV – not valid) gesetzt und wird sein Gültig-Bit zurückgesetzt. Nachdem die verknüpfte Anweisung die Ausführung beendet hat, wird das erzeugte Ergebnis in das ausgewählte Register geschrieben, wird sein Gültig-Bit gesetzt und wechselt sein Zustand zu ”Umbenennungspuffer (RB – rename buffer) gültig”. Später, wenn die verknüpfte Anweisung abgeschlossen wird, wird der zugeordnete Umbenennungspuffer zu dem architekturdefinierten Register erklärt, welches das in der gerade abgeschlossenen Anweisung angegebene Zielregister implementiert. Sein Zustand wechselt dann zum Zustand eines architekturdefinierten Registers (AR), um dies widerzuspiegeln.

-

Während Register hinsichtlich der Leistungsfähigkeit fast eine Universallösung sind, haben sie einen Nachteil. Verschiedene Teile eines Computerprogramms verwenden allesamt ihre eigenen temporären Werte und konkurrieren daher um die Verwendung der Register. Da es sehr schwierig ist, die Art und Weise des Programmablaufs während der Laufzeit richtig zu verstehen, gibt es für den Entwickler keinen einfachen Weg, im Voraus zu wissen, wie viele Register er verwenden und wie viele Register er für andere Teile des Programms beiseite lassen sollte. Im Allgemeinen werden derartige Überlegungen nicht berücksichtigt, und die Entwickler und wahrscheinlicher noch die von diesen verwendeten Compiler versuchen, alle für sie sichtbaren Register zu verwenden. Im Fall von Prozessoren mit zu Anfang sehr wenigen Registern ist dies auch die einzige vernünftige Vorgehensweise.

-

Registerfenster zielen darauf ab, dieses Problem zu lösen. Da jeder Teil eines Programms Register zum eigenen Gebrauch benötigt, werden mehrere Sätze von Registern für die verschiedenen Teile des Programms bereitgestellt. Wenn diese Register sichtbar wären, gäbe es mehr Register, um welche konkurriert würde, d. h. sie müssen unsichtbar gemacht werden.

-

Das Unsichtbarmachen der Register lässt sich effizient implementieren; die CPU erkennt die Verschiebung von einem Teil des Programms zu einem anderen während eines Prozeduraufrufs. Es wird durch eine aus einer kleinen Anzahl von Anweisungen ausgeführt (Prolog) und endet mit einer aus einem entsprechend kleinen Satz (Epilog). Beim Berkeley-Aufbau würden diese Aufrufe bei Beendigen des Aufrufs an dieser Stelle einen neuen Satz von Registern ”einlagern” oder als ”inaktiv” (oder ”wiederverwendbar”) kennzeichnen lassen.

-

Prozessoren wie PowerPC sichern den Zustand in vordefinierten und reservierten Maschinenregistern. Wenn eine Ausnahmebedingung eintritt, während der Prozessor bereits den Inhalt des aktuellen Fensters verwendet, um eine weitere Ausnahmebedingung zu verarbeiten, erzeugt der Prozessor in genau dieser Situation einen doppelten Fehler.

-

In einer beispielhaften RISC-Ausführungsform sind nur acht von insgesamt 64 Registern für die Programme sichtbar. Der vollständige Satz von Registern ist als Registerdatei und jeder einzelne Satz von acht Registern ist als Fenster bekannt. Die Datei ermöglicht, dass bis zu acht Prozeduraufrufe über eigene Registersätze verfügen. Solange das Programm nicht Ketten abruft, die länger als acht Aufrufe tief sind, muss den Registern nie gestattet werden, überzulaufen, d. h. außerhalb im Hauptspeicher oder Cachespeicher gesichert zu werden, was im Vergleich zum Registerzugriff ein langsamer Prozess ist. Für viele Programme ist eine Kette von sechs so tief, wie das Programm reicht.

-

Vergleichsweise bietet eine andere Architektur gleichzeitige Sicht in vier Sätze von jeweils acht Registern. Drei Sätze von jeweils acht Registern werden ”gefenstert”. Acht Register (i0 bis i7) bilden die Eingaberegister für die aktuelle Prozedurebene.

-

Acht Register (L0 bis L7) sind für die aktuelle Prozedurebene lokal, und acht Register (o0 bis o7) sind die Ausgaben aus der aktuellen Prozedurebene an die nächste aufgerufene Ebene. Bei Aufruf einer Prozedur verschiebt sich das Registerfenster um sechzehn Register, wodurch die alten Eingaberegister und die alten lokalen Register verborgen werden und die alten Ausgaberegister zu den neuen Eingaberegistern gemacht werden. Die gemeinsamen Register (alte Ausgaberegister und neue Eingaberegister) werden zur Parameterübergabe verwendet. Schließlich sind acht Register (g0 bis g7) für alle Prozedurebenen global sichtbar.

-

Bei einem verbesserten Aufbau können die Fenster ihre Größe verändern, was im gewöhnlichen Fall, wo weniger als acht Register für einen Aufruf benötigt werden, die Verwendung unterstützt. Außerdem werden dabei die Register in einen globalen Satz von 64 und 128 weitere für die Fenster getrennt.

-

Registerfenster stellen außerdem einen einfachen Upgrade-Pfad bereit. Da die zusätzlichen Register für die Programme unsichtbar sind, können jederzeit zusätzliche Fenster hinzugefügt werden. Zum Beispiel führt die Verwendung objektorientierter Programmierung häufig zu einer größeren Anzahl ”kleinerer” Aufrufe, welche zum Beispiel durch Vergrößern der Fenster von acht auf sechzehn untergebracht werden können. Das Endergebnis ist eine geringere Anzahl langsamer Registerfensterüberlauf- und -fülloperationen, weil die Registerfenster weniger häufig überlaufen.

-

Implementierungen von ”Out-of-Order”-Anweisungen für Anweisungssatz-Architektur-(ISA-)Prozessoren können architekturdefinierte Anweisungen direkt oder unter Verwendung von durch eine Hardware-Anweisungsdecodiereinheit aufgerufener Firmware ausführen. Jedoch ”zerschlagen” viele Prozessoren architekturdefinierte Anweisungen in an Hardware-Einheiten innerhalb des Prozessors gerichtete Mikro-Operationen. Ferner kann ein CISC-(complex instruction set computer)Architektur-Prozessor CISC-Anweisungen in RISC-(reduced instruction set computer)Architektur-Anweisungen umsetzen. Um Aspekte der Erfindung zu erläutern, werden ISA-Maschinenanweisungen beschrieben und können interne Operationen (iops) intern als die ISA-Maschinenanweisung oder als kleinere Einheiten (Mikro-ops) oder Mikrocode oder auf jede in der Fachwelt allgemein bekannte Art und Weise eingesetzt werden, wobei sie hierin nach wie vor als Maschinenanweisungen bezeichnet werden. Maschinenanweisungen einer ISA haben ein Format und eine Funktion wie durch die ISA definiert, sobald die ISA-Maschinenanweisung abgerufen und decodiert wird, kann sie in iops zur Verwendung im Prozessor umgewandelt werden.

-

Viele moderne Prozessoren verwenden eine große Anzahl von physischen Registern und einen Registerumbenennungs-Ansatz, um architekturdefinierte Register einem großen Satz von physischen Registern zuzuordnen. Viele Werte in Registern werden länger aufbewahrt als erforderlich, während Prozessoren nicht wissen, wann ein Register seinen Wert nicht mehr bewahren muss. Durch Behalten nicht benötigter Werte in der Physische-Register-Datei verringert sich die Anzahl verfügbarer Register im Pool von freien Registern, was sich negativ auf die Compiler-Leistungsfähigkeit auswirkt, und kommt es zu einer weniger aggressiven ”Out-of-Order”-Ausführung, niedrigerer Prozessorleistung, erhöhtem Strom- und Energieverbrauch und erhöhter Anfälligkeit von Transaktionen für normale Fehler wegen der längeren Ausführungszeit. Außerdem ermöglichen mehr verfügbare Register höhere Leistung für die Multithread-Ausführung und für mehrere Partitionen, wodurch eine besser Plattform für die Virtualisierung bereitgestellt wird, um Cloud-Computing-Umgebungen zu ermöglichen. Schließlich erhöht das Behalten nicht benötigter Werte die Anzahl verwundbarer Daten, die transiente Fehler erleiden können, welche entweder korrigiert werden oder eine Maschinenfehler-Anzeige auslösen müssen, um eine Anwendung, eine Partition oder ein System zu stoppen, um eine Ausbreitung fehlerhafter Daten zu vermeiden.

-

Im Fall von Multithread-Prozessoren kann ein Prozessor einen Thread abschließen, wenn etwaige persistente Daten im Hauptspeicher gespeichert wurden und wenige Register, wenn überhaupt eines, Werte enthalten können, die in der Zukunft gebraucht werden. An diesem Punkt könnten dem Thread zugewiesene architekturdefinierte Register in den Pool zurückgegeben werden, wenn der Prozessor wüsste, dass nicht mehr auf sie zugegriffen werden soll.

-

In einem Aspekt der Erfindung ist ein architekturdefiniertes Register möglicherweise ”nicht zugeordnet”, wenn angezeigt wird, dass sein Wert nicht mehr verwendet wird. So wird, wenn eine Anweisung angibt, dass ein letzter Verweis auf eine Zustandsbewahrungsposition (state holding location) aufgetreten ist oder gerade auftritt, das physische Register von der Zuordnung zum architekturdefinierten Register befreit und in den Pool von verfügbaren Registern zurückgegeben. In einer Ausführungsform werden Mechanismen verwendet, um Anweisungen abzurufen, Anweisungen unter Missachtung der Reihenfolge (”out of order”) auszugeben, einschließlich der Fähigkeit, Abhängigkeiten zwischen den Anweisungen zu erkennen, die von einer Anweisung verwendeten Register umzubenennen, die Verfügbarkeit der von einer Anweisung verwendeten Ressourcen zu erkennen und die Zuordnung eines Registers zu entfernen, das als ”Letztverwendung” gekennzeichnet wurde, und in einer seinen Inhalt nicht verfügbar machenden Ausführungsform den ”Out-of-Order”-Zustand des Prozessors zu bewahren, welcher die Auswirkungen von Anweisungen, während sie (unter Missachtung der Reihenfolge) ausgeführt werden, widerspiegelt, Anweisungen in Programmreihenfolge zurückzuziehen, gleichzeitig den reihenfolgegemäßen Zustand mit den Auswirkungen der zurückgezogen werdenden Anweisung zu aktualisieren und eine Anweisung in Programmreihenfolge zurückzuziehen, ohne den reihenfolgegemäßen Zustand zu aktualisieren (wobei die Auswirkungen der zurückgezogen werdenden Anweisung wirksam aufgehoben werden), und die reihenfolgegemäße Ausführung des Programms beginnend mit der zurückgezogen werdenden Anweisung wiederaufzunehmen (was das Aufheben aller im ”Out-of-Order”-Zustand vorliegenden Auswirkungen impliziert).

-

Heutzutage müssen Mikroprozessoren alle Werte, die so beschrieben werden, dass sie durch den Anweisungsstrom berechnet werden, berechnen und bewahren, bis dieser Wert überschrieben wird.

-

Viele moderne Prozessoren verwenden den Ansatz der Registerumbenennung, um architekturdefinierte Register einem großen Satz (Pool) von physischen Registern zuzuordnen.

-

Werden nicht benötigte Werte länger als erforderlich in Registern aufbewahrt, hat dies merkliche Beeinträchtigungen zur Folge, die zu einem Verlust an Zuverlässigkeit (RAS) und Leistung sowie zu erhöhtem Strom- und Energieverbrauch führen.

-

Computer haben üblicherweise ein Betriebssystem (OS) und ein oder mehrere auf einem oder mehreren Prozessoren laufende Anwendungsprogramme. Das OS verwaltet Ressourcen und stellt eine Anwendungsschnittstelle für Anwendungsprogramme bereit, um auf Ressourcen zuzugreifen. Das OS läuft üblicherweise mit Primärberechtigung auf den Prozessoren. Das OS gestattet Anwendungen, für Zeitspannen auf dem Prozessor zu laufen, indem es den Prozessor veranlasst, einen Kontextwechsel von für das OS bereitgestellten Ressourcen zu für das Anwendungsprogramm bereitgestellten Ressourcen vorzunehmen. An irgendeinem Punkt wird ein weiterer Kontextwechsel vom Anwendungsprogramm zum OS auftreten, zum Beispiel wegen eines Fehlers, auf den das Anwendungsprogramm oder das das OS aufrufende Anwendungsprogramm gestoßen ist.

-

Der architekturdefinierte Zustand (Kontext) eines Threads, eines Prozesses und eines Prozessors enthält durch die Architektur definierte und mit dem Thread, dem Prozess beziehungsweise dem Prozessor verknüpfte Register und Speicherwerte. Deshalb muss Software bei Kontextwechseln immer den gesamten mit dem Thread, Prozess oder Prozessor verknüpften Zustand speichern und wiederherstellen und muss Hardware teure Register unterhalten, um nicht benötigte Zustände von Ressourcen zu bewahren, die anderweitig zugeordnet werden könnten, um eine Leistungsbeschleunigung zu erreichen. Schließlich erhöht die Bewahrung nicht benötigter Zustände die Verwundbarkeit eines Systems durch Einzelereignis-Störungen (d. h. normale Fehler), wodurch die Zuverlässigkeit abnimmt, weil mehr Zustände verwundbar sind, und verändert sich die Fehlerrate proportional zur Anzahl der zustandsführenden Elemente, wobei das System bei Auftreten eines Fehlers immer davon ausgehen muss, dass es zu einer Beschädigung von Benutzerdaten gekommen ist, welche entweder kostspielige Korrektureinrichtungen erfordert oder fehlerhafte Daten anzeigt, z. B. mit einem Maschinenfehler-Stopvorgang, und die Systemverfügbarkeit beeinträchtigt.

-

Statusinformationen in einem Computersystem enthalten üblicherweise einen Programmbefehlszähler-Wert (die Speicheradresse der nächsten auszuführenden Anweisung), architekturdefinierte allgemeine Registerwerte (in einer beispielhaften Architektur 16 × 64-Bit-Register, in weiteren beispielhaften Architekturen beispielsweise 64 × 64-Bit-Register), architekturdefinierte Gleitkommaregister (in einem Beispiel beispielsweise 32 × 128-Bit-Register) und weitere für ein Programm verfügbare Register (wie beispielsweise IBM zArchitecture-Zugriffsregister). Weiterer Kontext könnte Bedingungscodes enthalten, die Informationen über ein Ergebnis einer vorher ausgeführten Anweisung angeben.

-

Wenn ein Betriebssystem in einem Prozessor aufgerufen wird, der zum Beispiel gerade eine Anwendung ausführt, wird der Kontext der Anwendung gesichert (zum Beispiel im Hauptspeicher), wobei der Programmbefehlszähler auf eine auszuführende nächste Anweisung und durch das Anwendungsprogramm bis zu diesem Punkt berechnete Registerwerte verweist, so dass, wenn die Ausführung des Anwendungsprogramms zu einem späteren Zeitpunkt wiederaufgenommen wird, der Programmbefehlszähler wiederhergestellt werden kann, damit die Ausführung der Anwendung beginnend mit der nächsten Anweisung mit den vorher berechneten Registerwerten wiederaufgenommen werden kann.

-

Nach Stand der Technik stellten Computeranweisungssatz-Architekturen (ISAs) eine feste Anzahl von Ressourcen (beispielsweise allgemeine Register) bereit und konnten Anweisungen eine der Ressourcen explizit oder implizit als eine adressierbare Entität angeben. Eine ISA, die 32 allgemeine Register vereinbart, würde die ISA ausführende Prozessoren erfordern, um stets den Kontext jedes einzelnen der 32 Register zu bewahren. In einer Ausführungsform wird nur eine Teilmenge der bezeichneten Ressource (32 Register) aktiviert, um einem Prozessor zu erlauben, die Tatsache auszunutzen, dass Kontext nur für aktivierte Ressourcen (Register) bewahrt zu werden braucht. So kann zum Beispiel, wenn eine aktivierte Ressource inaktiviert wird, der Wert der aktivierten Ressource gelöscht statt gesichert werden. Jeder Zugriff auf eine inaktivierte Ressource würde vorzugsweise einen architekturdefinierten Wert oder eine architekturdefinierte Bedingung anstelle eines zuletzt in der Ressource gespeicherten Werts liefern.

-

In einer Ausführungsform können Anweisungen eine Letztverwendung eines Registers angeben, was das Versetzen des Registers in einen inaktivierten Zustand bewirkt. In einer Ausführungsform wird ein Register in einem inaktivierten Zustand durch eine in das Register speichernde Anweisung in einen aktivierten Zustand versetzt. In einer Ausführungsform kann eine Anweisung Register angeben, die in einer weiteren Anweisung in einen inaktivierten Zustand zu versetzen sind. Zum Beispiel kann eine Präfixanweisung ein Register (oder eine Gruppe von Registern) angeben, das bzw. die in der nächsten folgenden Anweisung, einer späteren Anweisung oder sogar einer früheren Anweisung in Programmreihenfolge letztmals verwendet werden. In einer weiteren Ausführungsform kann eine Anweisung Register angeben, die in einer weiteren Anweisung in einen aktivierten Zustand zu versetzen sind. Zum Beispiel kann eine Präfixanweisung ein Register (oder eine Gruppe von Registern) angeben, das bzw. die in der nächsten folgenden Anweisung, einer späteren Anweisung oder sogar einer früheren Anweisung in Programmreihenfolge in einen aktivierten Zustand versetzt werden sollen.

-

Levy schlägt Anweisungen zur Angabe einer letzten Verwendung eines Umbenennungsregisters vor. Wie allgemein bekannt ist, ist ein Umbenennungsregister eine spekulative Form eines architekturdefinierten Registers, das vorübergehend Operanden für Anweisungen enthält, die nicht abgeschlossen sind. Levy sagt nichts darüber, wie ein Ereignis zu behandeln ist, wo eine spekulative Anweisung tatsächlich abgeschlossen wird, deren Umbenennungsregister inaktiviert und in den Pool von verfügbaren physischen Registern zurückgegeben wurde, oder wie Umbenennungsregister auf irgendeine Weise mit Kontextwechseln zu tun haben könnten. Ferner sind Umbenennungsregister keine architekturdefinierten Register, sie sind spekulative Register, die durch einen Kontextwechsel nicht gesichert oder wiederhergestellt werden. Umbenennungsregister sind für Compiler und Programme unsichtbar. Ausführungsformen befassen sich mit architekturdefinierten Ressourcen einschließlich allgemeiner Register, die für Compiler und Programmierer sichtbar sind. Ausführungsformen beinhalten, wie Kontextwechsel, Fehlererkennung und verschiedenartige Zugriffe auf von ihrer Zuordnung befreite architekturdefinierte Operanden (Register) gehandhabt werden.

-

Compilern (und Programmierern) ist klar, wann sie einen Wert nicht mehr brauchen. Es wird ein Weg bereitgestellt, einem Mikroprozessor bekannte Programmentwicklungs- und Kompilierzeit-Informationen mitzuteilen, damit der Mikroprozessor weiß, dass Werte nicht mehr benötigt werden, zum Beispiel dass zukünftige Anweisungen nicht auf einen Operandenwert in einem Register zugreifen werden, so dass das Register in einen inaktivierten Zustand versetzt werden und der Inhalt vom Prozessor gelöscht oder ignoriert werden kann. Eine solche Bedingung kann zum Beispiel vorliegen, wenn eine Anweisung ein Ergebnis und einen Bedingungscode sichert, wobei der Anweisung eine Verzweigungsanweisung zur Verzweigung auf Grundlage des Bedingungscodes folgt. Die Anweisung ist eine allgemeine Anweisung, und in anderen Verwendungen wird der gespeicherte Wert benötigt, in dieser Verwendung der allgemeinen Anweisung jedoch wird nur der Bedingungscode benötigt und greift keine zukünftige Anweisung auf das gespeicherte Ergebnis zu.

-

Eine beispielhafte Prozessor-Pipeline weist auf:

- 1. einen Mechanismus zum Abrufen von Anweisungen;

- 2. einen Mechanismus zum Ausgeben abgerufener Anweisungen unter Missachtung der Reihenfolge (”out of order”) einschließlich der Fähigkeit, Abhängigkeiten zwischen den Anweisungen zu erkennen, die von einer Anweisung verwendeten Register umzubenennen und die Verfügbarkeit der von einer Anweisung verwendeten Ressourcen zu erkennen;

- 3. einen Mechanismus zum Bewahren des ”Out-of-Order”-Zustands des Prozessors, welcher die Auswirkungen von Anweisungen, während sie (unter Missachtung der Reihenfolge) ausgeführt werden, widerspiegelt;

- 4. einen Mechanismus zum Zurückziehen von Anweisungen in Programmreihenfolge, der gleichzeitig den reihenfolgegemäßen Zustand mit den Auswirkungen der zurückgezogen werdenden Anweisung aktualisiert;

- 5. einen Mechanismus zum Zurückziehen einer Anweisung in Programmreihenfolge, ohne den reihenfolgegemäßen Zustand zu aktualisieren (wobei die Auswirkungen der zurückgezogen werdenden Anweisung wirksam aufgehoben werden), und zum Wiederaufnehmen der reihenfolgegemäßen Ausführung des Programms beginnend mit der zurückgezogen werdenden Anweisung (was das Aufheben aller im ”Out-of-Order”-Zustand vorliegenden Auswirkungen impliziert).

-

Ein Computerprozessor kann eine Anweisungsabrufeinheit zum Erlangen von Anweisungen aus dem Hauptspeicher, eine Decodiereinheit zum Decodieren von Anweisungen, eine Ausgabewarteschlange zum Einreihen von auszuführenden Anweisungen, Ausführungseinheiten zum Ausführen der Funktion von Anweisungen und eine Abfertigungseinheit zum Abfertigen von Anweisungen an entsprechende Ausführungseinheiten vorzugsweise in einer Pipeline aufweisen. In Ausführungsformen können zum Beispiel eine Ausgabewarteschlange, eine Decodiereinheit oder eine Abfertigungseinheit allein oder in Verbindung miteinander eine Anweisung so verändern, dass sie nach einer vorherigen Anweisung nicht ausgeführt zu werden braucht.

-

In einer Ausführungsform ermittelt der Prozessor, dass es eine erste Anweisung und eine zweite Anweisung gibt, wobei die zweite Anweisung so konfiguriert ist, dass sie die Ergebnisse der Ausführung der ersten Anweisung beim Ausführen der zweiten Anweisung verwendet. Ein Test der beiden Anweisungen ermittelt, dass sie verändert werden können, um Anweisungen zu erzeugen, die effizienter ausgeführt werden können. In einem Beispiel ermöglicht die Veränderung, die beiden Anweisungen ”out of order” (unter Missachtung der Reihenfolge) auszuführen (die zweite Anweisung (die zweite in der Programmreihenfolge) hängt nicht von Ergebnissen der ersten Anweisung (der ersten in der Programmreihenfolge) ab).

-

In einer beispielhaften Ausführungsform stellt ein architekturdefinierter Anweisungssatz Direktanweisungen bereit (Direktanweisungen haben ein Direktfeld, das bisweilen als Verschiebungsfeld oder Konstantenfeld bezeichnet wird, wobei das Direktfeld einen Direktwert bereitstellt). Die Direktanweisung kann auch ein Registerfeld enthalten, wobei ein Operand ein Registerwert eines durch das Registerfeld identifizierten Registers ist oder wobei ein Operand ein Speicherwert einer durch den Registerwert bestimmten Speicherposition ist. Außerdem weist die Direktanweisung ein Opcode-Feld auf, das einen Wert enthält, der eine durchzuführende Operation bestimmt (wie zum Beispiel ADDIEREN, SUBTRAHIEREN, UND, ODER, Laden, Speichern). Die Ausführung der Direktanweisung führt die Operation unter Verwendung des Operandenwerts und des Direktwerts durch und kann das Ergebnis in einem von der Direktanweisung angegebenen Ergebnisregister (oder im Hauptspeicher) speichern.

-

In einer beispielhaften Architektur enthält der Anweisungssatz eine Direktanweisung, in welcher eine Operation nur an einem Teil des Operanden durchgeführt wird. So kann zum Beispiel ein Direktwert zu einem niedrigstwertigen Teil des Operanden addiert werden. Der Anweisungssatz kann ein 16-Bit-Direktfeld und ein 32-Bit-Register bereitstellen, wobei in diesem Fall das Laden einer Konstante in ein 32-Bit-Register zwei Direktanweisungen erfordern würde. In einer beispielhaften Sequenz von Anweisungen wird eine erste Direktanweisung verwendet, um den niedrigstwertigen Teil zu laden, und wird eine zweite Direktanweisung verwendet, um den höchstwertigen Teil zu laden. In einem anderen Anweisungssatz können Direktfelder 8 Bits und Register 32 Bits haben, wobei in diesem Fall 4 Direktanweisungen erforderlich wären, um eine Konstante in das Register zu laden. In manchen Umgebungen wird möglicherweise nur ein Teil des Operanden benötigt, wie beim Erstellen einer Tabellenadresse, wobei durch eine Anweisung in einer Sequenz von Anweisungen nur der niedrigstwertige Teil bereitgestellt wird (wobei jede Sequenz von Anweisungen durch Verwendung eines Direktwerts für einen niedrigstwertigen Teil des Registers einen Tabelleneintrag identifiziert, aber den höchstwertigen Teil, der die Tabelle lokalisiert, nicht betrifft). In diesem Fall werden zum Laden der niedrigstwertigen 16 Bits des 32-Bit-Registers nur zwei 8-Bit-Direktanweisungen benötigt.

-

In einer beispielhaften Ausführungsform sind zwei Direktanweisungen in einem Programm enthalten, wobei auf eine erste Direktanweisung in der Programmreihenfolge eine zweite Direktanweisung folgt. Jede Anweisung enthält ein 16-Bit-Direkt-(oder Verschiebungs-)Feld (disp) und ein Zielregister (RT). Die Funktion der ersten Direktanweisung besteht darin, den Wert des ersten disp-Felds in den niedrigstwertigen Teil des ersten RT zu laden. Die Funktion der zweiten Direktanweisung besteht darin, den Wert des zweiten disp-Felds in den höchstwertigen Teil des zweiten RT zu laden. Der die beiden Anweisungen ausführende Prozessor stellt fest, dass die beiden Anweisungen zum Beispiel in einer Ausgabewarteschlange des Prozessors kombiniert werden können, weil der Prozessor über die Fähigkeit verfügt, die beiden Anweisungen zu erkennen und die disp-Felder durch Verketten des ersten disp und des zweiten disp zu einem internen Datenwert zusammenzusetzen, der in die Pipeline passt, wobei die erste Anweisung gelöscht wird und eine veränderte zweite Anweisung, welche den verketteten Wert als ein disp-Feld enthält, erstellt wird. In einer Ausführungsform ist der interne Datenwert, der unterstützt wird, so schmal, dass nur ein Teil des zweiten disp-Werts kombiniert werden kann, wobei in diesem Fall der Prozessor nur das Auftreten zweiter disp-Werte erkennt, die klein genug sind. Die Direktanweisungen haben die Form:

RT←disp

wobei

- erste Anweisung: RT←disp(low)

- zweite Anweisung: RT←disp(high)

- veränderte zweite Anweisung: RT←disp(high)//disp(low)

-

In einer weiteren Ausführungsform enthalten die erste und die zweite Anweisung außerdem ein zweites Registerfeld (RA-Feld) zum Identifizieren eines Operandenregisters (RA).

Anweisungsform RT←RA, disp

-

Durch jede das Operandenregister RA und das disp-Feld verwendende Anweisung wird eine Funktion durchgeführt. Ein Auftreten der beiden Anweisungen wird erkannt, wobei jede Anweisung dieselbe Operation durchführt, jedoch nur an einem Teil von RA und RT. Zum Beispiel werden der RA-Wert und der disp-Wert durch eine logische UND-Anweisung UND-verknüpft:

- erste Anweisung: r2←r3, disp(high) [disp wird mit dem hohen Teil des Werts des r3-Registers UND-Verknüpft, und das Ergebnis wird in den hohen Teil des r2-Registers gestellt]

- zweite Anweisung: r2←r3, disp(low) [disp wird mit dem niedrigen Teil des Werts des r3-Registers UND-Verknüpft, und das Ergebnis wird in den niedrigen Teil des r2-Registers gestellt]

- veränderte zweite Anweisung: r2←r3, disp(high)//disp(low) [disp(high) verkettet mit disp(low) wird mit dem Wert des r3-Registers UND-Verknüpft, und das Ergebnis wird in das r2-Register gestellt]

-

In einer Variante wird eine arithmetische Operation in zwei Anweisungen durchgeführt, wobei in diesem Fall die beiden Anweisungen in Programmreihenfolge ausgeführt werden müssen, da das Ergebnis der ersten Anweisung benötigt wird, um die zweite Anweisung auszuführen. In diesem Beispiel müssen ein r2- und ein r4-Ergebnis in den Registern gespeichert werden. In diesem Fall wird die zweite Anweisung verändert, um ein internes Paar von Anweisungen zu erstellen, die ”out of order” (unter Missachtung der Reihenfolge) ausgeführt werden können.

- erste Anweisung: r2←r3, disp(high) [addiert ein 8-Bit-disp verkettet mit 8 niedrigstwertigen Nullen zum Wert des 16-Bit-r3-Registers und stellt das Ergebnis in das 16-Bit-r2-Register]

- zweite Anweisung: r4←r2, disp(low) [addiert ein vorzeichenerweitertes 8-Bit-disp (16 Bits) zum 16-Bit-r2-Register und stellt das Ergebnis in das 16-Bit-r4-Register]

- veränderte zweite Anweisung: r4←r3, disp(high)//disp(low) [addiert disp(high) verkettet mit disp(low) zum Wert des r3-Registers und stellt das Ergebnis in das r4-Register]

-

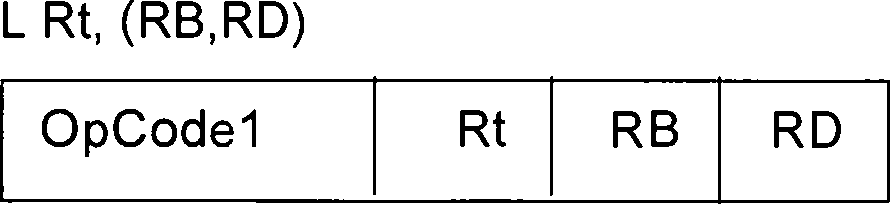

In einer Ausführungsform besteht eine erste Anweisungssequenz aus mindestens einer ersten Anweisung ”i0” und einer zweiten Anweisung ”i1” und einer Sequenz von mehreren internen Anweisungen (internen ops (iops)), welche Verbesserungen der Anweisungssequenz sind. Zum Beispiel könnte eine Erzeugeranweisung, auf welche eine Verbraucheranweisung in Programmreihenfolge (welche reihenfolgegemäße Ausführung erfordert) folgt, optimiert werden, um iop0 entsprechend der Erzeugeranweisung und iop1 entsprechend der Verbraucheranweisung zu erstellen, wobei iop0 und iop1 ”out of order” (unter Missachtung der Reihenfolge) ausgeführt werden können.

-