CN1186729C - 从虚地址计算页表索引的方法和装置 - Google Patents

从虚地址计算页表索引的方法和装置 Download PDFInfo

- Publication number

- CN1186729C CN1186729C CN00132829.8A CN00132829A CN1186729C CN 1186729 C CN1186729 C CN 1186729C CN 00132829 A CN00132829 A CN 00132829A CN 1186729 C CN1186729 C CN 1186729C

- Authority

- CN

- China

- Prior art keywords

- address

- page table

- page

- hash

- virtual address

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1009—Address translation using page tables, e.g. page table structures

- G06F12/1018—Address translation using page tables, e.g. page table structures involving hashing techniques, e.g. inverted page tables

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

- G06F2212/652—Page size control

Abstract

一种从虚地址计算页表索引的方法和装置。本发明像用一种支持两种不同散列页表配置的组合散列算法。“短格式”页表为每一虚拟区域提供,是线性的,它为在该区域内的每一转换有一个线性条目,而不存储标签或链连接。单一“长格式”页表为整个系统提供,它支持链段,并包括散列标签字段。

Description

技术领域

本发明涉及计算机系统中的存储器组织。更具体说,本发明涉及具有可通过散列函数访问的页表的虚拟存储器系统。

背景技术

常规计算机系统使用一种称为虚拟存储器的技术,虚拟存储器模拟比实际存在更多的逻辑存储器,并允许计算机并列运行几个程序,而不管它们的大小。并发用户程序通过由操作系统指定的虚地址访问主存地址。虚地址向主存的物理地址的映射是称为虚地址转换的过程。可以使用任何数目的技术实现虚地址转换,从而允许处理器访问主存中希望的信息。

虚地址和物理地址空间通常分成称为页的等大的存储器块,而页表提供虚地址和物理地址之间的转换。每一页表条目通常包含虚地址和/或物理地址,和有关该页的保护和状态信息。状态通常包括关于该页曾经经受的访问的类型的信息。例如,已修改位指示曾经对该表内的数据进行过修改。因为页表通常很大,因此它们存储在存储器中。所以,正常的存储器访问实际需要至少两次访问,一次是得到该转换,再一次是访问物理存储器位置。

许多支持虚地址转换的计算机系统使用一种转换查阅缓冲器(TLB)。TLB通常是一个小而快的关联存储器,它通常位于处理器单元上或在其邻近处,并存储最近使用的虚拟和物理地址对。TLB包含页表中转换的一个子集,可以被非常快地访问。当处理单元需要来自主存的信息时,它把虚地址发送给TLB。TLB接受该虚地址页号,而返回一个物理页号。该物理页号与低阶地址信息结合来访问主存中希望的字节或字。

在大多数场合,TLB不能包含整个页表,所以需要实现若干步骤来更新该TLB。当访问一个虚页,而该转换不在TLB内时,则访问页表来确定该虚页号对物理页号的转换,这一信息输入到TLB中。对页表的访问需要的时间可以比对TLB的访问长20倍,因此通过保持在TLB中使用转换来优化程序执行速度。

当今大多数计算机系统使用某种海量存储器,通常是磁盘,来扩大计算机中的物理随机访问(RAM)存储器。主存的这一扩大允许实现比只用主存所能执行的程序更大的程序。另外,磁盘存储器要比RAM便宜很多,但是也相当慢。取决于程序长度和与其它程序对主存的竞争,在任何特定的时间点,部分程序可以驻留在主存中,而部分驻留在磁盘上。需要被立即访问的程序部分被取入主存,而当前不用的部分留在磁盘上。

例如,考虑一个两兆字节长且在具有1兆字节主存的计算机上执行的程序。该程序将需要两兆字节虚地址空间。由于主存只能容纳1兆字节,在任何给定时间最多一半程序可以驻留在主存中,剩余的虚地址空间存储在磁盘上。对在主存中的信息的访问正常发生。亦即首先查阅TLB,看是否有该转换,如果不在TLB中,则使用页表中的信息更新TLB,然后再次引用TLB来获得希望的转换信息。

如果发生对不在主存内的信息进行访问的话,则首先访问TLB,检索不在其内的转换。然后引用页表以获得转换信息来更新TLB。然而该页表只有为在主存内的信息的转换,因此没有需要的转换信息。这一条件称为页错误。响应页错误,页错误处理程序寻找一个空物理页,用存储在磁盘上的需要的虚页加载该物理页。如果所有物理页已与其它虚页关联,则页错误处理程序需要选择当前存储在物理存储器中的哪一个虚页与磁盘交换。有许多执行这一任务的算法,诸如先进先出和最后使用算法。页错误处理程序通常以软件实现,而TLB更新处理可以由硬件或者软件处理,其在技术中公知。

图1说明上述处理。在步骤112给TLB提交一个虚地址。如果为该虚地址的转换存在于TLB(TLB命中),则从TLB中导出相关物理地址,并用来访问物理存储器(步骤114)。如果为该虚地址的转换在TLB中不存在(TLB未命中),则为该转换访问页表(步骤116)。如果该转换在页表中,则将这一信息插入TLB(步骤118),并再次提交虚地址(步骤112)。这一次将会是TLB命中,于是使用结果物理地址访问物理存储器。

如果该虚地址在一个无物理地址与之相关的虚地址页内,则在页表内没有为该页的条目,于是发生页错误。在这种情况,软件页错误处理程序(步骤120)将给该虚页分配一个物理页,从磁盘复制该页到该物理页,并更新页表。然后再次把该虚地址提交给TLB。因为TLB尚未有该转换,因此会发生另一TLB未命中,TLB将从页表更新。之后,把该虚地址再次提供给TLB,而这一次保证TLB命中,使用结果物理地址访问物理存储器。

图2说明响应虚地址的提交访问转换查阅缓冲器(TLB)中一个条目的简化方法。为简化该例,图示TLB只有一个条目,而TLB通常有多得多的条目。把虚地址加载到寄存器201。这一虚地址包括两部分,虚页号203和物理偏移205。物理偏移相应于页大小。对于具有页大小4千字节的计算机系统,物理偏移205是地址的低12位(位11-0),指定一页内的一个特定字节。寄存器内的剩余位指示虚页号。术语“页偏移”是工业中常用的一个术语,其与术语“物理偏移”是同义词。虚地址可以包括用于唯一指定向一个物理页号转换的其它位,诸如“地址空间标识符”位或“区域标识符”位。

对于所述例子,虚页号成为虚标签,它提供给TLB比较器207的一个输入。TLB209有两个连接的部分,TLB标签211和一个相关的物理页号213。TLB标签211给TLB比较器207提供第二输入,该比较器比较TLB标签和虚标签。如果两个标签匹配,则比较器指示TLB命中,并把物理页号213与物理偏移205结合来提供物理(真实)存储器地址。如果两个标签不匹配,则出现TLB未命中,则使用参考图1说明的TLB未命中处理更新TLB。

图3表示给定虚页号检索物理页信息的处理,需要这一处理来在TLB未命中后更新TLB。如上所述,在页表中维持虚拟到物理的映射。为把一个给定的虚地址转换为物理地址,一种方法是对该虚地址执行一种多对单(散列)函数以形成对页表的一个索引。这给出对一个链接的条目表的指针。然后检索这些条目寻找匹配。为确定一个匹配,比较该虚页号和在页表中的一个条目(虚标签)。如果这两个相等,则该页表条目提供物理地址转换。

在所述例子中,对虚页号203执行散列函数301形成一个索引。该索引是对页表303的偏移。如图所示,索引是0,亦即,该索引指向页表303中的第一条目305。页表中的每一条目包括多个部分,但是通常至少包括有虚标签307、物理页309和指针311。如果虚页号203等于虚标签307,则物理页309给出希望的物理(真实)存储器页地址。如果虚标签不匹配,则指针311指向包含虚拟对物理转换信息的存储器中的一个条目链。需要在该链中包含诸如可以散列多于一个的虚页号到同一页表条目的另外的信息。

如图所示,指针311指向一个链段。该链段包括同一类型的信息作为开始的页表条目。和前面一样,比较虚页号与下一虚标签315,看是否匹配。如果匹配,则相关的物理页317给出希望的物理存储器页的地址。如果不匹配,则检查指针309来定位下一链段,如果存在的话。如果指针319不指向另一链段,如图所示,则出现页错误。于是使用页错误软件程序来更新页表,其参考图1已说明。

上述方法对于虚标签少于或等于计算机的基本数据路径大小的系统工作的很好。然而,如果虚标签大于该数据路径大小,则需要两次比较来测试虚标签和虚页号是否相同。

因此转让给Dale Morris等人的美国专利NO5724538在此作为参考,其名称为“使用页表中的散列地址标签的计算机存储器地址控制装置,该散列地址标签与一个组合地址标签和索引比较,其长于相关计算机的基本数据宽度”,它公开了一种减少虚标签大小的方案,从而较少了测试虚标签和虚页号是否相同所需要的比较数目。基本上,Morris等人认识到部分虚地址已经由散列索引表示,因此部分地址不需要由虚标签表示。

图4表示由Dale Morris公开的一个实施例的简化方框图。在图4中,页表413包括“散列标签”421和423。通过取虚页号位401并对这些位执行索引散列函数405形成散列索引409,其结果不大于该计算机的基本数据宽度。相似地,通过取虚页号位401并执行标签散列函数427,其结果散列标签不大于该计算机的基本数据宽度。注意,虽然图4未表示在标签散列函数427和散列标签421和423之间的明显的连接,但是当产生散列标签421和423并插入页表413中时使用由标签散列函数427表示的算法。

索引散列函数405和标签散列函数427是值得称道的,因为对于任何给定的虚页号,结果散列索引和结果散列标签的组合是唯一的。因此,当访问一个虚页时,对索引散列函数405应用该虚页的号码401来产生散列索引,其指向页表413中的一个散列标签(诸如散列标签421或423)。从表413提供的散列标签导向比较函数429。同时,也把虚页号401提供给标签散列函数427来产生散列标签425。如果散列标签425和来自页表413的散列标签匹配,则使用该物理页(诸如在条目317和417存储的物理页)完成存储器访问操作。如果这两个标签不匹配,则访问页表条目的指针(诸如指针319和419)看是否存在一个链段。如果不存在链段,或者检索过所有链段而没有发现有匹配,则调用操作系统的页错误处理程序,如上所述。

注意,既用硬件也用软件访问索引散列函数405和标签散列函数427。当转换一个虚页号为物理页号时硬件必须访问该散列函数,而当初始化该页表并访问和修改该页表时软件必须访问该散列函数,诸如服务于页错误时所需要的。在现有技术中,散列算法基本上以两种形式提供。计算机硬件包括的基于硬件的散列算法版本允许虚拟对物理的转换迅速处理,而操作系统包括的基于软件的散列算法版本在初始化、访问和修改页表时产生虚拟对物理的转换。

某些计算机通过支持多区域扩展虚拟寻址概念。多区域通过把虚地址空间分成等大的区域而提供有效产生在该虚地址空间内独立的局部、共享和全局寻址空间的能力。通常,在任何时间只有多区域的一个子集可以激活。与每一区域相关的有一个区域标识符,它唯一标记给定区域的地址转换。如果把为一个区域的区域标识符分配给一个特定处理,则该区域空间成为对该处理的局部空间。如果为一个区域的区域标识符在多个处理之间共享,则该区域空间成为共享空间。如果为一个区域的区域标识符为所有处理共享,则该区域成为全局空间。改变为局部区域的区域标识符有效交换一个处理的局部空间的虚地址为另一处理的局部空间的虚地址。这样,多区域事实上消除了在切换处理时刷新TLB的需要,从而改善了总系统性能。

发明内容

根据本发明的一个方面,提供一种从虚地址形成引用页表条目的一个入口地址的方法,其中,虚地址包括一个区域部分,它引用标识一个区域的活动区域标识符,该页表能够采取长格式和短格式,所述方法包括:

通过右移该虚地址J位从该虚地址形成一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

如果该页表的格式设定为长格式的话,结合该散列页号和由该虚地址的区域部分引用的区域标识符形成散列索引;

如果该页表的格式设定为长格式的话,左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长;

如果该页表的格式设定为短格式的话,设定散列索引等于散列页号,形成一个散列索引;

如果该页表的格式设定为短格式的话,左移该散列索引L位形成一个表偏移,其中,每一短格式页表条目为2L字节长;

根据该页表的大小形成一个掩码;

使用该页表的基地址和该掩码形成一个第一地址部分;

使用页表偏移和该掩码形成一个第二地址部分;

通过结合第一和第二地址部分形成入口地址。

根据本发明的一个方面,提供一种从虚地址形成引用页表条目的一个入口地址的方法,其中,虚地址包括一个区域部分,它引用标识一个区域的活动区域标识符,页表的最小大小为2N字节,该页表能够采取长格式和短格式,所述方法包括:

通过只右移虚地址已经实现的那些部分J位而形成该虚地址的一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

如果页表的格式设定为长格式的话,通过结合散列页号、虚地址的区域部分、和由该虚地址的区域部分引用的区域标识符而形成一个散列索引,其中,在散列页号中根据右移虚地址J位知其为空的散列页号的位位置插入该虚地址的区域部分的位;

如果页表的格式设定为长格式的话,左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长;

如果页表的格式设定为长格式的话,通过从页表的基地址抽取区域部分形成一个页表区域;

如果页表的格式设定为短格式的话,设定散列索引等于散列页号,形成一个散列索引;

如果页表的格式设定为短格式的话,左移该散列索引L位形成一个表偏移,其中,每一短格式页表条目为2L字节长;

如果页表的格式设定为短格式的话,通过从虚地址中抽取区域部分形成一个页表区域;

通过用2的M次幂减1形成一个掩码,这里,2M是该表的大小;

通过对页表的基地址,不包括该页表基地址的低N位,和掩码的逆,不包括该掩码的逆的低N位,执行“与”运算,形成第一地址部分;

通过对表偏移,不包括该表偏移的低N位,和掩码,不包括该掩码的低N位,执行“与”运算,形成第二地址部分;和

通过对该第一和第二地址部分执行“与”运算形成一个第一结果,左移该第一结果N位形成一个第二结果,对页表区域、该第二结果、和该表偏移的低N位执行“或”运算,形成入口地址,其中,页表区域插入该入口地址的一个区域部分。

根据本发明的一个方面,提供一个计算机系统,具有定义一个由虚地址寻址的虚地址空间的结构,所述虚地址包括引用标识一个区域的一个活动区域标识符的一个区域部分,所述计算机系统包括:

存储器单元,它包括一个由页表基地址定位的页表,其中,该页表能够采取长格式和短格式;

用于执行指令的处理器,其中,该处理器包括一个页表入口地址产生单元,它能从虚地址产生到该页表的入口地址,该入口地址产生单元包括:

散列页号产生电路,它通过右移虚地址J位形成该虚地址的一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

散列索引产生电路,它在页表的格式设定为长格式时,通过结合该散列页号和由该虚地址的区域部分引用的区域标识符形成一个散列索引,而在页表的格式设定为短格式时,通过设定散列索引等于该散列页号,形成一个散列索引;

表偏移产生电路,它在页表的格式设定为长格式时,通过左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长,而在页表的格式设定为短格式时,通过左移该散列索引L位形成一个表偏移,其中每一短格式页表条目为2L字节长;

掩码发生电路,它根据页表大小形成一个掩码;

第一地址部分发生电路,它使用页表基地址和掩码形成一个第一地址部分;

第二地址部分发生电路,它使用表偏移和掩码形成一个第二地址部分;

入口地址发生电路,它通过组合第一和第二地址部分形成入口地址。

根据本发明的一个方面,提供一种计算机系统,具有定义一个由虚地址寻址的虚地址空间的结构,所述虚地址包括引用标识一个区域的一个活动区域标识符的一个区域部分,所述计算机系统包括:

存储器单元,它包括一个由页表基地址定位的页表,其中,该页表能够采取长格式和短格式,且具有2N位的最小大小;

用于执行指令的处理器,其中,该处理器包括一个页表入口地址发生单元,它能从虚地址产生到页表的入口地址,该入口地址发生单元包括:

散列页号发生电路,它通过只右移虚地址已经实现的部分J位而从该虚地址形成一个散列页号,其中,与该虚地址的区域部分相关的区域的页大小为2J字节;

散列索引发生电路,它在页表的格式设定为长格式时,通过组合散列页号、虚地址的区域部分、和由该虚地址的区域部分引用的区域标识符形成一个散列索引,其中,在该散列页号中根据右移虚地址J位知其为空的散列页号的位位置组合插入该虚地址的区域部分,而在页表的格式设定为短格式时,通过设定散列索引等于该散列页号,形成一个散列索引;

页表偏移发生电路,它在页表的格式设定为长格式时,通过左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长,而在页表的格式设定为短格式时,通过左移该散列索引L位形成一个表偏移,其中每一短格式页表条目为2L字节长;

页表区域发生电路,它在页表的格式设定为长格式时通过从页表基地址中抽取区域部分而形成一个页表区域,而在页表的格式设定为短格式时通过从虚地址中抽取区域部分而形成该页表区域部分;

掩码发生电路,它通过用2的M次幂减1形成一个掩码,这里,2M是该表的大小;

第一地址部分发生电路,它通过对页表的基地址,不包括该页表基地址的低N位,和掩码的逆,不包括该掩码的逆的低N位,执行“与”运算,形成第一地址部分;

第二地址部分发生电路,它通过对表偏移,不包括该表偏移的低N位,和掩码,不包括该掩码的低N位,执行“与”运算,形成第二地址部分;

条目发生电路,它通过对该第一和第二地址部分执行“与”运算形成一个第一结果,左移该第一结果N位形成一个第二结果,对页表区域、该第二结果、和表偏移的低N位执行“或”运算,形成入口地址,其中,页表区域插入该入口地址的一个区域部分。

本发明是一种从虚地址计算页表索引的方法和装置。本发明通过一个组合的散列算法实现,该散列算法通过配置寄存器和预先定义的常数支持在单一计算机结构中的两种不同的散列页表配置。

本发明例如可以与具有64位虚地址的虚拟寻址模式结合使用,其前3位形成虚区域部分。相应地,在任何给定时间可以由一个虚地址指定8个区域。虚地址剩余的61位用于寻址每一区域内的存储器,从而提供给每一区域261字节的虚拟存储器。与每一存储器页相关的有一个24位的区域标识符。因此,操作系统可以指定直到224个单独虚地址空间。存储器页可以从4千字节到256兆字节范围变化。

第一散列页表配置支持一个基于区域的线性页表,在此处将称为“短格式”页表。短格式页表为每一虚区域提供,它是线性的,并对在该区域中的每一转换有一个线性条目。短格式页表不需要链段,并且短格式页表不包括散列标签条目。第二散列页表配置支持为整个计算机系统的单一页表,在此处将称为“长格式”页表。长格式页表支持链段,长格式页表条目包括散列标签字段。

在一个实施例中,本发明的方法从一个虚地址形成一个入口地址,该入口地址引用页表的一个条目。为形成该入口地址,首先从虚地址通过右移该虚地址J位形成一个散列页号,其中与该虚地址的区域部分关联的区域的大小优选为2J字节。

如果计算机系统以长格式页表操作,则下一步骤是通过组合该散列页号和由虚地址的区域部分引用的区域标识符而形成一个散列索引,和通过左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长。

然而,如果计算机系统以短格式页表操作,则下一步是通过设定散列索引等于散列页号而形成一个散列索引,和通过左移该散列索引L位而形成一个表偏移,其中每一短格式页表条目为2L字节长。

接着,根据页表大小形成一个掩码。然后使用页表的基地址和该掩码形成第一地址部分,使用表偏移和该掩码形成第二地址部分。最后,结合第一和第二地址部分形成入口地址。

在一个实施例中,在入口地址中插入一个区域部分。如果设定格式为长格式,则该区域部分从页表的基地址的区域部分导出。然而,如果该区域设定为短格式,则从虚地址的区域部分导出该区域部分。

在另一个实施例中,长格式页表的最大尺寸通过在设定格式为长格式时在散列页号中插入虚地址的区域部分而增加。

本发明还包括几个实施例,它们基于某些实现独立的参数减少用于实现本发明的逻辑数量。通过提供能够为长格式和短格式页表两者产生一个页表条目的单一算法,本发明减少了访问这两种页表格式需要的逻辑数量,而不明显影响执行速度。

附图说明

图1表示现有技术响应在一个程序执行期间提供的虚地址的处理过程。

图2表示现有技术访问转换查阅缓冲器(TLB)中一个条目的方法。

图3表示现有技术在TLB未命中后检索物理页信息更新TLB的方法。

图4表示一个现有技术页表模式,其中在一个页表中存储散列标签。

图5表示由本发明支持的一个虚拟寻址模式。

图6表示一个“短格式”虚散列的页表的条目,其可以由本发明的散列函数的应用程序访问。

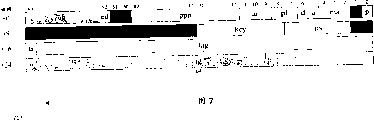

图7表示一个“长格式”虚散列的页表的条目,其可以由本发明的散列函数的应用程序访问。

具体实施方式

本发明是一种为从虚地址计算页表索引和散列标签的方法和装置。本发明由一个组合的散列算法和一个从虚地址产生散列标签的算法实现,所述组合散列算法通过配置寄存器支持在单一计算机结构中的两个不同的散列表结构。

在详细说明本发明之前,首先考虑本发明在其内可以实现的结构框架。为此,结合由Stephen Burger等人提交的、名称为“为把基于硬件的虚拟存储器散列模式暴露给软件的方法和装置”的待审美国专利申请作为参考。该申请转让给本申请的同一受让人,在1998年10月12日申请,分配的美国序列号为09/170143。Burger等人公开了两个把由硬件使用的散列算法暴露给软件来访问一个页表的指令。第一指令是转换散列的入口地址(THASH)指令,它从一个虚地址产生指向在页表中的一个条目的一个散列索引。第二指令是转换散列的条目标签(TTAG)指令,它从一个虚地址产生存储在由该散列索引引用的页表条目中的一个散列标签。通过提供这两个指令,Burger等人教导,计算机操作系统(或其它系统软件)不需用由计算机硬件使用的散列算法编码。相反,THASH和TTAG指令提供一个允许软件访问由硬件使用的散列算法的接口。本发明与上述申请在下面一点上相关,即本发明提供一种可能的算法,其可以由THASH指令使用。另外,一种可以由TTAG指令使用的可能算法在下面公开。

本发明支持在图5所示的虚拟寻址模式501。虚地址502是64位地址。前3位形成一个虚拟区域号码(VRN)503。因此,在任何给定时间可以由一个虚地址指定8个区域。使用虚地址502的剩余61位来寻址每一区域内的存储器,从而为每一区域提供261字节的虚拟存储器。与每一存储器页(诸如页504)相关的有一个24位的区域标识符(RID)。因此,操作系统可以指定直到224个单独的虚地址空间。存储器页可以在大小从4千字节到256兆字节的范围内变化,其在下面详述。说明虚区域的附加信息可以在Stephen Burger等人的美国待审专利申请、名称为“用于虚拟寻址模式中预验证区域的方法和装置”中找到。该申请因此结合在这里作为参考,其转让给和本申请同样的受让人,在1998年10月12日申请,分配有美国序列号09/170140。

本发明支持提供两个页表格式的结构。第一格式支持一个基于区域的线性页表,此处将称为“短格式”页表,短格式页表为每一虚区域提供,如图5所示。短格式页表是线性的,并为在该区域中的每一转换有一个线性条目。相应地,短格式页表不需要链段,并且短格式页表不包括散列标签条目。

第二格式支持为整个计算机系统的一个单一的大页表,在此处将称为“长格式”页表。长格式页表支持链段,长格式页表条目包括散列标签字段。

图6表示一个短格式页表条目601。注意,短格式页表条目包括单一64位字,因此总共大小为8字节。短格式条目601中的字段在下面的表1中说明。

表1

条目字段 说明

P 预设定位,指示映射的物理页是否实际在存储器

内。

Rv 保留。

Ma 存储器属性-说明所映射的物理页的超高速缓冲存

储能力,相干性,写策略和推测性。

A 被访问的位-指示如何处理页错误。

D 已修改位-指示如何处理由对该页写数据引起的错

误。

P1 特权级-指示该页的特权级。

Ar 访问权限-页级读、写和执行许可和特权控制。

ppn 物理页号-映射物理地址的最高有效位。取决于在

该映射中所用的页大小,忽略某些最小意义的PPN

位。

ig 可用于操作系统的软件字段,被CPU忽略。

ed 例外延迟-指示是否应该延迟一个例外或错误。

注意,短格式条目为在一个区域中的每一页存在,而一个转换的虚页号(vpn)由在虚散列页表(VHPT)中的该短格式条目的位置隐含。还应该注意,页大小在一个区域内是常数。因此,页大小可以通过访问与该区域关联的一个配置寄存器的preferred_page_size字段得到,其在下面讨论。

图7表示一个长格式页表条目701。注意,长格式条目包括4个64位字,因此总大小为32字节。长格式条目701的第一字和短格式条目601的相同,因此,第一字中的字段用上述表1说明。下面的表2说明长格式条目701的剩余字段。

表2

条目字段 说明

rv 保留。

ps 页大小-映射的页大小。对于页大小大于4K字节

的,忽略PPN和VPN的低阶位。页大小定义为2PS

字节。

key 保护键字-唯一标记对一个保护域的转换。

tag 转换标签。该标签与长格式索引结合,用于唯一标

识该转换。

ti 标签无效位。指示该标签无效。软件可以使用该位

使长格式条目无效。

ig 可用于操作系统的软件字段,被CPU忽略。注意,

长格式VHPT条目的最后64位(从偏移+24开始)

通常由操作系统使用来存储对另一长格式VHPT条

目的连接,如果两个或者多个虚拟对物理的转换散

列到该长格式VHPT的同一起始条目话。

注意,对所有虚地址使用单一长格式页表,条目可以链接到一起,对每一页,通常没有起始条目。因此,长格式页表条目包括附加信息,诸如页大小(ps)和标签。VPN由散列索引和标签唯一表示。

最后,在下面讨论本发明的算法之前,下述字段可用于本发明的算法。注意,这些字段的某些表示可编程变量,它们存储在配置寄存器中,因此可以由在一个特定的计算机系统中的软件执行改变。其它字段表示常数,它们在计算机系统的特定实现中不改变,因此可以硬编码为本发明的算法的特定实现。这些字段示于下面的表3。

表3

配置寄存器字段 说明

或常数

page_table_format 指示是在使用长格式还是短格式页表。这一可

编程字段是全局字段,应用于存储器内的所有

页。

preferred_page_size 指定一页中的字节数。页大小编码为N,其

中页大小为2N字节。这一可编程字段可以为每

一区域指定。注意,该preferred_page_size

被复制到每一长格式页表条目的(ps)字段。

page_table_size 这一可编程字段指示在该页表的线性部分内的

字节数。在短格式页表中,为每一虚区域提供

page_table_size,它决定该虚区域的大小,

因为短格式页表必须为在该虚区域内的每一页

有一个条目。因为短表格式是线性的,不能增

长,因此page_table_size表示短格式页表的

精确大小。在长格式页表中,page_table_size

指示该页表的线性部分的长度,该页表可以随

添加链段向更深处增长。页表大小编码为N,其

中该页表的大小为2N字节。

page_table_base 这一可编程字段指示存储器中第一页表条目的

地址。当使用短格式页表时,每一虚区域包括

它自己的页表并为每一虚区域提供

page_table_base。当使用长格式页表时,提供

单一页表,且单一页表基指示第一长格式页表

条目的地址。注意,只需要存储位

{63:min_pt_size}(见下面)。还要注意,

page_table_base必须位于2page_table_size边界。

impl_va_msb 这一常数指示由该特定计算机系统支持的虚地

址的最高有效位。

min_pt_size 这一常数指示长和短格式页表两者的最小大小

(以字节计)。该最小页表大小表示为N,其中

一个页表的最小大小为2N字节。

如上所述,在基于区域的短格式中,为每一区域的线性页表存在于它自己引用的区域内。其结果,短格式VHPT包括单独的每区域页表,其由page_table_base的位{60:min_pt_size}固定在每一区域。对在其内允许VHPT的区域,需要操作系统来维护一个每区域的线性页表。如在下面的短格式算法中所定义的,使用要被转换的虚地址(VA)、该区域的preferred_page_size、page_table_base和page_table_size来计算对该短格式VHPT的线性索引。

短格式VHPT的大小(page_table_size)定义映射的虚地址空间的大小。在短格式中的最大结构表大小为每区域252字节。为使用4千字节的页映射整个区域(261字节),必须有2(61-12)(或者另写为,249)个页是可映射的。一个短格式VHPT条目为8字节(或者另写为,23字节)大。其结果,最大表大小为每区域2(61-12+3)(或者另写为,252)字节。如果使用该短格式映射一个小于261的地址空间,则可以使用较小的短格式表(page_table_size<52)。使用4千字节的页映射2N的地址空间需要(N-9)的最小page_table_size。

当使用短格式VHPT时,THASH指令(上面已说明)返回一个基于区域的短格式索引。TTAG指令,其也已在上面说明,不用于短格式。在下面的短格式散列算法中,把希望为其得到一个VHPT入口地址的虚地址(VA)传送给函数tlb_vhpt_hash_short。该函数返回相应于该虚地址的条目的地址(vhpt_addr)。

短格式散列算法

1:tlb_vhpt_hash_short(VA)

2:{

3:

hash_page_number=VA{impl_va_msb:0}u>>preferred_page_size;

4:hash_index=hash_page_number;

5:vhpt_offset=hash_index<<3;

6:vhpt_region=VA{63:61};

7:pmask=2page_table_size-1;

8:vhpt_addr=(vhpt_region<<61)|

<!-- SIPO <DP n="15"> -->

<dp n="d15"/>

9:

(((page_table_base{60:min_pt_size}&-pmask{60:min_pt_size})|

10:

(vhpt_offset{60:min_pt_size}& pmask{60:min_pt_size}))<<min_p<br/>

t_size)|

11:vhpt_offset{min_pt_size-1:0};

12:return vhpt_addr;

13:}

在短格式散列算法的第—行,调用叫作函数tlb_vhpt_hash_short,虚地址(VA)传送给该函数。在第三行,通过使用preferred_page_size除VA计算hash_page_number。注意,只使用由特定计算机系统的一种实现使用的VA的那些位(由常数impl_va_msb定义)。通过右移VA N位实现该除法运算,这里页大小为2N。该右移是无符号的。如上所述,在一个实施例中,页大小可以在4千字节到256兆字节的范围之间变化,所以VA将右移12到28位。

在第4行,设定hash_index等于hash_page_number。在该短格式算法中,这一步骤有点冗余,但是包含它进来是为了协调短格式和长格式算法,下面将会看到。如上所述,短格式VHPT中的每一条目是8字节宽。因此在第5行,通过用8乘hash_page_number计算对该页表的偏移(vhpt_offset)。这通过左移hash_index3位执行。

在第六行,计算VHPT的区域(vhpt_region)。如上所述,当使用短格式VHPT时,每一区域包括它自己的VHPT,所以该VHPT的区域和VA的区域相同。因此,该VHPT的区域只是VA的位{63:61)。

在第七行,通过取2的相应于page_table_size的位数的幂减1形成一个掩码(pmask)。例如,为使用最小4千字节的preferred_page_size映射整个区域(261字节),必须有2(61-12)(或者另写为:249)个页可以映射。由于每一短格式VHPT条目是8(或另写为23)字节,因此最大page_table_size是252。在该第一例子中,pma sk的前12位将是“0”,而低52位将是“1”。相似地,为使用最大256兆字节的preferred_page_size映射整个区域(261字节),必须有2(61-28)(或者另写为:233)个页可以映射。由于每一短格式VHPT条目是8(或另写为23)字节,因此最小page_table_size(当映射一个完全的区域时)是236。在该第二例子中,pmask的前28位将是“0”,而低36位将是“1”。当然,还可以映射小于整个261字节的区域,取决于preferred_page_size,其可以产生page_table_size小于236。该掩码用于选择形成相应于VA的VHPT条目的结果地址的分量,其在下面说明。

在第8-11行,通过“或”运算一些分量计算相应于该VA的VHPT的条目的地址(vhpt_addr)。首先,在第8行通过左移vhpt_region61位计算该区域分量,从而把vhpt_region定位在vhpt_addr的合适位置。

在讨论第9-11行之前,考虑min_pt_size是为计算机系统的每一实现定义的常数。常数min_pt_size表示为N,这里该页表的最小大小是2N字节。因此,总知道vhpt_addr的位{min_pt_size-1:0}将由vhpt_offset提供。然而,位{60:min_pt_size}根据page_table_size既可由page_table_base也可由vhpt_offset提供。相应地,使用在第七行计算的pmask根据page_table_size来选择page_table_base和vhpt_offset的合适位。

定义最小页表大小的确减少(在某种程度上)为实现按照本发明的计算机系统需要的逻辑的数量。例如,存放每一page_table_base的寄存器只需要存储位{63:min_pt_size}。另外,下面参考第9和第10行讨论的“与”和“或”运算的宽度可以减少min_pt_size位。在一个实施例中,min_pt_size是15,导致32千字节的最小页表大小。

相应地,在第9行,page_table_base的位{60:min_pt_size}是和pmask的位{60:min_pt_size)的逆的“与”,在第10行,vhpt_offset的位{60:min_pt_size}是和pmask的位{60:min_pt_size}的“与”。两个“与”运算的结果“或”在一起,并将其结果左移min_pt_size位的位置。相应地,第9和第10行使用pmask和min_pt_size形成vhpt_addr的分量,其根据VHPT的大小变化,且已知不是唯一地由vhpt_offset根据min_pt_size提供。注意,把这一分量与在第8行计算的区域分量进行“或”运算。

最后,在第11行,把根据唯一的vhpt_offset(位{min_pt_size-:0})的vhpt_addr的分量和上面计算的其它两个分量进行“或”运算以形成vhpt_addr。在第12行,函数tlb_vhpt_hash_short结束,并返回vhpt_addr给调用子例程。

在短格式VHPT中,每一VHPT条目唯一相应于一个虚地址。然而,在长格式VHPT中,多个虚地址可以共享VHPT的一个初始条目,其存储在VHPT条目中的后面的转换由操作系统链接到该初始条目。在访问该初始条目后,通过检索该初始和链接的条目找到合适的虚拟对物理的转换而形成相应于该虚拟对物理转换的标签(在图7中表示)。长格式算法在下面叙述。注意,为避免混淆,对所有算法使用唯一行号。

长格式散列算法

14:tlb_vhpt_hash_long(VA,region_id)

15:{

16:

hash_page_number=VA{impl_va_msb:0}u>>preferred_page_size;

17:

hash_index=((VA{63:61}<<52|hash_page_number)^region_id;

18:vhpt_offset=hash_index<<5;

19:vhpt_region=page_table_base{63:61};

20:pmask=2page_table_size-1;

21:vhpt_addr=(vhpt_region<<61)|

22:

(((page_table_base{60:min_pt_size}&-pmask{60:min_pt_size})|

23:

(vhpt_offset{60:min_pt_size}& pmask{60:min_pt_size}))<<min_p<br/>

t_size)|

24:vhpt_offset{min_pt_size-1:0};

25:return vhpt_addr;

26:}

在长格式散列算法的第14行,叫作函数tlb_vhpt_hash_long,虚地址(VA)和24位的region_id传送给该函数。在第16行,通过使用preferred_page_size除VA,计算hash_page_number。注意,只使用由特定计算机系统的—种实现使用的VA的那些位(由常数impl_va_msb定义)。通过右移VA N位实现该除法运算,这里页大小为2N。该右移是无符号的。如上所述,在一个实施例中,页大小可以在4千字节到256兆字节的范围之间变化,所以VA将右移12到28位。

在第17行,形成hash_index。如上所述,通过右移VA至少12位形成该hash_page_number。因此,散列页号的最大数目是252,而hash_page_number的位{64:52}为“0”。第17行的第一部分左移VA的位{63:61}(VA的区域部分)52位,并且与hash_page_number进行“或”运算。这增加了长格式VHPT的最大可能大小,从252个条目(散列页号的最大值)到255个条目。最后,第17行的第一部分的结果与24位的region_id进行“异或”运算而形成hash_index。

如上所述,长格式VHPT条目是32(或另写为25)字节。因此,在第18行通过左移hash_index5位的位置形成vhpt_offset。在第19行,通过检索page_table_base的位{63:61}形成vhpt_region。与存在于每—区域中的短格式VHPT不同,为整个系统只定义一个长格式VHPT。

已经在第17-19行计算出hash_index、vhpt_offset、和vhpt_region,于是在第20-24行计算pmask和vhpt_addr。注意,长格式算法的第20-24行和短格式算法的第7-11行相同。因此,以和上面参考短格式算法叙述的同样方式形成vhpt_addr。最后,在第25行,结束函数tlb_vhpt_hash_long,给调用子例程返回vhpt_addr。

注意,当使用长格式VHPT时,vhpt_addr,结合存储在长格式VHPT条目中的标签一起,唯一标识一个虚拟对物理的转换。下面叙述与长格式散列算法一起保证唯一性的标签算法。

标签算法

27:tag(VA,region_id)

28:{

29:pmask=2page_table_size-1;

30:tpn=VA &-pmask;

31:tag_for_entry=(region_id<<40)|(tpn>>12);

32return tag_for_entry;

33:}

按照本发明设计的计算机系统支持长短两种格式的VHPT。如同上面讨论的,优选用硬件实现长和短格式散列算法。如在本技术中公知,总希望使实现一个特定函数而需要的事务处理数目最小,同时使该函数的执行速度最快。

在检查长和短格式算法时,可以发现在这两种算法之间有许多地方相似。按照本发明,下面提供一种组合长短格式算法。通过把长短格式算法组合,实现两种算法所需要的晶体管数目最少,而不明显影响任一种算法的执行速度。下面叙述组合散列算法:

组合散列算法

34:tlb_vhpt_hash_combined(VA,region_id)

35:{

36:

hash_page_number=VA{impl_VA_msb:0}u>>preferred_page_size;

37:if(page_table_format==long){

38:

hash_index=((VA{63:61}<<52)|hash_page_number)^region_id;

39:vhpt_offset=hash_index<<5;

40:vhpt_region=pafe_table_base{63:61};

41:}

42:else{

43:hash_index=hash_page_number;

44:vhpt_offset=hash_index<<3;

45:vhpt_region=VA{63:61};

46:}

47:pmask=2page_table_size-1;

48:vhpt_addr=(vhpt_region<<61)|

49:

(((page_table_base{60:min_pt_size}&-pmask{60:min_pt_size})|

50:

(vhpt_offset{60:min_pt_size}& pmask{60:min_pt_size}))<<min_p

<!-- SIPO <DP n="20"> -->

<dp n="d20"/>

t_size)|

51:vhpt_offset{min_pt_size-1:0};

52:return vhpt_addr;

53:}

基本上,组合散列算法组合了长和短格式散列算法的公共元件,而算法的不同部分在—个IF-THEN-ELSE框内提供,该框测试page_table_format是否设定为“长”格式。因此,在组合散列算法的第34行,调用函数tlb_vhpt_hash_combined,并把虚地址(VA)和24位的region_id传送给该函数。注意,如果page_table_format未设定为“长”格式,则将不使用region_id。在第36行,通过用preferred_page_size去除VA计算hash_page_number,如同在短格式散列算法的第3行和在长格式散列算法的第16行一样。

在第37行,测试page_table_format,看其是否设定为“长”格式。如果是,则分别在第38、39、和40行计算hash_index,vhpt_offset,和vhpt_region,如同在长格式散列算法的第17、18、和19行分别进行的那样。如果page_table_format未设定为“长”格式,则分别在第43、44、和45行计算hash_index,vhpt_offset,和vhpt_region,如同在短格式散列算法的第4、5、和6行分别进行的那样。之后,在第47-52行计算pmask和vhpt_addr并结束该函数(给调用子例程返回vhpt_addr)。注意,第47-52行和短格式散列算法的第7-12行相同,也和长格式散列算法的第20-25行相同。

因此,本发明提供一种组合散列算法,它既能为短格式VHPT(每一VHPT条目唯一标识一个虚拟对物理的转换)产生索引,也能为长格式VHPT(每一初始的VHPT条目与一个存储的标签唯一标识一个虚拟对物理的转换)产生索引。注意,实现本发明的组合算法的人也会发现在该组合散列算法中另外的公共的地方,它们单独为长格式和短格式执行。例如,在第39和44行执行的左移可以通过单一移位电路实现,该电路在page_table_format设定为“长”格式时另外左移两位的位置。类似地,在第40和45行对vhpt_region的计算可以使用多路转换器根据page_table_format从page_table_base或VA中选择位63-61。设计逻辑电路实现本发明的组合散列算法的人也可以认识到使实现本发明所需要的逻辑为最少的其它方式。

虽然参考优选实施例说明了本发明,但是本技术领域熟练的工作人员了解,在形式和细节上可以进行改变而不离开本发明的精神和范围。

Claims (20)

1.一种从虚地址形成引用页表条目的一个入口地址的方法,其中,虚地址包括一个区域部分,它引用标识一个区域的活动区域标识符,该页表能够采取长格式和短格式,所述方法包括:

通过右移该虚地址J位从该虚地址形成一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

如果该页表的格式设定为长格式的话,结合该散列页号和由该虚地址的区域部分引用的区域标识符形成散列索引;

如果该页表的格式设定为长格式的话,左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长;

如果该页表的格式设定为短格式的话,设定散列索引等于散列页号,形成一个散列索引;

如果该页表的格式设定为短格式的话,左移该散列索引L位形成一个表偏移,其中,每一短格式页表条目为2L字节长;

根据该页表的大小形成一个掩码;

使用该页表的基地址和该掩码形成一个第一地址部分;

使用页表偏移和该掩码形成一个第二地址部分;

通过结合第一和第二地址部分形成入口地址。

2.如权利要求1所述方法,另外包括:

如果页表的格式设定为长格式的话,通过从该页表的基地址中减去区域部分形成一个页表区域;

如果页表的格式设定为短格式的话,通过从虚地址中减去区域部分形成一个页表区域;

其中,形成入口地址包括:

通过组合该页表区域与第一和第二地址部分形成入口地址,其中,该页表区域插入该入口地址的区域部分中。

3.如权利要求1所述方法,其中,从虚地址形成散列页号包括:

通过只右移该虚地址已经实现的部分J位而从该虚地址形成散列页号,其中,与该虚地址的区域部分相关的区域的页大小为2K字节。

4.如权利要求1所述方法,其中,如果页表格式设定为长格式的话,通过组合散列页号和由该虚地址的区域部分引用的区域标识符而形成散列索引的步骤包括组合该虚地址的区域部分与该散列页号。

5.如权利要求4所述方法,其中,组合虚地址的区域部分与散列页号的步骤包括在该散列页号中根据右移该虚地址J位已知其为空的散列页号的位位置插入该虚地址的区域部分的位。

6.如权利要求1所述方法,其中,根据页表大小形成掩码包括:

设定该掩码等于2M减1,这里2M是页表大小。

7.如权利要求6所述方法,其中,使用页表的基地址和掩码形成一个第一地址部分包括:

通过对页表的基地址和掩码的逆执行“与”运算形成一个第一地址部分;

使用表偏移和掩码形成一个第二地址部分包括:

通过对该表偏移和掩码执行“与”运算形成一个第二地址部分。

8.如权利要求1所述方法,其中,通过组合第一和第二地址部分形成入口地址包括:

通过对该第一和第二地址部分执行“或”运算形成入口地址。

9.如权利要求1所述方法,其中,已经定义2N字节的最小页表大小,且使用页表的基地址和掩码形成第一地址部分包括:

使用页表的基地址,不包括该页表基地址的低N位,和掩码,不包括该掩码的低N位,形成第一地址部分;

使用表偏移和掩码形成第二地址部分包括:

使用表偏移,不包括该表偏移的低N位,和掩码,不包括该掩码的低N位,形成第二地址部分;和

组合第一和第二地址部分形成入口地址包括:

组合第一和第二地址部分形成一个结果,左移该结果N位,组合该结果与表偏移的低N位,通过上述步骤形成入口地址。

10.一种从虚地址形成引用页表条目的一个入口地址的方法,其中,虚地址包括一个区域部分,它引用标识一个区域的活动区域标识符,页表的最小大小为2N字节,该页表能够采取长格式和短格式,所述方法包括:

通过只右移虚地址已经实现的那些部分J位而形成该虚地址的一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

如果页表的格式设定为长格式的话,通过结合散列页号、虚地址的区域部分、和由该虚地址的区域部分引用的区域标识符而形成一个散列索引,其中,在散列页号中根据右移虚地址J位知其为空的散列页号的位位置插入该虚地址的区域部分的位;

如果页表的格式设定为长格式的话,左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长;

如果页表的格式设定为长格式的话,通过从页表的基地址抽取区域部分形成一个页表区域;

如果页表的格式设定为短格式的话,设定散列索引等于散列页号,形成一个散列索引;

如果页表的格式设定为短格式的话,左移该散列索引L位形成一个表偏移,其中,每一短格式页表条目为2L字节长;

如果页表的格式设定为短格式的话,通过从虚地址中抽取区域部分形成一个页表区域;

通过用2的M次幂减1形成一个掩码,这里,2M是该表的大小;

通过对页表的基地址,不包括该页表基地址的低N位,和掩码的逆,不包括该掩码的逆的低N位,执行“与”运算,形成第一地址部分;

通过对表偏移,不包括该表偏移的低N位,和掩码,不包括该掩码的低N位,执行“与”运算,形成第二地址部分;和

通过对该第一和第二地址部分执行“与”运算形成一个第一结果,左移该第一结果N位形成一个第二结果,对页表区域、该第二结果、和该表偏移的低N位执行“或”运算,形成入口地址,其中,页表区域插入该入口地址的一个区域部分。

11.一个计算机系统,具有定义一个由虚地址寻址的虚地址空间的结构,所述虚地址包括引用标识一个区域的一个活动区域标识符的一个区域部分,所述计算机系统包括:

存储器单元,它包括一个由页表基地址定位的页表,其中,该页表能够采取长格式和短格式;

用于执行指令的处理器,其中,该处理器包括一个页表入口地址产生单元,它能从虚地址产生到该页表的入口地址,该入口地址产生单元包括:

散列页号产生电路,它通过右移虚地址J位形成该虚地址的一个散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

散列索引产生电路,它在页表的格式设定为长格式时,通过结合该散列页号和由该虚地址的区域部分引用的区域标识符形成一个散列索引,而在页表的格式设定为短格式时,通过设定散列索引等于该散列页号,形成一个散列索引;

表偏移产生电路,它在页表的格式设定为长格式时,通过左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长,而在页表的格式设定为短格式时,通过左移该散列索引L位形成一个表偏移,其中每一短格式页表条目为2L字节长;

掩码发生电路,它根据页表大小形成一个掩码;

第一地址部分发生电路,它使用页表基地址和掩码形成一个第一地址部分;

第二地址部分发生电路,它使用表偏移和掩码形成一个第二地址部分;

入口地址发生电路,它通过组合第一和第二地址部分形成入口地址。

12.如权利要求11所述计算机系统,其中,页表入口地址发生单元和处理器另外包括:

页表区域发生电路,它在页表的格式设定为长格式时通过从页表基地址中抽取区域部分而形成一个页表区域,而在页表的格式设定为短格式时通过从虚地址中抽取区域部分而形成该页表区域部分;

入口地址发生电路,它通过组合该页表区域和第一和第二地址部分形成入口地址,其中,页表区域插入入口地址的区域部分。

13.如权利要求11所述计算机系统,其中,散列页号发生电路通过只右移虚地址已经实现的那些部分J位而从虚地址形成散列页号,其中,与该虚地址的区域部分关联的区域的页大小是2J字节;

14.如权利要求11所述计算机系统,其中,如果页表的格式设定为长格式的话,则散列索引发生单元通过组合散列页号、由虚地址的区域部分引用的区域标识符、和虚地址的区域部分形成散列索引。

15.如权利要求14所述计算机系统,其中,散列索引发生单元另外在散列页号中根据右移虚地址J位知其为空的散列页号的位位置插入该虚地址的区域部分的位。

16.如权利要求15所述计算机系统,其中,掩码发生单元通过设定掩码等于2M减1形成该掩码,这里,2M是页表的大小。

17.如权利要求16所述计算机系统,其中,第一地址部分发生电路通过对页表的基地址和掩码的逆执行“与”运算形成第一地址部分,第二地址部分发生电路通过对表偏移和掩码执行“与”运算形成第二地址部分。

18.如权利要求11所述计算机系统,其中,入口地址发生电路通过对第一和第二地址部分执行“或”运算形成入口地址。

19.如权利要求11所述计算机系统,其中,定义了2N字节的最小页表大小,以及第一地址部分发生电路使用页表的基地址,不包括该页表基地址的低N位,和掩码,不包括该掩码的低N位形成第一地址部分,而入口地址发生电路通过组合第一和第二地址部分形成一个结果,左移该结果N位,组合该结果与表偏移的低N位,形成入口地址。

20.一种计算机系统,具有定义一个由虚地址寻址的虚地址空间的结构,所述虚地址包括引用标识一个区域的一个活动区域标识符的一个区域部分,所述计算机系统包括:

存储器单元,它包括一个由页表基地址定位的页表,其中,该页表能够采取长格式和短格式,且具有2N位的最小大小;

用于执行指令的处理器,其中,该处理器包括一个页表入口地址发生单元,它能从虚地址产生到页表的入口地址,该入口地址发生单元包括:

散列页号发生电路,它通过只右移虚地址已经实现的部分J位而从该虚地址形成一个散列页号,其中,与该虚地址的区域部分相关的区域的页大小为2J字节;

散列索引发生电路,它在页表的格式设定为长格式时,通过组合散列页号、虚地址的区域部分、和由该虚地址的区域部分引用的区域标识符形成一个散列索引,其中,在该散列页号中根据右移虚地址J位知其为空的散列页号的位位置组合插入该虚地址的区域部分,而在页表的格式设定为短格式时,通过设定散列索引等于该散列页号,形成一个散列索引;

页表偏移发生电路,它在页表的格式设定为长格式时,通过左移该散列索引K位形成一个表偏移,其中每一长格式页表条目为2K字节长,而在页表的格式设定为短格式时,通过左移该散列索引L位形成一个表偏移,其中每一短格式页表条目为2L字节长;

页表区域发生电路,它在页表的格式设定为长格式时通过从页表基地址中抽取区域部分而形成一个页表区域,而在页表的格式设定为短格式时通过从虚地址中抽取区域部分而形成该页表区域部分;

掩码发生电路,它通过用2的M次幂减1形成一个掩码,这里,2M是该表的大小;

第一地址部分发生电路,它通过对页表的基地址,不包括该页表基地址的低N位,和掩码的逆,不包括该掩码的逆的低N位,执行“与”运算,形成第一地址部分;

第二地址部分发生电路,它通过对表偏移,不包括该表偏移的低N位,和掩码,不包括该掩码的低N位,执行“与”运算,形成第二地址部分;

条目发生电路,它通过对该第一和第二地址部分执行“与”运算形成一个第一结果,左移该第一结果N位形成一个第二结果,对页表区域、该第二结果、和表偏移的低N位执行“或”运算,形成入口地址,其中,页表区域插入该入口地址的一个区域部分。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/430,793 US6393544B1 (en) | 1999-10-31 | 1999-10-31 | Method and apparatus for calculating a page table index from a virtual address |

| US09/430793 | 1999-10-31 | ||

| US09/430,793 | 1999-10-31 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1296224A CN1296224A (zh) | 2001-05-23 |

| CN1186729C true CN1186729C (zh) | 2005-01-26 |

Family

ID=23709057

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00132829.8A Expired - Fee Related CN1186729C (zh) | 1999-10-31 | 2000-10-31 | 从虚地址计算页表索引的方法和装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6393544B1 (zh) |

| EP (1) | EP1096385B1 (zh) |

| JP (1) | JP4268332B2 (zh) |

| CN (1) | CN1186729C (zh) |

| DE (1) | DE60003273T2 (zh) |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6725366B1 (en) * | 2000-09-07 | 2004-04-20 | International Business Machines, Corporation | System and method for 32 bit code branching to 64 bit targets |

| US6947970B2 (en) * | 2000-12-19 | 2005-09-20 | Intel Corporation | Method and apparatus for multilevel translation and protection table |

| US6671791B1 (en) * | 2001-06-15 | 2003-12-30 | Advanced Micro Devices, Inc. | Processor including a translation unit for selectively translating virtual addresses of different sizes using a plurality of paging tables and mapping mechanisms |

| US6807616B1 (en) * | 2001-08-09 | 2004-10-19 | Advanced Micro Devices, Inc. | Memory address checking in a proccesor that support both a segmented and a unsegmented address space |

| US6934796B1 (en) * | 2002-02-01 | 2005-08-23 | Netlogic Microsystems, Inc. | Content addressable memory with hashing function |

| US7382637B1 (en) | 2002-02-01 | 2008-06-03 | Netlogic Microsystems, Inc. | Block-writable content addressable memory device |

| US6697276B1 (en) | 2002-02-01 | 2004-02-24 | Netlogic Microsystems, Inc. | Content addressable memory device |

| US7937554B2 (en) * | 2002-11-12 | 2011-05-03 | Broadcom Corporation | System and method for managing memory |

| KR20040046465A (ko) * | 2002-11-27 | 2004-06-05 | 한국전자통신연구원 | 다단계 해시함수를 이용하여 검색시간 한계를 보장하는분리 체이닝 구조의 데이터 처리 시스템 및 그 처리방법 |

| US7093099B2 (en) * | 2002-12-12 | 2006-08-15 | Alacritech, Inc. | Native lookup instruction for file-access processor searching a three-level lookup cache for variable-length keys |

| US7143272B2 (en) * | 2002-12-27 | 2006-11-28 | Intel Corporation | Using computation histories to make predictions |

| US7069268B1 (en) | 2003-01-13 | 2006-06-27 | Cisco Technology, Inc. | System and method for identifying data using parallel hashing |

| US6983355B2 (en) * | 2003-06-09 | 2006-01-03 | International Business Machines Corporation | Virtualization of physical storage using size optimized hierarchical tables |

| US7581010B2 (en) * | 2003-07-14 | 2009-08-25 | Microsoft Corporation | Virtual connectivity with local connection translation |

| US7509473B2 (en) * | 2003-08-27 | 2009-03-24 | Adaptec, Inc. | Segmented storage system mapping |

| US7720930B2 (en) * | 2003-12-30 | 2010-05-18 | Intel Corporation | Systems and methods using NIC-based prefetching for host TCP context lookup |

| US7272654B1 (en) | 2004-03-04 | 2007-09-18 | Sandbox Networks, Inc. | Virtualizing network-attached-storage (NAS) with a compact table that stores lossy hashes of file names and parent handles rather than full names |

| US7266670B2 (en) * | 2004-06-04 | 2007-09-04 | Faraday Technology Corp. | Method of determining whether a virtual address corresponds to a physical address in a translation lookaside buffer |

| US20060090034A1 (en) * | 2004-10-22 | 2006-04-27 | Fujitsu Limited | System and method for providing a way memoization in a processing environment |

| US7685400B2 (en) * | 2004-12-15 | 2010-03-23 | International Business Machines Corporation | Storage of data blocks of logical volumes in a virtual disk storage subsystem |

| US7886126B2 (en) | 2005-01-14 | 2011-02-08 | Intel Corporation | Extended paging tables to map guest physical memory addresses from virtual memory page tables to host physical memory addresses in a virtual machine system |

| JP4573710B2 (ja) * | 2005-06-16 | 2010-11-04 | 日本電信電話株式会社 | データベース管理装置、データベース管理方法及びデータベース管理プログラム |

| US7657725B2 (en) * | 2005-06-24 | 2010-02-02 | Sigmatel, Inc. | Integrated circuit with memory-less page table |

| FR2902208B1 (fr) * | 2006-06-12 | 2009-07-17 | Touret Richard | Procede de structuration polymorphe et systemique de la memoire associative via un gestionnaire tiers |

| US20080021865A1 (en) * | 2006-07-20 | 2008-01-24 | International Business Machines Corporation | Method, system, and computer program product for dynamically determining data placement |

| US7555628B2 (en) | 2006-08-15 | 2009-06-30 | Intel Corporation | Synchronizing a translation lookaside buffer to an extended paging table |

| US9690790B2 (en) | 2007-03-05 | 2017-06-27 | Dell Software Inc. | Method and apparatus for efficiently merging, storing and retrieving incremental data |

| CN101645043B (zh) * | 2009-09-08 | 2012-01-04 | 成都市华为赛门铁克科技有限公司 | 写数据的方法、读数据的方法及存储设备 |

| US8473684B2 (en) * | 2009-12-22 | 2013-06-25 | International Business Machines Corporation | Delayed replacement of cache entries |

| US8862859B2 (en) * | 2010-05-07 | 2014-10-14 | International Business Machines Corporation | Efficient support of multiple page size segments |

| US8745307B2 (en) | 2010-05-13 | 2014-06-03 | International Business Machines Corporation | Multiple page size segment encoding |

| US8478740B2 (en) | 2010-12-16 | 2013-07-02 | Microsoft Corporation | Deriving document similarity indices |

| US9141523B2 (en) * | 2011-02-25 | 2015-09-22 | Mitsubishi Electric Corporation | Control apparatus, control system, and communication method for controlling one or more motors in serial communication with a controller |

| GB2498571A (en) | 2012-01-20 | 2013-07-24 | Intellectual Ventures Holding 81 Llc | Base station able to communicate with a second device type on a narrow subset frequency band contained within a first main band |

| US9058268B1 (en) | 2012-09-20 | 2015-06-16 | Matrox Graphics Inc. | Apparatus, system and method for memory management |

| US9348757B2 (en) | 2012-10-08 | 2016-05-24 | International Business Machines Corporation | System supporting multiple partitions with differing translation formats |

| US9280488B2 (en) | 2012-10-08 | 2016-03-08 | International Business Machines Corporation | Asymmetric co-existent address translation structure formats |

| US9355040B2 (en) | 2012-10-08 | 2016-05-31 | International Business Machines Corporation | Adjunct component to provide full virtualization using paravirtualized hypervisors |

| US9600419B2 (en) | 2012-10-08 | 2017-03-21 | International Business Machines Corporation | Selectable address translation mechanisms |

| US9355032B2 (en) | 2012-10-08 | 2016-05-31 | International Business Machines Corporation | Supporting multiple types of guests by a hypervisor |

| US9740624B2 (en) | 2012-10-08 | 2017-08-22 | International Business Machines Corporation | Selectable address translation mechanisms within a partition |

| US10216642B2 (en) * | 2013-03-15 | 2019-02-26 | International Business Machines Corporation | Hardware-based pre-page walk virtual address transformation where the virtual address is shifted by current page size and a minimum page size |

| CN103942161B (zh) * | 2014-04-24 | 2017-02-15 | 杭州冰特科技有限公司 | 只读缓存的去冗余系统及方法以及缓存的去冗余方法 |

| JP6406283B2 (ja) * | 2016-03-01 | 2018-10-17 | 日本電気株式会社 | ストレージ装置およびストレージ方法 |

| US10528353B2 (en) | 2016-05-24 | 2020-01-07 | International Business Machines Corporation | Generating a mask vector for determining a processor instruction address using an instruction tag in a multi-slice processor |

| US10248555B2 (en) | 2016-05-31 | 2019-04-02 | International Business Machines Corporation | Managing an effective address table in a multi-slice processor |

| US10467008B2 (en) | 2016-05-31 | 2019-11-05 | International Business Machines Corporation | Identifying an effective address (EA) using an interrupt instruction tag (ITAG) in a multi-slice processor |

| US11341058B2 (en) * | 2018-07-26 | 2022-05-24 | Vmware Inc. | Handling software page faults using data from hierarchical data structures |

| US11481241B2 (en) | 2018-08-30 | 2022-10-25 | Micron Technology, Inc. | Virtual machine register in a computer processor |

| US20200073822A1 (en) * | 2018-08-30 | 2020-03-05 | Micron Technology, Inc. | Security Configuration for Memory Address Translation from Object Specific Virtual Address Spaces to a Physical Address Space |

| US10942863B2 (en) | 2018-08-30 | 2021-03-09 | Micron Technology, Inc. | Security configurations in page table entries for execution domains using a sandbox application operation |

| US11914726B2 (en) | 2018-08-30 | 2024-02-27 | Micron Technology, Inc. | Access control for processor registers based on execution domains |

| US11500665B2 (en) | 2018-08-30 | 2022-11-15 | Micron Technology, Inc. | Dynamic configuration of a computer processor based on the presence of a hypervisor |

| US11544069B2 (en) | 2018-10-25 | 2023-01-03 | Micron Technology, Inc. | Universal pointers for data exchange in a computer system having independent processors |

| CN110365806B (zh) * | 2019-06-06 | 2022-05-10 | 无线生活(杭州)信息科技有限公司 | 网址转换方法及装置 |

| CN113726661B (zh) * | 2021-08-27 | 2022-10-18 | 西安微电子技术研究所 | 一种高性能低功耗的路由哈希器及其控制方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5649142A (en) * | 1991-10-24 | 1997-07-15 | Intel Corporation | Method and apparatus for translating addresses using mask and replacement value registers and for accessing a service routine in response to a page fault |

| US5826057A (en) * | 1992-01-16 | 1998-10-20 | Kabushiki Kaisha Toshiba | Method for managing virtual address space at improved space utilization efficiency |

| US5555387A (en) * | 1995-06-06 | 1996-09-10 | International Business Machines Corporation | Method and apparatus for implementing virtual memory having multiple selected page sizes |

| DE4410060B4 (de) | 1993-04-08 | 2006-02-09 | Hewlett-Packard Development Co., L.P., Houston | Übersetzungsvorrichtung zum Umsetzen einer virtuellen Speicheradresse in eine physikalische Speicheradresse |

| US5630087A (en) * | 1994-11-02 | 1997-05-13 | Sun Microsystems, Inc. | Apparatus and method for efficient sharing of virtual memory translations |

| DE19602872A1 (de) * | 1995-01-27 | 1996-08-08 | Gmd Gmbh | Verfahren zum Betreiben einer Adreßumsetzvorrichtung |

| US5946716A (en) * | 1996-05-30 | 1999-08-31 | Hewlett-Packard Company | Sectored virtual memory management system and translation look-aside buffer (TLB) for the same |

| AUPO194696A0 (en) * | 1996-08-28 | 1996-09-19 | Canon Information Systems Research Australia Pty Ltd | A method of efficiently updating hashed page tables |

| US5809563A (en) * | 1996-11-12 | 1998-09-15 | Institute For The Development Of Emerging Architectures, Llc | Method and apparatus utilizing a region based page table walk bit |

| US5918251A (en) * | 1996-12-23 | 1999-06-29 | Intel Corporation | Method and apparatus for preloading different default address translation attributes |

| US6012132A (en) * | 1997-03-31 | 2000-01-04 | Intel Corporation | Method and apparatus for implementing a page table walker that uses a sliding field in the virtual addresses to identify entries in a page table |

| US6557121B1 (en) | 1997-03-31 | 2003-04-29 | International Business Machines Corporation | Method and system for fault isolation for PCI bus errors |

| US6088780A (en) * | 1997-03-31 | 2000-07-11 | Institute For The Development Of Emerging Architecture, L.L.C. | Page table walker that uses at least one of a default page size and a page size selected for a virtual address space to position a sliding field in a virtual address |

-

1999

- 1999-10-31 US US09/430,793 patent/US6393544B1/en not_active Expired - Lifetime

-

2000

- 2000-10-30 JP JP2000329869A patent/JP4268332B2/ja not_active Expired - Fee Related

- 2000-10-30 EP EP00309543A patent/EP1096385B1/en not_active Expired - Lifetime

- 2000-10-30 DE DE60003273T patent/DE60003273T2/de not_active Expired - Lifetime

- 2000-10-31 CN CN00132829.8A patent/CN1186729C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1296224A (zh) | 2001-05-23 |

| EP1096385A1 (en) | 2001-05-02 |

| DE60003273D1 (de) | 2003-07-17 |

| EP1096385B1 (en) | 2003-06-11 |

| DE60003273T2 (de) | 2004-05-06 |

| US6393544B1 (en) | 2002-05-21 |

| JP4268332B2 (ja) | 2009-05-27 |

| JP2001175536A (ja) | 2001-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1186729C (zh) | 从虚地址计算页表索引的方法和装置 | |

| CN1304960C (zh) | 用于实现文件的写入时复制的方法和系统 | |

| CN1297885C (zh) | 高速缓存数据区段的配置与初始化机制 | |

| CN1174313C (zh) | 多指令集的数据处理 | |

| CN1514374A (zh) | 变更高速缓存数据区段的方法与装置 | |

| CN1101019C (zh) | 数据序列产生方法及设备、转换方法及计算机 | |

| CN1227589C (zh) | 用于保存返回状态的数据处理设备和方法 | |

| CN1254739C (zh) | 处理器和操作处理器的方法 | |

| CN1249585C (zh) | 闪速存储器系统 | |

| CN101031888A (zh) | 用于直接存储器存取地址转换的错误处理 | |

| CN1315017A (zh) | 包含内部引用的两种版本数据表格之间的差别提取 | |

| CN1846200A (zh) | 在处理器中用于减少功耗的微变换检测缓冲器及微标记符 | |

| CN1934543A (zh) | 高速缓冲存储器及其控制方法 | |

| CN1276359C (zh) | 用于检查和操作数据的存储器引擎 | |

| CN1802632A (zh) | 用于在程序代码转换期间执行解释器优化的方法和装置 | |

| CN1791862A (zh) | 操作系统 | |

| CN1251185A (zh) | 具有risc结构的八位微控制器 | |

| CN1672150A (zh) | 用于软件原子化的视图 | |

| CN1881183A (zh) | 信息处理装置、进程控制方法及其计算机程序 | |

| CN1632877A (zh) | 可变延滞时间堆栈快取存储器及提供资料的方法 | |

| CN1898654A (zh) | 高速缓冲存储器及其控制方法 | |

| CN1236455A (zh) | 具有risc结构的八位微控制器 | |

| CN1225690C (zh) | 快取线配置与初始化之装置及方法 | |

| CN1882923A (zh) | 高速缓冲存储器及其控制方法 | |

| CN1265285C (zh) | 预取区段内存以进行储存的装置及方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20050126 Termination date: 20101031 |