CN100495373C - 虚拟先进先出直接存储器存取装置 - Google Patents

虚拟先进先出直接存储器存取装置 Download PDFInfo

- Publication number

- CN100495373C CN100495373C CNB2004101001370A CN200410100137A CN100495373C CN 100495373 C CN100495373 C CN 100495373C CN B2004101001370 A CNB2004101001370 A CN B2004101001370A CN 200410100137 A CN200410100137 A CN 200410100137A CN 100495373 C CN100495373 C CN 100495373C

- Authority

- CN

- China

- Prior art keywords

- unit

- virtual

- dma

- data

- virtual fifo

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Communication Control (AREA)

- Information Transfer Systems (AREA)

- Multi Processors (AREA)

Abstract

一种虚拟先进先出(FIFO)直接存储器存取(DMA)装置,用以装设在具有一处理器、一UART单元及一虚拟FIFO的电子装置中。虚拟FIFO DMA装置中,DMA单元用以将数据在UART单元及虚拟FIFO之间搬移。虚拟FIFO控制器与DMA单元电性连接,虚拟FIFO控制器具有一读取指标与一写入指标。当DMA单元对虚拟FIFO进行读取动作或写入动作时,虚拟FIFO控制器对应地改变读取指标或写入指标的值。虚拟端口分别与DMA单元及处理器电性连接,处理器通过虚拟端口与DMA单元读取虚拟FIFO的数据或将数据写入虚拟FIFO中。

Description

技术领域

本发明涉及一种直接存储器存取(Direct Memory Access,DMA)装置,尤其涉及一种虚拟先进先出(First In First Out,FIFO)DMA装置。

背景技术

请参照第1图,示出了传统电子装置中,使用通用异步收发器(UniversalAsynchronous Receiver/Transmitter,UART)传送数据时的方块图。当高层软件作业程序(Higher layer software task)102欲藉由UART单元110将一第一笔数据传送出去时,高层软件作业程序102先呼叫UART驱动软件(driver),使UART驱动软件将此第一笔数据填入缓冲器104中。缓冲器104例如是环状缓冲器(ring buffer)或是双缓冲器(double buffer)。当此第一笔数据完全地填入缓冲器104之后,UART驱动软件更新UART驱动软件中所设定的一缓冲器指标(buffer point)至下一个地址。然后,通过DMA单元106,储存在缓冲器104中的此第一笔数据被搬移至UART先进先出(First In First Out,FIFO)单元中储存,UART单元110将串行式地(serially)输出此第一笔数据。其中,缓冲器104与UART FIFO单元108之间的数据搬移,除了利用DMA单元106来完成之外,亦可藉由处理器(processor)来达成。通常利用DMA单元106来搬移数据时的效率较佳。

然而,在较复杂的电子装置中,可能会有数个高层软件作业程序102A与中断服务程序(Interrupt Service Routine,ISR)112同时使用同一个UART单元110来进行数据传送的情形,如第2图所示。此种状况下,缓冲器104中的数据很可能被覆盖而导致数据错误。其原因为,在高层软件作业程序102A的第一笔数据正被填入缓冲器104的过程中,若ISR 112亦同时有一第二笔数据需要藉由UART单元110来传送,则ISR 112会呼叫UART驱动软件,以将此第二笔数据存入缓冲器106中。因为之前高层软件作业程序102A的第一笔数据让未完全填入缓冲器104中,故UART驱动软件尚未更新缓冲器指针。故此第二笔数据将会根据原来的缓冲器指标,而被写入缓冲器104中。如此一来,原本已经储存在缓冲器104中的第一笔数据将被覆盖。而当UART驱动软件完成ISR 112的第二笔数据写入缓冲器104的动作之后,高层软件作业程序102A将会继续将其余的第一笔数据填入缓冲器104中,而覆盖掉部分的第二笔数据。此时储存在缓冲器104中第一笔数据与第二笔数据均会有漏失(loss)而产生错误。

传统解决缓冲器104中数据错误的作法有二。其一,在高层软件作业程序102A呼叫UART驱动软件前,先不使能ISR 112,以避免数据错误的情况产生。但是,当有时效性的ISR 112无法执行时,很可能导致系统无法实时对此ISR 112进行处理而产生系统错误。

其二,使用两个缓冲器。请参照第3图,示出了使用两个缓冲器以进行UART传送时的方块图。ISR 112的第二笔数据先储存在缓冲器104A中,而高层软件作业程序102A的第一笔数据则是先储存缓冲器104B中。然后,藉由控制多任务器114,第一笔数据与第二笔数据交替的移动至UART FIFO单元108中,并由UART单元110传送出去。然而,此法需使用较多的存储器来作为缓冲器,而且UART驱动软件的控制亦较为复杂。

除了上述的进行UART传送时会遇到数据漏失与错误的情形之外,进行UART接收时,传统的电子装置亦会有多项问题产生。请参照第4图,示出了传统电子装置中,进行UART接收时的方块图。当UART单元410接收到一第三笔数据之后,第三笔数据先暂存在UART FIFO单元408。然后,由DMA单元406将第三笔数据移动至缓冲器404中。当DMA单元406已将预设长度的数据传送至缓冲器404之后,DMA单元406通知处理器416来读取储存在缓冲器404中的数据。例如,每当DMA单元406将500个字节数据传送至缓冲器404之后,DMA单元406就会通知处理器416读取储存在缓冲器404中的数据。

然而由于UART单元410所接收到的第三笔数据的长度无法预知,故DMA单元406无法得知是否已经将第三笔数据接收完毕。例如,假设第三笔数据的长度为700个字节,当DMA单元406将前500个字节数据传送至缓冲器404之后,DMA单元406就会通知处理器416读取储存在缓冲器404中的数据。但是,当DMA单元406将后200个字节数据传送至缓冲器404之后,由于尚未达到预设的数据长度而且DMA单元406并不知道第三笔数据已经接受完毕,因此DMA单元406不会通知处理器416去读取储存在缓冲器404中的数据。因此,处理器416必须定时地去侦测UART FIFO单元408的状态,以得知UART FIFO单元408是处于空白(empty)状态(因为数据已经被搬移至缓冲器404),并且进一步判断UART FIFO单元408处于空白状态是否达到一预设期间,如果是,则表示数据已经接收完毕,此时,处理器416就会读取缓冲器404中的数据以进行处理。

在处理器416侦测UART FIFO单元408的状态之前,处理器416必须先将DAM单元406非使能(disabled),以免因为DAM单元406的数据搬移动作而使处理器416侦测错误。而在非使能DAM单元406之前,UART单元410必先被非使能,并发出信号以通知传送端禁止传送数据。

但是,若在将DMA单元406非使能的同时,数据正好传入UART单元410,此时,因DMA单元406无法实时地将UART FIFO单元408中的数据移动至缓冲器404中,故极可能导致UART FIFO单元408中的数据满溢(overflow),而使数据遗失。为了避免这样的情况,必须让UART FIFO单元418保留16字节以上的缓冲区,以避免数据遗失。

另一方面,若改用处理器416来移动UART FIFO单元408中的数据至缓冲器404的话,为了避免处理器416因为UART FIFO单元408很快地被填满,而常常被中断来处理数据搬移的动作,故必须加大UART FIFO单元408的大小。但,这样的作法会使成本提高。

总括来说,传统电子装置中,在进行UART传送时,会有UART驱动软件无法实时地更新缓冲器指针,而导致数据被覆盖的数据错误的情形。而在进行UART接收时,则会有(1)处理器416必须定时地去侦测缓冲器404与UART FIFO单元408的状态,而使处理器416效能降低;(2)DMA单元406被非使能时,为了避免UART FIFO单元408产生满溢的情形,UART FIFO单元408必须额外保留16字节的缓冲区,以避免上述的数据满溢的情形。如此,将会提高成本并增加UART FIFO单元408的芯片面积。

发明内容

有鉴于此,本发明的目的就是提供一种虚拟FIFO DMA装置,可于进行UART传送时,实时地更新指标的值,以避免数据被覆盖而导致数据错误。本发明还可于进行UART接收时,不需额外保留UART FIFO单元的16字节的空间,可达到节省成本并降低UART FIFO单元的芯片面积。

根据本发明的目的,提出一种虚拟先进先出(FIFO)直接存储器存取(DMA)装置,装设在一电子装置中,该电子装置具有一处理器、一通用异步收发器(UART)单元及一虚拟FIFO单元,该虚拟FIFO DMA装置包括:一DMA单元,与UART单元及虚拟FIFO单元电性连接,该DMA单元用以将数据在UART单元及虚拟FIFO单元之间搬移;一虚拟FIFO控制器,与DMA单元电性连接,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作;以及一虚拟端口,分别与DMA单元及处理器电性连接,该处理器连接于该虚拟FIFO DMA装置,通过该虚拟端口与DMA单元读取虚拟FIFO单元的数据或将数据写入虚拟FIFO单元中。

根据本发明的另一目的,提出一种电子装置,包括:一虚拟先进先出(FIFO)直接存储器存取(DMA)装置,包括:一DMA单元,与UART单元及虚拟FIFO单元电性连接,该DMA单元用以将数据在UART单元及虚拟FIFO单元之间搬移;一虚拟FIFO控制器,与DMA单元电性连接,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作;以及一虚拟端口,分别与DMA单元及处理器电性连接,一UART单元,与该DMA单元电性连接;一虚拟FIFO单元,与该DMA单元电性连接,该UART单元及该虚拟FIFO单元之间的数据搬移动作由该DMA单元来执行;一处理器,与该虚拟端口电性连接,该处理器通过该虚拟端口与该DMA单元读取该虚拟FIFO单元的数据或将数据写入该虚拟FIFO单元中。

根据本发明的又一目的,提出一种存储器存取方法,应用于一电子装置,该电子装置具有一处理器、一通用异步收发器(UART)单元收发单元,一存储器存取装置虚拟先进先出直接存储器存取(FIFO DMA)装置,以及一数据储存单元虚拟FIFO单元,该存储器存取装置FIFO DMA装置具有一存取单元DMA单元以及一虚拟FIFO控制器,该DMA单元存取单元连接于该UART收发单元及该虚拟FIFO单元数据储存单元之间,用来在该UART收发单元及该虚拟FIFO单元数据储存单元之间进行数据的搬移,该虚拟FIFO控制器连接于该DMA单元存取单元,用来控制该DMA单元存取单元对该虚拟FIFO单元数据储存单元的数据写入或读取动作,该存储器存取方法包括:(a)该UART收发单元接收数据;(b)该DMA单元存取单元将该UART收发单元中的数据移动至该虚拟FIFO单元数据储存单元;以及(c)该处理器经由该DMA单元存取单元读取该虚拟FIFO单元数据储存单元中的数据,其中,该UART单元具有一数据缓存器,该步骤(b)包括:(b1)当该UART单元收满一特定量的数据时,该UART单元发出一要求信号,以通知该DMA单元将该数据缓存器的数据移动至该虚拟FIFO单元中写入指针WP所指向的位置;以及(b2)该DMA单元发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标的值,其中,该虚拟端口具有一外围组件地址,以使该处理器将该虚拟FIFO DMA装置视为一外围组件,该步骤(c)包括:(c1)该处理器发出一读取信号至该虚拟端口,使得该虚拟端口发出一DMA读取要求至该DMA单元;(c2)该DMA单元依照该读取指针来读取该虚拟FIFO单元,以读取一第一数据;(c3)该DMA单元发出一读取通知信号至该虚拟FIFO控制器,使该虚拟FIFO控制器改变该读取指标的值;以及(c4)该DMA单元将该第一数据传送至该虚拟端口,该虚拟端口则将该第一数据传送给该处理器。

根据本发明的又一目的,提出了一种存储器存取方法,应用于一电子装置,该电子装置具有一处理器、一通用异步收发器(UART)单元,一虚拟先进先出直接存储器存取(FIFO DMA)装置,以及一虚拟FIFO单元,该FIFO DMA装置具有一DMA单元以及一虚拟FIFO控制器,该DMA单元连接于该UART单元及该虚拟FIFO单元之间,用来在该UART单元及该虚拟FIFO单元之间进行数据的搬移,该虚拟FIFO控制器连接于该DMA单元,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作,应用于一电子装置,该电子装置具有一处理器、一收发单元,一存储器存取装置,以及一数据储存单元,该存储器存取装置具有一存取单元以及一控制器,该存取单元连接于该收发单元及该数据储存单元之间,用来在该收发单元及该数据储存单元之间进行数据的搬移,该控制器连接于该存取单元,用来控制该存取单元对该数据储存单元的数据写入或读取动作,该存储器存取方法包括:(a)该处理器经由该存取单元将一数据写入至该数据储存单元中;(b)该存取单元将该数据从该数据储存单元,移动至该收发单元;以及(c)该收发单元传送该数据,其中,该UART单元具有一数据缓存器,该虚拟端口具有一外围组件地址,以使该处理器将该虚拟FIFO DMA装置视为一外围组件,该步骤(a)包括:(a1)该处理器将一传送指令与一待传送数据传送至该虚拟端口;(a2)该虚拟端口发出一写入要求至该DMA单元,使该DMA单元依照该写入指针的值将该待传送数据写入该虚拟FIFO单元中;以及(a3)该DMA单元发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标的值;而于该步骤(b)中,该DMA单元依序地将储存于该虚拟FIFO单元中的数据,移动至该UART单元的该数据缓存器中。

为让本发明的上述目的、特征、和优点能更明显易懂,下文特举一较佳实施例,并配合所附图式,作详细说明如下:

附图说明

图1示出了在传统电子装置中,使用通用异步收发器(UniversalAsynchronous Receiver/Transmitter,UART)传送数据时的方块图。

图2示出了当数个高层作业软件程序与中断服务程序(Interrupt ServiceRoutine,ISR)同时使用同一个UART单元来进行数据传送的示意图。

图3示出了使用两个缓冲器以进行UART传送时的方块图。

图4示出了在传统电子装置中,进行UART接收时的方块图。

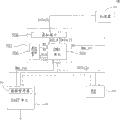

图5示出了依照本发明一较佳实施例的一种虚拟先进先出(First In FirstOut,FIFO)直接存储器存取(Direct Memory Access,DMA)装置的方块图。

图6示出了当UART单元执行数据接收时,使用本发明的虚拟FIFO DMA装置的电子装置的系统方块图。

图7示出了当UART单元执行传送功能时,使用本发明的虚拟FIFO DMA装置的电子装置的系统方块图。

具体实施方式

本发明与图1至图4所示的习知技术的不同之处在于,本发明将电子装置中的存储器中的某一区域做为虚拟FIFO,以取代习知技术中的UART FIFO单元,因此,本发明的UART单元中,并不需配置有UART FIFO单元。如此,可节省UART FIFO单元的成本与芯片面积。电子装置的处理器经由本发明的虚拟FIFO DMA装置来存取虚拟FIFO,以有效地避免数据被覆盖而导致的数据错误。

请参照图5,其绘示依照本发明一较佳实施例的一种虚拟先进先出(FirstIn First Out,FIFO)直接存储器存取(Direct Memory Access,DMA)装置的方块图。本发明的虚拟FIFO DMA装置502,用以装设在一电子装置500中。举例而言,电子装置500是行动电话。电子装置500具有一处理器(Processor)510、一UART单元512及一虚拟FIFO 514。本发明的虚拟FIFO DMA装置502包括有一DMA单元504、一虚拟FIFO控制器506及一虚拟端口(VirtualPort)508。DMA单元504用以与UART单元512及虚拟FIFO 514电性连接,DMA单元504用以将数据在UART单元512及虚拟FIFO 514之间搬移。虚拟FIFO控制器506与DMA单元504电性连接。虚拟FIFO控制器506具有一读取指标RP与一写入指标WP,分别用来指向对虚拟FIFO 514的数据读取位置与数据写入位置。当DMA单元504对虚拟FIFO 514进行读取动作或写入动作时,虚拟FIFO控制器506对应地改变读取指标RP或写入指标WP的值。虚拟端口508分别与DMA单元504及处理器510电性连接,以做为两者的存取接口。处理器510通过虚拟端口508与DMA单元504读取虚拟FIFO 514的数据或将数据写入虚拟FIFO 514中。

请参照图6,示出了当UART单元512执行数据接收时,使用本发明的虚拟FIFO DMA装置502的电子装置500的系统方块图。在电子装置500中,UART单元512与DMA单元504电性连接,虚拟FIFO 514与DMA单元504电性连接,而处理器510与虚拟端口508电性连接。UART单元512具有一数据缓存器516,数据缓存器516的存储器大小例如是1字节(byte)。在电子装置500开机之后,在UART单元512使能之前,处理器510会将存储器中的某一区域设定成虚拟FIFO,并且使能虚拟FIFO DMA装置502,并且发出DMA设定信号DMA_set以将写入指标WP与读取指标RP的初始值设定为该区域的启始位置。

接着,处理器510会使能UART单元512。当UART单元512接收到数据,且UART单元512收满一字节的数据时,UART单元512发出要求信号DMA_req,以通知DMA单元504将数据缓存器516中的数据移动(写入)至虚拟FIFO 514中写入指针WP所指向的位置。此时,DMA单元504会发出一写入通知信号Winc至虚拟FIFO控制器506,以使虚拟FIFO控制器506对应地改变写入指标WP的值。

此外,处理器510可以随时通过虚拟端口508与DMA单元504来读取虚拟FIFO 514的数据。虚拟端口508具有一外围组件地址(peripheral deviceaddress),以使处理器510将虚拟FIFO DMA装置502视为一外围组件。当处理器510欲读取虚拟FIFO 514中的数据时,其会发出一读取信号至虚拟端口508,使得虚拟端口508发出一DMA读取要求(read request)REQ_R至DMA单元504。此时,DMA单元504会依照读取指针RP来读取虚拟FIFO 514,以读取一第一数据DATA(1)。DMA单元504并发出读取通知信号Rinc至虚拟FIFO控制器506,使虚拟FIFO控制器506接着改变读取指标RP的值。然后,DMA单元504将第一数据DATA(1)传送至虚拟端口508,虚拟端口508则将第一数据DATA(1)传送给处理器510。

虚拟FIFO控制器506还具有一流量控制(flow control)功能。当虚拟FIFO514实质上为满态(full)时,虚拟FIFO控制器506使任何写入动作无效,虚拟FIFO控制器506将会指示UART单元512通知传送端停止传送数据。而当虚拟FIFO 514实质上为空态(full)时,虚拟FIFO控制器506使任何读取动作无效。虚拟FIFO 514可额外保留16字节的缓冲区,以满足虚拟FIFO 514为接近满态,且传送端尚未停止传送数据时,DMA单元504仍须将UART单元512中的数据传送至虚拟FIFO 514中时的情况。

在本发明中,由于处理器510经由UART单元512来对虚拟FIFO 514进行存取,而UART单元每收到一个字节数据时就会将数据写入虚拟FIFO 514中,因此即使UART单元512无法预知所接收的数据的长度,且DMA单元504无法得知是否已经将由多个字节所组成的整笔数据接收完毕,处理器510也不需将DMA单元504非使能,而仍可持续通过UART单元512来对虚拟FIFO 514进行存取。再者,由于本发明将存储器中的某一区域设定成虚拟FIFO,因此UART单元512不需额外设置16字节的UART FIFO单元,而可以节省UART单元512的芯片面积。

请参照图7,示出了当UART单元执行传送功能时,UART单元使用本发明的虚拟FIFO DMA装置502的电子装置的系统方块图。在电子装置500中,当处理器510有数据欲通过UART单元512传送时,处理器510将传送指令与待传送数据DATA(2)传送至虚拟端口508。虚拟端口508发出一写入请求(write request)REQ_W至DMA单元504,使DMA单元504依照写入指针WP的值将待传送数据DATA(2)写入虚拟FIFO 514中。同时,DMA单元504发出一写入通知信号Winc至虚拟FIFO控制器506,以使虚拟FIFO控制器506对应地改变写入指标WP的值。然后,DMA单元504依序地将储存在虚拟FIFO 514中的数据,移动至UART单元512中的数据缓存器516中以依序传送出去。

由于所有处理器510对虚拟FIFO 514的写入动作,包括由所有高层作业软件程序与ISR所指示的写入动作,皆经由虚拟FIFO DMA装置502来完成。不管是高层作业软件程序或是ISR所指示的写入动作,处理器510均通过虚拟端口508与DMA单元504来将数据写入虚拟FIFO 514中,并在写入的同时,DMA单元504发出写入通知信号Winc,以指示虚拟FIFO控制器506更新写入指标WP的值。与传统作法的UART驱动软件只能在高层作业软件程序或是ISR所欲写入的整笔数据均写入之后方更新缓冲器指标的值的作法相较,由于本发明的虚拟FIFO控制器506可在数据写入的同时实时地更新写入指标WP的值,故可以避免数据被覆盖的数据错误的情形。

通过本发明的虚拟FIFO DMA装置的使用,UART驱动软件可以将虚拟FIFO视为一个单纯的FIFO单元来进行控制。如此,可以减少UART驱动软件的复杂度。再者,与传统作法相较,本发明将存储器中的某一区域设定成虚拟FIFO,并且利用虚拟FIFO DMA装置来存取该虚拟FIFO,因此无须额外使用UART FIFO单元,故可节省UART单元的芯片面积。

综上所述,虽然本发明已以一较佳实施例揭露如上,然其并非用以限定本发明,任何熟习此技艺者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视后附的申请专利范围所界定者为准。

Claims (19)

1.一种虚拟先进先出(FIFO)直接存储器存取(DMA)装置,装设在一电子装置中,该电子装置具有一处理器、一通用异步收发器(UART)单元及一虚拟FIFO单元,该虚拟FIFO DMA装置包括:

一DMA单元,与UART单元及虚拟FIFO单元电性连接,该DMA单元用以将数据在UART单元及虚拟FIFO单元之间搬移;

一虚拟FIFO控制器,与DMA单元电性连接,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作;以及

一虚拟端口,分别与DMA单元及处理器电性连接,该处理器连接于该虚拟FIFO DMA装置,通过该虚拟端口与DMA单元读取虚拟FIFO单元的数据或将数据写入虚拟FIFO单元中。

2.如权利要求1所述的装置,其中,该虚拟FIFO控制器具有一读取指标与一写入指针,当该DMA单元对该虚拟FIFO单元进行读取动作或写入动作时,该虚拟FIFO控制器对应地改变该读取指标或该写入指标的值。

3.如权利要求2所述的装置,其中,该虚拟FIFO控制器的该读取指标与该写入指标分别用来指向对该虚拟FIFO单元的数据读取位置与数据写入位置,该UART单元具有一数据缓存器,当该UART单元接收到数据,且该UART单元收满一特定量的数据时,该UART单元发出一要求信号,以通知该DMA单元将该数据缓存器的数据移动至该虚拟FIFO单元中写入指针WP所指向的位置,该DMA单元还发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标的值;

其中,该虚拟端口具有一外围组件地址,以使该处理器将该虚拟FIFODMA装置视为一外围组件,当该处理器欲读取虚拟FIFO单元中的数据时,该处理器发出一读取信号至该虚拟端口,使得该虚拟端口发出一DMA读取要求至该DMA单元,该DMA单元将依照该读取指针来读取该虚拟FIFO单元,以读取一第一数据,该DMA单元并发出一读取通知信号至该虚拟FIFO控制器,使该虚拟FIFO控制器改变该读取指标的值,该DMA单元将该第一数据传送至该虚拟端口,该虚拟端口则将该第一数据传送给该处理器。

4.如权利要求3所述的装置,其中,该电子装置为一行动电话。

5.如权利要求2所述的装置,其中,该虚拟FIFO控制器的该读取指标与该写入指标分别用来指向对该虚拟FIFO单元的数据读取位置与数据写入位置,该UART单元具有一数据缓存器,当该处理器有数据欲通过该UART单元传送时,该处理器将一传送指令与一待传送数据传送至该虚拟端口,该虚拟端口发出一写入要求至该DMA单元,使该DMA单元依照该写入指针的值将该待传送数据写入该虚拟FIFO单元中,该DMA单元发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标WP的值,该DMA单元依序地将储存于该虚拟FIFO单元中的数据,移动至该UART单元的该数据缓存器中以依序传送出去。

6.如权利要求2所述的装置,其中,该虚拟端口具有一外围组件地址以使该处理器将该虚拟FIFO DMA装置视为一外围组件,当该处理器读取该虚拟端口时,该虚拟端口发出一DMA读取要求至该DMA单元,该DMA单元依照该读取指针读取该虚拟FIFO单元的一第一数据,该虚拟FIFO控制器改变该读取指标的值,该DMA单元并将该第一数据传送至该虚拟端口,该虚拟端口将该第一数据传送给该处理器;

当该处理器传送待写入的一第二数据至该虚拟端口时,该虚拟端口发出一DMA写入要求至该DMA单元,该DMA单元依照该写入指针将该第二数据写入该虚拟FIFO单元,该虚拟FIFO控制器并改变该写入指标的值。

7.如权利要求2所述的装置,该虚拟FIFO控制器具有一流量控制功能,当该虚拟FIFO单元实质上为满态时,该虚拟FIFO控制器使任何写入动作无效,而当该虚拟FIFO单元实质上为空态时,该虚拟FIFO控制器使任何读取动作无效。

8.一种电子装置,包括:

一虚拟先进先出(FIFO)直接存储器存取(DMA)装置,包括:

一DMA单元,与UART单元及虚拟FIFO单元电性连接,该DMA单元用以将数据在UART单元及虚拟FIFO单元之间搬移;

一虚拟FIFO控制器,与DMA单元电性连接,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作;以及

一虚拟端口,分别与DMA单元及处理器电性连接,

一UART单元,与该DMA单元电性连接;

一虚拟FIFO单元,与该DMA单元电性连接,该UART单元及该虚拟FIFO单元之间的数据搬移动作由该DMA单元来执行;

一处理器,与该虚拟端口电性连接,该处理器通过该虚拟端口与该DMA单元读取该虚拟FIFO单元的数据或将数据写入该虚拟FIFO单元中。

9.如权利要求8所述的电子装置,其中,该虚拟FIFO控制器具有一读取指标与一写入指针,当该DMA单元对该虚拟FIFO单元进行读取动作或写入动作时,该虚拟FIFO控制器对应地改变该读取指标或该写入指标的值。

10.如权利要求8所述的电子装置,其中,该UART单元具有一数据缓存器,当该数据缓存器为满态时,该DMA单元则将该数据缓存器的数据转移至该虚拟FIFO单元中。

11.如权利要求10所述的电子装置,其中,该电子装置为一行动电话。

12.如权利要求8所述的电子装置,其中,该虚拟端口具有一外围组件地址以使该处理器将该虚拟FIFO DMA装置视为一外围组件,当该处理器读取该虚拟端口时,该虚拟端口发出一DMA读取要求至该DMA单元,该DMA单元依照该读取指针读取该虚拟FIFO单元的一第一数据,该虚拟FIFO控制器改变该读取指标的值,该DMA单元并将该第一数据传送至该虚拟端口,该虚拟端口将该第一数据传送给该处理器;

当该处理器传送待写入的一第二数据至该虚拟端口时,该虚拟端口发出一DMA写入要求至该DMA单元,该DMA单元依照该写入指针将该第二数据写入该虚拟FIFO单元,该虚拟FIFO控制器并改变该写入指标的值。

13.如权利要求8所述的电子装置,该虚拟FIFO控制器具有一流量控制功能,当该虚拟FIFO单元实质上为满态时,该虚拟FIFO控制器使任何写入动作无效,而当该虚拟FIFO单元实质上为空态时,该虚拟FIFO控制器使任何读取动作无效。

14.一种存储器存取方法,应用于一电子装置,该电子装置具有一处理器、一通用异步收发器(UART)单元,一虚拟先进先出直接存储器存取(FIFODMA)装置,以及一虚拟FIFO单元,该FIFO DMA装置具有一DMA单元以及一虚拟FIFO控制器,该DMA单元连接于该UART单元及该虚拟FIFO单元之间,用来在该UART单元及该虚拟FIFO单元之间进行数据的搬移,该虚拟FIFO控制器连接于该DMA单元,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作,该存储器存取方法包括:

(a)该UART单元接收数据;

(b)该DMA单元将该UART单元中的数据移动至该虚拟FIFO单元;以及

(c)该处理器经由该DMA单元读取该虚拟FIFO单元中的数据,

其中,该UART单元具有一数据缓存器,该步骤(b)包括:

(b1)当该UART单元收满一特定量的数据时,该UART单元发出一要求信号,以通知该DMA单元将该数据缓存器的数据移动至该虚拟FIFO单元中写入指针WP所指向的位置;以及

(b2)该DMA单元发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标的值;

其中,该虚拟端口具有一外围组件地址,以使该处理器将该虚拟FIFODMA装置视为一外围组件,该步骤(c)包括:

(c1)该处理器发出一读取信号至该虚拟端口,使得该虚拟端口发出一DMA读取要求至该DMA单元;

(c2)该DMA单元依照该读取指针来读取该虚拟FIFO单元,以读取一第一数据;

(c3)该DMA单元发出一读取通知信号至该虚拟FIFO控制器,使该虚拟FIFO控制器改变该读取指标的值;以及

(c4)该DMA单元将该第一数据传送至该虚拟端口,该虚拟端口则将该第一数据传送给该处理器。

15.如权利要求14所述的方法,其中,该虚拟FIFO控制器具有一读取指标与一写入指针,当该DMA单元对该虚拟FIFO单元进行读取动作或写入动作时,该虚拟FIFO控制器对应地改变该读取指标或该写入指标的值。

16.如权利要求14所述的方法,其中,该电子装置为一行动电话。

17.一种存储器存取方法,应用于一电子装置,该电子装置具有一处理器、一通用异步收发器(UART)单元,一虚拟先进先出直接存储器存取(FIFODMA)装置,以及一虚拟FIFO单元,该FIFO DMA装置具有一DMA单元以及一虚拟FIFO控制器,该DMA单元连接于该UART单元及该虚拟FIFO单元之间,用来在该UART单元及该虚拟FIFO单元之间进行数据的搬移,该虚拟FIFO控制器连接于该DMA单元,用来控制该DMA单元对该虚拟FIFO单元的数据写入或读取动作,该存储器存取方法包括:

(a)该处理器经由该存取单元将一数据写入至该数据储存单元中;

(b)该存取单元将该数据从该数据储存单元,移动至该收发单元;以及

(c)该收发单元传送该数据,

其中,该UART单元具有一数据缓存器,该虚拟端口具有一外围组件地址,以使该处理器将该虚拟FIFO DMA装置视为一外围组件,该步骤(a)包括:

(a1)该处理器将一传送指令与一待传送数据传送至该虚拟端口;

(a2)该虚拟端口发出一写入要求至该DMA单元,使该DMA单元依照该写入指针的值将该待传送数据写入该虚拟FIFO单元中;以及

(a3)该DMA单元发出一写入通知信号至该虚拟FIFO控制器,以使该虚拟FIFO控制器对应地改变该写入指标的值;

而于该步骤(b)中,该DMA单元依序地将储存于该虚拟FIFO单元中的数据,移动至该UART单元的该数据缓存器中。

18.如权利要求17所述的方法,其中,该虚拟FIFO控制器具有一读取指标与一写入指针,当该DMA单元对该虚拟FIFO单元进行读取动作或写入动作时,该虚拟FIFO控制器对应地改变该读取指标或该写入指标的值。

19.如权利要求17所述的方法,其中,该电子装置为一行动电话。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CNB2004101001370A CN100495373C (zh) | 2003-12-05 | 2004-12-02 | 虚拟先进先出直接存储器存取装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN200310120798 | 2003-12-05 | ||

| CN200310120798.5 | 2003-12-05 | ||

| CNB2004101001370A CN100495373C (zh) | 2003-12-05 | 2004-12-02 | 虚拟先进先出直接存储器存取装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1641613A CN1641613A (zh) | 2005-07-20 |

| CN100495373C true CN100495373C (zh) | 2009-06-03 |

Family

ID=34888157

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2004101001370A Active CN100495373C (zh) | 2003-12-05 | 2004-12-02 | 虚拟先进先出直接存储器存取装置 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN100495373C (zh) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103678205B (zh) * | 2013-12-30 | 2017-01-04 | 杭州士兰微电子股份有限公司 | 基于dma的实时流数据传送系统及方法 |

| CN105786733B (zh) * | 2014-12-26 | 2020-08-07 | 南京中兴新软件有限责任公司 | 一种写入tcam条目的方法及装置 |

| CN110515872B (zh) * | 2018-05-21 | 2020-07-31 | 阿里巴巴集团控股有限公司 | 直接内存存取方法、装置、专用计算芯片及异构计算系统 |

| KR20210012825A (ko) * | 2019-07-26 | 2021-02-03 | 에스케이하이닉스 주식회사 | 저장 장치 및 그 동작 방법 |

-

2004

- 2004-12-02 CN CNB2004101001370A patent/CN100495373C/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN1641613A (zh) | 2005-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7698474B2 (en) | Virtual first in first out (FIFO) direct memory access (DMA) device, electronic device and memory access method using the same | |

| US6073190A (en) | System for dynamic buffer allocation comprising control logic for controlling a first address buffer and a first data buffer as a matched pair | |

| EP0732659B1 (en) | Controlling (n+i) I/O channels with (n) data managers in a homogeneous software programming environment | |

| US5247616A (en) | Computer system having different communications facilities and data transfer processes between different computers | |

| US8683093B2 (en) | Memory system having high data transfer efficiency and host controller | |

| CN1554050B (zh) | 具有自适应优先权控制器的数据处理器及其方法 | |

| US5819111A (en) | System for managing transfer of data by delaying flow controlling of data through the interface controller until the run length encoded data transfer is complete | |

| WO2008079468A1 (en) | Serial advanced technology attachment (sata) and serial attached small computer system interface (scsi) (sas) bridging | |

| US5937200A (en) | Using firmware to enhance the functionality of a controller | |

| JPS59100964A (ja) | ディスク制御システム及びその並列データ転送方法 | |

| EP1131732B1 (en) | A direct memory access engine for supporting multiple virtual direct memory access channels | |

| JPH0827707B2 (ja) | Fifoバッファの制御装置及び制御方法並びにデータ転送を制御する装置 | |

| EP0325856B1 (en) | Interface circuit for data transfer between processor and input/output device | |

| US5062073A (en) | Input output control system using a fifo to record access information of control registers by a master device | |

| CN100495373C (zh) | 虚拟先进先出直接存储器存取装置 | |

| US7409486B2 (en) | Storage system, and storage control method | |

| US6484218B1 (en) | Method for improving direct memory access performance | |

| EP0632626B1 (en) | Method and system for interrupt responsive execution of communications protocols | |

| US8996772B1 (en) | Host communication device and method with data transfer scheduler | |

| JPS6138510B2 (zh) | ||

| US7506079B2 (en) | Data processor and data communication method | |

| JPH02129746A (ja) | 入出力チャネル装置 | |

| CN1323529C (zh) | 一种数字信号处理器内部数据传输的方法 | |

| CN1234550B (zh) | 一种输入/输出总线系统 | |

| KR100633120B1 (ko) | 저장 매체의 데이터 대역폭 향상 방법 및 이를 위한 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |