JP3686155B2 - 画像復号装置 - Google Patents

画像復号装置 Download PDFInfo

- Publication number

- JP3686155B2 JP3686155B2 JP06438596A JP6438596A JP3686155B2 JP 3686155 B2 JP3686155 B2 JP 3686155B2 JP 06438596 A JP06438596 A JP 06438596A JP 6438596 A JP6438596 A JP 6438596A JP 3686155 B2 JP3686155 B2 JP 3686155B2

- Authority

- JP

- Japan

- Prior art keywords

- bank

- data

- pixel

- pixel data

- address

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/36—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the display of a graphic pattern, e.g. using an all-points-addressable [APA] memory

- G09G5/39—Control of the bit-mapped memory

- G09G5/393—Arrangements for updating the contents of the bit-mapped memory

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/42—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation

- H04N19/423—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation characterised by memory arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/61—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding in combination with predictive coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N11/00—Colour television systems

- H04N11/04—Colour television systems using pulse code modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/41—Structure of client; Structure of client peripherals

- H04N21/426—Internal components of the client ; Characteristics thereof

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/76—Television signal recording

- H04N5/907—Television signal recording using static stores, e.g. storage tubes or semiconductor memories

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

- Memory System (AREA)

- Color Television Systems (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

この発明は符号化された画像データを復号してもとの画像データを復元する画像復号装置に関し、特に、符号化された動画像データを復号し、かつ表示する画像復号表示装置に関する。

【0002】

【従来の技術】

フレーム間予測符号化は、膨大なデータ量を有する動画像を符号化するためによく用いられる手法である。このフレーム間予測符号化とは、動画像の時間的相関を利用する符号化手法であり、時間的に近接するフレーム(参照フレーム)に基づいて現在符号化しているフレームの画像データ(現画像データ)を予測し、その予測値と現画像データの差分(予測誤差)を符号化する。参照画像と現画像の時間的相関が強い場合には、この差分は小さい値となるため、伝送すべきデータ量を低減することができ、情報の圧縮が効果的に行なわれる。予測に用いられるフレーム(またはフィールド)としては、現フレーム(またはフィールド)に対し時間的に前のフレーム(またはフィールド)および後のフレーム(またはフィールド)の両方が用いられる。

【0003】

このような予測符号化方式の1つに、動画像を対象とする国際標準であるMPEG規格がある。このMPEG規格の画像データの符号化および復号化方式は、たとえば、日経エレクトロニクス、1994年3月14日号の第82頁ないし第116頁に解説されている。

【0004】

図41は、MPEG規格に従うフレーム間予測符号化を説明するための図である。図41においては、符号化および復号化された画像の時間的配列が示される。図41において、9枚の画像G1〜G9が代表的に示される。図41において参照画像(フレームまたはフィールド)と現画像の関係を矢印で示す。矢印の先が現画像であり、矢印のもとが参照画像である。

【0005】

画像G3は、Iピクチャーであり、フレーム間予測符号化を用いずに符号化が行なわれる。すなわち、Iピクチャーは、フレーム内またはフィールド内符号化され、その画素データそのものが符号化される画像である。画像G6およびG9は、Pピクチャーであり、過去の再生画像を用いてフレーム間またはフィールド間予測符号化処理される画像である。画像G1,G2,G4,G5,G7およびG8は、Bピクチャーである、過去および未来の再生画像のいずれかまたは両者の再生画像を用いて予測符号化される画像である。Bピクチャーは、IピクチャーおよびPピクチャーまたはPピクチャーおよびPピクチャーの組を用いて予測符号化される。Bピクチャーは予測符号化時および復号化時においては参照画像として用いられない。図41において、BピクチャーG1およびG2は、時間的に後に位置する未来の画像(Iピクチャー)G3を用いて予測符号化される。BピクチャーG4およびG5は、時間的に前に位置する過去の再生画像であるIピクチャーG3と、時間的に後に位置する未来の再生画像であるPピクチャーG6の両者を用いて予測符号化される。BピクチャーG7およびG8は、過去の再生画像であるPピクチャーG6と未来の再生画像であるPピクチャーG9を用いて予測符号化される。

【0006】

図42は、1枚の画像の構成を概略的に示す図である。図42においては、NTSCサイズの画像の構成が示される。1枚のNTSCサイズの画像は、輝度信号(Y)については、水平方向720画素、垂直方向480画素を含み、2種類の色差信号CbおよびCrそれぞれについては、水平方向360画素、かつ垂直方向240画素を含む。ここで、「画素」は、「画像信号」のサンプル点を示す。また「画像データ」は1枚の画像全体のデータを示す。

【0007】

図42において拡大して示すように、輝度信号(Y)のサンプル位置(白丸印で示す)は、画像画面上水平方向に整列して配置され、一方、色差信号(Cb,Cr)それぞれは、水平方向および垂直方向それぞれについて輝度信号の2画素に対して1つの色差信号画素が存在する。すなわち、色差信号CbおよびCrのサンプリング周波数は、輝度信号Yのサンプリング周波数の1/4となり、この符号化方式は、「4:2:0符号化方式」と呼ばれている。

【0008】

図43(A)および(B)は、画像復号処理を説明するための図である。図43(A)において、画像の復号処理は、マクロブロック(MB)と呼ばれる所定のサイズを有する画素群を単位として復号処理(符号化処理も同様)が行なわれる。通常このマクロブロックは、輝度信号については16×16画素のサイズを有し、色差信号CbおよびCrそれぞれについては8×8画素のサイズを備える。この輝度信号Yのマクロブロックは、通常、8×8画素の4つのブロックに分割される。MPEG規格における復号処理においては、図43(B)に示すように、動きベクトルMVと呼ばれるパラメータが利用される。この動きベクトルMVは、復号中のフレームFPにおいて、復号されるブロックMBと参照フレームFRにおいて、最も相関関係の強い参照ブロック(予測ブロック)MBRの変位を示す。復号処理においては、復号中のフレームFPのマクロブロックMBに対し、動きベクトルMBで指定される参照フレームFR内の予測ブロックMBRの画素データ(参照データ)との加算が行なわれ、このマクロブロックMBの各画素データの復元が行なわれる。

【0009】

符号化された画像データを復号(して表示)する装置においては、復号後の画像データを格納するために、外部にメモリが必要とされる。図41に示すように、Bピクチャーの復号のためには、過去および未来の2枚の画像データが必要とされる。Bピクチャーは参照画像としては用いられないが、転送される画像データはフレーム順序が入れ換えられているため(未来からの動き補償を可能にするため、時間的に後の画像が伝送順序においては先に送られる)、正しい時間順序に直すために、このBピクチャーデータも外部メモリに格納する必要がある。また、復号された画像データについてはマクロブロック単位で画素データが与えられ、一方表示は、ラスター走査順(図42の水平方向に沿って順に画素データを表示し、1ラインの表示完了後次の行の画素データの表示を行なう)で行なうため、この画素データの順序を変換する必要があり、また参照画像が表示される前に、新たに復元された画像データで書換えられるのを防止するために、外部メモリとしては、少なくとも3フレームの画像データを格納する記憶容量を有することが要求される。NTSCサイズ画像においては、フレームの輝度信号は720・480画素を有し、また色差信号CbおよびCrは、それぞれ360・240画素を有する。1画素データが8ビットで表現される場合、1フレームのデータ量はしたがって720・480・8×1.5=3.96Mビットと約4Mビットとなる。ここで、係数1.5は、2種類の色差信号CbおよびCrの画素数を考慮している。したがって、外部メモリとしては、12Mビット以上の大きな記憶容量が要求される。

【0010】

また、画像復号表示装置においては、外部メモリに対するアクセスの種類として、復元された画像データの書込、復号処理時における予測画像(参照画像)データの読出、および表示画像の読出という動作がある。復号処理時においては、MPEG規格によれば、最大4つの動きベクトルが必要とされ、NTSCサイズの30フレーム/秒の表示速度の場合、外部メモリに対し行なわれるデータ転送の総量は、約100Mバイト/秒にも達する。

【0011】

このような大きなデータ転送帯域を確保する1手法として、データ幅の拡張がある。たとえば、ページモードアクセスが20MHzで行なえるデータ幅16ビットの4MビットDRAMを、4個並列に接続し、データ幅を64ビットとする。この構成に従えば、単純に計算して、20MHz・8バイト=160Mバイト/秒のデータ転送能力が確保されることになり、前述の要求されるデータ転送帯域に対する要求性能を満足することができる。

【0012】

【発明が解決しようとする課題】

上記の4MビットDRAMを4つ並列に接続する構成の場合、1ワードが8バイトとなり、同時に8画素のデータを転送することができる。しかしながら、画像データ復元時において参照ブロックの画素データを読出す場合、動きベクトルの値により不必要な画素データが数多く読出される場合が生じる。

【0013】

図44に示すように、水平方向に整列して配置される画素0〜24…を考える。1ワードは8個の画素データで構成される。したがって、画素0〜7が同時に読出され、また画素8〜画素15が1ワードとして同時に読出される。輝度信号参照ブロックが、画素7ないし画素22で構成される場合を考える。この場合、必要とされる参照ブロックの画素データを読出すためには、画素0〜画素7からなるワード、画素8〜画素15からなるワード、および画素16〜画素23からなるワードの3ワードを読出し、画素0〜画素6および画素23を切捨てる操作が必要とされる。すなわち、16画素のデータを読出す場合、3ワードを読出す必要がある。1ワードが8バイトで構成されており、8個の画素単位で画素データが読出されるためである。したがって、このような参照ブロックの画素データ読出時において不必要な画素データが読出され、データ転送効率が悪くなるという問題が生じる。

【0014】

また、参照ブロックにおいて、画素ラインを切換える場合、DRAMにおいては、通常、同じロウアドレスの位置に、1画素ラインの画素データが配置されるため、したがって、画素ラインを切換える場合には、ロウアドレスを変更する必要があり、この場合、行切換のためにページモードアクセスが利用することができず、行切換(ページ切換)のためのオーバヘッドが生じ、データ転送効率が劣化する。

【0015】

さらに、最近、16MビットDRAMが広く利用されてきている。このような16MビットDRAMを用いれば、用いられるメモリの数を低減することができ、装置占有面積の低減およびコスト低減(1個の16MビットDRAMの価格は、4MビットDRAM4個の価格よりも低い)が実現される。しかしながら、16MビットDRAMの場合、そのI/O構成(データ幅)は、通常最大16ビットであり、したがって前述の100Mバイト/秒という要求される広いデータ転送帯域(バンド幅)を実現することができない。

【0016】

前述のようなダイナミック・ランダム・アクセス・メモリ(DRAM)を用いる手法に代えて、高速メモリを採用する手法がある。特に、近年汎用CPU(中央処理装置)の高性能化に従って、汎用DRAM(ダイナミック・ランダム・アクセス・メモリ)とCPUとの動作速度の差が顕著となり、汎用DRAMのデータ転送能力不足が問題となっている。すなわち、汎用DRAMのデータ転送能力に併わせてCPUのウェイト時間が長くなり、したがって汎用DRAMのデータ転送能力不足がシステム性能に対する1つのボトルネックとなるという問題が生じてきている。このような汎用DRAMのデータ転送能力不足を解決することを目的とする高速DRAMが種々実現されている。このような高速DRAMの1つに、シンクロナスDRAM(同期式DRAM:以下、SDRAMと称す)がある。

【0017】

図45は、SDRAMの構成を概略的に示す図である。図45において、SDRAMは、2つのバンクBKAおよびBKBと、クロック信号CLKに同期して選択状態とされたバンク(BKAまたはBKB)のデータの入出力を行なう入出力回路RDを含む。AバンクBKAおよびBバンクBKBは、互いに独立に活性状態への駆動およびプリチャージ状態への駆動を行なうことができ、またこれらのバンクBKAおよびBKBは、行列状に配列されるダイナミック型メモリセルを含む。クロック信号CLKはたとえばシステムクロックであり、周波数66MHzないし100MHzと高速である。バンクBKAおよびBKBは、それぞれ、メモリ番地は、2次元のアドレスすなわちロウアドレスおよびコラムアドレスにより指定される。同じロウアドレス(以下同じページと称す)のデータは高速に連続してアクセスすることが可能である。ロウアドレスにより、1ページのメモリセル(またはワード線)が指定されて選択状態とされて、この選択ページのデータが、周知のように、センスアンプによりラッチされているためである。1つのバンクにおいて、異なるページのデータをアクセスする場合には、ロウアドレスを変更する必要がある(別のワード線を選択状態とする必要がある)。この別のロウアドレスの指定のためには、汎用DRAMと同様、選択状態とされた行(ワード線)を非選択状態とした後に再び別のロウアドレスに対応する行(ワード線)を選択状態へ駆動する必要があり、したがって、1つのバンクにおいて、ページ変更のためにはある時間が必要とされる。これらのロウアドレス変更のためのオーバヘッドを解消するために、図45に示すように、SDRAMにおいては、AバンクBKAおよびBバンクBKBが設けられる。一方のバンクへのアクセス時に、他方のバンクを選択状態へ駆動し、一方のバンクのロウアドレス変更時に他方のバンクへアクセスすることにより、このロウアドレス変更のオーバヘッドを解消することが図られる。しかしながら、以下に説明するように、このSDRAMのバンク構成を利用して高速データ転送を実現するためには、バンクBKAおよびBKBにおける画素データの配置に対し工夫が必要とされる。

【0018】

たとえば、図46(A)に示すように、AバンクおよびBバンクそれぞれに対し、交互に画素ラインの画素データを格納することを考える。すなわち、1枚の画像データにおいて、奇数ラインの画素データをAバンクに格納し、偶数ラインの画素データをBバンクに格納する。この場合、ラスター走査方式に従って順次画素データを読出す場合には、SDRAMのバンク構成の特徴を活かして、高速でデータの転送を行なうことができる。しかしながら、図46(B)に示すように、画素ラインには輝度信号画素は720画素配置され、色差信号Cb,Crの画素はそれぞれ360画素配置される。通常16MビットSDRAMのコラムアドレスは256(0〜255)であり、1コラムアドレスのメモリ位置に16ビットのデータを格納することができたとしても、720画素の全てを1ページに格納できない。

【0019】

図47は、SDRAMのデータ読出シーケンスを示す図である。図47に示すように、SDRAMにおいては、このSDRAMが実行すべき動作指令はコマンドの形で与えられる。このコマンドは、クロック信号の立上がりまたは立下がりの一方で取込まれてデコードされてSDRAMの実行すべき動作が決定される。

【0020】

アクティブコマンドは、SDRAMにおいて、バンクを指定して、指定されたバンクにおいてページを選択する動作を指定する。このアクティブコマンドは、また指定されたバンクにおける、メモリサイクルの始まりを指定する。このアクティブコマンドに従ってページが選択状態とされ、すなわち指定されたバンクにおいてワード線が選択状態とされ、メモリセルデータが内部の列(ビット線対)上に読出されてセンスアンプで検知され増幅されてラッチされる。このアクティブコマンドが与えられてから選択されたメモリセルのデータが検知されてラッチされるまでに2クロックサイクル必要とされる。

【0021】

リードコマンドは、データ読出動作を指定する。このリードコマンドは、また同時にデータ読出を受けるバンクおよび列を指定する(リードコマンドと同時にコラムアドレスおよびバンクアドレスが与えられる)。このリードコマンドにより選択された列のデータ(ワード)が読出される。

【0022】

プリチャージコマンドは、バンクを指定し、この指定されたバンクを非選択状態へ駆動する。SDRAMにおいては、非選択時においては、内部の信号線はすべて所定の電位にプリチャージされる。このプリチャージコマンドにより指定されたバンクにおいてすべての信号線がプリチャージ状態に復帰するまでに、2クロックサイクルが必要とされる。したがって、プリチャージコマンドとアクティブコマンドとの間には、最低2クロックサイクル必要とされる。1つのバンクにおいてページの変更を行なう場合、プリチャージコマンドを与えてから、再びアクティブコマンドを与える必要がある。したがって、このページ変更のためには、最低4クロックサイクルが必要とされる。他方のバンクにおいてデータが読出されている場合、この4クロックサイクル、すなわち4ワードのデータよりも少ないデータしか読出されない場合、このページ変更を行なう前に、他方のバンクのデータ(破線ブロックで示す)がすべて読出された場合、ページ変更に必要とされるクロックサイクルすべてを利用してデータを読出すことができず、結果としてページ変更のオーバヘッドをすべて隠すことができず、高速データ転送を実現することができなくなる。

【0023】

それゆえ、この発明の目的は、効率的にデータ転送を行なうことのできる同期式メモリを備える画像復号装置を提供することである。

【0024】

この発明の他の目的は、同期式メモリの有するデータ転送能力を最大限に発揮して効率的にデータ転送を行なうことのできる画像復号装置を提供することである。

【0025】

【課題を解決するための手段】

請求項1に係る画像復号装置は、互いに独立にメモリセル選択動作を行うことのできる第1および第2のバンクを有し、クロック信号に同期してデータの入出力が行われる同期型メモリ素子と、符号化された画像データに含まれるサンプル画素データを受けて復号してもとの画像データを復元するための復号手段と、この復号手段により復元された画像データを同期型メモリ素子へ格納するための制御手段とを備える。この制御手段は、第1の信号成分について画像上水平方向に一列に配列される画素データが、連続して隣接する2個の画素を単位として交互に第1および第2のバンクに格納されるように復号手段からの画像データに含まれる画素データを同期型メモリ素子へ書込む手段を含む。

【0026】

請求項2に係る画像復号装置は、請求項1の装置において、画素データが、互いに種類が異なり、かつサンプル数の等しい第2および第3の信号成分を含む。

【0027】

請求項2に係る画像復号装置は、さらに、制御手段が、第2および第3の信号成分について同じサンプル画素の第2および第3の信号成分が第1および第2のバンクの同じアドレス位置に格納されるように画像データに含まれる画素データを同期型メモリ素子へ書込む手段を含む。

【0028】

請求項3に係る画像復号装置は、同期式メモリ素子が、Mビットを1ワードとしてワード単位でデータの入出力を行ない、画素データの輝度信号線分は、M/2ビットデータであり、2つの隣接画素を単位として交互に第1および第2のバンクに画素データが格納される。

【0029】

請求項4に係る画像復号装置は、請求項1の装置において、同期型メモリ素子がMビットを1ワードとしてワード単位でデータの入出力を行い、画素データの輝度信号成分がMビットデータであり、2画素ごとに交互に第1および第2のバンクへ画素データが格納される。

【0030】

請求項5に係る画像復号装置が、請求項1の装置にいおて、同期式メモリ素子は、Mビットワードをワード単位で入出力し、画素データはNビットデータあり、復号手段は、水平方向のサイズがLないしL+1の画素ブロックを参照画像ブロックとして画像データを復元する手段を含み、また制御手段はP回を単位として交互に第1および第2のバンクへアクセスして画素データを読出して復号手段へ与える手段を含む。Pは、(L+1)/(2・M/N)以上の整数でありかつ連続して1つのバンクに対しアクセスされるワードの回数を示す。

【0031】

請求項6に係る画像復号装置は、請求項2の装置において、同期式メモリ素子がMビットワードをワード単位で入出力し、画素データはNビットデータであり、復号手段は水平方向のサイズがLないし(L+1)の画素ブロックを参照画素ブロックとして画像データを復元する手段を含み、制御手段はP回を単位として交互に第1および第2のバンクへアクセスして画素データを読出して復号手段へ与える手段を含む。Pは(L+1)/(M/N)以上の整数であり、かつ1つのバンクに対し連続してアクセスされる回数を示す。

【0032】

請求項7に係る画像復号装置は、請求項5または6の装置において、制御手段が表示装置上での表示のためにP回を単位として交互に第1および第2のバンクへアクセスして画素データを読出す手段をさらに備える。

【0033】

請求項8に係る画像復号装置は、請求項1または2の装置において、同期式メモリ素子が16ビットデータを1ワードとしてワード単位でデータの入出力を行ない、画素データは8ビットデータであり、制御手段は5ワード単位で交互に第1および第2のバンクへアクセスする手段を含む。

【0034】

請求項9に係る画像復号装置は、請求項1または2の装置において、同期式メモリ素子が8ビットデータを1ワードとしてワード単位でデータの入出力し、画素データは8ビットデータであり、制御手段は9ワード単位で交互に第1および第2のバンクをアクセスする手段を含む。

【0035】

請求項10に係る画像復号装置は、請求項1ないし9のいずれかの装置において、同期式メモリ素子の1つの行アドレスの記憶位置に画像上水平方向の少なくとも1ライン上の画素データすべてを格納するようにアドレスを発生する手段を含む。

【0036】

請求項11に係る画像復号装置は、請求項1ないし10のいずれかの装置において、さらに画像データ以外のデータを2Qワードを単位としてデータ配列順序に従ってQワードずつ交互に第1および第2のバンクへ格納する手段を含む。

【0037】

請求項12に係る画像復号装置は、請求項11の装置において、Qは4であり、4ワードずつ交互に第1および第2のバンクへ画像データ内のデータがデータ配列順序に従って格納される。

【0038】

請求項13に係る画像復号装置は、請求項1の装置において、制御手段は同期式メモリ素子に対しワードのアドレスとして、最下位ビット位置をバンク指定アドレスビット位置としかつ上位ビットをバンク内列位置を示す列特定アドレスとする列アドレスを各ワードが有するように各画素データに対するアドレスを生成する手段を含む。

【0039】

請求項14に係る画像復号装置は、請求項1の装置において、制御手段がワードのアドレスとして、最下位から2番目のビットをバンク指定アドレスビットとし、残りのビット列指定アドレスビットとして有する列アドレスを生成する手段を含む。

【0040】

請求項15に係る画像復号装置は、請求項2の装置において、制御手段が、ワードのアドレスとして色差信号特定信号としてバンク特定ビットを含むアドレス信号を生成する手段を含む。

【0041】

請求項16に係る画像復号装置は、請求項1の第1の信号成分が輝度信号成分である。

【0042】

請求項17に係る画像復号装置は、請求項2の第2および第3の信号成分が色差信号成分である。

【0043】

最大2画素の隣接画素を単位として交互に第1および第2のバンクへ格納することにより、ページ変更時においては、バンク切換により輝度信号データを連続的に入出力することができる。また参照画像データ読出時においても分数精度で動き補償された予測画像の読出時においても第1および第2のバンクのアクセスワード数を同じとして画素データを読出すことができ、また不必要な画素データ数を最小とすることができる。

【0044】

2種類の色差信号はそれぞれ第1および第2のバンクの同じアドレス位置へ格納することにより、色差信号画素データをバンク切換を利用してページ変更時においても連続的に入出力することができる。また、色差信号の画素数は水平方向について輝度信号の画素数の1/2であり、最大2画素ずつ交互に第1および第2のバンクへ輝度信号画素データを格納する構成と組合せれば、1つのバンクの格納する1ラインの画素数は輝度信号と色差信号とで等しくなり、輝度信号および色差信号のデータ入出力時における同期式メモリへのアクセス制御が同じとなり、アクセス制御が簡略化される。

【0045】

【発明の実施の形態】

[実施の形態1]

図1(A)は、この発明に従う画像復号表示装置におけるSDRAM上への画像データの配置方法を概略的に示す図である。図1(A)において、SDRAMは2つのバンクBKA(Aバンク)およびバンクBKB(Bバンク)を含む。バンクBKAおよびBKBは同じ構成を備え、ロウアドレスADXとして、0〜2047を有し、コラムアドレスADYとして0〜255を有する。このSDRAMにおいては、ロウアドレスADXとコラムアドレスADYとにより1ワードの記憶位置が指定される。1ワードは16ビットである。したがってこのSDRAMは、記憶容量として2048・256・16・2=16Mビットを備える。先に説明したように、NTSCサイズの画像において、第1の信号としての輝度信号は720画素(列)・480画素(行)を含み、第1,第2のサンプル数の等しい信号としての色差信号CbおよびCrそれぞれは、360画素(列)・240画素(行)を含む。

【0046】

輝度信号画素データおよび色差信号画素データは8ビットデータである。SDRAMの1ワードは16ビットであり、1ワードに2画素のデータを格納することができる。AバンクBKAおよびBバンクBKBは同じアドレス配置を有しており、SDRAMの1つのアドレス(バンクアドレスを除く)に4画素のデータを格納することができる。したがって、以下に詳細に示すように、AバンクBKAおよびBバンクBKB両者を用いれば、180個のコラムアドレスに720画素のデータを格納することができ、輝度信号1ライン分の画素データを1つのロウアドレスについて格納することができ、また2つの色差信号CbおよびCr両者の1ライン(360・2=720)の画素データを同一ロウアドレス位置に格納することができる。

【0047】

図1(A)においては、ロウアドレス0〜719、コラムアドレス0〜179にフレーム♯0の画素データが格納され、ロウアドレス720ないし1439にフレーム♯1の画素データが格納される。後に詳細に説明するように、1つのバンクにおいて、各フレームは、480画素行および360画素列に配列される輝度信号Yの画素データと240画素行・360画素列に配列される色差信号(CbまたはCr)を備える。

【0048】

図1(B)に示すように、1つのロウアドレスADXiにおいて、コラムアドレスADYは、0番地〜179番地を有する。1つのコラムアドレスに対し、2画素のデータが格納される。したがってロウアドレスADXiについて360個の画素PX0〜PX359の画素データが格納される。バンクBKAおよびバンクBKB両者が同じ構成を備えるため、バンクBKAおよびBKBの同じロウアドレス位置に合計720画素のデータが格納される。この720個の画素データを、後に詳細に説明するように、効率的な画素データ転送を実現するように各バンクに振分ける。すなわち、1つのバンクにおいて、輝度信号Yの画素の半分の画素(480画素行・360画素列)と色差信号CbおよびCrの画素全体の半分の画素(240画素行・360画素列)の画素データを格納する。

【0049】

SDRAMの1つのロウアドレスに対し同一ライン上の画素データがすべて格納するように配置することにより、以下のような効果が得られる。1つのロウアドレスについてすべてのメモリ位置を利用して画素データを格納した場合、ロウアドレスと画素ラインとの対応関係がなくなる。すなわち、1つのロウアドレスにおいて2つのラインの画素データが混在する。このような構成の場合、各画素ラインの始まるコラムアドレス位置が異なる。すなわち、1つの画素ラインの先頭コラムアドレス位置がばらばらに分散される。したがって、参照画像ブロックを読出す場合、ページ変更を頻繁に行なう必要が生じ、ページ変更時のオーバヘッドが無視できなくなる場合が生じる。また各ページの先頭コラムアドレス位置を常時監視して参照ブロックの画素データを読出す必要が生じ、制御が複雑となる。これに対し、1つのロウアドレスと画素ラインとを対応づけることにより、画素ラインとロウアドレスとの対応関係は1対1となり(ロウアドレス1つに対し1画素ラインの画素データが格納される場合)、各画素ラインの先頭コラムアドレス位置も常時同じとなり、参照ブロックの画素データ読出時において、動きベクトルに従って容易に必要とされる画素データを読出すことができる。

【0050】

図2(A)−(C)は、輝度信号(Y)の画素データのSDRAMの記憶位置への配置を詳細に示す図である。図2(A)において、1フレームの各ラインに配置される輝度信号(Y)の画素において、隣接する2画素が、SDRAMの1ワードとして処理される。したがってフレームの各ラインには、SDRAMの360ワードの画素が存在する。偶数番号のワード♯0,♯2,♯4…は、AバンクBKA(以下、単にバンクAと称す)に格納され、奇数番号のワードー♯1,♯3,♯5…は、BバンクBKB(以下、単にバンクBと称す)に格納される。

【0051】

図2(B)に示すように、SDRAMのn番地のロウアドレスの記憶位置に関して、バンクAにおいては、ワード♯0,♯2,♯4…がコラムアドレス0,1,2,…にそれぞれ格納され、またバンクBにおいては、ワード♯1,♯3,♯5,…がコラムアドレス0,1,2,…にそれぞれ格納される。

【0052】

図2(C)に示すように、(n+1)番地のロウアドレスに関しても、同様、バンクAにおいては偶数番号のワード♯0,♯2,♯4,…がコラムアドレス0,1,2,…に格納され、バンクBにおいて、ワード♯1,♯3,♯5,…がコラムアドレス0,1,2,…にそれぞれ格納される。したがってバンクAにおいて、1つのロウアドレスの記憶位置において、1ラインの偶数番号のワードに相当する輝度信号の画素データが格納され、バンクBにおいては、奇数番号のワードに相当する輝度信号の画素データが格納される。この場合、1つのロウアドレスについて、バンクAおよびバンクBそれぞれにおいて360画素のデータが格納される。

【0053】

図3(A)−(C)は、色差信号CbおよびCrの画素データのSDRAMの記憶位置上への配置を示す図である。図3(A)において、色差信号Cbの同じラインにおける隣接2画素がSDRAMの1ワードとして処理される。同様、色差信号Crも同一ラインにおいて隣接する2画素がSDRAMの1ワードとして処理される。すなわち、フレーム内の1ラインにおいて、色差信号Cbの画素は、ワードCb♯0,Cb♯1,…と合計180ワード配置され、同様、色差信号Crもフレーム内の1ラインにおいて180ワードCr♯0、Cr♯1、…が配置される。

【0054】

図3(B)に示すように、ロウアドレスnの記憶位置においてバンクAには、色差信号Cbの画素データが、ワードを単位としてコラムアドレスそれぞれに配置され、またバンクBにおいては、色差信号Crの画素が、2画素を1ワードとして各コラムアドレスに対応して格納される。図3(C)に示すように、ロウアドレスn+1の記憶位置においても同様、バンクAには色差信号Cbの画素のデータが2画素を1ワードとして各コラムアドレスに格納され、バンクBにおいては、色差信号Crの2画素を1ワードとして各コラムアドレスに格納される。

【0055】

この色差信号CbおよびCrはそれぞれバンクAおよびバンクBに別々に格納することにより、バンクAおよびバンクBにおいて1つのロウアドレスの記憶位置(1行)において輝度信号および色差信号ともに360画素(180ワード)の画素データが格納される。

図4(A)は輝度信号(Y)のライン番号n上の画素の配列を示し、図4(B)は、画素PXiのSDRAM上のアドレスの構成を示す図である。図4(A)において、ライン番号nにおいて画素PX0…PXi,PXi+1,…が配置される。ここで、ライン番号nは0から始まる。画素PXiのアドレスは、図4(B)に示すように、ライン番号nと画素PXiの番号iとから得られる。すなわちロウアドレスは、ライン番号n(偶数フレーム♯0)またはライン番号(n)+720(奇数フレーム♯1)で与えられる。コラムアドレスは、画素番号iを2進表示した上位ビットで与えられる。下位2ビットは、バンクアドレスビットBAおよび上位/下位表示ビットU/Lとして利用される。バンクアドレスビットBAが、上位/下位指示ビットU/Lより上位に配置される。バンクアドレスビットBAが0の場合にはバンクAが指定され、バンクアドレスビットBAが1の場合にはバンクBが指定される。ビットU/Lが0の場合には上位バイトが指定され、ワードにおける先頭画素が指定される。ビットU/Lが1の場合には、下位バイトが指定され、ワードの後の画素を示す。このワードにおける先頭画素が上位バイトに格納される代わりに、下位バイトに格納されてもよい。

【0056】

ロウアドレスの生成は、偶数フレームまたは奇数フレームに従ってライン番号nから容易に生成される。一方、画素番号iが得られれば、容易に、SDRAMに対するアドレスを生成することができる。今、具体的に画素番号iからアドレスを生成する方法について説明する。

【0057】

今、図5(A)に示すように、輝度信号画素PX248を考える。10進数の「248」を2進表示すると、“11111000”となる。輝度信号画素は、1ライン上に720個存在するために10ビットのアドレスで画素位置が表現される。図5(B)に示すように、上位8ビットをSDRAMのコラムアドレスとして用いて、最下位から2番目のビットをバンクアドレスビットBAとして用い、最下位ビットを上位/下位指示ビットU/Lとして利用する。したがって、この場合、SDRAMに対するコラムアドレスは、62となり、バンクアドレスビットBAが0であり、バンクAが指定され、上位/下位指示ビットU/Lが0であるため、上位バイトが指定される。したがって、図5(C)に示すように、バンクAにおいてコラムアドレス♯62のワードの先頭位置に画素PX248のデータが格納される。

【0058】

図6は、色差信号の画素番号とSDRAMのアドレスとの対応関係を示す図である。図6においても、図4(A)に示す画素PXiのアドレスが示される。色差信号の場合、ロウアドレスは、図1の画素配置から明らかなように、ロウ番号+480(偶数フレーム)またはライン番号+1200(奇数フレームの場合)で与えられる。輝度信号の画素データに比べてロウアドレスが480大きくなるのは色差信号は輝度信号格納領域よりも上位のロウアドレス領域に格納されるためである。画素番号iはコラムアドレスと上位/下位指示ビットU/Lに分解される。この画素番号iを2進表示し、最下位ビットを上位/下位指示ビットU/Lとして利用する。バンクアドレスビットBAは、色差信号CbおよびCr特定信号として与えられる。色差信号Cbの場合には、バンクアドレスビットBAは0であり、バンクAを指定し、色差信号Crの場合、バンクアドレスビットBAは1であり、バンクBを指定する。このバンクアドレスビットBAは、図6に示す最上位ビット(ロウアドレスの左側)の位置に配置されてもよい。

【0059】

今、図7(A)に示すように、色差信号CbまたはCrの画素PX248のアドレスを考える。色差信号の場合、1ライン上には360画素が配列されるが輝度信号に合わせて、10ビットで画素位置が表現される。この画素番号248を2進表示し、最下位ビットを上位/下位指示ビットU/Lとして利用する。「248」は、“11111000”で表現されるため、最下位ビットの0を除くと、コラムアドレスが124となる。すなわち、図7(C)に示すように、SDRAMにおいてワード位置(コラムアドレス)♯124の位置の上位バイト位置に画素データPX248が格納される。バンクAに格納されるかバンクBに格納されるかは、この画素データPX248が色差信号Cbの画素データであるか色差信号Crの画素データであるかにより決定される。

【0060】

上述のようにして、画素単位で各ラインに配列される画像データにおいて、水平方向の隣接2画素を単位としてバンクAおよびバンクBに選択的に格納する場合でも、各画素データのSDRAMにおける格納位置を指定することができる。

【0061】

画像データを隣接2画素単位でSDRAMのバンクへ選択的に格納することにより、以下に詳細に説明するように、画像データの転送、特に参照画像ブロックの読出を効率的に行なうことが可能となる。

【0062】

[予測画像(参照画像)ブロック画素データの読出]

図8(A)は、動き補償予測画像の復号処理を概略的に示す図である。図8(A)において、現画像ブロックは、輝度信号(Y)については16行・16列に配列された画素で構成され、色差信号(Cb,Cr)については、8行・8列に配列された画素で構成される。現画像ブロックの画素データの予測値を与える参照画像ブロックは、現画像ブロックと同じサイズを備える。所定の処理が行なわれて復号された現画像ブロックの画素データは、参照ブロックの対応の画素データとの差分値を示している。したがって、復号処理においては更に、この現画像ブロックの各画素と参照画像ブロックの各対応の画素のデータとが加算され、現画像データが復元される。参照画像において現画像ブロック位置から参照画像ブロック位置に対する変位は動きベクトルで示される。したがって、現画像ブロックの各画素は復元時には、動きベクトルで示される位置に存在する画素と加算処理が行なわれる。

【0063】

この動き補償予測符号化においては、整数精度での予測および分数精度での予測がある。整数精度での予測においては、動きベクトルの水平方向成分および垂直方向成分はともに整数である。

【0064】

一方、分数精度予測においては、この動きベクトルの水平方向成分Hおよび垂直方向成分Vは分数値をとることができる。本実施例においては、動きベクトルの参照単位として、1/2画素、すなわち1/2精度が用いられる。

【0065】

図8(B)に、1/2画素精度の動きベクトルと対応の画素位置を例示的に示す。図8(B)においては、図面の水平右方向が動きベクトルの水平方向成分Hの正の方向であり、一方、図面の下部方向が、動きベクトルの垂直方向成分Vの正の方向である。動きベクトルを(H,V)で示すと、画素PXeが、動きベクトル(0,0)の位置に対応する。水平方向の正および負の方向に1画素離れた位置に配置される画素PXfおよびPXdの動きベクトルはそれぞれ(1,0)および(−1,0)である。画素PXeから垂直方向に1画素変位した画素PXbに対する動きベクトルは(0,−1)である。この画素PXbに水平方向に隣接する画素PXcおよびPXaは、それぞれ動きベクトル(1,−1)および(−1,−1)を有する。1/2画素精度においては、動きベクトルは±1/2を水平方向成分Hおよび垂直方向成分V両者においてとることができる。画素PX1から1/2画素垂直方向の負の方向に変位した画素PXgの動きベクトルは(0,−1/2)である。画素PXeに対し水平方向および垂直方向それぞれにおいて1/2画素負の方向に変位した画素PXhの動きベクトルは(−1/2,−1/2)である。

【0066】

動きベクトルの値域は、予め定められた探索範囲(最も相関度の高い参照画素ブロックを探索することのできる範囲)により決定され、動きベクトルはその整数値として任意の値をとることができる。この1/2画素精度の場合、画素PXgまたはPXhは、サンプリングされた画素ではない。これらは画素と画素の間に存在する仮想的な画素であり、したがって画素PXhのデータは、隣接する画素PXa,PXb,PXdおよびPXeを用いてたとえば算術平均を行なって算出される。画素PXgの場合には、画素PXbおよびPXeのデータから算出される。したがってこれらの1/2画素精度の場合、画素PXhなどの中間位置に存在する画素のデータを算出するために、整数精度における参照画像ブロックよりも1画素拡張された大きさの画像ブロックを読出すことが必要とされる。

【0067】

図8(C)において、現画像ブロックに対し、動きベクトル(−1/2,−1/2)の参照画像ブロックを破線で示す。この破線で示される参照画像ブロックの画素はすべてサンプリングされた画素データから算出する必要がある。したがって、この参照画像ブロックを格納する画像ブロックを読出す必要がある。動きベクトルがたとえば(−1/2,−1/2)の場合、輝度信号に関しては、17画素・17画素の画像ブロックを読出す必要があり、また色差信号の場合には、9画素・9画素の画像ブロックを読出す必要が生じる。すなわち、分数成分を有する方向について現画像ブロックよりも1画素大きなサイズを有する画像ブロックを読出す必要がある。したがって、動きベクトルの値に従って、16・16画素の輝度信号の画素ブロックの場合、16・16、17・16、16・17、または17・17画素の画像ブロックを読出すことが必要とされる。8・8画素の色差信号の現画像ブロックについても、したがって動きベクトルの値に従って8・8画素、8・9画素、9・8画素、および9・9画素の画素ブロックを読出すことが必要となる。

【0068】

図9(A)は輝度信号の17画素PY0〜PY16と読出されるワードとの対応関係を示す図である。図9(A)において、輝度信号画素PY0がワードの先頭バイトの場合、この必要とされる17番目の画素PY16もワードの先頭バイトとなる。一方、画素PY0がワード0の後半のバイトの場合、最終の画素PY16のワードの後半バイトの位置に存在する。いずれの場合においても、9ワードをSDRAMから読出す必要がある。

【0069】

図9(B)は、色差信号の参照ブロックの画素と読出されるワードとの対応関係を示す図である。先頭の色差信号画素PC0がワードの先頭バイト位置に格納されている場合、9番目の最終画素PC8も、ワードの先頭バイト位置に格納される。一方、先頭画素PC0がワードの後半バイト位置に格納される場合には、最終の画素PC8もワードの後半バイト位置に格納される。いずれの場合においても、色差信号の画素データを5ワード読出す必要がある。

【0070】

図10(A)および(B)は、SDRAMからの参照画像ブロックの輝度信号画素データを読出す順序を示す図である。図10(A)および(B)において、バンクAに格納される画素データを白丸印で示し、バンクBに格納される画素データを斜線を施した丸印で示す。1ワードには2画素含まれる。図10(A)において、参照画像ブロックの1ラインの先頭画素がバンクAに格納されている場合、まずバンクAから連続的に5ワード♯0〜♯4を読出し、次いでバンクBから4ワード♯5〜♯8を読出す。必要とされる17画素は、先頭のワード♯0の先頭バイトまたは後半バイトの位置に応じて異なる。

【0071】

図10(B)は、参照画像ブロックの1ラインにおける先頭画素がバンクBに格納されている際のデータ読出順序を示す。この場合においても、バンクAから先に必要な4ワード♯0〜♯3を読出し、次いでバンクBから5ワード♯4〜♯8を連続的に読出す。必要とされる17画素は、先頭画素のワード♯4における先頭バイト位置または後半バイト位置に応じて異なる。この図10(A)または(B)に示す読出動作を参照画像ブロックの必要とされるライン(16ラインまたは17ライン)分繰返すことにより、必要とされる参照ブロックの画素データをすべて読出すことができる。基本的に、先頭画素がバンクAおよびバンクBのいずれに格納されているかに応じて、バンクAおよびバンクBの一方から5ワード連続に読出し、他方から4ワード連続的に読出す。この動作を繰返す。ここで「読出」はSDRAMから復号ユニットへ必要データが与えられることを示す。

【0072】

図11は、色差信号のSDRAMからの読出順序を示す図である。図11において、白丸印により色差信号Cbの1画素を示し、斜線を施した丸印により色差信号Crの1画素を示す。色差信号Cbの各画素は、バンクAに格納されており、また色差信号Crの各画素データはバンクBに格納されている。この場合、まずバンクAにアクセスし、連続して5ワード♯0〜♯4を読出して、次いでバンクBへアクセスして連続的に5ワード♯5〜♯9を読出す。これにより、まず色差信号Cbの画素データが読出され、次いで色差信号Crの各画素データが読出される。色差信号CbおよびCrのサンプル位置は同じである。したがって、参照画像ブロックにおいて先頭の画素位置がワードの先頭バイト位置にあるか後半バイト位置にあるかに応じて、必要とされる9画素が選択される。色差信号の場合には、バンクAおよびバンクBに対し5ワード単位で交互にアクセスしてデータが読出される。この読出動作を、参照ブロック画像の必要とされるライン数(8ラインまたは9ライン)繰返し実行する。

【0073】

上述のように、輝度信号および色差信号いずれにおいても、バンクAおよびバンクBに対し一定のワード数を単位として交互にアクセスすることにより、後に詳細に説明するように、輝度信号および色差信号いずれに対しても、SDRAMのアクセスシーケンスを同じとすることができ、制御が容易となる。

【0074】

図12は、SDRAMの読出動作を示すタイミングチャート図である。以下、SDRAMのデータ読出動作について簡単に説明する。

【0075】

このSDRAMは、クロック信号CLKに同期してデータの入出力を行ない、また外部からの制御信号およびアドレス信号の取込みを実行する。クロックサイクル1において、アクティブコマンドActが与えられる。このアクティブコマンドActと同時に、ロウアドレスおよびバンクアドレスが与えられる。バンクアドレスがバンクAを指定しており、このバンクAが活性化され、ロウアドレスが指定されるページのメモリセルが選択状態とされる。SDRAMのコマンドは、外部制御信号の状態の組合せにより与えられる。

【0076】

クロックサイクル3においてリードコマンドRdが与えられ、データ読出動作が指定される。このリードコマンドRdとともに同時にコラムアドレスおよびバンクアドレスが与えられる。このコラムアドレスにより、ロウアドレスにより指定されたページの上のワードが指定される。2クロックサイクル経過したクロックサイクル5からこのコラムアドレスにより指定されたワードQ0が読出される。リードコマンドRdが与えられてから、対応のデータQ0が出力されるまでに要するクロックサイクル数は通常レイテンシーと呼ばれる。図12においては、レイテンシーは2である。

【0077】

次いで、各クロックサイクルごとにこのリードコマンドRdとともに与えられたコラムアドレスに基づいて順次隣接するワード(同一ページにおいて)が選択されて、ワードQ1、Q2およびQ3が出力される。SDRAMの出力データは、各クロックサイクルにおいてクロック信号CLKが立上がる以前において確定状態とされ、このクロック信号CLKの立上がりに同期してSDRAMの出力データがサンプリングされて読出データとして画像復号装置(または画像復号表示装置)へ与えられる。1つのコラムアドレスを与えることにより連続的に読出すことのできるデータの数をバースト長と呼び、図12においては、バースト長は4である。バースト長のデータが読出されると、SDRAMは出力ハイインピーダンス状態となる。この状態においては、バンクAにおいてページが選択状態を維持している。クロックサイクル10においてプリチャージコマンドPreをバンクアドレス(A)とともに与える。これにより、バンクAにおいて選択状態とされていたページが非選択状態とされ、バンクAはプリチャージ状態に復帰する。通常、バースト長は、最大1ページまでの任意の数を指定することができる。

【0078】

SDRAMはバンクAおよびバンクBを有しており、バンクアドレスに従ってバンクを指定することにより、バンクAおよびバンクBそれぞれ互いに独立に活性化およびプリチャージを行なうことができる。ただし、1つのクロックサイクルにおいては、1つのバンクに対するコマンドのみを与えることができる。この図10および図11に示す画素データ読出シーケンスを、コマンドの衝突を伴うことなく効率的に行なう読出動作について説明する。

【0079】

図13(A)および(B)は、SDRAMからの参照ブロック画素データ読出シーケンスを示す図である。図13(A)は、図10(A)に示す輝度信号画素データ読出動作シーケンスを示し、図13(B)は、図10(B)に示す輝度信号画素データ読出シーケンスを示す。図13(A)および(B)においては、レイテンシーが2であり、かつバースト長がフルページ(1ページの画素データすべて)である。プリチャージコマンドPreを用いてデータ連続読出動作を停止させる。

【0080】

図13(A)において、クロックサイクル♯0において、SDRAMのバンクAに対するアクティブコマンドActが与えられ、クロックサイクル♯2においてバンクAに対するリードコマンドRdが与えられる。このクロックサイクル♯2におけるリードコマンドRdに従って2クロックサイクル経過後のクロックサイクル♯4から連続的に画素データ(A)が読出される。

【0081】

クロックサイクル♯5において、SDRAMのバンクBに対するアクティブコマンドActを与え、クロックサイクル♯7においてバンクBに対するリードコマンドRdを与える。SDRAMにおいては、リードコマンドRdの場合、後に与えられたリードコマンドが有効とされる。したがって、クロックサイクル♯8まではバンクAからの画素データが連続的に読出され、クロックサイクル♯9からは、このクロックサイクル♯7のリードコマンドRdに従って、バンクBからの画素データ(B)が連続的に読出される。クロックサイクル♯8においてプリチャージコマンドPreを与え、バンクAをプリチャージ状態に復帰させる。

【0082】

バンクBの画素データが読出されている間のクロックサイクル♯10において、バンクAに対し再びアクティブコマンドActを与え次いでクロックサイクル♯12においてバンクAに対しリードコマンドRdを与える。このクロックサイクル♯12のリードコマンドRdに従ってクロックサイクル♯14からはバンクAの画素データ(A)が連続的に読出される。クロックサイクル♯13においてバンクBに対しプリチャージコマンドPreを与える。このとき、クロックサイクル♯13においては、クロックサイクル♯7において与えられたバンクBに対するリードコマンドRdに従って画素データが読出されるが、外部において無視される(この構成は後に説明する)。ここで、プリチャージコマンドPreが与えられても、そのクロックサイクルにおいては、有効データは出力される。プリチャージコマンドPreは、次のクロックサイクルにおけるデータの出力を禁止する(そのサイクルにおいてプリチャージが行なわれる)。

【0083】

クロックサイクル♯15において、アクティブコマンドActをバンクBに対して与え、またクロックサイクル♯17においてバンクBに対するリードコマンドRdを与える。これにより、クロックサイクル♯19からバンクBからの画素データ(B)が読出される。クロックサイクル♯18においてプリチャージコマンドPreをバンクAに対して与え、バンクAをプリチャージ状態に復帰させ、次のページ変更に備える。

【0084】

この図13(A)に示すように、バンクAおよびバンクBそれぞれからは、5クロックサイクルデータが連続的に読出されている。バンクBにおいてのみ5ワードのうちの最後のワードに含まれる画素データが無効とされている。また、コマンドAct、RdおよびPreは、それぞれ、5クロックサイクルごとに交互にバンクAおよびBに対して与えられている。バンクAおよびバンクBそれぞれにおいて、コマンドが与えられる周期は、10クロックサイクルである。したがって、周期的にコマンドを与えることができ、SDRAMに対するコマンド印加の制御が容易となる。また、確実にプリチャージコマンドとアクティブコマンドの間は、2クロックサイクルであり、またアクティブコマンドActとリードコマンドRdの間も2クロックサイクルあり、必要最小限の許容遅延時間をもってバンクAおよびBそれぞれに対しアクセスが行なわれている。バンクAおよびバンクBに対するアクセスのサイクルに対し1ワードの画素データが不要とされているだけであり、ページ変更のオーバヘッドを最小限に抑制して、参照画像ブロックの画素データを読出すことができる。

【0085】

図13(B)においては、参照画素ブロックの各ラインの先頭画素は、バンクBに格納されている。この場合においても、バンクAが先にアクセスされる。クロックサイクル♯0において、バンクAに対するアクティブコマンドActが与えられ、クロックサイクル♯2においてバンクAに対するリードコマンドRdが与えられる。クロックサイクル♯4からバンクAの格納ワードが順次読出される。クロックサイクル♯4において読出されるデータを、参照画像ブロック外部の画素データとして、外部装置において無視する。このバンクAからのワードの読出の間に、クロックサイクル♯5において、バンクBに対するアクティブコマンドActを与え、クロックサイクル♯7において、バンクBに対するリードコマンドRdを与える。これにより、クロックサイクル♯9からバンクBからの画素データが順次読出される。クロックサイクル♯8において、バンクAに対するプリチャージコマンドを与える。次いでクロックサイクル♯10において、バンクAに対するアクティブコマンドActを与え、クロックサイクル♯12においてバンクAに対するリードコマンドRdを与える。この状態においても、クロックサイクル♯14においてバンクAから読出されるワード(画素データ)は不要データとして外部装置において無視する。クロックサイクル♯15から連続して読出される4ワードのデータ(A)を参照画像ブロックの画素データとして処理する。

【0086】

クロックサイクル♯15において、再びバンクBに対するアクティブコマンドActを与え、クロックサイクル♯17においてバンクBに対するリードコマンドを与える。これにより、クロックサイクル♯19からバンクBからのワードデータが読出される。クロックサイクル♯18においてバンクAに対するプリチャージコマンドPreを与え、ページ変更に備える。

【0087】

この図13(B)に示す読出動作シーケンスにおいても、5ワード単位で交互にバンクAおよびバンクBからワードデータが読出されている。バンクAの先頭ワードが外部で無視される。したがってこの場合においても、参照画像ブロックの各ラインに対し1ワードの不要データが出力されるだけであり、SDRAMからは連続的に画素データが出力されており、ページ変更のオーバヘッドを最小限に抑制して必要とされる参照ブロック画素データを読出すことができる。

【0088】

また、図13(A)および(B)の動作シーケンスを見れば明らかなように、コマンドが与えられているクロックサイクルは同じである。すなわち、バンクAおよびBに対し5クロックサイクルごとにコマンドが交互に印加されており、また各バンクに対するコマンドの印加周期は10クロックサイクルである。したがって、参照画像ブロックの先頭画素位置にかかわらず、SDRAMに対するアクセス制御は変更する必要がなく(外部で画素データを不要とする処理が必要とされるだけである)、SDRAMに対するアクセス制御が容易となる。

【0089】

図14は、色差信号の画素データをSDRAMから読出すシーケンスを示す図である。この色差信号の読出シーケンスは、図11に示す色差信号CbおよびCrの読出シーケンスに対応する。

【0090】

図14において、クロックサイクル♯0において、バンクAに対するアクティブコマンドActが与えられ、クロックサイクル♯2において、バンクAに対するリードコマンドRdが与えられる。クロックサイクル♯4からバンクAからの画素データが5ワード順次読出される。クロックサイクル♯5において、バンクBに対するアクティブコマンドActを与え、クロックサイクル♯7において、バンクBに対するリードコマンドRdを与える。このバンクBに対するリードコマンドRdに従って、クロックサイクル♯9からバンクBから画素データワードが5ワード順次読出される。

【0091】

クロックサイクル♯8において、バンクAに対するプリチャージコマンドPreを与え、クロックサイクル♯10において再びバンクAに対するアクティブコマンドActを与える。次いでクロックサイクル♯12において、バンクAに対するリードコマンドRdを与える。このクロックサイクル♯12のリードコマンドRdに従って、クロックサイクル♯14から5ワードの画素データが連続的にバンクAから読出される。クロックサイクル♯13においてバンクBに対するプリチャージコマンドPreを与え、再びクロックサイクル♯15においてバンクBに対するアクティブコマンドActを与える。次いで、クロックサイクル♯17において、バンクBに対するリードコマンドRdを与える。クロックサイクル♯18において、バンクAに対するプリチャージコマンドPreを与える。

【0092】

この図14に示す読出シーケンスにおいても、バンクAおよびバンクBから交互に5ワードの画素データが連続して読出されている。またコマンドは、5クロックサイクルごとに交互にバンクAおよびバンクBに対し与えられており、また各バンクのコマンド印加周期は10クロックサイクルである。したがって、輝度信号の画素データ読出時と同じアクセスシーケンスに従って必要とされる色差信号画素データを読出すことができる。この色差信号の場合には、不必要なデータワードは存在しない。参照画像ブロックの位置に応じて、たとえば復号装置内部において、不要な画素が無効とされる。

【0093】

図15は、この発明に従う画像復号表示装置の構成を概略的に示す図である。図15において、画像復号表示装置は、ビットストリームの形態で与えられる画像符号化データを受け、この画像符号化データに含まれる符号化画素データに所定の復号処理を施して、元の画素データを復元する復号化ユニット2と、復号化ユニット2で復元された画素データを格納する外部メモリとしてのSDRAM4と、復号化ユニット2の動作タイミングの決定などの各種動作を制御するとともに、SDRAM4へのアクセス動作を制御する制御ユニット6を含む。復号化ユニット2は、一般に、MPEG2規格に従う復号化処理機能を備え、符号化画素データの復号処理および各画像の性質および属性などを示すヘッダ情報の解析の機能を有する。制御ユニット6は、図示しない外部に設けられた表示制御装置から与えられる同期信号(水平および垂直同期信号)に従って、復号化ユニット2の復号処理開始タイミングを決定する。

【0094】

復号化ユニット2とSDRAM4の間にメモリインタフェースユニット8が配置され、メモリインタフェースユニット8と図示しない外部に設けられた表示装置の間に表示インタフェース10が配置される。メモリインタフェースユニット8は、制御ユニット6の制御のもとに、SDRAM4に対するデータ書込アドレスおよびデータ読出アドレスを生成しかつこのSDRAM4と復号化ユニット2の間のまたはSDRAM4と表示インタフェース10との間にデータ伝送経路を確立する。表示インタフェース10は、表示装置における画素データの表示速度に従って、メモリインタフェースユニット8から与えられた画素データを順次出力する。

【0095】

図16は、図5に示すメモリインタフェースユニット8の構成を概略的に示す図である。図16において、メモリインタフェースユニット8は、図15に示す復号化ユニット2から与えられる動きベクトル情報MVを受け、制御ユニット6の制御のもとに参照フレーム(マクロブロック)の画素を読出すためのアドレスを発生する参照画像アドレス発生器80と、復号化ユニットで復号された画素データ(復元画素)をSDRAM4へ書込むためのアドレスを制御ユニット6の制御のもとに発生する復元画像アドレス発生器82と、制御ユニット6の制御のもとに表示装置への表示のために画素データをSDRAM4から読出すためのアドレスを発生する表示画像アドレス発生器84と、制御ユニット6の制御のもとに、SDRAM4に対するバンクアドレスBAおよびコマンドを所定の周期で出力するアクセスコントローラ86と、SDRAM4により読出された画素データの配列順序を変換して出力するワード列変換回路88を含む。

【0096】

制御ユニット6は、図示しない表示制御装置から与えられる水平同期信号および垂直同期信号に従って復号化ユニット2に対しフレーム期間を規定しかつ画素復号開始タイミングを決定するピクチャー同期信号を与える。またこのピクチャー同期信号PSYNCに従って、制御ユニット6は所定のシーケンスでアドレス発生器80、82および84を活性状態とする。

【0097】

アクセスコントローラ86は、SDRAM4へのアクセスが行なわれる場合には、常に1つのバンクに対し10クロックサイクル周期でかつ5クロックサイクルごとにバンクAおよびバンクB(SDRAM4に含まれる)へ交互にコマンドを出力する。このアクセスコントローラ86は、ただし参照画像ブロックの画素データ読出時において動きベクトル情報MVに含まれる垂直方向成分(V成分)が整数であるか分数(±1/2)であるかに従って、読出されるべきラインの数を決定し、決定されたライン数繰返しSDRAM4へアクセスする。復元画像データのSDRAM4への書込時および画像データのSDRAM4からの読出時においては、アクセスコントローラ86は、各画像の先頭画素から全ラインがアクセスされるようにそのアクセス動作を繰返し実行する。制御ユニット6は、復号化ユニット2から復号化される画像のタイプを示すフレームタイプ情報を受け、このフレームタイプ情報がIフレームを示すときには、参照画像アドレス発生器80からの参照画像アドレス発生動作を停止させる。復号化される画像がPピクチャーまたはBピクチャーの場合には、参照画像アドレス発生器80は、動きベクトル情報MVに従って読出アドレスを生成する。制御ユニット6は、アドレス発生器80、82および84から出力されるアドレスがSDRAM4に対するアドレスバス上で競合しないようにこれらのアドレス発生回路80、82および84のアドレス発生タイミングを調整するアービトレーション機能を備える。このSDRAM4へのアクセス競合を回避するためのアービタは、別に設けられてもよい。

【0098】

ワード列変換回路88は、SDRAM4から5ワード単位でSDRAM4から読出される画素データを、各画素ラインへの画素データの配列順序に従ってワード列を再配列し、必要とされるワードデータを選択して復号化ユニットへ与える。このワード列変換回路88において、図13(A)および(B)において不要データとして示すワードデータが切捨てられる。

【0099】

図17は、図16に示す参照画像アドレス発生器80の構成を概略的に示す図である。図17において、参照画像アドレス発生器80は、復号中の現画像ブロックの輝度信号および色差信号両者についての先頭画素位置情報を格納する現画像ブロックカウンタ80aと、現画像ブロックカウンタ80aからの先頭画素位置情報と動きベクトル情報MVに従って、参照画像ブロックの輝度信号および色差信号両者についての先頭画素位置を検出する先頭画素位置検出器80bと、偶/奇フレーム情報に従って先頭画素位置検出器80bからの先頭画素位置情報に基づいてSDRAMに対する先頭ロウアドレスおよび先頭コラムアドレスを色差信号および輝度信号両者について生成する先頭ロウ/コラムアドレス生成器80cと、先頭ロウ/コラムアドレス生成器80cからの先頭アドレスに従って、アクセスコントローラの制御のもとにSDRAMに対するロウアドレスADXおよびコラムアドレスADYを生成するアドレス発生器80dを含む。現画像ブロックカウンタ80aは、各フレーム(画像)において、復号処理はマクロブロック単位で行なわれるため、現在復号中の画像ブロックが何番目のマクロブロックであるかを示す情報をカウンタにより生成し、このカウンタのカウント値に基づいて、輝度信号および色差信号それぞれについての先頭画素位置情報を生成する。この現画像ブロックカウンタ80aからのカウント値は、水平方向成分および垂直方向成分両者を含む。

【0100】

先頭画素位置検出器80bは、この現画像ブロックカウンタ80aから与えられる現画像ブロックの先頭画素位置情報と動きベクトル情報MVと加算して、参照ブロックの先頭画素位置を検出する。先頭ロウ/コラムアドレス生成器80cの構成は後に説明するが、参照フレームが偶数フレームであるか奇数フレームであるかに従って、この先頭画素位置検出器80bから与えられた先頭ライン情報に所定の整数(図4および図6参照)を生成し、また先頭画素ライン上の先頭画素番号に基づいてコラムアドレスを生成する。アドレス発生器80dは、アクセスコントローラからの制御のもとに、この先頭ロウ/コラムアドレス生成器80cから与えられる先頭ロウアドレスを繰返し(10ワードごとに)増分する。この増分する回数は、動きベクトル情報MVの垂直方向成分が分数成分(±1/2)を含んでいるか否かに従って決定される。アドレス発生器80dからのコラムアドレスADYは、そのSDRAMのバースト長により異なるが、バースト長がフルページの場合には、先頭ロウ/コラムアドレス生成器8cにより生成された先頭コラムアドレスに固定される。

【0101】

図18は、図17に示す先頭ロウ/コラムアドレス生成器80cのコラムアドレス生成部の構成を概略的に示す図である。図18において、コラムアドレス生成部は、先頭画素位置検出器80bから与えられる先頭輝度信号画素番号を格納するレジスタ81aと、先頭画素位置検出器80bから与えられる先頭色差信号画素番号を格納するレジスタ81cと、レジスタ81aおよび81cの上位ビット(アドレス)の一方を輝度信号であるか色差信号であるかを示す輝度/色差指示に従って選択してコラムアドレスADYを生成するセレクタ81dを含む。輝度信号成分について、先頭画素がバンクBに含まれる場合、そのバンクアドレスビットBAは“1”である。この場合、最初にバンクBからワードを読出す必要があるが、先頭画素のアドレス(AD)はバンクおよびBにおいては同じである。バンクAから画素データワードを読出これを切捨てる。

【0102】

色差信号成分については、先頭画素位置検出器80bにより検出された先頭色差信号画素番号のうち上位のビットがコラムアドレスである。セレクタ81dは、輝度信号成分の必要ワードをすべて読出した後、次いで色差信号のワード情報を読出すために色差信号コラムアドレスを選択する。この輝度/色差指示信号は、アクセスコントローラから与えられる。アクセスコントローラは、必要とされるラインの輝度信号情報を読出した後に、色差信号の情報を読出すように、レジスタ81dの選択経路を制御する。

【0103】

図19は、図17に示す先頭ロウ/コラムアドレス生成器80cの先頭ロウアドレス生成部の構成を概略的に示す図である。図19において、先頭ロウアドレス生成部は、輝度信号の先頭画素ライン番号を格納するレジスタ81eと、レジスタ81eのライン番号情報と定数720とを加算する加算器81fと、偶/奇フレーム情報に従ってレジスタ81eのライン番号情報および加算器81fの出力する情報の一方を選択するセレクタ81gと、色差信号の先頭画素ライン番号情報を格納するレジスタ81hと、レジスタ81hの格納する先頭画素ライン番号情報と所定の定数480とを加算する加算器81iと、レジスタ81hの格納する色差信号先頭画素ライン番号情報と所定の定数1200とを加算する加算器81jと、偶/奇フレーム情報に従って加算器81iおよび81jの出力情報の一方を選択するセレクタ81kと、輝度/色差指示に従ってセレクタ81jおよび81kの一方の出力情報を選択するセレクタ81lを含む。セレクタ81gは、偶/奇フレーム情報が偶数フレーム(♯0)を指定するときには、レジスタ81eの出力情報を選択し、一方偶/奇フレーム情報が奇数フレーム(♯1)を指定するときには、セレクタ81gは加算器81fの出力情報を選択する。セレクタ81kは、偶/奇フレーム情報が偶数フレームを示すときには、加算器81iの出力情報を選択し、一方、偶/奇フレーム情報が奇数フレームを指定するときには、セレクタ81kは加算器81jの出力情報を選択する。この定数480、720および1200は、図1に示すSDRAMのロウアドレスと輝度信号および色差信号との対応関係により定められる。セレクタ81lから、輝度信号および色差信号それぞれについて先頭ロウアドレスが出力される。

【0104】

図20は、図16に示すワード列変換回路88の構成の一例を示す図である。図20において、ワード列変換回路88は、SDRAMから読出されたワードをセレクタ88aを介して受けて順次格納するレジスタ88bと、このレジスタ88bに格納されたワード情報を輝度/色差指示信号およびバンクアドレスビットBAに従って順次選択して出力するセレクタ88cを含む。セレクタ88aは、SDRAMから読出された10ワードのデータについて、バンクAから読出されたデータ(A)をレジスタ88bの偶数番号の格納位置に順次格納し、次いでバンクBから読出された5ワードのデータをレジスタ88bの奇数番号の記憶位置に格納する。レジスタ88cは、輝度/色差指示信号が輝度信号を示すときには、バンクアドレスビットBAを初期値としてレジスタ88bのワードを順次その格納位置番号に従って必要な数のワードを選択して出力する。輝度/色差指示信号が色差信号を示すときには、セレクタ88cは、まず偶数番号の格納位置に格納されたバンクAのデータ(A)を5ワード順次選択し、次いでバンクBから与えられた5ワードのデータを順次選択する。

【0105】

このワード列変換回路88の出力するワード(16ビット)は、復号化ユニット2に含まれる画素列生成回路2aへ与えられる。この画素列生成回路2aは、動きベクトル情報MVの水平方向成分情報MV(H)と先頭画素位置情報に含まれる上位/下位指示ビットU/Lに従って与えられたワードの先頭画素を検出し、この検出された先頭画素から順次8ビットの画素データを出力する。

このセレクタ88cにおいて、バンクアドレス信号ビットBAを初期値として輝度信号ワードを9ワード順次選択することにより、図13(A)および(B)において斜線ブロックで示す不要データを削除することができる。すなわち、バンクアドレス信号ビットBAが“1”のときには、先頭画素はバンクBに含まれており、レジスタ88bの0番地に格納されたバンクAのワードは不要データである。したがってアドレス1に格納された情報から順次9ワード読出すことにより不要データを削除することができる。

【0106】

一方、バンクアドレス信号ビットBAが0のときには、先頭画素はバンクAに含まれ格納されており、この場合には、アドレス0から9ワードを順次読出すことにより、バンクBから読出される最終ワードを削除することができる。これにより、不要画素データを確実に削除することができる。

【0107】

画素列生成回路2aは、水平方向動きベクトル情報MV(H)が整数成分の場合には、この与えられたワードから16画素情報を選択する(輝度信号成分の場合:色差信号の場合には8ワード)。一方、水平方向動きベクトル情報MV(H)が分数成分を有する場合には、画素列生成回路2aは、輝度信号については9ワードを選択し、また色差信号については10ワードを選択する。この選択された9ワード(輝度信号(Y)に関し)の先頭画素を上位/下位ビットU/Lにより識別し、輝度信号については17個の画素データを順次選択して出力する。色差信号については、色差信号CbおよびCrそれぞれについて上位/下位指示ビットU/Lに従って9個の画素データを順次選択して出力する。

【0108】

図16に示す復元画像アドレス発生器82の構成としては、この図17ないし図19に示す構成を利用することができる。復元画像データのSDRAMへの書込時においては、輝度信号については16ライン、色差信号については8ラインであり、アドレス発生器(図17の参照番号80d参照)がカウントアップするロウアドレスADXの値は輝度信号および色差信号それぞれについて固定される。また、復元された画素データをワード単位に変更するためには、図20に示すワード列変換回路88の構成を利用することができる。すなわち、復元された8ビットの画素データを16ビットのワードに変換してセレクタ88cを介してレジスタ88bに順次格納し、バンク単位で画素データを読出す。復元画像データの場合、輝度信号については4ワード単位でバンクAおよびバンクBに交互に書込む必要がある。この場合、SDRAMへのデータ書込時不要とされるワードに対し書込を禁止するマスクをかければよい。色差信号についても、4ワード単位で画素データの書込が行なわれるが、この場合、5ワード単位でバンクAおよびバンクBに交互にアクセスし、1ワードに対しデータ書込を禁止するマスクをかければよい。このマスクをかけるマスク指示信号は、コマンドと独立に外部からクロック信号と同期して与えることができ、コマンドの衝突は生じない。したがって、このマスクを用いれば、復元画像書込時および参照画像読出時においてバンクAおよびバンクBに対し5ワード単位で交互にアクセスするというアクセスシーケンスを維持することができる。

【0109】

復元画像の書込時において、復号化ユニットにおいて色差信号Cbの画素データおよび色差信号Crの画素データのブロックがそれぞれ別々に与えられる構成の場合、バッファメモリを用いる。色素信号CbおよびCrの画素データが2画素データを単位として交互に色差信号CbおよびCrを読出す。復号化ユニットにおいて、色差信号CbおよびCrの復号画素が1画素単位で交互に生成される場合と等価となり、輝度信号と同様のシーケンスに従って5ワードを単位とする色差信号画素データを生成することができる。

【0110】

図21は、図16に示す表示画像アドレス発生器の構成を概略的に示す図である。図21(A)に表示画像アドレスのコラムアドレス生成部の構成を示し、図21(B)に、画像表示アドレスのロウアドレス生成発生部の構成を示す。図21(A)において、画像表示アドレス発生回路84は、アクセスコントローラから与えられるカウントアップ信号に従ってカウント動作を行なうコラムアドレスカウンタ84aを含む。このコラムアドレスカウンタ84aは、SDRAMから10ワード読出されるごとにそのカウント値を5カウントアップする。

【0111】

図21(B)において、ロウアドレス発生部は、輝度信号に対するロウアドレスを発生するロウアドレスカウンタ84bと、ロウアドレスカウンタ84bの出力カウント値と定数720とを加算する加算器84cと、偶/奇フレーム情報に従ってロウアドレスカウンタ80bの出力するカウント値と加算器84cの出力するカウント値の一方を選択するセレクタ84dと、色差信号に対するロウアドレスを生成するロウアドレスカウンタ84eと、ロウアドレスカウンタ84eの出力カウントと定数480とを加算する加算器84fと、ロウアドレスカウンタ84eの出力カウント値と定数1200とを加算する加算器84gと、偶/奇フレーム情報に従って加算器84fおよび84gの一方の出力を選択するセレクタ84hと、輝度/色差指示信号に従ってセレクタ84dおよび84hの一方の出力を選択するセレクタ84iを含む。

【0112】

ロウアドレスカウンタ84bは、アクセスコントローラの制御のもとに、360ワードが読出されるごとにそのカウント値を1増分する。ロウアドレスカウンタ84eも、SDRAMから180ワード読出されるごとにそのカウント値を1増分する。セレクタ84dは、読出される表示画像が偶数フレームの場合には、ロウアドレスカウンタ84bの出力カウントを選択し、表示画像が奇数フレームの場合には加算器84cの出力を選択する。セレクタ84hは、偶数フレームの場合には、加算器84fの出力を選択し、奇数フレームの場合には、加算器84gの出力を選択する。セレクタ84iは輝度信号画素データが読出されるときにはセレクタ84dの出力を選択し、色差信号画素データが読出されるときにはセレクタ84hの出力を選択する。これにより、SDRAMからの表示画素データ読出時のロウアドレスおよびコラムアドレスを生成することができる。

【0113】

なお、コラムアドレスカウンタ84aがアクセスコントローラからの制御のもとに、輝度信号および色差信号の所定数の画素を表示のために読出したときにリセットされる構成の場合(輝度信号画素データの場合には720画素:360ワード)であり、色差信号の場合には360画素(180ワード)である)ロウアドレスカウンタ84bおよび84eを共用し、この共用されるロウアドレスカウンタがコラムアドレスカウンタ84aのリセット(初期値への復帰時)ごとにそのカウント値が1増分されるように構成されてもよい。

【0114】

図22は、図15に示す表示インタフェース15に対する画素列変換部の構成を示す図である。この画素列変換部は、表示インタフェースに含まれてもよいが、またメモリインタフェースユニット8に含まれてもよい。この画素列変換部は、SDRAMから読出された10ワードデータをセレクタ85aを介して順次格納するレジスタ85bと、レジスタ85bに格納されたワードデータをバイトデータに変換して順次所定のシーケンスで選択するセレクタ85cを含む。セレクタ85aは、SDRAMから読出された表示画像画素データワードをレジスタ85bの先頭格納位置から順次格納する。セレクタ85cは、表示画像データが輝度信号の場合には、このレジスタ85bからバンクA、バンクBのワードを交互に選択して読出し、次いでこの16ビットのワードデータを8ビットの画素データに変換して出力する。

【0115】

一方、セレクタ85cは色差信号が画素データの場合には、レジスタ85bの格納するワードデータを順次そのレジスタ85bの格納位置に従って選択する。この色差信号データはしたがって、SDRAMから読出されたワードと同じ順序となる。この場合、色差信号Cb(バンクB)からの画素データを、1ライン遅延を通すことにより、色差信号Crに対し1ライン遅れて色差信号Cbを生成することができる。この画素データの位置合わせは、図15に示す表示インタフェース10において実行される。この場合においても、SDRAMからは5ワード単位で交互にバンクAおよびBから画素データが読出されるだけである。SDRAMの外部において、画素データ列の配列の変換が実行される。

【0116】

なお、この図20および図22に示す画素列変換回路においては、10ワードの画素データが格納されている。この場合、SDRAMからの読出データの格納動作とこの画素列変換回路からの画素データ読出とを同時に行なうために、図20および図22に示す画素列変換回路を2つ並列に設け、この画素列変換回路を交互にアクセスする構成とすれば、SDRAMからの読出データの格納とこの画素列変換回路からの画素データ読出とを同時に実行することができる。

【0117】

以上のように、この発明の実施の形態1に従えば、画素データを隣接2画素2ワードとし、輝度信号についてはワード単位で交互にバンクAおよびバンクBに配置され、2種類の色差信号については各色差信号ごとに異なるバンクに格納されるように構成したため、このSDRAMからの画素データ書込および読出動作時において同じアクセスシーケンス(5ワード単位)でアクセスを行なうことができ、ページ変更のためのオーバヘッドを最小限に抑制して高速でデータ転送を実行することができる。

【0118】

[実施の形態2]

図23(A)および(B)は、この発明の実施の形態2に従うSDRAMの参照画像ブロック読出動作シーケンスを示す図である。図23(A)および(B)においては、輝度信号画素データの読出シーケンスが示される。この実施の形態2においては、SDRAMは、レイテンシーが2、バースト長が2に設定される。バースト長が2の場合、1つのリードコマンドによりコラムアドレスn,n+1が指定される。次に読出動作について説明する。

【0119】

図23(A)に、参照画像ブロックの先頭コラムアドレスが偶数の場合であり、また先頭画素がバンクAに含まれる場合の参照ブロック画像データ読出動作シーケンスを示す。クロックサイクル♯0において、バンクAに対しアクティブコマンドActが与えられ、バンクAにおいてページが選択される(ロウアドレスに従って)。

【0120】

次いで、クロックサイクル♯2においてバンクAに対しリードコマンドRdが与えられる。レイテンシーが2であり、クロックサイクル♯4からこのクロックサイクル♯2に与えられたリードコマンドRdに従って2ワードの画素データが順次ワード単位で読出される。バースト長は2であり、2つのワードのみがリードコマンドRdにより指定される。したがって、クロックサイクル♯4において再びリードコマンドRdをバンクAに対して与え、次の2ワードを指定する。これにより、クロックサイクル♯6からクロックサイクル♯4のリードコマンドRdにより指定された2ワードの画素データが順次ワード単位で読出される。

【0121】

一方、クロックサイクル♯5において、バンクBに対しアクティブコマンドActを与え、バンクBに対しページ選択動作を開始させる。クロックサイクル♯6において、バンクAに対しオートプリチャージ付きリードコマンドRdaを与える。このオートプリチャージ付きリードコマンドRdaは、リードコマンドにより指定されたバースト長分のワードが読出された後に、指定されたバンクがプリチャージ状態に復帰することを指示する。したがって、クロックサイクル♯6においてオートプリチャージ付きリードコマンドRdaを与えると、バースト長、すなわち2クロックサイクル経過後のクロックサイクル♯8においてプリチャージコマンドPが与えられたのと等しくなる。クロックサイクル♯7においてバンクBに対しリードコマンドRdを与える。このリードコマンドRdに従って、クロックサイクル♯9からバンクBから2ワードの画素データが順次ワード単位で読出される。次いでクロックサイクル♯9においてバンクBに対しリードコマンドRdを与え、次の2ワードの画素データをクロックサイクル♯11から読出す。次いでクロックサイクル♯11において、オートプリチャージ付きリードコマンドRdaをバンクBに与える。

【0122】

一方、クロックサイクル♯10においてバンクAに対しアクティブコマンドActを与え、次のページを選択する(ページ変更)。次いでクロックサイクル♯12においてバンクAに対しリードコマンドRdを与える。このリードコマンドRdに従って、クロックサイクル♯14から、バンクAから2ワードの画素データが順次読出される。次いでクロックサイクル♯14においてバンクAに対しリードコマンドRdを与え、次の2ワードの画素データを指定して順次クロックサイクル♯16から読出す。再びクロックサイクル♯16において、オートプリチャージ付きリードコマンドRdaを与え、次の2ワードの画素データを指定して順次読出す。このオートプリチャージ付きリードコマンドRdaにより、クロックサイクル♯18においてバンクAに対して、プリチャージコマンドが与えられたことと等価となり、バンクAはプリチャージ状態に復帰し、ページ変更に備える。

【0123】

一方、バンクBにおいては、クロックサイクル♯15においてアクティブコマンドActを与えて次のページ(バンクAと同じページ)を選択し、クロックサイクル♯17、およびクロックサイクル♯19においてそれぞれリードコマンドRdを与えて、2ワードの画素データを順次読出す。

【0124】

クロックサイクル♯13において読出された画素データは、前述の図20に示す画素列変換回路において切捨てられる。

【0125】

この図23(A)に示す参照ブロック画素データ読出シーケンスにおいて、アクティブコマンドActは、5クロックサイクルごとに交互にバンクAおよびバンクBへ与えられている。またリードコマンドRdおよびオートプリチャージコマンドRdaをバンクAおよびバンクBに与えるシーケンスも同じである。

【0126】

図23(B)は、先頭コラムアドレスが奇数の場合の参照画像ブロックの輝度信号画素データ読出シーケンスを示す。先頭画素はバンクAに含まれている。クロックサイクル♯0においてバンクAに対しアクティブコマンドActを与え、バンクAにおいてロウアドレスにより指定されたページを選択状態とする。クロックサイクル♯2においてリードコマンドRdをバンクAに対して与える。これにより、クロックサイクル♯4から画素データワードが順次バンクAから読出される。このとき、クロックサイクル♯3において再びリードコマンドRdをバンクAに対し与える。このクロックサイクル♯3において与えられたリードコマンドRdにより、クロックサイクル♯5からは、後で与えられたリードコマンドRd(クロックサイクル♯3)に従って指定されたデータワードが読出される。

【0127】

クロックサイクル♯5においてオートプリチャージ付きリードコマンドRdaをバンクAに対し与える。これにより、クロックサイクル♯7からは、このオートプリチャージ付きリードコマンドRdaによって指定された2ワードの画素データがバンクAから順次読出される。クロックサイクル♯7においてバンクAに対し等価的にプリチャージコマンドが与えられているため、バンクAはプリチャージ状態へ移行する。これにより、次のページ変更に備える。

【0128】

一方、バンクBに対して、クロックサイクル♯4においてアクティブコマンドActを与え、ページを選択状態とする。次いでクロックサイクル♯7においてバンクBに対しリードコマンドRdを与え、次いでクロックサイクル♯8においてリードコマンドRdを再び与える。クロックサイクル♯9においてバンクBから読出される画素データワードは、クロックサイクル♯7において与えられたリードコマンドRdによって指定されたものであり、一方、クロックサイクル♯10からは読出される2ワードの画素データは、クロックサイクル♯8において与えられたリードコマンドRdにより指定されたものである。クロックサイクル♯10において、オートプリチャージ付リードコマンドRdaをバンクBに与え、クロックサイクル♯12からこのオートプリチャージ付きリードコマンドRdaにより指定された2ワードの画素データがバンクBから順次読出される。

【0129】

一方、バンクAにおいて、クロックサイクル♯9において与えられたアクティブコマンドActに従ってページが選択状態とされており、クロックサイクル♯12および♯13においてそれぞれリードコマンドRdを与え、クロックサイクル♯14から画素データワードを読出し、クロックサイクル♯15においてオートプリチャージ付きリードコマンドRdaを与える。この読出動作と並行して、クロックサイクル♯14においてバンクBに対しアクティブコマンドActを与え、クロックサイクル♯17および♯18においてリードコマンドRdをそれぞれバンクBに与える。

【0130】

この先頭コラムアドレスが奇数の場合においても、バンクAおよびバンクBに対するアクセスシーケンスは同じである。特に、図23(B)において破線ブロックで示すように、バンクAに対するアクティブコマンドActをクロックサイクル♯0よりも前のサイクルにおいて与えれば、アクティブコマンドActは5クロックサイクルごとにバンクAおよびバンクBに対して与えられており、図23(A)に示す先頭コラムアドレスが偶数アドレスの場合と同じシーケンスを保持することができる。バンクAに対し、それぞれ最初に与えられるリードコマンドRdが先頭コラムアドレスが偶数の場合に比べて1クロックサイクル遅れる点が異なるだけであり、同様の動作シーケンスを実現することができる。

【0131】

プリチャージコマンドPを使用する場合、バンクAに対するプリチャージコマンドとバンクBに対するリードコマンドRdが同一クロックサイクルに与えられる状況が生じる。SDRAMに対しては、1つのバンクに対してのみコマンドを1つのクロックサイクルにおいて与えることが可能である。オートプリチャージ付リードコマンドRdaを利用することにより、このようなコマンドの衝突を防止することができ、効率的なデータ読出を実現することができる。

【0132】

また、図23(B)に示すように、アクティブコマンドActをクロックサイクル♯0よりも前のクロックサイクルにおいて与えた場合、参照画像ブロックの先頭画素の読出が1クロックサイクル遅れるものの、SDRAMに対するアクセスシーケンスをすべて同じとすることができる。

【0133】

図24(A)は、先頭コラムアドレスが偶数であり、かつ先頭画素がバンクBに含まれる場合のSDRAMからの参照画像ブロックの輝度信号画素データ読出シーケンスを示す図である。この図24(A)においても、SDRAMはレイテンシーが2であり、バースト長が2に設定される。

【0134】

クロックサイクル♯0において、バンクAに対しアクティブコマンドActを与え、次いでクロックサイクル♯2においてバンクAに対しリードコマンドRdを与える。クロックサイクル♯4からバンクAは2ワードの画素データが順次読出される。クロックサイクル♯4において再びリードコマンドRdをバンクAに対し与え、次の2ワード画素データを指定する。クロックサイクル♯5においてバンクBに対しアクティブコマンドActを与え、次いでクロックサイクル♯7においてバンクBに対しリードコマンドRdを与える。

【0135】

クロックサイクル♯6においては、バンクAに対しオートプリチャージ付リードコマンドRdaが与えられる。したがって、クロックサイクル♯9からはバンクBからの画素データワードが順次出力される。クロックサイクル♯8において、バンクAがプリチャージへ移行する。クロックサイクル♯9において再びリードコマンドRdをバンクBに対し与え、次の2ワードの画素データを指定する。

【0136】

クロックサイクル♯10において、バンクAに対しアクティブコマンドActを与え、バンクAにおいて次のページを選択状態とする。クロックサイクル♯11においてバンクBに対しオートプリチャージ付きリードコマンドRdaを与え、次の2ワードの画素データを指定するとともに、2ワードの画素データ読出後のバンクBのプリチャージを指定する。クロックサイクル♯12においてバンクAに対しリードコマンドを与え、クロックサイクル♯14からバンクAからの画素データワードを順次読出す。クロックサイクル♯14においてバンクAから読出された画素データワードは、外部に設けられたワード列変換回路において不要として切捨てられる。またクロックサイクル♯14において再びリードコマンドRdをバンクAに対し与える。またクロックサイクル♯16においてオートプリチャージ付きリードコマンドRdaをバンクAに対して与える。バンクBにおいては、クロックサイクル♯15においてアクティブコマンドActが与えられ次のページが選択状態とされている。クロックサイクル♯17においてリードコマンドRdを与えることにより、このリードコマンドに従ってクロックサイクル♯19からバンクBからの画素データワードが読出される。

【0137】

クロックサイクル♯18において再びバンクBに対しリードコマンドRdを与える。

【0138】

バンクAに対して最初に与えられるリードコマンドRdにより指定される画素データワードが外部で不要とされる。バンクAおよびバンクB交互に5ワードずつ読出し、外部で不要データワードを除去することにより、バンクAから4ワード、バンクBから5ワードを交互に読出すことができる。

【0139】

図24(B)は、先頭コラムアドレスが奇数でありかつ先頭画素がバンクBに含まれる場合のデータ読出シーケンスを示す図である。図24(B)において、クロックサイクル♯0においてバンクAに対するアクティブコマンドActが与えられ、次いでクロックサイクル♯2および♯3それぞれにおいてリードコマンドRdがバンクAに対して与えられる。クロックサイクル♯3において与えられたリードコマンドRdに従ってクロックサイクル♯4から2ワードの画素データが順次読出される。クロックサイクル♯2において与えられたリードコマンドRdにより指定される画素データワードは、外部で不要として除去される。クロックサイクル♯5において、オートプリチャージ付きリードコマンドRdaをバンクAに与え、クロックサイクル♯7から2ワードの画素データを順次バンクBから読出す。

【0140】

一方、バンクBに対しクロックサイクル♯4においてアクティブコマンドActを与え、ページを選択状態とし、クロックサイクル♯7および♯8において、それぞれリードコマンドRdをバンクBに対し与える。これにより、クロックサイクル♯9からバンクBからの画素データワードが順次読出される。この場合においても、クロックサイクル♯7において与えられたリードコマンドRdにより指定される2ワードの画素データのうち後のワードが読出されず、クロックサイクル♯8において与えられたリードコマンドRdに従って画素データワードが読出される。クロックサイクル♯10においてバンクBに対しオートプリチャージ付きリードコマンドRdaを与え、クロックサイクル♯12からバンクBから残りの2ワードの画素データを順次読出す。

【0141】

一方、クロックサイクル♯9において、バンクAに対し再びアクティブコマンドActを与え、次のページを選択状態とする。次いで、クロックサイクル♯12および♯13においてリードコマンドRdをそれぞれバンクAに対して与え、クロックサイクル♯14から順次画素データワードを読出す。この場合においても、クロックサイクル♯12において与えられたリードコマンドRdが指定する画素データワードは外部に設けられた回路により不要として削除される。クロックサイクル♯15において、オートプリチャージ付きリードコマンドRdaをバンクAに対して与え残りの2ワードの画素データを読出す。一方クロックサイクル♯14においてバンクBに対してアクティブコマンドActを与え、クロックサイクル♯17および♯18それぞれにおいて、バンクBに対しリードコマンドRdを与える。これにより、クロックサイクル♯19からバンクBからの画素データが順次読出される。

【0142】

この図24(B)に示すデータ読出シーケンスにおいても、バンクAから読出される先頭ワードの画素データが外部で不要とされる。したがって、読出データシーケンスは、図24(A)と同じである。コマンドの与え方が互いに異なっているだけである。この図24(B)に示す動作シーケンスにおいて、バンクAに対するアクティブコメントActを破線ブロックで示すようにクロックサイクル♯0の前のクロックサイクルにおいて与えるように構成してもよい。この場合、コマンドの印加シーケンスがバンクAおよびバンクBにおいてすべて同じとなる。ただしアクティブコマンドが与えられてから最初の画素データの読出しが1クロックサイクル遅れることになる。

【0143】

この図24(A)および(B)に示す読出シーケンスにおいても、バンクAおよびバンクBから交互に5ワードの画素データワードを順次読出すことができる。先頭コラムアドレスが偶数の場合、先頭画素がバンクAおよびバンクBのいずれに含まれるかにかかわらず、同じ動作シーケンスで必要とされる参照画像クロック画素データを読出すことができる(図23(A)および図24(A)参照)。また、先頭コラムアドレスが奇数の場合においても、先頭画素がバンクAおよびバンクBのいずれに含まれるかにかかわらず、同じシーケンスで必要とされる参照ブロック画素データを読出すことができる(図23(B)および図24(B)参照)。したがって同じシーケンスで必要とされる画素データを読出すことができるため、制御が容易となる。

【0144】

図25(A)および(B)は、色差信号画素データワードをSDRAMから読出す際のシーケンスを示す図である。この図25(A)および(B)においても、SDRAMはレイテンシーが2であり、バースト長が2に設定されている。まず図25(A)を参照して、先頭コラムアドレスが偶数である場合の色差信号画素データワードの読出シーケンスについて説明する。

【0145】

クロックサイクル♯0において、バンクAに対しアクティブコマンドActを与え、クロックサイクル♯2および♯4においてそれぞれバンクAに対しリードコマンドRdを与える。これにより、クロックサイクル♯4から画素データワードが順次読出される。クロックサイクル♯5において、バンクBに対してアクティブコマンドActを与え、ページを選択状態とする。クロックサイクル♯6においてバンクAに対しオートプリチャージ付リードコマンドRdaを与える。次いでクロックサイクル♯7においてバンクBに対しリードコマンドRdを与える。オートプリチャージ付リードコマンドRdaに従って、クロックサイクル♯8から画素データワードが読出されるが、クロックサイクル♯9においては、バンクBからクロックサイクル♯7に与えられたリードコマンドRdに従って画素データワードが読出される。これにより、バンクAからは、5ワードの画素データが連続して読出される。次いで、クロックサイクル♯9においてバンクBに対してリードコマンドRdを与え、続いてクロックサイクル♯11においてバンクBに対してオートプリチャージ付リードコマンドRdaを与える、クロックサイクル♯10においてアクティブコマンドActをバンクAに与え、次のページを選択状態とする。

【0146】

クロックサイクル♯12においてバンクAに対しリードコマンドRdを与える。これにより、クロックサイクル♯14からバンクAからの画素データワードが順次読出される。クロックサイクル♯14においてバンクAに対しリードコマンドRdを与え、クロックサイクル♯16においてオートプリチャージ付リードコマンドRdaをバンクAに対して与える。一方、クロックサイクル♯15においてバンクBに対しアクティブコマンドActを与え、クロックサイクル♯17および♯19においてそれぞれバンクBに対しリードコマンドRdを与える。これにより、クロックサイクル♯19からはバンクBからの画素データワードが順次5ワード連続して読出される。

【0147】

この先頭コラムアドレスが偶数の場合、5ワード単位でバンクAおよびバンクBから交互に画素データワードが読出されている。この色差信号の画素データの読出シーケンスは、図23(A)および図24(A)に示す輝度信号画素データ読出シーケンスと同じである。したがって、先頭コラムアドレスが偶数の場合、SDRAMに対するアクセスシーケンスを輝度信号および色差信号について同じとすることができる。

【0148】

次に、図25(B)を参照して、色差信号画素データの先頭コラムアドレスが奇数の場合の読出シーケンスについて説明する。クロックサイクル♯0においてアクティブコマンドActがバンクAに対して与えられ、次いでクロックサイクル♯2および♯3に対しリードコマンドRdがバンクAに対して与えられる。クロックサイクル♯2に与えられたリードコマンドにより指定された画素データワードがクロックサイクル♯4から読出され、次いでクロックサイクル♯5からは、クロックサイクル♯3において与えられたリードコマンドRdにより指定される画素データワードが読出される。

【0149】

次いでクロックサイクル♯5において、バンクAに対し応答プリチャージ付リードコマンドRdaを与える。これにより、クロックサイクル♯7から残りの2ワードの画素データが順次読出される。一方、クロックサイクル♯4においてバンクBに対しアクティブコマンドActを与え、バンクBのページを選択状態とする。次いでクロックサイクル♯7においてバンクBに対しリードコマンドRdを与え、クロックサイクル♯9からバンクBからの画素データワードを読出す。続いてクロックサイクル♯8においてリードコマンドRdをバンクBに対して与えることにより、クロックサイクル♯10からはこのクロックサイクル♯8において与えられたリードコマンドRdに従って選択された画素データワードが順次読出される。クロックサイクル♯10においてオートプリチャージ付リードコマンドRdaをバンクBに対して与える。これにより、クロックサイクル♯12から4ワードの画素データが順次読出される。

【0150】

一方、クロックサイクル♯9においてバンクAに対しアクティブコマンドActを与え、次のページを選択状態とする。クロックサイクル♯12および♯13においてそれぞれバンクA対しリードコマンドRdを与えて3ワードの画素データを順次読出す。次いでクロックサイクル♯15においてオートプリチャージ付リードコマンドRdaをバンクAに対して与えて残りの2ワードの画素データを順次クロックサイクル♯17から読出す。

【0151】

一方、バンクBに対しては、クロックサイクル♯14においてアクティブコマンドActを与えて次のページを選択状態とし、続いてクロックサイクル♯17および♯18においてリードコマンドRdをバンクBに対して与える。

【0152】

先頭コラムアドレスが奇数の場合、バンクAおよびバンクBに対し、リードコマンドを連続して与えることにより、必要とされる5ワードの画素データを読出すことができる。この図25(B)に示す読出動作シーケンスにおいて、図において破線ブロックで示すように、バンクAに対するアクティブコマンドActはクロックサイクル♯0よりも1クロックサイクル前のクロックサイクルにおいて与えられてもよい。またこの図25(B)に示す動作シーケンスは、図23(B)および図24(B)に示す読出シーケンスと同じであり、したがって先頭コラムアドレスが奇数の場合においても、輝度信号および色差信号に対し同じアクセスシーケンスでSDRAMから必要な画素データを読出すことができる。

【0153】

したがって、この実施の形態2においても、先頭コラムアドレスが偶数であるか奇数であるかに従ってアクセスシーケンスが異なるものの、輝度信号および色差信号に対し同じアクセスシーケンスで必要とされる画素データをSDRAMから読出すことができ、またページ変更のためのオーバヘッドは生じず、連続的に画素データワードを読出すことができる。

【0154】

図26は、この参照ブロック画像読出時におけるコラムアドレス発生部の構成を示す図である。この実施の形態2における参照画像アドレス発生器の構成は、図17に示す構成とロウアドレスについては同じである。ロウアドレスについては、アドレス発生器により、10ワード読出しごとにその値が1増分される。したがって同一の構成を利用することができ、図16に示すアクセスコントローラ86の制御の下に必要とされるロウアドレスを生成することができる。

【0155】

図26において、コラムアドレス発生部は、図17に示す先頭ロウ/コラムアドレス発生器80cに含まれる先頭コラムアドレス生成器80ccからの先頭コラムアドレスを受けてコラムアドレスADYを生成するコラムアドレス発生器80dを含む。このコラムアドレス発生器80dは、先頭コラムアドレス生成器80ccからの先頭コラムアドレスを初期値としてクロック信号CLKをカウントするクロックカウンタ80daと、クロックカウンタ80daのカウント値をアクセスコントローラ86の制御の下にコラムアドレスとして出力するセレクタ80dbを含む。

【0156】

クロックカウンタ80daは、アクセスコントローラ86の制御の下に、リードコマンドが与えられると起動されてクロック信号CLKをカウントする。このクロック信号CLKはアクセスサイクルを規定する。アクセスコントローラ86は、オートプリチャージ付リードコマンドを出力するとクロックカウンタ80daのカウント値を初期値にリセットする。セレクタ80dbは、アクセスコントローラ86がリードコマンドまたはオートプリチャージ付リードコマンドが与えられたときにクロックカウンタ80daのカウント値を選択して出力する。

【0157】

クロックカウンタ80daは、クロック信号CLKをカウントしており、したがって先頭コラムアドレスが偶数の場合には、クロックカウンタ80daは、リードコマンドまたはオートプリチャージコマンドが与えられることごとに2増分されており、したがってセレクタ80dbからは、各リードコマンドまたはオートプリチャージコマンドに従って2増分されたコラムアドレスADYが出力される。一方、奇数アドレスが先頭コラムアドレスの場合、アクセスコントローラ86は、リードコマンドを最初連続して与える。このとき、クロックカウンタ80daはカウント値が1増分されているだけであり、したがってリードコマンドが連続して与えられるときには、セレクタ80dbから出力されるコラムアドレスADYは、連続するコラムアドレス値となる。オートプリチャージ付リードコマンドをアクセスコントローラ86が出力するときにクロックカウンタ80daのカウント値を初期値にリセットすることにより、バンクAおよびバンクBに対し交互にアクセスする場合において、常時同じ先頭アドレスから必要とされる画素データワードを読出すことができる。

【0158】

読出される画素データワードの配列順序は実施の形態1と同じであり、したがって、先の実施の形態1と同様の画素データワードの配列順序を変換するための構成を利用することができる。

【0159】

以上のように、この発明の実施の形態2に従えば、レイテンシー2およびバースト長2のSDRAMを用いても、5ワード単位で交互にSDRAMから画素データワードを読出しているため、連続的に必要とされる画素データワードを読出すことができ、効率的なデータ転送を実現することができる。

【0160】

なお、表示画像データ読出時および復号画像データ書込時においては、先頭コラムアドレスは偶数アドレスとなるため、これらの動作においては、画像の先頭位置からアクセスが行なわれるため)、そのアクセスシーケンスに従って必要なアドレスが生成される。この場合においても、実施の形態1と同様、コラムアドレスがリードコマンドに従って2ずつ増分されればよく、またロウアドレスが、必要とされるデータワード(1ページのデータワード)がすべて読出されたときに1増分される構成が利用されればよく、実施の形態1と同様の構成を利用することができる。

【0161】

[実施の形態3]

図27(A)および(B)は、この発明の実施の形態3に従うデータ配置態様を示す図である。画像復号表示装置においては、符号化装置から符号化された画像データが転送される。この符号化画像データは、ビットストリームと呼ばれ、画像の圧縮データおよび画像の特性情報などを含む。通常、MPEG2規格においては、ビットストリームは複数のレイヤの階層構造を有しており、各レイヤは、レイヤの先頭および属性を示す情報を含んでいる。また音声データも同様与えられる。これらの、符号化画像データ(ビットストリーム)のデータの入出力順序(書込みおよび読出し)は固定されている。このような復元された画像データ以外のデータもSDRAMへ配置する。

【0162】

図27(A)において、データ列Data♯0、…は、1ワードを16ビットとして、かつ8ワードがアクセスの単位としてSDRAMに格納される。図27(B)に示すように、バンクAにおいては、この8ワードのデータData♯0〜Data♯7のうち、4ワードのデータData♯0〜Data♯3がバンクAに格納され、バンクBには、残りの4ワードデータData♯4〜Data♯7が格納される。これらのデータワードのアドレス構成は、図4において示すアドレス構成と同じである。次にこの図27(A)および(B)のデータ読出動作を、図28(A)に示すシーケンス図を参照して説明する。ここで、SDRAMはレイテンシーは2、バースト長が4に設定される。なお、SDRAMにおいて、バースト長は、外部からのコマンドにより、所望の値に設定することができる。

【0163】

クロックサイクル♯0において、アクティブコマンドActをバンクAに対し与え、クロックサイクル♯2においてオートプリチャージ付リードコマンドRdaをバンクAに対して与える。クロックサイクル♯4からバンクAからデータData♯0〜♯3が順次読出される。クロックサイクル♯4において、バンクBに対しアクティブコマンドActを与え、クロックサイクル♯6においてオートプリチャージコマンドRdaをバンクBに対して与える。これにより、クロックサイクル♯8からバンクBからのデータワードData♯4〜♯7が順次出力される。次いでクロックサイクル♯8において、バンクAに対しアクティブコマンドActを与え、クロックサイクル♯10においてオートプリチャージコマンドRdaを与える。次に、クロックサイクル♯12からバンクAからのデータワードが順次4ワード出力される。

次いでクロックサイクル♯12においてアクティブコマンドActをバンクBに対して与え、クロックサイクル♯14においてオートプリチャージ付リードコマンドRdaをバンクBに対して与える。それにより、クロックサイクル♯16からバンクBからデータワードが4ワード順次読出される。クロックサイクル♯16において、バンクAに対してアクティブコマンドActを与え、クロックサイクル♯18において、オートプリチャージ付リードコマンドRdaをバンクAに対して与える。

【0164】

このバースト長が4でありレイテンシーが2のSDRAMに対しては、アクティブコマンドとリードコマンドのクロックサイクルを2クロックサイクルとし、またバンクAとバンクBに対し、4クロックサイクル周期で交互にコマンドを与えることにより、4ワード単位でバンクAおよびBから連続的にデータワードを読出すことができる。このデータ読出シーケンスの場合でも、バンクAおよびバンクBが交互に読出されている。したがって、このアクセスシーケンスは、画像データ(復元後の画像データ)のアクセスシーケンスと同じである。したがって図28(B)に示すように、データDataをバンクAおよびバンクBから交互に読出し、他のデータ(Data)のバンクBからの読出時に、バンクAを活性状態として、画像データを読出す準備をし、必要とされるワードデータData読出完了後バンクAから画像データを順次必要とされる数だけ読出すことができる。バンクBからの画像データ読出時に他のデータワードDataを読出すためにバンクAを選択状態とし、画像データ読出完了後バンクAから必要とされるワードデータを出力する。したがって、復元後の画像データの読出シーケンスおよび必要とされるデータワードDataをバンクAおよびバンクBを交互に切換えて選択的にアクセスすることができ、効率的なデータ転送を実現することができる。

【0165】

[変更例]

図29(A)−(C)は、この発明の実施の形態3の変更例の構成を示す図である。図29(A)において、データワードDataは、10ワードをアクセスの単位としてSDRAMに格納される。10ワードのデータData♯0〜Data♯9のうち、前半の5ワードData♯0〜Data♯4がバンクAに格納され、後半の5ワードData♯5〜♯9がバンクBに格納される(図29(B)参照)。次に図29(C)に示すシーケンス図を参照して、データ読出動作について説明する。ただし、この変更例においては、SDRAMはレイテンシーが2であり、バースト長がフルページである。

【0166】

クロックサイクル♯0において、バンクAに対しアクティブコマンドActを与えてクロックサイクル♯2においてバンクAに対しリードコマンドRdを与える。これにより、クロックサイクル♯4においてバンクAからデータワードData♯0−♯4が順次出力される。クロックサイクル♯5においてバンクBに対しアクティブコマンドActを与え、クロックサイクル♯7においてバンクBに対しリードコマンドRdを与える。クロックサイクル♯9からバンクBからのデータワードData♯5−♯9が順次読出される。クロックサイクル♯8において、バンクAに対しプリチャージコマンドPreを与え、バンクAをプリチャージ状態に復帰させる。

【0167】

次いでクロックサイクル♯10においてバンクAに対しアクティブコマンドActを与え、クロックサイクル♯12においてリードコマンドRdをバンクAに対して与える。したがってクロックサイクル♯14からバンクAからの5ワードのデータが順次読出される。クロックサイクル♯13においてバンクBに対しプリチャージコマンドPreを与え、次いでクロックサイクル♯15および♯17においてアクティブコマンドActおよびリードコマンドRdをそれぞれバンクBに対して与える。これにより、クロックサイクル♯19から5ワードのデータがバンクBから読出し始められる。クロックサイクル♯18においてバンクAに対してプリチャージコマンドPreを与える。

【0168】

このアクセスシーケンスにおいても、バンクAおよびバンクBに対して同じアクセスシーケンスで交互に5ワードのデータが読出される。したがって効率的にデータ転送を行なうことができる。なおこのアクティブコマンドActが与えられる場合、ページが変更されてもよく、また同一ページに対し再びアクセスが行なわれてもよい。画像データ(復元後の画像データ)へのアクセスシーケンスと、それ以外の画像データへのアクセスシーケンスをほぼ同じとすることができ、SDRAMのアクセス制御が容易となる。

【0169】

このSDRAMの画像データ以外のデータワードの入出力の制御は、図15に示す制御ユニット6の制御のもとに実行される。このデータワードDataは、図1に示すSDRAMの空き領域に格納される。データの入出力シーケンスは固定であり、アドレスは、FIFO的に(ファーストイン・ファーストアウトメモリと同様に)発生されればよい。ビットストリームの転送速度と復号化ユニットにおける符号処理速度の相違を緩和するためのバッファをSDRAMを用いて実現することができる。

【0170】

SDRAMにおいて、アクティブコマンドのために2クロックサイクル必要とされ、プリチャージコマンドのために2クロックサイクル必要とされる。したがって合計4クロックサイクルの間1つのバンクからデータの読出しが行なわれない。したがって他方のバンクから最小4クロックサイクルのデータを連続的に読出す必要がある。したがって、Qを4以上の整数として、2・Qワードをデータアクセス単位とし、各バンクAおよびBそれぞれにNワードずつデータを格納することにより、復元画像データの転送と両立するデータ転送を実現することができる。

【0171】

以上のように、この発明の実施の形態3に従えば、画像データ(復元画像データ)以外のデータワードも、Nワードずつ交互にバンクAおよびバンクBにアクセスして格納するように構成しているため、復元画像データ転送と両立して効率的に必要とされるデータの転送を行なうことが可能となる。

【0172】

[実施の形態4]

図30(A)ないし(C)は、この発明の実施の形態4に従う画像復号装置におけるSDRAMのアドレス割当てを示す図である。図30(A)において、輝度信号(Y)の各画素データは、1画素置きの2画素がSDRAMの1ワードとして構成され、隣接ワードをそれぞれ交互にバンクAおよびバンクBに格納する。すなわち、隣接する偶数番号の2画素を1ワードとしてバンクAに格納し、隣接する奇数番号の2画素をSDRAMの1ワードとしてバンクBに格納する。図30(A)において、番号0および2の画素がワード♯0として取扱われ、番号1および3の画素がワード♯1として処理される。同様、隣接する偶数番号n,n+2の2画素が偶数番号のワード♯2nとして取扱われ、隣接する奇数番号n+1,n+3の2画素がワード♯2n+1として取扱われる。

【0173】

図30(B)において、SDRAMロウアドレスがnの記憶位置においては、隣接する2ワードがバンクAおよびバンクBの同じコラムアドレス位置に格納される。たとえば、コラムアドレスが0の記憶位置においてバンクAにはワード♯0が格納され、バンクBには、ワード♯1が格納される。すなわち、コラムアドレスがnのとき、バンクAには、ワード♯2nが格納され、バンクBにはワード♯2n+1が格納される。

【0174】

図30(C)において、隣接するロウアドレスn+1においても同様、バンクAには、偶数番号のワード♯0、♯2…が格納され、バンクBにおいては、帰趨番号のワード♯1、♯3…が格納される。このロウアドレスn+1においても、隣接する2ワードは同じコラムアドレス位置に格納される。

【0175】

色差信号については、先の実施の形態1の場合と同様、バンクAにおいては、色差信号Cbの画素データが格納され、バンクBには色差信号Crの画素データが格納される。これらは、それぞれ2画素を1ワードとして格納される。この実施の形態4においても、5ワード単位で輝度信号画素データおよび色差信号画素データをバンクAおよびバンクBから交互に読出して転送することができる。

【0176】

図31(A)−(D)は、輝度信号画素に対するアドレスを示す図である。今、図31(A)に示すように、ライン番号nに配列される輝度信号画素データPX0…PXi,PXi+1,…を考える。画素PXiの画素番号はiである。

【0177】

図31(B)に示すように、画素PXiに対するロウアドレスは、偶数フレームの場合にはライン番号nとなり、奇数フレームの場合には、ライン番号n+720となる(図1のフレーム格納アドレス参照)。一方、画素番号iを2進表示したとき最下位ビットがバンクアドレスビットBAとなり、2番目の最下位ビットは、ワードにおける上位/下位を示す上位/下位指示ビットU/Lとなる。残りの上位ビットがコラムアドレスとして利用される。バンクアドレス信号ビットBAが0の場合には、バンクAが指定され、バンクアドレス信号ビットBAが1の場合には、バンクBが指定される。上位/下位指示ビットU/Lは、0の場合には先頭画素を示し、上位バイト位置に格納される。また上位/下位指示ビットU/Lが1の場合には、その画素は、ワードの後半バイト位置に格納されることを示す。

【0178】

図31(C)に示すように、画素PX248は、番号「248」を2進表示すると「00011111000」となる。最下位ビットが「0」であり、この画素PX248がバンクAに格納されることが示される。2番目の最下位ビットは「0」であり、このバンクAにおけるワードの先頭画素であることが示される。残りのビットがコラムアドレスとして利用され、コラムアドレス62が指定される。

【0179】

図31(D)に示すように、隣接画素PX249については、番号「249」を2進表示すれば「00011111001」であり、最下位ビットは「1」であり、画素PX249はバンクBに格納されることが示される。2番目の最下位ビットは「0」であり、画素PX249はワードの先頭画素であることが示される。残りのビットがコラムアドレスとして利用される。したがって画素PX248およびPX249はそれぞれバンクAおよびバンクBの同じアドレス位置に格納されることが示される。

【0180】

この実施の形態4における各画素に対するアドレス割当ては、実施の形態1のアドレス割当てとバンクアドレスビットと上位/下位指示ビットの位置が交換されることを除いて同じである。したがってSDRAMのアクセス時においては、実施の形態1に示す構成(図16−図19参照)を利用してアドレスを生成することができる。

【0181】

色差信号画素のアドレスは、実施の形態1のアドレス割当てと同じである。

参照画像ブロックの画素データ読出時においては、バンクAおよびバンクBから交互に5ワードのデータが読出される。したがって、実施の形態1および実施の形態2のいずれかの方法にしたがって画素データワードが読出される。

【0182】

図32(A)および(B)は、分数精度で予測符号化された画素データの復元時に必要とされる参照画素(予測画素)を示す図である。図32(A)において、20個の輝度信号画素PX0〜PX19の配列を考える。

【0183】

シーケンスIにおいては、先頭画素が画素PX0であり、この場合には、画素PX0−PX16が必要とされる。シーケンスIIにおいては、先頭画素が、画素PX2であり、画素PX2−PX18が必要とされる。シーケンスIIIにおいては、先頭画素は画素PX1であり、画素PX1−PX17が必要とされる。シーケンスIVにおいては、先頭画素は画素PX3であり、画素PX3−PX19が必要とされる。このシーケンスI−IVそれぞれについて、図32(B)に示すようにバンクAおよびバンクBから5ワードを交互に読出す。この場合には、20画素PX0−PX19が読出される。外部に設けられるワード列変換回路において、不要とされる画素データを切捨てる(この構成については後に説明する)。

【0184】

図32(B)の(a)に示すように、シーケンスIにおいては、画素PX17−PX19が不要とされる。この場合、先頭画素の上位/下位指示ビットU/Lは0であり、バンクアドレスビットBAも0である。

【0185】

図32(B)の(b)に示すように、シーケンスIIでは、不要とされる画素は、画素PX0、およびPX1、およびPX19である。この場合には、先頭画素PX2の上位/下位指示ビットU/Lは1であり、バンクアドレスビットBAは0である。

【0186】

図32(B)の(c)に示すように、シーケンスIIIにおいては、不要画素は画素PX0、PX18およびPX19である。この先頭画素PX1の上位/下位指示ビットU/Lは、0であり、バンクアドレスビットBAは1である。

【0187】

図32(B)の(d)に示すように、シーケンスIVにおいては、不要とされる画素は画素PX0−PX2である。先頭画素PX3の上位/下位指示ビットU/Lは、1であり、バンクアドレスビットBAも1である。ワード番号♯2jとワード番号♯2j+1のワードは同じコラムアドレスを有する。(図30(B)および(C)参照)。したがって、この実施の形態4においては、先頭画素のコラムアドレスに従ってバンクAおよびバンクBから交互に5ワードを読出し、その後、不要とされる3画素データを外部で切捨てる。

【0188】

図33は、この発明の実施の形態4において用いられる参照画像アドレス発生器のコラムアドレス生成部の構成を示す図である。この図33に示す構成は、図18に示すコラムアドレス生成部の構成に対応する。図33において、参照画像アドレス生成器のコラムアドレス生成部は、輝度信号画素番号を格納するレジスタ81eと、色差信号画素番号を格納するレジスタ81cと、レジスタ81eの所定数の上位アドレスビットとレジスタ81cの所定数の上位アドレスビットの一方を輝度/色差指示信号に従って選択するセレクタ81dを含む。このレジスタ81eおよび81cへは、図17に示す先頭画素位置検出器80bからの情報が格納される。レジスタ81eからは、最下位2ビットを除く上位ビットが選択されてセレクタ81dへ与えられる。レジスタ81cからは、最下位ビットを除く上位ビットがセレクタ81dへ与えられる。図32(B)に示すように、先頭画素が画素PX0〜PX3のいずれの場合であっても、バンクAから先に画素データワードが読出されるが、いずれの場合でもコラムアドレスは同じである。したがって、先頭画素データが格納されるバンクに従ってコラムアドレスを変更する必要はない。ロウアドレスについては、実施の形態1の場合と同様、図19に示す構成が利用される。この図33に示すコラムアドレス生成部を利用して、バンクAおよびバンクBから交互に5ワードデータが連続的に読出される。これにより、参照画像ブロックを含む20画素のデータが読出される。

【0189】

図34は、ワード列変換回路の構成を示す図である。このワード列変換回路において、読出された20ワードの画素の配列が変換される。

【0190】

図34は、ワード列変換回路の構成を概略的に示す図である。図34において、ワード列変換回路88(図16参照)は、SDRAMから読出された16ビットの画素データワードのうち上位8ビットをセレクタ88eを介して順次格納するレジスタ88dと、16ビットの画素データワードの下位8ビットをセレクタ88gを介して順次格納するレジスタ88fと、レジスタ88dおよび88fに格納された画素データを順次16ビットの画素データワードとして読出すためのセレクタ88hを含む。

【0191】

レジスタ88dおよび88fは、それぞれ10画素データワードを格納する容量を備える。セレクタ88eは、上位8ビットの画素データを順次レジスタ88dへ格納する。セレクタ88gは、下位8ビットの画素データを順次レジスタ88fの格納位置へ格納する。したがってセレクタ88eおよび88gは、単に順次その選択位置がクロックサイクルごとに切換わるだけである。図34においては、レジスタ88dおよび88fに格納される輝度信号画素番号を示す。レジスタ88dには、画素データPX0、PX1、PX4、PX5、PX8、PX9、PX12、PX13、PX16およびPX17が格納される。一方、レジスタ88fには、画素PX2、PX3、PX6、PX7、PX18、PX11、PX14、PX15、PX18およびPX19が格納される。

【0192】

セレクタ88hは、輝度信号画素データ読出時においては、レジスタ88dおよび88fから交互に2画素データを読出す(実線で示す)。すなわち、レジスタ88dから画素データPX0およびPX1が読出された後、次いでレジスタ88fから画素データPX2およびPX3が読出される。次いでレジスタ88dから画素データPX4およびPX5が読出される。これにより、バンクAおよびバンクBから5ワード単位で読出された輝度信号画素データは、画素ライン上の配列順序に従った16ビットデータに変換されて出力される。

【0193】

色差信号の場合、セレクタ88eおよび88gの動作は輝度信号画素データの格納時の場合と同じであり、したがってレジスタ88dおよび88f各々の格納位置には、色差信号CbおよびCrが順次格納される。この場合には、セレクタ88hは、輝度/色差指示信号に従って、格納時と同様にしてレジスタ88dおよび88fからまず色差信号Cbを5ワード読出し、次いでレジスタ88dおよび88fから色差信号Crの画素データワードを読出す(破線で示す)。この場合、セレクタ88hは、色差信号Cbおよび色差信号Crのワードを交互に読出すように構成されてもよい。セレクタ88hには、単にレジスタの各格納位置を16ビットデータパスに接続するスイッチング素子のオン/オフを制御するシーケンスコントローラのシーケンスが輝度/色差指示信号に従って切換えられる構成が用いられればよい。

【0194】

このセレクタ88hにより配列順序が変換された画素データワードは復号化ユニット2に含まれる画素列生成回路2bへ与えられる。画素列生成回路2bは、輝度信号画素データの場合には、バンクアドレスビットBAおよび上位/下位指示ビットU/Lに従って不要とされる3画素のデータを切捨てて必要とされる17画素のデータを選択して8ビット画素データ列を生成する。この画素列生成回路2bにおいては、バンクアドレスビットBAおよび上位/下位指示ビットU/Lの値に従って、最終3画素(シーケンスI)、先頭2画素および最終1画素(シーケンスII)、先頭1画素および最終2画素(シーケンスIII)、および先頭3画素(シーケンスIV)のデータを切捨てる(先頭有効画素から17画素選択する)。色差信号画素データの場合には、実施の形態1と同様の選択動作が行なわれる。

【0195】

なお、この図34に示すワード列変換回路において、SDRAMからの画素データワードの読出しとワード列変換を同時に(パイプライン的に)行なう場合には、この図30に示す構成を2つ並列に設け、これらの2つの画素列変換回路を交互に書込みおよび読出す構成が利用されればよい。

【0196】

以上のように、この実施の形態4においても、SDRAMの1つ置きの隣接画素を1ワードとしてバンクAおよびバンクBに交互に格納されるようにアドレスを各画素データの割当てているため、実施の形態1と同様、バンクAおよびバンクBから交互に5ワードを連続して読出すことができ、ページ変更のオーバヘッドを最小限に抑制して効率的にデータ転送を行なうことができる。

【0197】

[実施の形態5]

図35は、この発明の実施の形態5に従うSDRAMのアドレス割当てを示す図である。図35において、SDRAMは8ビットデータの入出力を行ない、ロウアドレスが0−2047、コラムアドレスが0−511を含む。このSDRAMは、16Mビットの記憶容量を備える。偶数番号のフレーム♯0はロウアドレス0−719およびコラムアドレス0−359の記憶領域に格納され、奇数番号のフレーム♯1が、ロウアドレス720−1439およびコラムアドレス0−359の記憶領域に格納される。フレーム♯0およびフレーム♯1の各々は、480画素行・720画素列に配列される輝度信号画素データ(Y)および240画素行・360画素列に配列される色差信号画素データ(Cb,Cr)を含む。

【0198】

図36(A)および(B)は、画素データのSDRAMにおけるアドレスの割当てを示す図である。図36(A)において、1ライン(ロウアドレス:ページ)に整列して配置される8ビット輝度信号画素データは交互にバンクAおよびバンクBに格納される。

【0199】

すなわち、図36(B)に示すように、バンクAのコラムアドレス♯0、♯1、♯2には、偶数番号0,2,4の輝度信号画素データが格納され、バンクBのコラムアドレス♯0,♯1,♯2には、奇数番号の輝度信号画素データ1,3,5,が格納される。色差信号は、図35(C)に示すように、バンクAには色差信号Cbの画素データがコラムアドレス♯0,♯1,♯2にそれぞれ対応して格納され、バンクBには色差信号Crの画素データがコラムアドレス♯0,♯1,♯2にそれぞれ格納される。色差信号については、したがって同じ画素のデータはバンクAおよびバンクBの同じアドレスに格納される。バンクAおよびバンクBの1ラインに配置される画素データの数は、先の実施の形態1、2および4と同様360画素である。次に、図37に示す読出シーケンス図を参照してSDRAMからの輝度信号画素データ読出動作について説明する。

【0200】

図37において、SDRAMは、レイテンシーが2であり、バースト長はフルページに設定される。クロックサイクル♯0において、バンクAに対しアクティブコマンドActが与えられ、バンクAにおいてページが選択され、クロックサイクル♯2においてリードコマンドRdが与えられる。クロックサイクル♯4からバンクAから8ビットの輝度信号画素データが順次読出される。

【0201】

クロックサイクル♯9においてバンクBに対しアクティブコマンドActを与え、バンクBの同じページを選択状態とする。次いでクロックサイクル♯11においてバンクBに対してリードコマンドRdを与える。このクロックサイクル♯11のリードコマンドRdに従って、クロックサイクル♯13からはバンクBからの8ビット輝度信号画素データが順次読出される。クロックサイクル♯12においてバンクAに対しプリチャージコマンドPreを与え、バンクAをプリチャージ状態とし、ページ変更に備える。

【0202】

クロックサイクル♯18において、バンクAに対しアクティブコマンドActを与えて次のページを選択状態とする。次いでクロックサイクル♯20においてバンクAに対しリードコマンドRdを与え、クロックサイクル♯22からバンクAからの8ビット輝度信号画素データを順次読出す。クロックサイクル♯21において、バンクBに対しプリチャージコマンドPreが与えられる。

【0203】

この図37に示す読出シーケンスにおいては、9ワード単位でバンクAおよびバンクBから交互に輝度信号画素データが読出されている。参照画像ブロックの画素データを読出す際には、最大17画素が必要とされる。17画素必要なとき、先頭画素がAバンクに含まれるかBバンクに含まれるかに従って18ワードのうち1ワードの画素データが不要とされる(外部に設けられた装置により)。たとえば先頭画素がBバンクに含まれる場合には、バンクAから読出される9ワードの8ビット画素データのうち先頭の8ビット画素データが不要とされる。一方、先頭画素がAバンクに含まれる場合には、バンクBから読出される9ワードの8ビット画素データのうち最終の8ビット画素データが不要とされる。

【0204】

色差信号の読出時においても、同じシーケンスで9ワード単位でバンクAおよびバンクBから交互に画素データが読出される。色差信号の場合、参照サブブロックの大きさサイズは水平方向8画素または9画素である。動きベクトルの水平方向成分MV(H)の値に従って、9ワードの色差信号画素データのうち最終の色差信号画素データが有効または無効とされる。この有効/無効の処理は外部に設けられた装置によって行なわれる。したがって、輝度信号および色差信号いずれにおいても同じシーケンスで必要とされる画素データを読出すことができる。

【0205】

復元画像画素データのSDRAMの書込みおよび表示のための画像データの読出時においても同じシーケンスでバンクAおよびバンクBから交互に9ワードの画素データが読出される。

【0206】

図38(A)−(C)は、この発明の実施の形態5における8ビット輝度信号画素データに対するコラムアドレスおよびロウアドレスの生成手法を示す図である。図38(A)に示すようにライン番号nのライン上に、720個の輝度信号画素データPX0−PX719が配列される。ロウアドレスは、図38(B)に示すように、ライン番号nから生成される。これは実施の形態1、2および4の場合と同じである。偶数フレーム♯0の場合にはロウアドレスはライン番号nに等しく、奇数フレーム♯1の場合にはロウアドレスはn+720となる。一方、図38(B)に示すように、コラムアドレスは画素番号iから生成される。画素番号iは2進表示したときの最下位ビットがバンクアドレス信号ビットBAとして利用される。残りの上位ビットがコラムアドレスとして利用される。バンクアドレス信号ビットBAが0の場合にはバンクAが指定され、バンクアドレス信号ビットBAが1の場合にはバンクBが指定される。

【0207】

図38(C)に示すように、画素PX248のコラムアドレスを算出する。画素PX248の画素番号「248」は「00011111000」で表現される。最下位ビットは“0”であり、バンクAが指定される。残りの上位ビットがコラムアドレスとして用いられ、コラムアドレス124が指定される。すなわち、画素PX248は、バンクAのコラムアドレス124の格納位置に格納される。

【0208】

色差信号の場合には、バンクアドレス信号ビットBAは色差信号CbおよびCrを識別するために用いられており、画素番号iがコラムアドレスとして利用される。

【0209】

図39は、ワード列変換回路の構成を示す図である。この図39に示すワード列変換回路は、図16に示すワード列変換回路に対応する。図39においてワード列変換回路88は、8ビット画素データをセレクタ88xを介して受けて順次格納するレジスタ88yと、レジスタ88yに格納され、8ビット画素データを所定のシーケンスで順次選択して読出すセレクタ88zを含む。

【0210】

セレクタ88xは、SDRAMから順次読出された8ビット画素データを受けてバンクAから読出された画素データをレジスタ88yの偶数番号の格納位置に順次格納し、バンクBから読出された8ビット画素データをレジスタ88yの奇数番号の格納位置に順次格納する。セレクタ88zは輝度/色差指示信号が輝度信号を示すときには、このレジスタ88yに格納された8ビット画素データを順次最初の格納位置から読出して出力する。一方、セレクタ88zは、輝度/色差指示信号が色差信号を示す場合には、レジスタ88yの偶数番号の格納位置に格納された画素データを順次読出し、次いで奇数番号の格納された画素データを順次読出す。これにより、レジスタ88yにおいてバンクAから読出された9ワードの画素データA0−A8およびバンクBから読出された8ビット画素データB0−B8が、サンプリングされた画素データ配列順序に従って出力される。

【0211】

参照画像ブロックの画素データ読出時においては、図34に示すように、復号化ユニット2に含まれる画素列生成回路において必要な画素データのみが選択される。輝度信号画素データの場合には、先頭画素がバンクAに含まれるかまたはバンクBに含まれるかに従って17ワードの画素データが選択される。次いで、動きベクトルの水平方向成分MV(H)に従ってこの選択された17ワードの8ビット画素データのうち最終の8ビット画素データの有効/無効が決定される。動きベクトル水平方向成分MV(H)が整数の場合には、16画素が必要なだけであり、最終の8ビット画素データは切捨てられる。一方、動きベクトル水平方向成分MV(H)が分数成分の場合には、最終の8ビット画素データは有効とされる。

【0212】

色差信号成分の場合には、この図39に示すワード列変換回路88から与えられる9ワードの画素データのうち、動きベクトル水平方向成分MV(H)に従って輝度信号画素データの場合と同様にして、最終の8ビット色差信号画素データの有効/無効が決定される。これにより、必要とされる画素データをすべて転送することができる。

【0213】

表示装置への表示のためにSDRAMから画素データを読出す場合、1ライン上には360画素が配列されており、9ワード単位でバンクAおよびバンクBから交互に画素データを読出すことにより、1ラインの画素データを連続して全て読出すことができる。色差信号についても、1ライン上には360画素があり、同様9ワード単位でバンクAおよびバンクBから交互に画素データを読出すことにより、必要とされる画素データを効率的に連続して読出すことができる。

【0214】

復元画像画素データの書込時においては、復号化ユニットにおいてバッファメモリを設け、これを用いて偶数番号の輝度信号画素データを8ワード先にバンクAに書込み、次いで奇数番号の8ワードの輝度信号画素データをバンクBに書込む。バッファメモリに代えて奇数番号の画素データを8ワード遅延するよう構成を用いてもよい。この動作を繰返す。この復元画像アドレスは、18アクセスサイクルごとにコラムアドレスが8増分される。復元画像画素データの書込時においては、画像データの書込みはマクロクロック単位で行なわれるためである。このマクロブロックの先頭画素アドレスは、実施の形態1においても同様容易に知ることができる。したがって実施の形態1に示す構成を利用することができる。コラムアドレス復元画像画素データの場合、輝度信号画素データおよび色差信号画素データに対し、9クロックサイクル目の画素データ書込みにマスクをかけることにより、8ワード単位で交互にバンクAおよびバンクBに復元画像画素データが書込まれる。

【0215】

以上のように、この発明の実施の形態5に従えば、1ライン上の画素を交互にバンクAおよびバンクBに格納されるようにアドレスを割当て、複数ワード単位でバンクAおよびバンクB交互にアクセスするようにしているため、ページ変更のオーバヘッドを最小限に抑制して効率的なデータ転送を行なうことができる。

【0216】

[実施の形態6]

図40は、この発明の実施の形態6におけるSDRAMに対する8ビット輝度信号画素データのアドレスの割当てを示す図である。図40(A)において、ラインnに整列して配置される8ビット画素データは2画素を単位としてバンクAおよびバンクBに交互に格納される。最初の2画素がバンクAのコラムアドレス0および1にそれぞれ格納され、次の2画素がバンクBのコラムアドレス0および1にそれぞれ格納される。以下、同様のアドレス割当てにより、8ビット画素データがSDRAMに格納される。

【0217】

図40(B)は、この図40(A)に対する配置における各画素のアドレスを示す図である。図40(B)において画素のロウアドレスは、図38(B)に示すものと同様、ライン番号n(偶数フレーム♯0の場合)またはn+720(奇数フレーム♯1)により与えられる。コラムアドレスは、画素番号iの二進表示から2番目の最下位ビットを除くビット(上位ビットおよび最下位ビット(LSB))により与えられる。2番目の最下位ビットは、バンクアドレスビットBAとして利用される。

【0218】

今、図40(C)に示すように、画素PX248のコラムアドレスを算出する。この場合、2番目の最下位ビットは「0」であり、画素PX248はバンクAに格納される。残りのビットがコラムアドレスとなり、画素PX248はコラムアドレス124を有する。

【0219】

一方、図40(D)に示すように、隣接画素PX249は、その2進表示において2番目の最下位ビットは「0」であり、バンクAに格納される。残りのビットをコラムアドレスとして用いるため、この画素PX249はバンクAのコラムアドレス125のメモリ位置に格納される。

【0220】

隣接2画素を単位としてバンクAおよびバンクBに交互に格納する構成の場合、隣接2画素を1ワードとして格納する実施の形態1の場合とほぼ同じとなる(コラムアドレスのビットが1ビット増えてい、単位の画素のコラムアドレスが異なる点が異なるだけである)。したがって実施の形態1と同様にして参照画像ブロックの読出時のアドレスを発生することができる。画素データ読出シーケンスは図37に示すように9ワード単位でバンクAおよびバンクBに対し交互に実行される。不要画素データの識別には、上位/下位指示ビットU/Lに代えて最下位ビットLSBが用いられる。

【0221】

したがってこの図40(A)−(D)に示すように2画素を単位として交互にバンクAおよびバンクBに格納し、9ワード単位(9画素単位)で交互にバンクAおよびバンクBから画素データを読出す構成でも、ページ変更のオーバヘッドを最小に抑制して効率的なデータ転送を行なうことができる(特に参照画像ブロック画素データ転送時)。

【0222】

復元画像画素データの書込みおよび表示画像画素データの読出時においては、実施の形態1と同様にして行なうことができる(ただし9ワード(9画素)単位でバンクAおよびバンクBに交互にアクセスされる点が異なる)。

【0223】

以上のように、この発明の実施の形態6に従えば、隣接2画素を交互にバンクAおよびバンクBに格納されるようにアドレスを割当てているため、ページ変更のオーバヘッドを最小限に抑制して効率的なデータ転送を行なうことができる。

【0224】

[その他の構成]

上述の構成においては、SDRAMは16ビットデータまたは8ビットデータの入出力を行ない、また最小画像ブロックの基本単位は輝度信号については16画素・16画素、また色差信号については8画素・8画素である。また画素データは8ビットで構成されている。一般に、画素データがNビットデータであり、SDRAMがMビットワードを入出力するとき、参照画像ブロックのサイズが、水平方向LないしL+1の場合、(L+1)/(2・M/N)以上の整数Pを単位としてバンクAおよびバンクBへ交互にアクセスする構成とすればよい(輝度画素を1ワードとする場合)。または、(L+1)/(M/N)以上の整数Pを単位としてバンクAおよびバンクBに交互にアクセスされてもよい(色差信号の場合)。SDRAMとしては、同期式メモリ(クロック信号に同期してデータの入出力および制御信号の取込みを行なうメモリ)であればよい。

【0225】

また、画像復号装置として表示機能はなくてもよい。

【0226】

【発明の効果】

以上のように、この発明に従えば、最大2を所定数とする画素を単位としてバンクAおよびバンクBに交互に格納されるように画素データのアドレスを割付けたため、ページ変更時のオーバヘッドを最小限に抑制して効率的なデータ転送を行なうことができ、また制御も容易となる。

【0227】

すなわち、請求項1に係る発明に従えば、第1および第2のバンクを有する同期式メモリ素子に対し、復元画像データを同期式メモリ素子へ格納する際に、水平方向に1列に配列される画素データの最大2画素の所定数の画素を単位として交互に第1および第2のバンクへ格納されるように同期式メモリに書込むように構成したため、ページ変更時のオーバヘッドを最小限に抑制して連続的に画素データを読出し入出力することができ、データ転送効率を大幅に改善することができる。また、この構成により、参照画像ブロック画素データ読出時に効率的なデータ転送効率を実現することができる。

【0228】

請求項2に係る発明においては、種類が異なりかつサンプル数の同じ信号成分については、同じ画素の異なる第1および第2の色差信号はそれぞれ第1および第2のバンクの同じアドレス位置に格納するように構成したため、信号読出時においてバンクAおよびバンクB交互にアクセスして連続的に信号の入出力を行なうことができ、これらの信号のページ変更時のオーバヘッドを最小限に抑制することができる。

【0229】

請求項3に係る発明においては、隣接2画素を単位として交互にバンクAおよびバンクBに書込むように構成したため、標準の同期式メモリを利用して効率的にデータ転送を行なうことのできる画像復号装置を実現することができる。

【0230】

請求項4に係る発明に従えば、メモリ素子のデータのビット幅と画素データのビット幅とが等しい場合においても、隣接2画素を単位として交互に第1および第2のバンクへ画素データを格納しており、標準の同期型メモリを用いて効率的なデータ転送を実現することができる。

【0231】

請求項5に係る発明に従えば、Mビットワードの入出力を行なう同期式メモリ素子において、画素データはNビットであり、水平方向Lないし(L+1)の画素のブロックを参照画素ブロックとして処理を行なう画像復号装置においては、(L+1)/(2・M/N)以上の整数を単位として第1および第2のバンクへ交互にアクセスするように構成しているため、ページ変更時のオーバヘッドを伴うことなく効率的な参照画像データ転送を行なうことができる。

【0232】

請求項6に係る発明においては、Mビットワードの入出力を行なう同期式メモリ素子に対し、画素データがMビットデータであり、画像復号装置が水平方向のサイズがLないし(L+1)の画素ブロックを参照画像ブロックとして処理を行なう場合、(L+1)/(M/N)以上の整数を単位として第1および第2のバンクへ交互にアクセスするように構成しているため、参照画像ブロック画素データ転送時において同期式メモリから連続的に必要とされる画素データをページ変更のオーバヘッドを最小限に抑制して行なうことができ、効率的なデータ転送を実現することができる。

【0233】

請求項7に係る発明においては、表示装置への表示のためにも、所定数画素を単位として交互に第1および第2のバンクへアクセスしているため、参照画像ブロック画素データ読出時および表示装置へのデータ転送時においても同じシーケンスで同期式メモリからデータを読出すことができ、同期式メモリに対するアクセス制御が容易となる。

【0234】

請求項8に係る発明においては、16ビットデータの入出力を行なう同期式メモリ素子に対し、8ビット画素データを5ワード単位で交互に第1および第2のバンクへアクセスするように構成しているため、不必要とされる画素データを最少に抑制して効率的なデータ転送を標準の同期式メモリ素子を用いて実現することができる。

【0235】

請求項9に係る発明においては、同期式メモリが8ビットデータの入出力を行なうとき、画素データを9ワード単位で交互に第1および第2のバンクへアクセスするように構成しているため、標準の同期式メモリ素子を用いても、不必要とされる画素データ数を最小限に抑制して効率的なデータ転送を実現することができる(分数精度で予測符号化された画像データに対しても)。

請求項10に係る発明に従えば、同期式メモリ素子の1つの行アドレスの記憶位置に水平方向少なくとも1ライン上の画素データすべてを格納するようにアドレスが画素データに割当てられているため、ページ変更時のオーバヘッドを最小限に抑制することができる(サンプリング画面上のラインとロウアドレスとが対応することができるため)。

【0236】

請求項11に係る発明に従えば、画像データ以外のデータは2Qワードを単位としてデータ配列基準に従ってQワードずつ交互に第1および第2のバンクへ格納するように構成しているため、画像データ以外のデータに対しても、ページ変更および転送データの種類変更のオーバヘッドを最小限に抑制して効率的なデータ転送を行なうことができる。

【0237】

請求項12に係る発明においては、Qが4であり、同期式メモリ素子において1つのバンクにおいてプリチャージ/アクティブ動作に必要とされるクロックサイクル間において他方のバンクにアクセスしてデータを読出すことができ、効率的なデータ転送を実現することができる。

【0238】

請求項13に係る発明に従えば、同期式メモリ素子のワードのアドレスとして、最下位ビット位置をバンク指定アドレスとしかつ上位ビットをバンク内列位置を示す列特定アドレス(コラムアドレス)とするように各画素データに対しアドレスを生成しているため、隣接画素を交互に第1および第2のバンクへ格納することができる。

【0239】

請求項14に係る発明に従えば、最下位から2番目のビットをバンク指定アドレスビットとし残りのビットを列指定アドレスビットとしているため、隣接2画素を単位として第1および第2のバンクへ交互に格納することができる。

【0240】

請求項15に係る発明に従えば、第1,第2の信号の種類を特定する信号をバンク特定ビットとして色差信号画素データに対するワードアドレスを生成しているため、2種類の信号をそれぞれ第1および第2のバンクの同じアドレス位置(同じ画素について)に容易に格納することができる。

【0241】

請求項16に係る発明に従えば、第1の信号は輝度信号であり、輝度信号アクセス時のオーバヘッドが低減される。

【0242】

請求項17に係る発明に従えば、第1,第2の信号は色差信号であり、色差信号アクセス時のオーバヘッドが低減される。

【図面の簡単な説明】

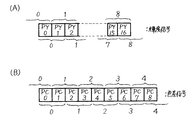

【図1】 (A)はこの発明において用いられるSDRAMにおける画素データの格納領域を示し、(B)は1つのロウアドレスにおいて配置される画素データ列を示す図である。

【図2】 (A)はこの発明の実施の形態1における輝度信号画素データとSDRAMの1ワードとの対応関係を示し、(B)および(C)はSDRAMにおける各画素データのコラムアドレスの割当てを示す図である。

【図3】 (A)はこの発明の実施の形態1における色差信号画素データとSDRAMの1ワードとの対応関係を示し、(B)および(C)は色差信号のSDRAMのバンクAおよびバンクBにおける格納態様およびコラムアドレスの割当てを示す図である。

【図4】 (A)は1つのロウアドレスにおける輝度信号画素データの配列を示し、(B)は輝度信号画素PXiに対するアドレスを示す図である。

【図5】 (A)は輝度信号画素の具体的例を示し、(B)はその2進表示からのコラムアドレス、バンクアドレスおよび上位/下位指示ビットの生成を示し、(C)は(A)に示す画素のSDRAM内の格納態様を示す図である。

【図6】 この発明の実施の形態1における色差信号画素データのアドレス生成を示す図である。

【図7】 (A)は色差信号の具体的画素を示し、(B)はこの画素の画素番号とコラムアドレスとの関係を示し、(C)はこの色差信号画素データのSDRAM内の格納位置を示す図である。

【図8】 (A)は復号中の現画像ブロックと参照画像ブロックとの対応関係を示し、(B)は動きベクトルを示し、(C)は動きベクトルに応じて読出される画像ブロックのサイズを示す図である。

【図9】 (A)は輝度信号参照画像ブロック読出時におけるワードと画素データとの対応関係を示し、(B)は色差信号参照画像ブロック読出時における用いられる画素と読出されるワードとの対応関係を示す図である。

【図10】 (A)および(B)は、輝度信号参照画像ブロック画素データ読出時における画素データの読出シーケンスを示す図である。

【図11】 色差信号参照画像ブロック画素データ読出シーケンスを示す図である。

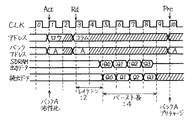

【図12】 SDRAMのアクセス動作を示すシーケンス図である。

【図13】 (A)および(B)は輝度信号参照画像ブロック画素データ読出時の動作を示すシーケンス図である。

【図14】 色差信号参照画像ブロック画素データ読出時の動作を示すシーケンス図である。

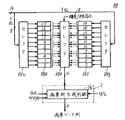

【図15】 この発明における画像復号表示装置の全体の構成を概略的に示す図である。

【図16】 図15に示すメモリインタフェースユニットの構成を概略的に示す図である。

【図17】 図16に示す参照画像アドレス発生器の構成を概略的に示す図である。

【図18】 図17に示す先頭ロウ/コラムアドレス生成器のコラムアドレス生成部の構成を概略的に示す図である。

【図19】 図17に示す先頭ロウ/コラムアドレス生成器のロウアドレス生成部の構成を概略的に示す図である。

【図20】 図16に示すワード列変換回路の構成を概略的に示す図である。

【図21】 (A)は図16に示す表示画像アドレス生成器のコラムアドレス生成部の構成を示し、(B)は図16に示す表示画像アドレス生成器のロウアドレス生成部の構成を概略的に示す図である。

【図22】 表示画像画素データ読出時のワード列変換回路の構成を概略的に示す図である。

【図23】 (A)および(B)はこの発明の実施の形態2におけるSDRAMからの参照画像ブロック画素データ読出シーケンスを示す図である。

【図24】 (A)および(B)はこの発明の実施の形態2における参照画像画素データ読出シーケンスを示す図である。

【図25】 (A)および(B)はこの発明の実施の形態2における色差信号参照画像ブロック画素データ読出シーケンスを示す図である。

【図26】 この発明の実施の形態2において用いられる参照画像アドレス発生器のコラムアドレス発生部の構成を概略的に示す図である。

【図27】 (A)はこの発明の実施の形態3におけるデータ配列を示し、(B)は(A)に示すデータのアドレス割当ておよびアクセス単位を示す図である。

【図28】 (A)はこの発明の実施の形態3におけるデータワード読出シーケンスを示す図であり、(B)は画像データとデータワード読出時のアクセスされるバンクを概略的に示す図である。

【図29】 (A)はこの発明の実施の形態3の変更例のデータ配列におけるアクセス単位を示し、(B)はそのSDRAMにおける格納態様を示し、(C)はSDRAM上のアクセス時の動作を示すシーケンス図である。

【図30】 (A)はこの発明の実施の形態4における輝度信号画素データとSDRAMの1ワードとの対応関係を示す図であり、(B)および(C)は(A)に示すワードのSDRAM格納時の態様を示す図である。

【図31】 (A)−(D)はこの発明の実施の形態4における輝度信号画素に対するアドレス生成およびその具体例を示す図である。

【図32】 この発明の実施の形態4における輝度信号参照画像ブロック画素データ読出時に必要とされる画素データを示す図である。

【図33】 この発明の実施の形態4における参照画像アドレス発生器のコラムアドレス発生部の構成を概略的に示す図である。

【図34】 この発明の実施の形態4におけるワード列変換回路の構成を概略的に示す図である。

【図35】 この発明の実施の形態5におけるSDRAMにおける画像データ格納領域を示す図である。

【図36】 (A)は、この発明の実施の形態5における1ラインに整列して配置される画素データを示し、(B)は輝度信号画素データのSDRAMに格納態様を示し、(C)は色差信号画素データのSDRAMへの格納態様を示す図である。

【図37】 この発明の実施の形態5における画像データ読出シーケンスを示す図である。

【図38】 (A)−(C)は、この発明の実施の形態5における画素に対するアドレス生成およびその具体例を示す図である。

【図39】 この発明の実施の形態5における参照画像ブロック画素データのワード列変換回路の構成を概略的に示す図である。

【図40】 (A)−(D)はこの発明の実施の形態6におけるSDRAM内の画素データの格納態様およびそのアドレス生成および具体例を示す図である。

【図41】 MPEG2規格に従う画像データの復号動作を説明するための図である。

【図42】 画像データの構成を概略的に示す図である。

【図43】 (A)は画像データ復号時の単位となるブロックおよび(B)は復号動作時において用いられる動きベクトルを示す図である。

【図44】 従来の画像復号処理装置の64ビットデータバスを利用するデータ転送の問題点を説明するための図である。

【図45】 従来のSDRAMの一般的構成を概略的に示す図である。

【図46】 (A)−(C)は従来のSDRAMを利用する際の問題点を説明するための図である。

【図47】 従来のSDRAMの基本アクセス動作を説明するための図である。

【符号の説明】

BKA,BKB バンク、2 復号化ユニット、6 制御ユニット、4 SDRAM、8 メモリインタフェースユニット、10 表示インタフェース、80参照画像アドレス発生器、82 復元画像アドレス発生器、84 表示画像アドレス発生器、86 アクセスコントローラ、88 ワード列変換回路、80a現画像ブロックカウンタ、80b 先頭画素位置検出器、80c 先頭ロウ/コラムアドレス生成器、80d アドレス発生器、81a,81c レジスタ、81d セレクタ、81e,81h レジスタ、81f,81i,81j 加算器、81g,81k,81l セレクタ、88a,88c セレクタ、88bレジスタ、2a 画素列生成回路、84a コラムアドレスカウンタ、84b,84e レジスタ、84c,84f,84g 加算器、84d,84h,84iセレクタ、85a,85c セレクタ、85b レジスタ、80cc 先頭コラムアドレス生成器、80ba クロックカウンタ、80db セレクタ、81e レジスタ、88e,88g,88h セレクタ、88d,88f レジスタ、2b 画素列生成回路、88x,88z セレクタ、88y レジスタ。

Claims (17)

- 符号化された画像データからもとの画像データを復元するための画像復号装置であって、

互いに独立にメモリセル選択動作を行うことのできる第1および第2のバンクを含み、クロック信号に同期してデータの入出力が行われる同期型メモリ素子と、

前記符号化された画像データに含まれるサンプリング画素データを受けて所定の復号処理を施してもとの画像データを復元する復号手段と、

前記復号手段により復元された画像データを前記同期型メモリ素子に格納するための制御手段とを備え、前記制御手段は第1の信号成分について画像上水平方向に一列に配列されるサンプリング画像データを、連続して隣接する2画素を単位として交互に前記第1および第2のバンクに格納されるように前記復号手段からの画像データに含まれる画素データを前記同期型メモリ素子へ書込む手段を含む、画像復号装置。 - 前記画像データは、さらに、互いに種類が異なり、かつサンプル数の等しい第2および第3の信号成分を含み、

前記制御手段は、前記第2および第3の信号成分について同じサンプリング画素の第2および第3の信号を前記第1および第2のバンクの同じアドレス位置に格納するように前記復元された画像データに含まれるサンプリング画素データを前記同期型メモリ素子に書き込む手段をさらに備える、請求項1記載の画像復号装置。 - 前記同期型メモリ素子はMビットを1ワードとしてワード単位でデータの入出力を行ない、前記画素データの輝度信号線分は、M/2ビットデータであり、前記所定数は2である、請求項1記載の画像復号装置。

- 前記同期型メモリ素子はMビットを1ワードとしてワード単位でデータの入出力を行い、前記画素データの第1の信号成分はMビットデータであり、前記制御手段は、2ワードごとに交互に前記第1および第2のバンクに画素データを書込む、請求項1記載の画像復号装置。

- 前記同期型メモリ素子は、Mビットワードをワード単位で入出力し、前記画素データはNビットデータあり、前記復号手段は、水平方向のサイズがLないしL+1の画素ブロックを参照ブロックとして画像データを復元する手段を含み、

前記制御手段はP回を単位として交互に前記第1および第2のバンクへアクセスして画素データを読出し、前記復号手段へ与える手段を含み、前記Pは、(L+1)/(2・M/N)以上の整数でありかつ1つのバンクに対し連続してアクセスされるワードの数を示す、請求項1記載の画像復号装置。 - 前記同期型メモリ素子はMビットワードをワード単位で入出力し、前記画素データはNビットデータであり、前記復号手段は水平方向のサイズがLないしL+1の画素ブロックを参照ブロックとして画像データを復元する手段を含み、

前記制御手段は、P回を単位として交互に前記第1および第2のバンクへアクセスして画素データを読出して前記復号手段へ与える手段を含み、前記Pは(L+1)/(M/N)以上の整数でありかつ1つのバンクに対し連続してアクセスする回数を示す、請求項2記載の画像復号装置。 - 前記制御手段は、表示装置上での表示のために、前記P回を単位として交互に前記第1および第2のバンクへアクセスして画素データを読出す手段をさらに備える、請求項5または6記載の画像復号装置。

- 前記同期型メモリ素子は16ビットデータを1ワードとしてワード単位でデータの入出力を行ない、

前記画素データは8ビットデータであり、

前記制御手段は、5ワード単位で交互に前記第1および第2のバンクへアクセスする手段を含む、請求項1または2記載の画像復号装置。 - 前記同期型メモリ素子は8ビットデータを1ワードとして、前記ワード単位でデータの入出力を行ない、

前記画素データは8ビットデータであり、

前記制御手段は、9ワード単位で交互に前記第1および第2のバンクをアクセスする手段を含む、請求項1または2記載の画像復号装置。 - 前記制御手段は、前記同期型メモリ素子の1つの行アドレスの記憶位置に画像上水平方向の少なくとも1ライン上に配列される画素データすべてを格納するように各画素データに対しアドレスを発生する手段を含む、請求項1ないし9のいずれかに記載の画像復号装置。

- 前記画像データ以外のデータを2Qワードを単位としてデータ配列順序に従ってQワードずつ交互に前記第1および第2のバンクへ格納する手段を含む、請求項1ないし10のいずれかに記載の画像復号装置。

- 前記Qは4である、請求項11記載の画像復号装置。

- 前記制御手段は、前記同期型メモリ素子に対し、各ワードのアドレスとして、最下位ビット位置をバンク指定アドレスビット位置としかつ上位ビットをバンク内の列位置を示す列特定アドレスとする列アドレスを各ワードが有するように各画素データに対するアドレスを生成する手段を含む、請求項1記載の画像復号装置。

- 前記制御手段は、ワードのアドレスとして、最下位から2番目のビット位置をバンク指定アドレスビット位置とし、残りのビット列指定アドレスビットとして有する列アドレスを各画素データに対するアドレスとして生成する手段を含む、請求項1記載の画像復号装置。

- 前記制御手段は前記同期型メモリ素子の各ワードに対するアドレスとして、色差信号特定信号としてバンク特定ビットを含むアドレス信号を各画素データに対して生成する手段を含む、請求項2記載の画像復号装置。

- 前記第1の信号成分は輝度信号成分である、請求項1記載の画像復号装置。

- 前記第2および第3の信号成分は色差信号成分である、請求項2記載の画像復号装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06438596A JP3686155B2 (ja) | 1996-03-21 | 1996-03-21 | 画像復号装置 |

| US08/780,369 US5850483A (en) | 1996-03-21 | 1997-01-09 | Image decompressing apparatus with efficient image data transfer |

| GB9701728A GB2311434B (en) | 1996-03-21 | 1997-01-28 | Image decompressing apparatus with efficient image data transfer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06438596A JP3686155B2 (ja) | 1996-03-21 | 1996-03-21 | 画像復号装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09261688A JPH09261688A (ja) | 1997-10-03 |

| JP3686155B2 true JP3686155B2 (ja) | 2005-08-24 |

Family

ID=13256806

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP06438596A Expired - Fee Related JP3686155B2 (ja) | 1996-03-21 | 1996-03-21 | 画像復号装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5850483A (ja) |

| JP (1) | JP3686155B2 (ja) |

| GB (1) | GB2311434B (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100230412B1 (ko) * | 1997-03-08 | 1999-11-15 | 윤종용 | 멀티 뱅크를 갖는 반도체 메모리장치 |

| JPH10283770A (ja) * | 1997-04-07 | 1998-10-23 | Oki Electric Ind Co Ltd | 半導体メモリ装置およびその読み出しおよび書き込み方法 |