WO2019012952A1 - 電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体 - Google Patents

電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体 Download PDFInfo

- Publication number

- WO2019012952A1 WO2019012952A1 PCT/JP2018/023808 JP2018023808W WO2019012952A1 WO 2019012952 A1 WO2019012952 A1 WO 2019012952A1 JP 2018023808 W JP2018023808 W JP 2018023808W WO 2019012952 A1 WO2019012952 A1 WO 2019012952A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- program

- authenticator

- partial

- electronic control

- verification

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/32—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials

- H04L9/3236—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials using cryptographic hash functions

- H04L9/3242—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials using cryptographic hash functions involving keyed hash functions, e.g. message authentication codes [MACs], CBC-MAC or HMAC

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/60—Protecting data

- G06F21/64—Protecting data integrity, e.g. using checksums, certificates or signatures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/30—Authentication, i.e. establishing the identity or authorisation of security principals

- G06F21/44—Program or device authentication

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/57—Certifying or maintaining trusted computer platforms, e.g. secure boots or power-downs, version controls, system software checks, secure updates or assessing vulnerabilities

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09C—CIPHERING OR DECIPHERING APPARATUS FOR CRYPTOGRAPHIC OR OTHER PURPOSES INVOLVING THE NEED FOR SECRECY

- G09C1/00—Apparatus or methods whereby a given sequence of signs, e.g. an intelligible text, is transformed into an unintelligible sequence of signs by transposing the signs or groups of signs or by replacing them by others according to a predetermined system

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/32—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials

- H04L9/3247—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials involving digital signatures

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/84—Vehicles

Definitions

- the present disclosure relates to an electronic control unit that detects program tampering, a program tampering detection method, a program of the program tampering detection method, and a computer-readable sustainable tangible recording medium.

- a control system ECU Electronic Control Unit

- a body system ECU that controls a meter, a power window, etc.

- an information system ECU such as a navigation device Etc.

- the programs of the on-board ECUs mounted on the vehicle include, for example, those in which strict time restrictions are imposed on the start-up time in order to ensure safety.

- Patent Document 1 describes the disclosure of a secure boot method in which only an intended OS or the like is operated with respect to a risk that an OS (Operating System) or the like is falsified by a third party in an embedded device such as a car.

- a computer is to be verified among partial programs in which a program is divided into a plurality of programs for each program activation of the system for the purpose of activating the system quickly and safely. It is determined whether the selection step of selecting the partial program, the calculation step of calculating the hash value of the selected partial program, and whether the calculated hash value and the correct hash value match, and if they match, start processing is continued. And a verification step of interrupting the start-up process if they do not match.

- the program area to be verified is divided into a plurality of divisions, and verification of the presence or absence of program tampering is sequentially performed in each division to satisfy the restriction of the activation time. It is stated that all program areas to be verified can be verified.

- wake-up wake-up time constraints from sleep are more stringent than normal wake-up time constraints. For this reason, in order to satisfy the time constraint at the time of wake-up activation from sleep, it is necessary to finely divide the area of the program to be verified into multiple partial programs.

- An object of the present invention is to provide an electronic control device, a program tampering detection method, a program of the program tampering detection method, and a computer-readable sustainable tangible recording medium.

- the electronic control unit generates a plurality of divided programs obtained by dividing the program and a storage unit for storing a verification authenticator, and generates a partial authenticator of each of the plurality of divided programs by cryptographic operation. And a logical operation using a plurality of partial authenticators to generate an operation authenticator, and falsification of the program depending on whether the authentication authenticator and the operation authenticator match or not. And a verification unit to be verified.

- the electronic control device described above matches the operation authenticator generated by the logical operation using a plurality of partial authenticators generated from the divided programs and the verification authenticator generated by performing the same logical operation in advance Whether the program has been tampered with or not is verified.

- the number of verification authenticators stored in advance in the storage unit can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the restriction of the activation time, the electronic control unit consumes a small amount of memory (memory) required for storing the verification authenticator.

- a program tampering detection method comprises: generating, by cryptographic operation, a partial authenticator of each of a plurality of divided programs obtained by dividing a program; and performing a logical operation using the plurality of partial authenticators And generating the operation certifier, and determining whether or not the operation certifier matches the previously-obtained verification certifier.

- the operation authentication code generated by the logical operation using a plurality of partial authentication codes generated from the divided programs matches the verification authentication code generated by performing the same logical operation in advance Whether the program is tampered or not is verified.

- the number of verification authenticators stored in advance can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the start time constraint, the consumption of the storage unit (memory) required for storing the verification authenticator decreases.

- the program generates a partial authenticator of each of a plurality of divided programs obtained by dividing the program by cryptographic operation, and performs a logical operation using the plurality of partial authenticators to perform arithmetic authentication.

- a computer is caused to execute a program tampering detection method including generation of a child, and determination as to whether or not the operation authenticator matches a previously-obtained authentication authenticator.

- the operation authentication code generated by the logical operation using a plurality of partial authentication codes generated from the divided programs matches the verification authentication code generated by performing the same logical operation in advance Whether the program is tampered or not is verified.

- the number of verification authenticators stored in advance can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the start time constraint, the consumption of the storage unit (memory) required for storing the verification authenticator decreases.

- the program generates a partial authenticator of each of a plurality of divided programs obtained by dividing the program by cryptographic operation, and performs a logical operation using the plurality of partial authenticators to perform arithmetic authentication.

- the program control method includes: generating a child; and determining whether the operation authenticator matches the authentication authenticator obtained in advance. Run it.

- the operation authentication code generated by the logical operation using a plurality of partial authentication codes generated from the divided programs matches the verification authentication code generated by performing the same logical operation in advance Whether the program is tampered or not is verified.

- the number of verification authenticators stored in advance can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the start time constraint, the consumption of the storage unit (memory) required for storing the verification authenticator decreases.

- a program generates, by cryptographic operation, a partial authenticator of each of a plurality of divided programs obtained by dividing a program, and performs logical operation using the plurality of partial authenticators to perform arithmetic authentication.

- a program tampering detection method comprising generation of a child, and determination as to whether or not the operation authenticator and the authentication authenticator obtained in advance coincide with each other is generally selected from the low power consumption mode of the electronic control device. Make it run on your computer when transitioning to mode.

- the operation authentication code generated by the logical operation using a plurality of partial authentication codes generated from the divided programs matches the verification authentication code generated by performing the same logical operation in advance Whether the program is tampered or not is verified.

- the number of verification authenticators stored in advance can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the start time constraint, the consumption of the storage unit (memory) required for storing the verification authenticator decreases.

- the instructions in a computer-readable non-transitory tangible storage medium including computer-executable instructions, the instructions generate a partial authenticator of each of a plurality of divided programs obtained by dividing a program by cryptographic operation. And performing a logical operation using a plurality of the partial authenticators to generate an operational authenticator, and determining whether the operational authenticator matches a verification authenticator obtained in advance. And.

- the above-described computer-readable persistent tangible recording medium is a verification authenticator generated by performing the same logical operation in advance as an operation authenticator generated by a logical operation using a plurality of partial authenticators generated from divided programs. Whether the program is tampered or not is verified by whether or not the two match.

- the number of verification authenticators stored in advance can be smaller than the number of divided programs. Therefore, even if the number of divisions of the program is increased in order to satisfy the start time constraint, the consumption of the storage unit (memory) required for storing the verification authenticator decreases.

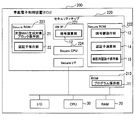

- FIG. 8 is an explanatory view schematically showing an outline of program falsification check processing by the electronic control unit of FIG. 1; 6 is a flowchart for explaining the operation of the electronic control unit of FIG. 1; It is a block diagram explaining the composition of the electronic control unit concerning Embodiment 2 of this indication.

- the electronic control unit 100 includes a ROM (Read Only Memory) 10, a RAM (Random Access Memory) 20, a CPU (Central Processing Unit) 30, an I / O (Input / Output), and a configuration of these. Are composed of bus lines etc.

- ROM Read Only Memory

- RAM Random Access Memory

- CPU Central Processing Unit

- I / O Input / Output

- the main object is to use an encryption operation using a message authentication code (MAC), but in the present disclosure, an operation (SHA-) using a hash function (Hash function) is described. Including 256) and other operations.

- MAC message authentication code

- SHA- hash function

- the ROM 10 includes a program storage unit 11 for tampering check, an encryption operation unit 12, an encryption key storage unit 13, an authenticator operation unit 14, and a verification authenticator storage unit 15.

- the program storage unit 11 (corresponding to the “storage unit” of the present disclosure) stores a program subjected to tampering check as a divided program divided into a plurality of blocks.

- the number of divisions of the program may be determined in consideration of the application of the electronic control unit 100, the activation time, and the like.

- vision is sufficient if the start point of the part of the program is specified by dividing the storage area or the like, and it is not necessary to divide the program itself.

- the encryption operation unit 12 (corresponding to the “encryption operation unit” in the present disclosure) is an area in which an encryption operation program is stored.

- the encryption operation is performed by the CPU (encryption operation unit) 30 which has read the program of the encryption operation unit 12.

- an encryption operation program using a message authentication code such as Cipher-based MAC (CMAC) is stored in the encryption operation unit 12.

- MAC message Authentication Code

- CMAC Cipher-based MAC

- cryptographic operations other than MAC include operations (such as SHA-256) using a HASH function (Hash function).

- a partial authenticator for each of a plurality of divided programs is generated by cryptographic operation.

- the encryption key storage unit 13 is an area in which an encryption key for MAC operation, which is required when the encryption operation unit 12 performs the encryption operation, is stored.

- the encryption key storage unit 13 is not necessary because the encryption key is unnecessary.

- the authenticator operation unit 14 (corresponding to the “verification unit” in the present disclosure) is a logic that generates an operation authenticator using a plurality of partial authenticators generated for each divided program of the program storage unit 11 for tampering check. It is an area in which an arithmetic program is stored.

- the logical operation is performed by the CPU (verification unit) 30 which has read the program of the authenticator operation unit 14.

- the logical operation used in the authenticator operation unit 14 will be described later with reference to FIGS. 2 and 3. In addition, verification of the presence or absence of program falsification will be described later with reference to FIGS. 2 and 3.

- the verification authenticator storage unit 15 (corresponding to the “storage unit” of the present disclosure) is an area in which the verification authenticator of the program to be verified stored in the program storage unit 11 which is the target of tampering verification is stored. is there.

- the verification authenticator is generated by performing predetermined cryptographic computation and logical computation on the program of the program storage unit 11 in advance.

- the electronic control unit 100 may have a function (reprogram function) capable of rewriting the program storage unit 11 stored in the ROM 10.

- a function reprogram function

- the verification authenticator storage unit 15 since the verification authenticator changes as the program storage unit 11 is rewritten, the verification authenticator storage unit 15 also needs to be rewritten.

- the reprogramming function is provided, there is a high possibility of being connected from the outside, so the number of divisions of the program storage unit 11 can be increased without increasing the area required for storing the verification authenticator.

- Device 100 is useful.

- the RAM 20 is provided with a next MAC generation target block storage unit 21 and an authentication code storage unit 22.

- the next MAC generation target block storage unit 21 stores information such as a block number and an address in the ROM 10 that can specify a divided program to be a target of MAC generation next.

- a new authenticator is overwritten and stored in the authenticator storage unit 22 each time an authenticator is generated.

- the CPU 30 is a device that executes a program, and executes each program of the cryptographic computation unit 12 and the authenticator computation unit 14 when verifying program tampering of the program storage unit 11. 2. Tamper Check Process The program tamper check process by the electronic control unit 100 having the above-described configuration will be described with reference to FIG.

- MAC operation is an encryption operation using a message authentication code (MAC), and using the encryption key of the encryption key storage unit 13 as execution of the program of the encryption operation unit 12, blocks of the tamper check area 10A of the ROM 10. It is performed for each of the divided programs of 1 to n. As a result of the MAC operation, MAC1 to MACn (partial authenticators) are generated for each of the divided programs of block 1 to block n.

- MAC1 to MACn partial authenticators

- the generated MAC is, for example, 128 bits in the case of an operation using an encryption algorithm of AES (Advanced Encryption Standard) 128.

- AES Advanced Encryption Standard

- the generated HASH value is 256 bits.

- the ROM 10 is divided into a tampering check area 10A in which the program storage unit 11 in which n partial programs are stored is placed, and a non-tampering check area 10B other than that.

- partial programs divided into blocks 1 to n are stored.

- partial programs of block 1 to block n may be referred to as block 1 to block n as appropriate.

- a verification authenticator is stored in the non-falsification check area 10B.

- the verifier for verification is generated in advance by calculation, and it is compared with the verifier [1-n] (verifier for calculation) whether the blocks 1 to n are tampered or not This data is highly important because it is used to determine Therefore, the non-tamper check area 10B of the ROM 10 is configured as a secure area.

- the secure area is an area where access to stored information is difficult and the function of protecting information is high.

- FIG. 2 shows an example in which the entire non-tamper check area 10B is configured as a secure area.

- the non-falsification check area 10B may not be a secure area but may be an area of an information protection function similar to that of the falsification check area 10A, or a part may be a secure area.

- an encryption operation unit 12 an encryption key storage unit 13, and an authentication code operation unit 14 (see FIG. 1) are also placed.

- 2.2. Logical operation When MACx is calculated by the cryptographic operation of block x (x is an integer of 2 to n), the logical operation of the authenticator and MACx stored in the authenticator storage unit 22 of the RAM 20 is performed to perform authentication The child [1-x] is generated and overwritten on the authenticator storage unit 22. At the same time, the block number x + 1 specifying the block x + 1 is stored in the next MAC generation target block storage unit 21.

- Logical operations include AND (AND operation), NOT of AND (NAND operation), OR (OR operation), NOT of OR (NOR operation), exclusive OR (XOR operation), and exclusive logic

- exclusive OR and negation of exclusive OR do not converge to either 0 or 1 by repetition of logical operation because the number of 0 and 1 in the truth table is the same. Preferred in point. 2.3. Relationship between MAC Operation and Logic Operation MAC operation and logic operation are implemented as described in 2.1 and 2.2, respectively. In the following, when the MACs are generated in order of block numbers, the partial authenticators generated by the MAC operation and the operation authenticators generated by the logical operation are sequentially implemented as to how they are used. The process will be described in order along the processing of blocks 1 to n.

- MAC1 of block 1 is a partial authenticator generated first. Therefore, at the time when MAC1 is generated, it is not possible to perform the logical operation using a plurality of partial authenticators. Therefore, the MAC 1 of the block 1 is stored in the authenticator storage unit 22 of the RAM 20 as the authenticator [1] (arithmetic authenticator). At the same time, the next MAC generation target block of the next MAC generation target block storage unit 21 is set to 2.

- the authentication code [1-2] (operation authentication code) generated by performing the logical operation of the authentication code [1] of the authentication code storage unit 22 and MAC 2 is authenticated. It is overwritten and stored in the child storage unit 22.

- the next MAC generation target block of the next MAC generation target block storage unit 21 is set to 3.

- the authenticator [1] is the same as MAC1, the logical operation of MAC2 and the authenticator [1] is performed using two partial authenticators.

- the authentication code [1-3] (operation authentication code) generated by performing the logical operation of the authentication code [1-2] of the authentication code storage unit 22 and MAC3 is generated. It is overwritten and stored in the authentication code storage unit 22.

- the next MAC generation target block of the next MAC generation target block storage unit 21 is set to 4.

- the authenticator [1-2] is generated by the logical operation using MAC1 and MAC2, the logical operation of the authenticator [1-2] and the MAC3 is performed by three partial authenticators MAC1 and MAC2 And MAC3.

- the “plurality of partial authenticators” used in the logical operation includes the partial authenticator used in the previous logical operation.

- an authentication code [1-n] (operational authentication generated by performing logical operation of the authentication code [1-n-1] of the authentication code storage unit 22 and MACn The child is overwritten and stored in the authenticator storage unit 22.

- the next MAC generation target block of the next MAC generation target block storage unit 21 is initialized to 1.

- the authenticator [1-n-1] is generated by the logical operation using MAC1 to MACn-1

- the logical operation between the authenticator [1-n-1] and the MACn is a partial authenticator. It is performed using all of MAC1 to MACn.

- the authentication code [1-n] is an operation authentication code generated as a result of a logical operation performed using all of MAC1 to MACn (partial authentication code) of block 1 to block n. Therefore, when one of the blocks 1 to n is falsified, the falsification is reflected on the authenticator [1-n] via any one of MAC1 to MACn. Therefore, if there is tampering, the certifier [1-n] does not match the certifier for verification obtained by the operation in advance.

- the electronic control unit 100 performs an operation using all of MAC1 to MACn to generate an authenticator [1-n] (arithmetic authenticator), compares it with the authenticator for verification, and generates the program storage unit 11 (FIG. See if there is any falsification. Therefore, it is sufficient to store one verification authenticator in the verification authenticator storage unit 15 of the ROM 10.

- the number n of blocks is n minus one, which is equal to the number of blocks required for verification for verifying that the program has been tampered with for each divided block.

- the storage capacity of the verification authenticator of can be reduced.

- the storage capacity of (n-1) ⁇ 128 bits can be reduced.

- the effect of reducing the storage capacity of the ROM 10 increases as the number of divisions of the program to be subjected to the tampering verification increases.

- the increase in the number of divided programs is effective to prevent the processing from being wasted when the start processing is interrupted, and to shorten the start time of the electronic control unit 100.

- FIG. 2 the case where there is one verification authenticator is described. As described above, it is preferable to use one verification authenticator from the viewpoint of reducing the storage capacity of the verification authenticator storage unit 15 of the ROM 10.

- the number of verification authenticators stored in the verification authenticator storage unit 15 is not limited to one, and may be plural.

- plural verification authenticators are used, a plurality of blocks 1 to n are used.

- the group is divided into groups, and a verification authenticator for each group is stored in advance in the ROM 10. Then, a verifier for verification by logical operation using all partial verifiers of each group is generated, and compared with the verifier for verification, it is determined whether or not the divided programs included in the group are tampered.

- the authenticator storage unit 22 stores an authenticator (arithmetic authenticator) obtained by the tampering check process until cancellation. Further, in the next MAC generation target block storage unit 21, a block to be a MAC generation target is stored next to the logical operation for which the certifier is obtained. Therefore, it is possible to resume from the next cryptographic operation of the logical operation that has generated the certifier in the falsification check process of the to be aborted. Then, in the logical operation following the resumed cryptographic operation, the certifier of the certifier storage unit 22 can be used, so that the result of the cryptographic processing and the logical operation on the block completed before interruption can be used effectively. .

- the RAM 20 includes a non-initialization region 20A which is not initialized and an initial region 20B which is initialized at the time of startup from the low power consumption mode to the normal mode (Wake Up startup).

- the next MAC generation target block storage unit 21 and the authentication code storage unit 22 are placed in the non-initialization area 20A. Therefore, the information written to the next MAC generation block storage unit 21 and the authentication unit storage unit 22 rewritten each time the authentication unit 1 to the authentication unit [1-n] are calculated is maintained when Wake Up is activated. Be done. Therefore, if a restart occurs during the computation of authenticator 1 to authenticator [1-n], based on the information of the next MAC generation target block storage unit 21 and authenticator storage unit 22 recorded before the restart. And the tamper check process can be resumed.

- the next-to-next MAC generation target block storage unit 21 and the authentication code storage unit 22 may be stored in rewritable non-volatile memory such as EEPROM or Data Flash.

- EEPROM electrically erasable programmable read-only memory

- the non-volatile memory in the above-mentioned example can be used only when the time constraint at the time of starting the electronic control device 100 can be satisfied.

- the present disclosure can also be implemented as an electronic control unit unit including a plurality of electronic control units.

- an electronic control unit having a plurality of electronic control units is used in combination with electronic control units having different time restrictions at the time of start-up. Therefore, it is preferable to make the number of divisions of the division program stored in the storage unit different depending on applications of a plurality of electronic control devices and time restrictions at the time of movement. As a result, it is possible to suppress the consumption of the memory as the entire storage unit in the electronic control unit unit while satisfying the restrictions of the activation times of the electronic control unit. 3.

- Program Tampering Detection Method With reference to FIG. 3, a program tampering detection method by the electronic control unit 100 described above will be described.

- the CPU 30 reads and executes the programs of the cryptographic operation unit 12 and the authenticator operation unit 14 (see FIG. 1), and changes from the low power consumption mode to the normal mode when the electronic control device 100 is started. It is called when migrating.

- the low power consumption mode is a state in which the electronic control unit 100 does not perform part of the processing performed in the normal mode, and the power consumption is smaller than that in the normal mode.

- the sleep mode in which a program being executed is stored in memory and temporarily stopped is an example of the low power consumption mode.

- S10 it is determined whether or not the block number is other than 1 with reference to the block number recorded in the next MAC generation target block storage unit 21 of the RAM 20. Then, if the block number of the next MAC generation target block storage unit 21 is not 1 (if it is 1) (S10: NO), the process proceeds to S20 (encryption operation step), and stores the next MAC generation target block If the block number of the unit 21 is other than 1 (S10: YES), the process proceeds to S50 (encryption operation step).

- the MAC 1 generated in S20 is stored in the authenticator storage unit 22 of the RAM 20 as an authenticator, and the process proceeds to S40 (authenticator operation step).

- the block number obtained by adding 1 to the block number of the partial program for which MAC was generated in S20 is written (set) in the next MAC generation block storage unit 21 of the RAM 20 as the next MAC generation target block. End the process.

- MACx of a divided program of block number x (x is an integer of 2 to n), which is a MAC generation target block, is generated, and the process proceeds to S60 (authenticator operation step).

- the authenticator operation unit 14 performs a logical operation on the MAC generated in S50 and the authenticator [1- (x-1)] stored in the authenticator storage unit 22 of the RAM 20, and the authenticator [ Calculate 1 ⁇ (x)], and shift to S70.

- the authenticator [1-n] stored in the authenticator storage unit 22 in S70 is obtained as a result of logical operation using partial authenticators of all divided programs. It is It can be used as a verification authenticator for verifying whether or not a tampered program is included in all divided programs. Therefore, the process proceeds to S90 (verification step).

- the certifier [1-n] stored in the certifier storage unit 22 is compared with the certifier for verification stored in the certifier storage unit 15 for verification.

- S100 verification step

- S100: YES the process proceeds to S110; if they do not match (S100: YES), the process proceeds to S120.

- the falsification check result is set to no falsification, and the process proceeds to S130.

- the present disclosure can also be implemented as a program that causes a computer to execute the program tampering detection method described above.

- the program is executed when the electronic control device is activated or when transitioning from the low power consumption mode to the normal mode.

- the electronic control unit of the present embodiment it can be obtained by performing logical operation using a plurality of partial authenticators rather than each partial authenticator itself required for each divided program into which the program is divided.

- the operation certifier is compared with the certifier for verification to detect whether the program has been tampered with. This makes it possible to reduce the number of verification authenticators to be stored and to suppress the large consumption of ROM.

- Second Embodiment An embodiment in which the present disclosure is applied to an electronic control unit (ECU) using a security chip will be described.

- the electronic control unit 200 of the present embodiment includes a ROM 210, a security chip 220, a RAM 20, a CPU 30, and I / O and a bus line connecting these components.

- the electronic control unit 200 is different from the electronic control unit 100 in that the configuration includes a ROM 210 and a security chip 220 instead of the ROM 10.

- the configuration includes a ROM 210 and a security chip 220 instead of the ROM 10.

- the program storage unit 11 is disposed in the ROM 210.

- the components other than the program storage unit 11 are placed on the security chip 220 which is highly resistant to tampering (difficulty of analyzing stored data).

- the security chip 220 includes a secure CPU 224, a secure RAM 223, a secure interface (Secure I / F), a hardware IP module (HWIP) 221, and a secure ROM 222.

- the hardware IP module 221 has a cryptographic operation unit 12.

- the secure ROM 222 has an encryption key storage unit 13, an authentication code calculation unit 14, and a verification authentication code storage unit 15.

- the secure (secure) RAM 223 includes a block storage unit for MAC generation next time 21 and an authentication unit storage unit 22.

- the CPU 30 executes the various cryptographic computations of FIG. 2 and the process of the flow of FIG. 3. However, in the present embodiment, the secure CPU 224 executes this.

- the security chip 220 stores the program (and temporary data such as the operation certifier and the next MAC generation target block), the encryption key, and the certifier for verification, which are used for processing for verifying the presence or absence of program tampering.

- the program and temporary data such as the operation certifier and the next MAC generation target block

- the encryption key and the certifier for verification, which are used for processing for verifying the presence or absence of program tampering.

- access to the program (and the temporary data), the encryption key, and the verifier for verification can be prevented.

- Examples of forms of the electronic control device of the present disclosure include semiconductors, electronic circuits, modules, and microcomputers.

- necessary functions such as an antenna and a communication interface may be added to these.

- it is also possible to take a form such as a car navigation system, a smartphone, a personal computer, and a portable information terminal.

- the present disclosure can not only be realized by the above-described dedicated hardware, but also a program recorded in a recording medium such as a memory or a hard disk, and general-purpose hardware having a dedicated or general-purpose CPU, memory, etc. It can be realized as a combination with

- Programs stored in dedicated or general-purpose hardware storage areas can be recorded via recording media or without recording media.

- the electronic control unit according to the present disclosure can be used as an on-vehicle electronic control unit (ECU).

- ECU electronic control unit

- electronic control devices other than those for use in vehicles are also included in the present disclosure.

- each section is expressed as, for example, S10.

- each section can be divided into multiple subsections, while multiple sections can be combined into one section.

- each section configured in this way can be referred to as a device, a module, or a means.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Computer Hardware Design (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Health & Medical Sciences (AREA)

- Bioethics (AREA)

- General Health & Medical Sciences (AREA)

- Power Engineering (AREA)

- Storage Device Security (AREA)

Abstract

電子制御装置は、プログラムを分割した複数の分割プログラム、および検証用認証子を記憶する記憶部(11、15)と、暗号演算により前記複数の分割プログラムそれぞれの部分認証子を生成する暗号演算部(12、13、30、224)と、複数の前記部分認証子を用いた論理演算を行って演算認証子を生成し、前記検証用認証子と前記演算認証子とが一致するか否かによって前記プログラムの改ざんを検証する検証部(14、30、224)とを有する。

Description

本出願は、2017年7月13日に出願された日本特許出願番号2017-136725号に基づくもので、ここにその記載内容を援用する。

本開示は、プログラム改ざんを検知する電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体に関するものである。

車両には、電子制御装置として、エンジン、ハンドル、ブレーキ等の制御を行う制御系ECU(Electronic Control Unit)や、メータやパワーウインドウ等の制御を行うボデー系ECUや、ナビゲーション装置等の情報系ECU等といった異なる種類のECUが搭載されている。これら、車両に搭載される車載ECUのプログラムには、例えば安全性を確保するため、起動時間に厳しい時間的制約が課せられるものが含まれる。

特許文献1には、自動車等の組み込み機器において、OS(Operating System)等が第三者によって改ざんされる危険に対し、意図したOS等のみを動作させるセキュアブート方法の開示が記載されている。同文献に記載のセキュアブート方法の開示は、高速かつ安全にシステムを起動させることを目的として、コンピュータが、システムのプログラム起動毎に、プログラムを複数に区分した部分プログラムのうち、検証対象となる部分プログラムを選択する選択工程と、選択した部分プログラムのハッシュ値を算出する算出工程と、算出したハッシュ値と正解ハッシュ値とが一致するかを判定し、一致する場合に起動処理を継続し、一致しない場合に起動処理を中断する検証工程とを、実行するものである。

このように、特許文献1には、検証対象となるプログラム領域を複数の区分に分割し、各区分単位でプログラムの改ざんの有無の検証を順次実施することで、起動時間の制約を満しつつ、検証すべきすべてのプログラム領域を検証できることが記載されている。

このように、特許文献1には、検証対象となるプログラム領域を複数の区分に分割し、各区分単位でプログラムの改ざんの有無の検証を順次実施することで、起動時間の制約を満しつつ、検証すべきすべてのプログラム領域を検証できることが記載されている。

特許文献1に記載されているセキュアブート方法は、起動時の時間制約を満たすためにプログラム領域を分割した部分プログラムごとに、認証子として生成したハッシュ値と、あらかじめ記憶しておいた検証用認証子である正解ハッシュ値とを比較し、プログラムの改ざんの有無を検証する。

無線インターフェースを経由して外部からの情報が自動車に提供される新たなサービスに伴って、自動車が外部と接続される機会も増える。このため、車載ECUのプログラムが改ざんのリスクも増大するといえる。したがって、安全なシステム起動のために、改ざんの有無を頻繁に検証することが必要になる。例えば、バッテリ接続時に起動する車載ECUの場合、バッテリ接続時にしか起動しないため、次回のバッテリ接続まで起動するタイミングがなく、その間にプログラムが改ざんされると改ざんがあったことに気付くのが遅れてしまう。したがって、スリープモードからのウェイクアップ起動(低消費電力モードから通常モードへの移行)時にも、改ざんの有無の検証を実施するようにすることで、改ざんに早期に気づくことが可能となる。

一般に、スリープからのウェイクアップ起動時間の制約は、通常の起動時間の制約よりも厳しい。このため、スリープからウェイクアップ起動時における時間的制約を満たそうとすると、検証すべきプログラムの領域を細かく分けて、多数の部分プログラムに分割する必要がある。

特許文献1に記載のセキュアブート方法は、各部分プログラムに対して一つずつの検証用認証子(正解ハッシュ値)をあらかじめ記憶しておく必要がある。このため、部分プログラムの数が増加すると、記憶領域に記憶される検証用認証子の数も増加する。したがって、多数の検証用認証子が限られた記憶領域(メモリ)における多くの領域を占めるという問題が発生する。

本開示は、起動時間の制約を満たしつつ、検証用認証子を記憶するために消費される記憶領域を抑制する、改ざんの検証対象プログラムを分割した分割プログラム毎にプログラムの改ざんを検知する処理を行なう電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体を提供することを目的とする。

本開示の第一の態様において、電子制御装置は、プログラムを分割した複数の分割プログラム、および検証用認証子を記憶する記憶部と、暗号演算により前記複数の分割プログラムそれぞれの部分認証子を生成する暗号演算部と、複数の前記部分認証子を用いた論理演算を行って演算認証子を生成し、前記検証用認証子と前記演算認証子とが一致するか否かによって前記プログラムの改ざんを検証する検証部とを有する。

上記の電子制御装置は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、記憶部にあらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少ない電子制御装置となる。

本開示の第二の態様において、プログラム改ざん検知方法は、プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成することと、複数の前記部分認証子を用いて論理演算を行って演算認証子を生成することと、前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定することとを有する。

上記のプログラム改ざん検知方法は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、あらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少なくなる。

本開示の第三の態様において、プログラムは、プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成することと、複数の前記部分認証子を用いて論理演算を行って演算認証子を生成することと、前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定することとを有するプログラム改ざん検知方法をコンピュータに実行させる。

上記のプログラム改ざん検知方法は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、あらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少なくなる。

本開示の第四の態様において、プログラムは、プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成することと、複数の前記部分認証子を用いて論理演算を行って演算認証子を生成することと、前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定することとを有するプログラム改ざん検知方法を、電子制御装置が起動する際にコンピュータに実行させる。

上記のプログラム改ざん検知方法は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、あらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少なくなる。

本開示の第五の態様において、プログラムは、プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成することと、複数の前記部分認証子を用いて論理演算を行って演算認証子を生成することと、前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定することとを有するプログラム改ざん検知方法を、電子制御装置の低消費電力モードから通常モードに移行する際にコンピュータに実行させる。

上記のプログラム改ざん検知方法は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、あらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少なくなる。

本開示の第六の態様において、コンピュータにより実行されるインストラクションを含むコンピュータ読み出し可能持続的有形記録媒体において、当該インストラクションは、プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成することと、複数の前記部分認証子を用いて論理演算を行って演算認証子を生成することと、前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定することとを有する。

上記のコンピュータ読み出し可能持続的有形記録媒体は、分割プログラムから生成された部分認証子を複数用いた論理演算によって生成された演算認証子と、あらかじめ同じ論理演算を行って生成された検証用認証子と、が一致するか否かにより、プログラムの改ざんの有無を検証する。この構成によって、あらかじめ記憶しておく検証用認証子の数を分割プログラムの数よりも少なくすることができる。したがって、起動時間の制約を満たすためにプログラムの分割数を増やしても、検証用認証子の記憶に要する記憶部(メモリ)の消費量が少なくなる。

本開示についての上記目的およびその他の目的、特徴や利点は、添付の図面を参照しながら下記の詳細な記述により、より明確になる。その図面は、

本開示の実施形態1に係る電子制御装置の構成を説明するブロック図であり、

図1の電子制御装置によるプログラムの改ざんチェック処理の概要を模式的に示す説明図であり、

図1の電子制御装置の動作を説明するフローチャートであり、

本開示の実施形態2に係る電子制御装置の構成を説明するブロック図である。

(実施形態1)

1.電子制御装置(ECU)の構成

本実施形態の電子制御装置の構成について以下に説明する。

1.電子制御装置(ECU)の構成

本実施形態の電子制御装置の構成について以下に説明する。

図1に示すように、電子制御装置100は、ROM(Read Only Memory)10、RAM(Random Access Memory)20、CPU(Central Processing Unit)30、I/O(Input / Output)、およびこれらの構成を接続するバスラインなどから構成されている。

なお、本実施形態は、メッセージ認証コード(Message Authentication Code、MAC)を用いた暗号演算を用いることを主眼として記載しているが、本開示はHASH関数(Hash function)を用いた演算(SHA-256など)をはじめ、その他の演算も含むものである。

ROM10は、改ざんチェック用のプログラム保存部11、暗号演算部12、暗号鍵保存部13、認証子演算部14、および検証用認証子保存部15を備えている。

プログラム保存部11(本開示の「記憶部」に相当)には、改ざんチェック対象のプログラムが、複数のブロックに分割された分割プログラムとして記憶されている。プログラムの分割数は、電子制御装置100の用途や起動時間等を考慮して決定すればよい。

なお、「分割」とは、記憶領域で区切るなどして、プログラムの部分の開始点が特定されていればよく、プログラム自体を分割する必要は必ずしもない。

暗号演算部12(本開示の「暗号演算部」に相当)は、暗号演算プログラムが保存された領域である。暗号演算は、暗号演算部12のプログラムを読み込んだCPU(暗号演算部)30によって実施される。本実施形態では、CMAC(Cipher-based MAC)などのメッセージ認証コード(Message Authentication Code、MAC)を用いた暗号演算プログラムが暗号演算部12に保存されている。MAC以外の暗号演算としては、HASH関数(Hash function)を用いた演算(SHA-256など)が挙げられる。暗号演算により、複数の分割プログラムそれぞれの部分認証子を生成する。

暗号鍵保存部13は、暗号演算部12が暗号演算を実施する際に必要となる、MAC演算の暗号鍵が記憶された領域である。なお、暗号演算部12が暗号演算プログラムとして、HASH関数(Hash function)を用いた演算を行う場合は、暗号鍵は不要なので暗号鍵保存部13を用いる必要はない。

認証子演算部14(本開示の「検証部」に相当)は、改ざんチェック用のプログラム保存部11の各分割プログラムについて生成された、複数の部分認証子を用いて演算認証子を生成する論理演算プログラムが記憶された領域である。論理演算は、認証子演算部14のプログラムを読み込んだCPU(検証部)30によって実施される。認証子演算部14において用いられる論理演算については、図2および図3を参照して後に説明する。また、プログラムの改ざんの有無の検証についても、図2および図3を参照して後に説明する。

検証用認証子保存部15(本開示の「記憶部」に相当)は、改ざんを検証する対象であるプログラム保存部11に記憶された検証対象のプログラムの検証用認証子が保存された領域である。検証用認証子は、プログラム保存部11のプログラムについて、所定の暗号演算および論理演算をあらかじめ行うことにより生成されたものである。

電子制御装置100は、ROM10に保存されているプログラム保存部11を書き換え可能な機能(リプログラム機能)を備えていてもよい。この場合、プログラム保存部11の書き換えにより、検証用認証子も変化するから、併せて検証用認証子保存部15も書き換える必要がある。リプログラム機能を備えている場合、外部から接続される可能性が高くなるから、検証用認証子の記憶に要する領域を増大させることなく、プログラム保存部11の分割数を増やすことができる電子制御装置100は有用である。

RAM20は、次回MAC生成対象ブロック保存部21および認証子保存部22を備えている。

次回MAC生成対象ブロック保存部21には、ブロック番号やROM10におけるアドレス等、次にMAC生成の対象となる分割プログラムを特定できる情報が保存される。

認証子保存部22には、認証子が生成される毎に、新たな認証子が上書き保存される。

CPU30は、プログラムを実行する装置であり、プログラム保存部11のプログラム改ざんを検証する際には、暗号演算部12および認証子演算部14の各プログラムを実行する。

2.改ざんチェック処理

上述した構成を備えた電子制御装置100による、プログラムの改ざんチェック処理について、図2を参照して説明する。

2.改ざんチェック処理

上述した構成を備えた電子制御装置100による、プログラムの改ざんチェック処理について、図2を参照して説明する。

図2に示すように、ROM10のプログラム保存部11に書かれたプログラムをチェック対象とする改ざんチェック処理では、MAC演算および論理演算が行われる。以下、MAC演算および論理演算について順に説明する。

2.1.MAC演算

MAC演算は、メッセージ認証コード(MAC)を用いた暗号演算であり、暗号演算部12のプログラムの実行として、暗号鍵保存部13の暗号鍵を用いて、ROM10の改ざんチェック領域10Aのブロック1~ブロックnの各分割プログラムを対象として行われる。MAC演算の結果として、ブロック1~ブロックnの各分割プログラムそれぞれに対してMAC1~MACn(部分認証子)が生成される。生成されたMACは、例えば、AES(Advanced Encryption Standard)128の暗号アルゴリズムを用いた演算の場合は、128ビットである。なお、SHA(Secure Hash Algorithm)-256のHASH関数を用いた演算の場合は、生成されるHASH値は、256ビットである。

2.1.MAC演算

MAC演算は、メッセージ認証コード(MAC)を用いた暗号演算であり、暗号演算部12のプログラムの実行として、暗号鍵保存部13の暗号鍵を用いて、ROM10の改ざんチェック領域10Aのブロック1~ブロックnの各分割プログラムを対象として行われる。MAC演算の結果として、ブロック1~ブロックnの各分割プログラムそれぞれに対してMAC1~MACn(部分認証子)が生成される。生成されたMACは、例えば、AES(Advanced Encryption Standard)128の暗号アルゴリズムを用いた演算の場合は、128ビットである。なお、SHA(Secure Hash Algorithm)-256のHASH関数を用いた演算の場合は、生成されるHASH値は、256ビットである。

ROM10は、n個の部分プログラムが保存されたプログラム保存部11が置かれた改ざんチェック領域10Aと、それ以外の非改ざんチェック領域10Bとに分かれている。

改ざんチェック領域10Aには、ブロック1~ブロックnに分割された部分プログラムが保存されている。以下では、ブロック1~ブロックnの部分プログラムを、適宜、ブロック1~ブロックnということもある。

非改ざんチェック領域10Bには、検証用認証子が保存されている。検証用認証子は、演算によってあらかじめ生成されたものであり、認証子[1-n](演算用認証子)と比較して、ブロック1~ブロックnが改ざんされたものが含まれるか否かの判定に用いられるから、重要性の高いデータである。このため、ROM10の非改ざんチェック領域10Bはセキュア領域として構成されている。セキュア領域とは、記憶されている情報へのアクセスが困難であって、情報を保護する機能が高い領域をいう。

図2には、非改ざんチェック領域10Bの全部がセキュア領域として構成された例を示す。しかし、非改ざんチェック領域10Bはセキュア領域ではなく、改ざんチェック領域10Aと同程度の情報保護機能の領域であってもよい、また、一部をセキュア領域としてもよい。

なお、図2では省略しているが、ROM10の非改ざんチェック領域10Bには、暗号演算部12、暗号鍵保存部13および認証子演算部14(図1参照)も置かれている。

2.2.論理演算

ブロックx(xは2~nの整数)の暗号演算によってMACxが算出されると、RAM20の認証子保存部22に記憶されている認証子とMACxとの論理演算が行われて、認証子[1-x]が生成され、認証子保存部22に上書きされる。併せて、次回MAC生成対象ブロック保存部21にブロックx+1を特定するブロック番号x+1が保存される。

2.2.論理演算

ブロックx(xは2~nの整数)の暗号演算によってMACxが算出されると、RAM20の認証子保存部22に記憶されている認証子とMACxとの論理演算が行われて、認証子[1-x]が生成され、認証子保存部22に上書きされる。併せて、次回MAC生成対象ブロック保存部21にブロックx+1を特定するブロック番号x+1が保存される。

論理演算としては、論理積(AND演算)、論理積の否定(NAND演算)、論理和(OR演算)、論理和の否定(NOR演算)、排他的論理和(XOR演算)および、排他的論理和の否定(XNOR演算=一致論理)が挙げられる。これらのうちでは、排他的論理和および排他的論理和の否定が、真理値表における0と1との数が同じであることから、論理演算の繰り返しによって、0または1の一方に収束しないという点において好ましい。

2.3.MAC演算と論理演算との関係

MAC演算および論理演算はそれぞれ、2.1および2.2で説明したように実施される。以下では、MACがブロック番号順に生成される場合、MAC演算により生成される部分認証子と、論理演算により生成される演算認証子とが、それぞれ、どのように用いられるかについて、順次実施されるブロック1~ブロックnの演算処理に沿って順に説明する。

2.3.MAC演算と論理演算との関係

MAC演算および論理演算はそれぞれ、2.1および2.2で説明したように実施される。以下では、MACがブロック番号順に生成される場合、MAC演算により生成される部分認証子と、論理演算により生成される演算認証子とが、それぞれ、どのように用いられるかについて、順次実施されるブロック1~ブロックnの演算処理に沿って順に説明する。

ブロック1のMAC1は、最初に生成される部分認証子である。このため、MAC1が生成された時点では、複数の部分認証子を用いた論理演算を行うことができない。そこで、認証子[1](演算認証子)として、ブロック1のMAC1がRAM20の認証子保存部22に保存される。併せて、次回MAC生成対象ブロック保存部21の次回MAC生成対象ブロックを2にする。

続いて、ブロック2のMAC2が生成されると、認証子保存部22の認証子[1]とMAC2との論理演算を行って生成された認証子[1-2](演算認証子)が認証子保存部22に上書き保存される。併せて、次回MAC生成対象ブロック保存部21の次回MAC生成対象ブロックを3にする。

認証子[1]はMAC1と同一だから、MAC2と認証子[1]との論理演算は、2つの部分認証子を用いて行われたものである。

さらに、ブロック3のMAC3が生成されると、認証子保存部22の認証子[1-2]とMAC3との論理演算を行って生成された認証子[1-3](演算認証子)が認証子保存部22に上書き保存される。併せて、次回MAC生成対象ブロック保存部21の次回MAC生成対象ブロックを4にする。

認証子[1-2]は、MAC1とMAC2とを用いた論理演算により生成されたものであるから、認証子[1-2]とMAC3との論理演算は、3つの部分認証子MAC1、MAC2およびMAC3を用いて行われたものである。本開示において、論理演算に用いられた「複数の部分認証子」には、先の論理演算で用いられた部分認証子が含まれる。

ブロックXのMACX(X=4~n-1)が生成された場合の演算処理は、ブロック3と同様である。

最後に、ブロックnのMACnが生成されると、認証子保存部22の認証子[1-n-1]とMACnとの論理演算を行って生成された認証子[1-n](演算認証子)が認証子保存部22に上書き保存される。併せて、次回MAC生成対象ブロック保存部21の次回MAC生成対象ブロックを1に初期化する。

認証子[1-n-1]は、MAC1~MACn-1を用いた論理演算により生成されたものであるから、認証子[1-n-1]とMACnとの論理演算は、部分認証子MAC1~MACnのすべてを用いて行われたものである。

認証子[1-n]は、ブロック1~ブロックnのMAC1~MACn(部分認証子)のすべてを用いて行われた論理演算の結果として、生成された演算認証子である。したがって、ブロック1~ブロックnのいずれかが改ざんされた場合、MAC1~MACnのいずれかを介して、認証子[1-n]に当該改ざんが反映される。したがって、改ざんがある場合、認証子[1-n]と、事前の演算によって求められた検証用認証子とは一致しない。

そこで、認証子[1-n]と検証用認証子とを比較して、一致しない場合にはプログラムの改ざん有、一致する場合にはプログラムの改ざん無、と判断することができる。当該比較によって、プログラムの改ざん有と判断した場合には、電子制御装置100(図1参照)の起動を中止したり、警告表示を出したりする。

電子制御装置100は、MAC1~MACnのすべてを用いた演算を行って認証子[1-n](演算認証子)生成し、検証用認証子とを比較して、プログラム保存部11(図1参照)の改ざんの有無を判断する。このため、ROM10の検証用認証子保存部15には一つの検証用認証子を保存すれば足りる。

したがって、従来のように、分割したブロック毎にプログラムの改ざんの有無を検証する、ブロック数と同じ数の検証用認証子が必要なものよりも、ブロック数nから1を引いたn-1個の検証用認証子の記憶容量を削減することができる。

例えば、部分認証子であるMAC1~MACnとして128ビットのものを用いた場合、(n-1)×128ビットの記憶容量を削減することができる。電子制御装置100によれば、改ざん検証の対象となるプログラムの分割数が多くなるほど、ROM10の記憶容量の削減効果が高くなる。プログラムの分割数の増大は、起動処理が中断した場合に、それまでの処理が無駄になることを防止し、電子制御装置100の起動時間を短縮するために有効である。

図2では、検証用認証子が一つである場合記載した。このように、検証用認証子を一つにすることは、ROM10の検証用認証子保存部15の記憶容量を削減する観点から好ましいといえる。

ただし、検証用認証子保存部15に保存される検証用認証子の数は、一つに限られず、複数としてもよい、検証用認証子を複数とする場合、ブロック1~ブロックnを複数のグループに分け、各グループ用の検証用認証子をあらかじめROM10に記憶しておく。そして、各グループの部分認証子をすべて用いた論理演算による検証用認証子を生成し、検証用認証子と比較し、当該グループに含まれる分割プログラムの改ざんの有無を判断する。

認証子[1]~認証子[1-n]の算出を連続して、一度で行うことが出来ない場合、暗号演算や論理演算の途中で改ざんチェック処理が中止される。この場合、認証子保存部22には、中止されるまでの改ざんチェック処理によって得られた認証子(演算認証子)が保存されている。また、次回MAC生成対象ブロック保存部21には、認証子が得られた論理演算の次に、MAC生成対象となるブロックが保存されている。したがって、中止される迄の改ざんチェック処理で、認証子を生成した論理演算の次の暗号演算から再開することができる。そして、再開した暗号演算に続く論理演算では、認証子保存部22の認証子を用いることができため、中断されるまでに完了したブロックに対する暗号処理および論理演算の結果を有効に用いることができる。

したがって、プログラムを分割して、改ざんチェック処理を行うことによって、プログラム検証に要する時間を短縮することが可能になる。

RAM20は、低消費電力モードから通常モードへの起動(Wake Up起動)において、初期化されない非初期化領域20Aと、初期化される初期領域20Bとからなっている。非初期化領域20Aには、次回MAC生成対象ブロック保存部21と認証子保存部22とが置かれている。このため、認証子1~認証子[1-n]が算出される毎に書き換えられた次回MAC生成対象ブロック保存部21、および認証子保存部22に書き込まれた情報は、Wake Up起動時に維持される。したがって、認証子1~認証子[1-n]の演算途中で、再起動が生じた場合、再起動前に記録された次回MAC生成対象ブロック保存部21および認証子保存部22の情報に基づいて、改ざんチェック処理を再開することができる。

次回MAC生成対象ブロック保存部21および認証子保存部22が保存される領域は、Wake Up起動時に初期化されない領域であれば、改ざんチェック処理の中断から素早く再開することができる。このため、次回MAC生成対象ブロック保存部21および認証子保存部22を、EEPROMやData Flash等の書き換え可能な不揮発性メモリに保存してもよい。ただし、処理速度は、例示の不揮発性メモリよりもRAM20の方が速いため、電子制御装置100の起動時における時間制約を満たすことができる場合に限って、前記例示の不揮発性メモリを使用できる。

本開示は、電子制御装置を複数備えた電子制御装置ユニットとして実施することもできる。電子制御装置を複数備えた電子制御装置ユニットは、起動時における時間的制約が異なる電子制御装置が組み合わせて用いられることが多い。したがって、記憶部に記憶されている分割プログラムの分割数を、複数の電子制御装置の用途や、移動時の時間的制約に応じて、異ならせることが好ましい。これにより、電子制御装置の各起動時間の制約を満たしつつ、電子制御装置ユニットにおける記憶部全体としてメモリの消費量を抑制することができる。

3.プログラム改ざん検知方法

図3を参照して、上述した電子制御装置100によるプログラム改ざん検知方法について、説明する。

3.プログラム改ざん検知方法

図3を参照して、上述した電子制御装置100によるプログラム改ざん検知方法について、説明する。

プログラム改ざん検知方法は、CPU30が暗号演算部12および認証子演算部14(図1参照)のプログラムを読み込んで実行するものであり、電子制御装置100の起動時、低消費電力モードから通常モードに移行する際等にコールされる。低消費電力モードは、電子制御装置100が、通常モードにおいて行う処理の一部を行わない、消費電力が通常モードよりも小さい状態をいう。実行中のプログラムがメモリに保存され一時的に停止するスリープモードは、低消費電力モードの一例である。

S10では、RAM20の次回MAC生成対象ブロック保存部21に記録されているブロック番号を参照して、ブロック番号が1以外であるか否かが判定される。そして、次回MAC生成対象ブロック保存部21のブロック番号が1以外ではない場合(1である場合)には(S10:NO)S20(暗号演算ステップ)に処理が移行され、次回MAC生成対象ブロック保存部21のブロック番号が1以外である場合には(S10:YES)S50(暗号演算ステップ)に移行する。

S20では、MAC生成対象ブロックであるブロック1の分割プログラムのMAC1を生成し、S30に移行する。

S30では、S20で生成されたMAC1をRAM20の認証子保存部22に、認証子として記憶し、S40(認証子演算ステップ)に移行する。

S40では、RAM20の次回MAC生成対象ブロック保存部21に、次回MAC生成対象ブロックとして、S20においてMACを生成した部分プログラムのブロック番号に1を加えたブロック番号を書き込んで(設定して)、本処理を終了する。

S50では、MAC生成対象ブロックである、ブロック番号x(xは2~nの整数)の分割プログラムのMACxを生成して、S60(認証子演算ステップ)に移行する。

S60では、認証子演算部14が、S50で生成されたMACとRAM20の認証子保存部22に記憶されている認証子[1-(x-1)]との論理演算を行い、認証子[1-(x)]を算出し、S70に移行する。

S70では、RAM20の認証子保存部22に、生成された認証子[1-x]を記憶し、S80に移行する。

S80では、S50でMACが生成されたブロックが最終ブロックか否か、すなわち、MACが生成されたブロックのブロック番号xが、分割プログラムのブロック数nと等しい(x=n)か否かが判断される。

x=nである場合には(S80:Yes)、S70で認証子保存部22に記憶された認証子[1-n]は、すべての分割プログラムの部分認証子を用いた論理演算の結果得られたものである。すべての分割プログラムのなかに、改ざんされたプログラムが含まれるか否かを検証する検証用認証子として用いることができる。そこで、S90(検証ステップ)に移行する。

x=nでない場合には、S40に移行する。

S90では、認証子保存部22に保存されている認証子[1-n]と、検証用認証子保存部15に保存されている検証用認証子と、を比較する。

S100(検証ステップ)では、S90において比較した値が一致したか否を判断する。

一致する場合には(S100:YES)S110に処理が移行され、一致しない場合には(S100:YES)S120に処理が移行される。

一致する場合には(S100:YES)S110に処理が移行され、一致しない場合には(S100:YES)S120に処理が移行される。

S110では、改ざんチェック結果を改ざんなしに設定し、S130に移行する。

S120では、改ざんチェック結果を改ざんありに設定し、S130に移行する。

S130では、次回MAC生成対象ブロック保存部21のブロック番号を1に初期化して、本処理を終了する。

本開示は、上述したプログラム改ざん検知方法をコンピュータに実行させるプログラムとして実施することもできる。当該プログラムは、電子制御装置が起動する際や、低消費電力モードから通常モードに移行する際に実行される。

以上のように、本実施形態の電子制御装置によれば、プログラムを分割した分割プログラム毎に必要となる各部分認証子そのものではなく、複数の部分認証子を用いて論理演算を行って得られる演算認証子を検証用認証子との比較対象とし、プログラムの改ざんの有無を検知する。これにより、記憶すべき検証用認証子の数を削減し、ROMの大量消費を抑えることが可能になる。

(実施形態2)

セキュリティチップを利用する電子制御装置(ECU)に本開示を適用する形態について説明する。

(実施形態2)

セキュリティチップを利用する電子制御装置(ECU)に本開示を適用する形態について説明する。

図4に示すように、本実施形態の電子制御装置200は、ROM210、セキュリティチップ220、RAM20、CPU30、およびI/Oおよびこれらの構成を接続するバスラインを備えている。

電子制御装置200は、ROM10に代えて、ROM210およびセキュリティチップ220を備えている構成において、電子制御装置100と異なっている。ROM10の各部のうち、ROM210に配置されているのはプログラム保存部11のみである。プログラム保存部11以外は、耐タンパー性(記憶データを解析する困難さ)が高いセキュリティチップ220に置かれている。

セキュリティチップ220は、セキュア(Secure)CPU224、セキュア(Secure)RAM223、セキュアインターフェース(Secure I/F)、ハードウェアIPモジュール(HWIP)221、およびセキュア(Secure)ROM222を備えている。ハードウェアIPモジュール221は、暗号演算部12を有している。セキュア(Secure)ROM222は、暗号鍵保存部13、認証子演算部14および検証用認証子保存部15を有している。セキュア(Secure)RAM223は、次回MAC生成対象ブロック保存部21、および認証子保存部22を有している。そして、実施形態1においては、図2の各種暗号演算や図3のフローの処理はCPU30が実行していたが、本実施形態においてはセキュア(Secure)CPU224がこれを実行する。

以上のように、プログラム改ざんの有無を検証する処理に用いられるプログラム(および演算認証子や次回MAC生成対象ブロック等の一時データ)、暗号鍵、および検証用認証子をセキュリティチップ220に記憶することにより、これらプログラム(および上記一時データ)、暗号鍵、および検証用認証子にアクセスされることを防止することができる。

本開示の電子制御装置の形態の例として、半導体、電子回路、モジュール、マイクロコンピュータが挙げられる。またこれらにアンテナや通信用インターフェースなど、必要な機能を追加してもよい。また、カーナビゲーションシステム、スマートフォン、パーソナルコンピュータ、携帯情報端末のような形態をとることも可能である。

加えて、本開示は、上述の専用のハードウェアで実現できるだけでなく、メモリやハードディスク等の記録媒体に記録したプログラム、及びこれを実行可能な専用又は汎用CPU及びメモリ等を有する汎用のハードウェアとの組み合わせとしても実現できる。

専用や汎用のハードウェアの記憶領域(外部記憶装置(ハードディスク、USBメモリ等)、内部記憶装置(RAM,ROM等))に格納されるプログラムは、記録媒体を介して、あるいは記録媒体を介さずにサーバから通信回線を経由して上述の専用又は汎用のハードウェア(本開示の「コンピュータ」に相当」に提供することもできる。これにより、プログラムのアップグレードを通じて常に最新の機能を提供することができる。

本開示にかかる電子制御装置は、車載用電子制御装置(ECU)として用いることができる。もちろん、車載用以外の電子制御装置も本開示に含むものである。

ここで、この出願に記載されるフローチャート、あるいは、フローチャートの処理は、複数のセクション(あるいはステップと言及される)から構成され、各セクションは、たとえば、S10と表現される。さらに、各セクションは、複数のサブセクションに分割されることができる、一方、複数のセクションが合わさって一つのセクションにすることも可能である。さらに、このように構成される各セクションは、デバイス、モジュール、ミーンズとして言及されることができる。

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

Claims (12)

- プログラムを分割した複数の分割プログラム、および検証用認証子を記憶する記憶部(11、15)と、

暗号演算により前記複数の分割プログラムそれぞれの部分認証子を生成する暗号演算部(12、13、30、224)と、

複数の前記部分認証子を用いた論理演算を行って演算認証子を生成し、前記検証用認証子と前記演算認証子とが一致するか否かによって前記プログラムの改ざんを検証する検証部(14、30、224)と、

を有する電子制御装置。 - 前記記憶部(11)に記憶されている前記検証用認証子が一つであり、

前記検証部(14、30、224)が、すべての前記部分認証子を用いた論理演算を行って一つの演算認証子を生成し、

前記検証部(14、30、224)は、前記一つの検証用認証子と前記一つの演算認証子とが一致するか否かによって前記プログラムの改ざんの有無を検証する、

請求項1に記載の電子制御装置。 - 前記検証部(14、30、224)が行う前記論理演算が、排他的論理和(XOR演算)または排他的論理和の否定(XNOR演算)であり、

排他的論理和は、XOR演算と定義され、

排他的論理和の否定は、XNOR演算と定義される、

請求項1または2に記載の電子制御装置。 - プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成すること(S20、S50)と、

複数の前記部分認証子を用いて論理演算を行って演算認証子を生成すること(S60)と、

前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定すること(S90、S100)と、

を有するプログラム改ざん検知方法。 - 電子制御装置が起動する際に、部分認証子の生成と、演算認証子の生成と、判定を実行する、

請求項4に記載のプログラム改ざん検知方法。 - 電子制御装置が低消費電力モードから通常モードに移行する際に、部分認証子の生成と、演算認証子の生成と、判定を実行する、

請求項4に記載のプログラム改ざん検知方法。 - プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成すること(S20、S50)と、

複数の前記部分認証子を用いて論理演算を行って演算認証子を生成すること(S60)と、

前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定すること(S90、S100)と、

を有するプログラム改ざん検知方法をコンピュータに実行させるプログラム。 - プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成すること(S20、S50)と、

複数の前記部分認証子を用いて論理演算を行って演算認証子を生成すること(S60)と、

前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定すること(S90、S100)と、

を有するプログラム改ざん検知方法を電子制御装置が起動する際にコンピュータに実行させるプログラム。 - プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成すること(S20、S50)と、

複数の前記部分認証子を用いて論理演算を行って演算認証子を生成すること(S60)と、

前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定すること(S90、S100)と、

を有するプログラム改ざん検知方法を電子制御装置の低消費電力モードから通常モードに移行する際にコンピュータに実行させるプログラム。 - コンピュータにより実行されるインストラクションを含むコンピュータ読み出し可能持続的有形記録媒体において、当該インストラクションは、

プログラムを分割した複数の分割プログラムそれぞれの部分認証子を暗号演算により生成すること(S20、S50)と、

複数の前記部分認証子を用いて論理演算を行って演算認証子を生成すること(S60)と、

前記演算認証子と、あらかじめ求めた検証用認証子とが一致するか否かを判定すること(S90、S100)とを有する、

コンピュータ読み出し可能持続的有形記録媒体。 - 電子制御装置が起動する際に、コンピュータは、当該インストラクションを実行する、

請求項10に記載のコンピュータ読み出し可能持続的有形記録媒体。 - 電子制御装置が低消費電力モードから通常モードに移行する際に、コンピュータは、当該インストラクションを実行する、

請求項10に記載のコンピュータ読み出し可能持続的有形記録媒体。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US16/738,927 US11392722B2 (en) | 2017-07-13 | 2020-01-09 | Electronic control device, program falsification detection method, and computer readable non- transitory tangible storage medium |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017136725A JP6949416B2 (ja) | 2017-07-13 | 2017-07-13 | 電子制御装置、プログラム改ざん検知方法 |

| JP2017-136725 | 2017-07-13 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US16/738,927 Continuation US11392722B2 (en) | 2017-07-13 | 2020-01-09 | Electronic control device, program falsification detection method, and computer readable non- transitory tangible storage medium |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2019012952A1 true WO2019012952A1 (ja) | 2019-01-17 |

Family

ID=65002583

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2018/023808 WO2019012952A1 (ja) | 2017-07-13 | 2018-06-22 | 電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US11392722B2 (ja) |

| JP (1) | JP6949416B2 (ja) |

| WO (1) | WO2019012952A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113646760A (zh) * | 2019-04-16 | 2021-11-12 | 华为技术有限公司 | 一种软件程序运行检查方法、电子设备及存储介质 |

| DE112020005818T5 (de) | 2020-01-28 | 2022-09-08 | Mitsubishi Electric Corporation | Authentifikatorverwaltungsvorrichtung, authentifikatorverwaltungsprogramm und authentifikatorverwaltungsverfahren |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7178500B2 (ja) * | 2019-07-23 | 2022-11-25 | 株式会社ソニー・インタラクティブエンタテインメント | アクセス制御装置、アクセス制御方法及びプログラム |

| JP2022142263A (ja) | 2021-03-16 | 2022-09-30 | 富士フイルムビジネスイノベーション株式会社 | 情報処理装置及び情報処理プログラム |

| JP7427697B2 (ja) * | 2022-02-08 | 2024-02-05 | 本田技研工業株式会社 | 電子機器監視装置、移動体、及び電子機器監視方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015090682A (ja) * | 2013-11-07 | 2015-05-11 | キヤノン株式会社 | 画像形成装置、その制御方法及びプログラム |

| WO2016185577A1 (ja) * | 2015-05-20 | 2016-11-24 | 富士通株式会社 | プログラム検証方法、検証プログラム、及び情報処理装置 |

| JP2017509082A (ja) * | 2014-03-25 | 2017-03-30 | オベルトゥル テクノロジOberthur Technologies | 不揮発性メモリ又はセキュア素子へのデータの読み込みを安全に行うこと |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3763477A (en) * | 1971-08-02 | 1973-10-02 | Bell Telephone Labor Inc | Magnetic domain logic control arrangement |

| US20040189713A1 (en) * | 2001-10-31 | 2004-09-30 | Metacyber.Net | Computer-based user interface for a memory-resident rapid comprehension document for original source information |

| JP4732921B2 (ja) * | 2006-02-24 | 2011-07-27 | アルパイン株式会社 | プログラム正当性検証装置 |

| US8949600B2 (en) * | 2006-10-27 | 2015-02-03 | Qualcomm Incorporated | Composed message authentication code |

| US8453206B2 (en) * | 2006-11-09 | 2013-05-28 | Panasonic Corporation | Detecting unauthorized tampering of a program |

| WO2010110605A2 (ko) * | 2009-03-25 | 2010-09-30 | 엘지전자 주식회사 | Iptv 수신기 및 그의 컨텐트 다운로드 방법 |

| JP2012078953A (ja) | 2010-09-30 | 2012-04-19 | Kyocera Mita Corp | 改ざん検知装置及び改ざん検知方法 |

| US8780635B2 (en) * | 2012-11-09 | 2014-07-15 | Sandisk Technologies Inc. | Use of bloom filter and improved program algorithm for increased data protection in CAM NAND memory |

| JP2015022521A (ja) | 2013-07-19 | 2015-02-02 | スパンション エルエルシー | セキュアブート方法、組み込み機器、セキュアブート装置およびセキュアブートプログラム |

| US20150033016A1 (en) * | 2013-07-23 | 2015-01-29 | Battelle Memorial Institute | Systems and methods for securing real-time messages |

| JP6244759B2 (ja) * | 2013-09-10 | 2017-12-13 | 株式会社ソシオネクスト | セキュアブート方法、半導体装置、及び、セキュアブートプログラム |

| KR102509594B1 (ko) * | 2016-06-28 | 2023-03-14 | 삼성전자주식회사 | 어플리케이션 코드의 위변조 여부 탐지 방법 및 이를 지원하는 전자 장치 |

| US10075425B1 (en) * | 2016-08-26 | 2018-09-11 | Amazon Technologies, Inc. | Verifiable log service |

| US10558812B2 (en) * | 2017-06-21 | 2020-02-11 | Microsoft Technology Licensing, Llc | Mutual authentication with integrity attestation |

-

2017

- 2017-07-13 JP JP2017136725A patent/JP6949416B2/ja active Active

-

2018

- 2018-06-22 WO PCT/JP2018/023808 patent/WO2019012952A1/ja active Application Filing

-

2020

- 2020-01-09 US US16/738,927 patent/US11392722B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015090682A (ja) * | 2013-11-07 | 2015-05-11 | キヤノン株式会社 | 画像形成装置、その制御方法及びプログラム |

| JP2017509082A (ja) * | 2014-03-25 | 2017-03-30 | オベルトゥル テクノロジOberthur Technologies | 不揮発性メモリ又はセキュア素子へのデータの読み込みを安全に行うこと |

| WO2016185577A1 (ja) * | 2015-05-20 | 2016-11-24 | 富士通株式会社 | プログラム検証方法、検証プログラム、及び情報処理装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113646760A (zh) * | 2019-04-16 | 2021-11-12 | 华为技术有限公司 | 一种软件程序运行检查方法、电子设备及存储介质 |

| DE112020005818T5 (de) | 2020-01-28 | 2022-09-08 | Mitsubishi Electric Corporation | Authentifikatorverwaltungsvorrichtung, authentifikatorverwaltungsprogramm und authentifikatorverwaltungsverfahren |

Also Published As

| Publication number | Publication date |

|---|---|

| US20200151361A1 (en) | 2020-05-14 |

| JP2019020872A (ja) | 2019-02-07 |

| JP6949416B2 (ja) | 2021-10-13 |

| US11392722B2 (en) | 2022-07-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2019012952A1 (ja) | 電子制御装置、プログラム改ざん検知方法、プログラム改ざん検知方法のプログラム、およびコンピュータ読み出し可能持続的有形記録媒体 | |

| JP6373888B2 (ja) | 情報処理装置及び制御方法 | |

| JP2021149964A (ja) | リモートコンピューティングデバイス上に存在するソフトウェアの検証 | |

| JP7038185B2 (ja) | レジスタ内容のインテグリティを検証するシステム、および、その方法 | |

| CN109445705B (zh) | 固件认证方法及固态硬盘 | |

| JP2022109024A (ja) | 車両制御システム | |

| JP5718373B2 (ja) | 不揮発性メモリのメモリブロックを検査する方法 | |

| CN113177201A (zh) | 程序校验、签名方法及装置、soc芯片 | |

| CN109753788B (zh) | 内核运行时的完整性校验方法及计算机可读存储介质 | |

| US8311212B2 (en) | Method of processing data protected against attacks by generating errors and associated device | |

| US20080263422A1 (en) | Control of the integrity of a memory external to a microprocessor | |

| JP6622360B2 (ja) | 情報処理装置 | |

| CN114547618A (zh) | 基于Linux系统的安全启动方法、装置、电子设备及存储介质 | |

| Brown | Over-the-Air (OTA) Updates in Embedded Microcontroller Applications: Design Trade-Offs and Lessons Learned | |

| WO2017012588A1 (en) | Fast authentication of code in low-power system | |

| JP2015049785A (ja) | プログラム処理装置 | |

| JP2021057043A (ja) | トラストアンカコンピューティング装置を備える処理システムおよび対応する方法 | |

| JP2019532402A (ja) | セキュア・ブート更新にわたる保護済みの機密情報の維持 | |

| CN111381846B (zh) | 用于电子控制器安全刷新的数据校验方法 | |

| CN109150534B (zh) | 终端设备及数据处理方法 | |

| US9213864B2 (en) | Data processing apparatus and validity verification method | |

| US11509640B2 (en) | Method for protecting an electronic control unit | |

| KR20240122518A (ko) | 차량의 전자 제어 유닛의 비휘발성 메모리에 저장된 데이터의 무결성을 확인하는 방법 및 디바이스 | |

| CN114253576B (zh) | 双bios镜像刷新验证的方法、装置、存储介质及设备 | |

| EP3620944A1 (en) | Low power embedded device using a write-once register to speed up the secure boot from sleep states of the device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 18832027 Country of ref document: EP Kind code of ref document: A1 |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 18832027 Country of ref document: EP Kind code of ref document: A1 |