METHOD FOR FAULT LOCALIZATION IN CIRCUITS

CROSS REFERENCE TO RELATED APPLICATION

This patent application claims the benefit of copending U.S. Provisional Patent Application, Serial Number 60/480184, filed 06/20/2003, entitled "FAULT LOCALIZATION USING TIME RESOLVED PHOTON EMISSION AND SIMULATED WAVEFORMS," by Desplats et al.

BACKGROUND

FIELD

The present writing generally relates to fault localization. More particularly, the present writing relates to the field of using measured time resolved photon emission data and simulated time resolved photon emission data for fault localization.

RELATED ART

When a device (e.g., an electronic device, an integrated circuit chip, etc.) is not operating correctly, a tester (e.g., automated test equipment (ATE)) can identify faults due to a wide range of sources (e.g., short circuits). To use a tester's capabilities to investigate defects, the minimum information required is a test sequence, which places the device in a failed mode and, therefore, the circuit in question in a failed mode. If the defect is more subtle, other solutions such as software based fault isolation may be used. With fault dictionaries and simulations, a greater range of defects may be covered but significant CPU time is required. When software diagnosis is insufficient (e.g., an incomplete fault model), fault isolation then requires the use of probes. Internal probing of a device can establish a measurement at specific nodes yielding valuable information concerning the actual behavior

of a circuit, both analog and digital. Existing techniques include: contact micro-probing, photon emission microscopy (PEM), electron beam probing, laser voltage probing and optical time resolved probing (e.g., time resolved photon emission (TRPE) and picoseconds imaging circuit analysis (PICA)). This latter technique makes it possible to measure precise optical waveforms through the backside silicon in order to obtain timing (e.g., signal delay) information.

To locate defects using these internal measurements, each waveform obtained must be compared with a known reference. This comparative approach works between two circuits (one good, one failed) or with regards to simulated signals. If simulation is used to obtain reference signals, the question that arises is "How to compare time resolved photo emission (TRPE) waveforms (linked with current) to logic state waveforms (linked with voltage)?"

SUMMARY

Methods for using measured time resolved photon emission data and simulated time resolved photon emission data for fault localization are provided and described. In one embodiment, a method of localizing a fault in a circuit includes generating simulation data based on logical states of the circuit at predetermined intervals. Moreover, the simulation data is converted into simulation photon emission data based on photon emission intensity of the circuit at the predetermined intervals. The simulation photon emission data is used in a fault localization technique.

In another embodiment, a method of localizing a fault in a circuit includes measuring photon emission from the circuit during a test time period to form photon emission data. The measurement is repeated a plurality of test cycles. Further, the photon emission data is digitized. The digitized photon emission data is converted into measured photon emission data based on photon emission intensity of the circuit at predetermined intervals. The measured photon emission data is used in a fault localization technique.

In yet another embodiment, a method of localizing a fault in a circuit includes generating simulation photon emission data for the circuit. Moreover, measured photon emission data for the circuit is generated. The simulation photon emission data is compared with the measured photon emission data to generate a comparison result. Further, the comparison result is classified according to predetermined criteria. The classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

In still another embodiment, a method of localizing a fault in a plurality of circuits includes generating simulation photon emission data for each circuit. The simulation photon emission data of each circuit is merged into a composite simulation photon emission data.

Moreover, composite measured photon emission data for the circuits is generated. The composite simulation photon emission data is compared with the composite measured photon emission data to generate a comparison result. Further, the comparison result is classified according to predetermined criteria. The classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated in and form a part of this specification, illustrate embodiments of the invention and, together with the description, serve to explain the principles of the present invention.

Figures 1-23 illustrate methods of localizing a fault in accordance with an embodiment of the present invention.

DETAILED DESCRIPTION

Reference will now be made in detail to embodiments of the present invention, examples of which are illustrated in the accompanying drawings. While the invention will be described in conjunction with these embodiments, it will be understood that they are not intended to limit the invention to these embodiments. On the contrary, the invention is intended to cover alternatives, modifications and equivalents, which may be included within the spirit and scope of the invention as defined by the appended claims. Furthermore, in the following detailed description of the present invention, numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, it will be recognized by one of ordinary skill in the art that the present invention may be practiced without these specific details.

Software diagnosis makes it possible to investigate many IC defects with fault simulation tools. Faster defect localization can be achieved by combining IC simulations with internal measurements. Internal probing techniques, such as time resolved photon emission (e.g., TRPE), can access "otherwise inaccessible" nodes. Time resolved photon emission records photons emitted during commutations (current changes) rather than changes in logic states (voltage changes). These internal hardware diagnosis tools can fine- tune the defect analysis and validate simulations by contributing "actual" measurements. The combination of software diagnosis and internal probing can reduce simulation time and internal measurements for faster isolation of the root cause of a defect or fault. Comparing measured waveforms with simulations (e. g., Standard Test Interface Language (STIL) or Voltage Change Dump (VCD) formats) localizes functional faults and timing issues. The challenge is to determine quickly if an "actual" measurement is good or not: Can some signal be measured (Is the transistor at least activated)? Are the measured delays matching the simulation? If a problem is detected, the present invention makes it possible to locate rapidly the fault site.

Integrated circuit diagnostics (debug and failure analysis) and characterization employ several techniques— testing, software and internal probing (e.g., time resolved photon emission (TRPE)).

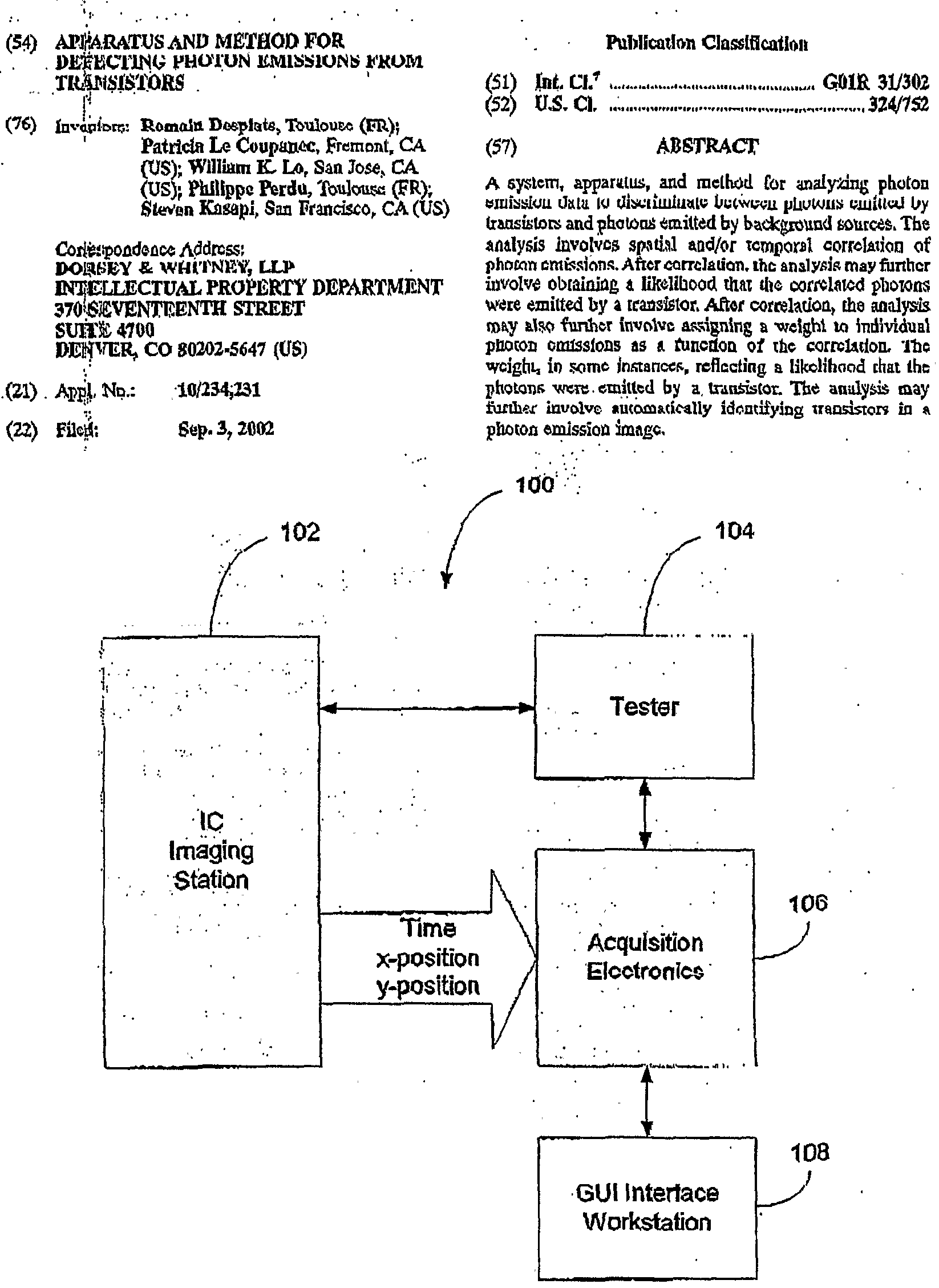

TRPE is a technique to capture photons that are emitted by transistor switching or commutation activity on an integrated circuit (IC) and to record the time of each photon relative to a trigger or timing reference signal. TRPE may incorporate either imaging (PICA) or single element type detectors. PICA is Picoseconds Imaging Circuit Analysis ( See J. A. Kash and J. C. Tsang, "Noninvasive Optical Method for Measuring Internal Switching and other Dynamic Parameters of CMOS Circuits", US Patent #5,940,545, issued August, 17, 1999). The PICA detector is an imaging type that records the time (t) and position (x, y) of individual photons. TRPE and PICA data, therefore, contain timing information useful in debug and failure analysis of integrated circuits and photon count, as illustrated by the graph 100 of Figure 1. The graph 100 shows two strong photon emission peaks and two weak photon emission peaks. A single element detector provides only timing data (t) from a local x, y region. A Photon Emission Microscope (PEM) camera records the position (x, y) of the sum of the optical emission from all switching events during the acquisition period.

Typically, test and validation of logic in a design is done using signals defined by voltage levels. A sequence of 0's and 1 's describe the input or output waveform for any points in a circuit. Internal probing of a device with either an e-beam prober or a laser voltage prober (LVP) makes it possible to measure the logic waveforms inside the device itself. Comparison of these measurements with simulation, for example, reveals disparities when a problem exists. However useful these tools are in general there are specific cases for which they do not work. E-beam probing requires physical access to the node being investigated (e.g., the metal interconnect). This is very challenging in present day integrated

circuits due to multiple levels of metallization and/or flip-chip packaging. Further the need to cool a flip chip package makes this completely unworkable through the silicon "back" side. The LVP is proving itself more useful than was believed several years ago, especially for timing measurements, but for silicon-on insulator (SOI) devices LVP has not been workable.

TRPE and PICA on the other hand record photons emitted due to current variation rather than changes in voltage logic states. The timing information obtained with TRPE and PICA while very precise is not compatible with existing testing tools. Histogram peaks (the optical waveforms) for some commutations are higher, i.e., contains more photons, than for other commutations and therefore are more readily classified. For example, a higher number of photons are collected from the NMOS transistor of an inverter whose output is switching from 1 to 0 than when it is switching from 0 to 1. For the PMOS transistor in the inverter, more photons are generated when the transistor switches from 0 to 1 than from 1 to O.

Photoemission from silicon devices such as an NMOS transistor that is pertinent to photon emission microscopy (PEM), TRPE and PICA is due to the generation of hot carriers, which have the highest probability of occurring when the transistor is switched ON via the VGS voltage and sufficient VDS is present while current is flowing through the channel to place the transistor in a saturation state, i.e., during commutation.

In addition to the substrate, an NMOS transistor has 3 nodes: gate G, drain D, and source S. From the electrical point of view, two quantities are considered— the gate to source voltage VGS and the drain to source voltage VDS. From a logic point of view, VGS and VDS are considered either logic 1 (>VT) or logic 0 (<VT). The threshold value Vτ comes from the circuit l-V curves illustrated in graph 200 of Figure 2.

Again, for the PMOS transistor photoemission from silicon devices that is pertinent to PEM, TRPE and PICA is due to the generation of hot carriers, as described for the NMOS transistor, i.e., during commutation. In addition to the substrate, a PMOS transistor also has 3 nodes: gate G, drain D, and source S. From the electrical point of view, two quantities are considered— the gate to source voltage VGS and the drain to source voltage VDS. In a typical CMOS device, a PMOS and NMOS pair forms the output stage in which drains of each device are electrically tied together. During logic switching operation, the possibility exists that both devices might be on for a brief moment resulting in photoemission from the NMOS via PMOS commutation activity. This is another mechanism by which photoemission from PMOS commutations can be observed.

As the voltage of ICs (integrated circuits) has decreased at each new process node, the signal that can be collected has also decreased. This means that the time to make a measurement has increased. Yet the number of transistors on a chip keeps increasing so the measurement time is growing exponentially. The PICA camera has poor photon detection (or quantum efficiency) when testing devices operating at low voltages (Vdd near 1 V). Other detectors used for TRPE are fairly exotic— InGaAs and super conducting Nb or NbN thin film based detectors. The cameras used for PEM are also getting more exotic— from silicon CCD's with thinned substrates to InGaAs, InSb, and MCT focal planar arrays (FPAs) and others. Even with the improved quantum efficiencies of these detectors, defect/fault localization is still challenging (design or process related) as the number of transistors increases on the IC chip, increased levels of metallization, smaller spacing, new materials, and increased transistor and interconnect density. The present invention decreases the time to make a decision in any localization technique utilized to localize the defect/fault.

Currently, there are several standards for voltage waveform simulations, such as STIL, VCD, Wave generation Language (WGL), etc. Previously, the transfer of data from simulation into the Automated Test Equipment (ATE) environment has been through the proprietary language of the specific ATE system. Value Change Dump (VCD) formats have been the typical way of capturing simulation output. The language is flexible enough to represent patterns from simple to the most complex devices, and has built in optimizing features to minimize the volume of data. VCD records every transition on each pin of the simulated device as a sequence of timed events and logic levels (1 's or 0's). This is fine for displaying a picture of the waveform, however it has limitations when used for creating test programs. VCD does not allow for any representation of the relation between events that is needed for any kind of analysis or characterization of the pattern from a real device. The VCD format requires an involved process to make the waveform/pattern realizable on most ATE systems which is usually done by means of expensive and time consuming conversion software.

In response to this issue and specifically to address growing concerns with large volumes of test data, an industry consortium of IC producers and ATE manufacturers came together to develop a Standard Test Interface Language (STIL) and is now part of standards committee (IEEE Std 1450.0-1999). STIL is designed to transfer high-density digital test patterns between simulation data created in Computer-Aided Engineering

(CAE) environments, automatic test pattern generation (ATPG) programs, built-in-self-test (BIST) data, and ATE equipment.

A tester (e.g., ATE equipment) is generally needed to activate the device while the probing tool acquires data. Converting ATE test vector data into a standard logic level format such as STIL provides a more efficient and easier means to review the data and

consequentially debug and characterize the device. The data conversion tools are generally part of the ATE tools suite.

While current simulation software tools have improved the methods of processing and displaying large volumes of data, the data is stored in logic level or voltage level formats which is not readily compatible with the data formats recorded by PEM, TRPE and PICA optical probing tools.

A discussion of prior art methods for fault localization may be found in U.S. Patent No.6,526,546 entitled "Method for locating faulty elements in an integrated circuit," issued February 25, 2003, which is hereby incorporated herein by reference.

SIMULATED AND MEASURED TIME RESOLVED PHOTON EMISSION DATA

Methods for using measured time resolved photon emission data and simulated time resolved photon emission data for fault localization are provided and described. In one embodiment, a method of localizing a fault in a circuit includes generating simulation data based on logical states of the circuit at predetermined intervals. Moreover, the simulation data is converted into simulation photon emission data based on photon emission intensity of the circuit at the predetermined intervals. The simulation photon emission data is used in a fault localization technique.

In another embodiment, a method of localizing a fault in a circuit includes measuring photon emission from the circuit during a test time period to form photon emission data. The measurement is repeated a plurality of test cycles. Further, the photon emission data is digitized. The digitized photon emission data is converted into measured photon emission

data based on photon emission intensity of the circuit at predetermined intervals. The measured photon emission data is used in a fault localization technique.

In yet another embodiment, a method of localizing a fault in a circuit includes generating simulation photon emission data for the circuit. Moreover, measured photon emission data for the circuit is generated. The simulation photon emission data is compared with the measured photon emission data to generate a comparison result. Further, the comparison result is classified according to predetermined criteria. The classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

In still another embodiment, a method of localizing a fault in a plurality of circuits includes generating simulation photon emission data for each circuit. The simulation photon emission data of each circuit is merged into a composite simulation photon emission data. Moreover, composite measured photon emission data for the circuits is generated. The composite simulation photon emission data is compared with the composite measured photon emission data to generate a comparison result. Further, the comparison result is classified according to predetermined criteria. The classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

In one aspect of the present invention, a method to compare the expected performance of the device— the simulations— to actual internal measurements from the device, for example the photon emissions/optical waveforms is provided. For example, the voltage/logic level simulation data generated by CAD/EDA tools can be exported in STIL, VCD or other useful data format which then can be converted into a photoemission compatible format such as a histogram indicating logic level transitions. This enables the fast localization of a discrepancy and therefore the identification of a design or process issue.

Once a design has been validated, any observed discrepancy would be a failure due to fabrication process issues, design marginality, or to misuse of the device.

Another aspect of the present invention is to provide the feedback from the "actual" measurements to the CAD/EDA models. For example, this might be performed by processing the actual photoemission data that can be in a histogram vs. time format and converted to a logic level format such as STIL, VCD or other useful data format by discerning which histogram transitions represent a 0 to 1 transition vs. a 1 to 0 transition. This is extremely valuable as it provides feedback to fine tune the models used by design.

In an embodiment of the present invention, simulated "optical waveforms" (or simulated time resolved photon emission data) are generated from simulated logic waveforms (typically in STIL or VCD format). Data processing is applied to correlate the simulated optical waveforms to actual optical waveforms (or measured time resolved photon emission data) with a minimum amount of real data as needed to provide sufficient confidence to determine the circuit to be functional or defective. The simulated logic waveforms providing the change of logic state information are used for generating the simulated optical waveforms. Also, in generating the simulated optical waveforms a variety of knowledge is used, where the knowledge can be the photon emission yield from a device which occurs due to a logic state change, which is a function of the transistor type (p or n channel), size, operating voltage, and fabrication process used.

Moreover, the invention enables the reconstruction of logic waveforms from PICA, TRPE and other optical waveform measurements. The invention may also be used in conjunction with the application of a differential laser voltage probing tool. An example of such a tool is described in U.S. Patent No. 6,252,222, entitled "Differential Pulsed Laser Probing of Integrated Circuits," issued June 26, 2001 , which is hereby incorporated herein

by reference. Further, the invention may be used with static photon emission. For example, simulated optical emission of a device can be performed. All emission events occurring during a specified period of time are added, yielding an expected cumulative emission height for that device which can be compared against actual static emission data. Although static photon emission would not show the waveforms it would tell, through peak height analysis, if the transistor is switching as would be appropriate for a properly functioning device.

This invention further includes a technique for faster fault localization that can be achieved by combining IC emission simulations with the internal optical probing measurements. The combination of simulation and internal probing of otherwise "inaccessible nodes" may be necessary to locate a fault in the heart of a device. Time resolved photoemission (TRPE) makes it possible to acquire precise timing waveforms corresponding to transistor commutations. A new data format is created, which contains simulated emission peaks (current levels). An example of this new data format is the

TRPEVCD (or TRPVCD) format or the TRPESTIL (or TRPs ) format. In one embodiment, the simulated emission in the new data format is derived from the logic "0" and "1 " simulation (voltage/logic levels) data, the transition points of the logic level data, and a scaling factor based on the specifics of the transistor as mentioned earlier. Actual TRPE measurements are acquired and converted into a TRPSTIL format or TRPVCD and compared to the simulated emission in order to generate a quick diagnosis: Is the gate working? Is there a timing issue? With a few measurements, the fault site can be located.

This invention further includes a method to rapidly decide whether a circuit node of a device is functioning correctly or not by defining a statistical confidence level as criteria to determine how many photons need to be collected to be statistically significant without

spending unnecessarily amount of acquisition time which otherwise does not add any relevance to the measurement.

Methods and apparatus for obtaining optical data for use in conjunction with the present invention may be found in U.S. Patent Application No. 10/234,231, entitled "Apparatus and Method for Detecting Photon Emissions from Transistors," filed 9/3/02, by Desplats et al., and in U.S. Patent Application entitled "Time-Resolved Optical Probing (PICA) with CAD Auto-Channeling for Faster IC Debugging," filed 12/5/02 by Desplats et. al., both of which are hereby incorporated herein by reference.

To convert 'Voltage/logic" information into a "current/emission" waveform, the electrical behavior of the circuit (e.g., transistor, logic gates, logic blocks, etc.) is needed. For the case of an NMOS transistor, all logic states and commutations are reviewed to understand the conditions for photoemission. From the static behavior (or truth table), a dynamic mode is built in order to show commutations and thus current/emission variations. Considering that photoemission is most probable when the transistor is switched ON via the VGS voltage and sufficient VDS is present while current is flowing through the channel to place the transistor in a saturation state, all transitions of VGS and VDS and expected emission are represented in a truth table 300 as illustrated in Figure 3. As depicted in truth table 300, these conditions are possible only in two cases 301 and 302, when the input VGS and the output VDS switch states from 0 to 1 and vice-versa.

Outside of switching in the CMOS architecture, saturation conditions occur only for a fault, as suggested in truth table 300 by "abnormal emission". Techniques such as lDDQ testing, Photon Emission Microscopy (PEM) and TLS (thermal laser stimulation) such as OBIRCH TΪVA/Seebeck Effect Imaging are often sufficient to locate the origin of these non- switching faults. In the TRPE analysis flow, the focus is on two possible emission peaks.

For initial illustration, the inverter is a good case. Further examples involve the analysis of the expected coverage of the truth table for CMOS structures such as NAND gates and XOR gates.

The invention may also be used with optically triggered devices such as those disclosed in U.S. Patent No. 6,501,288, entitled "On-Chip Optically Triggered Latch for IC Time Measurements," issued 12/31/2002, which is hereby incorporated herein by reference.

Again, as for the NMOS transistor, possible normal TRP emissions (or TRPE) occur only when both the input VGS and the output VDS of the transistor commutate in an opposite manner. For the inverter (Figure 4 shows a layout 410 and a schematic 420 of the inverter), all possibilities are determined from simulation 500 as depicted in Figure 5 and then listed in static truth table 610 and dynamic truth table 620 of Figure 6. The simulation 500 of Figure 5 shows voltage/logic state transitions in the input A and the output Y of the inverter of

Figure 4. Moreover, the simulation 500 depicts TRP emissions (or TRPE) associated with the NMOS 430 of the inverter of Figure 4. TRP emission (or TRPE) labeled #1 represents a strong photon emission peak while the TRP emission (or TRPE) labeled #2 represents a weak photon emission peak.

As depicted in Figure 6, TRP emission may happen only in two cases 631 and 632— when the inverter (Figure 4) is switching from 0 to 1 and vice-versa. The column labeled TNM0S displays TRP emissions for the NMOS Transistor 430 of the inverter (Figure 4) while the column labeled TPM0S displays TRP emissions for the PMOS Transistor 440 of the inverter (Figure 4). Moreover, the columns TNM0S and TPM0S indicate the type of TRP emission (e.g., #1 represents a strong photon emission peak, #2 represents a weak photon emission peak). In case 631 , the NMOS transistor 430 of the inverter (Figure 4)

generates a strong photon emission (shown as peak #1 in Figure 5) while the PMOS transistor 440 generates a weak photon emission. In case 632, the NMOS transistor 430 of the inverter (Figure 4) generates a weak photon emission (shown as peak #2 in Figure 5) while the PMOS transistor 440 generates a strong photon emission. For more complex gates such as NOR and NAND, this rule can be applied to create a dynamic truth table for TRP emissions.

To validate the functionality of a logic device, it is not necessary to cover all possible states. For the case of a NAND gate, the output may switch to 0 only if all inputs are at 1. As long as at least one input stays 0 it is not possible to validate the functionality of the NAND gate. (This is important as functionality can only be verified when all inputs are toggled high.) The truth table corresponds to all possible static state. Since photoemission in CMOS devices occurs only briefly during commutation, a dynamic truth table is necessary to cover the possible TRP emissions.

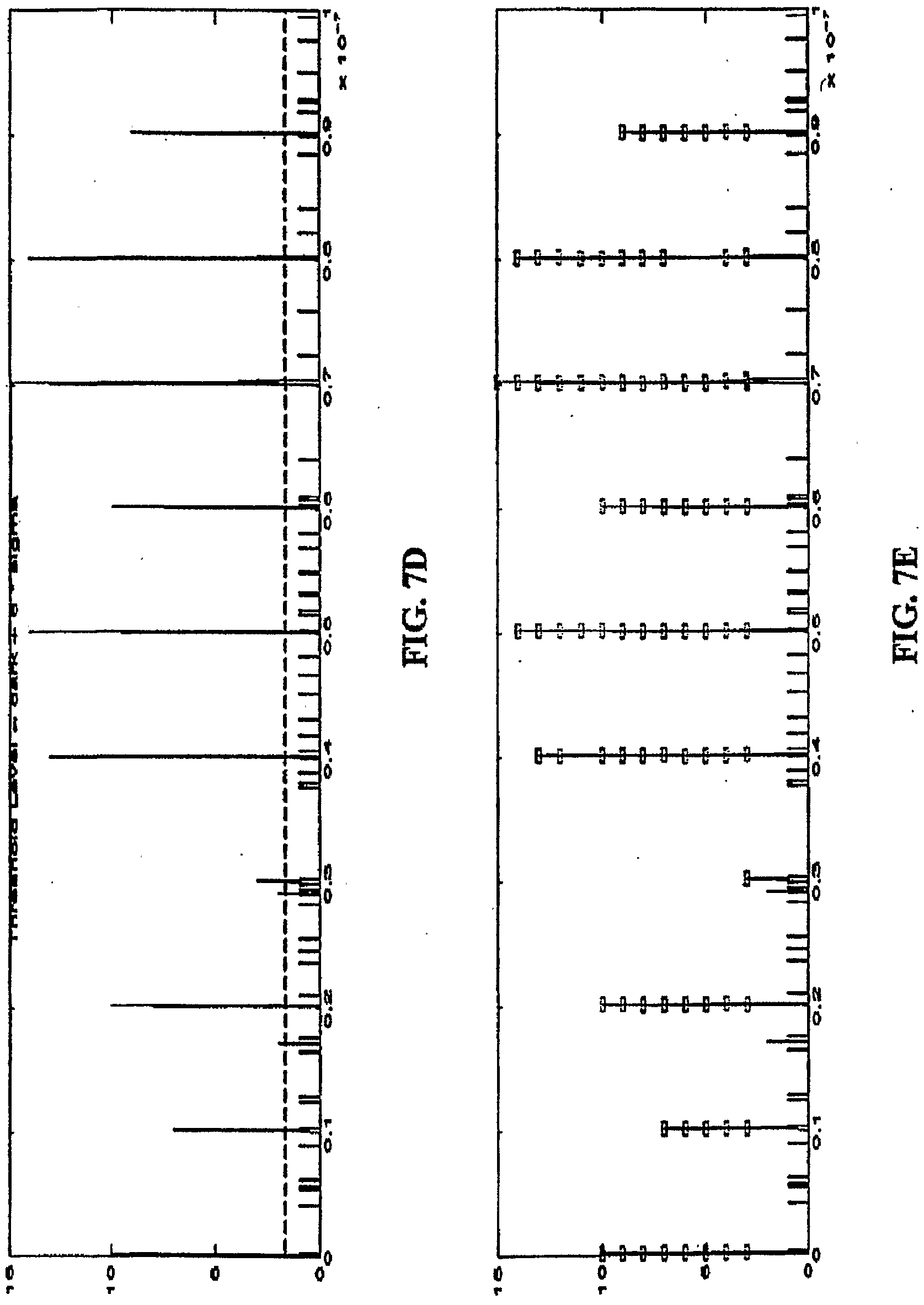

In Figure 7, the static truth table 700 for a variety of basic CMOS gates is shown. The static truth table 700 is derived to cover the different possibilities of photoemission (peak #1 or peak #2) for both NMOS and PMOS transistors.

For the NAND gate (Figure 8 shows a layout 810 and a schematic 820 of the

NAND gate), all possibilities of photoemission are determined from simulation 900 as depicted in Figure 9 and then listed in dynamic truth table 1000 of Figure 10. As shown in Figure 8, the schematic 820 of the NAND gate includes NMOS transistors 850 and 860 and includes PMOS transistors 830 and 840. The simulation 900 of Figure 9 shows voltage logic state transitions in the inputs A and B and voltage/logic state transitions in the output Y of the NAND gate of Figure 8. Moreover, the simulation 900 depicts TRP emissions (or TRPE) associated with the NMOS and PMOS transistors 830-860 of Figure

8, where TPA represents photon emissions by PMOS 840, TNA represents photon emissions by NMOS 850, TPB represents photon emissions by PMOS 830, and TNB represents photon emissions by NMOS 860. TRP emission (or TRPE) labeled #1 in TNB represents a strong photon emission peak while the TRP emission (or TRPE) labeled #2 in TNB represents a weak photon emission peak.

Symmetry is used to construct the dynamic truth table 1000 (Figure 10) for a NAND gate (Figure 8). The output Y is 1 if at least one input is 0 (see Figure 9). The dynamic truth table 1000 is limited to 6 (e.g., cases 1001-1006 of Figure 10) out of 16 possibilities: photon emission does not occur during the 4 static configurations, leaving 12 possibilities. Due to symmetry in the NAND gate (Figure 8), photon emission occurs in half the remaining commutations of the inputs (See Figure 10). In the dynamic truth table 1000 of Figure 10, the columns labeled TANMOS,TBNMOS, TAPM0S, and TBPM0S display TRP emissions for the transistors 850, 860, 840, and 830, respectively. Moreover, the columns TANM0S,TBNM0S, TAPMOg, and TBPMOg indicate the type of TRP emission (e.g., #1 represents a strong photon emission peak, #2 represents a weak photon emission peak).

For the NOR gate (Figure 11 shows a layout 1110 and a schematic 1120 of the NOR gate), all possibilities for photoemission are determined from simulation 1200 as depicted in Figure 12 and then listed in dynamic truth table 1300 of Figure 13. As shown in Figure 11 , the schematic 1120 of the NOR gate includes NMOS transistors 50 and 60 and includes PMOS transistors 30 and 40. The simulation 1200 of Figure 12 shows voltage/logic state transitions in the inputs A and B and voltage/logic state transitions in the output Y of the NOR gate of Figure 11. Moreover, the simulation 1200 depicts TRP emissions (or TRPE) associated with the NMOS and PMOS transistors 30-60 of Figure 11 , where TPA represents photon emissions by PMOS 40, TNA represents photon emissions by NMOS 60, TPB represents photon emissions by PMOS 30, and TNB

represents photon emissions by NMOS 50. TRP emission (or TRPE) labeled #1 in TNB represents a strong photon emission peak while the TRP emission (or TRPE) labeled #2 in TNB represents a weak photon emission peak.

The static table 700 of Figure 7 shows the NOR gate output is 0 if at least one input is 1. Therefore the interest is when all inputs commute to 1 and when at least one input switches to 0. This limits the dynamic truth table 1300 (Figure 13) to 6 cases 1301-1306 where photoemission occurs. In the dynamic truth table 1300 of Figure 13, the columns labeled TANM0S,TBNM0S, TAPM0S, and TBPM0S display TRP emissions for the transistors 60, 50, 40, and 30, respectively. Moreover, the columns TANM0S,TBNM0S, TAPM0S, and TBPM0S indicate the type of TRP emission (e.g., #1 represents a strong photon emission peak, #2 represents a weak photon emission peak). Plotting voltage variation as well as possible TRPE current peaks, the symmetry between n-transistors and p-transistors, is clear (see Figure 12). Only looking at the n-transistors, for each voltage change on the output, a possible emission peak is seen. It means that the possibility to transform the TRP emission peak into a state level exists.

The OR gate (Figure 14 shows a layout 1410 and a schematic 1420 of the OR gate) and AND gate (Figure 15 shows a layout 1510 and a schematic 1520 of the AND gate) are identical to the NOR and NAND gates (Figures 11 and 8, respectively) above except the output goes through an INVERTER at the final stage.

Increasing the gate complexity of CMOS structures to a 6 transistor XOR (Figure 16 shows a schematic 1620 of the XOR gate), its output is 0 if all inputs are identical. As for a NAND gate or NOR gate, TRP emission may be monitored on the n-transistors. By symmetry, the XNOR gate (Figure 17 shows a schematic 1720 of the NXOR gate) information is contained in the p-transistors.

Due to symmetry of logic gates in CMOS technology, probing n-transistors only can monitor the outputwaveform. Probing p-transistors yields the same results even though the photon emissions seem to be weaker and of longer wavelength. The coverage of the truth table is obtained only if all n-transistors connected to the output are probed. However, as a rule of thumb, a 2 input gate is probed at two locations and a 4 input gate at 4 locations. After this detailed review of the dynamic truth table, the role of "dynamic" emission peaks (current) versus "static" logic states (voltage) appears clear. For the NOR gate (Figure 11), as for example, there are 6 possible emission cases out of the 16 transitions while there is only 1 logic change out of 4.

As photoemission occurs only when a transistor switches (note: channel leakage does occur when the transistor is in the off state but is small in present technologies), only rise and fall of a logic state are discernable. In other words, the optical waveforms (e.g., TRPE) identify when a logic transition occurred. With the goal of reconstructing logic waveforms based on these emission peaks, it is necessary to see if it possible to differentiate emission from rising edges and emission from falling edges. Otherwise, reconstructing a logic state is difficult.

In previous paragraphs, emission peaks have been classified as #1 and #2 for both

N and P transistors. While these were represented differently for clarity purpose, the emission physics helps clarify what rising and falling transitions may be identified. Emission of photons associated with TRPE is related to hot electron generation occurring in the strong electron field during saturation. While photon emission is possible with hot holes, factors such as their lower mobility makes the probability much lower than for hot electrons. Comparison of emission peaks measured on NMOS and PMOS transistors of inverter chains shows a much higher photon count from N-transistors. Under the following

conditions: small size (e.g., 0.1 μm), low power (e.g., 1.2 V), photon emission detection technologies showed that photon counts from P-transistors are too close to the noise level to be consistent and therefore unreliable as a diagnostic tool. However, photon emission from the N-transistors also varies due to transistor load and, presumably, design-specific issues. For inverters, photon count rate for NMOS over PMOS is approximately 10 times higher when the output is switching from 1 to 0 (falling edge) than from 0 to 1 (rising edge). The graph 1800 of Figure 18 shows emission peaks for falling edges and rising edges. Therefore, logic state identification is possible.

Thus far, the conclusion is that the TRPE data may enable reconstruction of logic states. The problem arises is that if very few photons are detected for 0 to 1 (rising edge) commutations, it may always be possible to determine if a commutation occurred or that the few photons are just coming from the background noise. To capture the fainter P-transistor emissions with sufficient confidence level, acquisition time goes from minutes to several 10's of minutes. Acquisition times become even more discouraging as counts drop exponentially with the lower power supply voltage in new technologies.

Viewed from a practical approach, an alternative is needed— Can fault localization be done with short measurement times? This would not capture all rising commutations and thus leave uncertainty in 0 to 1 transitions.

To overcome this indetermination, a new data format for the Time Resolved Photon Emission is introduced to describe emissions (linked to a current) instead of a logic state (linked to a voltage level). This new data format is beneficial to any fault localization technique utilized. This new data format can be directly derived from logical (voltage) simulations.

Simulation logic waveforms are available in different industry standard formats such as Verilog-VCD, WGL, STIL, etc. The variety of formats has created duplicated effort for each vendor to interpret the format. In response to this issue and specifically to address growing concerns with large volumes of logic (voltage) test data, an industry consortium of IC manufacturers and ATE manufacturers came together to develop the Standard Test Interface language (STIL). For purpose of describing the present invention, reference is made to standard test vector data format, with the goal being to interface with the STIL vector data format specification. [Note: Verilog-VCD is an efficient way to dump value changes of variables in the design hierarchy and has been proved for performance and storage optimization.] In standard test data format, the series of logic states 0's and 1 's is stored to represent the voltage logic levels as Low (L) and High (H). From the photon emission perspective, only changes between logic states are meaningful. Therefore, in order to compare Time Resolved Photon Emission (or TRP emission) waveforms with simulations (STIL or VCD or other voltage-based waveforms), new data formats are introduced: TRPSTIL or TRPVCD. These new data formats represent commutation changes instead of logic states as seen in standard test vector data. An example of a test vector data for a simulation waveform converted to the simulation TRPSTIL format is shown in Figure 22.

As depicted in Figure 22, the STIL-formatted simulation data 110 is converted to simulation TRPSTIL data 120 (or simulation photon emission data). Since photon emission occurs during commutations, 1's are attributed to photon emission and 0's indicate no emission in simulation TRPSTIL data 120. With this terminology, TRPs 120 can be derived from logic/voltage STIL waveforms 110 and, further, the vice-versa is possible. To refine the Time Resolved Photon Emission, the lower probability of detecting photons for 0 to 1 commutations is addressed by adding a separate state value for the rising edge transitions on the output: "?/X" (for weaker photon emission peaks) while the falling edge has a state

value of 1 (for stronger photon emission peaks). From experimentation, the ratio between the peak for falling edge and the peak for rising edge is often greater than 10.

Thus, one embodiment of the TRPs format has 3 state values are possible: 0 (no TRPE emission); 1 (TRPE emission, falling edge); and "?/X" (Possible photon emission indicative of small rising edge peaks). In a second embodiment of the TRPSTIL format, the sub-threshold leakage current, which occurs when the transistor is 'off' is also taken into account. This added capability makes it possible to go beyond timing related faults and to tackle leakage problems, which grow in importance with each new process technology.

In one embodiment, time resolved photon emission probing, preferably from the backside, is used for measurements. That is, the photon emissions are detected with respect to a reference time. This technique makes it possible to measure precise signal waveforms through the silicon backside in order to obtain timing/delay information.

To locate defects/faults using internal probing, each measured waveform must be compared with a simulation logic waveform. To meet this goal, simulation logic waveforms (STIL or VCD format, for example) are first converted to the TRPSTIL format to serve as references for internal measurements and comparison.

Continuing, another step is to convert this photon emission measurement (analog waveform) into a waveform in the TRPST,L format. In a TRPE measurement instrument such as the NPTest IDS SSPD (Superconducting Single Photon Detector) or the IDS PICA system, the photon emission measurement (analog waveform) is digitized. In one embodiment, this digitization is done using a variable threshold with a Gaussian fit (Figure 20 shows digitization of analog photon emission measurement for a NOR gate), only the peaks are taken into account. However, the sub-threshold current variation can be taken into

account in order to increase the sensitivity to track subtle faults in the latest semiconductor technologies (e.g., size < 100 nm).

In Figure 19, the photon emission measurement for an NMOS device with the IDS SSPD system is shown. More specifically, logic (voltage) data 710, measured analog photon emission data 720, and digitized photon emission peaks 730 are depicted in Figure 19.

Moreover, in Figure 21 , the photon emission results for one N-transistor of a NOR gate is presented. More specifically, logic (voltage) data 41 , measured analog photon emission data 42, and expected digitized photon emission peaks 43 are depicted in Figure 21. In this case, not all weak photon emission peaks are detected. The reference 52 shows that a strong photon emission peak is detected while the reference 54 shows that a weak photon emission peak was not detected.

From the above discussion, it is evident that simulation TRPSTlL waveform can now be readily compared to the actual photon emission measurement from the internal node, generating a comparison result.

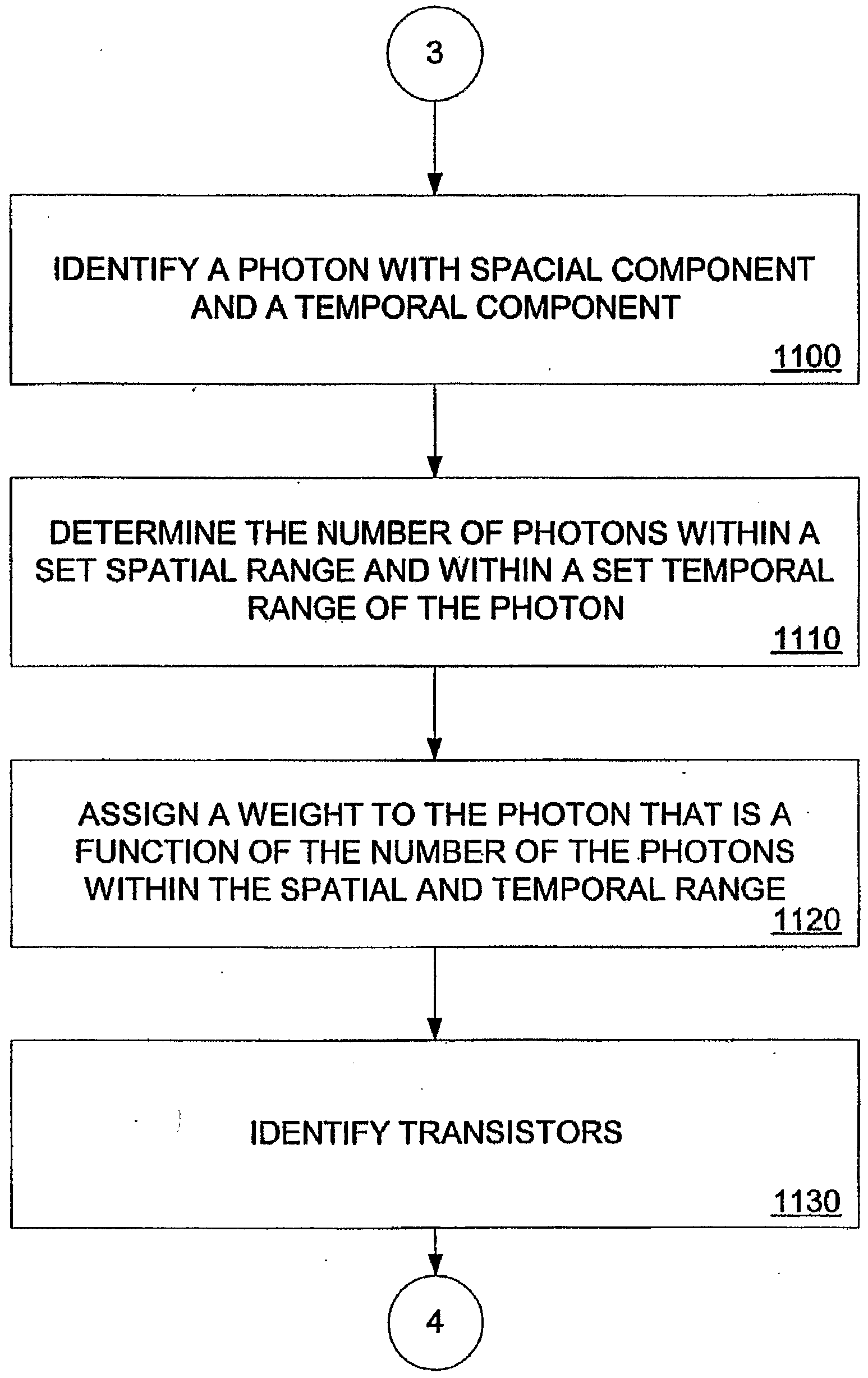

Now, a method for localizing a fault in a circuit (e.g., transistor, logic gates, logic blocks, etc.) that allows quick determination of fault origin in a device by combining logic simulation and optical measurements is presented. Reference is made to Figures 22 and 23.

At 2205 of Figure 22, simulation data 110 (e.g., simulation STIL-formatted data) based on logical states of the circuit at predetermined intervals is generated. Moreover, at 2215, the simulation data 110 is converted into simulation photon emission data 120 (e.g.,

simulation TRPSTIL format data) based on photon emission intensity of the circuit at the predetermined intervals.

Internal photon emission measurement (at 2220) may take several minutes to record a sufficient number of photons to become meaningful. As operating voltages decrease this time is expected to increase. Typically, the photon emission measurement is performed during a test time period. One test time period represents a test cycle. If an additional number of photons are to be measured, the test cycle is repeated as many times as needed.

At 2225, photon emission data 130 measured at 2220 is digitized. Moreover, the digitized photon emission data 140 is converted into measured photon emission data 150 (e.g., measured TRPSTIL format data) based on photon emission intensity of the circuit at predetermined intervals.

Continuing, at 2230, the simulation photon emission data 120 is compared with the measured photon emission data 150 to generate a comparison result. At 2235, the ■ comparison result is classified according to predetermined criteria. Further, the classified comparison result is used in the fault localization technique to determine next action in localizing the fault.

To locate quickly defects/faults with TRPE measurement and simulation, a strategy based on partially probed nodes is used. As shown in Figure 22, a 4 color coded diagnostic (e.g., Red, Orange, Yellow, and Green) has been chosen to guide the fault localization process, at 2235. Red and Orange correspond to detected faults (no commutation indicated by Red at 2255 or a delay problem indicated by Orange at 2250). At 2255, awareness of a major problem is made. At 2250, the next action in localizing the

fault is determined to be probing earlier in the propagation flow. At 2240, Green corresponds to the absence of faults (all measured commutations (e.g., measured TRPST,L) matching simulation (e.g., simulation TRPsτιl) and expected timing), allowing probing later in the propagation flow. Yellow corresponds to partially matching the measured commutations (e.g., measured TRPSTm) with the simulation (e.g., simulation TRPST(L) but, for at least the acquired peaks, the timing information seems to be correct, but may be incorrect for the missing peaks. At 2245, ft is determined that the photon emission measurement time needs to be increased. In the Yellow case, it may be assumed that the missing peaks are also correct, allowing the fault localization process to continue later in the propagation flow, at 2240. If a timing problem (Orange color) is then found, the last Yellow assumption must then be reconsidered. At this time only, a longer acquisition may be done, in order to verify the assumption made about the timing of the missing peak of the last Yellow assumption. Figure 23 illustrates the Green case 2320, the Yellow case 2310, the Orange case 2340, and the Red case 2330 of the 4 color coded diagnostic described above.

Further, at 2260, it is determined whether the fault has been localized. If not, a new measurement is performed at 2220. Otherwise, the fault localization process is ended at 2265.

To perform the fault localization technique as fast as possible, so as to probe as many points in the shortest amount of time, the following diagnostics questions are addressed:

1. Is Transistor On/Off (Is there a measured signal?)?;

2. Is Functionality validated (Is the data consistent with the logic gate being examined?)?; and

3. Is Delay/timing measurement accurate (Is there an issue here?)?

From the first minutes of measurement acquisition, the first diagnostic question is answerable—Is there a measured signal? If not, It means that the probed transistor is not activated. A major functional fault Is associated with this node. Probing nodes located earlier in the propagation flow will identify where the signal started to deteriorate.

if some photon emission is measured, the second diagnostic question concerning th validation of the unctional behavior is answerable. Is the number of measured commutations (photon emission peaks) matching the logic simulation? If not, probing earlier in the propagation flow is necessary to Isolate the fault site.

The third diagnostic question concerns timing and delay differences between measurement and simulation. If the margin is too great, probing earlier in the propagation flow to determine if the delay is coming from earlier gates is performed. If it is not coming from any earlier gate, the fault is due to an interconnect issue. If the timing of the measurements and simulation match, it means the fault is later in the propagation flow. In an embodiment, the determination of the next point to probe is done by following an extended binary search. With this strategy, at each measurement the number of remaining candidates is halved. If a sample of 512 nodes are potentially linked to a fault, the fault can be located after 8 measurements (28=512).

To speed fault localization, it is not always necessary to wait for a long acquisition to capture all commutations. Assuming the probed transistor is working, upon 2 out of 3 commutations are measured, the acquisition may be stopped. If later in the propagation flow a problem is found, it may be linked to the missing peak and a longer acquisition may then be necessary.

In an embodiment, the method for localizing faults described with respected to Figures 22 and 23 can be utilized to localize faults in a plurality of circuits rather than in a single circuit Here, simulation photon emission data (e.g., simulation TRPs ) for each circuit Is generated. The simulation photon emission data (e.g., simulation TRPδτlL) of each circuit Is merged into a composite simulation photon emission data. Composite measured photon emission data for tie circuits is generated since the plurality of circuits are measured at the same time. The composite simulation photon emission data is compared with the composite measured photon emission data to generate a comparison result. The comparison result is classified according to predetermined criteria. Further, the classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

In an embodiment, the methods of the present invention are performed by computer-executable instructions stored in a computer-readable medium, such as a magnetic disk, CD-ROM, an optical medium, a floppy disk, a flexible disk, a hard disk, a magnetic tape, a RAM, a ROM, a PROM, an EPROM, a flash-EPROM, or any other medium from which a computer can read. The foregoing descriptions of specific embodiments of the present invention have been presented for purposes of illustration and description. They are not intended to be exhaustive or to limit the invention to the precise forms disclosed, and many modifications and variations are possible in light of the above teaching. The embodiments were chosen and described in order to best explain the principles of the invention and its practical application, to thereby enable others skilled in the art to best utilize the invention and various embodiments with various modifications as are suited to the particular use contemplated. It is intended that the scope, of the invention be defined by the Claims appended hereto and their equivalents.

As a broad summary, this writing discloses methods for using measured time resolved iphoton emission data and simulated time resolved photon emission data for fault localization, ϊa one embodiment, a method of localizing a fault in a circuit includes generating simulation photon emission data for the circuit. Moreover, measured photon emission data for the circuit is generated. The simulation photon emission data is compared with the measured photon emission data to generate a comparison result. Further, the comparison result is classified according to predetermined criteria. The classified comparison result is used in a fault localization technique to determine next action in localizing the fault.

This application is related to and claims the benefit of U.S. Patent Nos.6,526,546 (filed oh 25 February 2003), 6,501,288 (filed on 31 December 2002), 6,252,222 (filed on 26 June 2001), and to U.S. Patent Application No; 10/234,231 (filed on 03 September 2002), the entire contents, of which are hereby attached and expressly incorporated herein by this reference.

!(i2) ύn tec tates' atent (io) Patent No.: US 6,526,546 Bl

Holland et al. (45) Date of Patent: Feb.25, 2003

(54) METHOD FOR LOCATING FAULTY (56) References Cited

ELEMENTS IN AN INTEGRATED CmCϋlT U.S. PATENT DOCUMENTS

(75) Inventors: Guy Rolland, Escalquens (FR); 5,602,856 A 2 1997 Teramoto Remain Desplats, Toulouse (FR) FOREIGN PATENT DOCUMENTS

(73) Assignee: Centre National d'Etudes Spatiales, EP 0305217 3/1989 Paris (FR) EP 0720097 7/1996

OTHER PUBLICATIONS

( * ) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 Stamenkoviό et al., May, 2000. International Conference On U.S.C. 154(b) by 0 days. MicToeletronics. pp. 735-738.*

(21) Appl. No.: 09/831,832 * cited by examiner

Primary Examiner— -Tom Thomas

(22) PCT Filed: Sep. 14, 2000 Assistant Examiner— -Douglas . Owens

(86) PCT No.: PCT FR00/02554 (74) Attorney, Agent, or Firm— Young & Thompson

§ 371 (c)(1), (57) ABSTRACT

(2), (4) Date: May IS, 2001 A process for locating defective elements in an integrated

(87) PCT Pub. No.: O01/20355 circuit. The integrated circuit is modelled in the form of a tree formed of nodes and oriented arcs. Measurements are PCT Pub. Date: Mar. 22, 2001 performed at various nodes of the circuit by applying a sequence of tests at the input of the circuit. The nodes to be

(30) Foreign Application Priority Data tested are determined recursively as a function of the result Sep. IS, 1999 (FR) 99 11534 of the tests previously performed. Each new test node is such that the number of its ancestors is substantially equal to the

(51) Int. Cl.7 G06F 17/50 number of its descendants.

(52) U.S. CI 716/4; 716/5

(58) Field of Search 716/4, 5, 6 9 Claims, 23 Drawing Sheets

Appendix A page 1 of 110

U.S. rateil '" "Feb 'S, 2 Sheet 1 of 23 ττ„

US 6,526,546 Bl

FIG.1

Appendix A page 2 of 110

.. eϋ , 3 Sheet 2 of 23 US 6,526,546 Bl

Appendix Apage 3 of 110

Sheet 3 of 23 US 6,526,546 Bl

Appendix A page 4 of 110

. , ee o , ,

FIG.3 FIG.4

Appendix A page 5 of 110

. . atent Feb.25, 2003 Sheet 5 of 23 US 6,526,546 Bl

FIG. 6 FIG. 7

FIG. 8A

Appendix A page 6 of 110

. . e . , ee o ZO tO JBl

Appendix A page 7 of 110

. * e . , ee o , ,

FIG 10

Appendix A page 8 of 110

. . eb.25, 2003 Sheet 8 of 23 US 6,526,546 Bl

FIG. 11

Appendix A page 9 of 110

e . , ee o

Appendix A page 10 of 110

Feb.25, 2003 Sheet 10 of 23 US 6,526,546 Bl

FIG. 13

Appendix A page 11 of 110

Reference tree

FIG. 15

.

CO

Appendix A page 13 of 110

.

Appendix A page 14 of 110

.o. ate I e. , eet o , ,

FIG.18

Appendix A page 15 of 110

e . , ee o 6,526,540 JS1

FIG. 19

Appendix A page 16 of 110

.O. raieil Feb. , 2003 Sheet 16 of 23 US 6,526,546 Bl

T=(Vertex~>counte ir_αncestors=<meαn)

FIG. 21

Appendix A page 17 of 110

U.S. Patent Feb.25, 2003 Sheet 17 of 23 US 6,526,546 Bl

Appendix A page 18 of 110

. . e . , eet o ,5 ,546 Bl

FIG.23

Appendix A page 19 of 110

ui e 5, Sheet 19 of 23 6,526,546 Bl

FIG. 24

Appendix A page 20 of 110

.

U.O. raten Feb.25, 2003 Sheet 20 of 23 US 6,526,546 Bl

FIG 25

Appendix A page 21 of 110

" . . n Feb.252003 Sheet 21 of 23 US 6,526,546 Bl

FIG.26

Appendix A page 22 of 110

. ateϊit Feb.25, 2003 Sheet 22 of 23 US 6,526,546 Bl

FIG 27

Appendix A page 23 of 110

. . e , ee o 6,526,546 J51

Appendix A page 24 of 110

U 6,526,54 B

METHOD FOR LOCATING FAULTY integrated circuit if the defective element is very close to an

ELEMENTS IN AN INTEGRATED CXRCUIT input of the circuit. Owing to the complexity of the circuits and their numerous constituent branches, the search for the

The present invention relates to a process for locating a defective element may prove to be extremely lengthy. defective element in an integrated circuit whose theoretical s The aim of the invention is to propose a process for layout is known, of the type comprising a succession of steps detecting errors in a circuit allowing faster locating of consisting in: defective zones, whilst preserving great reliability in this the determination of a measurement point of the inte- locating. 'grated circuit; and Accordingly, the subject of the invention is a process of the testing of the measurement point determined by 10 the aforesaid type, characterized in that it comprises iniimplementing: tially: the application of a sequence of tests to the inputs of the a step of modelling the theoretical layout of the integrated integrated circuit; circuit, in the form of at least one graph comprising a the measurement of signals at the determined measureset of nodes and of arcs oriented from the inputs of the ment point of the integrated circuit, during the applicircuit to the outputs of the circuit; cation of the sequence of tests; and is considering as a search subgraph, a subgraph whose the assessment of the measurement point by comparivertex-forming node corresponds to a faulty measureson of the measured signals with theoretical signals ment point , which ought to be obtained at the determined meaand in that, for the search for the defective element, it surement point so as to assess whether the measurecomprises the steps of: ment point is faulty or satisfactory; and 20 assigning each node of the search subgraph considered a in which the position of the defective element of the intecharacteristic variable dependent on the structure of the grated circuit is determined from assessments performed at search subgraph; the various determined measurement points. considering as measurement point the measurement point

It is expedient, in the manufacture of integrated circuits, or when searching for faults in industrial systems, to be able 25 corresponding to a node of the subgraph considered, to determine the origin of defects or breakdowns. obtained by applying a predetermined criterion pertain¬

In particular, in the case of defective integrated circuits, it ing to the characteristic variables of the set of nodes of is necessary to be able to determine which component or the search subgraph considered; performing a test of the measurement point considered; components constituting the integrated circuit exhibit an operating anomaly. 30 considering as new search subgraph: either the search subgraph previously considered,

The number of components involved in the construction while excluding the node corresponding to the of an integrated circuit is generally very high so that it is measurement point tested and all its parent nodes, very tricky to locate the one or the few defective elements if the measurement point is satisfactory from among the multitude of elements from which the breakdown may result. 35 or a subgraph whose node corresponding to the measurement point is the vertex, if the measure¬

Aprocess for analysing integrated circuits, known by the ment point is faulty; and English term "backtracking", is currently known. To implement this process, a testing rig is used, making it possible searching for the defective element in the new search with the aid of hardware or virtual probes to plot signals subgraph considered, until a predetermined stopping flowing at various circuit measurement points. 40 criterion is satisfied.

By knowing the theoretical structure of the integrated According to particular modes of implementation, the circuit analysed, the signals which ought to be measured at process comprises one or more of the following characterthe various circuit measurement points are determined as a istics: function of a sequence of tests applied to the inputs of the during the initial step of modelling the theoretical layout circuit. 45 of the integrated circuit, the circuit is modelled the form

In order to locate the defective elements in the circuit, a of a tree by possible creation of virtual nodes when one defective output of the circuit is first considered and then we and the same node is the parent of at least two nodes, backtrack from this output to the inputs, gradually testing themselves parents of one and the same node; each of the successive measurement points. As long as the it comprises, after satisfaction of the predetermined stopmeasurements performed at the various points reveal signals 50 ping criterion, the steps of: which are incorrect as compared with the theoretical signals evaluating in the or each last search subgraph whether, which ought to be obtained, one deduces that the defective for each virtual node corresponding to a faulty elements, of the circuit are upstream of the measurement measurement point, the twin node associated with point. As soon as correct signals are obtained at a measurethe said virtual node is a node of the same subgraph ment point, one deduces that the defective element is situ55 also corresponding to a faulty measurement point; ated between the measurement point where correct signals and are obtained and the previous measurement point where then considering the or each subgroup for which the incorrect measurement signals were obtained. condition is satisfied as corresponding to a part of the

Each measurement actually performed on the integrated integrated circuit comprising at least one defective circuit requires a considerable time which may range from element; a few seconds if the measurement point is at the surface to the said characteristic variable peculiar to each node is the 5 to 10 minutes if the measurement point is situated on a number of ancestors of this node in the search subgraph deep layer of the integrated circuit and if a prior hardware considered; port must be made with the aid, for example, of a focused ion the said predetermined criterion is suitable for determinbeam. 65 ing the node whose number of ancestors is substantially

It is appreciated that, with the method currently used, it is equal to the mean number of ancestors per node in the sometimes necessary to traverse back through the nub of the search subtree considered;

Appendix A page 25 of 110

Appendix A page 26 of 110

US 6,526,546 Bl

5 6

The program implemented by this rig makes it possible to The EDIF interpretation phase determine progressively, on the basis of the theoretical The marking phase diagram of an integrated circuit, the points where physical The numbering phase (this phase encompasses the con- measurements ought to be made by implementing a struction of the reference tree, the construction of the sequence of appropriate tests. 5 minimal subset and the creation of the virtual vertex)

After each acquisition of the result of the test performed The &ult location phase previously, making it possible to determine whether the The reporting phase, signal received at the measurement point is or is not correct, ^ calculations can be interru ted on completion of each the process implemented determines a new point where a of *e∞ P1""*- to cfe' aU * intermediate results

, , . . . . r - , ,, . . c r lo required for the subsequent resumption of the calculations tes ought to be performed on the basis of a new sequence automatically archived in save files. These files have of tests. names comprising a ".data" extension. The degree of

In tandem with the acquiring of the results of the auto- progress of the calculations is also archived, matically proposed tests, the process according to the inven- he calculations are resumed in a transparent manner, that tion makes it possible to locate that region of the integrated 1S is to say without having to make reference to these inter- circuit in which the defective element is situated and ulti- mediate files, by simply loading the appropriate session file, mately to locate the latter rapidly. Initially, the theoretical structure of the circuit, that is to

The test sequences implemented for each of the measure- sav &e structure of a defect-free circuit, is stored in a file ment points of the integrated circuit are of any suitable type 10*i ^ h e f<* βxamPk ^e EDIF format.

"backtracking^ process. Since the test sequences are known put -^ ^ foπn of m *mύ format sped&0 tø the per se, they will not be described in the subsequent descπp- implementation of the process. The manner of interpretation tion. ^ 102 and the format specific to the application of the process likewise, the means used to measure a signal at a ■will e described in the subsequent description, determined measurement point of the integrated circuit, 25 Generally, interpretation consists in modelling the theo- during the application of a sequence of tests will not be retical circuit in the form of a graph, whose nodes corre- described in detail, they being of any suitable type. spond to the inputs and to the outputs of the various

The process according to the invention can be imple- components of the integrated circuit and in which the mented with a rig comprising, on the one hand, test means components are represented by sets of oriented arcs inter- such as a scanning electron microscope making it possible to 30 linking the nodes. plot signals flowing at determined measurement points of The interpretation algorithm receives and addresses data the integrated circuit during the application of a sequence of to an internal session memory 104 catering in particular for tests, and, on the other hand, an information processing unit, temporary storage of the file containing the graph of the such as a microcomputer implementing a suitable program circuit presented according to a utilizable format, determining, in accordance with the process of the 35 This memory 104 is linked to a session file 106 catering invention, the points of the circuit where successive mea- for storage of the session data on a permanent medium such surements ought to be performed, and deducing from the as a hard disk. measurement results the position of the defective elements On completion of the interpretation 102, the session file is in the circuit. subjected to a marking phase 108 associated with other

Illustrated in FIG.1 are the various data files used as well 40 preliminary processing operations, as the processing operations performed on them, so as to The next phase denoted 110 is the so-called "minimal determine, on the one hand, the successive points where subset construction and numbering phase". Its aim is in measurements should be performed on the circuit and, on the particular to define subsets from among the various trees other hand, the defective elements or zones of the circuit. modelling the circuit. In particular, during phase 110, two

The general structure of the program implements the 45 series of information are taken into account, namely the list, session concept. denoted 112, of outputs of the circuit operating correctly, and

Asession can be defined as a set of consistent files relating the list, denoted 114, of outputs of the circuit not operating to given conditions for the inputs and the parameters of the correctly. Accordingly, the outputs of the circuit are tested on program. Asession also contains the set of intermediate files the basis of sequences of tests, as will be explained in the generated by the program, and which are necessary for 50 subsequent description. operations and for storing the number of the last calculation On the basis of the session file obtained at the output of step performed. step 110, a phase 116 of loading the lists is implemented.

The content of a session is defined in a text file whose This phase takes into account the list of disallowed nodes name bears the extension ".ses". The root of the name is stored in a file 118, the list of levels of metal 120 specifying defined freely by the user. 55 the metal layers on which the various elements of the circuit

The loading by the program of a preexisting session file are present, as well as a file 122 containing the list of nodes restores the calculation context specific to this session (same already tested. data files, same check parameters and intermediate results) The subsequent phase 123 consists in locating the defec- and enables the calculations to be restarted at the point tive components or groups of components causing faults in where they were interrupted. βo the operation of the circuit. According to the invention, this

The sequencing of the various operations is performed by search for faults is performed according to a dichotomy a function main( ). process effected with regard to certain particular trees of the

The code for this function is found in a file "principal.c". circuit, by taking account of a waiting also referred to as {he

According to the principle of the program, the various numbering of each of the nodes, performed according to a operations are chained together sequentially. 65 predetermined method.

Five main phases may be distinguished and will be During the dichotomy phase denoted 124, an additional detailed in what follows: analysis phase 126, the so-called "post-exhaustion analysis

Appendix A page 27 of 110

US 6,526,546 Bl

7 8 phase" is also implemented, this making it possible to Certain nodes are untestable nodes. These are for example supplement the dichotomy-based search for faults. This nodes situated on deep layers of the integrated circuit and to additional phase makes it possible to take account of the which access is impossible or difficult. These nodes are circuit modelling constraints which have led to certain designated by a nought inside which there is a question conventional modifications of the graph representing the 5 mark, circuit. The good nodes, as opposed to the bad nodes, are nodes

Finally, the results are made available to the user during where for a given sequence of tests, the measured signal the final phase 128. corresponds to the theoretical signal which ought to be

As represented in the schematic diagram, each of the obtained. These good nodes are designated by a nought processing phases 102, 108, 110, 116, 124, 126, 128 receives 10 inside which there is another nought, and addresses data from and to the internal session memory In the example of FIG.5, the faulty zone 500 consists of

104. The latter is moreover linked to a set of results files 130, a subtree whose vertex 502 is a bad node. This bad node 502 as well as to a storage journal 132. The latter respectively is controlled by two untestable nodes 503 and 504. The first ensure that the results of the analysis are made available to untestable node 503 is linked to two good nodes 506 and the user and ensure the archiving of the comments printed on 15 508. The second untestable node 504 is linked to a good the screen. node 510 and to an untestable node 512 itself linked to a

Each of the successive phases 102, 108, 110, 124 and 126 good node 514. for implementing the process according to the invention is In general, a subtree constituting a faulty zone has the described in greater detail in FIG. 2. following properties:

Thus, the detailed description of the full algorithm will be w The vertex is a node on which the signal is bad, performed with regard to FIG.2, where each of the elemen- All the terminations are nodes on which the signal is good tary steps will be described in succession with reference to Untestable nodes may exist between the vertex and the other yet more detailed illustrative figures. terminations. In the converse case, one is dealing with

The first step of the initial phase 102 for formatting the file a faulty cell or with faulty cells whose outputs are describing the integrated circuit is designated by the refer- 25 connected to the same node, ence 202 in FIG.2. An example of a faulty cell on its own is represented in

In general, a circuit can always be described as a set of HG. 6. An example of two faulty cells sharing the same cells comprising inputs and outputs connected by nodes. The output is described in FIG. 7. In these figures, the conven- choice of the hierarchical definition of a cell is arbitrary. It tions of FIG. 5 are used. may for example be a functional subset constituting a 30 τn practice, the interpretation step 202 consists in trans- macrocell, or be a gate or a transistor. Likewise, the concept forming the initial file describing the circuit, in the Edif of inputs and outputs of the circuit to be analysed can be format, for example, into a file of a. determined format immediately carried over to the inputs and outputs of an specific to the implementation of the process (file whose internal block, the. analysis then pertaining to this block. na e bears the suffix ".parsed").

With the type of description used, the signals are observed 35 According to the nature (tagged by one of the suffixes only on the nodes. ".edn", ".edf ' or ".edo") of the initial file, the program runs

The description of the cells reduces to the influence which the appropriate interpreter, their input nodes exert on their output nodes. The initial These interpretation programs are used as commands for circuit description formed of a set of cells and of nodes, can the operating system through the function "system( )" of the therefore be transformed into an inter-node influence graph 40 c language. by replacing each cell, an example of which is given in FIG. in the case where the initial description does not comply

3, by a set of oriented arcs such as illustrated in FIG.4. ^Jth the formats of the available interpreters, it is always

Represented in FIG.3 is a cell 300 consisting for example possible to make direct use of a description in the internal of an AND gate. This cell comprises two inputs El and E2 format (".parsed" format). linked to input nodes 302 and 304 respectively. These input 45 T e format of these internal files is given in Table 1. nodes are linked to the outputs of other cells (not T e conventional constraints to be adhered to are as represented) of the integrated circuit. The output, denoted S, follows: of the cell 300 is linked to a node 306 to which are linked It is a text file, the inputs of other cells (not represented) of the integrated - No ^ may be ^pp^

CU' ι Ui3r^-. Λ ιι inn - i j. «„ • . Λ ΛOΠ ° T e various blocks must be placed in the following order:

?!_?• ' ^"ϊ3^ repkcedby two oriented arcs 402 describing the outputs; the blocks de cribing and 404 respechvely linking the input nodes 302 and 304 to ^ ^s ^ ^^ j the output nodes 306 of the cell. .. . ,„„!„ J„_„,- J A. -,„Λ.„.

ThuJ the cellSOO is modelledsimplyby the two oriented e blocks describing the nodes, arcs 402 and 404 *■ •> J The numbering of the outputs commences at zero and

By virtue of such modelling of all the cells, the full terminates at N. description of the circuit thus takes the form of a graph. ^ numbering of the mputs commences at N+l and

Insuchamodeffingofthe circuitand asillustratedinFIG. terminates at (number_of_pιns-l) 5, a faulty zone 500 is a subgraph and even, after applying The numbering of the internal cells (instances) corn- modifications which will be explained later, a subgraph. 60 mences at (nurnber_of_pins) and terminates at

Several types of nodes appear in this figure. (number_of_4>ins+number_of_cells internal-1).

The bad nodes are designated by a nought at the centre of The nodes are numbered from zero to (number_of_ which there is a cross. The bad nodes are the nodes for nodes-1). which, for a, given test sequence applied to the input of the The numbering of the nodes in the blocks relating to the circuit, a signal is obtained which differs from the theoretical 65 outputs, to the inputs and to the instanced cells must be signal which ought to be obtained for this measurement consistent with the numbering of the blocks describing point. the nodes.

Appendix A page 28 of 110

US 6,526,546 Bl

10

The numbers for the cells in the blocks describing the At the start of step 204 for constructing the cones of nodes must be consistent with the numbering of the influence, a certain number of preliminary calculations relatinstanced cells, the numbering of the inputs, as well as ing to the outputs are performed. This involves: the numbering of the outputs which is performed Counting the number of outputs; upstream in the file. s Counting the number of groups of markers;

Filling in the common arrays associated with the outputs. TABLE 1 These common arrays are:

Stiucture ofa βle in the internal description format (".paiεed." The array giving the group number of each ouput: grouρOutout[ ]; Number _ofjjins Number of_ceU8_intemal Numbcr_of nodea ιo The array giving the rank of each output: rankoutput [ ];

The array giving the numerical value of the marker for

Name_Cell_Ou(put Number_Cell_Ouφut To be repeated each output: markeroutput ];

1 for each output; pin The array containing the addresses of the structures

Namejinjnput relating to each output: addressθutρut[ ];

Number_of_node_input 15 The array of names of the outputs nameθutρut ];

The array containing the total number of nodes in the cone relating to each output: totalθutout[ ].

Name_Cell_Ioput Nιuήber_CelI_Input lb be repeated The usefulness of these various arrays is apparent after

1 for each input reading the following paragraphs relating to the method of pin

0 20 marking the nodes.

To construct the code of influence of an output, we start

NameJPin^output from this output and we traverse the influence graph with a

Nαmbet_of_node_o£_outρut standard algorithm for traversing trees, such as a "prefixed order" algorithm. ame_Cell Number Cell -N 25 Since the influence graph is not a tree, according to the Numberjnputs nature of the initial circuit, this graph can comprise cycles due to the presence of sequential or combinatorial loops in the circuit.

NatneJPinJnpαt

For each When engaged in such a cycle, one returns at a given Number Df_node_jnput cell input To be moment to an already analysed node. The algorithm is repeated 30 suitable for detecting the return to a node. When this event for each

Number outputs input occurs, the algorithm creates a fictitious termination, dubbed pin a "cut", and goes back the way it came.

According to the principle of cuts, the latter are performed

Name_Pin ouψut

For each cell when remrning to already analysed nodes. The concept of Number of node of outp output 35 cut is illustrated in FIGS. 8A and 8B.

Represented in FIG.8 A is an influence graph which does not exhibit the form of a tree since one of the nodes, denoted

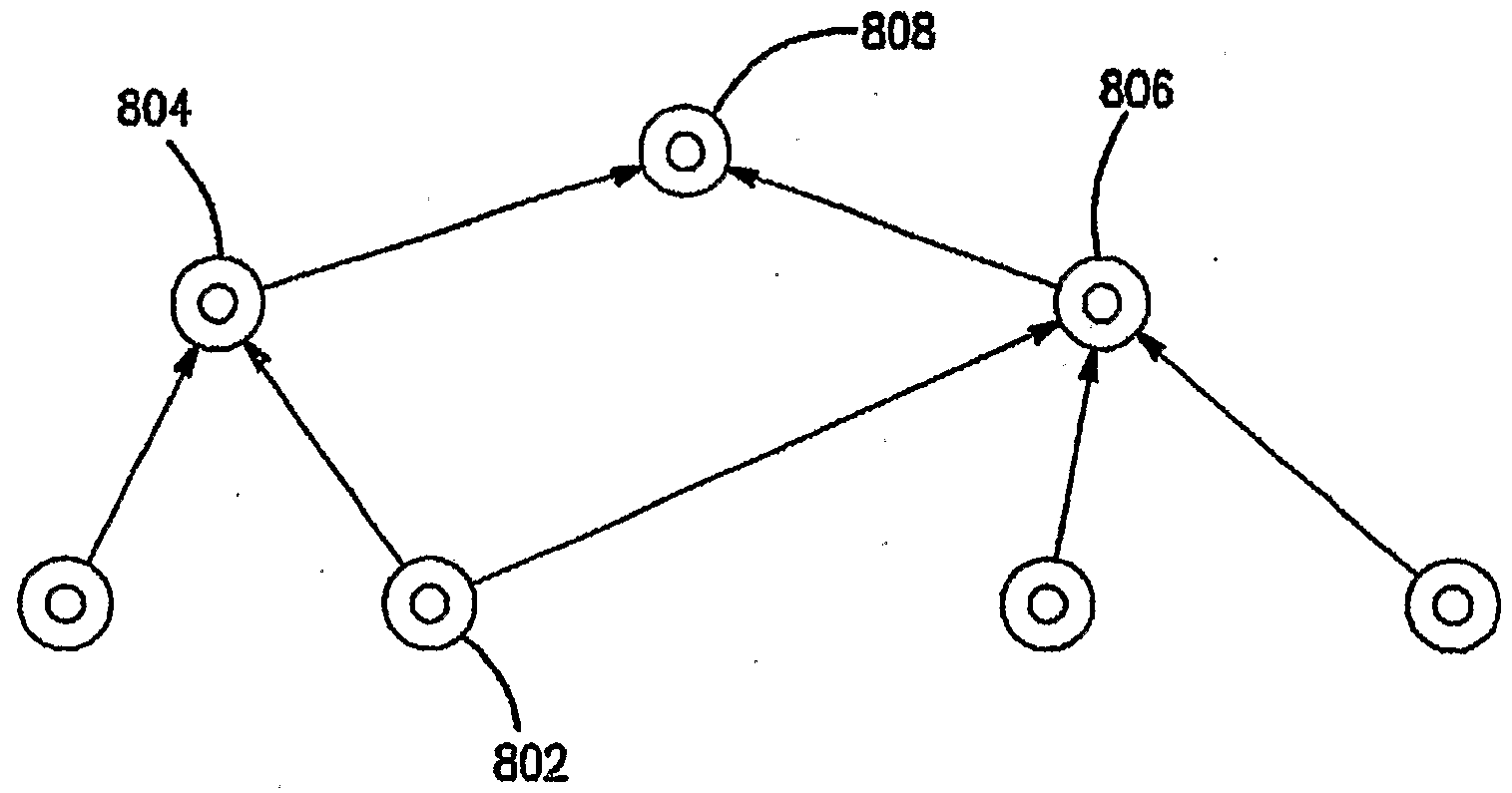

Name_of ιode Number_of_πode 802, is the parent of two nodes 804 and 806, the latter being

Number_of_p s_connected_to_this_node themselves the parents of one and the same node 808. Thus, 0 the nodes 802, 804, 808 and 806 form a combinatorial loop.

Name_pin For each pin /" For In order to create a tree from the graph of FIG. 8A, and Number_cell_to_which_the_pin_ (cell or input/ each output) node as illustrated in FIG.8B, a virtual node 810, constituting a cut, is added as parent of the node 806. In the subsequent drawings, the cuts are represented by a nought enclosing a

4S square.

Three fundamental lists are constructed from this file. The node 802 is retained as parent of the node 804. Thus, These are: the node 810 constitutes a virtual twin node of the node 802.

A chained list of structures of NODE type to describe the The oriented arc emanating from the node 802 and pointing nodes; to the node 806 is deleted from the data structure. It is

A chained list of structures of CELL type to describe the indicated as a reminder by dashes in FIG. 8B. pinout; so In the data structure, a "parent" field of the structure

A chained list of structures of CELL type to describe the describing the node 810 points to the twin node 802 in the instanced cells; list of nodes. By operating in this manner a tree is obtained,