US20010016023A1 - Elastic store for wireless communication systems - Google Patents

Elastic store for wireless communication systems Download PDFInfo

- Publication number

- US20010016023A1 US20010016023A1 US09/782,262 US78226201A US2001016023A1 US 20010016023 A1 US20010016023 A1 US 20010016023A1 US 78226201 A US78226201 A US 78226201A US 2001016023 A1 US2001016023 A1 US 2001016023A1

- Authority

- US

- United States

- Prior art keywords

- elastic store

- shift register

- read

- data

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W84/00—Network topologies

- H04W84/02—Hierarchically pre-organised networks, e.g. paging networks, cellular networks, WLAN [Wireless Local Area Network] or WLL [Wireless Local Loop]

- H04W84/10—Small scale networks; Flat hierarchical networks

- H04W84/14—WLL [Wireless Local Loop]; RLL [Radio Local Loop]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0602—Systems characterised by the synchronising information used

- H04J3/0605—Special codes used as synchronising signal

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/07—Synchronising arrangements using pulse stuffing for systems with different or fluctuating information rates or bit rates

Definitions

- the present invention generally relates to voice and data communication systems. More particularly, this invention relates to synchronous wireless communication systems.

- T-carrier systems have become an essential part of modern telecommunications systems.

- a T-carrier system is found in every telephone company in North America.

- a T-carrier allows for transmission of one or more telephone calls or data connections by modem.

- the basic unit of signaling is DS0, followed by progressively higher speed signaling rates.

- First generation T-carrier systems, called T1 which carry Digital Signal Level 1 (DS 1), employ a full duplex all-digital service.

- the digital stream is capable of carrying standard 64 kilobits per second (kbps) channels in which 24 channels are multiplexed to create an aggregate of 1.536 Mega bits per second (Mbps).

- Time division multiplexing allows a channel to use one of 24 timeslots.

- the 24 channels are time-division multiplexed into a frame to be carried along the data stream line.

- each frame contains one sample of 8 bits from each of the channels, and a framing bit. This structure results in a frame having 193 bits.

- PCM pulse code modulation

- a TI system employs Alternate Mark Inversion (AMI) coding to reduce the required bandwidth of 1.5 MHz by a factor of two.

- the transmission is byte-synchronous whereby timing synchronization for each channel is derived from the pulses that appear within the samples (8 bits in each sample). This timing keeps everything in sequence.

- a T1 system employs generically 24 channels of 64 kbps data plus 8 kbps of overhead (sometimes referred to as channelized service), the multiplexing equipment may be configured in other ways.

- T1 may be used for a single channel of 1.536 Mbps, two high-speed data channels at 384 kbps each, and a video channel at 768 kbps.

- a T1 system service does not have to be channelized into 24 timeslots. It can be split into any number of usable data streams.

- T1-systems may multiplex T1 signals into a T2 (DS2) system, but with additional framing bits and 4 times the data rate. This results in an aggregate data rate of 6.312 Mbps.

- a T3 digital link comprises a multiplexing of 7 T2 links (and additional framing bits), resulting in a data rate of 44.736 Mbps.

- the T3 system has greater demand in high capacity applications.

- the E carrier services are the European equivalents of the T-carrier.

- the problem addressed by the present invention is the special case of transmitting data wirelessly between two systems working at the same nominal frequency. Moreover, the invention is intended for use in high speed data transmission requiring the avoidance of clocks with frequencies higher than the data bit rate.

- a common synchronization technique used in the prior art is to synchronize received data to a local clock signal using a D-type flip-flop. This technique, however, produces errors whenever setup and hold time specifications for the flip-flop are violated.

- Another technique commonly used in the prior art is to use a first-in first-out (FIFO) register to provide the necessary elasticity required to properly synchronize the received data to the local clock signal. The use of a FIFO register, however, results in a certain ripple-through delay and initialization problems associated with such a register.

- some synchronization techniques are dependent on certain hardware characteristics. One such characteristic is a metastability problem which shows up whenever a flip-flop is clocked without a guaranteed setup and/or hold time, which is exactly what happens when efforts are made to synchronize the data with a new clock.

- Elastic store read/write pointers can be implemented with separate binary up or down counters, separate up or down ring counters, or single binary up/down or single up/down ring counter.

- Elastic store data storage implementations include shift registers, addressable latches, and RAM.

- the read and write subsystems are asynchronous to each other and need to be synchronized for some brief time for reliable data transfer.

- Some sort of arbitration scheme or handshake between read/write clocks, pointers, or data must take place in order to insure that the write data is not changing at the time it is being read (i.e. the metastable condition).

- Discussion of arbitration logic and its importance to reliable data transmission is neglected in the literature. The impact on Bit Error Rate when arbitration is ignored or improperly implemented is considerable. As an example, consider a 1 micosecond read/write data period and logic with a metastable window of 1 nanosecond.

- the present invention provides a system and method of buffering data of existing wireless communication systems without the disadvantages of the prior art.

- the above-mentioned problems are solved by providing an elastic store system which maintains synchronization at the receiver, maintains end-to-end signaling and codes overhead bits needed to encapsulate data frames for wireless communication systems in frequency bands, such as the Industrial, Scientific and Medical (ISM) frequency bands, the National Information Infrastructure (NII), the Personal Communications Services (PCS) and other bands.

- ISM frequency bands allocated by the Federal Communications Commission (FCC) are spread across the frequency ranges of 902-928 MHz, 2400-2484 MHz, and 5725-5850 MHz.

- the NII frequency bands are in the range of 5725-5825 MHz.

- the PCS technology operates in the frequency range 1850-1910 MHz for the uplink (i.e., mobile transmit, base receive) and 1930-1990 MHz for the downlink (i.e., base transmit, mobile receive).

- the elastic store system provides full duplex communications while maintaining proper end-to-end signaling schemes for a variety of wireless communication systems, such as mobile systems employing Code Division Multiple Access (CDMA) in which a transmitted signal is spread over a band of frequencies much wider than the minimum bandwidth required to transmit the signal, Time Division Multiple Access (TDMA) where the users share the radio spectrum in the time domain, Frequency Division Multiple Access (FDMA) where a user is allocated at least one unique frequency for communication without interference with users in the same frequency spectrum, or similar technologies.

- CDMA Code Division Multiple Access

- TDMA Time Division Multiple Access

- FDMA Frequency Division Multiple Access

- the elastic store system provides a means of buffering a data stream to be transmitted in the ISM frequency bands, which may be written into its input at a different rate than it is read from its output.

- the elastic store system comprises two main subsystems: a transmit elastic store (TxEsto) subsystem at a transmitter and a receive elastic store (RxEsto) subsystem at a receiver.

- TxEsto transmit elastic store

- RxEsto receive elastic store

- the TxEsto generates a stuffing request, and provides underflow and overflow status of the data received from a channelizer to a framer for further processing. After detailed parallel processing, this data is sent over the air interface in the ISM band frequencies to the receiver.

- the RxEsto subsystem receives data from a deframer. For synchronization between transmitter and receiver clocks, the RxEsto subsystem clocks out the data, which is stripped off the data overhead bits, at the same rate as it was sent before encapsulation at the transmitter.

- One embodiment of the present invention is a synchronous elastic store system, comprising a shift register having a plurality of data bits, the shift register receiving a stream of digital input data and a master clock input signal which is independent of the digital input data; and an arbiter that arbitrates between a read request and a write request to the shift register, the arbiter having the master clock as an input signal and providing a control signal to the shift register.

- Another embodiment of the present invention is a synchronous digital elastic store system, comprising a shift register receiving a stream of digital input data and a master clock input signal, said master clock signal being independent of the digital input data; an arbiter that arbitrates between a read request and a write request, the arbiter providing a control signal to the shift register and generating at least one counter control signal; an up/down counter receiving the counter control signal from the arbiter and generating selector control signals; and a selector circuit receiving data from the shift register and receiving selector control signals from the up/down counter, said selector circuit selecting one of the shift register bits to be read from the elastic store.

- Yet another embodiment of the invention is a method of storing a stream of digital data in a synchronous elastic store having a shift register, the method comprising the steps of receiving a stream of digital data and a master clock signal at the shift register; synchronously arbitrating between a read request and write request to generate an arbitration control signal; and shifting the digital data into the shift register in response to the arbitration control signal and the master clock signal.

- Yet another embodiment of the invention is a synchronous elastic store system, comprising a channelizer; a synchronous elastic store having a read/write arbiter, the synchronous elastic store receivably connected to the channelizer; a framer receivably connected to the synchronous elastic store; and a wireless transmitter circuit receivably connected to the framer.

- Yet another embodiment of the invention is a synchronous elastic store system, comprising a wireless receiver circuit; a deframer receivably connected to the wireless receiver circuit; a synchronous elastic store having a read/write arbiter, the synchronous elastic store Is receivably connected to the deframer; a dechannelizer receivably connected to the synchronous elastic store.

- FIG. 1 is a functional block diagram depicting the location of the elastic store system in a synchronous wireless communication system.

- FIG. 2 is a block diagram of a data frame format using a stuff bit for the elastic store system shown in FIG. 1.

- FIG. 3 is a block diagram of a structure for a shift register that is used within the elastic store system shown in FIG. 1.

- FIG. 4 is a functional block diagram depicting one embodiment of the elastic store system shown in FIG. 1.

- FIG. 5 is a functional block diagram of the receiver dejitter circuit used in the elastic store system shown in FIG. 4.

- FIG. 6 is a state machine diagram illustrating the process flow for the elastic store system shown in FIG. 1.

- FIG. 7 is a flowchart of the Reset process shown in FIG. 6.

- FIG. 8 is a flowchart of the Write request anti-metastable sampling process shown in FIG. 6.

- FIG. 9 is a flowchart of the Write request detection process shown in FIG. 6.

- FIG. 10 is a flowchart of the Read request anti-metastable sampling process shown in FIG. 6.

- FIG. 11 is a flowchart of the Read request detection process shown in FIG. 6.

- FIG. 12 is a flowchart of the Read/Write Semaphore process (Sampled Arbiter) shown in FIG. 6.

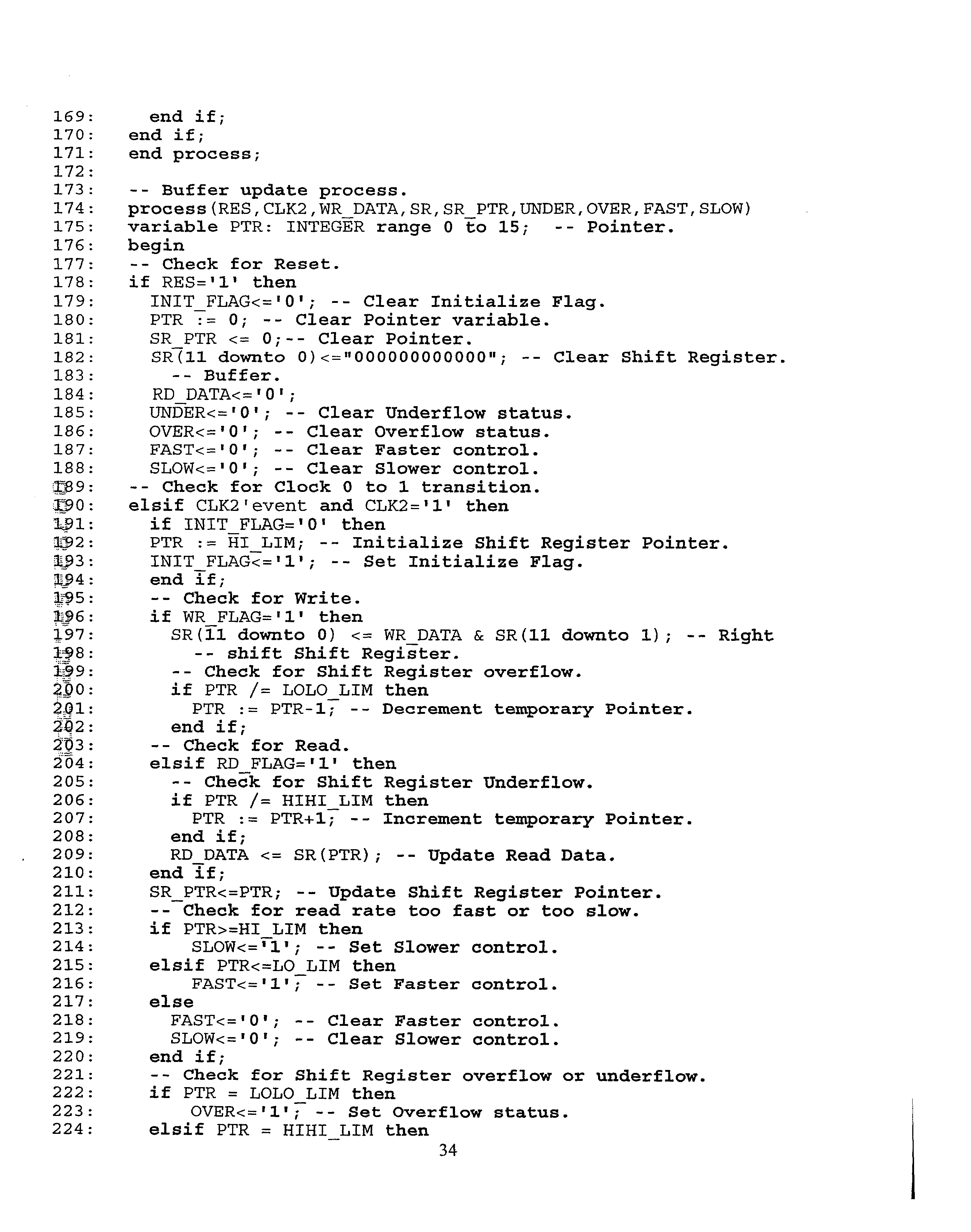

- FIGS. 13 a and 13 b are a flowchart of the Buffer update process shown in FIG. 6.

- FIG. 14 is a flowchart of the receiver dejitter process shown in FIG. 6.

- FIG. 15 is a block diagram showing exemplary dejitter circuit interconnections for a T3/E3 embodiment of the communication system receiver shown in FIG. 1.

- FIG. 16 is a block diagram showing exemplary dejitter circuit interconnections for a T1/E1 embodiment of the communication system receiver shown in FIG. 1.

- FIG. 17 is a functional block diagram of the arbitration control circuit used in the elastic store system shown in FIG. 4.

- the present invention maintains synchronization between the transmitter and receiver clocks, end-to-end signaling and coding, and overhead bits need to encapsulate data frames sent over wireless media.

- the elastic store system comprises two main subsystems, namely, a transmit elastic store (TxEsto) subsystem and a receive elastic store (RxEsto) subsystem.

- TxEsto subsystem receives parallel data from an existing channelizer, generates a stuffing request, and provides underflow and overflow status to a framer.

- the RxEsto subsystem receives parallel data from a deframer, strips off the data overhead bits and clocks out data at the same rate as it was sent before encapsulation at the transmitter.

- FIG. 1 is a block diagram depicting the location of the elastic store system 100 in a wireless communication system 98 .

- the elastic store system 100 supports full-duplex synchronous voice and data communications.

- the system 100 comprises a Transmit Elastic Store (TxEsto) subsystem 120 and a Receive Elastic Store (RxEsto) subsystem 300 .

- the TxEsto subsystem 120 comprises a shift register that provides a means of buffering data that may be written into its input at a slightly different rate that it is read from its output. In one embodiment, the clock frequency used in writing data to the TxEsto 120 is 20 MHz.

- the TxEsto subsystem 120 communicates with a channelizer 110 and a framer and signaling controller 130 within a transmitter 105 .

- the transmitter 105 consists of the TxEsto subsystem 120 , the channelizer 110 , the framer and signaling controller 130 and other functional elements.

- the channelizer acts as a demultiplexer or a line driver depending on the inputted data (e.g., demultiplexes the incoming data when it is of type T3 to 28 T1 channels).

- the input data signals may virtually be any standardized signal such as, for example, DSO/E0, T1/E1, T2/E2, T3/E3, Ethernet (LAN/WAN), intranet, or Internet signals.

- the input data signals are either multiple T1/E1 channels or a single T3/E3 channel.

- the transmitter 105 is characterized by a parallel structure for processing data extracted synchronously at substantially the same rate of a T1 (E1) channel.

- the elastic store system 100 provides an elastic store for each embedded channel.

- the framer and signaling controller 130 provides a frame structure to the data received from the TxEsto 120 . After further processing, the resulting data is sent over an air-link 150 by use of a wireless transmitter circuit a and a wireless receiver circuit (not shown). In one embodiment, the air-link 150 corresponds to the ISM bands.

- the RxEsto subsystem 300 receives data from a deframer 140 which is in addition to other functional elements, a subsystem within a receiver 160 .

- the deframer 140 strips the extra bits from the data stream and writes the resulting data to the RxEsto 300 at a certain clock frequency f 1 . In one embodiment the clock frequency f 1 is 20 MHz.

- the frequency f may be selected from a range of about 10 KHz to 1 GHz.

- the RxEsto subsystem 300 buffers the data received from the deframer 140 and reads it out at a clock frequency f 2 , which in one embodiment is a multiple of frequency f 1 , e.g., 10 MHz, but in another embodiment may be at same as frequency f 1 .

- the buffering of the data is done to avoid underflow and overflow states of the RxEsto.

- a Rx Dechannelizer 170 receives output signals from the Rx Elastic Store subsystem 300 . For example, when T3/E3 output is desired, the Dechannelizer 170 constructs T3/E3 data from N receive data streams. The Rx Dechannelizer 170 receives N data channels from the Rx Elastic Store 300 and constructs T3/E3 data from the N channels containing Rx packet data. The inputted data (multiple T1 channels/E1 channels) to the Rx Dechannelizer 170 can either be sent out as multiple T1/E1 channels or multiplexed into a single T3/E3 channel.

- bit stuffing allows reading and writing of data without underflow or overflow of the elastic store system 100 .

- the bit stuffing technique requires a pointer which indicates the current position in the buffer. The pointer is incremented when the elastic store is filling (write) and is decremented when the elastic store is emptying (read). Pointer status may indicate underflow, overflow, near underflow and near overflow. The near underflow status and the near overflow status are utilized by the elastic store subsystem to prevent occurrence of underflow or overflow conditions.

- Data is typically written into the elastic store at its lowest rank ordered position and shifted toward the highest rank ordered position. Data is read from the position indicated by the pointer.

- bit stuffing consider a typical synchronous communications link where data is encapsulated with overhead bits before transmission. At the receiver, the data overhead bits are stripped off and the data is clocked out at the same rate as it was sent before encapsulation at the transmitter.

- the postamble comprises the stuffing bit 202 and multiple justification bits.

- the stuffing bit 202 dynamically changes from a real data bit 202 ′ to a stuff bit 202 ′′ on a frame by frame basis (see FIG. 2). Whether the stuffing bit is a real data bit or not is indicated by the justification bits.

- the transmitter 105 normally sends real data in the stuffing bit position and sets the corresponding justification code.

- the receiver 160 decodes the justification bits, putting the stuffing bit into its elastic buffer 300 when the justification bits indicate the stuff bit is data, and throws away the bit and suppresses the write clock to the elastic store 300 when the justification bits indicate the stuff bit is not data.

- the shift register 320 consists of n-bits which corresponds to the number of Data bits in the shift register, i.e., the length of the shift register.

- n 12 bits for the Tx Elastic Store 120

- n 14 bits for the Rx Elastic Store 300 .

- the length of the shift register may vary depending on the type and format of the input data.

- the shift register 320 also includes a pointer 222 which is decremented for writes and incremented for reads, a HiHi_LIM 224 which indicates the underflow status (this limit is equal to eleven for the Tx Elastic Store and is equal to thirteen for the Rx Elastic Store), a LoLo_LIM 226 that indicates the overflow status (this limit is equal to zero for both the Tx and Rx Elastic Stores), and a Hi_LIM 228 (this limit is equal to nine for the Tx Elastic Store and eleven for the Rx Elastic Store).

- the Hi_LIM 228 indicates for the Tx Elastic Store 120 that a stuff request should be generated to the framer 130 and indicates for the Rx Elastic Store 300 a read slower control to the Dechannelizer 170 (FIG. 1).

- the Dechannelizer is a digital multiplexer whereby the 28 T1 channels, as an example, can be multiplexed back to one T3 channel.

- a Lo_LIM parameter 230 (this limit is equal to two for the Rx Elastic Store and is not needed for the Tx Elastic Store) is used to indicate a read faster control in the case of the receive elastic store.

- the shift register pointer 222 is initialized first to a given value, then, depending if it is a write or read operation, the shift register pointer 222 is shifted to the right or left respectively. Furthermore, the data is right shifted for a write operation only from the most significant bit 232 to the least significant bit 234 .

- the four limits described above may be dynamically set by a micro-controller (not shown), such as a Hitachi H8/3048, that is part of the communication system 98 (FIG. 1).

- the elastic store system 100 includes the Tx Elastic Store subsystem 120 and the Rx Elastic Store subsystem 300 .

- One embodiment of the Tx Elastic Store subsystem 120 includes an elastic store module 321 having a shift register buffer that provides a way to buffer data which may be written into its input at a slightly lower rate than it is read from its output. Functions include generation of a stuff request, underflow status and overflow status. All inputs and outputs are sampled by a high speed clock, except RESET which is asynchronous.

- VHDL Very high speed integrated circuit Hardware Description Language

- RX Elastic Store subsystem 300 includes the elastic store module 321 and a dejitter circuit 390 .

- the RX Elastic Store subsystem 300 has similar characteristics to the Tx Elastic Store 120 with slight variations. Functions for the Rx Elastic Store 300 include generation of a “faster” control signal, a “slower” control signal, underflow status and overflow status.

- the dejitter circuit logic 390 uses the faster and slower controls to produce a read request signal for reading out the contents of the elastic store. All inputs and outputs are sampled by a high speed clock, except RESET which is asynchronous.

- a VHDL code listing for the major modules of the Rx Elastic Store subsystem 300 is provided in Appendix B.

- Input and output signals for the elastic store module 321 are summarized in Table 1 below: TABLE 1 Input Signals Output Signals RESET Read Data Preset Stuff Request (I/O) Clock Underflow Status (I/O) Write Data (from Channelizer if TxEsto) Overflow Status (I/O) Write Request (From Channelizer if TxEsto) Read Request (from Framer if TxEsto)

- LO_LIM Shift register pointer low limit For Rx Elastic Store, this corresponds to read faster control.

- HI_LIM Shift register pointer high limit This corresponds for Tx Elastic Store to Stuff limit and for Rx Elastic Store to read slower control.

- HIHI_LIM HiHi limit represents the High high value for the Shift register pointer.

- the elastic store module 321 comprises an arbitration control block 310 , a shift register block 320 , a selector block 340 , an Up/Down counter block 330 , a register 350 , a near overflow comparator 360 , a near underflow comparator 370 , an underflow comparator 380 , an overflow comparator 385 .

- a dejitter circuit 390 connects to the elastic store module 321 .

- Proper arbitration requires some sort of delay element or sampling clock with a shorter period than the read/write data.

- the arbitration latency may be three or more delays in order to detect read/write clock edges rather than levels and to eliminate metastability.

- the arbitration in one embodiment is done on the data bit interval. While other implementations are possible ( e.g., at the frame rate), the required resolution of the arbiter is still the read/write data interval. More significantly, arbitration on a bit by bit basis provides more responsive fast/slow controls for the dejitter circuit from the receive elastic store.

- the dejittered output may be applied to a phase lock loop (PLL) which generates a smooth symmetrical read request multiple of the dejitter read request for multiplexing the read data from multiple Elastic Stores into a single high speed data stream which is synchronous with the transmit source.

- PLL phase lock loop

- VCO voltage controlled oscillator

- the arbitration control block 310 has three inputs, namely a Write_Request signal 302 from the channelizer 110 (FIG. 1) in the case of the transmit elastic store 120 or from the Deframer 140 in the case of the receive elastic store 300 ; a Read_Request signal 303 from the framer 130 in the case of transmit elastic store 120 or from the dechannelizer 170 in case of the receive elastic store 300 ; and a Master Clock (MClk) 301 (also referred to as a sampling clock).

- the receive elastic store 321 obtains the Read_Request signal from a phase lock loop (PLL) 1550 (FIG.

- PLL phase lock loop

- the arbitration control block 310 controls the metastable condition by monitoring the read and write.

- a metastable condition is an undefined state (neither one nor zero) which arises as a result of sampling at the instant that the data is changing.

- the arbitration control block 310 utilizes the three Write Request X sampling registers and the three Read Request X sampling registers to control the metastable condition.

- the arbitration control block 310 generates several output signals, namely a Write Activate control signal 304 , which is fed to the n-bit shift register 320 , a Read Activate control signal 305 , which is fed to the register 350 , a counter enable signal 306 and an up/down control pointer signal 307 , both of which are fed to the up/down counter block 330 .

- the n-bit shift register 320 (detailed in FIG. 3) has three inputs, namely a Write_Data signal 308 , the Write Activate control 304 and a Master Clock 301 (not shown as an input).

- the Write_Data signal 308 is received from the channelizer 110 in the case of the transmit elastic store 120 ; or from the deframer 140 in the case of the receive elastic store 300 .

- the Write_Request signal 302 has more priority than the Read_Request signal 303 , then at the activation of the Write Activate control 304 in conjunction with the Master clock, the data is right shifted (most significant bit to least significant bit) and the pointer 222 (FIG. 3 ) is moved to the right.

- the Read_Request 303 is prior to the Write_Request 302 , only the pointer 222 is moved to the left toward the most significant bit.

- the N to 1 selector 340 selects one of the n-bit shift register bits at its input from the bus 309 . This decision is carried out inside the selector block 340 and is based on the value of the up/down counter 330 .

- the up/down counter 330 is controlled by the counter enable signal 306 , the up/down control pointer 307 and the Master Clock 301 (not shown as an input).

- the Read Activate control 305 clocks the data bit selected by the 1 to N selector 340 into the register 350 .

- the value of a pointer 312 at the output of the up/down counter 330 is compared to a near overflow comparator 360 (this corresponds to Lo_LIM 230 in FIG.

- a near underflow comparator 370 (this corresponds to Hi_LIM 228 in FIG. 3); an underflow comparator 380 (this corresponds to HiHi_LIM 224 in FIG. 3) and to an overflow comparator (which corresponds to LoLo_LIM 226 in FIG. 3).

- a faster read signal 362 is generated for the receive elastic store 300 which goes into the dejitter circuit 390 .

- a stuff request 372 is sent to the framer 140 for the transmit elastic store 120 and a slow read is generated for the receive elastic store 300 .

- the underflow flag 382 is set, and if the up/down counter 330 is equal to the overflow comparator 385 , the overflow flag 386 is set.

- FIG. 5 a functional block diagram of one embodiment of the dejitter circuit 390 which is a part of the RxEsto 300 within the elastic store system 100 will be described.

- the RxEsto's Read_Request signal is typically recovered from the Master Clock using the dejitter circuit 390 .

- the dejitter circuit 390 produces a symmetrical Read_Request 303 at its output which has the average frequency of the MClk at its input. This is accomplished by adjusting rate of the Read_Request 303 up or down according to near overflow and near underflow buffer pointer indicators.

- the Read_Request 303 provided by the dejitter circuit is also used by the receiver interface. Under normal operation, the RxEsto 300 will not underflow or overflow. However, the underflow signal 382 and the overflow signal 386 are provided for downstream error handling.

- the dejitter circuit 390 comprises a decision block 400 , a counter selector block 405 , a down counter block 410 , a decoder block 420 and a flip-flop block 415 .

- the dejitter circuit 390 is replicated for each channel of the system. For example, in an embodiment having 28 channels, there are 28 elastic stores 321 and 28 dejitter circuits 390 , each of which have associated level signals and underflow/overflow signals as seen in FIGS. 4, 15 and 16 .

- the decision block 400 receives two of its three inputs 425 from the receive elastic store 321 (FIG. 4). In one embodiment, the decision block 400 performs the functions of states 1215 - 1230 of Dejitter process 492 (FIG. 14).

- the inputs to decision block 400 are the Near underflow signal 372 , the Near overflow signal 362 and the Master Clock (MClk) 301 .

- the decision block 400 provides the selector input for the counter selector block 405 to determine which value count of inputs 440 will be used depending on the inputted signals from the Rx elastic store 321 . Once this decision is made, it is fed into the counter selector block 405 via SEL signal 430 .

- the count selector block 405 selects the value for count from the inputs 440 which is then fed to the count input of the down counter block 410 .

- count value used by count select block 405 is calculated by the following formula:

- n (TotalnumberofMCLkperframe/Totallengthofdatawithintheframe)*numberofchannels

- n (TotalnumberofMCLKperframe/Totallengthofdatawithintheframe ⁇ 1)*numberofchannels

- n (TotalnumberofMCLKperframe+1/Totallengthofdataintheframe)*numberofchannels

- n (TotalnumberofMCLKperframe+1/Totallengthofdataintheframe ⁇ 1)*numberofchannels

- n (TotalnumberofMCLKperframe ⁇ 1/Totallengthofdataintheframe)*numberofchannels

- n (TotalnumberofMCLKperframe ⁇ 1/Totallengthofdataintheframe ⁇ 1)*numberofchannels

- each chip corresponds to 2 * MClk cycle rate.

- branches There are two branches (an I branch and a Q branch) and 14 channels per branch.

- MClk per bit can vary is: 28.729 to 29.173. Since only integer values can be used for

- these values are hard coded in the logic implementation. In other words, they are calculated following this method and then only the results (in this case, 27 to 29) are utilized for the logic design.

- the down counter block 410 starts from the reset state and keeps counting the master clock (MClk) pulses. Inside the down counter block 410 , the count value is input from the counter selector block 405 . A terminal count (Tc) is the output from the down counter block 410 to reset the pulse when it is equal to zero, and thus a LOAD signal is fed back to a LOAD input of the down counter block 410 . At the same time, the flip-flop block 415 is set. The down counter 410 communicates with the decoder block 420 which decodes the value of the counter received. When the counter's value is equal to n/2, it resets the flip-flop 415 .

- the variable n refers here to the number of channels utilized by the system 98, e.g., 28 channels in one embodiment.

- FIG. 5 shows the concept behind the digital dejitter circuit 390 used in one embodiment.

- a slight change is made when implementing the dejitter circuit for a T3/E3/DS3 system (further described in conjunction with FIG. 15 below) and the dejitter circuit for a TI/El/DS1 system (further described in conjunction with FIG. 16 below) because the destination of the dejitter output is different in each case.

- FIG. 6 shows a state machine diagram for the TxEsto and RxEsto subsystems within the elastic store system 100 .

- the process states comprise a Reset process 460 (FIG. 7), a Write request anti-metastable sampling process 464 (FIG. 8), a Write request detection process 468 (FIG. 9), a Read request anti-metastable sampling process 472 (FIG. 10), a Read request detection process 476 (FIG. 11), a Read/Write semaphore process 480 (FIG. 12), a Buffer update process 486 (FIG. 13 a, 13 b ), and for the RxEsto subsystem only, a dejitter circuit process 492 (FIG. 14).

- the inputs to each process of FIG. 6 are sampled by the master clock, whereas communication between processes is via flags and registers.

- the RESET process 460 is triggered when a power up or a manual reset state 505 is started.

- the following tasks are then carried out simultaneously: clear write request sampling registers 510 , clear detect Write request and process registers 515 , clear Read request sampling and process registers 520 , clear detect Read Request and process registers 525 , clear Read/Write semaphore and process registers 530 , clear Buffer update and process registers 535 , and clear Receiver Dejitter and process registers 540 .

- process 460 enters state 545 to proceed to a state machine state of FIG. 6.

- the state 510 corresponds to setting WR_RQ1, WR_RQ2 and WR_RQ3 signals to zero.

- Clearing detect Write Request registers at state 515 corresponds to setting the Write request Flag (WR_RQ_FLAG) to zero.

- clearing Read request sampling process registers at state 520 corresponds to setting RD_RQ1, RD_RQ2 and RD_RQ3 signals to zero.

- State 525 corresponds to clearing the Read request flag by setting RD_RQ_FLAG to zero.

- the Clear Read/Write semaphore state 530 corresponds to setting both Read and Write Flags to zero.

- Clearing Buffer update state 535 corresponds to clearing the initialize flag (INIT_Flag set to zero), clearing the shift register pointer (SR_PTR set to zero), clearing the shift register buffer (SR(11 to 0) set to zero), clearing the read data (RD_DATA set to zero), clearing the stuff request and clearing both underflow and overflow status.

- the clear receiver dejitter process registers state 540 corresponds to clearing the counter and clearing both “read faster” and “read slower” status.

- Process 464 has three parameters namely: RESET, CLOCK and WR_RQ signals.

- the initial task performed by the process 464 is to check for RESET. If RESET is set to one, the WR_RQ1, WR_RQ2 and WR_RQ3 signals are cleared. Otherwise, a test is carried out at state 605 to check for CLOCK. If CLOCK is set to one, then a test for an active state of write request (WR_RQ) is made at state 610 .

- process 464 samples Write Request 2 at state 615 , samples Write Request 1 at state 620 and samples Write Request at state 625 . Once these tasks are carried out, a loop 630 is entered where the process 464 goes back to state 605 to wait for the next Clock event to happen.

- Process 468 has two parameters, namely: RESET and CLOCK.

- process 468 detects a write request transition at decision states 725 and 730 . If write request 2 is equal to one, as determined at decision state 725 and write request 3 is equal to zero, as determined at decision state 730 , then process 468 sets the write request flag at state 735 . In any other case and after all the above tasks were carried out, the process enters a loop 740 where the write request detection process 468 goes back to state 710 waiting for the next Clock event.

- Process 472 has three parameters, namely: RESET, CLOCK and RD_RQ.

- RESET RESET

- CLOCK Read Request Anti-metastable Sampling process

- RD_RQ RD_RQ

- process 472 samples Read Request 2 by setting RD_RQ3 to RD_RQ2 at state 825 , samples Read Request1 by setting RD_RQ2 to RD_RQ1 at state 830 and samples Read Request by setting RD_RQ1 to RD_RQ at state 835 . Once these tasks are carried out, the process 472 enters a loop 840 waiting for the next event clock at state 815 .

- the Read Request Detection process 476 described in FIG. 11 has two parameters, namely: RESET and CLOCK.

- process 476 detects a read request transition at decision states 925 and 930 . If read request 2 is equal to one, as determined at decision state 925 and read request 3 is equal to zero, as determined at decision state 930 , then process 476 sets the read request flag at state 935 . In any other case and after all the above tasks were carried out, the process 476 enters a loop 940 waiting for the next clock event at state 910 .

- the Read/Write Semaphore process 480 will be described.

- the process 480 has two parameters, namely: RESET and CLOCK.

- RESET RESET

- CLOCK CLOCK

- a test is carried out to check for RESET. If the RESET signal is set to one, both write and read flags are cleared.

- Process 480 moves from the START state 1005 to a decision state 1010 wherein a test to check for clock event is carried out. If the CLOCK signal is sampled (in other words, if it is set to one), then process 480 checks the status of the read request flag at decision state 1015 . If the read request flag is set to zero, process 480 continues at a decision state 1020 to determine the status of the write request flag.

- write request flag is set to one as determined at decision state 1020 and both write and read flags are set to zero at decision states 1025 and 1030 , respectively; the write flag is set to one at state 1035 . Otherwise, if the read request flag is set to one as determined at decision state 1015 , the write request flag is set to zero as determined at decision state 1020 and either the read flag or the write flag are set to one at decision states 1030 and 1025 respectively, then process 480 sets the write flag to zero at state 1040 .

- process 480 sets the read flag to one at state 1065 . Otherwise, process 480 sets the read flag to zero at state 1070 .

- the read/write semaphore process 480 enters a loop 1075 to wait for an clock event to take place as determined at state 1010 . It is necessary to note that the test carried out at decision state 1015 is bypassed for the transmit elastic store 120 so that the write request has priority over the read request. Furthermore, the test carried out at decision state 1045 is bypassed for the receive elastic store 300 so that the read request has priority over the write request.

- Process 486 has ten parameters and one variable, namely: RESET, CLOCK, Write_Data, Shift Register, Shift Register Pointer, Stuff, Underflow and Overflow, and a pointer varying from 0 to 15.

- RESET is set to one

- process 486 clears the Initialize flag by setting its value to zero, clears the pointer variable 222 by setting it to zero, clears the shift register 320 shown in FIGS. 3 and 4 by setting the value of its twelve bits (for the transmit elastic store 120 ) to zero, clears the read data by setting its value to zero, clears the stuff request by setting it to zero and clears the underflow and overflows status by setting their values to zero.

- the buffer update process 486 moves from the START state 1105 to a decision state 1110 to check for a clock event. If the clock is set to one and the initialize flag (INIT_Flag) is set to zero at decision state 1115 , then process 486 initializes the shift register pointer 222 (FIG. 3) to Hi_LIM 228 and sets the INIT_Flag to one at state 1120 . A test is then carried out to check for the write flag at decision state 1125 . If the write flag is set to one, as determined at decision state 1125 , then process 486 shifts the shift register 320 to the right at state 1135 . Furthermore, process 486 checks for shift register overflow at decision state 1145 .

- process 486 decrements the pointer 222 at state 1155 . Otherwise, if the write flag is set to zero, as determined at decision state 1125 , and the read flag is set to one at decision state 1130 , then process 486 moves to state 1140 to obtain read data from the shift register bit indicated by the pointer 222 . Proceeding to a decision state 1150 , process 486 checks for shift register underflow. If the pointer 222 is not equal to HiHi_LIM 224 at decision state 1150 , the pointer 222 is incremented and the read data is updated at state 1160 .

- the process 486 updates the shift register pointer 222 and moves to decision state 1165 .

- a check for shift register overflow is then carried out at decision state 1165 . If the pointer PTR 222 (FIG. 3) is equal to LoLo_LIM 226 as determined at decision state 1165 , then process 486 sets the overflow flag to one at state 1170 . Otherwise, if the shift register pointer PTR 222 is equal to Hi_LIM 228 as determined at decision state 1175 , the underflow flag is set to one at state 1180 . However, if the shift register pointer 222 is not equal to Hi_LIM 228 , as determined at decision state 1175 , then process 486 clears both overflow and underflow flags at state 1185 . Proceeding to decision state 1190 on FIG.

- process 486 determines if the shift register pointer PTR 222 is equal to HI_LIM 228 and if the stuff request is set to zero at decision state 1192 . If so, then process 486 sets the stuff request to one at state 1194 . Otherwise, if the pointer PTR 222 is not equal to Hi_LIM 228 , as determined at decision state 1190 , or the stuff request (STF) is not set to zero at decision state 1192 , then process 486 clears the stuff request at state 1193 .

- the process 486 enters a loop 1199 waiting for the next clock event at decision state 1110 (FIG. 13 a ).

- the Dejitter process 492 carries out a test to check for RESET before it enters START state 1205 . If RESET is set to one, the dejitter process 492 clears all its parameters and sets the period to short (period corresponds to the amount of time the Read_Request is high).

- the dejitter counter 410 (FIG. 5), which is used to count the Master Clock (MClk) cycles, is incremented at state 1210 .

- a test is then carried out to test if an underflow status has occurred at decision state 1215 .

- process 492 checks if an overflow status has occurred at decision state 1225 . If so, then process 492 sets the period to a short value at state 1230 (this corresponds to a faster read).

- process 492 sets the Read_Request to zero at state 1255 and resets the counter 410 at state 1260 . Once these tasks are carried out, the process 492 enters a loop 1265 to wait for the next MClk event (Edge) at decision state 1207 .

- FIG. 5 shows the concept behind the digital dejitter circuit 390 used in one embodiment.

- a slight change is made when implementing the dejitter circuit for a T3/E3/DS3 system and the dejitter circuit for a T1/E1/DS1 system because the destination of the dejitter output is different in each case.

- the output of the dejitter circuit 390 goes to a phase comparator 1520 where it is fed to a low pass filter 1530 and into a voltage controlled oscillator (VCO) 1540 .

- the output of the VCO 1540 is sent to the dechannelizer 170 (which is in this case configured as a multiplexer).

- the output is sent directly to a T1 line interface as shown and described in conjunction with FIG. 16.

- the phase comparator 1520 has two input signals, namely the Dejitter Read_Req from the dejitter circuit 390 and a divide-by-28 count from a divider 1560 (this divide by n count corresponds to a Read-Req. from the elastic store, where n is the number of channels, e.g., 28 channels in one embodiment).

- the divider 1560 obtains its input from the VCO 1540 .

- the phase comparator 1520 outputs the instantaneous phase difference between the Dejitter Read_Req and the n/28 count signals. The resulting signal is then fed into the low pass filter 1530 to be averaged.

- the output signal from the low pass filter 1530 is then used to adjust the frequency of the VCO 1540 so that the phase difference on average of the whole system is equal to zero.

- the phase comparator 1520 , low-pass filter 1530 , the VCO 1540 and the divider circuit 1560 components together comprise the phase lock loop (PLL) circuit 1550 .

- FIG. 16 the processing of information at the output of the dejitter circuit 390 in the case of a T1/E1/DS1 system is shown.

- the output signals 1610 which correspond to the RD_Request, from the dejitter circuit 390 are sent back to the receive elastic store 321 .

- the data that is read from the Rx elastic store 321 is sent to a T1/E1/DS1 line interface 1620 (not shown) via a Read_Data signal 1630 .

- the arbitration control block 310 within the elastic store module 321 (FIG. 4) will now be described.

- the arbitration control block also known as the arbiter 310 comprises a Read latch 1710 , a Write latch 1720 and a Read/Write priority encoder block 1730 .

- the arbiter has three inputs, namely a Read_Req signal 303 from the framer 130 (FIG. 1) in the case of the transmit elastic store 120 or from the dechannelizer 170 in case of the receive elastic store 300 , a Write_Req signal 302 from the channelizer 110 in the case of the transmit elastic store 120 or from the deframer 140 in the case of the receive elastic store 300 , and a Master Clock (MClk) 301 (FIG. 4) from the timing block 135 .

- the Read latch 1710 converts the Read_Req pulse to a read level (which can be either zero or one) by utilizing the three Read Request X sampling registers previously mentioned above.

- the Read/Write priority encoder block 1730 converts the Write_Req pulse to a write level by utilizing the three Write Request X sampling registers, previously mentioned, and the resulting signal is then fed to the Read/Write priority encoder block 1730 .

- the Read/Write priority encoder block 1730 is an “AND gate” which, upon receipt of the signal from either the Write latch 1720 or Read latch 1710 and the MClik, activates the corresponding signal. For example, if a Read_Req is received, then block 1730 activates the Read Activate signal 305 . As seen in FIG. 4, the Read Activate signal 305 is a control signal for register 350 . Otherwise, if a Write_Req 302 is received, then block 1730 activates the Write Activate signal 304 . As seen in FIG. 4, the Write Activate signal 304 is a control signal for the shift register 320 .

- the Read/Write priority block 1730 controls the up/down counter 330 (FIG. 4) via the up/down control signal 307 and the counter_enable signal 306 . Indeed, if the Read signal 305 has been activated, then the up/down counter pointer 307 is decremented. Otherwise, if the Write signal 304 is activated, then Read/Write priority encoder block 1730 increments the up/down counter pointer 307 . The counter_enable signal 306 is activated for both read and write operations. Moreover, once either of the Read signal 305 or the Write signal 304 is activated, the corresponding levels are reset ( 1740 and 1750 ).

- the present invention overcomes the long-standing need for a simpler synchronization at the receiver, transparently transmitting data at a high data rate and monitoring the underflow and overflow states of the elastic store of wireless carrier systems without the disadvantages of conventional methods.

- the present invention may be embodied in other specific forms without departing from its spirit or essential characteristics.

- the described embodiment is to be considered in all respects only as illustrative and not restrictive and the scope of the invention is, therefore, indicated by the appended claims rather than by the foregoing description. All changes which come within the meaning and range of equivalency of the claims are to be embraced within their scope.

Abstract

Description

- This application is related to U.S. application Ser. No. 08/954,217, filed Oct. 29, 1997, entitled Wireless Multimedia Carrier System, and to U.S. application Ser. No. 08/970,729, filed Nov. 14, 1997, entitled Wireless T/E Transceiver Frame and Signaling Controller, each having a common assignee.

- The Appendices contain material which is subject to copyright protection. The copyright owner has no objection to the reproduction of such material, as it is appears in the files of the Patent and Trademark Office, but otherwise reserves all copyright rights whatsoever.

- 1. Field of the Invention

- The present invention generally relates to voice and data communication systems. More particularly, this invention relates to synchronous wireless communication systems.

- 2. Description of the Related Technology

- T-carrier systems have become an essential part of modern telecommunications systems. A T-carrier system is found in every telephone company in North America. A T-carrier allows for transmission of one or more telephone calls or data connections by modem. The basic unit of signaling is DS0, followed by progressively higher speed signaling rates. First generation T-carrier systems, called T1, which carry Digital Signal Level 1 (DS 1), employ a full duplex all-digital service. The digital stream is capable of carrying standard 64 kilobits per second (kbps) channels in which 24 channels are multiplexed to create an aggregate of 1.536 Mega bits per second (Mbps). Time division multiplexing (TDM) allows a channel to use one of 24 timeslots. More particularly, the 24 channels are time-division multiplexed into a frame to be carried along the data stream line. Typically, each frame contains one sample of 8 bits from each of the channels, and a framing bit. This structure results in a frame having 193 bits. In view of employing pulse code modulation (PCM) on each channel, there are 8000 frames per second. Hence, a frame is 125 microseconds long. Eight kbps of overhead bits are added (due to framing) to 1.536 Mbps, thereby yielding an aggregate of 1.544 Mbps.

- A TI system employs Alternate Mark Inversion (AMI) coding to reduce the required bandwidth of 1.5 MHz by a factor of two. The transmission is byte-synchronous whereby timing synchronization for each channel is derived from the pulses that appear within the samples (8 bits in each sample). This timing keeps everything in sequence. Although, a T1 system employs generically 24 channels of 64 kbps data plus 8 kbps of overhead (sometimes referred to as channelized service), the multiplexing equipment may be configured in other ways. For example, T1 may be used for a single channel of 1.536 Mbps, two high-speed data channels at 384 kbps each, and a video channel at 768 kbps. In short, a T1 system service does not have to be channelized into 24 timeslots. It can be split into any number of usable data streams.

- T1-systems may multiplex T1 signals into a T2 (DS2) system, but with additional framing bits and 4 times the data rate. This results in an aggregate data rate of 6.312 Mbps. Similarly, a T3 digital link comprises a multiplexing of 7 T2 links (and additional framing bits), resulting in a data rate of 44.736 Mbps. The T3 system has greater demand in high capacity applications. The E carrier services are the European equivalents of the T-carrier.

- The problem addressed by the present invention is the special case of transmitting data wirelessly between two systems working at the same nominal frequency. Moreover, the invention is intended for use in high speed data transmission requiring the avoidance of clocks with frequencies higher than the data bit rate.

- A common synchronization technique used in the prior art is to synchronize received data to a local clock signal using a D-type flip-flop. This technique, however, produces errors whenever setup and hold time specifications for the flip-flop are violated. Another technique commonly used in the prior art is to use a first-in first-out (FIFO) register to provide the necessary elasticity required to properly synchronize the received data to the local clock signal. The use of a FIFO register, however, results in a certain ripple-through delay and initialization problems associated with such a register. Furthermore, some synchronization techniques are dependent on certain hardware characteristics. One such characteristic is a metastability problem which shows up whenever a flip-flop is clocked without a guaranteed setup and/or hold time, which is exactly what happens when efforts are made to synchronize the data with a new clock.

- Text books and papers abound on elastic store implementation. Elastic store read/write pointers can be implemented with separate binary up or down counters, separate up or down ring counters, or single binary up/down or single up/down ring counter. Elastic store data storage implementations include shift registers, addressable latches, and RAM.

- Regardless of the implementation, the read and write subsystems are asynchronous to each other and need to be synchronized for some brief time for reliable data transfer. Some sort of arbitration scheme or handshake between read/write clocks, pointers, or data must take place in order to insure that the write data is not changing at the time it is being read (i.e. the metastable condition). Discussion of arbitration logic and its importance to reliable data transmission is neglected in the literature. The impact on Bit Error Rate when arbitration is ignored or improperly implemented is considerable. As an example, consider a 1 micosecond read/write data period and logic with a metastable window of 1 nanosecond. If the read and write are stochastically independent, the probability of reading a bit while it is changing is approximately equal to 1×10 −9 /1×1- −6=1×10−1! In fact the read and write rates are not independent since they are ideally equal. This could result in long periods where the read and write clock drift together, thus producing nearly continuous metastability and catastrophic error rates.

- To overcome the above problems, the present invention provides a system and method of buffering data of existing wireless communication systems without the disadvantages of the prior art. The above-mentioned problems are solved by providing an elastic store system which maintains synchronization at the receiver, maintains end-to-end signaling and codes overhead bits needed to encapsulate data frames for wireless communication systems in frequency bands, such as the Industrial, Scientific and Medical (ISM) frequency bands, the National Information Infrastructure (NII), the Personal Communications Services (PCS) and other bands. The ISM frequency bands allocated by the Federal Communications Commission (FCC) are spread across the frequency ranges of 902-928 MHz, 2400-2484 MHz, and 5725-5850 MHz. The NII frequency bands are in the range of 5725-5825 MHz. The PCS technology operates in the frequency range 1850-1910 MHz for the uplink (i.e., mobile transmit, base receive) and 1930-1990 MHz for the downlink (i.e., base transmit, mobile receive). The elastic store system provides full duplex communications while maintaining proper end-to-end signaling schemes for a variety of wireless communication systems, such as mobile systems employing Code Division Multiple Access (CDMA) in which a transmitted signal is spread over a band of frequencies much wider than the minimum bandwidth required to transmit the signal, Time Division Multiple Access (TDMA) where the users share the radio spectrum in the time domain, Frequency Division Multiple Access (FDMA) where a user is allocated at least one unique frequency for communication without interference with users in the same frequency spectrum, or similar technologies.

- In accordance with one embodiment of the present invention, the elastic store system provides a means of buffering a data stream to be transmitted in the ISM frequency bands, which may be written into its input at a different rate than it is read from its output. The elastic store system comprises two main subsystems: a transmit elastic store (TxEsto) subsystem at a transmitter and a receive elastic store (RxEsto) subsystem at a receiver. In one direction, the TxEsto generates a stuffing request, and provides underflow and overflow status of the data received from a channelizer to a framer for further processing. After detailed parallel processing, this data is sent over the air interface in the ISM band frequencies to the receiver. At the receiver, the RxEsto subsystem receives data from a deframer. For synchronization between transmitter and receiver clocks, the RxEsto subsystem clocks out the data, which is stripped off the data overhead bits, at the same rate as it was sent before encapsulation at the transmitter.

- One embodiment of the present invention is a synchronous elastic store system, comprising a shift register having a plurality of data bits, the shift register receiving a stream of digital input data and a master clock input signal which is independent of the digital input data; and an arbiter that arbitrates between a read request and a write request to the shift register, the arbiter having the master clock as an input signal and providing a control signal to the shift register.

- Another embodiment of the present invention is a synchronous digital elastic store system, comprising a shift register receiving a stream of digital input data and a master clock input signal, said master clock signal being independent of the digital input data; an arbiter that arbitrates between a read request and a write request, the arbiter providing a control signal to the shift register and generating at least one counter control signal; an up/down counter receiving the counter control signal from the arbiter and generating selector control signals; and a selector circuit receiving data from the shift register and receiving selector control signals from the up/down counter, said selector circuit selecting one of the shift register bits to be read from the elastic store.

- Yet another embodiment of the invention is a method of storing a stream of digital data in a synchronous elastic store having a shift register, the method comprising the steps of receiving a stream of digital data and a master clock signal at the shift register; synchronously arbitrating between a read request and write request to generate an arbitration control signal; and shifting the digital data into the shift register in response to the arbitration control signal and the master clock signal.

- Yet another embodiment of the invention is a synchronous elastic store system, comprising a channelizer; a synchronous elastic store having a read/write arbiter, the synchronous elastic store receivably connected to the channelizer; a framer receivably connected to the synchronous elastic store; and a wireless transmitter circuit receivably connected to the framer.

- Yet another embodiment of the invention is a synchronous elastic store system, comprising a wireless receiver circuit; a deframer receivably connected to the wireless receiver circuit; a synchronous elastic store having a read/write arbiter, the synchronous elastic store Is receivably connected to the deframer; a dechannelizer receivably connected to the synchronous elastic store.

- The above and other aspects, features and advantages of the present invention will be better understood by referring to the following detailed description of the preferred embodiment, which should be read in conjunction with the accompanying drawings, in which:

- FIG. 1 is a functional block diagram depicting the location of the elastic store system in a synchronous wireless communication system.

- FIG. 2 is a block diagram of a data frame format using a stuff bit for the elastic store system shown in FIG. 1.

- FIG. 3 is a block diagram of a structure for a shift register that is used within the elastic store system shown in FIG. 1.

- FIG. 4 is a functional block diagram depicting one embodiment of the elastic store system shown in FIG. 1.

- FIG. 5 is a functional block diagram of the receiver dejitter circuit used in the elastic store system shown in FIG. 4.

- FIG. 6 is a state machine diagram illustrating the process flow for the elastic store system shown in FIG. 1.

- FIG. 7 is a flowchart of the Reset process shown in FIG. 6.

- FIG. 8 is a flowchart of the Write request anti-metastable sampling process shown in FIG. 6.

- FIG. 9 is a flowchart of the Write request detection process shown in FIG. 6.

- FIG. 10 is a flowchart of the Read request anti-metastable sampling process shown in FIG. 6.

- FIG. 11 is a flowchart of the Read request detection process shown in FIG. 6.

- FIG. 12 is a flowchart of the Read/Write Semaphore process (Sampled Arbiter) shown in FIG. 6.

- FIGS. 13 a and 13 b are a flowchart of the Buffer update process shown in FIG. 6.

- FIG. 14 is a flowchart of the receiver dejitter process shown in FIG. 6.

- FIG. 15 is a block diagram showing exemplary dejitter circuit interconnections for a T3/E3 embodiment of the communication system receiver shown in FIG. 1.

- FIG. 16 is a block diagram showing exemplary dejitter circuit interconnections for a T1/E1 embodiment of the communication system receiver shown in FIG. 1.

- FIG. 17 is a functional block diagram of the arbitration control circuit used in the elastic store system shown in FIG. 4.

- The present invention maintains synchronization between the transmitter and receiver clocks, end-to-end signaling and coding, and overhead bits need to encapsulate data frames sent over wireless media. The elastic store system comprises two main subsystems, namely, a transmit elastic store (TxEsto) subsystem and a receive elastic store (RxEsto) subsystem. The TxEsto subsystem receives parallel data from an existing channelizer, generates a stuffing request, and provides underflow and overflow status to a framer. The RxEsto subsystem receives parallel data from a deframer, strips off the data overhead bits and clocks out data at the same rate as it was sent before encapsulation at the transmitter.

- A detailed description of the elastic store system is provided below. As one embodiment of the present invention, it is not intended to limit the enumerated claims, but serves as a particular example thereof.

- FIG. 1 is a block diagram depicting the location of the

elastic store system 100 in a wireless communication system 98. Theelastic store system 100 supports full-duplex synchronous voice and data communications. - In this embodiment, the

system 100 comprises a Transmit Elastic Store (TxEsto)subsystem 120 and a Receive Elastic Store (RxEsto)subsystem 300. TheTxEsto subsystem 120, comprises a shift register that provides a means of buffering data that may be written into its input at a slightly different rate that it is read from its output. In one embodiment, the clock frequency used in writing data to theTxEsto 120 is 20 MHz. TheTxEsto subsystem 120 communicates with achannelizer 110 and a framer andsignaling controller 130 within atransmitter 105. Thetransmitter 105 consists of theTxEsto subsystem 120, thechannelizer 110, the framer andsignaling controller 130 and other functional elements. The channelizer acts as a demultiplexer or a line driver depending on the inputted data (e.g., demultiplexes the incoming data when it is of type T3 to 28 T1 channels). Various input data types are accommodated by the communications system, some of which are not multiplexed. As noted above, the input data signals may virtually be any standardized signal such as, for example, DSO/E0, T1/E1, T2/E2, T3/E3, Ethernet (LAN/WAN), intranet, or Internet signals. For one preferred embodiment, it is assumed that the input data signals are either multiple T1/E1 channels or a single T3/E3 channel. Thetransmitter 105 is characterized by a parallel structure for processing data extracted synchronously at substantially the same rate of a T1 (E1) channel. For formats having multiple embedded channels, e.g., T3/T1, theelastic store system 100 provides an elastic store for each embedded channel. - The framer and

signaling controller 130 provides a frame structure to the data received from theTxEsto 120. After further processing, the resulting data is sent over an air-link 150 by use of a wireless transmitter circuit a and a wireless receiver circuit (not shown). In one embodiment, the air-link 150 corresponds to the ISM bands. TheRxEsto subsystem 300 receives data from adeframer 140 which is in addition to other functional elements, a subsystem within areceiver 160. The deframer 140 strips the extra bits from the data stream and writes the resulting data to theRxEsto 300 at a certain clock frequency f1. In one embodiment the clock frequency f1 is 20 MHz. In other embodiments, the frequency f, may be selected from a range of about 10 KHz to 1 GHz. TheRxEsto subsystem 300 buffers the data received from thedeframer 140 and reads it out at a clock frequency f2, which in one embodiment is a multiple of frequency f1, e.g., 10 MHz, but in another embodiment may be at same as frequency f1. The buffering of the data is done to avoid underflow and overflow states of the RxEsto. - A

Rx Dechannelizer 170 receives output signals from the RxElastic Store subsystem 300. For example, when T3/E3 output is desired, theDechannelizer 170 constructs T3/E3 data from N receive data streams. TheRx Dechannelizer 170 receives N data channels from theRx Elastic Store 300 and constructs T3/E3 data from the N channels containing Rx packet data. The inputted data (multiple T1 channels/E1 channels) to theRx Dechannelizer 170 can either be sent out as multiple T1/E1 channels or multiplexed into a single T3/E3 channel. - Referring now to FIG. 2, a

data framing technique 200 using a stuff bit for theelastic store system 100 is described. One of the main functions of theTxEsto 120 includes a stuffing request to the framer andsignaling controller 130 described in FIG. 1. Bit stuffing allows reading and writing of data without underflow or overflow of theelastic store system 100. The bit stuffing technique requires a pointer which indicates the current position in the buffer. The pointer is incremented when the elastic store is filling (write) and is decremented when the elastic store is emptying (read). Pointer status may indicate underflow, overflow, near underflow and near overflow. The near underflow status and the near overflow status are utilized by the elastic store subsystem to prevent occurrence of underflow or overflow conditions. Data is typically written into the elastic store at its lowest rank ordered position and shifted toward the highest rank ordered position. Data is read from the position indicated by the pointer. To illustrate bit stuffing, consider a typical synchronous communications link where data is encapsulated with overhead bits before transmission. At the receiver, the data overhead bits are stripped off and the data is clocked out at the same rate as it was sent before encapsulation at the transmitter. - Because of the relative drift of the transmitter and receiver clocks, a dynamic adjustment of the link data transfer rate is necessary to avoid eventual buffer underflow or overflow. This is done by adding more overhead bits including a preamble and a postamble to the frame encapsulation An example of a preamble is a two bit Barker Code, and examples of postamble bits are signaling, stuffing, and justify bits. In one embodiment, the postamble comprises the

stuffing bit 202 and multiple justification bits. The stuffingbit 202 dynamically changes from a real data bit 202′ to astuff bit 202″ on a frame by frame basis (see FIG. 2). Whether the stuffing bit is a real data bit or not is indicated by the justification bits. There are multiple justification bits to allow enough Hamming distance in coding the meaning of the stuffing bit. Thetransmitter 105 normally sends real data in the stuffing bit position and sets the corresponding justification code. When itselastic buffer 120 is near empty, it sends no data in the stuff position and sets the corresponding justification code. Thereceiver 160 decodes the justification bits, putting the stuffing bit into itselastic buffer 300 when the justification bits indicate the stuff bit is data, and throws away the bit and suppresses the write clock to theelastic store 300 when the justification bits indicate the stuff bit is not data. - Now referring to FIG. 3, a shift

register buffer structure 320 used within the elastic store system is described. Theshift register 320 consists of n-bits which corresponds to the number of Data bits in the shift register, i.e., the length of the shift register. In one embodiment, n=12 bits for theTx Elastic Store 120, and n=14 bits for theRx Elastic Store 300. In other embodiments, the length of the shift register may vary depending on the type and format of the input data. Theshift register 320 also includes apointer 222 which is decremented for writes and incremented for reads, aHiHi_LIM 224 which indicates the underflow status (this limit is equal to eleven for the Tx Elastic Store and is equal to thirteen for the Rx Elastic Store), aLoLo_LIM 226 that indicates the overflow status (this limit is equal to zero for both the Tx and Rx Elastic Stores), and a Hi_LIM 228 (this limit is equal to nine for the Tx Elastic Store and eleven for the Rx Elastic Store). TheHi_LIM 228 indicates for theTx Elastic Store 120 that a stuff request should be generated to theframer 130 and indicates for the Rx Elastic Store 300 a read slower control to the Dechannelizer 170 (FIG. 1). In one embodiment, the Dechannelizer is a digital multiplexer whereby the 28 T1 channels, as an example, can be multiplexed back to one T3 channel. In addition to these parameters, a Lo_LIM parameter 230 (this limit is equal to two for the Rx Elastic Store and is not needed for the Tx Elastic Store) is used to indicate a read faster control in the case of the receive elastic store. Theshift register pointer 222 is initialized first to a given value, then, depending if it is a write or read operation, theshift register pointer 222 is shifted to the right or left respectively. Furthermore, the data is right shifted for a write operation only from the mostsignificant bit 232 to the leastsignificant bit 234. In another embodiment, the four limits described above may be dynamically set by a micro-controller (not shown), such as a Hitachi H8/3048, that is part of the communication system 98 (FIG. 1). - Now referring to FIG. 4, a functional block diagram depicting one embodiment of the

elastic store system 100 is shown. Theelastic store system 100 includes the TxElastic Store subsystem 120 and the RxElastic Store subsystem 300. - One embodiment of the Tx

Elastic Store subsystem 120 includes anelastic store module 321 having a shift register buffer that provides a way to buffer data which may be written into its input at a slightly lower rate than it is read from its output. Functions include generation of a stuff request, underflow status and overflow status. All inputs and outputs are sampled by a high speed clock, except RESET which is asynchronous. A Very high speed integrated circuit Hardware Description Language (VHDL) code listing for the major modules of the TxElastic Store subsystem 120 is provided in Appendix A. - One embodiment of the RX

Elastic Store subsystem 300 includes theelastic store module 321 and adejitter circuit 390. The RXElastic Store subsystem 300 has similar characteristics to theTx Elastic Store 120 with slight variations. Functions for theRx Elastic Store 300 include generation of a “faster” control signal, a “slower” control signal, underflow status and overflow status. Thedejitter circuit logic 390 uses the faster and slower controls to produce a read request signal for reading out the contents of the elastic store. All inputs and outputs are sampled by a high speed clock, except RESET which is asynchronous. A VHDL code listing for the major modules of the RxElastic Store subsystem 300 is provided in Appendix B. - Input and output signals for the

elastic store module 321 are summarized in Table 1 below:TABLE 1 Input Signals Output Signals RESET Read Data Preset Stuff Request (I/O) Clock Underflow Status (I/O) Write Data (from Channelizer if TxEsto) Overflow Status (I/O) Write Request (From Channelizer if TxEsto) Read Request (from Framer if TxEsto) - Signals internal to the

elastic store module 321 are listed in Table 2 below:TABLE 2 Signal Name Significance WR_RQ1 Write Request 1 sampling register WR_RQ2 Write Request 2 sampling register WR_RQ3 Write Request 3 sampling register WR_RQFLAG Write Request Flag WR_FLAG Write Flag RD_RQ1 Read Request 1 sampling register RD_RQ2 Read Request 2 sampling register RD_RQ3 Read Request 3 sampling register RD_RQFLAG Read Request Flag RD_FLAG Read Flag LNLT_FLAG Initialize Flag LOLO_LIM LoLo limit represents the Lowest low value for the Shift register pointer. Corresponds to the lowest significant bit within the shift register and indicates the Overflow condition LO_LIM Shift register pointer low limit. For Rx Elastic Store, this corresponds to read faster control. HI_LIM Shift register pointer high limit. This corresponds for Tx Elastic Store to Stuff limit and for Rx Elastic Store to read slower control. HIHI_LIM HiHi limit represents the High high value for the Shift register pointer. Corresponds to the most significant bit within the shift register and indicates the Underflow condition. - The

elastic store module 321 comprises anarbitration control block 310, ashift register block 320, aselector block 340, an Up/Down counter block 330, aregister 350, anear overflow comparator 360, anear underflow comparator 370, anunderflow comparator 380, anoverflow comparator 385. In the RxElastic Store subsystem 300, adejitter circuit 390 connects to theelastic store module 321. - Proper arbitration requires some sort of delay element or sampling clock with a shorter period than the read/write data. The arbitration latency may be three or more delays in order to detect read/write clock edges rather than levels and to eliminate metastability. The arbitration in one embodiment is done on the data bit interval. While other implementations are possible ( e.g., at the frame rate), the required resolution of the arbiter is still the read/write data interval. More significantly, arbitration on a bit by bit basis provides more responsive fast/slow controls for the dejitter circuit from the receive elastic store. In one embodiment, the dejittered output may be applied to a phase lock loop (PLL) which generates a smooth symmetrical read request multiple of the dejitter read request for multiplexing the read data from multiple Elastic Stores into a single high speed data stream which is synchronous with the transmit source. Thus, data rate arbitration eases the PLL's voltage controlled oscillator (VCO) stability requirement by providing faster update to the PLL.

- The

arbitration control block 310 has three inputs, namely aWrite_Request signal 302 from the channelizer 110 (FIG. 1) in the case of the transmitelastic store 120 or from theDeframer 140 in the case of the receiveelastic store 300; aRead_Request signal 303 from theframer 130 in the case of transmitelastic store 120 or from thedechannelizer 170 in case of the receiveelastic store 300; and a Master Clock (MClk) 301 (also referred to as a sampling clock). However, in the case of a T3/E3 communications system, the receiveelastic store 321 obtains the Read_Request signal from a phase lock loop (PLL) 1550 (FIG. 15) connected to thedejitter circuit 390, or directly from thedejitter circuit 390 in the case of a T1/E1 system. The arbitration control block 310 controls the metastable condition by monitoring the read and write. A metastable condition is an undefined state (neither one nor zero) which arises as a result of sampling at the instant that the data is changing. Thearbitration control block 310 utilizes the three Write Request X sampling registers and the three Read Request X sampling registers to control the metastable condition. Thearbitration control block 310 generates several output signals, namely a Write Activatecontrol signal 304, which is fed to the n-bit shift register 320, a Read Activate control signal 305, which is fed to theregister 350, a counter enablesignal 306 and an up/downcontrol pointer signal 307, both of which are fed to the up/downcounter block 330. - The n-bit shift register 320 (detailed in FIG. 3) has three inputs, namely a

Write_Data signal 308, the Write Activatecontrol 304 and a Master Clock 301 (not shown as an input). TheWrite_Data signal 308 is received from thechannelizer 110 in the case of the transmitelastic store 120; or from thedeframer 140 in the case of the receiveelastic store 300. In addition, if theWrite_Request signal 302 has more priority than theRead_Request signal 303, then at the activation of the Write Activatecontrol 304 in conjunction with the Master clock, the data is right shifted (most significant bit to least significant bit) and the pointer 222 (FIG. 3) is moved to the right. However, if theRead_Request 303 is prior to theWrite_Request 302, only thepointer 222 is moved to the left toward the most significant bit. - The N to 1