RU2418373C2 - Receiver for wireless communication network with expanded range - Google Patents

Receiver for wireless communication network with expanded range Download PDFInfo

- Publication number

- RU2418373C2 RU2418373C2 RU2007148003/09A RU2007148003A RU2418373C2 RU 2418373 C2 RU2418373 C2 RU 2418373C2 RU 2007148003/09 A RU2007148003/09 A RU 2007148003/09A RU 2007148003 A RU2007148003 A RU 2007148003A RU 2418373 C2 RU2418373 C2 RU 2418373C2

- Authority

- RU

- Russia

- Prior art keywords

- results

- correlation

- character

- delay

- sequence

- Prior art date

Links

Images

Landscapes

- Synchronisation In Digital Transmission Systems (AREA)

Abstract

Description

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕFIELD OF THE INVENTION

Настоящее раскрытие изобретения в целом относится к связи, а конкретнее к приемнику для беспроводной связи.The present disclosure generally relates to communications, and more particularly to a receiver for wireless communications.

УРОВЕНЬ ТЕХНИКИBACKGROUND

Сети беспроводной связи широко используются для предоставления различных услуг связи, например данных, речи, видео и т.д. Эти сети включают в себя беспроводные региональные сети радиосвязи (WWAN), которые обеспечивают зону радиосвязи для больших географических областей (например, городов), беспроводные локальные вычислительные сети (WLAN), которые обеспечивают зону радиосвязи для географических областей среднего размера (например, зданий и кампусов), и персональные беспроводные сети (WPAN), которые обеспечивают зону радиосвязи для небольших географических областей (например, домов). Беспроводная сеть обычно включает в себя одну или несколько точек доступа (или базовых станций), которые поддерживают связь для одного или нескольких терминалов пользователей (или беспроводных устройств).Wireless networks are widely used to provide various communication services, such as data, voice, video, etc. These networks include wireless regional radio communications networks (WWANs) that provide a radio communications zone for large geographic areas (such as cities), wireless local area networks (WLANs) that provide a radio communications networks for medium sized geographical areas (such as buildings and campuses ), and Personal Wireless Networks (WPANs), which provide a radio communication area for small geographic areas (such as homes). A wireless network typically includes one or more access points (or base stations) that support communication for one or more user terminals (or wireless devices).

IEEE 802.11 является семейством стандартов, разработанных Институтом инженеров по электротехнике и электронике (IEEE) для WLAN. Эти стандарты описывают беспроводной интерфейс между точкой доступа и терминалом пользователя или между двумя терминалами пользователя. Стандарт IEEE 802.11 редакции 1999 (или просто «802.11»), который озаглавлен «Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications» (Часть 11: Спецификации протокола управления доступом к среде передачи (MAC) и протокола физического уровня (PHY) для беспроводной LAN), поддерживает скорости передачи данных в 1 и 2 мегабит в секунду (Мбит/с) в частотном диапазоне 2,4 гигагерц (ГГц), используя либо расширение спектра путем скачкообразной перестройки частоты (FHSS), либо расширение спектра методом прямой последовательности (DSSS). Стандарт IEEE 802.11a-1999 (или просто «802.11a») является дополнением к 802.11, использует мультиплексирование с ортогональным частотным разделением каналов (OFDM) вместо FHSS или DSSS и поддерживает скорости передачи данных до 54 Мбит/с в частотном диапазоне 5 ГГц. Стандарт IEEE 802.11b-1999 (или просто «802.11b») является другим дополнением к 802.11 и использует DSSS для поддержки скоростей передачи данных до 11 Мбит/с. Стандарт IEEE 802.11g-2003 (или просто «802.11g») является еще одним дополнением к 802.11, использует DSSS и OFDM и поддерживает скорости передачи данных до 54 Мбит/с в полосе 2,4 ГГц. Эти разные стандарты общеизвестны в данной области техники и являются общедоступными.IEEE 802.11 is a family of standards developed by the Institute of Electrical and Electronics Engineers (IEEE) for WLAN. These standards describe a wireless interface between an access point and a user terminal or between two user terminals. 1999 IEEE 802.11 Standard (or simply “802.11”), which is entitled “Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications” (Part 11: Media Access Control Protocol (MAC) and physical layer protocol (PHY) for wireless LAN), supports data transfer rates of 1 and 2 megabits per second (Mbps) in the frequency range of 2.4 gigahertz (GHz), using either spectrum expansion by frequency hopping (FHSS), or direct spectrum spreading (DSSS). The IEEE 802.11a-1999 standard (or simply “802.11a”) is in addition to 802.11, uses Orthogonal Frequency Division Multiplexing (OFDM) instead of FHSS or DSSS, and supports data rates up to 54 Mbps in the 5 GHz frequency band. The IEEE 802.11b-1999 standard (or simply “802.11b”) is another addition to 802.11 and uses DSSS to support data rates up to 11 Mbps. The IEEE 802.11g-2003 standard (or simply “802.11g”) is another addition to 802.11, uses DSSS and OFDM, and supports data rates of up to 54 Mbps in the 2.4 GHz band. These different standards are well known in the art and are publicly available.

Наименьшая скорость передачи данных, поддерживаемая 802.11, 802.11a, 802.11b и 802.11g, равна 1 Мбит/с. Для 802.11b и 802.11g (или просто «802.11b/g») для отправки передачи (передаваемых данных) на наименьшей скорости передачи (данных) в 1 Мбит/с используются особая схема DSSS и особая схема модуляции. DSSS и схема модуляции для 1 Мбит/с требуют определенного минимального отношения уровня сигнала к совокупному уровню взаимных помех и шумов (SNR) для надежного приема передачи (передаваемых данных). Диапазон передачи (передаваемых данных) затем определяется географической областью, в пределах которой приемная станция может достигать требуемого или лучшего SNR. В некоторых случаях желательно отправлять передачи (передаваемые данные) с диапазоном, который больше диапазона для наименьшей скорости передачи данных, поддерживаемой 802.11b/g.The lowest bit rate supported by 802.11, 802.11a, 802.11b and 802.11g is 1 Mbps. For 802.11b and 802.11g (or simply “802.11b / g”), a special DSSS scheme and a special modulation scheme are used to send transmission (transmitted data) at the lowest transmission speed (data) of 1 Mbps. DSSS and a modulation scheme for 1 Mbit / s require a certain minimum ratio of signal level to the total level of mutual interference and noise (SNR) for reliable reception of the transmission (transmitted data). The transmission range (transmitted data) is then determined by the geographical area within which the receiving station can achieve the desired or best SNR. In some cases, it is desirable to send transmissions (transmitted data) with a range that is larger than the range for the lowest data rate supported by 802.11b / g.

Следовательно, в данной области техники имеется необходимость в сети беспроводной связи и станции, допускающих функционирование с расширенным диапазоном покрытия.Therefore, in the art there is a need for a wireless communications network and stations capable of operating with an extended coverage range.

СУЩНОСТЬ ИЗОБРЕТЕНИЯSUMMARY OF THE INVENTION

В этом документе описываются методики для обнаружения и демодуляции сигнала/передачи (передаваемых данных) в плохих канальных условиях (например, низкое SNR). В одном аспекте обнаружение сигнала выполняют в несколько этапов, используя разные типы обработки сигнала для достижения хорошей эффективности обнаружения. В варианте осуществления обнаружение сигналов выполняют с использованием корреляции во временной области для первого этапа, обработки в частотной области для второго этапа и обработки во временной области для третьего этапа. Обнаружение сигнала для каждого этапа можно дополнительно выполнять на основе адаптивной (самонастраивающейся) пороговой величины, которую выводят на основании принятой энергии для интервала (окна) символов, для того чтобы эффективность обнаружения была менее чувствительной к уровню принятого сигнала. Наличие сигнала может быть объявлено на основании результатов всех трех этапов.This document describes techniques for detecting and demodulating a signal / transmission (transmitted data) in poor channel conditions (e.g., low SNR). In one aspect, signal detection is performed in several steps using different types of signal processing to achieve good detection efficiency. In an embodiment, signal detection is performed using time domain correlation for the first stage, frequency domain processing for the second stage, and time domain processing for the third stage. Signal detection for each stage can be additionally performed based on an adaptive (self-adjusting) threshold value that is derived based on the received energy for the symbol interval (window) so that the detection efficiency is less sensitive to the level of the received signal. The presence of a signal can be announced based on the results of all three stages.

В аспекте первого этапа входные выборки на приемной станции могут быть кодированы с сужением спектра с помощью кодовой последовательности для формирования суженных символов. Затем формируют произведения суженных символов по меньшей мере для двух задержек, например 1-символьной и 2-символьной задержек. Выполняют корреляцию между произведениями для каждой задержки и известными значениями для той задержки. Затем объединяют результаты корреляции для всех задержек, например, некогерентно или когерентно для множества предполагаемых фаз. Наличие сигнала и синхронизация сигнала могут быть определены на основании объединенных результатов корреляции.In an aspect of the first step, the input samples at the receiving station may be narrowed down using a code sequence for generating narrowed symbols. Then form the product of narrowed characters for at least two delays, for example 1-character and 2-character delays. A correlation is performed between the products for each delay and the known values for that delay. Then, the correlation results for all delays are combined, for example, incoherently or coherently for a plurality of expected phases. Signal presence and signal timing can be determined based on the combined correlation results.

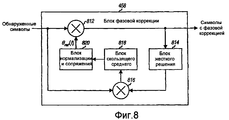

В другом аспекте демодуляцию выполняют таким образом, чтобы достичь хорошей эффективности при плохих канальных условиях. В варианте осуществления синхронизацию входных выборок регулируют (например, с помощью многофазного фильтра) для получения отрегулированных по времени выборок. Уход частоты оценивают и удаляют из отрегулированных по времени выборок для получения выборок с частотной коррекцией, которые обрабатывают с помощью оценки канала (например, используя многоотводный (рейк) приемник) для получения обнаруженных символов. Фазы обнаруженных символов корректируют для получения символов с фазовой коррекцией. Затем над символами с фазовой коррекцией выполняют демодуляцию для получения демодулированных символов, которые обратно перемежают и декодируют для получения декодированных данных.In another aspect, demodulation is performed in such a way as to achieve good efficiency under poor channel conditions. In an embodiment, the timing of the input samples is adjusted (for example, using a multiphase filter) to obtain time-adjusted samples. Frequency drift is estimated and removed from time-adjusted samples to obtain frequency-corrected samples, which are processed using channel estimation (for example, using a multi-tap (rake) receiver) to obtain detected characters. The phases of the detected symbols are corrected to obtain phase corrected symbols. Then, phase-corrected symbols are demodulated to obtain demodulated symbols, which are interleaved and decoded to obtain decoded data.

Обработка сигнала для каждого этапа обнаружения и для демодуляции подробно описывается ниже. Различные аспекты и варианты осуществления изобретения также описываются ниже.Signal processing for each detection step and for demodulation is described in detail below. Various aspects and embodiments of the invention are also described below.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙBRIEF DESCRIPTION OF THE DRAWINGS

Признаки и сущность настоящего изобретения станут более очевидными из изложенного ниже подробного описания, рассматриваемого совместно с чертежами, на которых одинаковые номера позиций определяют соответственно по всему документу.The features and essence of the present invention will become more apparent from the following detailed description, taken in conjunction with the drawings, in which the same reference numbers are determined respectively throughout the document.

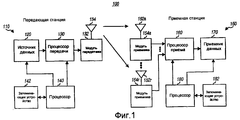

Фиг.1 показывает передающую станцию и приемную станцию.1 shows a transmitting station and a receiving station.

Фиг.2 показывает процессор передачи в передающей станции.2 shows a transmission processor in a transmitting station.

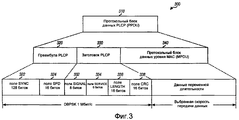

Фиг.3 показывает структуру PPDU, используемую 802.11b/g.Figure 3 shows the PPDU structure used by 802.11b / g.

Фиг.4 показывает процессор приема в приемной станции.4 shows a receive processor at a receiving station.

Фиг.5 показывает первый этап обнаружения и блок вхождения в синхронизм по времени.Fig. 5 shows a first detection step and a time synchronization entry unit.

Фиг.6 показывает второй этап обнаружения и блок вхождения в синхронизм по частоте.6 shows a second detection step and a frequency synchronization acquisition unit.

Фиг.7 показывает третий этап обнаружения и блок оценки канала.7 shows a third detection step and a channel estimator.

Фиг.8 показывает блок фазовой коррекции.Fig. 8 shows a phase correction block.

Фиг.9 показывает процесс для выполнения обнаружения сигнала для первого этапа.9 shows a process for performing signal detection for a first step.

Фиг.10 показывает процесс для выполнения обнаружения сигнала с несколькими этапами.10 shows a process for performing signal detection in several steps.

Фиг.11 показывает процесс для приема передачи (передаваемых данных).11 shows a process for receiving transmission (transmitted data).

ПОДРОБНОЕ ОПИСАНИЕDETAILED DESCRIPTION

Слово «типовой» используется в данном документе, чтобы обозначать «служащий в качестве примера, отдельного случая или иллюстрации». Любой вариант осуществления или образец, описанный в данном документе как «типовой», не обязательно должен быть истолкован как предпочтительный или выгодный по сравнению с другими вариантами осуществления или образцами.The word “typical” is used throughout this document to mean “serving as an example, individual case, or illustration”. Any embodiment or sample described herein as “typical” is not necessarily to be construed as preferred or advantageous over other embodiments or samples.

Фиг.1 показывает блок-схему передающей станции 110 и приемной станции 150 в беспроводной сети 100. Передающая станция 110 оборудована одной антенной и может быть точкой доступа или терминалом пользователя. Приемная станция 150 оборудована несколькими (например, R=2) антеннами и также может быть точкой доступа или терминалом пользователя. Вообще, каждая станция может быть оборудована любым количеством антенн, которые могут использоваться для передачи и приема данных. Точкой доступа обычно является стационарная станция, которая обменивается информацией с терминалами пользователя и также может называться базовой станцией, базовой приемопередающей системой (BTS) или какой-либо другой терминологией. Терминал пользователя может быть стационарным или мобильным и также может называться мобильной станцией, беспроводным устройством, абонентским оборудованием (UE) или какой-либо другой терминологией. 1 shows a block diagram of a

На передающей станции 110 процессор 130 передачи принимает данные трафика от источника 120 данных, обрабатывает данные трафика в соответствии со скоростью передачи данных, выбранной для передачи, и предоставляет выходные элементарные сигналы. Ниже описывается обработка процессором 130 передачи. Модуль 132 передатчика (TMTR) обрабатывает (например, преобразует в аналоговую форму, усиливает, фильтрует и преобразует с повышением частоты) выходные элементарные сигналы и формирует модулированный сигнал, который передается через антенну 134.At transmitting

На приемной станции 150 R антенн 152a-152r принимают переданный сигнал, и каждая антенна 152 предоставляет принятый сигнал соответствующему модулю 154 приемника (RCVR). Антенна также может называться «разнесением», и R приемных антенн обеспечивают кратность R разнесения. Каждый модуль 154 приемника обрабатывает свой принятый сигнал и предоставляет поток входных выборок процессору 160 приема. Процессор 160 приема обрабатывает входные выборки от всех R модулей 154a-154r приемника способом, дополнительным к обработке, выполненной процессором 130 передачи, и предоставляет декодированные данные приемнику 170 данных. Декодированные данные являются оценкой данных трафика, отправленных передающей станцией 110.At a receiving station 150 R,

Процессоры 140 и 180 управляют работой блоков обработки на передающей станции 110 и приемной станции 150 соответственно. Запоминающие устройства 142 и 182 хранят данные и/или программные коды, используемые процессорами 140 и 180 соответственно.

Станции 110 и 150 могут поддерживать 802.11b и/или 802.11g. 802.11g обратно совместим с 802.11b и поддерживает все режимы работы, определенные 802.11b. Станции 110 и 150 могут дополнительно поддерживать режим расширения диапазона, который поддерживает по меньшей мере одну скорость передачи данных, которая меньше наименьшей скорости передачи данных в 802.11b/g. Меньшая скорость (скорости) передачи данных может использоваться для расширения диапазона покрытия, который выгоден для некоторых применений, например портативных раций.

Таблица 1 перечисляет две наименьшие скорости передачи данных, поддерживаемые 802.11b и 802.11g и обработку для каждой скорости передачи данных. Таблица 1 также перечисляет три скорости передачи данных, поддерживаемые режимом расширения диапазона, и обработку для каждой скорости передачи данных в соответствии с вариантом осуществления. В Таблице 1 DBPSK обозначает дифференциальную двухпозиционную фазовую манипуляцию, а DQPSK обозначает дифференциальную квадратурную фазовую манипуляцию.Table 1 lists the two lowest data rates supported by 802.11b and 802.11g and the processing for each data rate. Table 1 also lists the three data rates supported by the range extension mode and the processing for each data rate in accordance with an embodiment. In Table 1, DBPSK stands for differential on-off phase shift keying, and DQPSK stands for differential quadrature phase shift keying.

Для ясности в последующем описании термин «бит» относится к количеству до модуляции (или преобразованию символов) на передающей станции, термин «символ» относится к количеству после преобразования символов и термин «элементарный сигнал» относится к количеству после спектрального кодирования с расширением спектра. Термин «выборка» относится к количеству до спектрального кодирования с сужением спектра на приемной станции.For clarity in the following description, the term “bit” refers to the number before modulation (or symbol conversion) at the transmitting station, the term “symbol” refers to the number after symbol conversion, and the term “chip” refers to the number after spread spectrum spectral coding. The term “sampling” refers to the amount before spectral coding with a narrowing of the spectrum at the receiving station.

Фиг.2 показывает вариант осуществления процессора 130 передачи на передающей станции 110. Процессор 130 передачи включает в себя генератор 210 пилот-сигнала, процессор 240 передачи DSSS для 802.11b/g, процессор 250 передачи DSSS для режима расширения диапазона и мультиплексор (Mux) 270. FIG. 2 shows an embodiment of a transmit

Генератор 210 пилот-сигнала формирует пилот-сигнал (который также называется преамбулой или опорным сигналом) как для 802.11b/g, так и для режима расширения диапазона. В генераторе 210 пилот-сигнала преобразователь 214 символов принимает биты пилот-сигнала, преобразует эти биты в символы модуляции на основе BPSK и предоставляет символы пилот-сигнала устройству 216 расширения спектра. Для целей данного документа символом пилот-сигнала является символ модуляции для пилот-сигнала, символом данных является символ модуляции для данных трафика, символ модуляции является комплексной величиной для точки в сигнальном созвездии для схемы модуляции (например, для M-PSK или M-QAM), и символ является любой комплексной величиной. Устройство 216 расширения спектра спектрально расширяет символы пилот-сигнала и предоставляет выходные элементарные сигналы. В устройстве 216 расширения спектра генератор 222 кода псевдослучайного числа (PN) формирует кодовую последовательность PN. В некоторых вариантах осуществления это может называться последовательностью Баркера. Последовательность Баркера длиной в 11 элементарных сигналов обладает скоростью передачи в 11 миллионов элементарных сигналов в секунду (Mcps) и состоит из следующей 11-сигнальной последовательности {+1, -1, +1, +1, -1, +1, +1, +1, -1, -1, -1}. Умножитель 224 принимает символы пилот-сигнала на скорости в 1 миллион символов в секунду (Msps) от преобразователя 214 символов и последовательность Баркера от генератора 222 кода PN. Умножитель 224 умножает каждый символ пилот-сигнала на все 11 элементарных сигналов из последовательности Баркера, формирует 11 выходных элементарных сигналов для каждого символа пилот-сигнала и предоставляет последовательность выходных элементарных сигналов для пилот-сигнала. Выходная скорость передачи элементарного сигнала в 11 раз выше скорости передачи символа пилот-сигнала, или 11 Mcps. Каждый выходной элементарный сигнал является комплексной величиной, которую необходимо отправить в один период Tc элементарного сигнала, который равен приблизительно 90,9 наносекунд (нс) для 802.11b/g.A

Процессор 240 передачи DSSS выполняет дифференциальную модуляцию и спектральное кодирование с расширением спектра для 802.11b/g. В процессоре 240 дифференциальный кодер 242 принимает информационные биты для данных трафика, выполняет дифференциальное кодирование информационных битов для DBPSK или DQPSK и предоставляет дифференциально-кодированные биты. Для DBPSK информационный бит «0» приводит к изменению фазы в 0°, а информационный бит «1» приводит к изменению фазы в 180°. Для DQPSK пара информационных битов «00» приводит к изменению фазы в 0°, пара информационных битов «01» приводит к изменению фазы в +90°, пара информационных битов «11» приводит к изменению фазы в +180° и пара информационных битов «10» приводит к изменению фазы в +270°. В некоторых вариантах осуществления преобразователь 244 символов преобразует дифференциально-кодированные биты в символы модуляции на основе BPSK для скорости передачи данных в 1 Мбит/с и на основе QPSK для скорости передачи данных в 2 Мбит/с. Тем не менее, могут использоваться другие схемы модуляции для скоростей передачи. Преобразователь 244 символов предоставляет символы модуляции BPSK на скорости в 1 Msps для скорости передачи данных 1 Мбит/с и предоставляет символы модуляции QPSK на скорости 1 Msps для скорости передачи данных 2 Мбит/с. Устройство 246 расширения спектра спектрально расширяет символы данных из преобразователя 244 символов и предоставляет выходные элементарные сигналы для данных трафика.DSSS transmit

Процессор 250 передачи DSSS выполняет кодирование с прямым исправлением ошибок (FEC), преобразование символов и спектральное кодирование с расширением спектра для режима расширения диапазона. В процессоре 250 кодер 252 FEC принимает информационные биты для данных трафика, кодирует информационные биты в соответствии со схемой кодирования FEC и предоставляет кодовые биты. Кодер 252 FEC может обеспечивать выполнение сверточного кода, турбо-кода, кода разреженного контроля четности (LDPC), блочного кода, какого-либо иного кода или их сочетания. Блок 254 повторения/исключения может либо повторять, либо исключать некоторые или все кодовые биты для получения нужной кодовой скорости. Перемежитель 256 перемежает или переупорядочивает кодовые биты на основе схемы перемежения. Дифференциальный кодер 262 выполняет дифференциальное кодирование перемеженных битов, например для DBPSK или DQPSK, и предоставляет дифференциально-кодированные биты. Преобразователь 264 символов преобразует дифференциально-кодированные биты в символы модуляции на основе схемы модуляции, например BPSK или QPSK. Устройство 266 расширения спектра спектрально расширяет символы данных из преобразователя 264 символов и предоставляет выходные элементарные сигналы для данных трафика. Устройства 246 и 266 расширения спектра могут реализовываться так же, как и устройство 216 расширения спектра, и могут расширять каждый символ данных с помощью 11-сигнальной последовательности Баркера для формирования 11 выходных элементарных сигналов для этого символа данных.The DSSS transmit

Мультиплексор 270 принимает выходные элементарные сигналы от генератора 210 пилот-сигнала и процессоров 240 и 250 передачи DSSS, предоставляет выходные элементарные сигналы для пилот-сигнала в нужное время, предоставляет выходные элементарные сигналы от процессора 240, если выбирается режим 802.11b/g, и предоставляет выходные элементарные сигналы от процессора 250, если выбирается режим расширения диапазона.A

Для IEEE 802.11 данные обрабатываются посредством уровня протокола управления доступом к среде передачи (MAC) в качестве протокольных блоков данных уровня MAC (MPDU). Каждый MPDU обрабатывается протоколом конвергенции физического уровня (PLCP) и помещается в протокольный блок данных PLCP (PPDU). Каждый PPDU обрабатывается физическим уровнем (как показано на фиг.2) и передается через радиоканал.For IEEE 802.11, data is processed through a medium access control protocol (MAC) protocol layer as MAC layer protocol data units (MPDUs). Each MPDU is processed by the Physical Layer Convergence Protocol (PLCP) and placed in the PLCP Protocol Data Unit (PPDU). Each PPDU is processed by a physical layer (as shown in FIG. 2) and transmitted through a radio channel.

Фиг.3 показывает структуру 300 PPDU, используемую 802.11b/g. Для структуры 300 PPDU, PPDU 310 включает в себя преамбулу 320 PLCP, заголовок 330 PLCP и MPDU 340. MPDU 340 служит носителем данных трафика для PPDU 310 и имеет переменную длину. Преамбула 320 PLCP включает в себя поле 322 синхронизации PLCP (SYNC) и поле 324 ограничителя начала кадра (SFD). Поле 322 SYNC служит носителем фиксированной 128-битной последовательности, которая может использоваться приемной станцией для обнаружения сигнала, вхождения в синхронизм и других целей. Биты в 128-битной последовательности обозначаются d 0, d 1,…, d 127 . Поле 324 SFD служит носителем фиксированной 16-битной последовательности, которая указывает начало заголовка PLCP. Заголовок 330 PLCP включает в себя поле 332 SIGNAL, которое указывает скорость передачи данных для MPDU, поле 334 SERVICE, которое устанавливается в «0» для обозначения соответствия IEEE 802.11, поле 336 LENGTH, которое указывает количество времени (в единицах, равных миллисекундам), требуемое для отправки MPDU 340, и поле 338 CRC, которое служит носителем значения CRC, сформированного на основе полей SIGNAL, SERVICE и LENGTH. Преамбула 320 PLCP и заголовок 330 PLCP отправляются на скорости 1 Мбит/с с использованием DBPSK. Преамбула 320 PLCP содержит в целом 144 бита, которые обрабатываются для формирования 144 символов BPSK. Каждый символ BPSK состоит из 11 выходных элементарных сигналов, которые получаются путем кодирования с расширением спектра этого символа BPSK с помощью 11 элементарных сигналов из последовательности Баркера. 144 символа BPSK передаются в 144 периодах символов, при этом каждый период символа имеет длительность в 1 микросекунду (мкс). 3 shows a

Для режима расширения диапазона может использоваться структура 300 PPDU или другая структура PPDU. Структура PPDU для режима расширения диапазона может включать в себя поле SYNC, поле CHANEST, которое служит носителем фиксированной (например 32-битной) последовательности, используемой для оценки канала, одно или несколько полей сигнализации и MPDU.For range extension mode, a

Приемная станция 150 выполняет вхождение в синхронизм для обнаружения PPDU, отправленных передающей станцией 110. Вхождение в синхронизм для режима расширения диапазона более перспективно, чем обычное вхождение в синхронизм для 802.11b/g вследствие следующих отличий:The receiving

1. Низкое SNR/разнесение. Требуемое отношение энергии бита к общему уровню шума (Eb/No) ниже, например для 802.11b/g оно приблизительно 8 децибел (дБ), тогда как требуемое Eb/No для режима расширения диапазона приблизительно равно 3 дБ. Требуемое отношение энергии символа к общему уровню шума на кратность разнесения (Es/No/div) приблизительно равно -6 дБ при наименьшей скорости передачи данных 250 кбит/с. Желательно достигать обнаружения лучше 90% при этой пороговой величине Es/No/div в диспергирующих канальных условиях.1. Low SNR / diversity. The required ratio of bit energy to total noise level (Eb / No) is lower, for example, for 802.11b / g it is approximately 8 decibels (dB), while the required Eb / No for the range extension mode is approximately 3 dB. The required ratio of the symbol energy to the total noise level by the diversity factor (Es / No / div) is approximately -6 dB at the lowest data rate of 250 kbit / s. It is desirable to achieve a detection better than 90% at this threshold value Es / No / div in dispersive channel conditions.

2. Вхождения в синхронизм по частоте. Приемник стандарта 802.11b/g обычно выполняет дифференциальную демодуляцию. Приемник для режима расширения диапазона может выполнять когерентную демодуляцию для повышения эффективности. Для получения хорошей оценки канала, используемой для когерентной демодуляции, приемнику может потребоваться определить отклонение частоты между генераторами на передающей и приемной станциях. Отклонение частоты ±20 промилле (ppm) на приемной станции интерпретируется в отклонение частоты ±232 кГц на частоте 5,8 ГГц, что может ухудшить эффективность.2. Entering synchronism in frequency. An 802.11b / g receiver typically performs differential demodulation. The receiver for the band extension mode may perform coherent demodulation to increase efficiency. To obtain a good estimate of the channel used for coherent demodulation, the receiver may need to determine the frequency deviation between the generators at the transmitting and receiving stations. A frequency deviation of ± 20 ppm at the receiving station is interpreted as a frequency deviation of ± 232 kHz at 5.8 GHz, which may degrade performance.

3. Оценка канала. Мощность шума в оценке канала должна быть гораздо ниже, чем общая мощность шума, чтобы достигать хорошей эффективности для когерентной демодуляции.3. Channel rating. The noise power in the channel estimate should be much lower than the total noise power in order to achieve good efficiency for coherent demodulation.

Фиг.4 показывает вариант осуществления процессора 160 приема на приемной станции 150 на фиг.1. В процессоре 160 приема буфер 402 выборок принимает поток входных выборок от каждого из модулей 154a-154r приемника. Процессор 404 вхождения в синхронизм выполняет вхождение в синхронизм для PPDU. В процессоре 404 первый этап обнаружения и блок 410 вхождения в синхронизм по времени принимает входные выборки из буфера 402, обнаруживает PPDU и определяет синхронизацию каждого обнаруженного PPDU. Второй этап обнаружения и блок 420 вхождения в синхронизм по частоте также обнаруживает PPDU и дополнительно оценивает отклонение частоты во входных выборках. Третий этап обнаружения и блок 430 оценки канала также обнаруживает PPDU и дополнительно оценивает отклик радиоканала между передающей станцией 110 и приемной станцией 150. Блоки 410, 420 и 430 могут выполнять обработку на основе 128-битной последовательности в поле SYNC из преамбулы PPDU, как описано далее. FIG. 4 shows an embodiment of a

Фиг.5 показывает вариант осуществления первого этапа обнаружения и блока 410 вхождения в синхронизм по времени, который выполняет обнаружение сигнала с использованием корреляции во временной области. Блок 410 производит действия над комплекснозначными входными выборками на частоте выборки, которая больше либо равна скорости передачи элементарного сигнала. Для простоты последующее описание предполагает, что входные выборки предоставляются со скоростью передачи элементарного сигнала. В последующем описании «m» является индексом для приемной антенны, «n» является индексом для периода элементарного сигнала, «k» является индексом для элемента разрешения по частоте и «i» является индексом для 128 битов в фиксированной последовательности, отправленной в поле SYNC. Скорость передачи символов равна скорости передачи битов для пилот-сигнала, отправленного в поле SYNC. Когерентная сумма относится к сумме комплексных величин, а некогерентная сумма относится к сумме действительных величин (например, значений величин). 5 shows an embodiment of a first detection step and a

В блоке 410 корреляторы 510a-510r задержки принимают входные выборки от модулей 154a-154r приемника соответственно. В корреляторе 510a задержки для антенны 1 (или m=1) устройство 512a сужения спектра по Баркеру декодирует с сужением спектра входные выборки с помощью 11-сигнальной последовательности Баркера и предоставляет суженные символы на скорости передачи элементарного сигнала. Для каждого периода n элементарного сигнала устройство 512a сужения спектра по Баркеру умножает 11 входных выборок для периодов элементарного сигнала с n по n-10 на 11 элементарных сигналов из последовательности Баркера, суммирует результаты умножения и предоставляет суженный символ x m(n) для этого периода элементарного сигнала. Устройство 512a сужения спектра по Баркеру выполняет корреляцию с перестраиваемым опорным сигналом последовательности Баркера с входными выборками для получения суженного символа для каждого периода элементарного сигнала (вместо каждого периода символа) и предоставляет суженные символы буферу 514a символов и умножителю 520a задержки.At a

Умножитель 520a задержки формирует 1-символьные и 2-символьные произведения с задержкой из суженных символов. В умножителе 520a задержки суженные символы предоставляются двум последовательно соединенным блокам 522a и 522b задержки, при этом каждый блок задержки обеспечивает задержку в один период Ts символа, который равен 11 периодам элементарных сигналов, или Ts=11·Tc. Блоки 524a и 524b обеспечивают комплексное сопряжение суженных символов от блоков 522a и 522b задержки соответственно. Умножитель 526a умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524a и предоставляет 1-символьное произведение y1,m(n) с задержкой для этого периода элементарного сигнала. Аналогично умножитель 526b умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524b и предоставляет 2-символьное произведение y2,m(n) с задержкой для этого периода элементарного сигнала.

Коррелятор задержки для каждой оставшейся антенны обрабатывает входные выборки для этой антенны способом, описанным выше для антенны 1. Каждый коррелятор задержки предоставляет 1-символьные произведения y 1,m(n) с задержкой и 2-символьные произведения y 2,m(n) с задержкой для ассоциированной антенны m. Для каждого периода n элементарного сигнала сумматор 528a когерентно суммирует произведения y 1,m(n) для m=1, …, R от всех R корреляторов 510a-510r задержки и предоставляет произведение y 1(n) для этого периода элементарного сигнала. Для каждого периода n элементарного сигнала сумматор 528b суммирует произведения y 2,m(n) для m=1, …, R от всех корреляторов 510a-510r задержки и предоставляет произведение y 2(n) для этого периода элементарного сигнала. Произведения y 1(n) и y 2(n) могут выражаться в виде:The delay correlator for each remaining antenna processes the input samples for this antenna in the manner described above for

1-символьное произведение y 1,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-Ts), которые разделены одним периодом символа для антенны m. 2-символьное произведение y 2,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-2Ts), которые разделены двумя периодами символов для антенны m. Фиг.5 показывает использование 1-символьного и 2-символьного произведений с задержкой для обнаружения сигнала. Вообще, для обнаружения сигнала могут использоваться произведения для любого количества различных задержек (например, 1, 2, 3 периода символов и т.д.). Использование произведений для больших задержек может улучшить SNR и эффективность обнаружения. Однако, поскольку уход частоты вызывает чередование фаз во входных выборках, максимальная задержка может быть ограничена уходом частоты. Величина задержки также влияет на сложность дифференциальных корреляторов 530a и 530b. Например, имеются 127 операций умножения и суммирования для задержки в один период символа, 126 операций умножения и суммирования для задержки в два периода символов и т.д.The 1-character product y 1, m ( n ) with a delay indicates the phase difference between the two narrowed characters x m ( n ) and x m ( n- T s ), which are separated by one symbol period for antenna m. The 2-character product y 2, m ( n ) with a delay indicates the phase difference between the two narrowed characters x m ( n ) and x m ( n -2T s ), which are separated by two symbol periods for the antenna m. 5 shows the use of 1-character and 2-character delayed products for signal detection. In general, products for any number of different delays (for example, 1, 2, 3 symbol periods, etc.) can be used to detect a signal. Using works for longer delays can improve SNR and detection efficiency. However, since frequency drift causes phase rotation in the input samples, the maximum delay can be limited by frequency drift. The amount of delay also affects the complexity of the differential correlators 530a and 530b. For example, there are 127 operations of multiplication and summation for a delay of one symbol period, 126 operations of multiplication and summation for a delay of two symbol periods, etc.

Дифференциальные корреляторы 530a и 530b принимают произведения y 1(n) и y 2(n) соответственно. В дифференциальном корреляторе 530a произведения y 1(n) предоставляются последовательности чередующихся элементов 532a и 534a задержки. Каждый элемент 532a задержки обеспечивает задержку в один период элементарного сигнала, каждый элемент 534a задержки обеспечивает задержку в 10 периодов элементарного сигнала, каждая пара соседних элементов 532a и 534a задержки обеспечивает задержку в 11 периодов элементарного сигнала (которая равна одному периоду символа), и вся последовательность элементов 532a и 534a задержки обеспечивает задержку примерно в 126 периодов символов. Группа из 127 сумматоров 536a соединяется со 127 элементами 532a задержки. Каждый сумматор 536a суммирует входной сигнал и выходной сигнал ассоциированного элемента 532a задержки и предоставляет выходной сигнал y 1(n-11·i)·y 1(n-11·i-1), где i {0, …, 126}. Группа из 127 умножителей 538a соединяется с группой из 127 сумматоров 536a и также принимает 1-символьную дифференциальную последовательность, содержащую 127 известных значений. Эта последовательность образуется посредством побитового произведения первой последовательности d 0 - d 126 на вторую последовательность d 1-d 127, где d 0-d 127 являются 128 битами фиксированной последовательности (или битами пилот-сигнала), используемой для поля SYNC. Поскольку биты пилот-сигнала являются действительными значениями, для i {0, …, 126}. Каждый умножитель 538a умножает выходной сигнал ассоциированного сумматора 536a на d i d i+1 . Для каждого периода n элементарного сигнала сумматор 540a добавляет выходные сигналы от всех 127 умножителей 538a и предоставляет результат c 1(n) корреляции для этого периода элементарного сигнала.

Дифференциальный коррелятор 530b аналогичен дифференциальному коррелятору 530a. Произведения y 2(n) предоставляются последовательности чередующихся элементов 532b и 534b задержки, которые обеспечивают задержку приблизительно в 125 периодов символов. Группа из 126 сумматоров 536b соединяется со 126 элементами 532b задержки. Каждый сумматор 536b суммирует входной сигнал и выходной сигнал ассоциированного элемента 532b задержки и предоставляет выходной сигнал y 2(n-11·i)·y 2(n-11·i-1), где i {0, …, 125}. Группа из 126 умножителей 538b соединяется с группой из 126 сумматоров 536b и также принимает 2-символьную дифференциальную последовательность, содержащую 126 известных значений. Эта последовательность образуется посредством побитового произведения последовательности d 0-d 125 с последовательностью d 2-d 127. Каждый умножитель 538b умножает выходной сигнал ассоциированного сумматора 536b на d i d i+2 . Для каждого периода n элементарного сигнала сумматор 540b добавляет выходные сигналы от всех 126 умножителей 538b и предоставляет результат c 2(k) корреляции для этого периода элементарного сигнала.The differential correlator 530b is similar to the

Дифференциальный коррелятор 530a выполняет корреляцию между 1-символьными произведениями y 1(n) с задержкой с 1-символьной дифференциальной последовательностью. Дифференциальный коррелятор 530b выполняет корреляцию между 2-символьными произведениями y 2(n) с задержкой с 2-символьной дифференциальной последовательностью. Показанный на фиг.5 вариант осуществления предполагает, что радиоканал имеет разброс задержек (т.е. рассеяние или загрязнение) из небольшого количества элементарных сигналов. Сумматоры 536a и 536b используются для накопления энергии на этом разбросе задержек. Энергия также может накаливаться на большем количестве элементарных сигналов для большего разброса задержек либо может пропускаться, если радиоканал обладает нулевым или очень маленьким разбросом задержек (например, для строгой траектории радиоволны при распространении в пределах прямой видимости).

Каждый дифференциальный коррелятор 530 предоставляет результат корреляции для каждого периода элементарного сигнала. Фазы результатов c 2(n) корреляции из дифференциального коррелятора 530b могут не совпадать с фазами соответствующих результатов c 1(n) корреляции из дифференциального коррелятора 530a. Умножитель 542 умножает каждый результат c 2(n) корреляции из дифференциального коррелятора 530b на комплексный вектор для L различных предполагаемых фаз и предоставляет множество из L повернутых по фазам результатов корреляции. Например, предполагаемыми фазами могут быть {0, 90°, 180°, -90°} для L=4, {0, 60°, -60°} для L=3 и т.д. L предполагаемых фаз могут выбираться для охвата возможного диапазона относительных фаз. Например, максимальный уход частоты может составлять 232 кГц для отклонения частоты в ±20 ppm и 5,8 ГГц несущей частоты. Максимальная разность фаз между 1-символьными и 2-символьными корреляциями с задержкой равна ±232 кГц умножить на 1 мкс, что приблизительно равно 90 градусам. Отсюда, если используются предполагаемые фазы 0, 60° и -60°, то по меньшей мере одна предполагаемая фаза находится в пределах 30°. Если разность фаз больше (например, вследствие использования большей задержки или большего ухода частоты), то предполагаемые фазы должны охватывать больший диапазон, вплоть до полных ±180°.Each differential correlator 530 provides a correlation result for each chip period. The phases of the correlation results c 2 ( n ) from the differential correlator 530b may not coincide with the phases of the corresponding correlation results c 1 ( n ) from the

Умножитель 542 поворачивает c 2(n) на разные фазы. Для каждого периода n элементарного сигнала сумматор 544 когерентно складывает результат c 1(n) корреляции из сумматора 540a с каждым из L соответствующих повернутых по фазам результатов корреляции из умножителя 542 и предоставляет L объединенных результатов z p(n) корреляции для p=1,…, L. Если используются K дифференциальных корреляторов для K разных задержек, где K>1, то один дифференциальный коррелятор может использоваться в качестве опорного (без фазового сдвига). Тогда один объединенный результат корреляции получается для каждого предположения, соответствующего определенной фазе для каждого из K-1 оставшихся дифференциальных корреляторов. Например, если K=3, то один объединенный результат корреляции получается для каждого предположения, соответствующего другой паре предполагаемых фаз для двух дифференциальных корреляторов. Для LK-1 возможных предположений получаются вплоть до LK-1 объединенных результатов корреляции. Для каждого периода n элементарного сигнала блок 546 вычисляет возведенную в квадрат величину каждого из L объединенных результатов корреляции (для K=2), определяет наибольшее значение величины в квадрате среди L значений величин в квадрате и предоставляет это наибольшее значение Z(n) величины в квадрате. Для каждого периода n элементарного сигнала детектор 548 сигналов сравнивает наибольшее значение Z(n) величины в квадрате с заранее установленной пороговой величиной Zth и объявляет наличие PPDU, если Z(n) превосходит пороговую величину, или Z(n)>Zth. Детектор 548 сигналов продолжает наблюдать за значениями величин в квадрате для поиска максимального значения и предоставляет период элементарного сигнала для этого максимального значения как начальную синхронизацию tau для обнаруженного PPDU.

В качестве альтернативы результаты c 1(n) и c 2(n) корреляции для каждого периода элементарного сигнала могут некогерентно объединяться. Это может достигаться путем вычисления величины c 1(n) в квадрате, вычисления величины c 2(n) в квадрате и суммирования двух возведенных в квадрат величин для получения Z(n). Пороговая величина Zth может устанавливаться в различные значения в зависимости от того, как выводится Z(n).Alternatively, the results of c 1 ( n ) and c 2 ( n ) correlations for each elementary signal period may be incoherently combined. This can be achieved by calculating the value of c 1 ( n ) squared, calculating the value of c 2 ( n ) squared and summing the two squared values to obtain Z (n). The threshold value Z th can be set to various values depending on how Z ( n ) is derived.

Пороговая величина Zth, используемая для первого этапа обнаружения, может быть самонастраивающейся пороговой величиной, которая изменяется, например, вместе с принятой энергией Erx для 128-битного поля SYNC. Например, пороговая величина Zth может быть задана равной принятой энергии Erx, умноженной на масштабный коэффициент S1, или Zth=Erx·S1. Использование нормализованной принятой энергии для обнаружения сигнала приводит к сходной эффективности обнаружения для широкого диапазона принятых уровней сигнала. Компьютерное моделирование показывает, что вероятность обнаружения порядка 90% и частота ложных тревог меньше 1% могут достигаться для 2 равных некоррелированных каналов Релея при общем SNR в -3 дБ, используя S1=22. Вероятность обнаружения относится к правдоподобию безошибочного объявления наличия PPDU, когда PPDU отправляется. Частота ложных тревог относится к правдоподобию ложного объявления наличия PPDU, когда ничего не отправляется. Компромисс между вероятностью обнаружения и частотой ложных тревог может быть достигнут путем выбора подходящей величины для масштабного коэффициента S1.The threshold value Z th used for the first detection step may be a self-tuning threshold value that changes, for example, together with the received energy E rx for the 128-bit SYNC field. For example, the threshold value Z th may be set equal to the received energy E rx times the scale factor S 1 , or Z th = E rx · S 1 . The use of normalized received energy for signal detection results in similar detection efficiency for a wide range of received signal levels. Computer simulation shows that a detection probability of about 90% and a false alarm rate of less than 1% can be achieved for 2 equal uncorrelated Rayleigh channels with a total SNR of -3 dB using S 1 = 22. Detection probability refers to the likelihood of an error-free declaration of the presence of PPDUs when the PPDU is sent. The false alarm rate refers to the likelihood of a false PPDU announcement when nothing is sent. A compromise between the probability of detection and the frequency of false alarms can be achieved by choosing the appropriate value for the scale factor S 1 .

Фиг.6 показывает вариант осуществления второго этапа обнаружения и блока 420 вхождения в синхронизм по частоте, который выполняет обнаружение сигнала с использованием обработки в частотной области. Для этого варианта осуществления блок 420 включает в себя R блоков 610a-610r оценки ухода частоты для R приемных антенн. Каждый блок оценки ухода частоты обнаруживает энергии в различных элементах разрешения по частоте для определения ухода частоты во входных выборках от ассоциированной антенны. 6 shows an embodiment of a second detection step and a

Для приемной антенны 1 (m=1) буфер 516a символов предоставляет N суженных символов, которые разнесены 11 периодами элементарных сигналов (или одним периодом символа), начиная с начальной синхронизации tau, предоставленной блоком 410 вхождения в синхронизм по времени. Первый суженный символ, таким образом, выравнивается по времени с наилучшим предположением синхронизации из этапа вхождения в синхронизм по времени. Вообще, N может быть любым целым числом, являющимся степенью двойки, и не превышает 128, например N может быть 32, 64 или 128. В блоке 610a оценки ухода частоты группа из N умножителей 612 принимает N суженных символов из буфера 514a символов и N соответствующих битов пилот-сигнала в 128-битной последовательности. Каждый умножитель 612 умножает суженный символ на его бит пилот-сигнала для удаления модуляции из этого суженного символа. Блок 620 N-точечного быстрого преобразования Фурье (FFT) принимает N выходных сигналов от N умножителей 612, выполняет N-точечное FFT над этими N выходными сигналами и предоставляет N значений частотной области для N элементов разрешения по частоте. Группа из N блоков 622 принимает N значений частотной области из блока 620 FFT. Каждый блок 622 вычисляет возведенную в квадрат величину его значения частотной области и предоставляет обнаруженную энергию для соответствующего элемента k разрешения по частоте.For receive antenna 1 ( m = 1), the

После удаления модуляции с помощью умножителей 612 N выходных сигналов из этих умножителей могут иметь периодическую составляющую. Эта периодическая составляющая обусловлена уходом частоты в генераторе на приемной станции 150, что приводит к тому, что принятый сигнал не преобразуется с понижением частоты точно в DC. Блок 620 FFT предоставляет спектральную чувствительность N выходных сигналов от умножителей 612. Элемент k разрешения по частоте с наибольшей обнаруженной энергией свидетельствует об уходе частоты для входных выборок от антенны m.After modulation is removed using

Блок оценки ухода частоты для каждой оставшейся приемной антенны обрабатывает суженные символы для этой антенны способом, описанным для антенны 1. Группа из N сумматоров 632 принимает R множеств из N обнаруженных энергий от R блоков 610a-610r оценки ухода частоты для R приемных антенн. Каждый сумматор 632 суммирует обнаруженные энергии от всех R блоков 610a-610r оценки ухода частоты для ассоциированного элемента k разрешения по частоте и предоставляет общую обнаруженную энергию E(k) для этого элемента разрешения по частоте. Селектор 634 выбирает наибольшую общую обнаруженную энергию E max(k) среди N общих обнаруженных энергий для N элементов разрешения по частоте. Детектор 636 сигналов сравнивает наибольшую общую обнаруженную энергию E max(k) с заранее установленной пороговой величиной Eth, объявляет обнаружение сигнала, если E max(k) больше пороговой величины Eth, и предоставляет элемент разрешения по частоте с наибольшей общей обнаруженной энергией в качестве предполагаемого отклонения k os частоты. Пороговая величина Eth может быть задана равной, например, принятой энергии Erx для 128-битного поля SYNC, умноженной на масштабный коэффициент S2, или Em=Erx·S2.The frequency drift estimation unit for each remaining receiving antenna processes the narrowed symbols for this antenna in the manner described for

Показанный на фиг.6 вариант осуществления использует N-точечное FFT, где N≤128. Если N=64, что является размером FFT, обычно используемым для 802.11b и 802.11g для OFDM, то расстояние между соседними элементами разрешения по частоте равно 15,625 кГц для скорости передачи символов 1 Msps и неточность в оценке ухода частоты равна половине расстояния между элементами разрешения, или 7,812 кГц. Эта неточность может быть уменьшена путем выполнения интерполяции и/или использования большего 128-точечного FFT.The embodiment shown in FIG. 6 uses an N-point FFT, where

Выигрыш от обработки для когерентного накопления посредством FFT приблизительно равен 18 дБ для N=64. Наихудшая потеря когерентного накопления - около 4 дБ, которая возникает, когда фактический уход частоты находится точно между двумя элементами разрешения по частоте. Минимальное общее объединенное SNR почти в 14 дБ может достигаться для N=64. Большинство потерь когерентного накопления может быть восстановлено путем суммирования обнаруженных энергий для пар соседних элементов разрешения по частоте (например, аналогично суммированию, выполненному сумматорами 536a и 536b на фиг.5) перед выбором наибольшей общей обнаруженной энергии. Суммирование обнаруженных энергий для соседних пар элементов разрешения по частоте повышает вероятность обнаружения ценой небольшого увеличения в частоте ложных тревог. Вероятность обнаружения лучше 90% при SNR, равном -7 дБ, и лучше 99.9% при SNR, равном -4 дБ, может достигаться с использованием пороговой величины S2=8. Вероятность ложных тревог составляет менее 0,5% для второго этапа обнаружения, приводя в результате к совокупной частоте ложных тревог в 5·10-5 для первого и второго этапов обнаружения.The gain from processing for coherent accumulation by FFT is approximately 18 dB for N = 64. The worst loss of coherent accumulation is about 4 dB, which occurs when the actual frequency drift is exactly between the two frequency resolution elements. A minimum total combined SNR of almost 14 dB can be achieved for N = 64. Most coherent storage losses can be recovered by summing the detected energies for pairs of neighboring frequency resolution elements (for example, similar to the summation performed by

Многолучевое распространение может ухудшить вероятность обнаружения, поскольку вся энергия не используется на втором этапе обнаружения (вследствие FFT, функционирующего на расстоянии между символами вместо расстояния между элементарными сигналами). В варианте осуществления повышенная эффективность может достигаться для второго этапа обнаружения путем выполнения 128-точечного FFT, а отсюда интегрирования по всей 128-битной последовательности для поля SYNC. В другом варианте осуществления одно 64-точечное FFT может выполняться для первой половины 128-битной последовательности, как описано выше, другое 64-точечное FFT может выполняться для второй половины 128-битной последовательности и обнаруженные энергии для двух FFT могут быть некогерентно суммированы сумматорами 632.Multipath propagation can worsen the probability of detection, since all the energy is not used in the second stage of detection (due to the FFT operating at a distance between symbols instead of the distance between chips). In an embodiment, increased efficiency can be achieved for the second detection step by performing a 128-point FFT, and hence integration over the entire 128-bit sequence for the SYNC field. In another embodiment, one 64-point FFT may be performed for the first half of the 128-bit sequence, as described above, another 64-point FFT may be performed for the second half of the 128-bit sequence, and the detected energies for the two FFTs may be incoherently summed by

В другом варианте осуществления оценки ухода частоты входные выборки коррелируются с известной 128-битной последовательностью для различных предполагаемых уходов частоты. Для каждого предполагаемого ухода частоты входные выборки поворачиваются на этот уход частоты, повернутые выборки коррелируются с 128-битной последовательностью, результат корреляции сравнивается снова с пороговой величиной и объявляется обнаружение сигнала, если результат корреляции превышает пороговую величину. Корреляция может выполняться во временной области с помощью устройства фильтра конечной импульсной характеристики (FIR) или в частотной области с помощью операции FFT-умножения-IFFT. Оценка ухода частоты определяется посредством предполагаемого отклонения частоты, которое приводит к наибольшему результату корреляции, превышающему пороговую величину.In another embodiment, the frequency offset estimates of the input samples are correlated with a known 128-bit sequence for the various estimated frequency offsets. For each assumed frequency drift, the input samples are rotated by this frequency drift, rotated samples are correlated with a 128-bit sequence, the correlation result is compared again with the threshold value and signal detection is announced if the correlation result exceeds the threshold value. Correlation can be performed in the time domain using a finite impulse response (FIR) filter device or in the frequency domain using the FFT-IFFT operation. The estimate of the frequency drift is determined by the assumed frequency deviation, which leads to the greatest correlation result exceeding the threshold value.

В еще одном варианте осуществления оценки ухода частоты входные выборки сначала кодируются с сужением спектра для получения суженных символов на скорости передачи элементарного сигнала, как показано на фиг.5. Суженные символы затем умножаются на соответствующие биты пилот-сигнала для удаления модуляции пилот-сигнала. Результирующие символы используются для формирования 1-символьного и 2-символьного произведений с задержкой, используя, например, умножитель 520a задержки на фиг.5. Произведения с задержкой для каждой задержки обрабатываются для формирования комплексной величины для этой задержки. Для каждой задержки d, где d={1, 2}, d-символьные произведения с задержкой предоставляются группе из 10 последовательно соединенных элементов задержки, разделенных элементарными сигналами (например, аналогичные элементам 722 задержки на фиг.7) для получения d-символьных произведений с задержкой на 11 разных интервалах элементарных сигналов. d-символьные произведения с задержкой для каждого интервала элементарного сигнала когерентно суммируются по полю SYNC (например, используя переключатели 724 и накопители 730 на фиг.7). 11 суммированных результатов для 11 интервалов элементарных сигналов могут объединяться (например, используя суммирование дифференциально взвешенных сигналов каждого канала) для формирования комплексной величины Vd для задержки d. Разность фаз между комплексными величинами V1 и V2 для 1-символьных и 2-символьных задержек может вычисляться и использоваться для выведения ухода частоты. R приемных антенн могут объединяться различными способами, например произведения с задержкой могут объединяться по антеннам, как показано на фиг.5, комплексные величины для различных антенн могут объединяться для каждой задержки d и т.д. Более двух задержек и/или большая задержка также могут использоваться для частотного анализа. Большая задержка приводит к большей разности фаз, которая обеспечивает лучшую разрешающую способность для ухода частоты. Однако большая задержка может привести к погрешности, например фазовый сдвиг больше 180° может интерпретироваться как отрицательный сдвиг меньше 180°. Для заданного количества задержек и заданного максимального ухода частоты для оптимизации разрешающей способности без погрешности может быть выбрано множество задержек.In yet another embodiment, frequency drift estimates, the input samples are first coded to a narrowed spectrum to obtain narrowed symbols at a chip rate, as shown in FIG. 5. The narrowed symbols are then multiplied by the corresponding pilot bits to remove pilot modulation. The resulting symbols are used to form 1-character and 2-character delayed products using, for example, the

Независимо от методики, используемой для частотного анализа, предполагаемый уход k os частоты из блока 420 вхождения в синхронизм по частоте обычно содержит остаточное отклонение частоты. Чтобы оценить это остаточное отклонение частоты, первая 11-отводная оценка канала может выводиться на основе первых 64 битов поля SYNC (например, как описано ниже), вторая 11-отводная оценка канала может выводиться на основе последних 64 битов поля SYNC, с обеими оценками канала, выводимыми с исключенным уходом k os частоты. На основе отвода может вычисляться произведение второй оценки канала и комплексного сопряжения первой оценки канала. 11 результирующих произведений могут быть когерентно суммированы для получения разности фаз между двумя оценками канала. Сравнение с пороговой величиной может выполняться на (1) каждом канальном отводе перед вычислением произведения и/или (2) каждом произведении перед суммированием произведений. Сравнение с пороговой величиной удаляет канальные отводы с низкой энергией, ниже заранее установленной пороговой величины. Остаточное отклонение частоты может быть оценено на основе разности фаз между двумя оценками каналов и может предоставляться фильтру 452 и/или блоку 454 частотной коррекции и использоваться для коррекции синхронизации и/или частоты входных выборок (не показано на фиг.4). Это обновление ухода k os частоты с оценкой остаточного отклонения частоты может повысить эффективность демодуляции.Regardless of the technique used for frequency analysis, the estimated departure of k os frequency from the

Фиг.7 показывает вариант осуществления третьего этапа обнаружения и блока 430 оценки канала, который выполняет обнаружение сигнала с использованием обработки во временной области. Для этого варианта осуществления блок 430 включает в себя R блоков 710a-710r оценки канала для R приемных антенн. Каждый блок оценки канала может выводить оценку импульсной характеристики канала, содержащую канальные отводы, которые располагаются с интервалами частоты выборки. Например, могут быть получены до 11 канальных отводов, разделенных одним элементарным сигналом, если суженные символы получаются на скорости передачи элементарного сигнала, могут быть получены до 22 канальных отводов, разделенных половиной элементарного сигнала, если суженные символы получаются на удвоенной скорости передачи элементарного сигнала (или элементарного сигнала х 2), и т.д. Для показанного на фиг.7 варианта осуществления каждый блок оценки канала выводит 11-отводную оценку импульсной характеристики канала на интервале элементарного сигнала для ассоциированной антенны. 7 shows an embodiment of a third detection step and a

В блоке 710a оценки канала для антенны 1 (m=1) умножитель 712 умножает суженные символы для антенны m на комплексный вектор для удаления отклонения k os частоты, определенного блоком 420 вхождения в синхронизм по частоте. Умножитель 712 предоставляет символы с частотной коррекцией на скорости передачи элементарного сигнала группе из 10 последовательно соединенных элементов 722 задержки. Каждый элемент 722 задержки обеспечивает задержку в один период элементарного сигнала. Группа из 11 переключателей 724 соединяется с выходом умножителя 712 и выходами 10 элементов 722 задержки. Переключатели 724 задействуются для одного периода элементарного сигнала в каждом периоде символа и предоставляют 11 символов с частотной коррекцией для этого периода символа. Управляющий сигнал для переключателей 724 определяется начальной синхронизацией tau от блока 410 вхождения в синхронизм по времени и формируется из условия, чтобы символ с частотной коррекцией из пятого элемента 722 задержки (который предназначен для центрального отвода 11-отводной оценки импульсной характеристики канала) соответствовал наилучшему предположению синхронизации, предоставленному этапом вхождения в синхронизм по времени.At a

Оценка канала выполняется в течение заранее установленного временного интервала W, который выбирается для достижения адекватного SNR или качества для оценок канала. Временной интервал W может быть M периодов символов длиной, где M может быть, например, M>31. Группа из 11 умножителей 726 принимает бит d i пилот-сигнала для каждого периода символа, в котором выполняется оценка канала. Каждый умножитель 726 умножает выходной сигнал соответствующего переключателя 724 на бит d i пилот-сигнала, удаляет модуляцию посредством бита пилот-сигнала и предоставляет свой выходной сигнал соответствующему накопителю 730. Группа из 11 накопителей 730 обнуляется в начале оценки канала. Каждый накопитель 730 когерентно суммирует выходной сигнал соответствующего умножителя 726 в течение временного интервала W. Группа из 11 переключателей 732 соединяется с группой из 11 накопителей 730. Переключатели 732 задействуются в конце временного интервала W и предоставляют 11 канальных отводов h m,0-h m,10 для оценки импульсной характеристики канала для антенны m. Эта оценка канала может использоваться для демодуляции данных, как описано далее. Группа из 11 блоков 734 принимает 11 канальных отводов, и каждый блок 734 вычисляет возведенную в квадрат величину своего канального отвода. Сумматор 736 суммирует выходные сигналы от всех 11 блоков 734 и предоставляет общую энергию для всех канальных отводов для антенны m. В качестве альтернативы выходной сигнал каждого блока 734 может сравниваться с пороговой величиной и сумматор 736 может суммировать только выходные сигналы, которые превышают пороговую величину. Пороговая величина может быть установлена в заранее установленное процентное отношение от общей энергии для всех 11 канальных отводов.Channel estimation is performed over a predetermined time interval W, which is selected to achieve adequate SNR or quality for channel estimates. The time interval W may be M symbol periods of length, where M may be, for example, M> 31. A group of 11

Блок оценки канала для каждой оставшейся приемной антенны обрабатывает суженные символы для этой антенны способом, описанным выше для антенны 1. Сумматор 738 суммирует общие энергии для всех R блоков 710a-710r оценки канала и предоставляет общую энергию H для всех R антенн. Детектор 740 сигналов сравнивает общую энергию H с заранее установленной пороговой величиной Hth и объявляет обнаружение сигнала, если H превышает пороговую величину Hth. Пороговая величина Hth может быть задана равной, например, принятой энергии Erx для 128-битного поля SYNC, умноженной на масштабный коэффициент S3, или Hth=Erx·S3.The channel estimator for each remaining receiving antenna processes the narrowed symbols for that antenna in the manner described above for

Вероятность обнаружения больше 99% и частота ложных тревог менее 10-5 могут достигаться при SNR в -4 дБ, используя пороговую величину S3=14. Суммарная частота ложных тревог менее 10-9 может достигаться со всеми тремя этапами обнаружения. Это допускает, что три этапа обнаружения являются некоррелированными, так как для трех этапов используются разные типы обработки сигнала.A detection probability of greater than 99% and a false alarm rate of less than 10 -5 can be achieved with an SNR of -4 dB using a threshold value of S 3 = 14. A total false alarm rate of less than 10 -9 can be achieved with all three stages of detection. This assumes that the three stages of detection are uncorrelated, since three types of signal processing are used for the three stages.

Для описанных выше вариантов осуществления обнаружение сигнала может достигаться на основе корреляции во временной области (фиг.5), обработки в частотной области (фиг.6) и обработки во временной области (фиг.7). Все три типа обработки сигнала могут использоваться для обеспечения хорошей эффективности обнаружения (например, высокая вероятность обнаружения и низкая частота ложных тревог) для плохих канальных условий (например, низкого SNR). Также может использоваться любая комбинация обработки сигнала для обнаружения сигнала.For the above embodiments, signal detection can be achieved based on time domain correlation (FIG. 5), frequency domain processing (FIG. 6) and time domain processing (FIG. 7). All three types of signal processing can be used to provide good detection efficiency (for example, high detection probability and low false alarm rate) for poor channel conditions (for example, low SNR). Any combination of signal processing for signal detection may also be used.

Фиг.5, 6 и 7 показывают определенные варианты осуществления обнаружения сигнала, вхождения в синхронизм по времени, вхождения в синхронизм по частоте и оценки канала, которые могут выполняться другими способами. Например, обнаружение сигнала и вхождение в синхронизм по времени могут выполняться только с помощью 1-битного дифференциального коррелятора 530a с задержкой. Также может использоваться комбинация методик. Например, входные выборки могут поворачиваться на небольшое количество (например, два) предполагаемых уходов частоты. Остаточное отклонение частоты меньше для одного из предполагаемых уходов частоты, так что кодирование с сужением спектра по Баркеру (или когерентное накопление) может выполняться за большую длительность (например, 22 элементарных сигнала). Суженные символы от более длительного когерентного накопления могут предоставляться умножителю задержки и дифференциальному коррелятору, показанным на фиг.5. Обнаружение сигнала может достигаться для меньшего действующего SNR, поскольку когерентное накопление выполняется за большую длительность.5, 6 and 7 show certain embodiments of signal detection, time synchronism, frequency synchronism, and channel estimation, which may be performed in other ways. For example, signal detection and time synchronization can only be performed using a 1-bit delayed

Фиг.5, 6 и 7 показывают типовую обработку сигнала блоками 410, 420 и 430 соответственно. Обработка может реализовываться различными способами, используя аппаратные средства, программное обеспечение и/или микропрограммное обеспечение. Например, блоки 410, 420 и 430 могут реализовываться с помощью выделенных аппаратных средств либо могут совместно использовать аппаратные средства. Цифровой процессор сигнала (DSP) и/или какой-нибудь другой тип процессора может выполнять обработку для блоков 410, 420 и 430 способом мультиплексирования с временным разделением. Буфер 402 выборок, буфер 514 символа и/или какой-нибудь другой буфер могут использоваться для буферизации данных для обработки.5, 6, and 7 show typical signal processing by

Возвращаясь к фиг.4, после того как обнаружен PPDU, выполняется определение, предназначается ли принятый PPDU для 802.11b/g либо режима расширения диапазона, например, на основе преамбулы PLCP и/или заголовка PLCP. Процессор 440 приема DSSS обрабатывает принятый PPDU, если он предназначен для 802.11b/g. Процессор 450 приема DSSS обрабатывает принятый PPDU, если он предназначен для режима расширения диапазона.Returning to FIG. 4, after the PPDU is detected, a determination is made whether the received PPDU is intended for 802.11b / g or range extension mode, for example, based on the PLCP preamble and / or PLCP header. A DSSS receive processor 440 processes the received PPDU if it is for 802.11b / g. A DSSS receive processor 450 processes the received PPDU if it is intended for range extension mode.

Процессор 440 приема DSSS выполняет спектральное кодирование с сужением спектра и демодуляцию для 802.11b/g. В процессоре 440 многоотводный когерентный приемник/корректор 442 кодирует с сужением спектра входные выборки с помощью последовательности Баркера, корректирует суженные символы на основе оценок канала, объединяет компоненты сигнала по R приемным антеннам и предоставляет обнаруженные символы. Демодулятор (Demod) 444 преобразует обнаруженные символы на основе схемы модуляции (например, BPSK или QPSK), использованной для передачи, выполняет дифференциальное декодирование и предоставляет выходные биты, которые являются оценками информационных битов, отправленных передающей станцией 110.A DSSS receive processor 440 performs spectral narrowing spectral coding and demodulation for 802.11b / g. In processor 440, the multi-tap coherent receiver / corrector 442 encodes the constricted input samples using a Barker sequence, corrects the constricted symbols based on channel estimates, combines signal components over R receive antennas, and provides detected symbols. A demodulator (Demod) 444 converts the detected symbols based on a modulation scheme (eg, BPSK or QPSK) used for transmission, performs differential decoding, and provides output bits that are estimates of information bits sent by transmitting

Процессор 450 приема DSSS выполняет спектральное кодирование с сужением спектра, демодуляцию и декодирование FEC для режима расширения диапазона. В процессоре 450 фильтр 452 фильтрует входные выборки для каждой приемной антенны для удаления внеполосного шума и взаимных помех. Фильтр 452 также может производить повторную выборку входных выборок для каждой приемной антенны (1) для преобразования частоты дискретизации из частоты дискретизации в скорость передачи элементарного сигнала и/или (2) для компенсации ухода синхронизации по принятому PPDU. Для 802.11g входные выборки обычно имеют скорость в несколько раз выше скорости передачи элементарного сигнала OFDM в 20 МГц. В этом случае фильтр 452 может выполнять повторную дискретизацию от многократно 20 МГц до либо 11 МГц для многоотводного когерентного приемника, разделенного элементарными сигналами, либо 22 МГц для многоотводного когерентного приемника, разделенного половинами элементарных сигналов. Сигнал гетеродина (LO), используемый для преобразования с понижением частоты, и тактовый сигнал, используемый для формирования входных выборок, обычно получаются из одного и того же генератора опорной частоты. В этом случае отклонение частоты в тактовом сигнале может быть определено исходя из отклонения k os частоты, определенного блоком 420 вхождения в синхронизм по частоте для сигнала LO. Затем может быть определен уход синхронизации во входных выборках исходя из ухода k os частоты и несущей частоты. Фильтр 452 может выполнять периодическую регулировку ± Tadj исходя из ухода k os частоты, где Tadj может быть частью периода выборки.A DSSS receive processor 450 performs spectral narrowing spectral coding, demodulation, and FEC decoding for the spreading mode. At processor 450, a filter 452 filters the input samples for each receive antenna to remove out-of-band noise and interference. Filter 452 can also re-sample input samples for each receive antenna (1) to convert the sampling frequency from the sampling frequency to the chip rate and / or (2) to compensate for the timing offset from the received PPDU. For 802.11g, input samples typically have speeds several times higher than the OFDM chip rate of 20 MHz. In this case, the filter 452 can re-sample from repeatedly 20 MHz to either 11 MHz for a multi-tap coherent receiver separated by chips, or 22 MHz for a multi-tap coherent receiver split by halves. The local oscillator (LO) signal used for down-conversion and the clock used to form input samples are usually obtained from the same reference frequency generator. In this case, the frequency deviation in the clock signal can be determined based on the frequency deviation k os determined by the

В варианте осуществления фильтр 452 реализуется как многофазный фильтр, состоящий из блока из N базовых фильтров, где N>1. Каждый базовый фильтр ассоциируется с определенным множеством коэффициентов для определенного временного сдвига. В типовой конструкции фильтр 452 включает в себя 11 фильтров FIR, где каждый фильтр FIR имеет четыре отвода. Для создания каждой последующей выходной выборки может использоваться другой базовый фильтр. Если уход частоты равен нулю, то 11 базовых фильтров могут быть циклически пройдены в неизменном порядке, где каждая 11-я выборка образуется из того же базового фильтра. Чтобы компенсировать уход синхронизации, заданный базовый фильтр может пропускаться, а вместо него использоваться следующий базовый фильтр, либо один и тот же базовый фильтр может использоваться для двух последовательных выходных выборок. Регулировка синхронизации, таким образом, может достигаться путем выбора соответствующего базового фильтра, находящегося в употреблении.In an embodiment, filter 452 is implemented as a multiphase filter, consisting of a block of N base filters, where N> 1. Each base filter is associated with a specific set of coefficients for a specific time offset. In a typical design, filter 452 includes 11 FIR filters, where each FIR filter has four taps. A different base filter can be used to create each subsequent output sample. If the frequency drift is zero, then 11 basic filters can be cyclically traversed in the same order, where every 11th sample is formed from the same basic filter. To compensate for synchronization drift, a given base filter can be skipped and the next base filter can be used instead, or the same base filter can be used for two consecutive output samples. Thus, adjustment of synchronization can be achieved by selecting the appropriate base filter in use.

Блок 454 частотной коррекции удаляет уход частоты в отрегулированных по времени выборках для каждой приемной антенны. Блок 454 может быть реализован с помощью генератора с числовым программным управлением (NCO) и комплексного умножителя, аналогичного умножителю 712 на фиг.7. NCO формирует вектор, вращающийся на уходе k os частоты, предоставленном блоком 420 вхождения в синхронизм по частоте. Умножитель умножает отрегулированные по времени выборки для каждой приемной антенны на вектор и предоставляет выборки с частотной коррекцией для этой антенны.Frequency correction unit 454 removes frequency drift in time-adjusted samples for each receiving antenna. Block 454 may be implemented using a numerically controlled generator (NCO) and a complex multiplier similar to