KR20240025897A - 이미지 센서 - Google Patents

이미지 센서 Download PDFInfo

- Publication number

- KR20240025897A KR20240025897A KR1020220104084A KR20220104084A KR20240025897A KR 20240025897 A KR20240025897 A KR 20240025897A KR 1020220104084 A KR1020220104084 A KR 1020220104084A KR 20220104084 A KR20220104084 A KR 20220104084A KR 20240025897 A KR20240025897 A KR 20240025897A

- Authority

- KR

- South Korea

- Prior art keywords

- blocking

- blocking bar

- image sensor

- lens

- dummy

- Prior art date

Links

- 230000000903 blocking effect Effects 0.000 claims abstract description 198

- 239000000758 substrate Substances 0.000 claims abstract description 84

- 230000003287 optical effect Effects 0.000 claims abstract description 38

- 239000011248 coating agent Substances 0.000 claims description 12

- 238000000576 coating method Methods 0.000 claims description 12

- 238000001914 filtration Methods 0.000 claims description 10

- 239000012528 membrane Substances 0.000 claims 1

- 239000000463 material Substances 0.000 description 16

- 238000009792 diffusion process Methods 0.000 description 15

- 238000002955 isolation Methods 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 13

- 239000004020 conductor Substances 0.000 description 11

- 239000011810 insulating material Substances 0.000 description 10

- 239000000853 adhesive Substances 0.000 description 7

- 230000001070 adhesive effect Effects 0.000 description 7

- 238000000926 separation method Methods 0.000 description 6

- 230000002596 correlated effect Effects 0.000 description 5

- 239000012535 impurity Substances 0.000 description 5

- 230000000875 corresponding effect Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000035945 sensitivity Effects 0.000 description 4

- 239000002313 adhesive film Substances 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000000465 moulding Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910001512 metal fluoride Inorganic materials 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14627—Microlenses

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

- H01L27/14605—Structural or functional details relating to the position of the pixel elements, e.g. smaller pixel elements in the center of the imager compared to pixel elements at the periphery

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14621—Colour filter arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14685—Process for coatings or optical elements

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

Abstract

본 발명 개념의 실시예들에 따른 이미지 센서는 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판; 상기 픽셀 어레이 영역 위에 제공되는 마이크로 렌즈; 상기 옵티컬 블랙 영역 위에 제공되는 더미 렌즈; 및 상기 옵티컬 블랙 영역 위에 제공되는 블로킹 바를 포함한다. 상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길다. 상기 블로킹 바의 상면은 굴곡진다.

Description

본 발명은 이미지 센서에 관한 것으로, 더욱 상세하게는 블로킹 바를 포함하는 이미지 센서에 관한 것이다.

이미지 센서는 광학 영상(Optical image)을 전기적 신호로 변환하는 소자이다. 이미지 센서는 CCD(Charge coupled device) 형 및 CMOS(Complementary metal oxide semiconductor) 형으로 분류될 수 있다. CMOS 형 이미지 센서는 CIS(CMOS image sensor)라고 약칭된다. 상기 CIS는 2차원적으로 배열된 복수개의 픽셀들을 구비한다. 픽셀들 각각은 포토 다이오드(photodiode, PD)를 포함한다. 포토다이오드는 입사되는 광을 전기 신호로 변환해주는 역할을 한다.

본 발명 개념의 실시예들은 감도가 향상된 이미지 센서를 제공하는 것을 목적으로 한다.

일부 실시예들에 따른 이미지 센서는 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판; 상기 픽셀 어레이 영역 위에 제공되는 마이크로 렌즈; 상기 옵티컬 블랙 영역 위에 제공되는 더미 렌즈; 및 상기 옵티컬 블랙 영역 위에 제공되는 블로킹 바를 포함하고, 상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고, 상기 블로킹 바의 상면은 굴곡질 수 있다.

일부 실시예들에 따른 이미지 센서는 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판; 상기 픽셀 어레이 영역 위의 마이크로 렌즈; 상기 옵티컬 블랙 영역 위의 더미 렌즈; 및 상기 옵티컬 블랙 영역 위의 블로킹 바를 포함하고, 상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고, 상기 블로킹 바는 상기 마이크로 렌즈를 둘러쌀 수 있다.

일부 실시예들에 따른 이미지 센서는 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판; 상기 픽셀 어레이 영역 위의 컬러 필터; 상기 옵티컬 블랙 영역 위의 블랙 벌크 필터링막; 상기 컬러 필터 및 상기 블랙 벌크 필터링막 상의 렌즈막; 및 상기 렌즈막 상의 코팅막을 포함하고, 상기 렌즈막은, 베이스부; 상기 베이스부 상의 마이크로 렌즈; 상기 베이스부 상의 더미 렌즈; 및 상기 베이스부 상의 블로킹 바를 포함하고, 상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고, 상기 블로킹 바는 상기 마이크로 렌즈를 둘러싸고, 상기 블로킹 바의 상면은 굴곡질 수 있다.

본 발명 개념의 실시예들에 따른 이미지 센서는 옵티컬 블랙 영역 위의 블로킹 바를 포함함에 따라, 옵티컬 블랙 영역 위에 도포되는 접착성 물질이 픽셀 어레이 영역으로 칩투되는 것이 방지될 수 있고, 이미지 센서의 감도가 저하되는 것이 방지될 수 있다.

도 1은 일부 실시예들에 따른 이미지 센서를 설명하기 위한 블록도이다.

도 2는 일부 실시예들에 따른 이미지 센서의 액티브 픽셀 센서 어레이의 회로도이다.

도 3a는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 3b는 도 3a의 A영역의 확대도이다.

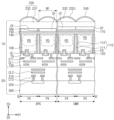

도 3c는 도 3a의 B-B'선에 따른 단면도이다.

도 3d는 도 3b의 C-C'선에 따른 단면도이다.

도 3e는 도 3a에 따른 이미지 센서의 렌즈막을 설명하기 위한 사시도이다.

도 4a는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 4b는 도 4a의 D-D'선에 따른 단면도이다.

도 5는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 6은 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 7은 일부 실시예들에 따른 이미지 센서 패키지의 단면도이다.

도 8a 및 8b는 일부 실시예들에 따른 이미지 센서의 단면도들이다.

도 9는 일부 실시예들에 따른 이미지 센서의 단면도이다.

도 2는 일부 실시예들에 따른 이미지 센서의 액티브 픽셀 센서 어레이의 회로도이다.

도 3a는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 3b는 도 3a의 A영역의 확대도이다.

도 3c는 도 3a의 B-B'선에 따른 단면도이다.

도 3d는 도 3b의 C-C'선에 따른 단면도이다.

도 3e는 도 3a에 따른 이미지 센서의 렌즈막을 설명하기 위한 사시도이다.

도 4a는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 4b는 도 4a의 D-D'선에 따른 단면도이다.

도 5는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 6은 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 7은 일부 실시예들에 따른 이미지 센서 패키지의 단면도이다.

도 8a 및 8b는 일부 실시예들에 따른 이미지 센서의 단면도들이다.

도 9는 일부 실시예들에 따른 이미지 센서의 단면도이다.

도 1은 일부 실시예들에 따른 이미지 센서를 설명하기 위한 블록도이다. 도 2는 일부 실시예들에 따른 이미지 센서의 액티브 픽셀 센서 어레이의 회로도이다.

도 1을 참조하면, 이미지 센서는 액티브 픽셀 센서 어레이(Active Pixel Sensor array; 1001), 행 디코더(row decoder; 1002), 행 드라이버(row driver; 1003), 열 디코더(column decoder; 1004), 타이밍 발생기(timing generator; 1005), 상관 이중 샘플러(CDS: Correlated Double Sampler; 1006), 아날로그 디지털 컨버터(ADC: Analog to Digital Converter; 1007) 및 입출력 버퍼(I/O buffer; 1008)를 포함할 수 있다.

액티브 픽셀 센서 어레이(1001)는 2차원적으로 배열된 복수의 단위 픽셀들을 포함하며, 광 신호를 전기적 신호로 변환할 수 있다. 액티브 픽셀 센서 어레이(1001)는 행 드라이버(1003)로부터 픽셀 선택 신호, 리셋 신호 및 전하 전송 신호와 같은 복수의 구동 신호들에 의해 구동될 수 있다. 또한, 변환된 전기적 신호는 상관 이중 샘플러(1006)에 제공될 수 있다.

행 드라이버(1003)는 행 디코더(1002)에서 디코딩된 결과에 따라 다수의 단위 픽셀들을 구동하기 위한 다수의 구동 신호들을 액티브 픽셀 센서 어레이(1001)로 제공할 수 있다. 단위 픽셀들이 행렬 형태로 배열된 경우에는 각 행별로 구동 신호들이 제공될 수 있다.

타이밍 발생기(1005)는 행 디코더(1002) 및 열 디코더(1004)에 타이밍(timing) 신호 및 제어 신호를 제공할 수 있다.

상관 이중 샘플러(CDS; 1006)는 액티브 픽셀 센서 어레이(1001)에서 생성된 전기 신호를 수신하여 유지(hold) 및 샘플링할 수 있다. 상관 이중 샘플러(1006)는 특정한 잡음 레벨(noise level)과 전기적 신호에 의한 신호 레벨을 이중으로 샘플링하여, 잡음 레벨과 신호 레벨의 차이에 해당하는 차이 레벨을 출력할 수 있다.

아날로그 디지털 컨버터(ADC; 1007)는 상관 이중 샘플러(1006)에서 출력된 차이 레벨에 해당하는 아날로그 신호를 디지털 신호로 변환하여 출력할 수 있다.

입출력 버퍼(1008)는 디지털 신호를 래치(latch)하고, 래치된 신호는 열 디코더(1004)에서의 디코딩 결과에 따라 순차적으로 영상 신호 처리부(도면 미도시)로 디지털 신호를 출력할 수 있다.

도 1 및 도 2를 참조하면, 액티브 픽셀 센서 어레이(1001)는 복수의 단위 화소들(UP)을 포함하며, 단위 화소들(UP)은 매트릭스 형태로 배열될 수 있다. 각각의 단위 화소(UP)는 전송 트랜지스터(TX)를 포함할 수 있다. 각각의 단위 화소(UP)는 로직 트랜지스터(RX, SX, DX)를 더 포함할 수 있다. 로직 트랜지스터는 리셋 트랜지스터(RX), 선택 트랜지스터(SX), 또는 소스 팔로워 트랜지스터(DX)일 수 있다. 전송 트랜지스터(TX)는 전송 게이트(TG)를 포함할 수 있다. 각각의 단위 화소들(UP)은 광전 변환부(PD) 및 부유 확산 영역(FD)를 더 포함할 수 있다. 로직 트랜지스터들(RX, SX, DX)은 복수개의 단위 화소들(UP)끼리 서로 공유될 수 있다.

광전 변환부(PD)는 외부에서 입사된 빛의 양에 비례하여 광전하들을 생성 및 축적할 수 있다. 광전 변환부(PD)는 포토 다이오드, 포토 트랜지스터, 포토 게이트, 핀드 포토 다이오드 및 이들의 조합을 포함할 수 있다. 전송 트랜지스터(TX)는 광전 변환부(PD)에서 생성된 전하를 부유 확산 영역(FD)으로 전송할 수 있다. 부유 확산 영역(FD)은 광전 변환부(PD)에서 생성된 전하를 전송 받아 누적적으로 저장할 수 있다. 부유 확산 영역(FD)에 축적된 광전하들의 양에 따라 소스 팔로워 트랜지스터(DX)가 제어될 수 있다.

리셋 트랜지스터(RX)는 부유 확산 영역(FD)에 축적된 전하들을 주기적으로 리셋시킬 수 있다. 리셋 트랜지스터(RX)의 드레인 전극은 부유 확산 영역(FD)과 연결되며 소스 전극은 전원 전압(VDD)에 연결될 수 있다. 리셋 트랜지스터(RX)가 턴 온(turn-on)되면, 리셋 트랜지스터(RX)의 소스 전극과 연결된 전원 전압(VDD)이 부유 확산 영역(FD)으로 인가될 수 있다. 따라서, 리셋 트랜지스터(RX)가 턴 온되면, 부유 확산 영역(FD)에 축적된 전하들이 배출되어 부유 확산 영역(FD)이 리셋될 수 있다.

소스 팔로워 게이트 전극(SF)을 포함하는 소스 팔로워 트랜지스터(DX)는 소스 팔로워 버퍼 증폭기(source follower buffer amplifier) 역할을 할 수 있다. 소스 팔로워 트랜지스터(DX)는 부유 확산 영역(FD)에서의 전위 변화를 증폭하고, 이를 출력 라인(Vout)으로 출력할 수 있다.

선택 게이트 전극(SEL)을 포함하는 선택 트랜지스터(SX)는 행 단위로 읽어낼 단위 화소들(UP)을 선택할 수 있다. 선택 트랜지스터(SX)가 턴 온될 때, 전원 전압(VDD)이 소스 팔로워 트랜지스터(DX)의 드레인 전극으로 인가될 수 있다.

도 3a는 일부 실시예들에 따른 이미지 센서의 평면도이다. 도 3b는 도 3a의 A영역의 확대도이다. 도 3c는 도 3a의 B-B'선에 따른 단면도이다. 도 3d는 도 3b의 C-C'선에 따른 단면도이다. 도 3e는 도 3a에 따른 이미지 센서의 렌즈막을 설명하기 위한 사시도이다.

도 3a, 3b, 3c, 3d 및 3e를 참조하면, 이미지 센서는 센서 칩(10)을 포함할 수 있다. 센서 칩(10)은 제1 기판(100)을 포함할 수 있다. 제1 기판(100)은 제1 방향(D1) 및 제2 방향(D2)에 의해 정의되는 평면을 따라 확장하는 플레이트의 형태를 가질 수 있다. 제1 방향(D1) 및 제2 방향(D2)은 서로 교차할 수 있다. 일 예로, 제1 방향(D1) 및 제2 방향(D2)은 서로 직교하는 수평 방향일 수 있다.

제1 기판(100)은 반도체 기판일 수 있다. 예를 들어, 제1 기판(100)은 실리콘 기판, 게르마늄 기판, 또는 실리콘-게르마늄 기판일 수 있다. 제1 기판(100)은 제1 도전형의 불순물을 포함할 수 있다. 예를 들어, 제1 기판(100)은 알루미늄(Al), 붕소(B), 인듐(In) 또는 갈륨(Ga)을 제1 도전형의 불순물로 포함할 수 있다. 일부 실시예들에 있어서, 제1 기판(100)은 SOI(Silicon on insulator) 기판일 수 있다.

제1 기판(100)은 픽셀 어레이 영역(APS), 더미 영역(DMR), 옵티컬 블랙 영역(OBR) 및 패드 영역(PDR)을 포함할 수 있다. 픽셀 어레이 영역(APS), 더미 영역(DMR), 옵티컬 블랙 영역(OBR) 및 패드 영역(PDR)은 제1 방향(D1) 및 제2 방향(D2)에 의해 정의되는 평면적으로 구분되는 영역들일 수 있다. 더미 영역(DMR)은 픽셀 어레이 영역(APS)을 둘러쌀 수 있고, 옵티컬 블랙 영역(OBR)은 더미 영역(DMR) 및 픽셀 어레이 영역(APS)을 둘러쌀 수 있고, 패드 영역(PDR)은 옵티컬 블랙 영역(OBR), 더미 영역(DMR) 및 픽셀 어레이 영역(APS)을 둘러쌀 수 있다.

제1 기판(100)은 서로 반대되는 전면 및 후면을 포함할 수 있다. 빛은 제1 기판(100)의 후면으로 입사될 수 있다.

제1 기판(100)의 픽셀 어레이 영역(APS)은 복수개의 픽셀 영역들(PX)을 포함할 수 있다. 픽셀 어레이 영역(APS)의 픽셀 영역(PX)은 입사광(incident light)으로부터 광전 신호를 출력할 수 있다. 픽셀 영역들(PX)은 픽셀 어레이 영역(APS) 내에서 평면적으로 배열될 수 있다.

일부 실시예들에 있어서, 제1 기판(100)의 더미 영역(DMR)은 복수개의 픽셀 영역들(PX)을 포함할 수 있다. 더미 영역(DMR)의 픽셀 영역들(PX)은 더미 픽셀 영역들일 수 있다.

제1 기판(100)은 복수개의 광전 변환 영역들(PD)을 포함할 수 있다. 광전 변환 영역들(PD)은 제1 기판(100)의 전면과 후면 사이에 배치될 수 있다. 광전 변환 영역들(PD)은 제1 기판(100)의 픽셀 영역들(PX) 내에 각각 제공될 수 있다.

광전 변환 영역(PD)은 제2 도전형의 불순물을 포함할 수 있다. 제2 도전형은 제1 도전형과 다를 수 있다. 예를 들어, 광전 변환 영역(PD) 인, 비소, 비스무스 또는 안티몬을 제2 도전형의 불순물로 포함할 수 있다. 광전 변환 영역(PD)은 제1 기판(100)의 후면에 인접할 수 있다.

제1 기판(100)은 복수개의 플로팅 확산 영역들(FD)을 포함할 수 있다. 플로팅 확산 영역들(FD)은 제1 기판(100)의 픽셀 영역들(PX) 내에 각각 제공될 수 있다. 플로팅 확산 영역들(FD)은 제2 도전형의 불순물을 포함할 수 있다. 플로팅 확산 영역(FD)은 제1 기판(100)의 전면에 인접할 수 있다.

센서 칩(10)은 픽셀 분리 패턴(110)을 포함할 수 있다. 픽셀 분리 패턴(110)은 제1 기판(100) 내에 제공될 수 있다. 픽셀 분리 패턴(110)은 제3 방향(D3)으로 연장하여 제1 기판(100)을 관통할 수 있다. 제3 방향(D3)은 제1 방향(D1) 및 제2 방향(D2)과 교차할 수 있다. 일 예로, 제3 방향(D3)은 제1 방향(D1) 및 제2 방향(D2)과 직교하는 수직 방향일 수 있다. 픽셀 분리 패턴(110)에 의해 픽셀 영역들(PX)이 정의될 수 있다. 픽셀 분리 패턴(110)은 예를 들어 그리드의 형태를 가질 수 있다.

픽셀 분리 패턴(110)은 분리 도전막(111) 및 분리 절연막(112)을 포함할 수 있다. 분리 도전막(111)은 제1 기판(100)을 관통할 수 있다. 분리 절연막(112)은 분리 도전막(111)과 제1 기판(100) 사이에 개재될 수 있다. 분리 도전막(111)은 도전 물질을 포함할 수 있다. 분리 절연막(112)은 절연 물질을 포함할 수 있다.

센서 칩(10)은 소자 분리 패턴(120)을 포함할 수 있다. 소자 분리 패턴(120)은 제1 기판(100) 내에 제공될 수 있다. 소자 분리 패턴(120)은 제1 기판(100)의 전면에 인접하게 배치될 수 있다. 소자 분리 패턴(120)은 제1 기판(100)의 활성 영역을 정의할 수 있다. 소자 분리 패턴(120)은 절연 물질을 포함할 수 있다.

센서 칩(10)은 제1 기판(100)의 전면을 덮는 제1 배선 절연막(130)을 포함할 수 있다. 제1 배선 절연막(130)은 제1 기판(100)의 활성 영역을 덮을 수 있다. 제1 배선 절연막(130)은 절연 물질을 포함할 수 있다. 일부 실시예들에 있어서, 제1 배선 절연막(130)은 복수개의 절연막들을 포함하는 다중 절연막일 수 있다.

센서 칩(10)은 전송 게이트들(TG) 및 게이트 절연막들(GI)을 포함할 수 있다. 전송 게이트(TG)는 제1 기판(100)과 제1 배선 절연막(130) 사이에 제공될 수 있다. 전송 게이트(TG)는 도전 물질을 포함할 수 있다.

전송 게이트 전극(TG)과 제1 기판(100) 사이에 게이트 절연막(GI)이 제공될 수 있다. 게이트 절연막(GI)은 절연 물질을 포함할 수 있다.

제1 배선 절연막(130) 내에 제1 컨택들(CT1) 및 제1 도전 라인들(CL1)이 제공될 수 있다. 제1 컨택들(CT1) 중 적어도 몇몇은 플로팅 확산 영역(FD)에 연결될 수 있다. 제1 도전 라인들(CL1) 중 적어도 몇몇은 제1 컨택(CT1)에 연결될 수 있다. 제1 컨택들(CT1) 및 제1 도전 라인들(CL1)은 도전 물질을 포함할 수 있다.

센서 칩(10)은 제1 기판(100)의 후면을 덮는 고정 전하막(140)을 포함할 수 있다. 고정 전하막(140)은 예를 들어 화학양론비 보다 부족한 양의 산소를 포함하는 금속 산화막 또는 화학양론비 보다 부족한 양의 불소를 포함하는 금속 불화막일 수 있다. 고정 전하막(140)은 음의 고정전하를 가질 수 있고, 정공의 축적(hole accumulation)을 발생시킬 수 있다. 고정 전하막(140)에 의해 제1 기판(100)의 암전류 및 화이트 스팟(white spot)이 효과적으로 감소될 수 있다. 일부 실시예들에 있어서, 고정 전하막(140)은 서로 다른 복수개의 막들을 포함할 수 있다.

센서 칩(10)은 고정 전하막(140) 상의 반사 방지막(150)을 포함할 수 있다. 반사 방지막(150)은 예를 들어 알루미늄 산화물을 포함할 수 있다. 일부 실시예들에 있어서, 반사 방지막(150)은 서로 다른 복수개의 막들을 포함할 수 있다.

센서 칩(10)은 반사 방지막(150) 상의 펜스 패턴(160)을 포함할 수 있다. 펜스 패턴(160)은 제1 기판(100)의 픽셀 어레이 영역(APS) 위에 배치될 수 있다. 펜스 패턴(160)은 후술하는 컬러 필터들(CF)을 서로 분리시킬 수 있다. 예를 들어, 펜스 패턴(160)은 그리드의 형태를 가질 수 있다. 펜스 패턴(160)은 도전 물질을 포함할 수 있다. 예를 들어, 펜스 패턴(160)은 텅스텐을 포함할 수 있다.

센서 칩(10)은 반사 방지막(150) 상의 차광막(170)을 포함할 수 있다. 차광막(170)은 제1 기판(100)의 더미 영역(DMR), 옵티컬 블랙 영역(OBR) 및 패드 영역(PDR) 위에 배치될 수 있다. 차광막(170)은 도전 물질을 포함할 수 있다. 차광막(170)은 펜스 패턴(160)과 동일한 물질을 포함할 수 있다. 예를 들어, 차광막(170)은 텅스텐을 포함할 수 있다.

일부 실시예들에 있어서, 센서 칩(10)은 펜스 패턴(160) 및 차광막(170)을 덮는 보호막을 포함할 수 있다. 상기 보호막은 절연 물질을 포함할 수 있다.

센서 칩(10)은 연결 컨택(180)을 포함할 수 있다. 연결 컨택(180)은 제1 기판(100)의 옵티컬 블랙 영역(OBR) 위에 배치될 수 있다. 연결 컨택(180)은 고정 전하막(140) 및 반사 방지막(150)을 관통하여 픽셀 분리 패턴(110)에 연결될 수 있다. 연결 컨택(180)은 픽셀 분리 패턴(110)에 연결되는 제1 컨택 패턴(181) 및 제1 컨택 패턴(181) 상의 제2 컨택 패턴(182)을 포함할 수 있다.

제1 컨택 패턴(181)은 차광막(170)과 경계 없이 연결될 수 있다. 제1 컨택 패턴(181)과 차광막(170)은 일체의 구조를 이룰 수 있다. 제1 컨택 패턴(181)은 차광막(170)과 동일한 물질을 포함할 수 있다. 제2 컨택 패턴(182)은 제1 컨택 패턴(181)과 다른 물질을 포함할 수 있다. 일 예로, 제2 컨택 패턴(182)은 알루미늄을 포함할 수 있다.

센서 칩(10)은 제1 연결 구조체(190)를 포함할 수 있다. 제1 연결 구조체(190)는 제1 기판(100)의 옵티컬 블랙 영역(OBR) 위에 배치될 수 있다. 제1 연결 구조체(190)는 고정 전하막(140), 반사 방지막(150), 제1 기판(100) 및 제1 배선 절연막(130)을 관통하여 후술하는 회로 칩(20)에 연결될 수 있다. 제1 연결 구조체(190)는 제1 배선 절연막(130) 내의 제1 도전 라인들(CL1) 중 적어도 하나와 연결될 수 있다.

제1 연결 구조체(190)는 회로 칩(20)에 연결되는 제1 도전 패턴(191), 제1 도전 패턴(191) 상의 제1 절연 패턴(192), 제1 절연 패턴(192) 상의 제1 캡핑 패턴(193)을 포함할 수 있다. 제1 도전 패턴(191)은 차광막(170)과 경계 없이 연결될 수 있다. 제1 도전 패턴(191)과 차광막(170)은 일체의 구조를 이룰 수 있다. 제1 도전 패턴(191)은 차광막(170)과 동일한 물질을 포함할 수 있다.

제1 절연 패턴(192)은 절연 물질을 포함할 수 있다. 제1 캡핑 패턴(193)은 절연 물질을 포함할 수 있다.

센서 칩(10)은 도전 패드(210)를 포함할 수 있다. 도전 패드(210)는 제1 기판(100)의 패드 영역(PDR) 위에 배치될 수 있다. 도전 패드(210)는 고정 전하막(140) 및 반사 방지막(150)을 관통하여 제1 기판(100)에 연결될 수 있다.

도전 패드(210)는 제1 기판(100) 상의 제1 패드 패턴(211) 및 제1 패드 패턴(211) 상의 제2 패드 패턴(212)을 포함할 수 있다. 제1 패드 패턴(211)은 차광막(170)과 경계 없이 연결될 수 있다. 제1 패드 패턴(211)과 차광막(170)은 일체의 구조를 이룰 수 있다. 제1 패드 패턴(211)은 차광막(170)과 동일한 물질을 포함할 수 있다.

제2 패드 패턴(212)은 제1 패드 패턴(211)과 다른 물질을 포함할 수 있다. 일 예로, 제2 패드 패턴(212)은 알루미늄을 포함할 수 있다.

센서 칩(10)은 제2 연결 구조체(220)를 포함할 수 있다. 제2 연결 구조체(220)는 제1 기판(100)의 패드 영역(PDR) 위에 배치될 수 있다. 제2 연결 구조체(220)는 고정 전하막(140), 반사 방지막(150), 제1 기판(100) 및 제1 배선 절연막(130)을 관통하여 후술하는 회로 칩(20)에 연결될 수 있다. 제2 연결 구조체(220)는 제1 배선 절연막(130) 내의 제1 도전 라인들(CL1) 중 적어도 하나와 연결될 수 있다.

제2 연결 구조체(220)는 회로 칩(20)에 연결되는 제2 도전 패턴(221), 제2 도전 패턴(221) 상의 제2 절연 패턴(222), 제2 절연 패턴(222) 상의 제2 캡핑 패턴(223)을 포함할 수 있다. 제2 도전 패턴(221)은 차광막(170)과 경계 없이 연결될 수 있다. 제2 도전 패턴(221)과 차광막(170)은 일체의 구조를 이룰 수 있다. 제2 도전 패턴(221)은 차광막(170)과 동일한 물질을 포함할 수 있다.

제2 절연 패턴(222)은 절연 물질을 포함할 수 있다. 제2 캡핑 패턴(223)은 절연 물질을 포함할 수 있다.

센서 칩(10)은 컬러 필터들(CF)을 포함할 수 있다. 컬러 필터들(CF)은 제1 기판(100)의 픽셀 어레이 영역(APS) 및 더미 영역(DMR) 위에 배치될 수 있다. 컬러 필터들(CF)은 픽셀 영역들(PX) 위에 각각 배치될 수 있다. 컬러 필터들(CF)은 광전 변환 영역들(PD)에 대응되는 위치들에 각각 제공될 수 있다. 컬러 필터들(CF) 각각은 레드 필터, 블루 필터 및 그린 필터 중 하나일 수 있다. 컬러 필터들(CF)은 컬러 필터 어레이들을 이룰 수 있다. 예를 들어, 컬러 필터들(CF)은 베이어 패턴(Bayer pattern) 방식으로 2차원적으로 배열될 수 있다.

픽셀 어레이 영역(APS) 위에 배치되는 컬러 필터들(CF) 사이에 펜스 패턴(160)이 제공될 수 있다. 더미 영역(DMR) 위에 배치되는 컬러 필터들(CF)은 차광막(170) 상에 제공될 수 있다. 일부 실시예들에 있어서, 더미 영역(DMR) 위에 배치되는 컬러 필터들(CF)은 더미 컬러 필터들일 수 있다.

센서 칩(10)은 블랙 벌크 필터링막(FI)을 포함할 수 있다. 블랙 벌크 필터링막(FI)은 제1 기판(100)의 옵티컬 블랙 영역(OBR) 위에 배치될 수 있다. 블랙 벌크 필터링막(FI)은 차광막(170) 상에 배치될 수 있다. 블랙 벌크 필터링막(FI)은 컬러 필터들(CF)과 다른 파장의 빛을 차단할 수 있다.

센서 칩(10)은 렌즈막(230)을 포함할 수 있다. 렌즈막(230)은 제1 기판(100)의 픽셀 어레이 영역(APS), 더미 영역(DMR), 옵티컬 블랙 영역(OBR) 및 패드 영역(PDR) 위에 배치될 수 있다. 렌즈막(230)은 컬러 필터들(CF) 및 블랙 벌크 필터링막(FI) 상에 배치될 수 있다. 렌즈막(230)은 투명할 수 있다. 렌즈막(230)은 빛을 투과시킬 수 있다. 렌즈막(230)은 유기 물질을 포함할 수 있다. 예를 들어, 렌즈막(230)은 포토 레지스트 물질 또는 열경화성 수지를 포함할 수 있다.

렌즈막(230)은 컬러 필터들(CF) 및 블랙 벌크 필터링막(FI) 상의 베이스부(231)를 포함할 수 있다. 렌즈막(230)은 베이스부(231) 상의 마이크로 렌즈들(232), 더미 렌즈들(233) 및 블로킹 바들(234)을 포함할 수 있다. 마이크로 렌즈들(232), 더미 렌즈들(233) 및 블로킹 바들(234)은 동일한 레벨에 배치될 수 있다. 마이크로 렌즈들(232), 더미 렌즈들(233) 및 블로킹 바들(234)은 베이스부(231)에서 제3 방향(D3)으로 돌출되는 부분들일 수 있다. 마이크로 렌즈들(232), 더미 렌즈들(233) 및 블로킹 바들(234)은 베이스부(231)와 경계없이 연결될 수 있다. 마이크로 렌즈들(232), 더미 렌즈들(233), 블로킹 바들(234) 및 베이스부(231)는 일체의 구조를 이룰 수 있다. 마이크로 렌즈들(232)은 제1 기판(100)의 픽셀 어레이 영역(APS) 및 더미 영역(DMR) 위에 배치될 수 있다. 더미 렌즈들(233) 및 블로킹 바들(234)은 제1 기판(100)의 옵티컬 블랙 영역(OBR) 위에 배치될 수 있다.

마이크로 렌즈들(232)은 픽셀 영역들(PX) 위에 각각 배치될 수 있다. 마이크로 렌즈들(232)은 광전 변환 영역들(PD)에 대응되는 위치들에 각각 제공될 수 있다. 더미 영역(DMR) 위에 배치되는 마이크로 렌즈들(232)은 더미 마이크로 렌즈들일 수 있다.

블로킹 바(234)는 제1 방향(D1)으로 연장하는 2개의 부분들 및 제2 방향(D2)으로 연장하는 2개의 부분들을 포함할 수 있다. 블로킹 바(234)는 마이크로 렌즈들(232)을 둘러쌀 수 있다. 마이크로 렌즈들(232)은 블로킹 바(234)의 제1 방향(D1)으로 연장하는 2개의 부분들 사이에 배치될 수 있다. 마이크로 렌즈들(232)은 블로킹 바(234)의 제2 방향(D2)으로 연장하는 2개의 부분들 사이에 배치될 수 있다. 블로킹 바(234)는 더미 렌즈들(233) 중 적어도 몇몇을 둘러쌀 수 있다. 도 3a에 따른 평면적 관점에서, 블로킹 바(234)는 링의 형태를 가질 수 있다.

블로킹 바(234)의 길이는 마이크로 렌즈(232)의 길이 및 더미 렌즈(233)의 길이보다 클 수 있다. 일 예로, 블로킹 바(234)의 제1 방향(D1)으로 연장하는 부분의 제1 방향(D1)으로의 길이는 마이크로 렌즈(232)의 제1 방향(D1)으로의 길이 및 더미 렌즈(233)의 제1 방향(D1)으로의 길이보다 클 수 있다. 블로킹 바(234)의 길이는 제1 기판(100)의 픽셀 어레이 영역(APS)의 길이보다 클 수 있다.

마이크로 렌즈(232)의 상면(232t), 더미 렌즈(233)의 상면(233t) 및 블로킹 바(234)의 상면(234t)은 굴곡질 수 있다. 마이크로 렌즈(232)의 상면(232t)의 곡률 반경, 더미 렌즈(233)의 상면(233t)의 곡률 반경 및 블로킹 바(234)의 상면(234t)의 곡률 반경은 동일할 수 있다. 예를 들어, 도 3c 및 3d에 따른 단면적 관점에서, 마이크로 렌즈(232)의 상면(232t)의 곡률 반경, 더미 렌즈(233)의 상면(233t)의 곡률 반경 및 블로킹 바(234)의 상면(234t)의 곡률 반경은 동일할 수 있다. 일부 실시예들에 있어서, 마이크로 렌즈(232)의 상면(232t)의 곡률 반경, 더미 렌즈(233)의 상면(233t)의 곡률 반경 및 블로킹 바(234)의 상면(234t)의 곡률 반경은 서로 다를 수 있다.

마이크로 렌즈(232)의 최대폭, 더미 렌즈(233)의 최대폭 및 블로킹 바(234)의 최대폭은 동일할 수 있다. 일 예로, 마이크로 렌즈(232)의 제1 방향(D1)으로의 최대폭(W1), 더미 렌즈(233)의 제1 방향(D1)으로의 최대폭(W2) 및 블로킹 바(234)의 제1 방향(D1)으로의 최대폭(W3)은 동일할 수 있다. 일부 실시예들에 있어서, 마이크로 렌즈(232)의 최대폭, 더미 렌즈(233)의 최대폭 및 블로킹 바(234)의 최대폭은 서로 다를 수 있다.

마이크로 렌즈(232)의 최상부의 레벨, 더미 렌즈(233)의 최상부의 레벨 및 블로킹 바(234)의 최상부의 레벨은 동일할 수 있다. 일부 실시예들에 있어서, 마이크로 렌즈(232)의 최상부의 레벨, 더미 렌즈(233)의 최상부의 레벨 및 블로킹 바(234)의 최상부의 레벨은 서로 다를 수 있다.

센서 칩(10)은 렌즈막(230) 상의 코팅막(240)을 포함할 수 있다. 코팅막(240)은 투명할 수 있다. 코팅막(240)은 렌즈막(230)의 상면을 컨포멀하게 덮을 수 있다.

코팅막(240)은 마이크로 렌즈(232) 상의 제1 부분, 더미 렌즈(233) 상의 제2 부분 및 블로킹 바(234) 상의 제3 부분을 포함할 수 있다. 코팅막(240)의 제1 부분의 상면, 제2 부분의 상면 및 제3 부분의 상면은 굴곡질 수 있다.

코팅막(240) 및 렌즈막(230)을 관통하는 리세스(RS)가 정의될 수 있다. 리세스(RS)에 의해 도전 패드(210)가 노출될 수 있다.

이미지 센서는 회로 칩(20)을 포함할 수 있다. 회로 칩(20)은 제2 기판(300)을 포함할 수 있다. 제2 기판(300)은 반도체 기판일 수 있다. 일부 실시예들에 있어서, 제2 기판(300)은 SOI 기판일 수 있다.

회로 칩(20)은 제2 기판(300) 상의 제2 배선 절연막(310)을 포함할 수 있다. 제2 배선 절연막(310)은 제2 기판(300)의 활성 영역을 덮을 수 있다. 제2 배선 절연막(310)은 절연 물질을 포함할 수 있다. 일부 실시예들에 있어서, 제2 배선 절연막(310)은 복수개의 절연막들을 포함하는 다중 절연막일 수 있다.

회로 칩(20)은 제2 기판(300)과 제2 배선 절연막(310) 사이의 집적 회로들(320)을 포함할 수 있다. 집적 회로들(320)은 로직 회로 및 메모리 회로 중 적어도 하나를 포함할 수 있다.

회로 칩(20)은 제2 배선 절연막(310) 내의 제2 컨택들(CT2) 및 제2 도전 라인들(CL2)을 포함할 수 있다. 제2 컨택들(CT2) 중 적어도 몇몇은 집적 회로(320)에 연결될 수 있다. 제2 도전 라인들(CL2) 중 적어도 몇몇은 제2 컨택(CT2)에 연결될 수 있다. 제2 도전 라인들(CL2) 중 적어도 하나는 제1 연결 구조체(190)에 연결될 수 있다. 제2 도전 라인들(CL2) 중 적어도 하나는 제2 연결 구조체(220)에 연결될 수 있다. 제2 컨택들(CT2) 및 제2 도전 라인들(CL2)은 도전 물질을 포함할 수 있다.

도 3a 및 3b를 참조하면, 더미 렌즈들(233)은 제1 더미 렌즈들(DL1), 제2 더미 렌즈들(DL2), 제3 더미 렌즈들(DL3) 및 제4 더미 렌즈들(DL4)을 포함할 수 있다. 블로킹 바들(234)은 제1 블로킹 바(BB1), 제2 블로킹 바(BB2) 및 제3 블로킹 바(BB3)를 포함할 수 있다.

도시된 것과 달리, 블로킹 바들(234)의 개수는 3개에 제한되지 않을 수 있다. 일부 실시예들에 있어서, 블로킹 바들(234)의 개수는 2개 이하일 수도 있고, 4개 이상일 수도 있다.

제1 블로킹 바(BB1)는 제1 더미 렌즈들(DL1) 및 마이크로 렌즈들(232)을 둘러쌀 수 있다. 제2 블로킹 바(BB2)는 제1 블로킹 바(BB1), 제2 더미 렌즈들(DL2), 제1 더미 렌즈들(DL1) 및 마이크로 렌즈들(232)을 둘러쌀 수 있다. 제3 블로킹 바(BB3)는 제2 블로킹 바(BB2), 제3 더미 렌즈들(DL3), 제1 블로킹 바(BB1), 제2 더미 렌즈들(DL2), 제1 더미 렌즈들(DL1) 및 마이크로 렌즈들(232)을 둘러쌀 수 있다.

제1 더미 렌즈(DL1)와 마이크로 렌즈(232) 사이의 거리는 제1 블로킹 바(BB1)와 마이크로 렌즈(232) 사이의 거리보다 작을 수 있다. 제2 더미 렌즈(DL2)는 제1 및 제2 블로킹 바들(BB1, BB2) 사이에 배치될 수 있다. 제3 더미 렌즈(DL3)는 제2 및 제3 블로킹 바들(BB2, BB3) 사이에 배치될 수 있다. 제4 더미 렌즈(DL4)와 마이크로 렌즈(232) 사이의 거리는 제3 블로킹 바(BB3)와 마이크로 렌즈(232) 사이의 거리보다 클 수 있다. 제1 더미 렌즈(DL1) 및 제4 더미 렌즈(DL4) 사이에 제1 내지 제3 블로킹 바들(BB1, BB2, BB3)이 배치될 수 있다.

일부 실시예들에 따른 이미지 센서를 포함하는 이미지 센서 패키지를 제조하는 방법은 이미지 센서의 제1 기판(100)의 패드 영역(PDR) 위에 접착성 물질을 도포하고, 접착성 물질 상에 댐 구조체를 형성하는 것을 포함할 수 있다. 예를 들어, 상기 접착성 물질은 에폭시를 포함할 수 있다.

옵티컬 블랙 영역(OBR) 위에 블로킹 바(234)가 제공됨에 따라, 패드 영역(PDR) 위에 도포되는 상기 접착성 물질이 픽셀 어레이 영역(APS)으로 침투되는 것이 방지될 수 있고, 이미지 센서의 감도가 저하되는 것이 방지될 수 있다.

일부 실시예들에 따른 이미지 센서는 블로킹 바(234) 내에 압축 응력이 생성될 수 있고, 블로킹 바(234)의 압축 응력에 의해 옵티컬 블랙 영역(OBR) 위에서 발생한 코팅막(240)의 크랙이 픽셀 어레이 영역(APS) 위로 전파되는 것이 방지될 수 있다.

도 4a는 일부 실시예들에 따른 이미지 센서의 평면도이다. 도 4b는 도 4a의 D-D'선에 따른 단면도이다.

도 4a 및 4b를 참조하면, 이미지 센서는 센서 칩(10a) 및 회로 칩(20a)을 포함할 수 있다. 센서 칩(10a)은 렌즈막(230a)을 포함할 수 있다.

렌즈막(230a)은 베이스부(231a)를 포함할 수 있다. 렌즈막(230a)은 베이스부(231a) 상의 상의 제1 더미 렌즈들(DL1a), 제2 더미 렌즈들(DL2a), 제1 블로킹 바(BB1a), 제2 블로킹 바(BB2a) 및 제3 블로킹 바(BB3a)를 포함할 수 있다.

제1 더미 렌즈들(DL1a)은 제1 내지 제3 블로킹 바들(BB1a, BB2a, BB3a)에 의해 둘러싸일 수 있다. 제2 더미 렌즈들(DL2a)은 제3 블로킹 바(BB3a) 보다 패드 영역(PDR)에 가깝게 배치될 수 있다. 제1 및 제2 블로킹 바들(BB1a, BB2a) 사이에 더미 렌즈가 배치되지 않을 수 있다. 제2 및 제3 블로킹 바들(BB2a, BB3a) 사이에 더미 렌즈가 배치되지 않을 수 있다.

베이스부(231a)는 제1 및 제2 블로킹 바들(BB1a, BB2a) 사이의 제1 플랫 상면(FS1a) 및 제2 및 제3 블로킹 바들(BB2a, BB3a) 사이의 제2 플랫 상면(FS2a)을 포함할 수 있다.

제1 플랫 상면(FS1a)은 제1 블로킹 바(BB1a) 및 제2 블로킹 바(BB2a)를 연결할 수 있다. 제1 플랫 상면(FS1a)은 평평할 수 있다. 제1 플랫 상면(FS1a)은 제1 방향(D1)으로 연장하는 2개의 부분들 및 제2 방향(D2)으로 연장하는 2개의 부분들을 포함할 수 있다. 평면적 관점에서, 제1 플랫 상면(FS1a)은 링의 형태를 가질 수 있다. 제1 플랫 상면(FS1a)의 폭은 제1 블로킹 바(BB1a)의 폭 및 제2 블로킹 바(BB2a)의 폭보다 클 수 있다. 일 예로, 제1 플랫 상면(FS1a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1)으로의 폭은 제1 블로킹 바(BB1a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1) 으로의 폭 및 제2 블로킹 바(BB2a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1) 으로의 폭보다 클 수 있다.

제2 플랫 상면(FS2a)은 제2 블로킹 바(BB2a) 및 제3 블로킹 바(BB3a)를 연결할 수 있다. 제2 플랫 상면(FS2a)은 평평할 수 있다. 제2 플랫 상면(FS2a)은 제1 방향(D1)으로 연장하는 2개의 부분들 및 제2 방향(D2)으로 연장하는 2개의 부분들을 포함할 수 있다. 평면적 관점에서, 제2 플랫 상면(FS2a)은 링의 형태를 가질 수 있다. 제2 플랫 상면(FS2a)의 폭은 제2 블로킹 바(BB2a)의 폭 및 제3 블로킹 바(BB3a)의 폭보다 클 수 있다. 일 예로, 제2 플랫 상면(FS2a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1)으로의 폭은 제2 블로킹 바(BB2a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1) 으로의 폭 및 제3 블로킹 바(BB3a)의 제2 방향(D2)으로 연장하는 부분의 제1 방향(D1) 으로의 폭보다 클 수 있다.

도 5는 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 5를 참조하면, 이미지 센서는 제1 더미 렌즈들(DL1b), 제2 더미 렌즈들(DL2b), 제3 더미 렌즈들(DL3b), 제4 더미 렌즈들(DL4b), 제1 블로킹 바들(BB1b), 제2 블로킹 바들(BB2b) 및 제3 블로킹 바들(BB3b)을 포함할 수 있다.

제1 블로킹 바들(BB1b)은 서로 이격될 수 있다. 제1 블로킹 바들(BB1b)은 제1 방향(D1)으로 연장하는 제1 블로킹 바들(BB1b) 및 제2 방향(D2)으로 연장하는 제1 블로킹 바들(BB1b)을 포함할 수 있다. 제1 방향(D1)으로 연장하는 제1 블로킹 바들(BB1b)은 제1 방향(D1)으로 배열될 수 있다. 제2 방향(D2)으로 연장하는 제1 블로킹 바들(BB1b)은 제2 방향(D2)으로 배열될 수 있다.

제2 블로킹 바들(BB2b)은 서로 이격될 수 있다. 제2 블로킹 바들(BB2b)은 제1 방향(D1)으로 연장하는 제2 블로킹 바들(BB2b) 및 제2 방향(D2)으로 연장하는 제2 블로킹 바들(BB2b)을 포함할 수 있다. 제1 방향(D1)으로 연장하는 제2 블로킹 바들(BB2b)은 제1 방향(D1)으로 배열될 수 있다. 제2 방향(D2)으로 연장하는 제2 블로킹 바들(BB2b)은 제2 방향(D2)으로 배열될 수 있다.

제3 블로킹 바들(BB3b)은 서로 이격될 수 있다. 제3 블로킹 바들(BB3b)은 제1 방향(D1)으로 연장하는 제3 블로킹 바들(BB3b) 및 제2 방향(D2)으로 연장하는 제3 블로킹 바들(BB3b)을 포함할 수 있다. 제1 방향(D1)으로 연장하는 제3 블로킹 바들(BB3b)은 제1 방향(D1)으로 배열될 수 있다. 제2 방향(D2)으로 연장하는 제3 블로킹 바들(BB3b)은 제2 방향(D2)으로 배열될 수 있다.

서로 인접하는 제1 블로킹 바들(BB1b) 사이에 제1 갭(GA1b)이 정의될 수 있다. 서로 인접하는 제2 블로킹 바들(BB2b) 사이에 제2 갭(GA2b)이 정의될 수 있다. 서로 인접하는 제3 블로킹 바들(BB3b) 사이에 제3 갭(GA3b)이 정의될 수 있다. 제1 내지 제3 갭들(GA1b, GA2b, GA3b)을 통해 베이스부(231b)의 상면의 일부들이 노출될 수 있다.

갭(GA1b, GA2b, GA3b)의 폭은 블로킹 바(BB1b, BB2b, BB3b)의 폭과 동일할 수 있다. 일 예로, 제2 방향(D2)으로 연장하는 제1 블로킹 바들(BB1b) 사이에 제공되는 제1 갭(GA1b)의 제1 방향(D1)으로의 폭은 제2 방향(D2)으로 연장하는 제1 블로킹 바(BB1b)의 제1 방향(D1)으로의 폭과 동일할 수 있다.

갭(GA1b, GA2b, GA3b)의 길이보다 블로킹 바(BB1b, BB2b, BB3b)의 길이가 클 수 있다. 일 예로, 제2 방향(D2)으로 연장하는 제1 블로킹 바들(BB1b) 사이에 제공되는 제1 갭(GA1b)의 제2 방향(D2)으로의 길이보다 제2 방향(D2)으로 연장하는 제1 블로킹 바(BB1b)의 제2 방향(D2)으로의 길이가 클 수 있다.

도 6은 일부 실시예들에 따른 이미지 센서의 평면도이다.

도 6을 참조하면, 이미지 센서는 제1 블로킹 바들(BB1c), 제2 블로킹 바들(BB2c), 제3 블로킹 바들(BB3c), 제1 블로킹 바들(BB1c)에 의해 둘러싸이는 제1 더미 렌즈들(DL1c), 제3 블로킹 바들(BB3c)을 둘러싸는 제2 더미 렌즈들(DL2c)을 포함할 수 있다.

제1 블로킹 바들(BB1c) 사이에 제1 갭들(GA1c)이 정의될 수 있고, 제2 블로킹 바들(BB2c) 사이에 제2 갭들(GA2c)이 정의될 수 있고, 제3 블로킹 바들(BB3c) 사이에 제3 갭들(GA3c)이 정의될 수 있다.

베이스부(231c)는 제1 블로킹 바들(BB1c) 및 제2 블로킹 바들(BB2c) 사이의 제1 플랫 상면(FS1c) 및 제2 블로킹 바들(BB2c) 및 제3 블로킹 바들(BB3c) 사이의 제2 플랫 상면(FS2c)을 포함할 수 있다. 제1 플랫 상면(FS1c)은 제1 및 제2 갭들(GA1c, GA2c)과 연결될 수 있다. 제2 플랫 상면(FS2c)은 제2 및 제3 갭들(GA2c, GA3c)과 연결될 수 있다.

도 7은 일부 실시예들에 따른 이미지 센서 패키지의 단면도이다.

도 7을 참조하면, 이미지 센서 패키지는 패키지 기판(410)을 포함할 수 있다. 패키지 기판(410)은 예를 들어 인쇄회로기판(Printed Circuit Board, PCB)일 수 있다.

패키지 기판(410)은 상부 패드들(430)을 포함할 수 있다. 상부 패드들(430)은 도전 물질을 포함할 수 있다. 패키지 기판(410) 아래에 외부 연결 단자들(420)이 제공될 수 있다. 외부 연결 단자(420)를 통해 이미지 센서 패키지가 외부 장치와 전기적으로 연결될 수 있다. 외부 연결 단자들(420)은 도전 물질을 포함할 수 있다.

패키지 기판(410) 상에 접착막(440)이 제공될 수 있다. 접착막(440)은 예를 들어 고분자 물질을 포함할 수 있다.

접착막(440) 상에 이미지 센서(450)가 제공될 수 있다. 이미지 센서(450)는 픽셀 어레이 영역(451), 옵티컬 블랙 영역(452) 및 패드 영역(453)을 포함할 수 있다. 이미지 센서(450)는 패드 영역(453) 내의 도전 패드(454)를 포함할 수 있다. 도전 패드(454)는 예를 들어 와이어를 통해 상부 패드(430)에 전기적으로 연결될 수 있다.

일부 실시예들에 있어서, 이미지 센서(450)는 센서 칩 및 회로 칩을 포함할 수 있고, 도전 패드(454)는 이미지 센서(450)의 센서 칩 및 회로 칩 사이에 제공되어 회로 칩에 직접 연결될 수 있다.

이미지 센서(450)의 픽셀 어레이 영역(451)에 마이크로 렌즈가 제공될 수 있다. 이미지 센서(450)의 옵티컬 블랙 영역(452)에 더미 렌즈 및 블로킹 바가 제공될 수 있다.

이미지 센서(450)의 패드 영역(453) 및 옵티컬 블랙 영역(452)의 일부 상에 댐 구조체(480)가 제공될 수 있다. 일부 실시예들에 있어서, 이미지 센서(450)는 패드 영역(453) 상에만 제공될 수도 있다. 댐 구조체(480)는 접착성 물질을 이용하여 이미지 센서(450)에 부착될 수 있다. 댐 구조체(480)에 의해 이미지 센서(450)의 픽셀 어레이 영역(451)이 노출될 수 있다. 댐 구조체(480)는 예를 들어 고분자 물질 또는 금속 중 적어도 하나를 포함할 수 있다. 평면적 관점에서, 댐 구조체(480)는 링의 형태를 가질 수 있다.

댐 구조체(480) 상에 투명 기판(490)이 제공될 수 있다. 투명 기판(490)은 높은 광 투과율을 가지는 물질을 포함할 수 있다. 예를 들어, 투명 기판(490)은 유리를 포함할 수 있다.

투명 기판(490), 댐 구조체(480) 및 이미지 센서(450)를 둘러싸는 몰딩막(470)이 제공될 수 있다. 몰딩막(470)은 예를 들어 고분자 물질을 포함할 수 있다.

일부 실시예들에 따른 이미지 센서 패키지는 이미지 센서(450)가 블로킹 바를 포함함에 따라, 댐 구조체(480)를 이미지 센서(450)에 부착하기 위한 접착성 물질이 픽셀 어레이 영역(451)으로 침투되는 것이 방지될 수 있고, 이미지 센서(450)의 감도가 저하되는 것이 방지될 수 있다.

도 8a 및 8b는 일부 실시예들에 따른 이미지 센서의 단면도이다.

도 8a 및 8b를 참조하면, 이미지 센서는 서브 칩(20d), 회로 칩(30d) 및 센서 칩(10d)을 포함할 수 있다. 회로 칩(30d) 상에 서브 칩(20d)이 제공될 수 있고, 서브 칩(20d) 상에 센서 칩(10d)이 제공될 수 있다. 센서 칩(10d)은 마이크로 렌즈들(231d), 더미 렌즈들(232d) 및 블로킹 바(233d)를 포함할 수 있다.

센서 칩(10d)은 제1 기판(100d) 및 제1 배선 절연막(130d)을 포함할 수 있다. 서브 칩(20d)은 제2 기판(300d) 및 제2 배선 절연막(310d)을 포함할 수 있다. 회로 칩(30d)은 제3 기판(500d) 및 제3 배선 절연막(510d)을 포함할 수 있다. 제1 배선 절연막(130d) 및 제2 배선 절연막(310d)은 서로 접할 수 있다. 제2 기판(300d) 및 제3 배선 절연막(510d)은 서로 접할 수 있다.

센서 칩(10d)은 서브 칩(20d)에 접하는 제1 본딩 패드(BP1)를 포함할 수 있다. 서브 칩(20d)은 제1 본딩 패드(BP1)에 접하는 제2 본딩 패드(BP2)를 포함할 수 있다. 센서 칩(10d) 및 서브 칩(20d)은 제1 및 제2 본딩 패드들(BP1, BP2)을 통해 전기적으로 연결될 수 있다. 제1 및 제2 본딩 패드들(BP1, BP2)은 예를 들어 구리를 포함할 수 있다.

서브 칩(20d)은 전자 소자(320d), 전자 소자(320d)에 연결되는 제1 컨택들(330d), 제1 도전 라인(340d)을 포함할 수 있다. 제1 컨택(330d)은 제1 도전 라인(340d) 또는 제2 본딩 패드(BP2)에 연결될 수 있다. 전자 소자(320d)는 선택 트랜지스터, 리셋 게이트 또는 소스 팔로워 게이트 중 적어도 하나를 포함할 수 있다. 제1 컨택(330d) 및 제1 도전 라인(340d)은 제2 배선 절연막(310d) 내에 제공될 수 있다.

회로 칩(30d)은 집적 회로(520d), 집적 회로(520d)에 연결되는 제2 컨택(530d) 및 제2 컨택(530d)에 연결되는 제2 도전 라인(540d)을 포함할 수 있다. 제2 컨택(530d) 및 제2 도전 라인(540d)은 제3 배선 절연막(510d) 내에 제공될 수 있다.

관통 비아(TV)가 제공될 수 있다. 관통 비아(TV)는 서브 칩(20d)의 제2 기판(300d)을 관통할 수 있다. 관통 비아(TV)는 제1 도전 라인(340d) 및 제2 도전 라인(540d)에 연결될 수 있다. 서브 칩(20d) 및 회로 칩(30d)은 관통 비아(TV)에 의해 전기적으로 연결될 수 있다. 관통 비아(TV)는 도전 물질을 포함할 수 있다.

도 9는 일부 실시예들에 따른 이미지 센서의 단면도이다.

도 9를 참조하면, 이미지 센서는 센서 칩(10e) 및 회로 칩(20e)을 포함할 수 있다. 센서 칩(10e)은 베이스부(231e), 더미 렌즈들(232e) 및 블로킹 바(233e)를 포함할 수 있다.

이미지 센서는 회로 칩(20e)에 직접 연결되는 도전 패드(210e)를 포함할 수 있다. 도전 패드(210e)는 리세스(RSe) 내에 제공될 수 있다. 리세스(RSe)는 센서 칩(10e)의 렌즈막(230e), 반사 방지막(150e), 고정 전하막(140e), 제1 기판(100e) 및 제1 배선 절연막(130e)을 관통하여 회로 칩(20e)의 제2 배선 절연막(310e) 내의 도전 구조체(CSe)를 노출시킬 수 있다. 도전 패드(210e)는 회로 칩(20e)의 제2 배선 절연막(310e) 내의 도전 구조체(CSe)에 직접 연결될 수 있다. 도전 패드(210e)는 도전 물질을 포함할 수 있다.

도전 구조체(CSe)는 도전 물질을 포함할 수 있다. 도전 구조체(CSe)는 도전 라인, 도전 컨택 또는 도전 패드일 수 있다.

이상의 발명의 상세한 설명은 개시된 실시 상태로 본 발명을 제한하려는 의도가 아니며, 본 발명의 요지를 벗어나지 않는 범위 내에서 다양한 다른 조합, 변경 및 환경에서 사용할 수 있다. 첨부된 청구범위는 다른 실시 상태도 포함하는 것으로 해석되어야 할 것이다.

Claims (20)

- 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판;

상기 픽셀 어레이 영역 위에 제공되는 마이크로 렌즈;

상기 옵티컬 블랙 영역 위에 제공되는 더미 렌즈; 및

상기 옵티컬 블랙 영역 위에 제공되는 블로킹 바를 포함하고,

상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고,

상기 블로킹 바의 상면은 굴곡진 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바는 상기 마이크로 렌즈를 둘러싸는 이미지 센서. - 제2 항에 있어서,

상기 블로킹 바는 상기 마이크로 렌즈를 둘러싸는 제1 블로킹 바 및 상기 제1 블로킹 바를 둘러싸는 제2 블로킹 바를 포함하는 이미지 센서. - 제3 항에 있어서,

상기 더미 렌즈는 상기 제1 블로킹 바에 의해 둘러싸이는 제1 더미 렌즈들 및 제1 및 제2 블로킹 바들 사이에 배치되는 제2 더미 렌즈들을 포함하는 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바의 상면의 곡률 반경은 상기 마이크로 렌즈의 상면의 곡률 반경과 동일한 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바의 폭은 상기 마이크로 렌즈의 폭과 동일한 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바는 제1 방향으로 연장하는 복수개의 블로킹 바들을 포함하고,

상기 블로킹 바들은 상기 제1 방향으로 배열되는 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바는 제1 블로킹 바들 및 상기 제1 블로킹 바들보다 상기 마이크로 렌즈에 멀리 배치되는 제2 블로킹 바들을 포함하고,

상기 제1 블로킹 바들은 제1 방향으로 배열되고,

상기 제2 블로킹 바들은 상기 제1 방향으로 배열되는 이미지 센서. - 제8 항에 있어서,

상기 제1 블로킹 바들 사이에 갭들이 정의되고,

상기 제1 블로킹 바들 각각의 길이는 상기 갭들 각각의 길이보다 큰 이미지 센서. - 제1 항에 있어서,

상기 블로킹 바의 최상부의 레벨은 상기 마이크로 렌즈의 최상부의 레벨과 동일한 이미지 센서. - 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판;

상기 픽셀 어레이 영역 위의 마이크로 렌즈;

상기 옵티컬 블랙 영역 위의 더미 렌즈; 및

상기 옵티컬 블랙 영역 위의 블로킹 바를 포함하고,

상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고,

상기 블로킹 바는 상기 마이크로 렌즈를 둘러싸는 이미지 센서. - 제11 항에 있어서,

상기 마이크로 렌즈, 상기 더미 렌즈 및 상기 블로킹 바에 연결되는 베이스부를 더 포함하는 이미지 센서. - 제12 항에 있어서,

상기 블로킹 바는 제1 블로킹 바 및 상기 제1 블로킹 바를 둘러싸는 제2 블로킹 바를 포함하고,

상기 베이스부는 상기 제1 블로킹 바 및 상기 제2 블로킹 바를 연결하는 플랫 상면을 포함하는 이미지 센서. - 제11 항에 있어서,

상기 블로킹 바는 제1 방향으로 연장하는 블로킹 바들을 포함하고,

상기 블로킹 바들은 상기 제1 방향으로 배열되고,

상기 블로킹 바들 사이에 갭이 제공되는 이미지 센서. - 제11 항에 있어서,

상기 마이크로 렌즈, 상기 더미 렌즈 및 상기 블로킹 바를 덮는 코팅막을 더 포함하는 이미지 센서. - 제11 항에 있어서,

상기 블로킹 바의 상면은 굴곡진 이미지 센서. - 제11 항에 있어서,

상기 블로킹 바의 폭은 상기 마이크로 렌즈의 폭과 동일한 이미지 센서. - 제11 항에 있어서,

상기 블로킹 바의 폭은 상기 마이크로 렌즈의 폭과 다른 이미지 센서. - 픽셀 어레이 영역 및 상기 픽셀 어레이 픽셀 영역을 둘러싸는 옵티컬 블랙 영역을 포함하는 기판;

상기 픽셀 어레이 영역 위의 컬러 필터;

상기 옵티컬 블랙 영역 위의 블랙 벌크 필터링막;

상기 컬러 필터 및 상기 블랙 벌크 필터링막 상의 렌즈막; 및

상기 렌즈막 상의 코팅막을 포함하고,

상기 렌즈막은,

베이스부;

상기 베이스부 상의 마이크로 렌즈;

상기 베이스부 상의 더미 렌즈; 및

상기 베이스부 상의 블로킹 바를 포함하고,

상기 블로킹 바의 길이는 상기 마이크로 렌즈의 길이 및 상기 더미 렌즈의 길이보다 길고,

상기 블로킹 바는 상기 마이크로 렌즈를 둘러싸고,

상기 블로킹 바의 상면은 굴곡진 이미지 센서. - 제19 항에 있어서,

상기 코팅막은 상기 마이크로 렌즈 상의 제1 부분, 상기 더미 렌즈 상의 제2 부분 및 상기 블로킹 바 상의 제3 부분을 포함하고,

상기 코팅막의 상기 제3 부분의 상면은 굴곡진 이미지 센서.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020220104084A KR20240025897A (ko) | 2022-08-19 | 2022-08-19 | 이미지 센서 |

| CN202310328788.8A CN117594616A (zh) | 2022-08-19 | 2023-03-23 | 图像传感器 |

| US18/300,009 US20240063243A1 (en) | 2022-08-19 | 2023-04-13 | Image sensor |

| JP2023068545A JP2024028099A (ja) | 2022-08-19 | 2023-04-19 | イメージセンサー |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020220104084A KR20240025897A (ko) | 2022-08-19 | 2022-08-19 | 이미지 센서 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20240025897A true KR20240025897A (ko) | 2024-02-27 |

Family

ID=89906105

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020220104084A KR20240025897A (ko) | 2022-08-19 | 2022-08-19 | 이미지 센서 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20240063243A1 (ko) |

| JP (1) | JP2024028099A (ko) |

| KR (1) | KR20240025897A (ko) |

| CN (1) | CN117594616A (ko) |

-

2022

- 2022-08-19 KR KR1020220104084A patent/KR20240025897A/ko unknown

-

2023

- 2023-03-23 CN CN202310328788.8A patent/CN117594616A/zh active Pending

- 2023-04-13 US US18/300,009 patent/US20240063243A1/en active Pending

- 2023-04-19 JP JP2023068545A patent/JP2024028099A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| JP2024028099A (ja) | 2024-03-01 |

| US20240063243A1 (en) | 2024-02-22 |

| CN117594616A (zh) | 2024-02-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10608031B2 (en) | Image sensor | |

| KR102699535B1 (ko) | 이미지 센서 | |

| CN101521216B (zh) | 固态成像装置和照相机 | |

| KR102638779B1 (ko) | 이미지 센서 | |

| US8614494B2 (en) | Solid-state imaging device, manufacturing method of the same and electronic apparatus | |

| KR20180016699A (ko) | 이미지 센서 | |

| US7511324B2 (en) | Solid-state imaging device | |

| US11631710B2 (en) | Image sensors | |

| CN101582436B (zh) | 固体摄像器件和电子装置 | |

| KR20090078552A (ko) | 화합물 반도체 수직 적층 이미지 센서 | |

| KR102637626B1 (ko) | 이미지 센서 | |

| KR20170094693A (ko) | 이미지 센서 | |

| CN114551485A (zh) | 图像传感器及其制造方法 | |

| KR100688589B1 (ko) | 필 팩터가 증대된 이미지 센서 및 그의 제조방법 | |

| KR20220087227A (ko) | 이미지 센서 | |

| US9991308B2 (en) | Image sensor | |

| US12068350B2 (en) | Complementary metal-oxide semiconductor (CMOS) image sensor | |

| KR20240025897A (ko) | 이미지 센서 | |

| KR20220047465A (ko) | 이미지 센서 및 그 제조 방법 | |

| US20090194835A1 (en) | Image sensor | |

| US20240250103A1 (en) | Image sensor | |

| US20240170522A1 (en) | Image sensors | |

| US20230282668A1 (en) | Image sensor | |

| US20240047488A1 (en) | Image sensor | |

| KR102722463B1 (ko) | 고체 촬상 장치, 촬상 장치 |