KR20180098172A - 알고리즘으로의 마스킹의 자동 삽입 - Google Patents

알고리즘으로의 마스킹의 자동 삽입 Download PDFInfo

- Publication number

- KR20180098172A KR20180098172A KR1020180022242A KR20180022242A KR20180098172A KR 20180098172 A KR20180098172 A KR 20180098172A KR 1020180022242 A KR1020180022242 A KR 1020180022242A KR 20180022242 A KR20180022242 A KR 20180022242A KR 20180098172 A KR20180098172 A KR 20180098172A

- Authority

- KR

- South Korea

- Prior art keywords

- call graph

- function

- variable

- computer

- mask

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/002—Countermeasures against attacks on cryptographic mechanisms

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/71—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information

- G06F21/75—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information by inhibiting the analysis of circuitry or operation

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/71—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information

- G06F21/75—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information by inhibiting the analysis of circuitry or operation

- G06F21/755—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information by inhibiting the analysis of circuitry or operation with measures against power attack

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/76—Arrangements for rearranging, permuting or selecting data according to predetermined rules, independently of the content of the data

- G06F7/764—Masking

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/002—Countermeasures against attacks on cryptographic mechanisms

- H04L9/003—Countermeasures against attacks on cryptographic mechanisms for power analysis, e.g. differential power analysis [DPA] or simple power analysis [SPA]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/008—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols involving homomorphic encryption

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/06—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols the encryption apparatus using shift registers or memories for block-wise or stream coding, e.g. DES systems or RC4; Hash functions; Pseudorandom sequence generators

- H04L9/0618—Block ciphers, i.e. encrypting groups of characters of a plain text message using fixed encryption transformation

- H04L9/0631—Substitution permutation network [SPN], i.e. cipher composed of a number of stages or rounds each involving linear and nonlinear transformations, e.g. AES algorithms

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/72—Indexing scheme relating to groups G06F7/72 - G06F7/729

- G06F2207/7219—Countermeasures against side channel or fault attacks

- G06F2207/7223—Randomisation as countermeasure against side channel attacks

- G06F2207/7233—Masking, e.g. (A**e)+r mod n

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/72—Indexing scheme relating to groups G06F7/72 - G06F7/729

- G06F2207/7219—Countermeasures against side channel or fault attacks

- G06F2207/7223—Randomisation as countermeasure against side channel attacks

- G06F2207/7233—Masking, e.g. (A**e)+r mod n

- G06F2207/7238—Operand masking, i.e. message blinding, e.g. (A+r)**e mod n; k.(P+R)

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/04—Masking or blinding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/04—Masking or blinding

- H04L2209/046—Masking or blinding of operations, operands or results of the operations

Landscapes

- Engineering & Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Theoretical Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Mathematical Physics (AREA)

- Devices For Executing Special Programs (AREA)

- Stored Programmes (AREA)

- Storage Device Security (AREA)

Abstract

- 호출 그래프의 각각의 입력을 마스킹하는 단계,

- 호출 그래프의 각각의 마스킹되지 않은 내부 변수를 마스킹된 변수로 대체하는 단계,

- 호출 그래프의 적어도 각각의 비선형 함수를, 마스킹된 변수에 적용되는 등가 함수로 대체하는 단계,

- 호출 그래프의 각각의 출력을 마스킹 해제하는 단계.

Description

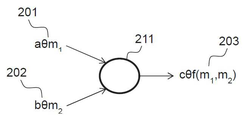

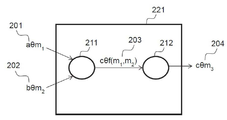

- 도 1a는 종래 기술로부터 알려져 있는 바와 같은 보호되지 않은 호출 그래프를 나타낸 도면,

- 도 1b 및 도 1c는, 본 발명의 두 실시형태에 따라 보호되어, 유익하게도, 그래프의 반복 부분의 입력 및 출력으로서 사용되는 변수에 적용되는 마스크의 일관성을 특히 보장하게 되는 호출 그래프를 나타낸 도면,

- 도 2a 및 도 2b는 선형 함수를 프로세싱하는 두 가지 방식을 예시한 도면,

- 도 3은, 마스킹된 입력 및 출력을 고려하여, 상기 비선형 함수와 등가의 매치 테이블을 구성하는 것에 의해, 비선형 함수를 프로세싱하는 하나의 방식을 예시한 도면,

- 도 4a는, 반복 부분이 예시의 목적을 위해 전개된 보호되지 않은 호출 그래프를 나타낸 도면,

- 도 4b 및 도 4c는 본 발명의 두 실시형태에 따라 보호되는 호출 그래프를 나타낸 도면으로, 호출 그래프의 반복 부분에서 사용되는 내부 변수의 마스크는 각각의 반복에서 수정되고, 반복 부분은 예시의 목적을 위해 전개되어 있음,

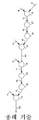

- 도 5a는 AES 알고리즘의 전형적인 호출 그래프 표현이고, 도 5b는 본 발명의 하나의 실시형태에 따라 생성되는 대응하는 보호된 호출 그래프,

- 도 6은 소정의 실시형태에 따른 컴퓨터 구현 방법을 묘사하는 플로우차트, 및

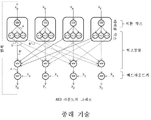

- 도 7은 본 발명을 프로세싱하기 위해 사용될 수 있는 시스템을 예시한 도면.

본 명세서에서 개시되는 예는 단지 본 발명의 몇몇 실시형태의 예시에 불과하다. 그들은 첨부된 청구범위에 의해 정의되는 본 발명의 범위를 어떤 식으로든 제한하지는 않는다.

Claims (12)

- 알고리즘의 호출 그래프 표현(call graph representation)을 상기 알고리즘의 보안 호출 그래프 표현(secured call graph representation)으로 변환하기 위한 컴퓨터 구현 방법으로서,

상기 호출 그래프는 적어도 하나의 입력(a, b, f), 적어도 하나의 에지(c, d, e), 적어도 하나의 노드(P, Q, R, S) 및 적어도 하나의 출력(g)을 포함하고, 상기 호출 그래프의 상기 에지는 상기 알고리즘의 내부 변수를 나타내고, 상기 호출 그래프의 상기 노드는 상기 알고리즘의 선형 또는 비선형 기본 함수를 나타내고, 상기 컴퓨터 구현 방법은,

- 상기 호출 그래프의 각각의 입력을 마스킹하는 단계(601),

- 상기 호출 그래프의 각각의 마스킹되지 않은(unmasked) 내부 변수를 마스킹된 변수로 대체하는 단계(602),

- 상기 호출 그래프의 적어도 각각의 비선형 함수를, 마스킹된 변수에 적용되는 등가 함수로 대체하는 단계(603),

- 상기 호출 그래프의 각각의 출력을 마스킹 해제하는(unmasking) 단계(604)를 포함하는, 컴퓨터 구현 방법. - 제1항에 있어서, 상기 호출 그래프는 반복적으로 프로세싱되는 부분을 포함하고, 상기 마스킹되지 않은 내부 변수를 마스킹된 내부 변수에 의해 대체하는 단계(602)는, 반복적으로 프로세싱되는 상기 호출 그래프의 부분의 입력 및 출력 둘 다로서 사용되는 내부 변수(b, g)를 식별하는 단계, 및 상기 호출 그래프의 상기 부분의 입력 및 출력에서 이들 변수에 대해 동일한 마스크(m2)를 사용하는 단계를 포함하는, 컴퓨터 구현 방법.

- 제1항에 있어서, 상기 호출 그래프는 반복적으로 프로세싱되는 부분을 포함하고, 상기 마스킹되지 않은 내부 변수를 마스킹된 내부 변수에 의해 대체하는 단계(602)는, 반복적으로 프로세싱되는 상기 호출 그래프의 부분의 입력 및 출력 둘 다로서 사용되는 내부 변수(b, g)를 식별하는 단계, 및 상기 내부 변수의 마스크를 수정하기 위한 추가 노드(120)를 상기 반복 부분의 피드백 에지에 삽입하는 단계를 포함하는, 컴퓨터 구현 방법.

- 제1항 내지 제3항 중 어느 한 항에 있어서, 반복적으로 프로세싱되는 상기 호출 그래프의 부분에서의 내부 변수의 상기 마스크는 규칙적인 간격으로 변경되고, 관련된 함수가 상응하게 수정되는, 컴퓨터 구현 방법.

- 제4항에 있어서, 상기 반복 부분의 상기 내부 변수의 상기 마스크를 리프레쉬하기 위한 추가 노드(402)를 상기 호출 그래프에 삽입하는 단계를 더 포함하는, 컴퓨터 구현 방법.

- 제1항 내지 제5항 중 어느 한 항에 있어서, 상기 호출 그래프의 적어도 각각의 비선형 함수를, 마스킹된 변수에 적용되는 등가 함수로 대체하는 단계(603)에서 계산되는 등가 함수는 매치 테이블(match table)을 사용하여 구현되는, 컴퓨터 구현 방법.

- 제1항 내지 제6항 중 어느 한 항에 있어서, 상기 호출 그래프의 적어도 각각의 비선형 함수를, 마스킹된 변수에 적용되는 등가 함수로 대체하는 단계(603)는, 상기 호출 그래프의 각각의 선형 함수를, 상기 입력 및 출력 내부 변수의 마스크를 고려하는 등가 함수에 의해 대체하는 단계를 더 포함하는, 컴퓨터 구현 방법.

- 제1항 내지 제7항 중 어느 한 항에 있어서, 모든 마스크 값은 랜덤하게 결정되는, 컴퓨터 구현 방법.

- 제1항 내지 제8항 중 어느 한 항에 있어서, 보호된 실행 가능 코드를 생성하도록 상기 호출 그래프를 컴파일하는 추가 단계를 더 포함하는, 컴퓨터 구현 방법.

- 컴퓨터 시스템으로 하여금 제1항 내지 제9항 중 어느 한 항에 따른 방법을 수행하게 하기 위한 컴퓨터 실행 가능 명령어를 포함하는, 비휘발성 컴퓨터 판독 가능 데이터 저장 매체 상에 저장되는 컴퓨터 프로그램 제품.

- 컴퓨터 시스템으로 하여금 제1항 내지 제9항 중 어느 한 항에 따른 방법을 수행하게 하기 위한 컴퓨터 실행 가능 명령어를 포함하는 비휘발성 컴퓨터 판독 가능 데이터 저장 매체.

- 메모리에 커플링되는 프로세서를 포함하는 시스템으로서,

상기 메모리는, 상기 시스템으로 하여금 알고리즘의 호출 그래프 표현을 상기 알고리즘의 보안 호출 그래프 표현으로 변환하기 위한 컴퓨터 구현 방법을 수행하게 하기 위한 컴퓨터 실행가능 명령어를 저장하고, 상기 호출 그래프는 적어도 하나의 입력, 적어도 하나의 에지(c, d, e), 적어도 하나의 노드(P, Q, R, S) 및 적어도 하나의 출력(g)을 포함하며, 상기 호출 그래프의 상기 에지는 상기 알고리즘의 내부 변수를 나타내고, 상기 호출 그래프의 상기 노드는 상기 알고리즘의 선형 또는 비선형 기본 함수를 나타내며, 상기 시스템은 상기 프로세싱 디바이스를 포함하고, 상기 프로세싱 디바이스는,

- 상기 호출 그래프의 각각의 입력을 마스킹하도록,

- 상기 호출 그래프의 각각의 마스킹되지 않은 내부 변수를 마스킹된 변수로 대체하도록,

- 상기 호출 그래프의 적어도 각각의 비선형 함수를, 상기 마스킹된 변수에 적용되는 등가 함수에 의해 대체하도록, 그리고

- 상기 호출 그래프의 각각의 출력을 마스킹 해제하도록

구성되는, 메모리에 커플링되는 프로세서를 포함하는 시스템.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP17305202.8 | 2017-02-24 | ||

| EP17305202.8A EP3367606B1 (en) | 2017-02-24 | 2017-02-24 | Automatic insertion of masking into an algorithm |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180098172A true KR20180098172A (ko) | 2018-09-03 |

| KR102049656B1 KR102049656B1 (ko) | 2019-11-28 |

Family

ID=58709897

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020180022242A Active KR102049656B1 (ko) | 2017-02-24 | 2018-02-23 | 알고리즘으로의 마스킹의 자동 삽입 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US10735179B2 (ko) |

| EP (1) | EP3367606B1 (ko) |

| KR (1) | KR102049656B1 (ko) |

| CN (1) | CN108512645B (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3624390A1 (en) * | 2018-09-17 | 2020-03-18 | Secure-IC SAS | Devices and methods for protecting cryptographic programs |

| US11042634B2 (en) * | 2018-12-21 | 2021-06-22 | Fujitsu Limited | Determining information leakage of computer-readable programs |

| US11507699B2 (en) * | 2019-09-27 | 2022-11-22 | Intel Corporation | Processor with private pipeline |

| US11632231B2 (en) * | 2020-03-05 | 2023-04-18 | Novatek Microelectronics Corp. | Substitute box, substitute method and apparatus thereof |

| US11652721B2 (en) * | 2021-06-30 | 2023-05-16 | Capital One Services, Llc | Secure and privacy aware monitoring with dynamic resiliency for distributed systems |

| US11934327B2 (en) * | 2021-12-22 | 2024-03-19 | Microsoft Technology Licensing, Llc | Systems and methods for hardware acceleration of data masking using a field programmable gate array |

| US20240364497A1 (en) * | 2023-04-28 | 2024-10-31 | Cryptography Research, Inc. | Protection of secret data using unprotected data path |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8091139B2 (en) * | 2007-11-01 | 2012-01-03 | Discretix Technologies Ltd. | System and method for masking arbitrary Boolean functions |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6594761B1 (en) * | 1999-06-09 | 2003-07-15 | Cloakware Corporation | Tamper resistant software encoding |

| CN101364203A (zh) * | 2008-09-19 | 2009-02-11 | 南京大学 | 一种面向隐蔽通道分析的系统分析和划分方法 |

| FR2950721B1 (fr) * | 2009-09-29 | 2011-09-30 | Thales Sa | Procede d'execution d'un algorithme de protection d'un dispositif electronique par masquage affine et dispositif associe |

| WO2011056081A2 (en) * | 2009-11-09 | 2011-05-12 | Exergy Limited | System and method for maximising thermal efficiency of a power plant |

| US9230455B2 (en) * | 2009-12-11 | 2016-01-05 | Digital Immunity Llc | Steganographic embedding of executable code |

| US8971526B2 (en) * | 2011-07-26 | 2015-03-03 | Crocus-Technology Sa | Method of counter-measuring against side-channel attacks |

| US9424038B2 (en) * | 2012-12-10 | 2016-08-23 | Nvidia Corporation | Compiler-controlled region scheduling for SIMD execution of threads |

| US9721120B2 (en) * | 2013-05-14 | 2017-08-01 | Apple Inc. | Preventing unauthorized calls to a protected function |

| CN103279414B (zh) * | 2013-05-23 | 2016-04-20 | 北京大学 | 一种适用于Xen虚拟化平台的隐蔽通道检测方法 |

| US9158604B1 (en) * | 2014-05-13 | 2015-10-13 | Qualcomm Incorporated | Lightweight data-flow tracker for realtime behavioral analysis using control flow |

-

2017

- 2017-02-24 EP EP17305202.8A patent/EP3367606B1/en active Active

-

2018

- 2018-02-16 US US15/898,327 patent/US10735179B2/en active Active

- 2018-02-23 KR KR1020180022242A patent/KR102049656B1/ko active Active

- 2018-02-23 CN CN201810155080.6A patent/CN108512645B/zh active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8091139B2 (en) * | 2007-11-01 | 2012-01-03 | Discretix Technologies Ltd. | System and method for masking arbitrary Boolean functions |

Non-Patent Citations (1)

| Title |

|---|

| Alexander DeTrano et. al., "Exploiting small leakages in masks to turn a second-order attack into a first-order attack and improved rotating substitution box masking with linear code cosets", Hindawi Publishing Corporation, The Scientific World Journal (2015.)* * |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3367606A1 (en) | 2018-08-29 |

| EP3367606B1 (en) | 2019-09-18 |

| US10735179B2 (en) | 2020-08-04 |

| CN108512645A (zh) | 2018-09-07 |

| KR102049656B1 (ko) | 2019-11-28 |

| US20180248682A1 (en) | 2018-08-30 |

| CN108512645B (zh) | 2021-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102049656B1 (ko) | 알고리즘으로의 마스킹의 자동 삽입 | |

| EP4371023B1 (en) | Cryptographic system for post-quantum cryptographic operations | |

| Coron et al. | Conversion from arithmetic to boolean masking with logarithmic complexity | |

| Moss et al. | Compiler assisted masking | |

| US8918768B2 (en) | Methods and apparatus for correlation protected processing of data operations | |

| CN105453481B (zh) | 包括表网络的计算设备 | |

| JP7242675B2 (ja) | コンパイル装置及び方法 | |

| JP7132926B2 (ja) | コンパイルデバイス及びコンパイル方法 | |

| CN111819542B (zh) | 编译设备和方法 | |

| US20130259226A1 (en) | Methods and apparatus for correlation protected processing of cryptographic operations | |

| US8707053B2 (en) | Performing boolean logic operations using arithmetic operations by code obfuscation | |

| CN108141352A (zh) | 密码设备和编码设备 | |

| WO2018115143A1 (en) | A calculation device for encoded addition | |

| CN105765896B (zh) | 用于表格网络的迭代应用的计算设备 | |

| JP6919973B2 (ja) | プログラムコードのコンピュータ支援難読化方法 | |

| Vandersmissen et al. | A white-box speck implementation using self-equivalence encodings | |

| US8862896B2 (en) | Data protection using key translation | |

| CN111602367B (zh) | 用于保护在使白盒密码算法安全的对策中使用的熵源的方法 | |

| Cui et al. | A Generalized Obfuscation Method to Protect Software of Mobile Apps | |

| Liu et al. | Automated Verification of Correctness for Masked Arithmetic Programs | |

| Vandersmissen et al. | A white-box speck implementation using self-equivalence encodings (full version) | |

| Amro | Distributed Obfuscation Model for Software Protection (DOSP) | |

| Tropnikova et al. | System for Protecting Executable Files of the Java Programming Language | |

| EP4533730A1 (en) | Secure processing system and method | |

| Löfström et al. | Hiding Information in Software With Respect to a White-box Security Model |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| U11 | Full renewal or maintenance fee paid |

Free format text: ST27 STATUS EVENT CODE: A-4-4-U10-U11-OTH-PR1001 (AS PROVIDED BY THE NATIONAL OFFICE) Year of fee payment: 7 |