KR20160100665A - 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 - Google Patents

길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 Download PDFInfo

- Publication number

- KR20160100665A KR20160100665A KR1020150023409A KR20150023409A KR20160100665A KR 20160100665 A KR20160100665 A KR 20160100665A KR 1020150023409 A KR1020150023409 A KR 1020150023409A KR 20150023409 A KR20150023409 A KR 20150023409A KR 20160100665 A KR20160100665 A KR 20160100665A

- Authority

- KR

- South Korea

- Prior art keywords

- bit

- codeword

- ldpc

- interleaving

- length

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2792—Interleaver wherein interleaving is performed jointly with another technique such as puncturing, multiplexing or routing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

- H03M13/1165—QC-LDPC codes as defined for the digital video broadcasting [DVB] specifications, e.g. DVB-Satellite [DVB-S2]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/118—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

- H03M13/255—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM] with Low Density Parity Check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2778—Interleaver using block-wise interleaving, e.g. the interleaving matrix is sub-divided into sub-matrices and the permutation is performed in blocks of sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/61—Aspects and characteristics of methods and arrangements for error correction or error detection, not provided for otherwise

- H03M13/615—Use of computational or mathematical techniques

- H03M13/616—Matrix operations, especially for generator matrices or check matrices, e.g. column or row permutations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6522—Intended application, e.g. transmission or communication standard

- H03M13/6552—DVB-T2

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Multimedia (AREA)

- Computer Networks & Wireless Communication (AREA)

- General Physics & Mathematics (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Algebra (AREA)

- Computing Systems (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Abstract

비트 인터리버, BICM 장치 및 비트 인터리빙 방법이 개시된다. 본 발명의 일실시예에 따른 비트 인터리버는 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장하는 제1 메모리; 상기 LDPC 부호어를, 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성하는 프로세서; 및 상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 제공하는 제2 메모리를 포함한다.

Description

본 발명은 인터리버(interleaver)에 관한 것으로, 특히 디지털 방송 채널에서 발생한 군집오류(burst error)를 분산시키기 위한 비트 인터리버에 관한 것이다.

BICM(Bit-Interleaved Coded Modulation)은 대역-효율적인(bandwidth-efficient) 전송기술로 오류정정부호기(error-correction coder), 비트단위 인터리버(bit-by-bit interleaver) 및 높은 차수의 변조기(modulator)가 결합된 형태이다.

BICM은 오류정정부호기로 LDPC(Low-Density Parity Check) 부호기 또는 터보 부호기를 이용함으로써, 간단한 구조로 뛰어난 성능을 제공할 수 있다. 또한, BICM은 변조 차수(modulation order)와 오류정정부호의 길이 및 부호율 등을 다양하게 선택할 수 있기 때문에, 높은 수준의 플렉서빌러티(flexibility)를 제공한다. 이와 같은 장점 때문에, BICM은 DVB-T2나 DVB-NGH 와 같은 방송표준에서 사용되고 있을 뿐만 아니라 다른 차세대 방송시스템에서도 사용될 가능성이 높다.

이와 같은 장점에도 불구하고, BICM은 채널에서 발생한 군집오류(burst errors)를 비트 단위 인터리버를 통해 적절히 분산시키지 못하면, 그 성능이 급격하게 열화된다. 따라서, BICM에 사용되는 비트단위 인터리버는 변조차수나 오류정정부호의 길이 및 부호율 등에 최적화되어 설계되어야 한다.

본 발명의 목적은 방송 시스템 채널에서 발생한 군집오류(burst errors)를 효과적으로 분산시킬 수 있는 BICM 내부의 비트 인터리버를 제공하는 것이다.

또한, 본 발명의 목적은 길이가 64800이고 부호율이 2/15인 LDPC 부호기 및 256-심볼 맵핑(symbol mapping)을 수행하는 변조기에 최적화되어 ATSC 3.0 등 차세대 방송시스템에 적용될 수 있는 비트 인터리버를 제공하는 것이다.

상기한 목적을 달성하기 위한 본 발명에 따른 비트 인터리버는 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장하는 제1 메모리; 상기 LDPC 부호어를, 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성하는 프로세서; 및 상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 제공하는 제2 메모리를 포함한다.

이 때, 256-심볼 맵핑은 256개의 컨스틸레이션들을 가지는 NUC(Non-Uniform Constellation) 심볼 맵핑일 수 있다.

이 때, 패러럴 팩터는 360이고, 상기 비트그룹은 360비트들을 포함할 수 있다.

이 때, LDPC 부호어는 부호어는 (N ldpc 는 64800)와 같이 표현되고, 하기 수학식 9와 같이 각각 360개의 비트들로 구성된 180개의 비트그룹들로 분할될 수 있다.

[수학식 9]

(X j 는 j번째 비트그룹, N ldpc 는 64800, N group 은 180)

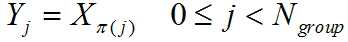

이 때, 인터리빙은 퍼뮤테이션 오더(permutation order)를 이용한 하기 수학식 10을 이용하여 수행될 수 있다.

[수학식 10]

(X j 는 j번째 비트그룹, Y j 는 인터리빙된 j번째 비트그룹, π(j)는 비트그룹 단위 인터리빙을 위한 퍼뮤테이션 오더)

이 때, 퍼뮤테이션 오더는 하기 수학식 11에 의하여 표현되는 인터리빙 시퀀스에 상응하는 것일 수 있다.

[수학식 11]

인터리빙 시퀀스

={112 78 104 6 59 80 49 120 114 27 113 3 109 44 69 164 91 137 39 31 21 127 151 8 47 176 117 68 122 148 79 73 7 166 51 50 116 66 152 61 29 107 22 154 118 94 24 35 55 38 88 54 2 15 19 67 101 74 169 138 41 162 175 136 62 161 121 163 115 135 123 25 140 156 58 33 119 111 146 129 150 147 97 18 60 4 81 168 43 105 36 65 13 5 108 145 23 70 20 173 159 100 128 172 170 1 37 83 102 103 157 139 179 32 144 92 131 75 155 14 9 149 63 11 134 53 99 17 57 90 30 98 64 40 87 158 77 93 124 46 171 141 133 85 177 132 26 160 42 34 82 96 48 10 142 125 178 153 72 45 89 52 28 126 143 167 76 86 130 110 174 16 165 56 84 95 0 106 12 71}

또한, 본 발명에 따른 비트 인터리빙 방법은 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장하는 단계; 상기 LDPC 부호어를 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성하는 단계; 및 상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 출력하는 단계를 포함한다.

또한, 본 발명에 따른 BICM 장치는 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 출력하는 오류정정 부호화기; 상기 LDPC 부호어를 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 출력하는 비트 인터리버; 및 상기 인터리빙된 부호어를 256-심볼 맵핑하는 변조기를 포함한다.

본 발명에 따르면, 방송 시스템 채널에서 발생한 군집오류(burst errors)를 효과적으로 분산시킬 수 있는 BICM 내부의 비트 인터리버가 제공된다.

또한, 본 발명은 길이가 64800이고 부효율이 2/15인 LDPC 부호기 및 256-심볼 맵핑을 수행하는 변조기에 최적화되어 ATSC 3.0 등 차세대 방송시스템에 적용될 수 있는 비트 인터리버가 제공된다.

도 1은 본 발명의 일실시예에 따른 방송 신호 송/수신 시스템을 나타낸 블록도이다.

도 2는 본 발명의 일실시예에 따른 방송 신호 송/수신 방법을 나타낸 동작 흐름도이다.

도 3은 본 발명의 일실시예에 따른 LDPC 부호에 상응하는 패러티 검사 행렬의 구조를 나타낸 도면이다.

도 4는 길이가 64800인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 5는 길이가 16200인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 6은 인터리빙 시퀀스에 따른 비트 그룹들 단위의 인터리빙을 나타낸 도면이다.

도 7은 본 발명의 일실시예에 따른 비트 인터리버를 나타낸 블록도이다.

도 8은 본 발명의 일실시예에 따른 비트 인터리빙 방법을 나타낸 동작 흐름도이다.

도 2는 본 발명의 일실시예에 따른 방송 신호 송/수신 방법을 나타낸 동작 흐름도이다.

도 3은 본 발명의 일실시예에 따른 LDPC 부호에 상응하는 패러티 검사 행렬의 구조를 나타낸 도면이다.

도 4는 길이가 64800인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 5는 길이가 16200인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 6은 인터리빙 시퀀스에 따른 비트 그룹들 단위의 인터리빙을 나타낸 도면이다.

도 7은 본 발명의 일실시예에 따른 비트 인터리버를 나타낸 블록도이다.

도 8은 본 발명의 일실시예에 따른 비트 인터리빙 방법을 나타낸 동작 흐름도이다.

본 발명을 첨부된 도면을 참조하여 상세히 설명하면 다음과 같다. 여기서, 반복되는 설명, 본 발명의 요지를 불필요하게 흐릴 수 있는 공지 기능, 및 구성에 대한 상세한 설명은 생략한다. 본 발명의 실시형태는 당 업계에서 평균적인 지식을 가진 자에게 본 발명을 보다 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있다.

이하, 본 발명에 따른 바람직한 실시예를 첨부된 도면을 참조하여 상세하게 설명한다.

도 1은 본 발명의 일실시예에 따른 방송 신호 송/수신 시스템을 나타낸 블록도이다.

도 1을 참조하면, BICM 장치(10)와 BICM 수신 장치(30)가 무선 채널(20)을 매개로 통신을 수행하는 것을 알 수 있다.

BICM 장치(10)는 k비트의 정보 비트들(information bits; 11)을 오류정정 부호화기(13)에서 부호화(encoding)하여 n비트의 부호어(codeword)를 생성한다. 이 때, 오류정정 부호화기(13)는 LDPC 부호화기 또는 터보 부호화기 등일 수 있다.

부호어는 비트 인터리버(14)에 의하여 인터리빙되어 인터리빙된 부호어가 생성된다.

이 때, 인터리빙은 비트그룹 단위로 수행될 수 있다. 이 때, 오류정정 부호화기(13)는 길이가 64800이고 부호율이 2/15인 LDPC 부호화기일 수 있고, 길이 64800의 부호어는 총 180개의 비트그룹들로 구분될 수 있고, 비트그룹들 각각은 LDPC 부호어의 패러럴 팩터(parallel factor)인 360개의 비트들을 포함할 수 있다.

이 때, 인터리빙은 후술할 인터리빙 시퀀스에 상응하여 비트그룹 단위로 수행될 수 있다.

이 때, 비트 인터리버(14)는 채널에서 발생한 군집오류를 효과적으로 분산시켜서 오류정정부호의 성능열화를 방지한다. 이 때, 비트 인터리버(14)는 오류정정부호의 길이 및 부호율, 그리고 변조차수에 따라서 개별적으로 설계될 수 있다.

인터리빙된 부호어는 변조기(15)에 의해 변조되어 안테나(17)를 통해 전송된다.

이 때, 변조기(15)는 심볼 맵핑장치를 포함하는 개념이다. 이 때, 변조기(15)는 256개의 컨스틸레이션(constellation)들에 코드들을 맵핑하는 256-심볼 맵핑을 수행하는 심볼 맵핑 장치일 수 있다.

이 때, 변조기(15)는 QAM(Quadrature Amplitude Modulation) 변조기 등의 균등(uniform) 변조기일 수도 있고, 비균등(non-uniform) 변조기일 수도 있다.

특히, 변조기(15)는 256개의 컨스틸레이션(constellation)들을 가지는 NUC(Non-Uniform Constellation) 심볼맵핑을 수행하는 심볼 맵핑 장치일 수 있다.

무선 채널(20)을 통해 전송된 신호는 BICM 수신 장치(30)의 안테나(31)를 통해 수신되고, BICM 수신 장치(30)에서는 BICM 장치(10)에서 일어났던 과정의 역과정을 거친다. 즉, 수신된 데이터가 복조기(33)에 의해 복조되고, 비트 디인터리버(34)에 의해 디인터리빙되고, 오류정정 복호화기(35)에 의해 복호되어 최종적으로 정보 비트들을 복원할 수 있다.

전술한 바와 같은 송/수신 과정은 본 발명의 특징을 설명하기 위해 필요한 최소한의 범위 내에서 설명된 것으로 이외에도 데이터 전송을 위해 필요한 많은 과정이 추가될 수 있음은 당업자에게 자명하다.

도 2는 본 발명의 일실시예에 따른 방송 신호 송/수신 방법을 나타낸 동작 흐름도이다.

도 2를 참조하면, 본 발명의 일실시예에 따른 방송 신호 송/수신 방법은 먼저 입력 비트들(information bits)을 오류정정 부호화한다(S210).

즉, 단계(S210)는 k비트의 정보 비트들(information bits)을 오류정정 부호화기에서 부호화하여 n비트의 부호어(codeword)를 생성한다.

이 때, 단계(S210)는 후술할 LDPC 부호화 방법과 같이 수행될 수 있다.

또한, 방송 신호 송/수신 방법은 n비트의 부호어를 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성한다(S220).

이 때, n비트의 부호어는 길이가 64800이고 부호율이 2/15인 LDPC 부호어일 수 있고, 길이 64800의 부호어는 총 180개의 비트그룹들로 구분될 수 있고, 비트그룹들 각각은 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 360개의 비트들을 포함할 수 있다.

이 때, 인터리빙은 후술할 인터리빙 시퀀스에 상응하여 비트그룹 단위로 수행될 수 있다.

또한, 방송 신호 송/수신 방법은 부호화된 데이터를 변조한다(S230).

즉, 단계(S230)는 인터리빙된 부호어를 변조기에 의해 변조한다.

이 때, 변조기는 심볼 맵핑장치를 포함하는 개념이다. 이 때, 변조기는 256개의 컨스틸레이션(constellation)들에 코드들을 맵핑하는 256-심볼 맵핑을 수행하는 심볼 맵핑 장치일 수 있다.

이 때, 변조기는 QAM(Quadrature Amplitude Modulation) 변조기 등의 균등(uniform) 변조기일 수도 있고, 비균등(non-uniform) 변조기일 수도 있다.

특히, 변조기는 256개의 컨스틸레이션(constellation)들을 가지는 NUC(Non-Uniform Constellation) 심볼맵핑을 수행하는 심볼 맵핑 장치일 수 있다.

또한, 방송 신호 송/수신 방법은 변조된 데이터를 송신한다(S240).

즉, 단계(S240)는 변조된 부호어를 안테나를 통해 무선 채널로 전송한다.

또한, 방송 신호 송/수신 방법은 수신된 데이터를 복조(demodulation)한다(S250).

즉, 단계(S250)는 수신기의 안테나를 통해 무선 채널을 통해 전송된 신호를 수신하고 수신된 데이터를 복조기에 의하여 복조한다.

또한, 방송 신호 송/수신 방법은 복조된 데이터를 디인터리빙한다(S260). 이 때, 단계(S260)의 디인터리빙은 단계(S220)의 역과정에 해당하는 것일 수 있다.

또한, 방송 신호 송/수신 방법은 디인터리빙된 부호어를 오류정정 복호화한다(S270).

즉, 단계(S270)는 수신기의 오류정정 복호기를 통해 오류정정 복호화를 수행하여 최종적으로 정보 비트들을 복원한다.

이 때, 단계(S270)는 후술할 LDPC 부호화 방법의 역과정에 해당하는 것일 수 있다.

LDPC(Low Density Parity Check) 부호는 AWGN(Additive White Gaussian Noise) 채널에서 쉐넌(Shannon) 한계에 근접하는 부호로 알려져 있으며, 터보부호보다 근사적으로(asymptotically) 우수한 성능, 병렬복호(parallelizable decoding) 등의 장점이 있다.

일반적으로, LDPC 부호는 랜덤하게 생성된 낮은 밀도의 PCM(Parity Check Matrix)에 의해 정의된다. 그러나, 랜덤하게 생성된 LDPC 부호는 PCM을 저장하기 위해 많은 메모리가 필요할 뿐만 아니라, 메모리를 액세스하는데 많은 시간이 소요된다. 이와 같은 문제를 해결하기 위해 쿼시-사이클릭(Quasi-cyclic) LDPC(QC-LDPC) 부호가 제안되었으며, 제로 메트릭스(zero matrix) 또는 CPM(Circulant Permutation Matrix)으로 구성된 QC-LDPC 부호는 하기 수학식 1에 의해 표현되는 PCM에 의해 정의된다.

[수학식 1]

여기서, J는 크기가 L x L인 CPM이며 하기 수학식 2와 같이 주어진다. 이하에서, L은 360일 수 있다.

[수학식 2]

또한, Ji는 L x L 항등행렬(identity matrix) I(=J0)를 오른쪽으로 i(0=i<L)번 이동시킨 것이며, J∞는 L x L 영행렬(zero matrix)이다. 따라서, QC-LDPC 부호에서는 Ji를 저장하기 위해 지수(exponent) i만 저장하면 되기 때문에, PCM를 저장하기 위해 요구되는 메모리가 크게 줄어든다.

도 3은 본 발명의 일실시예에 따른 LDPC 부호에 상응하는 패러티 검사 행렬의 구조를 나타낸 도면이다.

도 3을 참조하면, 행렬 A와 C의 크기는 각각 g x K와 (N-K-g) x (K+g)이며, 크기가 L x L인 영행렬과 CPM으로 구성된다. 또한, 행렬 z는 크기가 g x (N-K-g)인 영행렬이고, 행렬 D는 크기가 (N-K-g) x (N-K-g)인 항등행렬(identity matrix)이며, 행렬 B는 크기가 g x g인 이중 대각행렬(dual diagonal matrix)이다. 이 때, 행렬 B는 대각선의 원소와 대각선의 아래쪽에 이웃하는 원소들 이외의 모든 원소들이 모두 0인 행렬일 수도 있고, 하기 수학식 3과 같이 정의될 수도 있다.

[수학식 3]

여기서, ILxL는 크기가 L x L인 항등행렬이다.

즉, 행렬 B는 일반적인(bit-wise) 이중 대각행렬일 수도 있고, 상기 수학식 3에 표기된 바와 같이 항등행렬을 블록으로 하는 블럭와이즈(block-wise) 이중 대각행렬일 수도 있다. 일반적인(bit-wise) 이중 대각행렬에 대해서는 한국공개특허 2007-0058438호 등에 상세히 개시되어 있다.

특히, 행렬 B가 일반적인(bit-wise) 이중 대각행렬인 경우, 이러한 행렬 B를 포함하는 도 3에 도시된 구조의 PCM에 행 퍼뮤테이션(row permutation) 또는 열 퍼뮤테이션(column permutation)을 적용하여 쿼시 사이클릭으로 변환할 수 있음은 당업자에게 자명하다.

이 때, N은 부호어(codeword)의 길이이며, K는 정보(information)의 길이를 각각 나타낸다.

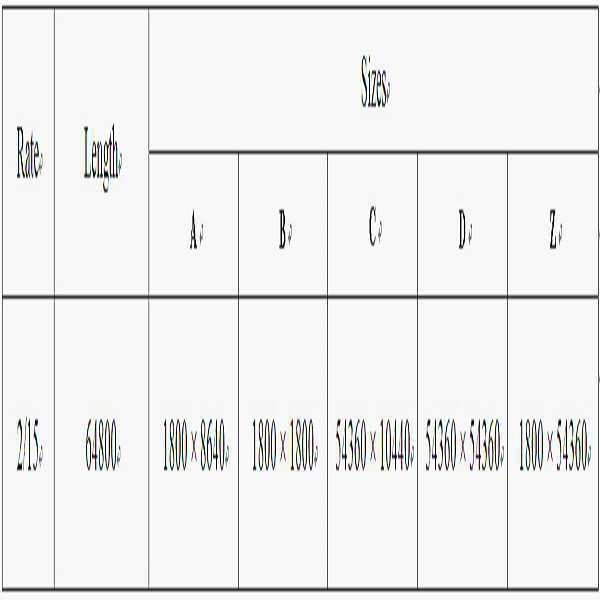

본 발명에서는 아래 표 1과 같이 부호율(code rate)이 2/15이며, 부호어의 길이가 64800인 새롭게 설계된 QC-LDPC 부호를 제안한다. 즉, 길이가 8640인 정보를 입력 받아, 길이가 64800인 LDPC 부호어를 생성하는 LDPC 부호를 제안한다.

표 1은 본 발명의 QC-LDPC 부호의 A, B, C, D, Z 행렬의 크기를 나타낸다.

[표 1]

새롭게 설계된 LDPC 부호는 수열 형태로 표시될 수 있으며, 수열과 행렬(패러티 비트 체크 행렬)은 등가(equivalent) 관계가 성립하고, 수열은 하기 테이블과 같이 표현될 수 있다.

[테이블]

제1행: 615 898 1029 6129 8908 10620 13378 14359 21964 23319 26427 26690 28128 33435 36080 40697 43525 44498 50994

제2행: 165 1081 1637 2913 8944 9639 11391 17341 22000 23580 32309 38495 41239 44079 47395 47460 48282 51744 52782

제3행: 426 1340 1493 2261 10903 13336 14755 15244 20543 29822 35283 38846 45368 46642 46934 48242 49000 49204 53370

제4행: 407 1059 1366 2004 5985 9217 9321 13576 19659 20808 30009 31094 32445 39094 39357 40651 44358 48755 49732

제5행: 692 950 1444 2967 3929 6951 10157 10326 11547 13562 19634 34484 38236 42918 44685 46172 49694 50535 55109

제6행: 1087 1458 1574 2335 3248 6965 17856 23454 25182 37359 37718 37768 38061 38728 39437 40710 46298 50707 51572

제7행: 1098 1540 1711 7723 9549 9986 16369 19567 21185 21319 25750 32222 32463 40342 41391 43869 48372 52149 54722

제8행: 514 1283 1635 6602 11333 11443 17690 21036 22936 24525 25425 27103 28733 29551 39204 42525 49200 54899 54961

제9행: 357 609 1096 2954 4240 5397 8425 13974 15252 20167 20362 21623 27190 42744 47819 49096 51995 55504 55719

제10행: 25 448 1501 11572 13478 24338 29198 29840 31428 33088 34724 37698 37988 38297 40482 46953 47880 53751 54943

제11행: 328 1096 1262 10802 12797 16053 18038 20433 20444 25422 32992 34344 38326 41435 46802 48766 49807 52966 55751

제12행: 34 790 987 5082 5788 10778 12824 18217 23278 24737 28312 34464 36765 37999 39603 40797 43237 53089 55319

제13행: 226 1149 1470 3483 8949 9312 9773 13271 17804 20025 20323 30623 38575 39887 40305 46986 47223 49998 52111

제14행: 1088 1091 1757 2682 5526 5716 9665 10733 12997 14440 24665 27990 30203 33173 37423 38934 40494 45418 48393

제15행: 809 1278 1580 3486 4529 6117 6212 6823 7861 9244 11559 20736 30333 32450 35528 42968 44485 47149 54913

제16행: 369 525 1622 2261 6454 10483 11259 16461 17031 20221 22710 25137 26622 27904 30884 31858 44121 50690 56000

제17행: 423 1291 1352 7883 26107 26157 26876 27071 31515 35340 35953 36608 37795 37842 38527 41720 46206 47998 53019

제18행: 540 662 1433 2828 14410 22880 24263 24802 28242 28396 35928 37214 39748 43915 44905 46590 48684 48890 55926

제19행: 214 1291 1622 7311 8985 20952 22752 23261 24896 25057 28826 37074 37707 38742 46026 51116 51521 52956 54213

제20행: 109 1305 1676 2594 7447 8943 14806 16462 19730 23430 24542 34300 36432 37133 41199 43942 45860 47598 48401 49407

제21행: 242 388 1360 6721 14220 21029 22536 25126 32251 33182 39192 42436 44144 45252 46238 47369 47607 47695 50635 51469

제22행: 199 958 1111 13661 18809 19234 21459 25221 25837 28256 36919 39031 39107 39262 43572 45018 45959 48006 52387 55811

제23행: 668 1087 1451 2945 3319 12519 21248 21344 22627 22701 28152 29670 31430 32655 38533 42233 43200 44013 44459 51398

제24행: 244 1133 1665 8222 8740 11285 12774 15922 20147 20978 28927 35086 40197 40583 41066 41223 42104 44650 45391 48437

제25행: 5623 8050 9679 12978 15846 16049 21807 23364 27226 27758 28661 38147 46337 48141 51364 51927 55124

제26행: 10369 13704 14491 18632 19430 21218 33392 36182 36722 37342 37415 46322 47449 51136 53392 54356 55108

제27행: 7460 9411 11132 11739 13722 15501 25588 26463 26738 31980 31981 35002 39659 39783 41581 51358 55114

제28행: 8915 15253 15264 16513 16896 18367 19110 23492 32074 33302 42443 43797 44715 47538 48515 53464 53548

제29행: 5884 8910 10123 11311 13654 14207 16122 18113 23100 23784 24825 39629 46372 52454 52799 55039 55973

수열형태로 표기된 LDPC 부호는 DVB 표준에서 널리 사용되고 있다.

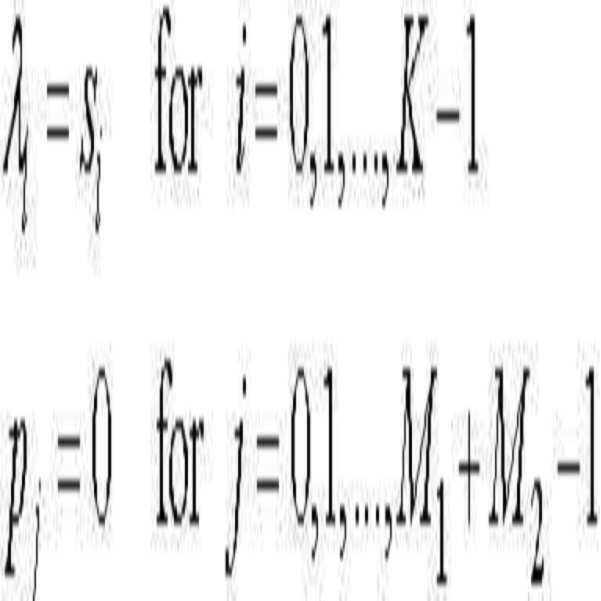

본 발명의 일실시예에 따르면, 수열형태로 표기된 LDPC 부호는 다음과 같이 부호화(encoding)된다. 정보크기(information size)가 K인 정보블록(information block) S=(s0, s1, ..., sK - 1)를 가정하자. LDPC 부호화기(encoder)는 크기가 K인 정보블록 S를 이용하여 크기가 N=K+M1+M2인 부호어(codeword) 를 생성한다. 여기서, M1=g, M2=N-K-g이다. 또한, M1은 이중 대각행렬(dual diagonal matrix) B에 대응하는 패러티(parity)의 크기이며, M2는 항등행렬 D에 대응하는 패러티의 크기이다. 부호화 과정은 다음과 같다.

-초기화(initialization):

[수학식 4]

-첫 번째 를 상기 테이블의 수열의 제1행에 명시된 패러티 비트 주소들(parity bit addresses)에서 누적(accumulate)한다. 예를 들어, 길이가 64800이며, 부호율이 2/15인 LDPC 부호에서의 누적 과정은 다음과 같다.

[수학식 5]

여기서, x는 첫 번째 비트 에 대응되는 패러티 비트 주소들, 즉 상기 테이블의 수열의 제1행에 표기된 패러티 비트 주소들을 나타내며, Q1 = M1/L, Q2 = M2/L, L = 360이다. 또한, Q1과 Q2는 하기 표 2에 정의된다. 예를 들어, 길이가 64800이며, 부호율이 2/15인 LDPC 부호는 M1 = 1800, Q1 = 5, M2 = 54360, Q2 = 151, L = 360이므로, 두 번째 비트 에 대해서는 상기 수학식 5를 이용하면 다음과 같은 연산이 수행된다.

표 2는 설계된 QC-LDPC 부호의 M1, M2, Q1, Q2의 크기를 나타낸다.

[표 2]

-비슷한 방법으로, 새로운 L개의 정보비트들로 구성된 모든 그룹(group)들에 대해서, 상기 수열들의 새로운 행을 이용하여, 상기 수학식 5로부터 패러티 비트 누적기들의 주소를 계산하고, 누적한다.

[수학식 6]

-다음으로, 하기 수학식 7과 같은 패러티 인터리빙(interleaving)을 수행하면, 이중 대각행렬 B에 대응하는 패러티 생성이 완료된다.

[수학식 7]

-에서 까지의 L개의 비트들로 구성된 모든 그룹(group)들에 대해서, 상기 수열들의 새로운 행(이중 대각행렬 B에 대응하는 패러티를 생성할 때 이용한 마지막 행의 바로 다음 행부터 시작)과 상기 수학식 5를 이용하여 패러티 비트 누적기들의 주소를 계산하고, 관련 연산을 수행한다.

[수학식 8]

도 4는 길이가 64800인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 4를 참조하면, 길이가 64800인 LDPC 부호어가 180개의 비트그룹들(0th group ~ 179th group)로 구분되는 것을 알 수 있다.

이 때, 360은 LDPC 부호어의 패러럴 팩터(Parallel Factor; PF)일수 있다. 즉, PF가 360이기 때문에, 길이가 64800인 LDPC 부호어는 도 4에 도시된 바와 같이 180개의 비트그룹들로 구분되고, 각각의 비트그룹들은 360비트들을 포함한다.

도 5는 길이가 16200인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 5를 참조하면, 길이가 16200인 LDPC 부호어가 45개의 비트그룹들(0th group ~ 44th group)으로 구분되는 것을 알 수 있다.

이 때, 360은 LDPC 부호어의 패러럴 팩터(Parallel Factor; PF)일수 있다. 즉, PF가 360이기 때문에, 길이가 16200인 LDPC 부호어는 도 5에 도시된 바와 같이 45개의 비트그룹들로 구분되고, 각각의 비트그룹들은 360비트들을 포함한다.

도 6은 인터리빙 시퀀스에 따른 비트 그룹들 단위의 인터리빙을 나타낸 도면이다.

도 6을 참조하면, 설계된 인터리빙 시퀀스에 의해 비트그룹의 순서를 바꿈으로써 인터리빙이 수행되는 것을 알 수 있다.

예를 들어, 길이가 16200인 LDPC 부호어에 대한 인터리빙 시퀀스가 아래와 같다고 가정하자.

인터리빙 시퀀스 = {24 34 15 11 2 28 17 25 5 38 19 13 6 39 1 14 33 37 29 12 42 31 30 32 36 40 26 35 44 4 16 8 20 43 21 7 0 18 23 3 10 41 9 27 22}

그러면, 도 4에 도시된 것과 같은 LDPC 부호어의 비트그룹들의 순서는 인터리빙 시퀀스에 의해 도 6에 도시된 것처럼 바뀐다.

즉, LDPC 부호어(610) 및 인터리빙된 부호어(620)가 각각 45개의 비트그룹들을 포함하고, 인터리빙 시퀀스에 의해 LDPC 부호어(610)의 24번째 비트그룹이 인터리빙된 LDPC 부호어(620)의 0번째 비트그룹이 되고, LDPC 부호어(610)의 34번째 비트그룹이 인터리빙된 LDPC 부호어(620)의 1번째 비트그룹이 되고, LDPC 부호어(610)의 15번째 비트그룹이 인터리빙된 LDPC 부호어(620)의 2번째 비트그룹이 되고, LDPC 부호어(610)의 11번째 비트그룹이 인터리빙된 LDPC 부호어(620)의 3번째 비트그룹이 되고, LDPC 부호어(610)의 2번째 비트그룹이 인터리빙된 LDPC 부호어(620)의 4번째 비트그룹이 되는 것을 알 수 있다.

[수학식 9]

여기서, X j 는 j번째 비트그룹을 나타내며, 각각의 X j 는 360 비트들로 구성된다.

비트그룹들로 분할된 LDPC 부호어는 하기 수학식 10과 같이 인터리빙된다.

[수학식 10]

여기서, Y j 는 인터리빙된 j번째 비트그룹을 나타내며, π(j)는 비트그룹 단위 인터리빙을 위한 퍼뮤테이션 오더(permutation order)이다. 퍼뮤테이션 오더는 하기 수학식 11의 인터리빙 시퀀스에 대응한다.

[수학식 11]

인터리빙 시퀀스

={112 78 104 6 59 80 49 120 114 27 113 3 109 44 69 164 91 137 39 31 21 127 151 8 47 176 117 68 122 148 79 73 7 166 51 50 116 66 152 61 29 107 22 154 118 94 24 35 55 38 88 54 2 15 19 67 101 74 169 138 41 162 175 136 62 161 121 163 115 135 123 25 140 156 58 33 119 111 146 129 150 147 97 18 60 4 81 168 43 105 36 65 13 5 108 145 23 70 20 173 159 100 128 172 170 1 37 83 102 103 157 139 179 32 144 92 131 75 155 14 9 149 63 11 134 53 99 17 57 90 30 98 64 40 87 158 77 93 124 46 171 141 133 85 177 132 26 160 42 34 82 96 48 10 142 125 178 153 72 45 89 52 28 126 143 167 76 86 130 110 174 16 165 56 84 95 0 106 12 71}

즉, 부호어 및 인터리빙된 부호어 각각이 0번째 비트그룹부터 179번째 비트그룹까지 180개의 비트그룹들을 포함한다고 할 때, 수학식 11의 인터리빙 시퀀스는 부호어의 112번째 비트그룹이 인터리빙된 부호어의 0번째 비트그룹이 되고, 부호어의 78번째 비트그룹이 인터리빙된 부호어의 1번째 비트그룹이 되고, 부호어의 104번째 비트그룹이 인터리빙된 부호어의 2번째 비트그룹이 되고, 부호어의 6번째 비트그룹이 인터리빙된 부호어의 3번째 비트그룹이 되고, ..., 부호어의 12번째 비트그룹이 인터리빙된 부호어의 178번째 비트그룹이 되고, 부호어의 71번째 비트그룹이 인터리빙된 부호어의 179번째 비트그룹이 됨을 의미한다.

특히, 수학식 11에 나타내어진 인터리빙 시퀀스는 256-심볼 맵핑(특히, NUC 심볼 맵핑)이 사용되고, 길이가 64800이고 부호율이 2/15인 LDPC 부호기가 사용되는 경우에 최적화된 것이다.

도 7은 본 발명의 일실시예에 따른 비트 인터리버를 나타낸 블록도이다.

도 7을 참조하면, 본 발명의 일실시예에 따른 비트 인터리버는 메모리들(710, 730) 및 프로세서(720)를 포함한다.

메모리(710)는 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장한다.

프로세서(720)는 상기 LDPC 부호어를, 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성한다.

이 때, 패러럴 팩터는 360일 수 있다. 이 때, 비트그룹은 360 비트들을 포함할 수 있다.

이 때, LDPC 부호어는 상기 수학식 9와 같이 180개의 비트그룹들로 분할될 수 있다.

이 때, 인터리빙은 퍼뮤테이션 오더(permutation order)를 이용한 상기 수학식 10을 이용하여 수행될 수 있다.

이 때, 퍼뮤테이션 오더는 상기 수학식 11에 의하여 표현되는 인터리빙 시퀀스에 상응하는 것일 수 있다.

메모리(730)는 상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 제공한다.

이 때, 변조기는 NUC(Non-Uniform Constellation) 심볼 맵핑을 수행하는 심볼 맵핑 장치일 수 있다.

메모리(710) 및 메모리(730)는 비트들의 집합을 저장하기 위한 다양한 하드웨어에 상응하는 것일 수도 있고, 어레이(array), 리스트(list), 스택(stack), 큐(queue) 등의 자료구조(data structure)에 상응하는 것일 수도 있다.

이 때, 메모리(710) 및 메모리(730)는 물리적으로 별개의 장치가 아니라, 물리적으로는 하나의 장치의 서로 다른 주소에 상응하는 것일 수 있다. 즉, 메모리(710) 및 메모리(730)는 물리적으로는 구분되지 않고, 논리적으로만 구분되는 것일 수 있다.

도 1에 도시된 오류정정 부호화기(13)는 도 7과 같은 구조로 구현될 수도 있다.

즉, 오류정정 부호화기는 메모리들 및 프로세서를 포함할 수 있다. 이 때, 제1 메모리는 길이가 64800이고 부호율이 2/15인 LDPC 부호어(codeword)를 저장하기 위한 메모리이고, 제2 메모리는 0으로 초기화되는 메모리일 수 있다.

메모리들은 각각 λi(i=0, 1, ..., N-1) 및 Pj(j=0, 1, ..., M1+M2-1)에 상응하는 것일 수 있다.

프로세서는 패러티 검사 행렬(parity check matrix)에 상응하는 수열을 이용하여 상기 메모리에 대한 누적(accumulation)을 수행하여, 정보 비트들(information bits)에 상응하는 상기 LDPC 부호어를 생성할 수 있다.

이 때, 누적은 상기 테이블의 수열을 이용하여 갱신되는 패러티 비트 주소들(parity bit addresses)에서 수행될 수 있다.

이 때, LDPC 부호어는 상기 정보 비트들에 상응하고 길이가 8640(=K)인 시스터매틱(systematic) 파트(λ0, λ1, ..., λK -1), 패러티 검사 행렬에 포함된 이중 대각행렬에 상응하고 길이가 1800(=M1=g)인 제1 패러티 파트(λK, λK + 1, ..., λK +M1-1) 및 상기 패러티 검사 행렬에 포함된 항등행렬에 상응하고 길이가 54360(=M2)인 제2 패러티 파트(λK +M1, λK +M1+ 1, ..., λK +M1+M2- 1)를 포함할 수 있다.

이 때, 수열은 상기 시스터매틱 파트의 길이인 8640을 상기 패러티 검사 행렬에 상응하는 CPM 사이즈(L)인 360으로 나눈 값에 제1 패러티 파트의 길이(M1)인 1800을 360으로 나눈 값을 더한 수(8640/360+1800/360=29)만큼의 행들(rows)을 가질 수 있다.

전술한 바와 같이, 수열은 상기 테이블로 표현될 수 있다.

이 때, 제2 메모리는 제1 패러티 파트의 길이(M1) 및 제2 패러티 파트의 길이(M2)의 합(M1+M2)에 상응하는 사이즈를 가질 수 있다.

이 때, 패러티 비트 주소들은 상기 수열의 각각의 행에 나타내진 이전 패러티 비트 주소들 각각(x)과 제1 패러티 파트의 길이(M1)를 비교한 결과에 기반하여 갱신될 수 있다.

즉, 패러티 비트 주소들은 상기 수학식 5에 의하여 갱신될 수 있다. 이 때, x는 이전 패러티 비트 주소, m은 정보 비트 인덱스로 0보다 크고 L보다 작은 정수, L은 상기 패러티 검사 행렬의 CPM 사이즈, Q1은 M1/L, M1은 상기 제1 패러티 파트의 사이즈, Q2는 M2/L, M2는 상기 제2 패러티 파트의 사이즈일 수 있다.

이 때, 상기 누적은 전술한 바와 같이 상기 패러티 검사 행렬의 CPM 사이즈 L=360 단위로 수열의 행을 바꿔가면서 수행될 수 있다.

이 때, 제1 패러티 파트(λK, λK+1, ..., λK+M1-1)는 상기 수학식 7을 통하여 설명한 바와 같이, 제1 메모리 및 제2 메모리를 이용한, 패러티 인터리빙(parity interleaving)을 수행하여 생성될 수 있다.

이 때, 제2 패러티 파트(λK +M1, λK +M1+ 1, ..., λK +M1+M2- 1)는 상기 수학식 8을 통하여 설명한 바와 같이 제1 패러티 파트(λK, λK+1, ..., λK+M1-1)의 생성이 완료된 후 상기 제1 패러티 파트(λK, λK+1, ..., λK+M1-1)와 상기 수열을 이용하여 수행되는 상기 누적이 완료된 후, 제1 메모리 및 제2 메모리를 이용한 패러티 인터리빙(parity interleaving)을 수행하여 생성될 수 있다.

도 8은 본 발명의 일실시예에 따른 비트 인터리빙 방법을 나타낸 동작 흐름도이다.

도 8을 참조하면, 본 발명의 일실시예에 따른 비트 인터리빙 방법은 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장한다(S810).

또한, 본 발명의 일실시예에 따른 비트 인터리빙 방법은 상기 LDPC 부호어를 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성한다(S820).

이 때, 인터리빙은 퍼뮤테이션 오더(permutation order)를 이용한 상기 수학식 10을 이용하여 수행될 수 있다.

이 때, 퍼뮤테이션 오더는 상기 수학식 11에 의하여 표현되는 인터리빙 시퀀스에 상응하는 것일 수 있다.

이 때, 패러럴 팩터는 360이고, 비트그룹은 360 비트들을 포함할 수 있다.

또한, 본 발명의 일실시예에 따른 비트 인터리빙 방법은 상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 출력한다(S830).

이상에서와 같이 본 발명에 따른 비트 인터리버, BICM 장치 및 비트 인터리빙 방법은 상기한 바와 같이 설명된 실시예들의 구성과 방법이 한정되게 적용될 수 있는 것이 아니라, 상기 실시예들은 다양한 변형이 이루어질 수 있도록 각 실시예들의 전부 또는 일부가 선택적으로 조합되어 구성될 수도 있다.

710, 730:

메모리

720: 프로세서

720: 프로세서

Claims (6)

- 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장하는 제1 메모리;

상기 LDPC 부호어를, 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성하는 프로세서; 및

상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 제공하는 제2 메모리

를 포함하는 것을 특징으로 하는 비트 인터리버. - 청구항 1에 있어서,

상기 256-심볼 맵핑은 256개의 컨스틸레이션들을 가지는 NUC(Non-Uniform Constellation) 심볼 맵핑인 것을 특징으로 하는 비트 인터리버. - 청구항 2에 있어서,

상기 패러럴 팩터는 360이고, 상기 비트그룹은 360비트들을 포함하는 것을 특징으로 하는 비트 인터리버. - 청구항 5에 있어서,

상기 퍼뮤테이션 오더는

하기 수학식에 의하여 표현되는 인터리빙 시퀀스에 상응하는 것을 특징으로 하는 비트 인터리버.

[수학식]

인터리빙 시퀀스

={112 78 104 6 59 80 49 120 114 27 113 3 109 44 69 164 91 137 39 31 21 127 151 8 47 176 117 68 122 148 79 73 7 166 51 50 116 66 152 61 29 107 22 154 118 94 24 35 55 38 88 54 2 15 19 67 101 74 169 138 41 162 175 136 62 161 121 163 115 135 123 25 140 156 58 33 119 111 146 129 150 147 97 18 60 4 81 168 43 105 36 65 13 5 108 145 23 70 20 173 159 100 128 172 170 1 37 83 102 103 157 139 179 32 144 92 131 75 155 14 9 149 63 11 134 53 99 17 57 90 30 98 64 40 87 158 77 93 124 46 171 141 133 85 177 132 26 160 42 34 82 96 48 10 142 125 178 153 72 45 89 52 28 126 143 167 76 86 130 110 174 16 165 56 84 95 0 106 12 71}

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150023409A KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| US14/639,646 US9577681B2 (en) | 2015-02-16 | 2015-03-05 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US15/403,394 US10447310B2 (en) | 2015-02-16 | 2017-01-11 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US16/559,482 US10979082B2 (en) | 2015-02-16 | 2019-09-03 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US17/176,903 US11750225B2 (en) | 2015-02-16 | 2021-02-16 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| KR1020210101620A KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150023409A KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020210101620A Division KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160100665A true KR20160100665A (ko) | 2016-08-24 |

| KR102287616B1 KR102287616B1 (ko) | 2021-08-10 |

Family

ID=56621463

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150023409A KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020210101620A KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020210101620A KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US9577681B2 (ko) |

| KR (3) | KR102287616B1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102207744B1 (ko) | 2020-09-22 | 2021-01-26 | (주)한동엔지니어링 | 공동주택의 사물 인터넷 통신 시스템 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102240744B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102240740B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287619B1 (ko) * | 2015-02-12 | 2021-08-10 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287621B1 (ko) * | 2015-02-16 | 2021-08-10 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287635B1 (ko) * | 2015-02-17 | 2021-08-10 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287639B1 (ko) * | 2015-02-17 | 2021-08-10 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| CN110858789B (zh) * | 2018-08-22 | 2021-01-22 | 大唐移动通信设备有限公司 | 一种编码方法及装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150005426A (ko) * | 2013-07-05 | 2015-01-14 | 삼성전자주식회사 | 송신 장치 및 그의 신호 처리 방법 |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5341396A (en) * | 1993-03-02 | 1994-08-23 | The Boeing Company | Multi-rate spread system |

| EP0620668B1 (en) * | 1993-04-15 | 2000-06-07 | Samsung Electronics Co., Ltd. | Removal of plus/minus 90 and 180 phase errors in QAM receivers |

| US5559506A (en) * | 1994-05-04 | 1996-09-24 | Motorola, Inc. | Method and apparatus for encoding and decoding a digital radio signal |

| US5946357A (en) * | 1997-01-17 | 1999-08-31 | Telefonaktiebolaget L M Ericsson | Apparatus, and associated method, for transmitting and receiving a multi-stage, encoded and interleaved digital communication signal |

| AU2003249708A1 (en) | 2002-07-03 | 2004-01-23 | Hughes Electronics Corporation | Method and system for memory management in low density parity check (ldpc) decoders |

| KR20040036460A (ko) * | 2002-10-26 | 2004-04-30 | 삼성전자주식회사 | Ldpc 복호화 장치 및 그 방법 |

| KR100981503B1 (ko) * | 2004-02-13 | 2010-09-10 | 삼성전자주식회사 | 최대 오류 정정/오류 검출 능력을 가지는 저밀도 패리티검사 부호 부호화/복호화 장치 및 방법 |

| KR100946884B1 (ko) * | 2005-07-15 | 2010-03-09 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 채널인터리빙/디인터리빙 장치 및 그 제어 방법 |

| EP2186200B1 (en) * | 2007-08-28 | 2016-06-15 | Samsung Electronics Co., Ltd. | Apparatus and method for transmitting and receiving data in a communication system using low density parity check codes |

| WO2009041979A1 (en) * | 2007-09-28 | 2009-04-02 | Agere Systems Inc. | Systems and methods for reduced complexity data processing |

| WO2009145588A2 (ko) | 2008-05-29 | 2009-12-03 | 한국전자통신연구원 | 방송/통신 데이터 송수신 방법 및 장치 |

| KR20090130808A (ko) | 2008-06-16 | 2009-12-24 | 한국전자통신연구원 | 디지털 케이블 송수신 시스템에서 적응/가변형 변복조 장치 |

| KR101189770B1 (ko) | 2008-12-19 | 2012-10-10 | 한국전자통신연구원 | 맵 디코딩 방법과 장치 및 이를 이용한 터보 맵 디코더 |

| EP2282470A1 (en) | 2009-08-07 | 2011-02-09 | Thomson Licensing | Data reception using low density parity check coding and constellation mapping |

| US8930793B2 (en) * | 2009-08-27 | 2015-01-06 | Indian Space Research Organisation | Method of communicating signal data in GNSS using LDPC convolution codes and a system thereof |

| US8255768B2 (en) * | 2009-09-25 | 2012-08-28 | Stmicroelectronics, Inc. | Interlaced iterative system design for 1K-byte block with 512-byte LDPC codewords |

| WO2011062424A2 (en) * | 2009-11-18 | 2011-05-26 | Samsung Electronics Co., Ltd. | Method and apparatus for transmitting and receiving data in a communication system |

| EP2536030A1 (en) * | 2011-06-16 | 2012-12-19 | Panasonic Corporation | Bit permutation patterns for BICM with LDPC codes and QAM constellations |

| KR101868901B1 (ko) | 2011-12-01 | 2018-07-23 | 한국전자통신연구원 | 디지털 방송 시스템에서 부가데이터 전송 및 수신을 위한 장치 및 방법 |

| US9077378B2 (en) * | 2013-01-31 | 2015-07-07 | Lsi Corporation | Integrated-interleaved low density parity check (LDPC) codes |

| US9735809B2 (en) | 2013-09-26 | 2017-08-15 | Samsung Electronics Co., Ltd. | Transmitting apparatus and signal processing method thereof |

| US9577678B2 (en) * | 2014-01-29 | 2017-02-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 7/15 and quadrature phase shift keying, and bit interleaving method using same |

| EP3565209B1 (en) * | 2014-02-05 | 2020-06-17 | Samsung Electronics Co., Ltd. | Transmitting apparatus and modulation method thereof |

| US9602135B2 (en) * | 2014-02-20 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 64-symbol mapping, and bit interleaving method using same |

| US9602131B2 (en) * | 2014-02-20 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 16-symbol mapping, and bit interleaving method using same |

| US9602136B2 (en) * | 2014-03-06 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and 256-symbol mapping, and bit interleaving method using same |

| US10419023B2 (en) * | 2014-03-20 | 2019-09-17 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 1024-symbol mapping, and bit interleaving method using same |

| US10432228B2 (en) * | 2014-03-27 | 2019-10-01 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 4096-symbol mapping, and bit interleaving method using same |

| US10326471B2 (en) * | 2014-05-22 | 2019-06-18 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 3/15 and quadrature phase shift keying, and bit interleaving method using same |

| US10361720B2 (en) * | 2014-05-22 | 2019-07-23 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 3/15 and 64-symbol mapping, and bit interleaving method using same |

| US9600367B2 (en) * | 2014-05-22 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 4/15 and 16-symbol mapping, and bit interleaving method using same |

| US10360102B2 (en) * | 2014-05-22 | 2019-07-23 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 10/15 and 256-symbol mapping, and bit interleaving method using same |

| KR102240728B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

-

2015

- 2015-02-16 KR KR1020150023409A patent/KR102287616B1/ko active IP Right Grant

- 2015-03-05 US US14/639,646 patent/US9577681B2/en active Active

-

2017

- 2017-01-11 US US15/403,394 patent/US10447310B2/en active Active

-

2019

- 2019-09-03 US US16/559,482 patent/US10979082B2/en active Active

-

2021

- 2021-02-16 US US17/176,903 patent/US11750225B2/en active Active

- 2021-08-02 KR KR1020210101620A patent/KR102429513B1/ko active IP Right Grant

-

2022

- 2022-08-01 KR KR1020220095537A patent/KR102557439B1/ko active IP Right Grant

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150005426A (ko) * | 2013-07-05 | 2015-01-14 | 삼성전자주식회사 | 송신 장치 및 그의 신호 처리 방법 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102207744B1 (ko) | 2020-09-22 | 2021-01-26 | (주)한동엔지니어링 | 공동주택의 사물 인터넷 통신 시스템 |

Also Published As

| Publication number | Publication date |

|---|---|

| US9577681B2 (en) | 2017-02-21 |

| KR102429513B1 (ko) | 2022-08-05 |

| KR20220113323A (ko) | 2022-08-12 |

| KR102557439B1 (ko) | 2023-07-20 |

| US20210167802A1 (en) | 2021-06-03 |

| US20160241263A1 (en) | 2016-08-18 |

| US11750225B2 (en) | 2023-09-05 |

| US20190393899A1 (en) | 2019-12-26 |

| KR102287616B1 (ko) | 2021-08-10 |

| KR20210097680A (ko) | 2021-08-09 |

| US10447310B2 (en) | 2019-10-15 |

| US20170126252A1 (en) | 2017-05-04 |

| US10979082B2 (en) | 2021-04-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20210064166A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089767A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20210098418A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20210098898A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220113323A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR20160099265A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092354A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102429457B1 (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100667A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 1024-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092351A (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20210097683A (ko) | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220112727A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 4096-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR20160092350A (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089766A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220112730A (ko) | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR20210097684A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 4096-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089765A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102240740B1 (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100666A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092353A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100668A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 1024-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20150105191A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220110712A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 4096-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR20220063132A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 bicm 수신 장치 및 이를 이용한 방법 | |

| KR20150098561A (ko) | 길이가 64800이며, 부호율이 5/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| A107 | Divisional application of patent | ||

| GRNT | Written decision to grant |