KR20160100665A - 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 - Google Patents

길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 Download PDFInfo

- Publication number

- KR20160100665A KR20160100665A KR1020150023409A KR20150023409A KR20160100665A KR 20160100665 A KR20160100665 A KR 20160100665A KR 1020150023409 A KR1020150023409 A KR 1020150023409A KR 20150023409 A KR20150023409 A KR 20150023409A KR 20160100665 A KR20160100665 A KR 20160100665A

- Authority

- KR

- South Korea

- Prior art keywords

- bit

- codeword

- ldpc

- interleaving

- length

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2792—Interleaver wherein interleaving is performed jointly with another technique such as puncturing, multiplexing or routing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

- H03M13/1165—QC-LDPC codes as defined for the digital video broadcasting [DVB] specifications, e.g. DVB-Satellite [DVB-S2]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/118—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

- H03M13/255—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM] with Low Density Parity Check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2778—Interleaver using block-wise interleaving, e.g. the interleaving matrix is sub-divided into sub-matrices and the permutation is performed in blocks of sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/61—Aspects and characteristics of methods and arrangements for error correction or error detection, not provided for otherwise

- H03M13/615—Use of computational or mathematical techniques

- H03M13/616—Matrix operations, especially for generator matrices or check matrices, e.g. column or row permutations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6522—Intended application, e.g. transmission or communication standard

- H03M13/6552—DVB-T2

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Probability & Statistics with Applications (AREA)

- Mathematical Physics (AREA)

- Multimedia (AREA)

- Computer Networks & Wireless Communication (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Mathematical Analysis (AREA)

- General Physics & Mathematics (AREA)

- Computational Mathematics (AREA)

- Algebra (AREA)

- Computing Systems (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Abstract

Description

도 2는 본 발명의 일실시예에 따른 방송 신호 송/수신 방법을 나타낸 동작 흐름도이다.

도 3은 본 발명의 일실시예에 따른 LDPC 부호에 상응하는 패러티 검사 행렬의 구조를 나타낸 도면이다.

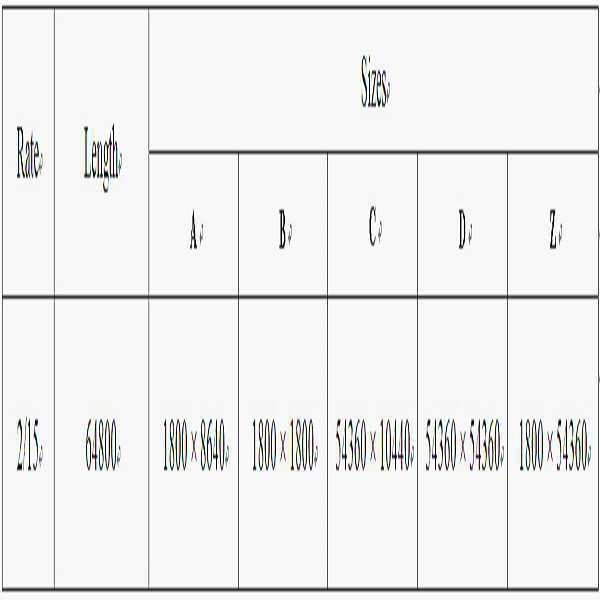

도 4는 길이가 64800인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 5는 길이가 16200인 LDPC 부호어의 비트그룹들을 나타낸 도면이다.

도 6은 인터리빙 시퀀스에 따른 비트 그룹들 단위의 인터리빙을 나타낸 도면이다.

도 7은 본 발명의 일실시예에 따른 비트 인터리버를 나타낸 블록도이다.

도 8은 본 발명의 일실시예에 따른 비트 인터리빙 방법을 나타낸 동작 흐름도이다.

720: 프로세서

Claims (6)

- 길이가 64800이고 부호율이 2/15인 LDPC 부호어를 저장하는 제1 메모리;

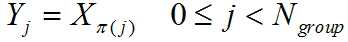

상기 LDPC 부호어를, 상기 LDPC 부호어의 패러럴 팩터(parallel factor)에 상응하는 사이즈의 비트그룹 단위로 인터리빙하여 인터리빙된 부호어를 생성하는 프로세서; 및

상기 인터리빙된 부호어를 256-심볼 맵핑을 위한 변조기로 제공하는 제2 메모리

를 포함하는 것을 특징으로 하는 비트 인터리버. - 청구항 1에 있어서,

상기 256-심볼 맵핑은 256개의 컨스틸레이션들을 가지는 NUC(Non-Uniform Constellation) 심볼 맵핑인 것을 특징으로 하는 비트 인터리버. - 청구항 2에 있어서,

상기 패러럴 팩터는 360이고, 상기 비트그룹은 360비트들을 포함하는 것을 특징으로 하는 비트 인터리버. - 청구항 5에 있어서,

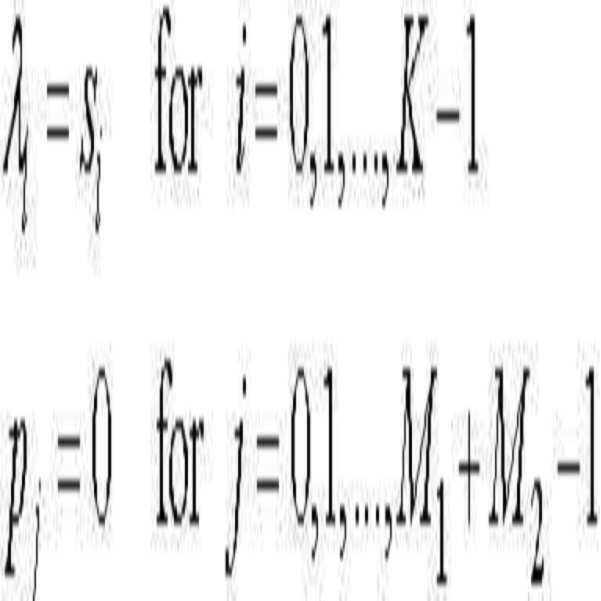

상기 퍼뮤테이션 오더는

하기 수학식에 의하여 표현되는 인터리빙 시퀀스에 상응하는 것을 특징으로 하는 비트 인터리버.

[수학식]

인터리빙 시퀀스

={112 78 104 6 59 80 49 120 114 27 113 3 109 44 69 164 91 137 39 31 21 127 151 8 47 176 117 68 122 148 79 73 7 166 51 50 116 66 152 61 29 107 22 154 118 94 24 35 55 38 88 54 2 15 19 67 101 74 169 138 41 162 175 136 62 161 121 163 115 135 123 25 140 156 58 33 119 111 146 129 150 147 97 18 60 4 81 168 43 105 36 65 13 5 108 145 23 70 20 173 159 100 128 172 170 1 37 83 102 103 157 139 179 32 144 92 131 75 155 14 9 149 63 11 134 53 99 17 57 90 30 98 64 40 87 158 77 93 124 46 171 141 133 85 177 132 26 160 42 34 82 96 48 10 142 125 178 153 72 45 89 52 28 126 143 167 76 86 130 110 174 16 165 56 84 95 0 106 12 71}

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150023409A KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| US14/639,646 US9577681B2 (en) | 2015-02-16 | 2015-03-05 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US15/403,394 US10447310B2 (en) | 2015-02-16 | 2017-01-11 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US16/559,482 US10979082B2 (en) | 2015-02-16 | 2019-09-03 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| US17/176,903 US11750225B2 (en) | 2015-02-16 | 2021-02-16 | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 256-symbol mapping, and bit interleaving method using same |

| KR1020210101620A KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150023409A KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020210101620A Division KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160100665A true KR20160100665A (ko) | 2016-08-24 |

| KR102287616B1 KR102287616B1 (ko) | 2021-08-10 |

Family

ID=56621463

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150023409A Active KR102287616B1 (ko) | 2015-02-16 | 2015-02-16 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020210101620A Active KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A Active KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020210101620A Active KR102429513B1 (ko) | 2015-02-16 | 2021-08-02 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR1020220095537A Active KR102557439B1 (ko) | 2015-02-16 | 2022-08-01 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US9577681B2 (ko) |

| KR (3) | KR102287616B1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102207744B1 (ko) | 2020-09-22 | 2021-01-26 | (주)한동엔지니어링 | 공동주택의 사물 인터넷 통신 시스템 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102240744B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102240740B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287619B1 (ko) * | 2015-02-12 | 2021-08-10 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287621B1 (ko) * | 2015-02-16 | 2021-08-10 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287635B1 (ko) * | 2015-02-17 | 2021-08-10 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| KR102287639B1 (ko) * | 2015-02-17 | 2021-08-10 | 한국전자통신연구원 | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

| CN110858789B (zh) * | 2018-08-22 | 2021-01-22 | 大唐移动通信设备有限公司 | 一种编码方法及装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150005426A (ko) * | 2013-07-05 | 2015-01-14 | 삼성전자주식회사 | 송신 장치 및 그의 신호 처리 방법 |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5341396A (en) * | 1993-03-02 | 1994-08-23 | The Boeing Company | Multi-rate spread system |

| EP0620668B1 (en) * | 1993-04-15 | 2000-06-07 | Samsung Electronics Co., Ltd. | Removal of plus/minus 90 and 180 phase errors in QAM receivers |

| US5559506A (en) * | 1994-05-04 | 1996-09-24 | Motorola, Inc. | Method and apparatus for encoding and decoding a digital radio signal |

| US5946357A (en) * | 1997-01-17 | 1999-08-31 | Telefonaktiebolaget L M Ericsson | Apparatus, and associated method, for transmitting and receiving a multi-stage, encoded and interleaved digital communication signal |

| EP1518328B1 (en) | 2002-07-03 | 2007-04-18 | The DIRECTV Group, Inc. | Encoding of low-density parity check (ldpc) codes using a structured parity check matrix |

| KR20040036460A (ko) * | 2002-10-26 | 2004-04-30 | 삼성전자주식회사 | Ldpc 복호화 장치 및 그 방법 |

| KR100981503B1 (ko) * | 2004-02-13 | 2010-09-10 | 삼성전자주식회사 | 최대 오류 정정/오류 검출 능력을 가지는 저밀도 패리티검사 부호 부호화/복호화 장치 및 방법 |

| KR100946884B1 (ko) * | 2005-07-15 | 2010-03-09 | 삼성전자주식회사 | 저밀도 패리티 검사 부호를 사용하는 통신 시스템에서 채널인터리빙/디인터리빙 장치 및 그 제어 방법 |

| US8190981B2 (en) * | 2007-08-28 | 2012-05-29 | Samsung Electronics Co., Ltd. | Apparatus and method for transmitting and receiving data in a communication system using low density parity check codes |

| JP2010541375A (ja) * | 2007-09-28 | 2010-12-24 | アギア システムズ インコーポレーテッド | 複雑度を低減したデータ処理のためのシステムおよび方法 |

| CA2726022C (en) | 2008-05-29 | 2016-11-29 | Electronics And Telecommunications Research Institute | Method and apparatus for transmitting/receiving broadcasting-communication data |

| KR20090130808A (ko) | 2008-06-16 | 2009-12-24 | 한국전자통신연구원 | 디지털 케이블 송수신 시스템에서 적응/가변형 변복조 장치 |

| KR101189770B1 (ko) | 2008-12-19 | 2012-10-10 | 한국전자통신연구원 | 맵 디코딩 방법과 장치 및 이를 이용한 터보 맵 디코더 |

| EP2282470A1 (en) | 2009-08-07 | 2011-02-09 | Thomson Licensing | Data reception using low density parity check coding and constellation mapping |

| WO2011024206A1 (en) * | 2009-08-27 | 2011-03-03 | Indian Space Research Organisation | Method of communicating signal data in gnss using ldpc convolution codes and a system thereof |

| US8255768B2 (en) * | 2009-09-25 | 2012-08-28 | Stmicroelectronics, Inc. | Interlaced iterative system design for 1K-byte block with 512-byte LDPC codewords |

| WO2011062424A2 (en) * | 2009-11-18 | 2011-05-26 | Samsung Electronics Co., Ltd. | Method and apparatus for transmitting and receiving data in a communication system |

| EP2536030A1 (en) * | 2011-06-16 | 2012-12-19 | Panasonic Corporation | Bit permutation patterns for BICM with LDPC codes and QAM constellations |

| KR101868901B1 (ko) | 2011-12-01 | 2018-07-23 | 한국전자통신연구원 | 디지털 방송 시스템에서 부가데이터 전송 및 수신을 위한 장치 및 방법 |

| US9077378B2 (en) * | 2013-01-31 | 2015-07-07 | Lsi Corporation | Integrated-interleaved low density parity check (LDPC) codes |

| US9735809B2 (en) | 2013-09-26 | 2017-08-15 | Samsung Electronics Co., Ltd. | Transmitting apparatus and signal processing method thereof |

| US9577678B2 (en) * | 2014-01-29 | 2017-02-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 7/15 and quadrature phase shift keying, and bit interleaving method using same |

| CN113271281B (zh) * | 2014-02-05 | 2023-12-12 | 三星电子株式会社 | 发送方法和接收方法 |

| US9602131B2 (en) * | 2014-02-20 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 16-symbol mapping, and bit interleaving method using same |

| US9602135B2 (en) * | 2014-02-20 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 64-symbol mapping, and bit interleaving method using same |

| US9602136B2 (en) * | 2014-03-06 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and 256-symbol mapping, and bit interleaving method using same |

| US10419023B2 (en) * | 2014-03-20 | 2019-09-17 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 1024-symbol mapping, and bit interleaving method using same |

| US10432228B2 (en) * | 2014-03-27 | 2019-10-01 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 4096-symbol mapping, and bit interleaving method using same |

| CA2989608C (en) * | 2014-05-22 | 2021-03-09 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 10/15 and 256-symbol mapping, and bit interleaving method using same |

| US10361720B2 (en) * | 2014-05-22 | 2019-07-23 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 3/15 and 64-symbol mapping, and bit interleaving method using same |

| US9600367B2 (en) * | 2014-05-22 | 2017-03-21 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 4/15 and 16-symbol mapping, and bit interleaving method using same |

| US10326471B2 (en) * | 2014-05-22 | 2019-06-18 | Electronics And Telecommunications Research Institute | Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 3/15 and quadrature phase shift keying, and bit interleaving method using same |

| KR102240728B1 (ko) * | 2015-01-27 | 2021-04-16 | 한국전자통신연구원 | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

-

2015

- 2015-02-16 KR KR1020150023409A patent/KR102287616B1/ko active Active

- 2015-03-05 US US14/639,646 patent/US9577681B2/en active Active

-

2017

- 2017-01-11 US US15/403,394 patent/US10447310B2/en active Active

-

2019

- 2019-09-03 US US16/559,482 patent/US10979082B2/en active Active

-

2021

- 2021-02-16 US US17/176,903 patent/US11750225B2/en active Active

- 2021-08-02 KR KR1020210101620A patent/KR102429513B1/ko active Active

-

2022

- 2022-08-01 KR KR1020220095537A patent/KR102557439B1/ko active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150005426A (ko) * | 2013-07-05 | 2015-01-14 | 삼성전자주식회사 | 송신 장치 및 그의 신호 처리 방법 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102207744B1 (ko) | 2020-09-22 | 2021-01-26 | (주)한동엔지니어링 | 공동주택의 사물 인터넷 통신 시스템 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20210167802A1 (en) | 2021-06-03 |

| US10447310B2 (en) | 2019-10-15 |

| KR102557439B1 (ko) | 2023-07-20 |

| US9577681B2 (en) | 2017-02-21 |

| KR20210097680A (ko) | 2021-08-09 |

| US11750225B2 (en) | 2023-09-05 |

| US10979082B2 (en) | 2021-04-13 |

| KR20220113323A (ko) | 2022-08-12 |

| US20160241263A1 (en) | 2016-08-18 |

| US20190393899A1 (en) | 2019-12-26 |

| KR102287616B1 (ko) | 2021-08-10 |

| US20170126252A1 (en) | 2017-05-04 |

| KR102429513B1 (ko) | 2022-08-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20210064166A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102429462B1 (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102429454B1 (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220113323A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR102429471B1 (ko) | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089767A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160099265A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092354A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102429457B1 (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100667A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 1024-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092351A (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092350A (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 16-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089766A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20210097684A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 4096-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100669A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 4096-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160089765A (ko) | 길이가 64800이며, 부호율이 2/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR102240740B1 (ko) | 길이가 16200이며, 부호율이 2/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100666A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160092353A (ko) | 길이가 64800이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160101391A (ko) | 길이가 16200이며, 부호율이 4/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20160100668A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 1024-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20150105191A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 256-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20220110712A (ko) | 길이가 64800이며, 부호율이 4/15인 ldpc 부호어 및 4096-심볼 맵핑에 상응하는 bicm 수신 장치 및 방법 | |

| KR20150135054A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 64-심볼 맵핑을 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 | |

| KR20150135051A (ko) | 길이가 16200이며, 부호율이 3/15인 ldpc 부호어 및 qpsk를 위한 비트 인터리버 및 이를 이용한 비트 인터리빙 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20150216 |

|

| PG1501 | Laying open of application | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20200123 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20150216 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20201118 Patent event code: PE09021S01D |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

Patent event code: PE07011S01D Comment text: Decision to Grant Registration Patent event date: 20210503 |

|

| A107 | Divisional application of patent | ||

| PA0107 | Divisional application |

Comment text: Divisional Application of Patent Patent event date: 20210802 Patent event code: PA01071R01D |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

Comment text: Registration of Establishment Patent event date: 20210803 Patent event code: PR07011E01D |

|

| PR1002 | Payment of registration fee |

Payment date: 20210804 End annual number: 3 Start annual number: 1 |

|

| PG1601 | Publication of registration | ||

| PR1001 | Payment of annual fee |

Payment date: 20240827 Start annual number: 4 End annual number: 4 |