JP7690992B2 - Fpgaシステム - Google Patents

Fpgaシステム Download PDFInfo

- Publication number

- JP7690992B2 JP7690992B2 JP2023544828A JP2023544828A JP7690992B2 JP 7690992 B2 JP7690992 B2 JP 7690992B2 JP 2023544828 A JP2023544828 A JP 2023544828A JP 2023544828 A JP2023544828 A JP 2023544828A JP 7690992 B2 JP7690992 B2 JP 7690992B2

- Authority

- JP

- Japan

- Prior art keywords

- function

- fpga

- client

- circuit

- token

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7867—Architectures of general purpose stored program computers comprising a single central processing unit with reconfigurable architecture

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/17724—Structural details of logic blocks

- H03K19/17728—Reconfigurable logic blocks, e.g. lookup tables

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/17748—Structural details of configuration resources

- H03K19/1776—Structural details of configuration resources for memories

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/65—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using error resilience

- H04N19/68—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using error resilience involving the insertion of resynchronisation markers into the bitstream

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- Computing Systems (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Stored Programmes (AREA)

Description

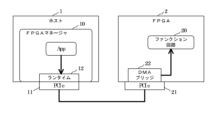

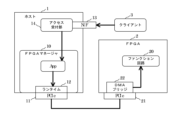

Appは、FPGA2に処理を実行させるときに、ファンクション回路20を使用するためのプログラムであるランタイム12を呼び出す。ランタイム12は、PCIeインタフェース部11,21を介してFPGA2内のファンクション回路20に処理を要求する。ファンクション回路20は、要求に応じた処理の結果をランタイム12に返送する。ランタイム12は、処理結果をAppに渡す。ホスト装置1とFPGA2との間のデータ転送は、DMA(Direct Memory Access)ブリッジコントローラ22によるDMA転送によって行われる。

また、本発明のFPGAシステムの1構成例において、前記FPGAは、前記アプリケーション実行部から受信したファンクション名とトークンとを前記テーブルに書き込み、書き込みを行ったテーブルの行に割り当てたファンクションIDを前記アプリケーション実行部に返送するように構成されたコントローラをさらに備えることを特徴とするものである。

また、本発明のFPGAシステムの1構成例において、前記ホスト装置は、前記テーブルに格納された内容に対応して前記ファンクション回路を再構成するためのビットストリームデータを前記FPGAに送信するように構成されたファンクション回路管理部をさらに備えることを特徴とするものである。

また、本発明のFPGAシステムの1構成例において、前記FPGAは、前記クライアントとネットワークを介して通信を行うためのネットワークインタフェース部をさらに備え、前記アクセス受付部は、前記クライアントからのファンクション使用要求を前記ネットワークインタフェース部を介して受信し、前記ファンクション回路による処理結果を前記ネットワークインタフェース部を介して前記クライアントに返送することを特徴とするものである。

また、本発明のFPGAシステムの1構成例において、前記アプリケーション実行部は、前記クライアントからのファンクション使用要求を前記FPGAに送信し、前記FPGAから受信した処理結果を前記クライアントに返送し、前記アクセス受付部は、前記ファンクション使用要求を前記アプリケーション実行部から受信し、前記ファンクション回路による処理結果を前記アプリケーション実行部に返送することを特徴とするものである。

以下、本発明の実施例について図面を参照して説明する。図1は本発明の第1の実施例に係るFPGAシステムの構成を示すブロック図である。

本実施例のFPGA2aは、アクセス受付部23を有する。図7に示した従来の構成では、クライアントからのファンクション使用要求に応えるアクセス受付部14がホスト装置1に設けられていた。一方、本実施例では、アクセス受付部23をFPGA2aのボード上に実装する。

ファンクション回路管理部15は、事前に用意されたビットストリームデータの中から、ファンクショントークンテーブル24に登録された内容に対応するビットストリームデータを読み出す。ファンクション回路管理部15は、FPGA2aにビットストリームデータを送信する。ビットストリームデータは、FPGA2aのコンフィグレーションメモリ26に書き込まれる。これにより、FPGA2aの回路領域31が再構成され、回路領域31にファンクション回路20-0,20-1が構築される。デバイスファイル16については、第2の実施例で説明する。

利用申請を受け取った開発者は、ホスト装置1aのAppを起動する。

ファンクション回路管理部15は、事前に登録されたビットストリームデータの中からファンクション名に対応するビットストリームデータを読み出す。ファンクション回路管理部15は、読み出したビットストリームデータを、Appから受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2aに送信する。

アクセス受付部23は、ファンクション回路20-0による処理結果を、ファンクション使用要求に対する応答として要求元のクライアント端末3に返送する。

ホスト装置1aのネットワークインタフェース部13を介してクライアント端末3からの利用完了通知を受け取ったAppは、利用が終わった機能に対応するファンクション名とトークンとをファンクショントークンテーブル24から削除するようFPGA2aに要求する。

ファンクション回路管理部15は、ファンクション回路を削除するビットストリームデータを、Appから受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2aに送信する。

FPGA2aの利用効率の向上は、FPGAシステムが提供するサービスの利用効率の向上に繋がるため、FPGAシステムを運用する開発者にとっては収益性の向上に繋がる。

また、本実施例では、ベンダーに依存したランタイムを使用しないため、FPGAシステムが特定のベンダーの技術に依存することがない。

次に、本実施例の第2の実施例について説明する。図2は本発明の第2の実施例に係るFPGAシステムの構成を示すブロック図である。本実施例では、FPGAシステムを構築するプラットフォームとしてkubernetesを用いる。kubernetesについては、例えば文献「“Kubernetesドキュメント”,Linux Foundation(登録商標),2021年,<https://kubernetes.io/ja/docs/home/>」に開示されている。以下、kubernetesのことをK8sと略する。

具体的には、K8sマスターノード4は、クライアントとの通信、アクセストークンの管理、ファンクションマネージャポッド(Function Manager Pod)50の起動・削除要求を行う。

HTTP(Hypertext Transfer Protocol)パーサー29は、要求の内容を解釈して、解釈の結果に基づく処理をファンクション回路またはファンクショントークンテーブル24に対して行う。

本実施例では、アプリケーション層の通信プロトコルとしてHTTPを例に挙げて説明するが、通信プロトコルはHTTPに限るものではない。

FPGAシステムの開発者は、クライアントに提供したいFPGA2bの機能を開発し、その機能を実現するファンクション回路を定義するためのビットストリームデータ503をホスト装置1bに格納しておく。

K8sマスターノード4は、クライアントから申請があった機能に割り当てるトークンを生成する(図3ステップS101)。図3の例では、作成したトークンを“XXX”とする。K8sマスターノード4は、クブレット51を介し、デバイスプラグイン52に従い、ポッド50を起動させる(図3ステップS102~S105)。

コンテナ501は、ホスト装置1bに事前に登録されたビットストリームデータ503の中からファンクション名に対応するビットストリームデータを読み出す。コンテナ501は、読み出したビットストリームデータを、コンテナ500から受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2bに送信する。

DMAブリッジコントローラ22は、回路書き込み完了通知をポッド50に対する応答として返送する。

FPGA2bのスイッチ28は、TOE27が発行するセッションIDに基づいて、TOE27から受け取ったデータがクライアントからのデータであることを検知する。そして、スイッチ28は、TOE27から受け取ったデータがファンクション使用要求であることから、HTTPパーサー29にファンクション使用要求を転送する。

FPGA2bのHTTPデパーサー30は、ファンクション回路20-0による処理結果を、ファンクション使用要求に対する応答データとして作成する。

TOE27は、スイッチ28から受け取った応答データから応答パケットを組み立てて、応答パケットをネットワークインタフェース部25を介して要求元のクライアント端末3に返送する。

そして、クライアントは、所望の処理の終了後に、クライアント端末3を用いてホスト装置1bのK8sマスターノード4にリソース解放通知を送る(図3ステップS111)。

ポッド削除要求を受け取ったポッド50のコンテナ500は、利用が終わった機能に対応するファンクション名とトークンとをファンクショントークンテーブル24から削除するようFPGA2bに要求する(図3ステップS114)。

コンテナ501は、ファンクション回路を削除するビットストリームデータを、コンテナ500から受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2bに送信する。

以上で、FPGAシステムの動作が終了する。

FPGAシステムの開発者は、クライアントに提供したいFPGA2bの機能を開発し、その機能を実現するファンクション回路を定義するためのビットストリームデータ503をホスト装置1bに格納しておく。

K8sマスターノード4は、クライアントから申請があった機能に割り当てるトークンを生成する(図4ステップS201)。図4の例では、作成したトークンを“XXX”とする。K8sマスターノード4は、クブレット51を介し、デバイスプラグイン52に従い、ポッド50を起動させる(図4ステップS202~S205)。

コンテナ501は、ホスト装置1bに事前に登録されたビットストリームデータ503の中からファンクション名に対応するビットストリームデータを読み出す。コンテナ501は、読み出したビットストリームデータを、コンテナ500から受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2bに送信する。

DMAブリッジコントローラ22は、回路書き込み完了通知をポッド50に対する応答として返送する。

クブレット51は、クライアントがファンクション回路を利用するためのコンテナ502を作成する(図4ステップS208~S210)。クブレット51は、コンテナ502の作成完了後、クライアント端末3にリソース割当完了を通知する(図4ステップS211,S212)。このリソース割当完了通知には、クライアントから申請があった機能を表すファンクション名とクライアントから申請があった機能に割り当てたトークンとが付加されている。

ホスト装置1bのコンテナ502は、クライアントからのファンクション使用要求をFPGA2bに送信する(図4ステップS214)。

FPGA2bのスイッチ28は、DMAブリッジコントローラ22が発行するセッションIDに基づいて、DMAブリッジコントローラ22から受け取ったデータがクライアントからのデータであることを検知する。そして、スイッチ28は、DMAブリッジコントローラ22から受け取ったデータがファンクション使用要求であることから、HTTPパーサー29にファンクション使用要求を転送する。

FPGA2bのHTTPデパーサー30は、ファンクション回路による処理結果を、ファンクション使用要求に対する応答データとして作成する。

DMAブリッジコントローラ22は、スイッチ28から受け取った応答データをホスト装置1bに返送する。

クライアントが希望する処理が終了するまで、ファンクション使用要求の送信と処理結果の受信とが繰り返し行われる。

リソース解放通知を受け取ったK8sマスターノード4は、クブレット51にポッド削除要求を送る(図4ステップS217)。

コンテナ501は、ファンクション回路を削除するビットストリームデータを、コンテナ500から受け取ったファンクションIDに対応するコンフィグレーションメモリ26の領域に書き込むためにFPGA2bに送信する。

以上で、FPGAシステムの動作が終了する。

FPGA2bの利用効率の向上は、FPGAシステムが提供するサービスの利用効率の向上に繋がるため、FPGAシステムを運用する開発者にとっては収益性の向上に繋がる。

また、本実施例では、ベンダーに依存したランタイムを使用しないため、FPGAシステムが特定のベンダーの技術に依存することがない。

Claims (7)

- FPGAと、

ホスト装置とを備え、

前記FPGAは、

再構成可能な回路領域と、

クライアントからのファンクション使用要求に含まれる処理対象のデータを前記回路領域に構築されたファンクション回路に転送し、このファンクション回路による処理結果を前記クライアントに返送するように構成されたアクセス受付部と、

前記回路領域の部分毎の識別情報であるファンクションIDと、前記ファンクション回路の機能を表すファンクション名と、前記ファンクション回路の識別情報であるトークンとが対応付けて格納されたテーブルとを備え、

前記アクセス受付部は、前記テーブルに格納された内容と、前記ファンクション使用要求に含まれるファンクション名とトークンとに基づいて、前記処理対象のデータを転送すべきファンクション回路を特定し、

前記ホスト装置は、前記ファンクション使用要求の前に、前記クライアントから機能の利用申請のためのリソース要求を受信したときに、前記利用申請があった機能に割り当てる前記トークンを生成し、生成したトークンと前記利用申請があった機能を表す前記ファンクション名とを前記FPGAと前記クライアントに送信するように構成されたアプリケーション実行部を備えることを特徴とするFPGAシステム。 - 請求項1記載のFPGAシステムにおいて、

前記アプリケーション実行部は、クライアント毎に異なる前記トークンを生成することを特徴とするFPGAシステム。 - 請求項1または2記載のFPGAシステムにおいて、

前記FPGAは、前記アプリケーション実行部から受信したファンクション名とトークンとを前記テーブルに書き込み、書き込みを行ったテーブルの行に割り当てたファンクションIDを前記アプリケーション実行部に返送するように構成されたコントローラをさらに備えることを特徴とするFPGAシステム。 - 請求項3記載のFPGAシステムにおいて、

前記ホスト装置は、前記テーブルに格納された内容に対応して前記ファンクション回路を再構成するためのビットストリームデータを前記FPGAに送信するように構成されたファンクション回路管理部をさらに備えることを特徴とするFPGAシステム。 - 請求項4記載のFPGAシステムにおいて、

前記ファンクション回路管理部は、前記クライアントから前記リソース要求を受信したときに、前記テーブルに格納された内容に対応して前記ファンクション回路を再構成するためのビットストリームデータを前記FPGAに送信し、前記クライアントからリソース解放通知を受信したときに、前記ファンクション回路を未定義の状態に戻すビットストリームデータを前記FPGAに送信することを特徴とするFPGAシステム。 - 請求項1乃至5のいずれか1項に記載のFPGAシステムにおいて、

前記FPGAは、前記クライアントとネットワークを介して通信を行うためのネットワークインタフェース部をさらに備え、

前記アクセス受付部は、前記クライアントからのファンクション使用要求を前記ネットワークインタフェース部を介して受信し、前記ファンクション回路による処理結果を前記ネットワークインタフェース部を介して前記クライアントに返送することを特徴とするFPGAシステム。 - 請求項1乃至5のいずれか1項に記載のFPGAシステムにおいて、

前記アプリケーション実行部は、前記クライアントからのファンクション使用要求を前記FPGAに送信し、前記FPGAから受信した処理結果を前記クライアントに返送し、

前記アクセス受付部は、前記ファンクション使用要求を前記アプリケーション実行部から受信し、前記ファンクション回路による処理結果を前記アプリケーション実行部に返送することを特徴とするFPGAシステム。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2021/031861 WO2023032023A1 (ja) | 2021-08-31 | 2021-08-31 | Fpgaおよびfpgaシステム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2023032023A1 JPWO2023032023A1 (ja) | 2023-03-09 |

| JP7690992B2 true JP7690992B2 (ja) | 2025-06-11 |

Family

ID=85410791

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023544828A Active JP7690992B2 (ja) | 2021-08-31 | 2021-08-31 | Fpgaシステム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20240429920A1 (ja) |

| JP (1) | JP7690992B2 (ja) |

| WO (1) | WO2023032023A1 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015207832A (ja) | 2014-04-17 | 2015-11-19 | キヤノン株式会社 | 再構成可能回路を含む電子装置及び画像処理装置及び画像処理方法 |

| JP2016063490A (ja) | 2014-09-19 | 2016-04-25 | 株式会社東芝 | 再構成可能な半導体集積回路および電子機器 |

| JP2021086341A (ja) | 2019-11-27 | 2021-06-03 | 株式会社リコー | ユーザ認証システム、ユーザ認証方法、およびユーザ認証プログラム |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11436160B2 (en) * | 2019-10-03 | 2022-09-06 | Microsoft Technology Licensing, Llc | Protection of data in memory of an integrated circuit using a secret token |

-

2021

- 2021-08-31 US US18/684,807 patent/US20240429920A1/en active Pending

- 2021-08-31 JP JP2023544828A patent/JP7690992B2/ja active Active

- 2021-08-31 WO PCT/JP2021/031861 patent/WO2023032023A1/ja not_active Ceased

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015207832A (ja) | 2014-04-17 | 2015-11-19 | キヤノン株式会社 | 再構成可能回路を含む電子装置及び画像処理装置及び画像処理方法 |

| JP2016063490A (ja) | 2014-09-19 | 2016-04-25 | 株式会社東芝 | 再構成可能な半導体集積回路および電子機器 |

| JP2021086341A (ja) | 2019-11-27 | 2021-06-03 | 株式会社リコー | ユーザ認証システム、ユーザ認証方法、およびユーザ認証プログラム |

Non-Patent Citations (1)

| Title |

|---|

| 宇野 正樹 他,DRLチップを用いたリコンフィギュラブルテストベッド上におけるWASMIIシステム,電子情報通信学会技術研究報告,社団法人電子情報通信学会,2002年01月16日,Vol.101 No.578,第9頁-第16頁,ISSN:0913-5685 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2023032023A1 (ja) | 2023-03-09 |

| US20240429920A1 (en) | 2024-12-26 |

| JPWO2023032023A1 (ja) | 2023-03-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11157304B2 (en) | System for peering container clusters running on different container orchestration systems | |

| US10698717B2 (en) | Accelerator virtualization method and apparatus, and centralized resource manager | |

| US8201190B2 (en) | Sharing a network I/O adapter between logical partitions | |

| CN112416737B (zh) | 一种容器的测试方法、装置、设备和存储介质 | |

| CN111324558A (zh) | 数据处理方法、装置、分布式数据流编程框架及相关组件 | |

| US20110239216A1 (en) | Service providing system, a virtual machine server, a service providing method, and a program thereof | |

| CN113268308A (zh) | 信息处理方法、装置以及存储介质 | |

| WO2022143714A1 (zh) | 服务器系统、虚拟机创建方法及装置 | |

| CN110532106B (zh) | 进程间的通讯方法、装置、设备和存储介质 | |

| CN116383127B (zh) | 节点间通信方法、装置、电子设备及存储介质 | |

| US12452331B1 (en) | File-sharing method, apparatus and system, electronic device, and storage medium | |

| US20250190237A1 (en) | Device access method and system for secure docker | |

| CN115509435A (zh) | 一种数据读写方法、装置、设备、介质 | |

| CN117061270A (zh) | 一种基于分布式软总线实现远程设备本地化虚拟与访问的方法 | |

| US8442939B2 (en) | File sharing method, computer system, and job scheduler | |

| JP7690992B2 (ja) | Fpgaシステム | |

| US11221807B2 (en) | Non-transitory computer-readable medium and device management system | |

| WO2021258861A1 (zh) | 一种作业处理方法以及相关设备 | |

| CN117041147B (zh) | 智能网卡设备、主机设备和方法及系统 | |

| JP2024541872A (ja) | コンテナ・エンジン及びコンテナ・エンジンの実現方法 | |

| CN115225693A (zh) | 一种容器间的通信方法及相关产品 | |

| JP7709666B2 (ja) | ネットワーク管理装置、ネットワーク管理方法及びプログラム | |

| CN114237738B (zh) | 设备管理方法、装置、电子设备及计算机可读存储介质 | |

| US11849005B2 (en) | Method and apparatus for accelerating network transmission in memory-disaggregated environment | |

| CN117648210A (zh) | 一种远程访问图形处理器的方法和装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20240130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20241217 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20250124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250430 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250513 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7690992 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |