JP7581312B2 - Display device - Google Patents

Display device Download PDFInfo

- Publication number

- JP7581312B2 JP7581312B2 JP2022211895A JP2022211895A JP7581312B2 JP 7581312 B2 JP7581312 B2 JP 7581312B2 JP 2022211895 A JP2022211895 A JP 2022211895A JP 2022211895 A JP2022211895 A JP 2022211895A JP 7581312 B2 JP7581312 B2 JP 7581312B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- subpixel

- signal

- gate

- row

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000011159 matrix material Substances 0.000 claims description 3

- 239000003990 capacitor Substances 0.000 description 136

- 238000010586 diagram Methods 0.000 description 58

- 230000007704 transition Effects 0.000 description 58

- 238000004364 calculation method Methods 0.000 description 28

- 238000009825 accumulation Methods 0.000 description 18

- 230000004044 response Effects 0.000 description 18

- 230000010354 integration Effects 0.000 description 10

- 101100313728 Vitis vinifera VINST1 gene Proteins 0.000 description 9

- 238000006243 chemical reaction Methods 0.000 description 9

- 230000006870 function Effects 0.000 description 9

- 101100491263 Oryza sativa subsp. japonica AP2-4 gene Proteins 0.000 description 8

- 101100311249 Schizosaccharomyces pombe (strain 972 / ATCC 24843) stg1 gene Proteins 0.000 description 8

- 101100041125 Arabidopsis thaliana RST1 gene Proteins 0.000 description 7

- 101100448781 Oryza sativa subsp. indica GL18 gene Proteins 0.000 description 7

- 101100443250 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) DIG1 gene Proteins 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 7

- 101100443251 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) DIG2 gene Proteins 0.000 description 6

- 101100041128 Schizosaccharomyces pombe (strain 972 / ATCC 24843) rst2 gene Proteins 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 6

- 238000006731 degradation reaction Methods 0.000 description 6

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 6

- 238000000034 method Methods 0.000 description 4

- 101001019455 Homo sapiens ICOS ligand Proteins 0.000 description 3

- 101000885321 Homo sapiens Serine/threonine-protein kinase DCLK1 Proteins 0.000 description 3

- 102100034980 ICOS ligand Human genes 0.000 description 3

- 102100039758 Serine/threonine-protein kinase DCLK1 Human genes 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 238000013528 artificial neural network Methods 0.000 description 2

- 238000010801 machine learning Methods 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

Description

本発明は、表示装置に関する。 The present invention relates to a display device.

特許文献1には、2つの副画素が1本のデータ線を共有するダブルレート駆動(Double Rate Driving:DRD)を用いた表示装置が開示されている。

特許文献1に記載されている表示装置においては、消費電力の低減の観点において十分でない場合がある。

The display device described in

本発明は、上述した課題に鑑みてなされたものであって、消費電力が低減された表示装置を提供することを目的とする。 The present invention has been made in consideration of the above-mentioned problems, and aims to provide a display device with reduced power consumption.

本発明の一観点によれば、行列状に配列された複数の副画素、行方向に延在する複数のゲート線、および列方向に延在する複数のデータ線を有する表示パネルと、前記複数のゲート線を介して、前記複数の副画素をアクティブにするための複数のゲート信号を前記複数の副画素に供給するゲート駆動部と、前記複数のデータ線を介して、前記複数の副画素の輝度に対応する複数のデータ信号を前記複数の副画素に供給するデータ駆動部と、前記ゲート駆動部および前記データ駆動部を制御するタイミング制御部と、を含み、前記複数の副画素は、第1の行において前記複数のデータ線のうちの第1のデータ線を共有する第1の色の第1の副画素および第2の色の第2の副画素、第2の行において前記第1のデータ線を共有する前記第1の色の第3の副画素および前記第2の色の第4の副画素を含み、前記タイミング制御部は、前記第1の副画素の前記データ信号が前記第3の副画素の前記データ信号に類似すると判定した場合に、前記第1の副画素に続いて前記第3の副画素に前記データ信号を供給させるように、前記ゲート駆動部および前記データ駆動部を制御する、表示装置が提供される。 According to one aspect of the present invention, there is provided a display device including a display panel having a plurality of subpixels arranged in a matrix, a plurality of gate lines extending in a row direction, and a plurality of data lines extending in a column direction; a gate driver that supplies a plurality of gate signals to the plurality of subpixels via the plurality of gate lines to activate the plurality of subpixels; a data driver that supplies a plurality of data signals corresponding to the luminance of the plurality of subpixels via the plurality of data lines to the plurality of subpixels; and a timing controller that controls the gate driver and the data driver, the plurality of subpixels including a first subpixel of a first color and a second subpixel of a second color that share a first data line of the plurality of data lines in a first row, and a third subpixel of the first color and a fourth subpixel of the second color that share the first data line in a second row, and the timing controller controls the gate driver and the data driver to supply the data signal to the third subpixel following the first subpixel when it is determined that the data signal of the first subpixel is similar to the data signal of the third subpixel.

本発明によれば、消費電力が低減された表示装置を提供することができる。 The present invention provides a display device with reduced power consumption.

以下、本発明に係る実施形態について図面を参照しつつ詳細に説明する。各図面を通じて共通する機能を有する要素には同一の符号を付し、重複する説明を省略または簡略化することがある。 Embodiments of the present invention will be described in detail below with reference to the drawings. Elements having common functions throughout the drawings will be given the same reference numerals, and duplicate descriptions may be omitted or simplified.

[第1実施形態]

図1は、本実施形態に係る表示装置10の概略構成を示すブロック図である。本実施形態に係る表示装置10は有機発光ダイオード表示装置であるがこれに限定されない。例えば、本発明に係る表示装置10は液晶表示装置であり得る。表示装置10は、表示パネル100、ゲート駆動部200、データ駆動部300、電源400およびタイミング制御部500を有する。

[First embodiment]

1 is a block diagram showing a schematic configuration of a

表示パネル100は表示装置10の表示画像を構成する。表示パネル100は、ゲート駆動部200から行方向に延在するゲート線GL1~GLnとデータ駆動部300から列方向に延在するデータ線DL1~DLm(m、nは正の整数、以下同様)とが交差して画定される各画素領域に、行列状に配列された複数の副画素Pを含む。ゲート線GL1~GLnの各々に沿って隣接する一対の副画素は、データ線DL1~DLmのうちの1本を共有するように配置されている。

The

ゲート駆動部200は、ゲート制御信号GCSに基づいて決定された順序でゲート線GL1~GLnの各々にゲート信号を出力する。ゲート駆動部200は、レベルシフタ、シフトレジスタ、遅延回路、フリップフロップ等の内部回路を備え、ゲート制御信号GCSに応じて、ゲート開始パルス信号GSP、ゲートシフトクロック信号GSC、ゲート出力イネーブル信号GOE等の制御信号を連続的に生成する。ゲート開始パルス信号GSPは、ゲート駆動部200に含まれるゲートドライバ集積回路の動作の開始のタイミングを制御する。ゲートシフトクロック信号GSCは、ゲートドライバ集積回路に共通に入力されるクロック信号であり、走査信号(ゲート信号)のシフトタイミングを制御する。ゲート出力イネーブル信号GOEは、ゲートドライバ集積回路のタイミング情報を指定する。ゲート駆動部200は、ゲートシフトクロック信号GSCに応じてゲート開始パルス信号GSPをシフトすることにより、連続してゲート信号を生成する。また、ゲート駆動部200は、生成されたゲート信号をゲート線GL1~GLnの各々に供給する。ゲート線GL1~GLnを介して供給されるゲート信号は、表示パネル100に含まれる複数の副画素の各々をアクティブにするために用いられる。ゲート駆動部200は、タイミング制御部500によって出力幅が変調されたデータイネーブル信号DEおよびデータイネーブル信号DEによって出力幅が変化したゲート出力イネーブル信号GOEによってゲート信号の出力幅を制御する。なお、ゲート駆動部200の配置は図1に示さされる形態に限定されない。例えば、ゲート駆動部200は、表示パネル100の両端に存する非表示領域に配されることもできる。

The gate driver 200 outputs gate signals to each of the gate lines GL1 to GLn in an order determined based on the gate control signal GCS. The gate driver 200 includes internal circuits such as a level shifter, a shift register, a delay circuit, and a flip-flop, and continuously generates control signals such as a gate start pulse signal GSP, a gate shift clock signal GSC, and a gate output enable signal GOE in response to the gate control signal GCS. The gate start pulse signal GSP controls the timing of the start of operation of the gate driver integrated circuit included in the gate driver 200. The gate shift clock signal GSC is a clock signal commonly input to the gate driver integrated circuits, and controls the shift timing of the scanning signal (gate signal). The gate output enable signal GOE specifies the timing information of the gate driver integrated circuit. The gate driver 200 continuously generates gate signals by shifting the gate start pulse signal GSP in response to the gate shift clock signal GSC. The gate driver 200 also supplies the generated gate signals to each of the gate lines GL1 to GLn. The gate signals supplied via the gate lines GL1 to GLn are used to activate each of the sub-pixels included in the

データ駆動部300は、タイミング制御部500によって整列された画像データR’G’B’W’を行毎にタイミング制御部500から受信する。データ駆動部300は、ソース・スタート・パルス信号SSP、ソース・シフト・クロック信号SSCおよびソース出力イネーブル信号SOEを含むデータ制御信号DSCをタイミング制御部500から受信する。ソース・スタート・パルス信号SSPは、データ駆動部300に含まれるソースドライバ集積回路のデータサンプリングの開始のタイミングを制御する。ソース・シフト・クロック信号SSCは、ソースドライバ集積回路の各々でデータのサンプリングのタイミングを制御するクロック信号である。ソース出力イネーブル信号SOEは、データ駆動部300からの信号の出力タイミングを制御する。データ駆動部300は、データ制御信号DSCを用いて、画像データRGBWを整列させ、各行に対するアナログのデータ電圧に変換する。なお本発明は、画像データ形式がRGBWの表示装置だけでなく、白色サブピクセルを含まないRGBの表示装置や、黄色サブピクセルを含むRGBYの表示装置にも同じように適用できる。以下の説明ではRGBWを用いるが、それに限定されるものではない。

The

具体的には、データ駆動部300は、ソース出力イネーブル信号SOEに応じてゲート信号がゲート線GL1~GLnの各々に供給される1水平周期毎に、ソース・シフト・クロック信号SSCに応じて整列された画像データR’G’B’W’を1行毎にサンプリングしてデータ電圧DATAに変換する。データ駆動部300は、アナログ信号であるデータ電圧DATAを、データ線DL1~DLmを介しての表示パネル100に含まれる複数の副画素の各々に供給する。データ駆動部300のデータ電圧への変換期間および出力期間は、タイミング制御部500により出力幅が変調されたデータイネーブル信号DEおよびデータイネーブル信号DEにより出力幅が変更されたソース出力イネーブル信号SOEに応じて変更されることができる。データ駆動部300は、データ線方向に配置された同色の副画素を所定の行数だけ連続して発光させるようにデータ電圧を生成し、ゲート信号の出力タイミングと同期させてデータ電圧をデータ線DL1~DLmを介して表示パネル100に含まれる複数の副画素の各々に連続して供給する。複数の副画素に供給される複数のデータ電圧は、それぞれ複数の画素の輝度に対応する。

Specifically, the

電源400は、電源線を介して各副画素Pに高電位側の電源電圧VDDおよび低電位側の電源電圧VSSを供給する。また、電源400は、補償電源線CPLを介して各副画素Pに補償電圧Vrefを供給する。 The power supply 400 supplies a high-potential side power supply voltage VDD and a low-potential side power supply voltage VSS to each subpixel P via a power supply line. The power supply 400 also supplies a compensation voltage Vref to each subpixel P via a compensation power supply line CPL.

タイミング制御部500は、ダブルレート駆動(DRD)により表示パネル100の副画素Pを駆動するための信号を生成する。タイミング制御部500は、データ線DL1~DLmの方向に沿って配置された同色の副画素を所定の行数だけ発光させるように画像データRGBWを整列させる。また、タイミング制御部500は、入力された画像データRGBWを整列させてからデータ駆動部300に出力することにより、副画素Pを1フレーム単位ごとに異なる駆動順序で動作させ、同色の副画素を所定の行数だけ連続して発光させる。

The

また、タイミング制御部500は、ドットクロックDCLK、データイネーブル信号DE、水平同期信号Hsync、垂直同期信号Vsync等の信号を用いてゲート制御信号GCSおよびデータ制御信号DSCを生成する。タイミング制御部500は、表示装置10をDRD方式で駆動するために、生成したゲート制御信号GCSをゲート駆動部200に、データ制御信号DSCをデータ駆動部300にそれぞれ送信する。タイミング制御部500は、データ線DL1~DLmの方向に沿って配置された同色の副画素Pを、DRD法によって同色の副画素を所定の行数だけ連続して発光させるように、ゲート制御信号GCSおよびデータ制御信号DSCを生成することができる。

The

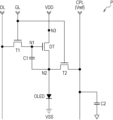

表示装置10に含まれるゲート線GL1~GLn、データ線DL1~DLmおよび副画素Pの接続関係について、図2を参照して詳細に説明する。図2は本実施形態に係る副画素Pの等価回路図である。副画素Pの各々は、有機発光ダイオードOLED、駆動素子DT、第1スイッチ素子T1、第2スイッチ素子T2、第1キャパシタC1、第2キャパシタC2を含む。また、副画素Pはデータ線DL、ゲート線GL、高電位側の電源電圧VDD、低電位側の電源電圧VSSおよび補償電源線CPLと接続される。有機発光ダイオードOLEDは、本実施形態では画素面を構成する赤色(R)、緑色(G)、青色(B)または白色(W)のいずれかの発光色を有する。有機発光ダイオードOLEDのアノードは駆動素子DTを介して電源電圧VDDに接続され、有機発光ダイオードOLEDのカソードは電源電圧VSSに接続される。

The connection relationship between the gate lines GL1 to GLn, the data lines DL1 to DLm, and the sub-pixels P included in the

駆動素子DT、第1スイッチ素子T1および第2スイッチ素子T2はMOSFET(金属酸化膜半導体電界効果トランジスタ)から構成され得る。駆動素子DTのゲートは第1ノードN1を介して第1スイッチ素子T1のソースに接続され、駆動素子DTのドレインは第3ノードN3を介して電源電圧VDDに接続され、駆動素子DTのソースは第2ノードN2を介して有機発光ダイオードOLEDのアノードに接続される。第1スイッチ素子T1のゲートはゲート線GLに接続され、第1スイッチ素子T1のドレインはデータ線DLに接続される。第1キャパシタC1は、第1ノードN1と第2ノードN2との間に接続される。第2スイッチ素子T2のゲートはゲート線GLに接続され、第2スイッチ素子T2のドレインは第2ノードN2に接続され、第2スイッチ素子T2のソースは補償電源線CPLに接続される。第2スイッチ素子T2は、ゲート線GLからのゲート信号に応答して、補償電源線CPLを介して入力される補償電圧Vrefを第2ノードN2に供給し、データ電圧の出力端子である駆動素子DTのドレイン端子の電位を補償する。補償電源線CPLには補償電圧Vrefを安定化させるために第2キャパシタC2が接続されている。 The driving element DT, the first switch element T1 and the second switch element T2 may be composed of MOSFETs (metal oxide semiconductor field effect transistors). The gate of the driving element DT is connected to the source of the first switch element T1 via the first node N1, the drain of the driving element DT is connected to the power supply voltage VDD via the third node N3, and the source of the driving element DT is connected to the anode of the organic light emitting diode OLED via the second node N2. The gate of the first switch element T1 is connected to the gate line GL, and the drain of the first switch element T1 is connected to the data line DL. The first capacitor C1 is connected between the first node N1 and the second node N2. The gate of the second switch element T2 is connected to the gate line GL, the drain of the second switch element T2 is connected to the second node N2, and the source of the second switch element T2 is connected to the compensation power supply line CPL. In response to a gate signal from the gate line GL, the second switch element T2 supplies the compensation voltage Vref input via the compensation power line CPL to the second node N2, thereby compensating for the potential of the drain terminal of the driving element DT, which is the output terminal of the data voltage. A second capacitor C2 is connected to the compensation power line CPL to stabilize the compensation voltage Vref.

ゲート線GLのレベルによって有機発光ダイオードOLEDの駆動または停止が決定され、有機発光ダイオードOLEDが駆動される場合にはデータ線DLの電圧によってその輝度が決定される。有機発光ダイオードOLEDが走査(駆動)される場合にゲート線GLのレベルはハイレベルとなり、それ以外の場合にはゲート線GLのレベルはローレベルとなる。ゲート線GLのレベルがハイレベルとなると、第1スイッチ素子T1がオンされ、データ線DLの電圧に基づく電圧が第1キャパシタC1に充電される。第1キャパシタC1の電圧が駆動素子DTのオン閾値を超えると、駆動素子DTがオンされる。オン状態の駆動素子DTは、ゲート電圧、即ち、データ線DLの電圧と補償電圧Vrefとの間の電位差に応じたドレイン電流を電源電圧VDDから有機発光ダイオードOLEDに供給する。このドレイン電流に応じて、有機発光ダイオードOLEDが発光する。第1キャパシタC1は、いわゆるストレージキャパシタとして機能し、ある走査フレームにおける駆動素子DTのゲート-ソース電圧を次の走査フレームまで保持して有機発光ダイオードOLEDの発光状態または消灯状態を維持する。 The level of the gate line GL determines whether the organic light emitting diode OLED is driven or not, and when the organic light emitting diode OLED is driven, its brightness is determined by the voltage of the data line DL. When the organic light emitting diode OLED is scanned (driven), the level of the gate line GL becomes high level, and otherwise the level of the gate line GL becomes low level. When the level of the gate line GL becomes high level, the first switch element T1 is turned on, and a voltage based on the voltage of the data line DL is charged to the first capacitor C1. When the voltage of the first capacitor C1 exceeds the on threshold of the driving element DT, the driving element DT is turned on. The driving element DT in the on state supplies a drain current corresponding to the gate voltage, that is, the potential difference between the voltage of the data line DL and the compensation voltage Vref, from the power supply voltage VDD to the organic light emitting diode OLED. The organic light emitting diode OLED emits light in response to this drain current. The first capacitor C1 functions as a so-called storage capacitor, and holds the gate-source voltage of the driving element DT in a certain scanning frame until the next scanning frame, thereby maintaining the light-emitting or non-light-emitting state of the organic light-emitting diode OLED.

図3は、本実施形態に係る表示パネル100の概略構成を示す平面図である。表示パネル100上には2次元配列された複数の副画素Pを有する画素面が構成される。複数の副画素Pは、緑色副画素G、赤色副画素R、白色副画素W、および青色副画素Bを含む。各色の副画素は、ゲート線GL1~GLnとデータ線DL1~DLmとが交差して画定される各画素領域に配される。各色の副画素Pは、それぞれデータ線DLに沿って列をなすように設けられている。一例として、緑色副画素Gおよび赤色副画素Rは互いに隣接して配列され、1本のデータ線DL1が緑色副画素Gと赤色副画素Rとの間に設けられている。各行において互いに隣接する一対の副画素である緑色副画素Gおよび赤色副画素Rは、各副画素の第1スイッチ素子T1を介して同一のデータ線DL1に接続されている。即ち、一対の副画素である緑色副画素Gおよび赤色副画素Rは、1本のデータ線DL1を共有している。同様に、白色副画素Wおよび青色副画素Bは互いに隣接して配列され、1本のデータ線DL2が白色副画素Wと青色副画素Bとの間に設けられている。各行において互いに隣接する一対の副画素である白色副画素Wおよび青色副画素Bは、各副画素の第1スイッチ素子T1を介して同一のデータ線DL2に接続されている。即ち、一対の副画素である白色副画素Wおよび青色副画素Bは、1本のデータ線DL2を共有している。表示パネル100に含まれるすべての副画素に対して上述のようにデータ線を配することで、表示パネル100に配されるデータ線DL1~DLmの本数は、副画素の列の合計数の半数となる。

FIG. 3 is a plan view showing a schematic configuration of a

また、赤色副画素Rおよび白色副画素Wは互いに隣接して配列され、補償電源線CPLが赤色副画素Rと白色副画素Wとの間に設けられている。各色の副画素は、各副画素の第2スイッチ素子T2を介して補償電源線CPLに接続されている。各行の赤色副画素Rおよび白色副画素Wに含まれる第1スイッチ素子T1のゲートおよび第2スイッチ素子T2のゲートは、それぞれゲート線GL1~GLnのうちの第1ゲート線に接続される。また、同行に配置された緑色副画素Gおよび青色副画素Bに含まれる第1スイッチ素子T1のゲートおよび第2スイッチ素子T2のゲートは、それぞれゲート線GL1~GLnのうちの第1ゲート線とは別の第2ゲート線に接続される。他の行の副画素に対しては、第1のゲート線および第2のゲート線とは別の2本のゲート線が同様の接続関係で配される。表示パネル100に含まれるすべての副画素に対して上述のようにゲート線を配することで、表示パネル100に配されるゲート線GL1~GLnの本数は、副画素の行の合計数の倍となる。なお、緑色副画素G、赤色副画素R、白色副画素W、および青色副画素Bの配列の順序は図3の順序に限定されず適宜変更することができる。また、本実施形態では、奇数列に緑色副画素Gおよび白色副画素Wを配し、偶数列に赤色副画素Rおよび青色副画素Bを配することとしたが、副画素の配列はこれに限定されず適宜変更することができる。さらに、本実施形態では、奇数列に配された緑色副画素Gと偶数列に配された赤色副画素Rが1本のデータ線DL1を共有し、奇数列に配された白色副画素Wと偶数列に配された青色副画素Bとが1本のデータ線DL2を共有することとしたが、データ線を共有する画素列はこれに限定されず適宜変更することができる。例えば、奇数列に配された緑色副画素Gおよび白色副画素Wが1本のデータ線DL1を共有し、偶数列に配された赤色副画素Rおよび青色副画素Bが1本のデータ線DL2を共有するように構成することができる。

The red subpixel R and the white subpixel W are arranged adjacent to each other, and a compensation power line CPL is provided between the red subpixel R and the white subpixel W. The subpixels of each color are connected to the compensation power line CPL via the second switch element T2 of each subpixel. The gates of the first switch element T1 and the second switch element T2 included in the red subpixel R and the white subpixel W of each row are connected to a first gate line among the gate lines GL1 to GLn. The gates of the first switch element T1 and the second switch element T2 included in the green subpixel G and the blue subpixel B arranged in the same row are connected to a second gate line different from the first gate line among the gate lines GL1 to GLn. For the subpixels of the other rows, two gate lines different from the first gate line and the second gate line are arranged in a similar connection relationship. By providing gate lines for all subpixels included in the

図4は、本実施形態に係るタイミング制御部の概略構成を示すブロック図である。タイミング制御部500は、信号変調部510、行メモリ部520、データ制御信号生成部530、ゲート制御信号生成部540、類似度判定部550およびスケジューラ560を含む。

Figure 4 is a block diagram showing a schematic configuration of the timing control unit according to this embodiment. The

信号変調部510は、データイネーブル信号DEのパルス幅を変調する。例えば、同色の副画素を連続して走査する場合に、変調されたデータイネーブル信号tDEを生成し、

副画素ごとに別個の充電期間を設定することができる。信号変調部510は、変調されたデータイネーブル信号tDEを、行メモリ部520、データ制御信号生成部530およびゲート制御信号生成部540に伝送する。

The

A separate charging period can be set for each sub-pixel. The

行メモリ部520は、行単位で画像データRGBWを保存する。例えば、行メモリ部520は、第x行の画像データRGBW(x)を保存する(xは正の整数、以下同様)。行メモリ部520は第(x-1)行の画像データRGBW(x-1)を類似度判定部550に伝送する。行メモリ部520は、信号変調部510から受信した変調されたデータイネーブル信号tDEに基づいて画像データRGBWを整列させる。行メモリ部520は、整列された画像データR’G’B’W’をデータ駆動部300に伝送する。

The

データ制御信号生成部530は、変調されたデータイネーブル信号tDE、ドットクロックDCLK、垂直同期信号Vsync等の信号を用いてデータ制御信号DSCを生成する。具体的には、データ制御信号生成部530は、変調されたデータイネーブル信号tDEを用いてソース出力イネーブル信号SOEの出力幅を変調し、各副画素のための充電期間を調整する。また、データ制御信号生成部530は、生成したソース・スタート・パルス信号SSP、ソース・シフト・クロック信号SSCをデータ駆動部300に伝送する。

The data control

ゲート制御信号生成部540は、変調されたデータイネーブル信号tDE、ドットクロックDCLK、水平同期信号Hsync等の信号を用いてゲート制御信号GCSを生成する。具体的には、ゲート制御信号生成部540は、変調されたデータイネーブル信号tDEを用いてゲート出力イネーブル信号GOEの出力幅を変調し、副画素のためのゲート信号の供給期間を調整する。また、ゲート制御信号生成部540は、生成したソース・スタート・パルス信号SSP、ソース・シフト・クロック信号SSCをデータ駆動部300に伝送する。

The gate control

類似度判定部550は、2行分の画像データの類似度を判定し、判定結果RESをスケジューラ560に伝送する。例えば、類似度判定部550は。行メモリ部520から第(x-1)行の画像データRGBW(x-1)を受信し、第x行の画像データRGBW(x)と類似しているか判定する。例えば、類似度判定部550は、2行の間の画像データが互いに類似すると判定したときに判定結果RESとして1を出力する。一方、類似度判定部550は、2行の間の画像データが互いに類似しないと判定したときに判定結果RESとして0を出力する。

The

スケジューラ560は、類似度判定部550から受信した判定結果RESに基づき、ゲート信号を送信するゲート線GLの番号を指定するゲート線指定信号GL_Numを生成する。ゲート線指定信号GL_Numは、変調されたデータイネーブル信号tDEを生成するために変調部510に伝送される。また、スケジューラ560は、行メモリ部520から伝送される画像データR’G’B’W’が格納されるべきレジスタを指定するためのレジスタ選択信号RSSをデータ駆動部300に伝送する。データ駆動部300は、受信したレジスタ選択信号RSSに基づき、画像データR’G’B’W’を指定されたレジスタに格納する。

The

図5は、本実施形態に係るゲート駆動部200の概略構成を示すブロック図である。ゲート駆動部200は、第1レベルシフタ211、第2レベルシフタ212、第1シフトレジスタ221、222および第2シフトレジスタ231、232を含む。

Figure 5 is a block diagram showing a schematic configuration of the gate driver 200 according to this embodiment. The gate driver 200 includes a

第1レベルシフタ211および第2レベルシフタ212は、タイミング制御部500から入力されるクロック信号CLK1のTTL(Transistor-Transistor-Logic)レベルを遷移させる。具体的には、第1レベルシフタ211および第2レベルシフタ212は、表示パネル100に含まれるトランジスタをオン状態とオフ状態との間を遷移させるために、ゲートハイ電圧とゲートロー電圧との間を切り替えるための信号を生成する。第1レベルシフタ211は、生成された信号を第1シフトレジスタ221に伝送する。第2レベルシフタ212は、生成された信号を第1シフトレジスタ222に伝送する。また、第1レベルシフタ211は、タイミング制御部500から入力されるクロック信号CLK2のTTLレベルを遷移させる。具体的には、第1レベルシフタ211および第2レベルシフタ212は、表示パネル100に含まれるトランジスタをオン状態とオフ状態との間を遷移させるために、ゲートハイ電圧とゲートロー電圧との間を切り替えるための信号を生成する。第1レベルシフタ211は、生成された信号を第2シフトレジスタ231に伝送する。第2レベルシフタ212は、生成された信号を第2シフトレジスタ232に伝送する。

The

第1シフトレジスタ221、222の各々は、複数のステージを含む。複数のステージの各々は、Qノード、Qbノード、プルアップ素子およびプルダウン素子を含む。第1シフトレジスタ221、222は、表示パネル100の表示領域110の外側の非表示領域内にゲートインパネル(Gate-In-Panel,GIP)方式で配置される。例えば、第1シフトレジスタ221は、図5に示されるように、平面視において表示領域110の一方の短辺部(図5において左側短辺部)に隣接する非表示領域内に配置されることができる。また、第1シフトレジスタ222は、図5に示されるように、平面視において表示領域110の他方の短辺部(図5において右側短辺部)に隣接する非表示領域内に配置されることができる。第1シフトレジスタ221からのゲート線GLは、第1シフトレジスタ222からのゲート線GLと互いに連結された構造を有し得る。

Each of the

第1シフトレジスタ221は、第1レベルシフタ211から受信された信号に基づきゲート線GLにゲート信号を供給する。また、第1シフトレジスタ222は、第2レベルシフタ212から受信された信号に基づきゲート線GLにゲート信号を供給する。第1シフトレジスタ221、222は、タイミング制御部500からゲートスタート信号VST1を受信する。第1シフトレジスタ221、222は、受信されたゲートスタート信号VST1に基づき、キャリー信号を順次に生成する。第1シフトレジスタ221、222は、生成されたキャリー信号をゲートスタート信号として第1シフトレジスタ221、222に含まれる複数のステージのいずれかに供給する。第1シフトレジスタ221、222は、1フレームの走査開始時または1フレームの走査終了時にタイミング制御部500からリセット信号RST1を受信する。リセット信号RST1を介してQノードをリセットすることで、第1シフトレジスタ221、222のQノードおよびQBノードの電圧を安定的に維持させることができる。

The

第2シフトレジスタ231、232の各々は、複数のステージを含む。複数のステージの各々は、Qノード、Qbノード、プルアップ素子およびプルダウン素子を含む。第2シフトレジスタ231、232は、表示パネル100の表示領域110の外側の非表示領域内にゲートインパネル(Gate-In-Panel,GIP)方式で配置される。例えば、第2シフトレジスタ231は、図5に示されるように、平面視において表示領域110の一方の短辺部(図5において左側短辺部)に隣接する非表示領域内に、第1シフトレジスタ221と重畳するように配置されることができる。また、第2シフトレジスタ232は、図5に示されるように、平面視において表示領域110の他方の短辺部(図5において右側短辺部)に隣接する非表示領域内に、第1シフトレジスタ222と重畳するように配置されることができる。また、第2シフトレジスタ231、232は、それぞれ第1シフトレジスタ221、222と同一の領域に配置されることができる。即ち、本実施形態によるゲート駆動部200は、第2シフトレジスタ231、232から表示領域110までの距離が第1シフトレジスタ221、222からから表示領域110までの距離と同じとなるように構成され得る。また、第2シフトレジスタ231からのゲート線GLは、第2シフトレジスタ232からのゲート線GLと互いに連結された構造を有し得る。

Each of the

第2シフトレジスタ231は、第1レベルシフタ211から受信された信号に基づきゲート線GLにゲート信号を供給する。また、第2シフトレジスタ232は、第2レベルシフタ212から受信された信号に基づきゲート線GLにゲート信号を供給する。第2シフトレジスタ231、232は、タイミング制御部500からゲートスタート信号VST2を受信する。ここで、第2シフトレジスタ231、232がゲートスタート信号VST2を受信するタイミングは、第1シフトレジスタ221、222がゲートスタート信号VST1を受信するタイミングと異なる。第2シフトレジスタ231、232は、受信されたゲートスタート信号VST2に基づき、キャリー信号を順次に生成する。第2シフトレジスタ231、232は、生成されたキャリー信号をゲートスタート信号として第2シフトレジスタ231、232に含まれる複数のステージのいずれかに供給する。第2シフトレジスタ231、232は、1フレームの走査開始時または1フレームの走査終了時にタイミング制御部500からリセット信号RST2を受信する。リセット信号RST2を介してQノードをリセットすることで、第2シフトレジスタ231、232のQノードとQBノードの電圧を安定的に維持させることができる。ここで、第2シフトレジスタ231、232がリセット信号RST2を受信するタイミングは、第1シフトレジスタ221、222がリセット信号RST1を受信するタイミングと異なる。即ち、本実施形態による第2シフトレジスタ231、232は、回路構成上において第1シフトレジスタ221、222から独立して動作する。なお、ゲートスタート信号VST1およびゲートスタート信号VST2として、共通のゲートスタート信号が用いられることもできる。ただし、共通のゲートスタート信号が用いられた場合、ゲートスタート信号が入力されてから最初のクロックが入力されるまでシフトレジスタのステージはオン状態で待機することになる。よって、動作の安定性の観点から、相互に独立した信号であるゲートスタート信号VST1およびゲートスタート信号VST2を用いることが望ましい。

The

図6は本実施形態に係る第1シフトレジスタ221,222に含まれるステージとクロック配線との間の接続を示す回路図である。第1シフトレジスタ221,222は複数のステージを含む。複数のステージの各々は、Qノード、Qbノード、プルアップ素子、プルダウン素子を含む。

FIG. 6 is a circuit diagram showing the connections between the stages included in the

第1シフトレジスタ221,222のプルアップ素子はトランジスタで構成されることができる。プルアップ素子のゲートはQノードと電気的に接続される。プルアップ素子のソースまたはドレインはクロック信号の入力端と電気的に接続される。プルアップ素子のドレインまたはソースはプルダウン素子のソースまたはドレインおよびクロック信号の出力端と電気的に接続される。プルアップ素子は、Qノードの電圧によりオン状態に遷移し、クロック信号を走査信号(ゲート信号)として出力する。

The pull-up elements of the

第1シフトレジスタ221,222のプルダウン素子はトランジスタで構成されることができる。プルアップ素子のゲートはQbノードと電気的に接続される。プルダウン素子のソースまたはドレインはプルアップ素子のドレインまたはソースおよびクロック信号の出力端と電気的に接続される。プルダウン素子のドレインまたはソースは低電位電源GVSSと電気的に接続される。プルダウン素子は、Qbノードの電圧によりオン状態に遷移し、基底電圧をローレベルの走査信号として出力する。

The pull-down elements of the

各ステージにおいて、プルアップ素子がオン状態のときにはプルダウン素子はオフ状態である。即ち、Qノードにプルアップ素子をオン状態にするオン電圧が印加されているとき、Qbノードにプルダウン素子をオフ状態にするオフ電圧が印加されている。この状態をステージのオン状態と呼ぶ。また、各ステージにおいて、プルダウン素子がオン状態のときにはプルアップ素子はオフ状態である。即ち、Qbノードにプルダウン素子をオン状態にするオン電圧が印加されているとき、Qノードにプルアップ素子をオフ状態にするオフ電圧が印加されている。この状態をステージのホールド状態と呼ぶ。 In each stage, when the pull-up element is in the on state, the pull-down element is in the off state. That is, when an on voltage that turns the pull-up element on is applied to the Q node, an off voltage that turns the pull-down element off is applied to the Qb node. This state is called the on state of the stage. Also, in each stage, when the pull-down element is in the on state, the pull-up element is in the off state. That is, when an on voltage that turns the pull-down element on is applied to the Qb node, an off voltage that turns the pull-up element off is applied to the Q node. This state is called the hold state of the stage.

以下に、図6に示されるQ(1)ノードおよびQb(1)ノードを含む第1ステージSTG1について説明する。第1シフトレジスタ221,222は、Q(1)ノードからゲート駆動部の動作の開始を指示するゲートスタート信号VST1の印加を受ける。第1ステージSTG1には3つのプルアップ素子が含まれている。3つのプルアップ素子の各ゲートノードはQ(1)ノードと共通に連結されており、3つのプルアップ素子は、Q(1)ノードの電圧によってオン状態に遷移する。1つめのプルアップ素子のソースまたはドレインはキャリーシフトクロック信号CRCLK1の入力端と連結されており、1つめのプルアップ素子のドレインまたはソースは走査信号の出力端C1と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、キャリーシフトクロック信号CRCLK1が走査信号の出力端から出力される。キャリーシフトクロックは、キャリー信号を生成するためのクロック信号である。2つめのプルアップ素子のソースまたはドレインはスキャンシフトクロック信号SCCLK1の入力端と連結されており、2つめのプルアップ素子のドレインまたはソースは走査信号の出力端S1と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、スキャンシフトクロック信号SCCLK1が走査信号の出力端から出力され得る。スキャンシフトクロック信号は、パルスを有する走査信号を生成するためのクロック信号である。例えばスキャンシフトクロック信号SCCLK1は、ゲート線GL1によって伝送されるゲート信号を生成するためのクロック信号である。3つめのプルアップ素子のソースまたはドレインはスキャンシフトクロック信号SCCLK3の入力端と連結されており、3つめのプルアップ素子のドレインまたはソースは走査信号の出力端S3と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、スキャンシフトクロック信号SCCLK3が走査信号の出力端から出力され得る。例えばスキャンシフトクロック信号SCCLK3は、ゲート線GL3によって伝送されるゲート信号を生成するためのクロック信号である。

The first stage STG1 including the Q(1) node and the Qb(1) node shown in FIG. 6 will be described below. The

また、第1ステージSTG1には3つのプルダウン素子が含まれている。3つのプルダウン素子の各ゲートノードはQb(1)ノードと共通に連結されており、3つのプルダウン素子は、Qb(1)ノードの電圧によってオン状態に遷移する。3つのプルダウン素子の各々はドレインまたはソースは低電位電源GVSSと連結されており、3つのプルダウン素子のソースまたはドレインは走査信号の出力端C1、S1、S3とそれぞれ連結されている。よって、プルダウン素子がQbノードの電圧によってオン状態に遷移されると、ローレベルの走査信号としての基底電圧が出力端C1、S1、S3にそれぞれ出力される。 The first stage STG1 also includes three pull-down elements. The gate nodes of the three pull-down elements are commonly connected to the Qb(1) node, and the three pull-down elements transition to an on state according to the voltage of the Qb(1) node. The drain or source of each of the three pull-down elements is connected to the low-potential power supply GVSS, and the source or drain of each of the three pull-down elements is connected to the output terminals C1, S1, and S3 of the scanning signal, respectively. Therefore, when the pull-down elements transition to an on state according to the voltage of the Qb node, a ground voltage as a low-level scanning signal is output to the output terminals C1, S1, and S3, respectively.

図6に示されるQ(3)ノードおよびQb(3)ノードを含む第3ステージSTG3からQ(11)ノードおよびQb(11)ノードを含む第11ステージSTG11までについても、上述の第1ステージSTG1と同様に構成され得る。なお、第11ステージSTG11に含まれるQ(11)ノードには、リセット信号RST1が印加されるように構成されることができる。また、第1シフトレジスタ221,222は、1つのQbノードが2つのステージによって共有されるように構成されることもできる。例えば、第1ステージSTG1のQb(1)ノードおよび第3ステージSTG3のQb(3)ノードは第1Qb共通ノード(不図示)で構成され、第1ステージSTG1および第3ステージSTG3は、第1Qb共通ノードを共有するように構成されることができる。同様に、第5ステージSTG5のQb(5)ノードおよび第7ステージSTG7のQb(7)ノードは第2Qb共通ノード(不図示)で構成され、第5ステージSTG5および第7ステージSTG7は、第2Qb共通ノードを共有するように構成されることができる。同様に、第9ステージSTG9のQb(9)ノードおよび第11ステージSTG11のQb(11)ノードは第3Qb共通ノード(不図示)で構成され、第9ステージSTG9および第11ステージSTG11は、第3Qb共通ノードを共有するように構成されることができる。上記構成によれば、Qbノードの配置によって占有される領域が減少される。結果として、第1シフトレジスタ221、222が非表示領域を占有する回路面積は減少される。したがって、表示装置10のベゼル幅をより小さくすることができる。なお、第1シフトレジスタ221,222は、第2シフトレジスタ231,232から独立したシフトレジスタであるため、第1シフトレジスタ221,222に含まれるステージは、第2シフトレジスタ231,232に含まれるステージとQbノードを共有しない。

The third stage STG3 including the Q(3) node and the Qb(3) node shown in FIG. 6 to the eleventh stage STG11 including the Q(11) node and the Qb(11) node can be configured in the same manner as the first stage STG1 described above. The Q(11) node included in the eleventh stage STG11 can be configured to receive a reset signal RST1. The

図7は本実施形態に係る第2シフトレジスタ231,232に含まれるステージとクロック配線との間の接続を示す回路図である。第2シフトレジスタ231,232は複数のステージを含む。複数のステージの各々は、Qノード、Qbノード、プルアップ素子、プルダウン素子を含む。

Figure 7 is a circuit diagram showing the connections between the stages included in the

第2シフトレジスタ231,232のプルアップ素子はトランジスタで構成されることができる。プルアップ素子のゲートはQノードと電気的に接続される。プルアップ素子のソースまたはドレインはクロック信号の入力端と電気的に接続される。プルアップ素子のドレインまたはソースはプルダウン素子のソースまたはドレインおよびクロック信号の出力端と電気的に接続される。プルアップ素子は、Qノードの電圧によりオン状態に遷移し、クロック信号を走査信号として出力する。

The pull-up elements of the

第2シフトレジスタ231,232のプルダウン素子はトランジスタで構成されることができる。プルアップ素子のゲートはQbノードと電気的に接続される。プルダウン素子のソースまたはドレインはプルアップ素子のドレインまたはソースおよびクロック信号の出力端と電気的に接続される。プルダウン素子のドレインまたはソースは低電位電源GVSSと電気的に接続される。プルダウン素子は、Qbノードの電圧によりオン状態に遷移し、基底電圧をローレベルの走査信号として出力する。

The pull-down elements of the

各ステージにおいて、プルアップ素子がオン状態のときにはプルダウン素子はオフ状態である。即ち、Qノードにプルアップ素子をオン状態にするオン電圧が印加されているとき、Qbノードにプルダウン素子をオフ状態にするオフ電圧が印加されている。また、各ステージにおいて、プルダウン素子がオン状態のときにはプルアップ素子はオフ状態である。即ち、Qbノードにプルダウン素子をオン状態にするオン電圧が印加されているとき、Qノードにプルアップ素子をオフ状態にするオフ電圧が印加されている。 In each stage, when the pull-up element is on, the pull-down element is off. That is, when an on voltage that turns the pull-up element on is applied to the Q node, an off voltage that turns the pull-down element off is applied to the Qb node. Also, in each stage, when the pull-down element is on, the pull-up element is off. That is, when an on voltage that turns the pull-down element on is applied to the Qb node, an off voltage that turns the pull-up element off is applied to the Q node.

以下に、図7に示されるQ(2)ノードおよびQb(2)ノードを含む第2ステージSTG2について説明する。第2シフトレジスタ231,232は、Q(2)ノードからゲート駆動部の動作の開始を指示するゲートスタート信号VST2の印加を受ける。ゲートスタート信号VST2は、第1シフトレジスタ221,222に印加されるゲートスタート信号VST1から独立した信号である。第2ステージSTG2には3つのプルアップ素子が含まれている。3つのプルアップ素子の各ゲートノードはQ(2)ノードと共通に連結されており、3つのプルアップ素子は、Q(2)ノードの電圧によってオン状態に遷移する。1つめのプルアップ素子のソースまたはドレインはキャリーシフトクロック信号CRCLK2の入力端と連結されており、1つめのプルアップ素子のドレインまたはソースは走査信号の出力端C2と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、キャリーシフトクロック信号CRCLK2が走査信号の出力端から出力される。2つめのプルアップ素子のソースまたはドレインはスキャンシフトクロック信号SCCLK2の入力端と連結されており、2つめのプルアップ素子のドレインまたはソースは走査信号の出力端S2と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、スキャンシフトクロック信号SCCLK2が走査信号の出力端から出力され得る。例えばスキャンシフトクロック信号SCCLK2は、ゲート線GL2によって伝送されるゲート信号を生成するためのクロック信号である。3つめのプルアップ素子のソースまたはドレインはスキャンシフトクロック信号SCCLK4の入力端と連結されており、3つめのプルアップ素子のドレインまたはソースは走査信号の出力端S4と連結されている。よって、プルアップ素子がQノードの電圧によってオン状態に遷移されると、スキャンシフトクロック信号SCCLK4が走査信号の出力端から出力され得る。例えばスキャンシフトクロック信号SCCLK4は、ゲート線GL4によって伝送されるゲート信号を生成するためのクロック信号である。

The second stage STG2 including the Q(2) node and the Qb(2) node shown in FIG. 7 will be described below. The

また、第2ステージSTG2には3つのプルダウン素子が含まれている。3つのプルダウン素子の各ゲートノードはQb(2)ノードと共通に連結されており、3つのプルダウン素子は、Qb(2)ノードの電圧によってオン状態に遷移する。3つのプルダウン素子の各々はドレインまたはソースは低電位電源GVSSと連結されており、3つのプルダウン素子のソースまたはドレインは走査信号の出力端C2、S2、S4とそれぞれ連結されている。よって、プルダウン素子がQbノードの電圧によってオン状態に遷移されると、ローレベルの走査信号としての基底電圧が出力端C2、S2、S4にそれぞれ出力される。 The second stage STG2 also includes three pull-down elements. The gate nodes of the three pull-down elements are commonly connected to the Qb(2) node, and the three pull-down elements transition to an on state according to the voltage of the Qb(2) node. The drain or source of each of the three pull-down elements is connected to the low-potential power supply GVSS, and the source or drain of each of the three pull-down elements is connected to the output terminals C2, S2, and S4 of the scanning signal, respectively. Therefore, when the pull-down elements transition to an on state according to the voltage of the Qb node, a ground voltage as a low-level scanning signal is output to the output terminals C2, S2, and S4, respectively.

図7に示されるQ(4)ノードおよびQb(4)ノードを含む第4ステージSTG4からQ(12)ノードおよびQb(12)ノードを含む第12ステージSTG12までについても、上述の第2ステージSTG2と同様に構成され得る。なお、第12ステージSTG12に含まれるQ(12)ノードには、リセット信号RST2が印加されるように構成されることができる。リセット信号RST2は、第1シフトレジスタ221,222に印加されるリセット信号RST1から独立した信号である。また、第2シフトレジスタ231,232は、1つのQbノードが2つのステージによって共有されるように構成されることもできる。例えば、第2ステージSTG2のQb(2)ノードおよび第4ステージSTG4のQb(4)ノードは第4Qb共通ノード(不図示)で構成され、第2ステージSTG2および第4ステージSTG4は、第4Qb共通ノードを共有するように構成されることができる。同様に、第6ステージSTG6のQb(6)ノードおよび第8ステージSTG8のQb(8)ノードは第5Qb共通ノード(不図示)で構成され、第6ステージSTG6および第8ステージSTG8は、第5Qb共通ノードを共有するように構成されることができる。同様に、第10ステージSTG10のQb(10)ノードおよび第12ステージSTG12のQb(12)ノードは第6Qb共通ノード(不図示)で構成され、第10ステージSTG10および第12ステージSTG12は、第6Qb共通ノードを共有するように構成されることができる。上記構成によれば、Qbノードの配置によって占有される領域が減少される。結果として、第2シフトレジスタ231、232が非表示領域を占有する回路面積は減少される。したがって、表示装置10のベゼル幅をより小さくすることができる。なお、第2シフトレジスタ231,232は、第1シフトレジスタ221,222から独立したシフトレジスタであるため、第2シフトレジスタ231,232に含まれるステージは、第1シフトレジスタ221,222に含まれるステージとQbノードを共有しない。

The fourth stage STG4 including the Q(4) node and the Qb(4) node shown in FIG. 7 to the twelfth stage STG12 including the Q(12) node and the Qb(12) node can be configured in the same manner as the second stage STG2 described above. The Q(12) node included in the twelfth stage STG12 can be configured to receive a reset signal RST2. The reset signal RST2 is a signal independent of the reset signal RST1 applied to the

図8は、本実施形態による第1シフトレジスタ221,222に含まれるステージおよび第2シフトレジスタ231,232に含まれるステージとクロック配線との間の接続の一例を示す回路図である

Figure 8 is a circuit diagram showing an example of the connection between the stages included in the

図5に示されるように、第2シフトレジスタ231,232は、平面視において表示パネル100の非表示領域の中に、の第1シフトレジスタ221,222と重畳するように配置されることができる。また、第1シフトレジスタ221,222および第2シフトレジスタ231,232は、GIP方式で実装されることができる。たとえば、第1シフトレジスタ221,222が第1GIPとして表示パネル100の中に実装され、第2シフトレジスタ231,232を第2GIPとして表示パネルの中に実装された場合を、図8を参照しながら説明する。本例において、第1GIPおよび第2GIPは、同一の低電位電源GVSSを共有する同一の回路領域に配される。具体的には、第1GIPの第3ステージSTG3の次段には第2GIPの第2ステージSTG2が配されている。また、第2GIPの第4ステージSTG4の次段には第1GIPの第5ステージSTG5および第2GIPの第4ステージSTG4が配されている。また、第1GIPの第7ステージSTG7の次段には第2GIPの第6ステージSTG6が配されている。ただし、上述の通り、第1GIPおよび第2GIPは、互いに独立したシフトレジスタである。具体的には、第1GIPおよび第2GIPは、入力クロック信号CRCLK,SCCLKを共有しない。また、第1GIPはゲートスタート信号VST1およびリセット信号RST1を受信し、第2GIPは、ゲートスタート信号VST1およびリセット信号RST1からそれぞれ独立した別個のゲートスタート信号VST2およびリセット信号RST2を受信する。第1GIPのステージに入出力されるキャリー信号は第1GIPの他のステージに伝送される一方で、第1GIPのステージに入出力されるキャリー信号は第2GIPのステージには伝送されない。同様に、第2GIPのステージに入出力されるキャリー信号は第2GIPの他のステージに伝送される一方で、第2GIPのステージに入出力されるキャリー信号は第1GIPのステージには伝送されない。即ち、第1GIPは、第2GIPの動作から独立して駆動される。同様に、第2GIPは、第1GIPの動作から独立して駆動される。

As shown in FIG. 5, the

図9は、本実施形態に係る第1GIPの信号出力端および第2GIPの信号出力端とゲート線との間の対応関係を示す図である。本実施形態によれば、第1GIPおよび第2GIPに含まれる走査信号の出力端S1~S16の配置は、ゲート線GL1~GL16の配置と対応していない。即ち、図9に示されるように、第1GIPの第1ステージSTG1の出力端S3のゲート線GL3への出力線は、第2GIPの第2ステージSTG2の出力端S2のゲート線GL2への出力線と交差する。また、第1GIPの第3ステージSTG3の出力端S5のゲート線GL5への出力線は、第2GIPの第2ステージSTG2の出力端S2のゲート線GL2への出力線および第2GIPの第2ステージSTG2の出力端S4のゲート線GL4への出力線と交差する。また、第1GIPの第3ステージSTG3の出力端S7のゲート線GL7への出力線は、第2GIPの第2ステージSTG2の出力端S2のゲート線GL2への出力線、第2GIPの第2ステージSTG2の出力端S4のゲート線GL4への出力線および第2GIPの第4ステージSTG4の出力端S6のゲート線GL6への出力線と交差する。また、第1GIPの第5ステージSTG5の出力端S11のゲート線GL11への出力線は、第2GIPの第6ステージSTG6の出力端S10のゲート線GL10への出力線と交差する。また、第1GIPの第7ステージSTG7の出力端S13のゲート線GL13への出力線は、第2GIPの第6ステージSTG6の出力端S10のゲート線GL10への出力線および第2GIPの第6ステージSTG6の出力端S12のゲート線GL12への出力線と交差する。また、第1GIPの第7ステージSTG7の出力端S15のゲート線GL15への出力線は、第2GIPの第6ステージSTG6の出力端S10のゲート線GL10への出力線、第2GIPの第6ステージSTG6の出力端S12のゲート線GL12への出力線および第2GIPの第8ステージSTG8の出力端S14のゲート線GL14への出力線と交差する。即ち、第1GIPから供給されるゲート信号の出力端から当該出力端に対応するゲート線までを直線で結ぶ経路は、第2GIPから供給されるゲート信号の出力端から当該出力端に対応するゲート線までを直線で結ぶ経路と交差するように構成され得る。なお、第1GIPの第1ステージSTG1の出力端S1のゲート線GL1への出力線および第1GIPの第5ステージSTG5の出力端S9のゲート線GL9への出力線は、第2GIPの信号出力端からの出力線と交差しない。また、第2GIPの第4ステージSTG4の出力端S8のゲート線GL8への出力線および第2GIPの第8ステージSTG8の出力端S16のゲート線GL16への出力線は、第1GIPの信号出力端からの出力線と交差しない。 Figure 9 is a diagram showing the correspondence between the signal output terminals of the first GIP and the second GIP and the gate lines according to this embodiment. According to this embodiment, the arrangement of the output terminals S1 to S16 of the scanning signals included in the first GIP and the second GIP does not correspond to the arrangement of the gate lines GL1 to GL16. That is, as shown in Figure 9, the output line of the output terminal S3 of the first stage STG1 of the first GIP to the gate line GL3 intersects with the output line of the output terminal S2 of the second stage STG2 of the second GIP to the gate line GL2. In addition, the output line of the output terminal S5 of the third stage STG3 of the first GIP to the gate line GL5 intersects with the output line of the output terminal S2 of the second stage STG2 of the second GIP to the gate line GL2 and the output line of the output terminal S4 of the second stage STG2 of the second GIP to the gate line GL4. The output line of the output terminal S7 of the third stage STG3 of the first GIP to the gate line GL7 crosses the output line of the output terminal S2 of the second stage STG2 of the second GIP to the gate line GL2, the output line of the output terminal S4 of the second stage STG2 of the second GIP to the gate line GL4, and the output line of the output terminal S6 of the fourth stage STG4 of the second GIP to the gate line GL6. The output line of the output terminal S11 of the fifth stage STG5 of the first GIP to the gate line GL11 crosses the output line of the output terminal S10 of the sixth stage STG6 of the second GIP to the gate line GL10. The output line of the output terminal S13 of the seventh stage STG7 of the first GIP to the gate line GL13 crosses the output line of the output terminal S10 of the sixth stage STG6 of the second GIP to the gate line GL10 and the output line of the output terminal S12 of the sixth stage STG6 of the second GIP to the gate line GL12. Also, the output line of the output terminal S15 of the seventh stage STG7 of the first GIP to the gate line GL15 crosses the output line of the output terminal S10 of the sixth stage STG6 of the second GIP to the gate line GL10, the output line of the output terminal S12 of the sixth stage STG6 of the second GIP to the gate line GL12, and the output line of the output terminal S14 of the eighth stage STG8 of the second GIP to the gate line GL14. That is, a straight line path from the output terminal of the gate signal supplied from the first GIP to the gate line corresponding to the output terminal can be configured to cross a straight line path from the output terminal of the gate signal supplied from the second GIP to the gate line corresponding to the output terminal. Note that the output line of the output terminal S1 of the first stage STG1 of the first GIP to the gate line GL1 and the output line of the output terminal S9 of the fifth stage STG5 of the first GIP to the gate line GL9 do not cross the output line from the signal output terminal of the second GIP. In addition, the output line from the output end S8 of the fourth stage STG4 of the second GIP to the gate line GL8 and the output line from the output end S16 of the eighth stage STG8 of the second GIP to the gate line GL16 do not intersect with the output line from the signal output end of the first GIP.

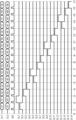

図10は、本実施形態に係る第1GIPおよび第2GIPのオン状態とホールド状態の遷移の一例を示す図である。上述の通り、本実施形態に係る第1GIPおよび第2GIPに含まれる各ステージは、プルアップ素子およびプルダウン素子に印加される電圧にしたがってオン状態またはホールド状態となる。ホールド状態にあるステージからは、走査信号は出力されない。一方、オン状態にあるステージからは、走査信号が出力されることができる。しかしながら、同クロックにおいて2以上の走査信号またはキャリー信号が出力端から伝送されないようにするために、オン状態のステージの数を制限する必要がある。具体的には、例えばGIPに入力されるクロック数をxとした場合、オン状態のステージの数は2x未満としなければならない(xは正の整数)。本実施形態の第1GIPは、キャリー信号を介して、順次ホールド状態のステージをオン状態へ遷移させる。また、本実施形態の第1GIPは、キャリー信号を介して、順次オン状態のステージをホールド状態へ遷移させる。同様に、本実施形態の第2GIPは、キャリー信号を介して、順次ホールド状態のステージをオン状態へ遷移させる。また、本実施形態の第2GIPは、キャリー信号を介して、順次オン状態のステージをホールド状態へ遷移させる。第1GIPで用いられるキャリー信号は、第2GIPに伝送されない。よって、第1GIPのステージのオン状態とホールド状態との間の遷移は、第2GIPの動作から独立している。同様に、第1GIPで用いられるキャリー信号は、第2GIPに伝送されない。よって、第2GIPのステージのオン状態とホールド状態との間の遷移は、第1GIPの動作から独立している。 FIG. 10 is a diagram showing an example of the transition between the on state and the hold state of the first GIP and the second GIP according to this embodiment. As described above, each stage included in the first GIP and the second GIP according to this embodiment is in the on state or the hold state according to the voltage applied to the pull-up element and the pull-down element. A stage in the hold state does not output a scan signal. On the other hand, a stage in the on state can output a scan signal. However, in order to prevent two or more scan signals or carry signals from being transmitted from the output terminal in the same clock, it is necessary to limit the number of stages in the on state. Specifically, for example, if the number of clocks input to the GIP is x, the number of stages in the on state must be less than 2x (x is a positive integer). The first GIP of this embodiment sequentially transitions the stages in the hold state to the on state via the carry signal. Also, the first GIP of this embodiment sequentially transitions the stages in the on state to the hold state via the carry signal. Similarly, the second GIP of this embodiment sequentially transitions the stages in the hold state to the on state via the carry signal. In addition, the second GIP of this embodiment transitions the stages in the on state to the hold state sequentially via the carry signal. The carry signal used in the first GIP is not transmitted to the second GIP. Thus, the transition between the on state and the hold state of the stage in the first GIP is independent of the operation of the second GIP. Similarly, the carry signal used in the first GIP is not transmitted to the second GIP. Thus, the transition between the on state and the hold state of the stage in the second GIP is independent of the operation of the first GIP.

図10には、第1GIPおよび第2GIPに含まれる各ステージのオン状態とホールド状態との間の遷移の一例が示されている。本例では、奇数番目のゲート線GL1、GL3、...、GL31には、第1GIPから走査信号(ゲート信号)が伝送される。例えば、図3に示される副画素の配列によれば、第1GIPは、奇数番目のゲート線を介して赤色副画素Rの第1スイッチ素子T1および白色副画素Wの第1スイッチ素子T1にゲート電圧を供給する。一方、偶数番目のゲート線GL2、GL4、...、GL32には、第2GIPから走査信号(ゲート信号)が伝送される。例えば、図3に示される副画素の配列によれば、第2GIPは、偶数番目のゲート線を介して緑色副画素Gの第1スイッチ素子T1および青色副画素Bの第1スイッチ素子T1にゲート電圧を供給する。なお、第1GIPに接続されるゲート線は奇数番目のゲート線に限定されず、第2GIPに接続されるゲート線は偶数番目のゲート線に限定されない。ゲート駆動部の回路設計等に従い、第1GIPおよび第2GIPは、任意の場所に配置されたゲート線と接続され得る。 10 shows an example of the transition between the on state and the hold state of each stage included in the first GIP and the second GIP. In this example, the first GIP transmits a scanning signal (gate signal) to the odd-numbered gate lines GL1, GL3, ..., GL31. For example, according to the arrangement of the subpixels shown in FIG. 3, the first GIP supplies a gate voltage to the first switch element T1 of the red subpixel R and the first switch element T1 of the white subpixel W via the odd-numbered gate lines. On the other hand, the second GIP transmits a scanning signal (gate signal) to the even-numbered gate lines GL2, GL4, ..., GL32. For example, according to the arrangement of the subpixels shown in FIG. 3, the second GIP supplies a gate voltage to the first switch element T1 of the green subpixel G and the first switch element T1 of the blue subpixel B via the even-numbered gate lines. In addition, the gate lines connected to the first GIP are not limited to odd-numbered gate lines, and the gate lines connected to the second GIP are not limited to even-numbered gate lines. Depending on the circuit design of the gate driver, the first GIP and the second GIP can be connected to gate lines located in any position.

図10に示される例では、奇数番目のゲート線を介して所定の数の走査信号が連続して伝送された後に、偶数番目のゲート線を介して所定の数の走査信号が連続して伝送される。例えば、図3に示される副画素の配列によれば、最初に、第1GIPが、奇数番目のゲート線を介して表示パネル100の各行に配された赤色副画素Rおよび白色副画素Wに、走査信号を所定の行数にわたり連続して供給する。次いで、第2GIPが、偶数番目のゲート線を介して表示パネル100の各行に配された緑色副画素Gおよび青色副画素Bに、走査信号を所定の行数に渡り連続して供給する。

In the example shown in FIG. 10, a predetermined number of scanning signals are transmitted continuously through odd-numbered gate lines, and then a predetermined number of scanning signals are transmitted continuously through even-numbered gate lines. For example, according to the arrangement of subpixels shown in FIG. 3, the first GIP first supplies scanning signals continuously through a predetermined number of rows to the red subpixels R and white subpixels W arranged in each row of the

具体的には、クロック(1)において、第1GIPに含まれる第1ステージ、第3ステージ、第5ステージ、第7ステージおよび第2GIPに含まれる第2ステージ、第4ステージ、第6ステージ、第8ステージがオン状態である。このとき、第1GIPは、オン状態のステージに対応するゲート線のグループ(GL1、GL3、GL5、GL7、GL9、GL11、GL13、GL15)を介してゲート信号の供給が可能な状態にある。また、第2GIPは、オン状態のステージに対応するゲート線のグループ(GL2、GL4、GL6、GL8、GL10、GL12、GL14、GL16)を介してゲート信号の供給が可能な状態にある。一方、第1GIPに含まれる第9ステージ、第11ステージ、第13ステージ、第15ステージおよび第2GIPに含まれる第10ステージ、第12ステージ、第14ステージ、第16ステージがホールド状態である。クロック(1)において、例えば、第1GIPは、第3ステージからゲート線GL5に走査信号を伝送する。結果として、ゲート線GL5と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第3ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(1)とクロック(2)との間の時刻に、第3ステージからゲート線GL7に走査信号を伝送し得る。 Specifically, in clock (1), the first, third, fifth, and seventh stages included in the first GIP and the second, fourth, sixth, and eighth stages included in the second GIP are in the on state. At this time, the first GIP is in a state in which a gate signal can be supplied via the group of gate lines (GL1, GL3, GL5, GL7, GL9, GL11, GL13, and GL15) corresponding to the on-state stages. Also, the second GIP is in a state in which a gate signal can be supplied via the group of gate lines (GL2, GL4, GL6, GL8, GL10, GL12, GL14, and GL16) corresponding to the on-state stages. Meanwhile, the ninth, eleventh, thirteenth, and fifteenth stages included in the first GIP and the tenth, twelfth, fourteenth, and sixteenth stages included in the second GIP are in the hold state. In clock (1), for example, the first GIP transmits a scanning signal from the third stage to gate line GL5. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W that are electrically connected to gate line GL5. No scanning signal is transmitted to the gate line GL from stages other than the third stage. Note that the first GIP may transmit a scanning signal from the third stage to gate line GL7 at a time between clock (1) and clock (2).

クロック(2)において、第1GIPに含まれる第1ステージがオン状態からホールド状態に遷移される。一方、クロック(2)において、第1GIPに含まれる第9ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第1ステージおよび第9ステージ以外のステージは、クロック(1)における状態と同じ状態に維持される。このとき、第1GIPは、オン状態のステージに対応するゲート線のグループ(GL5、GL7、GL9、GL11、GL13、GL15、GL17、GL19)を介してゲート信号の供給が可能な状態にある。また、第2GIPに含まれるすべてのステージは、クロック(1)における状態と同じ状態に維持される。即ち、第2GIPは、オン状態のステージに対応するゲート線のグループ(GL2、GL4、GL6、GL8、GL10、GL12、GL14、GL16)を介してゲート信号の供給が可能な状態にある。クロック(2)において、第1GIPは、第5ステージからゲート線GL9に走査信号を伝送する。結果として、ゲート線GL9と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第5ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(2)とクロック(3)との間の時刻に、第5ステージからゲート線GL11に走査信号を伝送し得る。 In clock (2), the first stage included in the first GIP transitions from an on state to a hold state. Meanwhile, in clock (2), the ninth stage included in the first GIP transitions from a hold state to an on state. Stages other than the first stage and the ninth stage included in the first GIP are maintained in the same state as in clock (1). At this time, the first GIP is in a state in which a gate signal can be supplied via the group of gate lines (GL5, GL7, GL9, GL11, GL13, GL15, GL17, GL19) corresponding to the on-state stage. In addition, all stages included in the second GIP are maintained in the same state as in clock (1). That is, the second GIP is in a state in which a gate signal can be supplied via the group of gate lines (GL2, GL4, GL6, GL8, GL10, GL12, GL14, GL16) corresponding to the on-state stage. In clock (2), the first GIP transmits a scanning signal from the fifth stage to the gate line GL9. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W that are electrically connected to the gate line GL9. No scanning signal is transmitted to the gate line GL from stages other than the fifth stage. Note that the first GIP may transmit a scanning signal from the fifth stage to the gate line GL11 at a time between clock (2) and clock (3).

クロック(3)において、第1GIPに含まれる第3ステージがオン状態からホールド状態に遷移される。一方、クロック(3)において、第1GIPに含まれる第11ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第3ステージおよび第11ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(2)における状態と同じ状態に維持される。クロック(3)において、第1GIPは、第7ステージからゲート線GL13に走査信号を伝送する。結果として、ゲート線GL13と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第7ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(3)とクロック(4)との間の時刻に、第7ステージからゲート線GL15に走査信号を伝送し得る。 At clock (3), the third stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (3), the eleventh stage included in the first GIP transitions from a hold state to an on state. Stages other than the third stage and the eleventh stage included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (2). At clock (3), the first GIP transmits a scanning signal from the seventh stage to the gate line GL13. As a result, a scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL13. No scanning signal is transmitted from stages other than the seventh stage to the gate line GL. Note that the first GIP may transmit a scanning signal from the seventh stage to the gate line GL15 at a time between clock (3) and clock (4).

クロック(4)において、第1GIPに含まれる第5ステージがオン状態からホールド状態に遷移される。一方、クロック(4)において、第1GIPに含まれる第13ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第5ステージおよび第13ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(3)における状態と同じ状態に維持される。クロック(4)において、第1GIPは、第9ステージからゲート線GL17に走査信号を伝送する。結果として、ゲート線GL17と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第9ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(4)とクロック(5)との間の時刻に、第9ステージからゲート線GL19に走査信号を伝送し得る。 At clock (4), the fifth stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (4), the thirteenth stage included in the first GIP transitions from a hold state to an on state. Stages other than the fifth and thirteenth stages included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (3). At clock (4), the first GIP transmits a scanning signal from the ninth stage to the gate line GL17. As a result, a scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL17. No scanning signal is transmitted from stages other than the ninth stage to the gate line GL. Note that the first GIP may transmit a scanning signal from the ninth stage to the gate line GL19 at a time between clock (4) and clock (5).

クロック(5)において、第1GIPに含まれる第7ステージがオン状態からホールド状態に遷移される。一方、クロック(5)において、第1GIPに含まれる第15ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第7ステージおよび第15ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(4)における状態と同じ状態に維持される。クロック(5)において、第1GIPは、第11ステージからゲート線GL21に走査信号を伝送する。結果として、ゲート線GL21と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第11ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(5)とクロック(6)との間の時刻に、第11ステージからゲート線GL23に走査信号を伝送し得る。 At clock (5), the seventh stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (5), the fifteenth stage included in the first GIP transitions from a hold state to an on state. Stages other than the seventh stage and the fifteenth stage included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (4). At clock (5), the first GIP transmits a scanning signal from the eleventh stage to the gate line GL21. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL21. No scanning signal is transmitted from stages other than the eleventh stage to the gate line GL. Note that the first GIP may transmit a scanning signal from the eleventh stage to the gate line GL23 at a time between clock (5) and clock (6).

クロック(6)において、第2GIPに含まれる第2ステージがオン状態からホールド状態に遷移される。一方、クロック(6)において、第2GIPに含まれる第10ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第2ステージおよび第10ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(5)における状態と同じ状態に維持される。クロック(6)において、第2GIPは、第4ステージからゲート線GL6に走査信号を伝送する。結果として、ゲート線GL6と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第4ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(6)とクロック(7)との間の時刻に、第4ステージからゲート線GL8に走査信号を伝送し得る。 At clock (6), the second stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (6), the tenth stage included in the second GIP transitions from a hold state to an on state. Stages other than the second stage and the tenth stage included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (5). At clock (6), the second GIP transmits a scanning signal from the fourth stage to the gate line GL6. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL6. No scanning signal is transmitted to the gate line GL from stages other than the fourth stage. Note that the second GIP may transmit a scanning signal from the fourth stage to the gate line GL8 at a time between clock (6) and clock (7).

クロック(7)において、第2GIPに含まれる第4ステージがオン状態からホールド状態に遷移される。一方、クロック(7)において、第2GIPに含まれる第12ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第4ステージおよび第12ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(6)における状態と同じ状態に維持される。クロック(7)において、第2GIPは、第6ステージからゲート線GL10に走査信号を伝送する。結果として、ゲート線GL10と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第6ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(7)とクロック(8)との間の時刻に、第6ステージからゲート線GL12に走査信号を伝送し得る。 At clock (7), the fourth stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (7), the twelfth stage included in the second GIP transitions from a hold state to an on state. Stages other than the fourth stage and the twelfth stage included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (6). At clock (7), the second GIP transmits a scanning signal from the sixth stage to the gate line GL10. As a result, a scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL10. No scanning signal is transmitted from stages other than the sixth stage to the gate line GL. Note that the second GIP may transmit a scanning signal from the sixth stage to the gate line GL12 at a time between clocks (7) and (8).

クロック(8)において、第2GIPに含まれる第6ステージがオン状態からホールド状態に遷移される。一方、クロック(8)において、第2GIPに含まれる第14ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第6ステージおよび第14ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(7)における状態と同じ状態に維持される。クロック(8)において、第2GIPは、第8ステージからゲート線GL14に走査信号を伝送する。結果として、ゲート線GL14と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第8ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(8)とクロック(9)との間の時刻に、第8ステージからゲート線GL16に走査信号を伝送し得る。 At clock (8), the sixth stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (8), the fourteenth stage included in the second GIP transitions from a hold state to an on state. Stages other than the sixth and fourteenth stages included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (7). At clock (8), the second GIP transmits a scanning signal from the eighth stage to the gate line GL14. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL14. No scanning signal is transmitted from stages other than the eighth stage to the gate line GL. Note that the second GIP may transmit a scanning signal from the eighth stage to the gate line GL16 at a time between clock (8) and clock (9).

クロック(9)において、第2GIPに含まれる第8ステージがオン状態からホールド状態に遷移される。一方、クロック(9)において、第2GIPに含まれる第16ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第8ステージおよび第16ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(8)における状態と同じ状態に維持される。クロック(9)において、第2GIPは、第10ステージからゲート線GL18に走査信号を伝送する。結果として、ゲート線GL18と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第10ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(9)の後の時刻に、第10ステージからゲート線GL20に走査信号を伝送し得る。 At clock (9), the 8th stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (9), the 16th stage included in the second GIP transitions from a hold state to an on state. Stages other than the 8th stage and the 16th stage included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (8). At clock (9), the second GIP transmits a scanning signal from the 10th stage to the gate line GL18. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL18. The scanning signal is not transmitted to the gate line GL from stages other than the 10th stage. Note that the second GIP may transmit a scanning signal from the 10th stage to the gate line GL20 at a time after clock (9).

図11は、第1GIPおよび第2GIPに含まれる各ステージのオン状態とホールド状態との間の遷移に関して、図10に示された例とは別の一例を示す表である。図10と同一の構成についてはその記載は省略されることがある。 Figure 11 is a table showing another example, different from the example shown in Figure 10, regarding the transition between the on state and the hold state of each stage included in the first GIP and the second GIP. Descriptions of the same configuration as in Figure 10 may be omitted.

図11に示される例では、偶数番目のゲート線を介して所定の数の走査信号が連続して伝送された後に、奇数番目のゲート線を介して所定の数の走査信号が連続して伝送される。例えば、図3に示される副画素の配列によれば、最初に、第2GIPが、偶数番目のゲート線を介して表示パネル100の各行に配された緑色副画素Gおよび青色副画素Bに、走査信号を所定の行数にわたり連続して供給する。次いで、第1GIPが、奇数番目のゲート線を介して表示パネル100の各行に配された赤色副画素Rおよび白色副画素Wに、走査信号を所定の行数に渡り連続して供給する。

In the example shown in FIG. 11, a predetermined number of scanning signals are transmitted continuously through the even-numbered gate lines, and then a predetermined number of scanning signals are transmitted continuously through the odd-numbered gate lines. For example, according to the arrangement of subpixels shown in FIG. 3, the second GIP first supplies scanning signals continuously through a predetermined number of rows to the green subpixels G and blue subpixels B arranged in each row of the

具体的には、クロック(1)において、第1GIPに含まれる第1ステージ、第3ステージ、第5ステージ、第7ステージおよび第2GIPに含まれる第2ステージ、第4ステージ、第6ステージ、第8ステージがオン状態である。一方、第1GIPに含まれる第9ステージ、第11ステージ、第13ステージ、第15ステージおよび第2GIPに含まれる第10ステージ、第12ステージ、第14ステージ、第16ステージがホールド状態である。クロック(1)において、例えば、第2GIPは、第4ステージからゲート線GL6に走査信号を伝送する。結果として、ゲート線GL6と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第4ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(1)とクロック(2)との間の時刻に、第4ステージからゲート線GL8に走査信号を伝送し得る。 Specifically, in clock (1), the first, third, fifth, and seventh stages included in the first GIP and the second, fourth, sixth, and eighth stages included in the second GIP are in the on state. On the other hand, the ninth, eleventh, thirteenth, and fifteenth stages included in the first GIP and the tenth, twelfth, fourteenth, and sixteenth stages included in the second GIP are in the hold state. In clock (1), for example, the second GIP transmits a scanning signal from the fourth stage to the gate line GL6. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL6. The scanning signal is not transmitted to the gate line GL from stages other than the fourth stage. Note that the second GIP may transmit a scanning signal from the fourth stage to the gate line GL8 at a time between clock (1) and clock (2).

クロック(2)において、第2GIPに含まれる第2ステージがオン状態からホールド状態に遷移される。一方、クロック(2)において、第2GIPに含まれる第10ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第2ステージおよび第10ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(1)における状態と同じ状態に維持される。クロック(2)において、第2GIPは、第6ステージからゲート線GL10に走査信号を伝送する。結果として、ゲート線GL10と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第6ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(2)とクロック(3)との間の時刻に、第6ステージからゲート線GL12に走査信号を伝送し得る。 At clock (2), the second stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (2), the tenth stage included in the second GIP transitions from a hold state to an on state. Stages other than the second stage and the tenth stage included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (1). At clock (2), the second GIP transmits a scanning signal from the sixth stage to the gate line GL10. As a result, a scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL10. No scanning signal is transmitted to the gate line GL from stages other than the sixth stage. Note that the second GIP may transmit a scanning signal from the sixth stage to the gate line GL12 at a time between clock (2) and clock (3).

クロック(3)において、第2GIPに含まれる第4ステージがオン状態からホールド状態に遷移される。一方、クロック(3)において、第2GIPに含まれる第12ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第4ステージおよび第12ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(2)における状態と同じ状態に維持される。クロック(3)において、第2GIPは、第8ステージからゲート線GL14に走査信号を伝送する。結果として、ゲート線GL14と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第8ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(3)とクロック(4)との間の時刻に、第8ステージからゲート線GL16に走査信号を伝送し得る。 At clock (3), the fourth stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (3), the twelfth stage included in the second GIP transitions from a hold state to an on state. Stages other than the fourth stage and the twelfth stage included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (2). At clock (3), the second GIP transmits a scanning signal from the eighth stage to the gate line GL14. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL14. The scanning signal is not transmitted to the gate line GL from stages other than the eighth stage. Note that the second GIP may transmit a scanning signal from the eighth stage to the gate line GL16 at a time between clock (3) and clock (4).

クロック(4)において、第2GIPに含まれる第6ステージがオン状態からホールド状態に遷移される。一方、クロック(4)において、第2GIPに含まれる第14ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第6ステージおよび第14ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(3)における状態と同じ状態に維持される。クロック(4)において、第2GIPは、第10ステージからゲート線GL18に走査信号を伝送する。結果として、ゲート線GL18と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第10ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(4)とクロック(5)との間の時刻に、第10ステージからゲート線GL20に走査信号を伝送し得る。 At clock (4), the sixth stage included in the second GIP transitions from an on state to a hold state. Meanwhile, at clock (4), the fourteenth stage included in the second GIP transitions from a hold state to an on state. Stages other than the sixth and fourteenth stages included in the second GIP and all stages included in the first GIP are maintained in the same state as in clock (3). At clock (4), the second GIP transmits a scanning signal from the tenth stage to the gate line GL18. As a result, a scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL18. No scanning signal is transmitted from stages other than the tenth stage to the gate line GL. Note that the second GIP may transmit a scanning signal from the tenth stage to the gate line GL20 at a time between clock (4) and clock (5).

クロック(5)において、第2GIPに含まれる第8ステージがオン状態からホールド状態に遷移される。一方、クロック(5)において、第2GIPに含まれる第16ステージがホールド状態からオン状態に遷移される。第2GIPに含まれる第8ステージおよび第16ステージ以外のステージならびに第1GIPに含まれるすべてのステージは、クロック(4)における状態と同じ状態に維持される。クロック(5)において、第2GIPは、第12ステージからゲート線GL22に走査信号を伝送する。結果として、ゲート線GL22と電気的に接続されている緑色副画素Gおよび青色副画素Bに走査信号が供給される。第12ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第2GIPは、クロック(5)とクロック(6)との間の時刻に、第12ステージからゲート線GL24に走査信号を伝送し得る。 At clock (5), the 8th stage included in the second GIP is transitioned from an on state to a hold state. At clock (5), the 16th stage included in the second GIP is transitioned from a hold state to an on state. The stages other than the 8th stage and the 16th stage included in the second GIP and all the stages included in the first GIP are maintained in the same state as in clock (4). At clock (5), the second GIP transmits a scanning signal from the 12th stage to the gate line GL22. As a result, the scanning signal is supplied to the green subpixel G and the blue subpixel B electrically connected to the gate line GL22. The scanning signal is not transmitted to the gate line GL from the stages other than the 12th stage. Note that the second GIP may transmit a scanning signal from the 12th stage to the gate line GL24 at a time between clock (5) and clock (6).

クロック(6)において、第1GIPに含まれる第1ステージがオン状態からホールド状態に遷移される。一方、クロック(6)において、第1GIPに含まれる第9ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第1ステージおよび第9ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(5)における状態と同じ状態に維持される。クロック(6)において、第1GIPは、第3ステージからゲート線GL5に走査信号を伝送する。結果として、ゲート線GL5と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第3ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(6)とクロック(7)との間の時刻に、第3ステージからゲート線GL7に走査信号を伝送し得る。 At clock (6), the first stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (6), the ninth stage included in the first GIP transitions from a hold state to an on state. Stages other than the first stage and the ninth stage included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (5). At clock (6), the first GIP transmits a scanning signal from the third stage to the gate line GL5. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL5. No scanning signal is transmitted from stages other than the third stage to the gate line GL. Note that the first GIP may transmit a scanning signal from the third stage to the gate line GL7 at a time between clock (6) and clock (7).

クロック(7)において、第1GIPに含まれる第3ステージがオン状態からホールド状態に遷移される。一方、クロック(7)において、第1GIPに含まれる第11ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第3ステージおよび第11ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(6)における状態と同じ状態に維持される。クロック(7)において、第1GIPは、第5ステージからゲート線GL9に走査信号を伝送する。結果として、ゲート線GL9と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第5ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(7)とクロック(8)との間の時刻に、第5ステージからゲート線GL11に走査信号を伝送し得る。 At clock (7), the third stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (7), the eleventh stage included in the first GIP transitions from a hold state to an on state. Stages other than the third stage and the eleventh stage included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (6). At clock (7), the first GIP transmits a scanning signal from the fifth stage to the gate line GL9. As a result, a scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL9. No scanning signal is transmitted from stages other than the fifth stage to the gate line GL. Note that the first GIP may transmit a scanning signal from the fifth stage to the gate line GL11 at a time between clocks (7) and (8).

クロック(8)において、第1GIPに含まれる第5ステージがオン状態からホールド状態に遷移される。一方、クロック(8)において、第1GIPに含まれる第13ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第5ステージおよび第13ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(7)における状態と同じ状態に維持される。クロック(8)において、第1GIPは、第7ステージからゲート線GL13に走査信号を伝送する。結果として、ゲート線GL13と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第7ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(8)とクロック(9)との間の時刻に、第7ステージからゲート線GL15に走査信号を伝送し得る。 At clock (8), the fifth stage included in the first GIP transitions from an on state to a hold state. At clock (8), the thirteenth stage included in the first GIP transitions from a hold state to an on state. The stages other than the fifth and thirteenth stages included in the first GIP and all the stages included in the second GIP are maintained in the same state as in clock (7). At clock (8), the first GIP transmits a scanning signal from the seventh stage to the gate line GL13. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL13. The scanning signal is not transmitted to the gate line GL from the stages other than the seventh stage. Note that the first GIP may transmit a scanning signal from the seventh stage to the gate line GL15 at a time between clock (8) and clock (9).

クロック(9)において、第1GIPに含まれる第7ステージがオン状態からホールド状態に遷移される。一方、クロック(9)において、第2GIPに含まれる第15ステージがホールド状態からオン状態に遷移される。第1GIPに含まれる第7ステージおよび第15ステージ以外のステージならびに第2GIPに含まれるすべてのステージは、クロック(8)における状態と同じ状態に維持される。クロック(9)において、第1GIPは、第9ステージからゲート線GL17に走査信号を伝送する。結果として、ゲート線GL17と電気的に接続されている赤色副画素Rおよび白色副画素Wに走査信号が供給される。第9ステージ以外のステージからゲート線GLに走査信号は伝送されない。なお、第1GIPは、クロック(9)の後の時刻に、第9ステージからゲート線GL19に走査信号を伝送し得る。 At clock (9), the seventh stage included in the first GIP transitions from an on state to a hold state. Meanwhile, at clock (9), the fifteenth stage included in the second GIP transitions from a hold state to an on state. Stages other than the seventh stage and the fifteenth stage included in the first GIP and all stages included in the second GIP are maintained in the same state as in clock (8). At clock (9), the first GIP transmits a scanning signal from the ninth stage to the gate line GL17. As a result, the scanning signal is supplied to the red subpixel R and the white subpixel W electrically connected to the gate line GL17. The scanning signal is not transmitted to the gate line GL from stages other than the ninth stage. Note that the first GIP may transmit a scanning signal from the ninth stage to the gate line GL19 at a time after clock (9).

本実施形態によるゲート駆動部は第1GIPとして動作する第1シフトレジスタ221,222および第2GIPとして動作する第2シフトレジスタ231,232を含む。第1GIPは、奇数番目のゲート線と接続される。一方、第2GIPは、偶数番目のゲート線と接続される。第1GIPが走査信号を奇数番目のゲート信号に伝送する期間において、第1GIPに含まれる複数のステージはオン状態とホールド状態との間で遷移され得る。具体的には、第1GIPが走査信号を奇数番目のゲート信号に伝送する期間において、あるステージをオン状態からホールド状態に遷移させるとともに別のステージをホールド状態からオン状態に遷移させる。一方、第1GIPが走査信号を奇数番目のゲート信号に伝送する期間において、第2GIPに含まれるすべてのステージの状態は変更されない。同様に、第2GIPが走査信号を偶数番目のゲート信号に伝送する期間において、第2GIPに含まれる複数のステージはオン状態とホールド状態との間で遷移され得る。具体的には、第2GIPが走査信号を偶数番目のゲート信号に伝送する期間において、あるステージをオン状態からホールド状態に遷移させるとともに別のステージをホールド状態からオン状態に遷移させる。一方、第2GIPが走査信号を偶数番目のゲート信号に伝送する期間において、第1GIPに含まれるすべてのステージの状態は変更されない。即ち、第1GIPは、第2GIPから独立して駆動される。同様に、第2GIPは、第1GIPから独立して駆動される。本実施形態によるゲート駆動部200は、第1GIPを第2GIPから独立に駆動することにより、奇数番目のゲート線に、任意の画素の行数にわたり連続して走査信号を伝送することができる。即ち、ゲート駆動部200は、同じ色を発光する複数の副画素の第1スイッチ素子T1に、任意の行数にわたり連続してゲート信号を供給することができる。本実施形態によるゲート駆動部200は、同じ色を発光する複数の副画素に任意の行数にわたり連続してゲート信号を供給するためにオン状態のステージの数を増加させる必要がない。したがって、オン状態のステージの数を増加させるために入力クロック数を上昇させる必要がない。よって、本実施形態による表示装置10は、消費電力を増大させることなく、同じ色を発光する副画素に、所定の行数にわたり連続して書き込みを行うことができる。

The gate driver according to the present embodiment includes

図12は、本実施形態に係るデータ駆動部300の概略構成を示すブロック図である。データ駆動部300は、データ選択部310およびデータ変換部320を含む。データ選択部310は、行メモリ部520から画像データR’G’B’W’を受信し、スケジューラ560からレジスタ選択信号RSSを受信する。レジスタ選択信号RSSは、入力レジスタ選択信号IRSS、入力有効化信号VALIDおよび出力レジスタ選択信号ORSSを含む。入力レジスタ選択信号IRSSは、画像データR’G’B’W’が格納されるべきレジスタを指定する。出力レジスタ選択信号ORSSは、出力されるべき画像データR’G’B’W’が格納されているレジスタを指定する。入力有効化信号VALIDは、入力レジスタ選択信号IRSSを有効化または無効化する。データ選択部310は複数のレジスタを有し、行メモリ部520から受信した画像データR’G’B’W’を、スケジューラ560から受信したレジスタ選択信号IRSSおよび入力有効化信号VALIDにしたがって格納する。具体的には、データ選択部310は、入力有効化信号VALIDがハイレベルの場合に、レジスタ選択信号IRSSを有効にし、レジスタ選択信号IRSSで指定されたレジスタに画像データR’G’B’W’を格納する。また、データ選択部310は、出力レジスタ選択信号ORSSで指定されたレジスタに格納された画像データR’G’B’W’をデータ変換部320に伝送する。データ変換部320は、データ制御信号DSCを用いて画像データR’G’B’W’をアナログのデータ電圧DATAに変換し、データ線DL1~GLmを介して各画素に伝送する。

Figure 12 is a block diagram showing a schematic configuration of the

図13は、本実施形態に係る類似度判定部550の概略構成を示すブロック図である。類似度判定部550は、第1差分算出部551、第2差分算出部552、第1積算部553、第2積算部554、第1閾値判定部557、第2閾値判定部558およびリセット判定部559を含む。

Fig. 13 is a block diagram showing a schematic configuration of the

第1差分算出部551は、奇数列に配された副画素Pに係る第x行の画像データRGBW_O(x)を行メモリ部520から受信する。受信された画像データRGBW_O(x)は、例えば第x行に配された緑色副画素Gおよび白色副画素Wに書き込まれる画像データのRGBW値である。また、第1差分算出部551は、行メモリ部520から奇数列に配された副画素Pに係る第x-1行の画像データRGBW_O(x-1)を受信する。受信された画像データRGBW_O(x-1)は、画像データRGBW_O(x)の1行前の画像データであり、例えば第x-1行に配された緑色副画素Gおよび白色副画素Wに書き込まれる画像データのRGBW値である。第1差分算出部551は、受信した第x行の画像データRGBW_O(x)と第x-1行の画像データRGBW_O(x-1)との間の差分Diff_Oを計算し、計算の結果を第1積算部553に伝送する。

The first

第1積算部553は、各奇数列における第x行のRGBW値と第x-1行のRGBW値との間の差分Diff_Oのデータを第1差分算出部551から受信する。第1積算部553は、第1差分算出部551から受信した各奇数列の画像データの差分Diff_Oを積算する。例えば表示パネル100に含まれる奇数列の副画素の列数がmである場合、第1積算部553は、第x行のRGBW値と第x-1行のRGBW値との間の差分Diff_Oについて、奇数列の数に対応した(m-1)個の差分値を第1差分算出部551から受信する。第1積算部553は、第1差分算出部551から受信した各列間についての(m-1)個の差分Diff_Oを積算する。第1積算部553は、差分Diff_Oを積算した値Sum_Oを第1閾値判定部557に伝送する。なお、奇数列の画像データの差分Diff_Oの個数が1である場合、第1積算部553は省略され得る。

The

第1閾値判定部557は、第1積算部553から奇数列に係る第x行のRGBW値と奇数列に係る第x-1行のRGBW値との間の差分Diff_Oの積算値Sum_Oを受信する。第1閾値判定部557は、受信された積算値Sum_Oを所定の閾値と比較する。第1閾値判定部557は、受信された積算値Sum_Oが所定の閾値未満であると判断した場合に、奇数列に係る第x行の画像データは奇数列に係る第x-1行の画像データと類似していると判定する。一方、第1閾値判定部557は、受信した積算値Sum_Oが所定の閾値以上であると判断した場合に、奇数列に係る第x行の画像データは奇数列に係る第x-1行の画像データと類似していないと判定する。第1閾値判定部557は、判定の結果である信号RES_O(x)をスケジューラ560に伝送する。例えば、第1閾値判定部557は、奇数列に係る第x行の画像データが奇数列に係る第x-1行の画像データと類似していると判定した場合に信号RES_O(x)として1を出力する。一方、第1閾値判定部557は、奇数列に係る第x行の画像データが奇数列に係る第x-1行の画像データと類似していないと判定した場合に信号RES_O(x)として0を出力する。

The first

第2差分算出部552は、偶数列に配された副画素Pに係る第x行の画像データRGBW_E(x)を行メモリ部520から受信する。受信された画像データRGBW_E(x)は、例えば第x行に配された赤色副画素Rおよび青色副画素Bに書き込まれる画像データのRGBW値である。また、第2差分算出部552は、行メモリ部520から偶数列に配された副画素Pに係る第x-1行の画像データRGBW_E(x-1)を受信する。受信された画像データRGBW_E(x-1)は、画像データRGBW_E(x)の1行前の画像データであり、例えば第x-1行に配された赤色副画素Rおよび青色副画素Bに書き込まれる画像データのRGBW値である。第2差分算出部552は、受信した第x行の画像データRGBW_E(x)と第x-1行の画像データRGBW_E(x-1)との間の差分Diff_Eを計算し、計算の結果を第2積算部554に伝送する。

The second

第2積算部554は、各偶数列における第x行のRGBW値と第x-1行のRGBW値との間の差分Diff_Eのデータを第2差分算出部552から受信する。第2積算部554は、第2差分算出部552から受信した各偶数列の画像データの差分Diff_Eを積算する。例えば表示パネル100に含まれる偶数列の副画素の列数がmである場合、第2積算部554は、第x行のRGBW値と第x-1行のRGBW値との間の差分Diff_Eについて、偶数列の数に対応した(m-1)個の差分値を第2差分算出部552から受信する。第2積算部554は、第2差分算出部552から受信した各列間についての(m-1)個の差分Diff_Eを積算する。第2積算部554は、差分Diff_Eを積算した値Sum_Eを第2閾値判定部558に伝送する。なお、偶数列の画像データの差分Diff_Eの個数が1である場合、第2積算部554は省略され得る。

The

第2閾値判定部558は、第2積算部554から偶数列に係る第x行のRGBW値と偶数列に係る第x-1行のRGBW値との間の差分Diff_Eの積算値Sum_Eを受信する。第2閾値判定部558は、受信された積算値Sum_Eを所定の閾値と比較する。第2閾値判定部558は、受信された積算値Sum_Eが所定の閾値未満であると判断した場合に、偶数列に係る第x行の画像データは偶数列に係る第x-1行の画像データと類似していると判定する。一方、第2閾値判定部558は、受信した積算値Sum_Eが所定の閾値以上であると判断した場合に、偶数列に係る第x行の画像データは偶数列に係る第x-1行の画像データと類似していないと判定する。第2閾値判定部558は、判定の結果である信号RES_E(x)をスケジューラ560に伝送する。例えば、第2閾値判定部558は、偶数列に係る第x行の画像データが偶数列に係る第x-1行の画像データと類似していると判定した場合に信号RES_E(x)として1を出力する。一方、第1閾値判定部557は、偶数列に係る第x行の画像データが偶数列に係る第x-1行の画像データと類似していないと判定した場合に信号RES_E(x)として0を出力する。

The second

リセット判定部559は、水平同期信号Hsyncに基づいてリセット信号を生成する。具体的には、リセット判定部559は、水平同期信号Hsyncがハイレベルからローレベルに遷移するタイミングでリセット信号RSTを第1積算部553および第2積算部554に伝送する。第1積算部553および第2積算部554は、受信したリセット信号RSTに応じて画像データの差分の積算値をリセットして0に戻す。また、リセット判定部559は、水平同期信号Hsyncがハイレベルからローレベルに遷移するタイミングで第1閾値判定部557および第2閾値判定部558にイネーブル信号RES_Enableを伝送する。第1閾値判定部557および第2閾値判定部558は、受信したイネーブル信号RES_Enableに応じて閾値判定の結果である信号RES_O(x)およびRES_E(x)をスケジューラ560に伝送する。

The

図14は、本実施形態に係るスケジューラ560の概略構成を示すブロック図である。スケジューラ560は、バッファ561、走査順序決定部562、ゲート線決定部563、レジスタ564および選択信号決定部565を含む。

FIG. 14 is a block diagram showing a schematic configuration of a

バッファ561は、類似度判定部550から閾値判定の結果である信号RES_O(x)およびRES_E(x)を受信する。バッファ561は、受信した信号RES_O(x)およびRES_E(x)を走査順序決定部562に伝送する。例えば、バッファ561は、信号RES_OおよびRES_Eを任意の行数までバッファに格納し、当該行数分の信号RES_OおよびRES_Eを走査順序決定部562に伝送する。

The

走査順序決定部562は、任意の行数分の閾値判定の結果である信号RESをバッファ561から受信する。走査順序決定部562は、受信した信号RESに基づき、奇数列の副画素の列または偶数列の副画素の列に対して連続して走査する行数を決定する。走査順序決定部562は、連続して走査する行数を示す信号C_Numをゲート線決定部563、レジスタ564および選択信号決定部565に伝送する。

The scanning

ゲート線決定部563は、連続して走査する行数を示す信号C_Numを走査順序決定部562から受信する。ゲート線決定部563は、信号C_Numに基づいてゲート信号が印加されるゲート線の順序を決定する。ゲート線決定部563は、ゲート線指定信号GL_Numを信号変調部510に伝送する。信号変調部510は、ゲート線指定信号GL_Numに基づき変調されたデータイネーブル信号tDEを生成し、行メモリ部520は、信号変調部510から受信した変調されたデータイネーブル信号tDEに基づいて画像データRGBWを整列させる。

The gate

レジスタ564は、連続して走査する行数を示す信号C_Numを走査順序決定部562から受信および格納する。レジスタ564に格納された信号C_Numは、走査順序決定部562が次の任意の行数分について連続して走査する行数を決定する際に呼び出される。走査順序決定部562は、レジスタ564から受信した信号C_Numを用いて、奇数列の副画素の列または偶数列の副画素の列に対して連続して走査する行数を決定する。例えば、走査順序決定部562は、任意の行数分について直前に決定した出力した信号C_Num(x-1)に基づき、連続して走査する行数を示す信号C_Num(x)を決定する。具体的は、連続して走査する行数に上限が定められている場合に、ゲート線決定部563は信号C_Num(x)を信号C_Num(x-1)に応じて修正する。また、例えば奇数列の副画素について信号C_Num(x-1)と信号C_Num(x)との間に連続した類似性が認められる場合に、ゲート線決定部563は、奇数列の副画素について対応する行を連続して走査するように決定する。

The

選択信号決定部565は、連続して走査する行数を示す信号C_Numを走査順序決定部562から受信する。選択信号決定部565は、信号C_Numに基づき、入力レジスタ選択信号IRSS、出力レジスタ選択信号ORSSおよび入力有効化信号VALIDを生成する。入力レジスタ選択信号IRSSは、データ駆動部300に含まれるデータ選択部310において画像データR’G’B’W’が格納されるべきレジスタを指定する。出力レジスタ選択信号ORSSは、データ選択部310から出力されるべき画像データR’G’B’W’が格納されているレジスタを指定する。入力有効化信号VALIDは、入力レジスタ選択信号IRSSを有効化または無効化する。選択信号決定部565は、生成された入力レジスタ選択信号IRSS、出力レジスタ選択信号ORSSおよび入力有効化信号VALIDをデータ選択部310に伝送する。

The selection

図15は、本実施形態に係るデータ選択部310の概略構成を示すブロック図である。データ選択部310は、データ分割部311-1~311-m、第1レジスタ312-1~312-m、第2レジスタ313-1~313-mおよび選択部314-1~314-mを含む。

Figure 15 is a block diagram showing a schematic configuration of the

データ分割部311-1~311-mは、タイミング制御部500に含まれる行メモリ部520から画像データR’G’B’W’を受信する。また、データ分割部311-1~311-mは、スケジューラ560に含まれる選択信号決定部565から入力レジスタ選択信号IRSSおよび入力有効化信号VALIDを受信する。データ分割部311-1~311-mは、受信された入力レジスタ選択信号IRSSに基づき、受信された画像データR’G’B’W’を分割する。次いでデータ分割部311-1~311-mは、受信された入力レジスタ選択信号IRSSおよび入力有効化信号VALIDに基づき分割された画像データR’G’B’W’を第1レジスタ312-1~312-mまたは第2レジスタ313-1~313-mに伝送する。

The data division units 311-1 to 311-m receive image data R'G'B'W' from the

入力レジスタ選択信号IRSSが第1レジスタ312-1~312-mを指定しており且つ入力有効化信号VALIDが入力レジスタ選択信号IRSSを有効化している場合に、第1レジスタ312-1~312-mは、データ分割部311-1~311-mから受信した分割された画像データR’G’B’W’を格納する。即ち、第1レジスタ312-1~312-mは、画像データを記憶する記憶部として機能する。一方、入力レジスタ選択信号IRSSが第1レジスタ312-1~312-mを指定しているが入力有効化信号VALIDが入力レジスタ選択信号IRSSを無効化している場合に、第1レジスタ312-1~312-mは、データ分割部311-1~311-mから受信した分割された画像データR’G’B’W’を格納しない。 When the input register selection signal IRSS designates the first registers 312-1 to 312-m and the input enable signal VALID activates the input register selection signal IRSS, the first registers 312-1 to 312-m store the divided image data R'G'B'W' received from the data division units 311-1 to 311-m. That is, the first registers 312-1 to 312-m function as a storage unit that stores image data. On the other hand, when the input register selection signal IRSS designates the first registers 312-1 to 312-m but the input enable signal VALID disables the input register selection signal IRSS, the first registers 312-1 to 312-m do not store the divided image data R'G'B'W' received from the data division units 311-1 to 311-m.

入力レジスタ選択信号IRSSが第2レジスタ313-1~313-mを指定しており且つ入力有効化信号VALIDが入力レジスタ選択信号IRSSを有効化している場合に、第2レジスタ313-1~313-mは、データ分割部311-1~311-mから受信した分割された画像データR’G’B’W’を格納する。即ち、第2レジスタ313-1~313-mは、画像データを記憶する記憶部として機能する。一方、入力レジスタ選択信号IRSSが第2レジスタ313-1~313-mを指定しているが入力有効化信号VALIDが入力レジスタ選択信号IRSSを無効化している場合に、第2レジスタ313-1~313-mは、データ分割部311-1~311-mから受信した分割された画像データR’G’B’W’を格納しない。 When the input register selection signal IRSS designates the second registers 313-1 to 313-m and the input enable signal VALID activates the input register selection signal IRSS, the second registers 313-1 to 313-m store the divided image data R'G'B'W' received from the data division units 311-1 to 311-m. That is, the second registers 313-1 to 313-m function as storage units that store image data. On the other hand, when the input register selection signal IRSS designates the second registers 313-1 to 313-m but the input enable signal VALID disables the input register selection signal IRSS, the second registers 313-1 to 313-m do not store the divided image data R'G'B'W' received from the data division units 311-1 to 311-m.

選択部314-1~314-mは、スケジューラ560に含まれる選択信号決定部565から出力レジスタ選択信号ORSSを受信する。選択部314-1~314-mは、出力レジスタ選択信号ORSSが指定する第1レジスタ312-1~312-mまたは第2レジスタ313-1~313-mに格納されている分割された画像データR’G’B’W’(1~m)をデータ変換部320に伝送する。データ変換部320は、データ制御信号DSCを用いて受信された画像データR’G’B’W’をアナログのデータ電圧DATAに変換し、データ線DL1~GLmを介して各画素に伝送する。

The selection units 314-1 to 314-m receive an output register selection signal ORSS from a selection

図16および図17を参照して、スケジューラ560への入力信号に応じたデータ選択部310の動作の一例を説明する。図16は、本実施形態に係るスケジューラ560への入力の例を示す表である。図17は、本実施形態に係るデータ選択部310へ入力される信号の例を示す表である。

An example of the operation of the