JP7216640B2 - 極度のスループットのニューラル・ネットワークのためのスケーラブル・ストリーム・シナプス・スーパーコンピュータ - Google Patents

極度のスループットのニューラル・ネットワークのためのスケーラブル・ストリーム・シナプス・スーパーコンピュータ Download PDFInfo

- Publication number

- JP7216640B2 JP7216640B2 JP2019514276A JP2019514276A JP7216640B2 JP 7216640 B2 JP7216640 B2 JP 7216640B2 JP 2019514276 A JP2019514276 A JP 2019514276A JP 2019514276 A JP2019514276 A JP 2019514276A JP 7216640 B2 JP7216640 B2 JP 7216640B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- neurosynaptic

- core

- network

- board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/049—Temporal neural networks, e.g. delay elements, oscillating neurons or pulsed inputs

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0495—Quantised networks; Sparse networks; Compressed networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0499—Feedforward networks

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- General Physics & Mathematics (AREA)

- Data Mining & Analysis (AREA)

- Evolutionary Computation (AREA)

- General Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Computational Linguistics (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Artificial Intelligence (AREA)

- Neurology (AREA)

- Multi Processors (AREA)

- Management, Administration, Business Operations System, And Electronic Commerce (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Complex Calculations (AREA)

- Peptides Or Proteins (AREA)

- Image Generation (AREA)

- Image Processing (AREA)

- Measurement And Recording Of Electrical Phenomena And Electrical Characteristics Of The Living Body (AREA)

- Casting Devices For Molds (AREA)

Description

本開示の実施形態によれば、極度の並列性が、高スループットを可能にする。

100:ニューロシナプス・コア

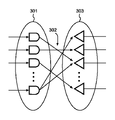

101、301:軸索

102:樹状突起

103、302:シナプス

104、303:ニューロン

201:メッシュ・ルータ

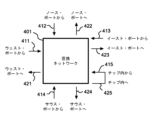

401:チップ

411、412、413、414、415:入りポート

421、422、423、424、425:出ポート

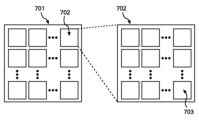

701:ボード

702:チップ

703:コア

704:ネットワーク

Claims (16)

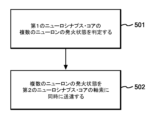

- 第1のニューロシナプス・コアの複数のニューロンの発火状態を、複数の時間ステップの各々の間に、並列に判定することであって、前記第1のニューロシナプス・コアは複数の軸索を含み、時分割多重化されていることを含む、前記判定することと、

前記第1のニューロシナプス・コア内で、前記複数のニューロンのすべてを前記複数の軸索上で並列に、一度に1つの軸索を動作させ、前記複数の時間ステップ内の前記複数のニューロンの前記発火状態に対応するバイナリ・ベクトルを構築することと、

各時間ステップを複数のサブ時間ステップに分割することと、

各サブ時間ステップ内で、送達されるべきスパイクについて複数の軸索の各々を同期的にチェックすることと、

前記チェックに応答して、1つまたは複数のスパイクを送達する必要があると判定し、複数のニューロンの発火状態を並列して更新することと、

複数の時間ステップの各々の間に、複数のチップ上の複数の付加的なニューロシナプス・コアに、複数の付加的なニューロシナプス・コアの各々の軸索に送達するために、バイナリ・ベクトルを複数のチップの各々に送達することによって、複数のニューロンの発火状態を並列に送達することと、

前記複数のニューロンの前記発火状態をパイプライン化することと、

前記第1のニューロシナプス・コアが第1のチップ上に位置し、少なくとも1つの前記付加的なニューロシナプス・コアが第2のチップ上に位置することと、

前記第1のチップが第1のボード上に位置し、前記第2のチップが第2のボード上に位置し、前記第1のボードと前記第2のボードとが接続されていることと、

前記第1のボード及び前記第2のボードを含む複数のボードが多重化して配置され、前記第1のボードと前記第2のボードとがルータを介して3次元的に接続されること、

を含む、方法。 - 前記第1のニューロシナプス・コア及び前記少なくとも1つの付加的なニューロシナプス・コアが、第1のチップ上に位置する、請求項1に記載の方法。

- 前記時間ステップ内で並列な送達が、コア間ネットワークを介する、請求項2に記載の方法。

- 前記時間ステップ内で並列な送達が、置換ネットワーク、Closネットワーク、又はバタフライ・ネットワークによって行われる、請求項3に記載の方法。

- 前記複数のニューロンの前記発火状態を、前記第1のチップと前記第2のチップとを接続するチップ間ネットワークを介して伝送すること、

をさらに含む請求項1に記載の方法。 - 前記チップ間ネットワークは、前記第1のチップの出ポート及び前記第2のチップの入りポートを含む、請求項5に記載の方法。

- 前記チップ間ネットワークは、前記第1のチップの入りポートに接続された前記第1のチップの出ポートを含む、請求項6に記載の方法。

- 前記第1及び第2のチップが第1のボード上に位置する、請求項1~7のいずれか1項に記載の方法。

- 複数のニューロシナプス・コアであって、前記ニューロシナプス・コアが、複数の軸索、複数のシナプス、及び複数のニューロンを含む、複数のニューロシナプス・コアと、

前記複数のニューロシナプス・コアを接続する第1のコア間ネットワークと、

を含むシステムであって、

第1のニューロシナプス・コアの複数のニューロンの発火状態を、複数の時間ステップの各々の間に、並列に判定することであって、前記第1のニューロシナプス・コアは複数の軸索を含み、時分割多重化されていることを含む、前記判定することと、

前記第1のニューロシナプス・コア内で、前記複数のニューロンのすべてを前記複数の軸索上で並列に、一度に1つの軸索を動作させ、前記複数の時間ステップ内の前記複数のニューロンの前記発火状態に対応するバイナリ・ベクトルを構築することと、

各時間ステップを複数のサブ時間ステップに分割することと、

各サブ時間ステップ内で、送達されるべきスパイクについて複数の軸索の各々を同期的にチェックすることと、

前記チェックに応答して、1つまたは複数のスパイクを送達する必要があると判定し、複数のニューロンの発火状態を並列して更新することと、

前記第1のコア間ネットワークは、前記複数のニューロシナプス・コアの第1のニューロシナプス・コアから、複数の時間ステップの各々の間に、複数のチップ上の複数の付加的なニューロシナプス・コアに、複数の付加的なニューロシナプス・コアの各々の軸索に送達するために、バイナリ・ベクトルを複数のチップの各々に送達することによって、複数のニューロンの発火状態を並列に送達するように適合され、

前記複数のニューロンの前記発火状態をパイプライン化し、

前記第1のコア間ネットワークは、第1のチップ上に位置し、第2のコア間ネットワークは、第2のチップ上に位置し、少なくとも1つの前記付加的なニューロシナプス・コアは、前記第2のコア間ネットワークに接続され、

前記第1のチップが第1のボード上に位置し、前記第2のチップが第2のボード上に位置し、前記第1のボードと前記第2のボードとが接続され、

前記第1のボード及び前記第2のボードを含む複数のボードが多重化して配置され、前記第1のボードと前記第2のボードとがルータを介して3次元的に接続される、

システム。 - 前記コア間ネットワークが、置換ネットワーク、Closネットワーク、又はバタフライ・ネットワークを含む、請求項9に記載のシステム。

- 前記第1のチップ及び前記第2のチップが隣接している、請求項9に記載のシステム。

- 前記第1のコア間ネットワークを前記第2のコア間ネットワークに接続するポートをさらに含む、請求項9~11のいずれか1項に記載のシステム。

- 前記第1のコア間ネットワークをそれ自体に接続するポートをさらに含む、請求項9~12のいずれか1項に記載のシステム。

- 前記第1及び第2のチップが第1のボード上に位置する、請求項9~12のいずれか1項に記載のシステム。

- 請求項1から請求項8のいずれか1項に記載の方法をコンピュータに実行させる、コンピュータ・プログラム。

- 請求項15に記載の前記コンピュータ・プログラムを、コンピュータ可読ストレージ媒体に格納した、ストレージ媒体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/282,705 US11270193B2 (en) | 2016-09-30 | 2016-09-30 | Scalable stream synaptic supercomputer for extreme throughput neural networks |

| US15/282,705 | 2016-09-30 | ||

| PCT/IB2017/055830 WO2018060840A1 (en) | 2016-09-30 | 2017-09-26 | Scalable stream synaptic supercomputer for extreme throughput neural networks |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2019537093A JP2019537093A (ja) | 2019-12-19 |

| JP7216640B2 true JP7216640B2 (ja) | 2023-02-01 |

Family

ID=61758251

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019514276A Active JP7216640B2 (ja) | 2016-09-30 | 2017-09-26 | 極度のスループットのニューラル・ネットワークのためのスケーラブル・ストリーム・シナプス・スーパーコンピュータ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11270193B2 (ja) |

| JP (1) | JP7216640B2 (ja) |

| CN (1) | CN109564637B (ja) |

| DE (1) | DE112017002931T5 (ja) |

| GB (1) | GB2569074B (ja) |

| WO (1) | WO2018060840A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10810488B2 (en) * | 2016-12-20 | 2020-10-20 | Intel Corporation | Neuromorphic core and chip traffic control |

| US10726331B1 (en) * | 2019-08-26 | 2020-07-28 | International Business Machines Corporation | Neural network circuits providing early integration before analog-to-digital conversion |

| CN113241369B (zh) * | 2021-04-29 | 2022-05-06 | 齐鲁工业大学 | 一种支持孤波传导的模拟神经纤维的pn微米线 |

| CN113554162B (zh) * | 2021-07-23 | 2022-12-20 | 上海新氦类脑智能科技有限公司 | 轴突输入扩展方法、装置、设备和存储介质 |

| CN115099395B (zh) * | 2022-08-25 | 2022-11-15 | 北京灵汐科技有限公司 | 神经网络构建方法及装置、设备、介质 |

| US12468549B2 (en) | 2023-06-13 | 2025-11-11 | Bank Of America Corporation | Automated system for restarting large scale cluster supercomputers |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120259804A1 (en) | 2011-04-08 | 2012-10-11 | International Business Machines Corporation | Reconfigurable and customizable general-purpose circuits for neural networks |

| US20140180984A1 (en) | 2012-12-21 | 2014-06-26 | International Business Machines Corporation | Time-division multiplexed neurosynaptic module with implicit memory addressing for implementing a universal substrate of adaptation |

| US20150262057A1 (en) | 2012-03-29 | 2015-09-17 | International Business Machines Corporation | Synaptic, dendritic, somatic, and axonal plasticity in a network of neural cores using a plastic multi-stage crossbar switching |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0652132A (ja) | 1992-07-28 | 1994-02-25 | Mitsubishi Electric Corp | 並列演算半導体集積回路装置およびそれを用いたシステム |

| US8676734B2 (en) | 2010-07-07 | 2014-03-18 | Qualcomm, Incorporated | Methods and systems for replaceable synaptic weight storage in neuro-processors |

| US8510239B2 (en) * | 2010-10-29 | 2013-08-13 | International Business Machines Corporation | Compact cognitive synaptic computing circuits with crossbar arrays spatially in a staggered pattern |

| US8515885B2 (en) | 2010-10-29 | 2013-08-20 | International Business Machines Corporation | Neuromorphic and synaptronic spiking neural network with synaptic weights learned using simulation |

| US8812414B2 (en) * | 2011-05-31 | 2014-08-19 | International Business Machines Corporation | Low-power event-driven neural computing architecture in neural networks |

| US9147156B2 (en) * | 2011-09-21 | 2015-09-29 | Qualcomm Technologies Inc. | Apparatus and methods for synaptic update in a pulse-coded network |

| US8909576B2 (en) * | 2011-09-16 | 2014-12-09 | International Business Machines Corporation | Neuromorphic event-driven neural computing architecture in a scalable neural network |

| US8996430B2 (en) * | 2012-01-27 | 2015-03-31 | International Business Machines Corporation | Hierarchical scalable neuromorphic synaptronic system for synaptic and structural plasticity |

| IN2014DN09465A (ja) | 2012-05-24 | 2015-07-17 | Ericsson Telefon Ab L M | |

| US9159020B2 (en) | 2012-09-14 | 2015-10-13 | International Business Machines Corporation | Multiplexing physical neurons to optimize power and area |

| US9020867B2 (en) | 2012-11-06 | 2015-04-28 | International Business Machines Corporation | Cortical simulator for object-oriented simulation of a neural network |

| US20140143191A1 (en) | 2012-11-20 | 2014-05-22 | Qualcomm Incorporated | Piecewise linear neuron modeling |

| US8990130B2 (en) | 2012-11-21 | 2015-03-24 | International Business Machines Corporation | Consolidating multiple neurosynaptic cores into one memory |

| US9753959B2 (en) | 2013-10-16 | 2017-09-05 | University Of Tennessee Research Foundation | Method and apparatus for constructing a neuroscience-inspired artificial neural network with visualization of neural pathways |

| US9798972B2 (en) | 2014-07-02 | 2017-10-24 | International Business Machines Corporation | Feature extraction using a neurosynaptic system for object classification |

| US9881252B2 (en) * | 2014-09-19 | 2018-01-30 | International Business Machines Corporation | Converting digital numeric data to spike event data |

| US10339439B2 (en) * | 2014-10-01 | 2019-07-02 | Thalchemy Corporation | Efficient and scalable systems for calculating neural network connectivity in an event-driven way |

| US10552740B2 (en) * | 2014-11-10 | 2020-02-04 | International Business Machines Corporation | Fault-tolerant power-driven synthesis |

| US10679120B2 (en) * | 2014-11-10 | 2020-06-09 | International Business Machines Corporation | Power driven synaptic network synthesis |

| CN104615909B (zh) * | 2015-02-02 | 2018-02-13 | 天津大学 | 基于FPGA的Izhikevich神经元网络同步放电仿真平台 |

| US9984323B2 (en) * | 2015-03-26 | 2018-05-29 | International Business Machines Corporation | Compositional prototypes for scalable neurosynaptic networks |

| CN105095967B (zh) * | 2015-07-16 | 2018-02-16 | 清华大学 | 一种多模态神经形态网络核 |

| CN105095961B (zh) * | 2015-07-16 | 2017-09-29 | 清华大学 | 一种人工神经网络和脉冲神经网络的混合系统 |

| CN105488565A (zh) * | 2015-11-17 | 2016-04-13 | 中国科学院计算技术研究所 | 加速深度神经网络算法的加速芯片的运算装置及方法 |

| CN105550749A (zh) * | 2015-12-09 | 2016-05-04 | 四川长虹电器股份有限公司 | 一种新型网络拓扑结构的卷积神经网络的构造方法 |

-

2016

- 2016-09-30 US US15/282,705 patent/US11270193B2/en active Active

-

2017

- 2017-09-26 GB GB1904766.1A patent/GB2569074B/en active Active

- 2017-09-26 JP JP2019514276A patent/JP7216640B2/ja active Active

- 2017-09-26 CN CN201780047346.9A patent/CN109564637B/zh active Active

- 2017-09-26 DE DE112017002931.7T patent/DE112017002931T5/de active Pending

- 2017-09-26 WO PCT/IB2017/055830 patent/WO2018060840A1/en not_active Ceased

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120259804A1 (en) | 2011-04-08 | 2012-10-11 | International Business Machines Corporation | Reconfigurable and customizable general-purpose circuits for neural networks |

| US20150262057A1 (en) | 2012-03-29 | 2015-09-17 | International Business Machines Corporation | Synaptic, dendritic, somatic, and axonal plasticity in a network of neural cores using a plastic multi-stage crossbar switching |

| US20140180984A1 (en) | 2012-12-21 | 2014-06-26 | International Business Machines Corporation | Time-division multiplexed neurosynaptic module with implicit memory addressing for implementing a universal substrate of adaptation |

Non-Patent Citations (8)

| Title |

|---|

| Anargyros Krikelis,"A novel massively parallel associative processing architecture for the implementation of artificial neural networks",Proceedings of 1991 International Conference on Acoustics, Speech, and Signal Processing (ICASSP 91),IEEE,1991年04月17日,Pages 1057-1060,ISBN: 0-7803-0003-3, <DOI: 10.1109/ICASSP.1991.150828>. |

| Arnon Amir, et al.,"Cognitive Computing Programming Paradigm: A Corelet Language for Composing Networks of Neurosynaptic Cores",Proceedings of the 2013 International Joint Conference on Neural Networks (IJCNN),2013年08月09日,Pages 1-10,ISBN:978-1-4673-6129-3, <DOI: 10.1109/IJCNN.2013.6707078>. |

| Djones Lettnin, et al.,"Synthesis of Embedded SystemC Design: A Case Study of Digital Neural Networks",Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers' Forum (DATE'04),2004年02月20日,Pages 1-6,ISBN:0-7695-2085-5, <DOI: 10.1109/DATE.2004.1269239>. |

| Dmitri Vainbrand, et al.,"Scalable network-on-chip architecture for configurable neural networks",Microprocessors and Microsystems,Elsevier B.V.,2010年08月13日,Vol.35, No.2,Pages 152-166,[online], [令和3年10月31日検索], インターネット, <URL: https://webee.technion.ac.il/people/ran/papers/NoCforNN-VainbrandGinosarMicroMicro2011.pdf>,ISSN: 0141-9331, <DOI: 10.1016/j.micpro.2010.08.005>. |

| Paul Merolla, et al.,"A Digital Neurosynaptic Core Using Embedded Crossbar Memory with 45pJ per Spike in 45nm",Proceedings of 2011 IEEE Custom Integrated Circuits Conference (CICC),2011年09月21日,Pages 1-4,ISBN: 978-1-4577-0223-5, <DOI: 10.1109/CICC.2011.6055294>. |

| Raqibul Hasan, et al.,"A Reconfigurable Low Power High Throughput Architecture for Deep Network Training",arXiv:1603.07400v2,version v2,[online], arXiv,2016年06月15日,Pages 1-9,[令和3年2月19日検索], インターネット, <URL: https://arxiv.org/abs/1603.07400v2> and <URL: https://arxiv.org/ftp/arxiv/papers/1603/1603.07400.pdf>. |

| Robert Preissl, et al.,"Compass: A scalable simulator for an architecture for Cognitive Computing",Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis,IEEE,2012年11月16日,Pages 1-11,ISBN: 978-1-4673-0806-9, <DOI: 10.1109/SC.2012.34>. |

| Steve K. Esser, et al.,"Cognitive Computing Systems: Algorithms and Applications for Networks of Neurosynaptic Cores",Proceedings of the 2013 International Joint Conference on Neural Networks (IJCNN),2013年08月09日,Pages 1-10,ISBN: 978-1-4673-6129-3, <DOI: 10.1109/IJCNN.2013.6706746>. |

Also Published As

| Publication number | Publication date |

|---|---|

| CN109564637B (zh) | 2023-05-12 |

| JP2019537093A (ja) | 2019-12-19 |

| GB2569074A (en) | 2019-06-05 |

| US20180096242A1 (en) | 2018-04-05 |

| GB201904766D0 (en) | 2019-05-22 |

| US11270193B2 (en) | 2022-03-08 |

| DE112017002931T5 (de) | 2019-03-14 |

| CN109564637A (zh) | 2019-04-02 |

| GB2569074B (en) | 2022-03-23 |

| WO2018060840A1 (en) | 2018-04-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7216640B2 (ja) | 極度のスループットのニューラル・ネットワークのためのスケーラブル・ストリーム・シナプス・スーパーコンピュータ | |

| JP7051854B2 (ja) | 面積高効率、再設定可能、エネルギ高効率、速度高効率のニューラル・ネットワーク基板 | |

| US12165050B2 (en) | Networks for distributing parameters and data to neural network compute cores | |

| US10782726B2 (en) | Optimizing core utilization in neurosynaptic systems | |

| US12067472B2 (en) | Defect resistant designs for location-sensitive neural network processor arrays | |

| JP6912491B2 (ja) | 省エネルギな多重ニューラル・コア回路、方法及びニューロシナプティック・システム | |

| US12554961B2 (en) | Block transfer of neuron output values through data memory for neurosynaptic processors | |

| US11586893B2 (en) | Core utilization optimization by dividing computational blocks across cores | |

| US11645501B2 (en) | Distributed, event-based computation using neuromorphic cores | |

| CN116348890A (zh) | 神经网络处理 | |

| US20180082182A1 (en) | Optimizing neurosynaptic networks | |

| US12400109B2 (en) | Functional synthesis of networks of neurosynaptic cores on neuromorphic substrates | |

| US12067481B2 (en) | Array-integrated upstream/downstream router for circuit switched parallel connectivity | |

| KR102824062B1 (ko) | 온칩 오퍼레이션 초기화 | |

| CN115362448A (zh) | 来自存储器元件网格的神经网络权重分发 | |

| US12518149B2 (en) | Implicit vector concatenation within 2D mesh routing | |

| US11295203B2 (en) | Optimizing neuron placement in a neuromorphic system | |

| US20220129769A1 (en) | Modular neural network computing apparatus with distributed neural network storage |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210316 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210604 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20211116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220210 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20220502 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20220517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220906 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20220906 |

|

| C11 | Written invitation by the commissioner to file amendments |

Free format text: JAPANESE INTERMEDIATE CODE: C11 Effective date: 20220920 |

|

| C12 | Written invitation by the commissioner to file intermediate amendments |

Free format text: JAPANESE INTERMEDIATE CODE: C12 Effective date: 20220920 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20221107 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20221108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230120 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7216640 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |