JP6957134B2 - Evaluation method of oxide semiconductor - Google Patents

Evaluation method of oxide semiconductor Download PDFInfo

- Publication number

- JP6957134B2 JP6957134B2 JP2016143073A JP2016143073A JP6957134B2 JP 6957134 B2 JP6957134 B2 JP 6957134B2 JP 2016143073 A JP2016143073 A JP 2016143073A JP 2016143073 A JP2016143073 A JP 2016143073A JP 6957134 B2 JP6957134 B2 JP 6957134B2

- Authority

- JP

- Japan

- Prior art keywords

- insulator

- oxide semiconductor

- transistor

- conductor

- oxide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明は、例えば、絶縁膜、トランジスタ及び半導体装置に関する。または、本発明は、例えば、絶縁膜、トランジスタ及び半導体装置の評価方法に関する。または、本発明は、例えば、絶縁膜、トランジスタ及び半導体装置の製造方法に関する。または、本発明は、例えば、絶縁膜、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサ、電子機器に関する。または、絶縁膜、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の製造方法に関する。または、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の駆動方法に関する。 The present invention relates to, for example, insulating films, transistors and semiconductor devices. Alternatively, the present invention relates to, for example, an evaluation method for an insulating film, a transistor, and a semiconductor device. Alternatively, the present invention relates to, for example, a method for manufacturing an insulating film, a transistor, and a semiconductor device. Alternatively, the present invention relates to, for example, an insulating film, a display device, a light emitting device, a lighting device, a power storage device, a storage device, a processor, and an electronic device. Alternatively, the present invention relates to a method for manufacturing an insulating film, a display device, a liquid crystal display device, a light emitting device, a storage device, and an electronic device. Alternatively, the present invention relates to a semiconductor device, a display device, a liquid crystal display device, a light emitting device, a storage device, and a method for driving an electronic device.

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。 One aspect of the present invention is not limited to the above technical fields. The technical field of one aspect of the invention disclosed in the present specification and the like relates to a product, a method, or a manufacturing method. Alternatively, one aspect of the invention relates to a process, machine, manufacture, or composition of matter.

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路及び電子機器は、半導体装置を有する場合がある。 In the present specification and the like, the semiconductor device refers to all devices that can function by utilizing the semiconductor characteristics. Display devices, light emitting devices, lighting devices, electro-optical devices, semiconductor circuits and electronic devices may have semiconductor devices.

絶縁表面を有する基板上の半導体膜を用いて、トランジスタを構成する技術が注目されている。当該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体膜としてシリコンが知られている。 Attention is being paid to a technique for constructing a transistor by using a semiconductor film on a substrate having an insulating surface. The transistor is widely applied to semiconductor devices such as integrated circuits and display devices. Silicon is known as a semiconductor film applicable to transistors.

トランジスタの半導体膜に用いられるシリコンは、用途によって非晶質シリコンと多結晶シリコンとが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積基板への成膜技術が確立されている非晶質シリコンを用いると好適である。一方、駆動回路を一体形成した高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコンを用いると好適である。多結晶シリコンは、非晶質シリコンに対し高温での熱処理、またはレーザ光処理を行うことで形成する方法が知られる。 Amorphous silicon and polycrystalline silicon are used as the silicon used for the semiconductor film of the transistor depending on the application. For example, when applied to a transistor constituting a large-scale display device, it is preferable to use amorphous silicon for which a film-forming technique for a large-area substrate has been established. On the other hand, when applied to a transistor constituting a high-performance display device in which a drive circuit is integrally formed, it is preferable to use polycrystalline silicon capable of producing a transistor having high field effect mobility. A method of forming polycrystalline silicon by heat-treating amorphous silicon at a high temperature or performing laser light treatment is known.

一方で、近年では、トランジスタの半導体膜として、酸化物半導体が用いられている。(特許文献1参照。)。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタの半導体に用いることができる。また、酸化物半導体を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路を一体形成した高機能の表示装置を実現できる。また、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用できるため、設備投資を抑えられるメリットもある。

On the other hand, in recent years, oxide semiconductors have been used as semiconductor films for transistors. (See

また、酸化物半導体の諸特性を非接触で評価する方法として、酸化物半導体に励起光及びマイクロ波を照射し、励起光の照射により変化するマイクロ波の反射波を測定する方法が開示されている(特許文献2参照。)。この測定はマイクロ波光導電減衰法(μ―PCD:Microwave−Photo Conductive Decay)と呼ばれる。非特許文献1には、非晶質の酸化物半導体は、波長349nmの励起光の浸透長(侵入長または進入長などとも呼ばれる。)が300nm程度であることが示されている。

Further, as a method for evaluating various characteristics of an oxide semiconductor in a non-contact manner, a method of irradiating an oxide semiconductor with excitation light and microwaves and measuring the reflected wave of microwaves changed by the irradiation of the excitation light is disclosed. (See Patent Document 2). This measurement is called the microwave photoconductive attenuation method (μ-PCD: Microwave-Photo Conductive Decay).

また、非特許文献2には、代表的な酸化物半導体であるIn−Ga−Zn酸化物の電子スピン共鳴(ESR:Electron Spin Resonance)によるスピン密度と導電率との関係が開示されている。また、In−Ga−Zn酸化物のキャリア発生源として、酸素欠損及び水素に起因する欠陥準位が示されている。

Further,

トランジスタを作製する場合、チャネル、ソース、ドレイン、ゲート電極などを形成した後に電気特性の測定が可能となる。その為、トランジスタ作製工程の途中で異常があった場合でも、電気特性測定の結果を工程管理にフィードバックするには時間がかかり、生産性悪化の原因となる。 When manufacturing a transistor, it is possible to measure electrical characteristics after forming channels, sources, drains, gate electrodes, and the like. Therefore, even if there is an abnormality in the middle of the transistor manufacturing process, it takes time to feed back the result of the electrical characteristic measurement to the process control, which causes deterioration of productivity.

また、酸化物半導体を用いたトランジスタにおいて、良好な電気特性を得るには、酸化物半導体のキャリア密度の制御が重要である。 Further, in a transistor using an oxide semiconductor, it is important to control the carrier density of the oxide semiconductor in order to obtain good electrical characteristics.

上記に鑑み、本発明の一態様は、トランジスタ作製工程途中で酸化物半導体のキャリア密度を評価する方法を提供することを課題の一とする。または、トランジスタのしきい値電圧のマイナスシフトを抑制することを課題の一とする。または、トランジスタのオン電流を向上することを課題の一とする。または、トランジスタの電界効果移動度を向上することを課題の一とする。 In view of the above, one aspect of the present invention is to provide a method for evaluating the carrier density of an oxide semiconductor during the transistor manufacturing process. Alternatively, one of the issues is to suppress a negative shift of the threshold voltage of the transistor. Alternatively, one of the issues is to improve the on-current of the transistor. Alternatively, one of the tasks is to improve the electric field mobility mobility of the transistor.

また、本発明の一態様は、トランジスタを生産性高く作製することを課題の一とする。または、該トランジスタを有する半導体装置を生産性高く作製することを課題の一とする。 Further, one aspect of the present invention is to manufacture a transistor with high productivity. Alternatively, one of the tasks is to manufacture a semiconductor device having the transistor with high productivity.

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出できる。 The description of these issues does not prevent the existence of other issues. It should be noted that one aspect of the present invention does not need to solve all of these problems. It should be noted that the problems other than these are naturally clarified from the description of the description, drawings, claims and the like, and the problems other than these can be extracted from the description of the description, drawings, claims and the like.

μ―PCD測定は、非接触、非破壊、短時間で酸化物半導体の物性の測定が可能であり、μ―PCD測定で得られるピーク強度及びライフタイムはキャリア密度と相関がある。 The μ-PCD measurement can measure the physical properties of oxide semiconductors in a non-contact, non-destructive manner in a short time, and the peak intensity and lifetime obtained by the μ-PCD measurement correlate with the carrier density.

トランジスタ作製工程途中にμ―PCD測定を行うことにより、トランジスタ作製工程途中の酸化物半導体のキャリア密度を評価できる。よって、トランジスタ作製工程途中にトランジスタの電気特性を推測できるようになる為、トランジスタ作製の生産性を高めるには有効である。 By performing μ-PCD measurement during the transistor manufacturing process, the carrier density of the oxide semiconductor during the transistor manufacturing process can be evaluated. Therefore, since the electrical characteristics of the transistor can be estimated during the transistor manufacturing process, it is effective in increasing the productivity of transistor manufacturing.

本明細書で開示する発明の一態様は、試料を準備し、試料は、基板と、基板上に形成した酸化物半導体と、を有し、マイクロ波及び励起光を試料に照射するマイクロ波光導電減衰法を用いて、試料によって反射されたマイクロ波の強度を測定し、反射されたマイクロ波の強度のピーク値から酸化物半導体のキャリア密度を評価する、酸化物半導体の評価方法である。 One aspect of the invention disclosed herein is to prepare a sample, the sample having a substrate and an oxide semiconductor formed on the substrate, and irradiating the sample with microwaves and excitation light. This is an oxide semiconductor evaluation method in which the intensity of microwaves reflected by a sample is measured by using an attenuation method, and the carrier density of the oxide semiconductor is evaluated from the peak value of the intensity of the reflected microwaves.

本明細書で開示する発明の一態様は、キャリア密度は、マイクロ波光導電減衰法の反射強度のピーク値及びホール効果測定で得られた酸化物半導体のキャリア密度の相関より評価される、酸化物半導体の評価方法である。 In one aspect of the invention disclosed herein, the carrier density is evaluated from the correlation between the peak value of the reflection intensity of the microwave photoconductive attenuation method and the carrier density of the oxide semiconductor obtained by the Hall effect measurement. This is a semiconductor evaluation method.

本明細書で開示する発明の一態様は、励起光のエネルギーが、酸化物半導体のバンドギャップより大きく、基板のバンドギャップより小さいことを特徴とする酸化物半導体の評価方法である。 One aspect of the invention disclosed in the present specification is a method for evaluating an oxide semiconductor, characterized in that the energy of the excitation light is larger than the band gap of the oxide semiconductor and smaller than the band gap of the substrate.

本明細書で開示する発明の一態様は、試料が、酸化物半導体の上に形成された第1の絶縁体と、を有し、マイクロ波光導電減衰法の励起光のエネルギーが、第1の絶縁体のバンドギャップより小さいことを特徴とする酸化物半導体の評価方法である。 In one aspect of the invention disclosed herein, the sample has a first insulator formed on an oxide semiconductor, and the energy of the excitation light of the microwave photoconductive attenuation method is the first. This is an evaluation method for an oxide semiconductor, which is characterized by being smaller than the band gap of an insulator.

本明細書で開示する発明の一態様は、試料が、基板と酸化物半導体の間に形成された第2の絶縁体と、を有し、マイクロ波光導電減衰法の励起光のエネルギーが、第2の絶縁体のバンドギャップより小さいことを特徴とする酸化物半導体の評価方法である。 In one aspect of the invention disclosed herein, the sample has a second insulator formed between the substrate and the oxide semiconductor, and the energy of the excitation light of the microwave photoconductive attenuation method is the first. This is an evaluation method for an oxide semiconductor, which is characterized in that it is smaller than the band gap of the insulator of 2.

本明細書で開示する発明の一態様は、第1の絶縁体または第2の絶縁体が積層構造であることを特徴とする酸化物半導体の評価方法である。 One aspect of the invention disclosed in the present specification is a method for evaluating an oxide semiconductor, characterized in that the first insulator or the second insulator has a laminated structure.

本明細書で開示する発明の一態様は、絶縁体と、酸化物半導体と、導電体と、を有し、

酸化物半導体は、絶縁体を介して、酸化物半導体と導電体とが互いに重なる領域を有し、領域のバンドギャップが3.17eV以上3.58eV以下、かつ膜厚が27.7nm以上32.5nm以下において、酸化物半導体のマイクロ波光導電減衰法によるマイクロ波の反射強度のピーク値が1042mV以下となる領域を有することを特徴とする半導体装置である。

One aspect of the invention disclosed herein comprises an insulator, an oxide semiconductor, and a conductor.

The oxide semiconductor has a region in which the oxide semiconductor and the conductor overlap each other via an insulator, the band gap of the region is 3.17 eV or more and 3.58 eV or less, and the film thickness is 27.7 nm or more and 32. It is a semiconductor device characterized by having a region where the peak value of the reflection intensity of microwaves by the microwave photoconductive attenuation method of an oxide semiconductor is 1042 mV or less at 5 nm or less.

本明細書で開示する発明の一態様は、領域において、酸化物半導体のマイクロ波光導電減衰法によるライフタイムτ1が50nsec以上となる領域を有することを特徴とする半導体装置である。 One aspect of the invention disclosed in the present specification is a semiconductor device characterized in that the region has a region in which the lifetime τ1 of the oxide semiconductor by the microwave photoconductive attenuation method is 50 nsec or more.

本明細書で開示する発明の一態様は、第1の基板及び第2の基板上に酸化物半導体を形成し、第2の基板上の酸化物半導体をマイクロ波光導電減衰法で測定し、マイクロ波光導電減衰法の励起光のエネルギーは、酸化物半導体のバンドギャップより大きく、第2の基板のバンドギャップより小さく、測定におけるマイクロ波の反射強度のピーク値を算出し、ピーク値から酸化物半導体のキャリア密度を評価し、酸化物半導体の評価を行う、半導体装置の作製方法である。 One aspect of the invention disclosed herein is to form an oxide semiconductor on a first substrate and a second substrate, measure the oxide semiconductor on the second substrate by a microwave photoconductive attenuation method, and micron. The energy of the excitation light of the wave light conductivity attenuation method is larger than the band gap of the oxide semiconductor and smaller than the band gap of the second substrate. This is a method for manufacturing a semiconductor device, which evaluates the carrier density of an oxide semiconductor and evaluates an oxide semiconductor.

トランジスタ作製工程途中で酸化物半導体のキャリア密度を評価する方法を提供できる。または、トランジスタのしきい値電圧のマイナスシフトを抑制できる。または、トランジスタのオン電流を向上できる。または、トランジスタの電界効果移動度を向上できる。 It is possible to provide a method for evaluating the carrier density of an oxide semiconductor during the transistor manufacturing process. Alternatively, the negative shift of the threshold voltage of the transistor can be suppressed. Alternatively, the on-current of the transistor can be improved. Alternatively, the field effect mobility of the transistor can be improved.

または、トランジスタを生産性高く作製できる。または、該トランジスタを有する半導体装置を生産性高く作製できる。 Alternatively, the transistor can be manufactured with high productivity. Alternatively, a semiconductor device having the transistor can be manufactured with high productivity.

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の

一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果

は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図

面、請求項などの記載から、これら以外の効果を抽出することが可能である。

The description of these effects does not preclude the existence of other effects. It should be noted that one aspect of the present invention does not necessarily have to have all of these effects. It should be noted that the effects other than these are naturally clarified from the description of the description, drawings, claims, etc., and it is possible to extract the effects other than these from the description of the description, drawings, claims, etc. Is.

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。 Hereinafter, embodiments will be described with reference to the drawings. However, it is easily understood by those skilled in the art that the embodiments can be implemented in many different embodiments, and that the embodiments and details can be variously changed without departing from the spirit and scope thereof. .. Therefore, the present invention is not construed as being limited to the description of the following embodiments.

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。 Also, in the drawings, the size, layer thickness, or area may be exaggerated for clarity. Therefore, it is not necessarily limited to that scale. The drawings schematically show ideal examples, and are not limited to the shapes or values shown in the drawings.

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。 In addition, the ordinal numbers "first", "second", and "third" used in the present specification are added to avoid confusion of the components, and are not limited numerically. I will add it.

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。 Further, in the present specification, terms indicating the arrangement such as "above" and "below" are used for convenience in order to explain the positional relationship between the configurations with reference to the drawings. In addition, the positional relationship between the configurations changes as appropriate according to the direction in which each configuration is depicted. Therefore, it is not limited to the words and phrases explained in the specification, and can be appropriately paraphrased according to the situation.

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域またはドレイン電極)とソース(ソース端子、ソース領域またはソース電極)の間にチャネル領域を有しており、ドレインとチャネル領域とソースとを介して電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。 Further, in the present specification and the like, a transistor is an element having at least three terminals including a gate, a drain, and a source. Then, a channel region is provided between the drain (drain terminal, drain region or drain electrode) and the source (source terminal, source region or source electrode), and a current flows through the drain, the channel region and the source. Can be done. In the present specification and the like, the channel region refers to a region in which a current mainly flows.

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。 Further, the functions of the source and the drain may be interchanged when transistors having different polarities are adopted or when the direction of the current changes in the circuit operation. Therefore, in the present specification and the like, the terms source and drain can be used interchangeably.

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。 Further, in the present specification and the like, "electrically connected" includes a case where they are connected via "something having some kind of electrical action". Here, the "thing having some kind of electrical action" is not particularly limited as long as it enables the exchange of electric signals between the connection targets. For example, "things having some kind of electrical action" include electrodes, wirings, switching elements such as transistors, resistance elements, inductors, capacitors, and other elements having various functions.

また、本明細書等において、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる場合がある。 Further, in the present specification and the like, when explaining the structure of the invention using drawings, reference numerals indicating the same thing may be commonly used between different drawings.

また、本明細書等において、「平行」とは、二つの直線が−10°以上10°以下の角度で配置されている状態をいう。したがって、−5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が−30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。 Further, in the present specification and the like, "parallel" means a state in which two straight lines are arranged at an angle of −10 ° or more and 10 ° or less. Therefore, the case of −5 ° or more and 5 ° or less is also included. Further, "substantially parallel" means a state in which two straight lines are arranged at an angle of −30 ° or more and 30 ° or less. Further, "vertical" means a state in which two straight lines are arranged at an angle of 80 ° or more and 100 ° or less. Therefore, the case of 85 ° or more and 95 ° or less is also included. Further, "substantially vertical" means a state in which two straight lines are arranged at an angle of 60 ° or more and 120 ° or less.

また、本明細書等において、「膜」という用語と、「層」という用語とは、場合によっては、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。 Further, in the present specification and the like, the term "membrane" and the term "layer" can be interchanged with each other in some cases. For example, it may be possible to change the term "conductive layer" to the term "conductive layer". Alternatively, for example, it may be possible to change the term "insulating film" to the term "insulating layer".

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。 Even when the term "semiconductor" is used, for example, if the conductivity is sufficiently low, it may have characteristics as an "insulator". In addition, the boundary between "semiconductor" and "insulator" is ambiguous, and it may not be possible to strictly distinguish between them. Therefore, the "semiconductor" described in the present specification may be paraphrased as an "insulator". Similarly, the "insulator" described herein may be paraphrased as a "semiconductor."

(実施の形態1)

本実施の形態においては、本発明の一態様に用いることのできる、μ―PCD測定を用いて酸化物半導体の評価を行う方法について、図1乃至図3を参照して説明する。

(Embodiment 1)

In the present embodiment, a method for evaluating an oxide semiconductor using μ-PCD measurement, which can be used in one aspect of the present invention, will be described with reference to FIGS. 1 to 3.

<μ―PCD測定>

以下に、μ―PCD測定について説明する。

<Μ-PCD measurement>

The μ-PCD measurement will be described below.

図1は、μ―PCD測定を行うための装置の一例を示す模式図である。図1に示す装置は、ワイドギャップ半導体の薄膜の評価に好適である。特に、トランジスタの半導体に用いられる、1nm以上1μm以下、2nm以上500nm以下、3nm以上200nm以下または5nm以上100nm以下の膜厚のワイドギャップ半導体の評価に好適である。 FIG. 1 is a schematic view showing an example of an apparatus for performing μ-PCD measurement. The apparatus shown in FIG. 1 is suitable for evaluating a thin film of a wide-gap semiconductor. In particular, it is suitable for evaluation of wide-gap semiconductors having a film thickness of 1 nm or more and 1 μm or less, 2 nm or more and 500 nm or less, 3 nm or more and 200 nm or less, or 5 nm or more and 100 nm or less, which are used for transistor semiconductors.

図1に示す装置は、パルスレーザ発振器1301と、マイクロ波発振器1302と、方向性結合器1303と、導波管1305と、ミキサー1306と、信号処理装置1307と、試料ステージ1311と、を有する。なお、図1において、導波管1305は、コーナー部が曲率を有する形状を示しているが、これに限定されるものではない。試料ステージ1311上には、試料1320を配置できる。試料1320は、例えば、基板1320bと、基板1320b上の酸化物半導体1320aと、を有する。

The apparatus shown in FIG. 1 includes a

試料ステージ1311の上面には、導電体が配置されている。導電体としては、アルミニウム、チタン、クロム、マンガン、鉄、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタル若しくはタングステンを一種以上、又は該金属元素の一種以上及びホウ素、窒素、酸素、フッ素、シリコン若しくはリンの一種以上含む導電体を、単層で、または積層で用いればよい。例えば、ステンレス鋼などの合金や化合物であってもよく、アルミニウムを含む導電体、銅及びチタンを含む導電体、銅及びマンガンを含む導電体、インジウム、スズ及び酸素を含む導電体、チタン及び窒素を含む導電体などを用いてもよい。

A conductor is arranged on the upper surface of the

なお、試料1320と試料ステージ1311との間にスペーサ1310を配置しても構わない。スペーサ1310は、マグネシウム、アルミニウム、シリコン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウム又はタンタルの一種以上及びアルゴン、ホウ素、炭素、窒素、酸素、フッ素、リン又は塩素の一種以上を含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

The

スペーサ1310は、例えば、酸化物半導体1320aの上面と、試料ステージ1311の上面と、の距離が基板1320b及びスペーサ1310におけるマイクロ波の波長の1/4程度となるように厚さを選択すればよい。なお、スペーサ1310を配置することにより、試料1320を上下逆さまに配置した場合でも評価が可能となる場合がある。試料1320を上下逆さまに配置することで、例えば、基板1320bと酸化物半導体1320aとの界面の影響を多く含んだ情報が得られる場合がある。

The thickness of the

以下に、酸化物半導体1320aのμ―PCD測定による評価方法を示す。

The evaluation method of the

まず、マイクロ波発振器1302より、マイクロ波を放射する。放射されたマイクロ波を特に進行波(入射波ともいう。)と呼ぶ。方向性結合器1303を介して進行波が、導波管1305と位相器1315とに分かれる。導波管1305を通った進行波は、試料1320に入射する。このとき、試料1320の酸化物半導体1320aで反射したマイクロ波(特に反射波と呼ぶ。)が、再び導波管1305を通る。反射波は、ミキサー1306にて、位相器1315を介して分かれた進行波と混合される。混合された信号は、信号処理装置1307において検出される。

First, microwaves are radiated from the

このとき、信号処理装置1307で検出される信号の強度は、酸化物半導体1320aにおけるマイクロ波の反射強度によって変化する。例えば、酸化物半導体1320aのキャリア密度が高いほど、酸化物半導体1320aの導電率が高くなる。導電率が高くなると、マイクロ波の反射強度は高くなり、それに伴って信号処理装置1307で検出される信号の強度も強くなる。

At this time, the signal intensity detected by the

また、酸化物半導体1320aは、励起光を吸収することで正孔及び電子を生成する。即ち、励起光を酸化物半導体1320aに照射することで、酸化物半導体1320aのキャリア密度が高くなり、それに伴いマイクロ波の反射強度が高くなる。なお、励起光は、ミラー1313及びレンズ1314を介して酸化物半導体1320aに照射させればよい。

Further, the

ある程度の時間、酸化物半導体1320aに励起光を当て続けると、マイクロ波の反射強度は、励起光によるキャリアの生成と、再結合などによるキャリアの消失と、のバランスによって一定値をとる。この値が、マイクロ波の反射強度の最も高い値となることから、マイクロ波の反射強度のピーク値と呼ぶことができる。

When the

なお、励起光としては、例えば、パルスレーザ発振器1301から放射されたレーザ光を用いることができる。レーザ光は、酸化物半導体1320aのバンドギャップよりも十分に高いエネルギーの波長を用いると好ましい。また、光学系のコストの上昇を抑えるためには、レーザ光の波長は200nm以上が好ましい。ただし、波長が200nm未満のレーザ光を用いても構わない。なお、光の進入長は、光の強度が1/eに減衰する深さであり、数式1で表すことができる。

As the excitation light, for example, a laser beam emitted from the

ここで、dは光の進入長、λは光の波長、kは減衰係数を示す。 Here, d is the penetration length of light, λ is the wavelength of light, and k is the attenuation coefficient.

例えば、酸化物半導体1320aのバンドギャップよりも十分に高いエネルギーの波長の励起光を用いない場合、検出感度を高めるために励起光の出力をある程度高くしなくてはならない。そのため、酸化物半導体1320aを変質させてしまう場合がある。酸化物半導体1320aのバンドギャップよりも十分に高いエネルギーの波長の励起光を用いることで、励起光の出力を小さくした場合でも酸化物半導体1320aのキャリア密度を十分に高くできる。したがって、上述したような、酸化物半導体1320aの変質を抑制できる。

For example, when excitation light having a wavelength having a wavelength sufficiently higher than the band gap of the

また、酸化物半導体1320aへの進入長の浅い励起光を用いることで、基板1320bなど下地の情報が測定結果に反映されることを抑制できる。また、干渉効果により、酸化物半導体1320aの厚さに応じて測定結果にムラが生じることを抑制できる。

Further, by using the excitation light having a shallow penetration length into the

基板1320bとして、μ―PCD測定での励起光のエネルギーよりもバンドギャップが小さい基板を用いる場合、励起光照射によって基板にキャリアが多数発生する。このような試料のμ―PCD測定を行うと、基板1320b由来の信号が大きくなり、酸化物半導体1320a由来の信号を打ち消す場合がある。そのため、励起光のエネルギーよりもバンドギャップが大きい基板、例えば、ガラスや石英を用いることが望ましい。

When a substrate having a bandgap smaller than the energy of the excitation light in the μ-PCD measurement is used as the

酸化物半導体1320aの上または下に、μ―PCD測定での励起光のエネルギーよりもバンドギャップが大きい膜を有する場合においても、酸化物半導体1320a由来の信号を検出できる。例えばシリコン酸化膜は、励起光よりバンドギャップが大きく、キャリアが発生しづらいことから、μ―PCD測定においてシリコン酸化膜由来の信号は小さくなり、酸化物半導体1320a由来の信号を検出できる。なお、酸化物半導体1320aの上または下に設ける、μ―PCD測定での励起光のエネルギーよりもバンドギャップが大きい膜は、積層構造としてもよい。

Even when a film having a bandgap larger than the energy of the excitation light in the μ-PCD measurement is provided above or below the

酸化物半導体1320aへの励起光の照射を止めると、キャリアの生成が止まり、酸化物半導体1320aのキャリア密度は減衰していく。酸化物半導体において、励起光の照射により生成したキャリアは単純に指数関数的に減衰するのではなく、減衰の途中から減衰が緩やかになる場合がある。つまり、キャリアの減衰は、速やかに減衰する成分と緩やかに減衰する成分の二つから構成される。速やかに減衰する成分はおおよそ指数関数的であり、緩やかに減衰する成分は非指数関数型の傾向となる場合がある。キャリア密度の減衰は、速やかな減衰成分に対する指数関数型モデルと、緩やかな減衰成分に対する拡張指数関数型モデルを組み合わせた数式2で表すことができる。

When the irradiation of the

ここで、tは励起光の照射を停止してからの時間、n(t)は時間tにおけるキャリア密度、n0は励起光照射下でのキャリア密度、τ1は速やかに減衰する成分の時定数、τ2は緩やかに減衰する成分の時定数、βは拡張指数係数を示す。 Here, t is the time after the irradiation of the excitation light is stopped, n (t) is the carrier density at the time t, n 0 is the carrier density under the irradiation of the excitation light, and τ1 is the time constant of the component that rapidly attenuates. , Τ2 is the time constant of the slowly decaying component, and β is the extended exponential coefficient.

本明細書では、速やかに減衰する成分の時定数をライフタイムτ1、緩やかに減衰する成分の時定数をライフタイムτ2と呼ぶ。 In the present specification, the time constant of the rapidly decaying component is referred to as lifetime τ1, and the time constant of the slowly decaying component is referred to as lifetime τ2.

酸化物半導体1320aに照射されたマイクロ波は、酸化物半導体1320aのキャリア密度で決まる導電率に基づいたマイクロ波の反射強度で反射される。つまり、酸化物半導体1320aのキャリア密度とマイクロ波の反射強度が対応することから、マイクロ波の反射強度の減衰を、数式3で表すことができる。なお、μ―PCD測定によるライフタイムτ1及びライフタイムτ2の算出方法は、S. Yasuno, et al.: Journal of Applied Physics 2012 vol.112, 053715の記載を参照できる。

The microwave irradiated on the

ここで、tは励起光の照射を停止してからの時間、R(t)は時間tにおけるマイクロ波の反射強度、R0は励起光照射下でのマイクロ波の反射強度、τ1は速やかに減衰する成分のライフタイム、τ2は緩やかに減衰する成分のライフタイム、βは拡張指数関数を示す。 Here, t is the time after the irradiation of the excitation light is stopped, R (t) is the reflection intensity of the microwave at time t, R 0 is the reflection intensity of the microwave under the irradiation of the excitation light, and τ1 is promptly. The lifetime of the decaying component, τ2 is the lifetime of the slowly decaying component, and β is the extended exponential function.

μ―PCD測定で得られる減衰曲線の例を図3(A)に示す。図3(A)は、横軸に励起光の照射を停止してからの時間[nsec]をとり、左の縦軸にマイクロ波の反射強度[mV]をとる。プロットは実測値を示し、実線は数式3を用いたフィッティングから得られた速やかに減衰する成分、破線はフィッティングから得られた緩やかに減衰する成分を示す。このように、得られたマイクロ波の反射強度の減衰曲線から、キャリアのライフタイムτ1及びτ2を算出できる。

An example of the attenuation curve obtained by μ-PCD measurement is shown in FIG. 3 (A). In FIG. 3A, the horizontal axis represents the time [nsec] after the irradiation of the excitation light is stopped, and the left vertical axis represents the reflection intensity [mV] of the microwave. The plot shows the measured values, the solid line shows the rapidly decaying component obtained from the

マイクロ波の反射強度が非常に低い例を図3(B)に示す。図3(B)は、横軸に励起光の照射を停止してからの時間[nsec]をとり、左の縦軸にマイクロ波の反射強度[mV]をとる。このように、マイクロ波の反射強度が低い試料においては、減衰曲線のノイズの影響が大きくなり、ライフタイムτ1及びτ2を算出できない場合がある。 An example in which the reflection intensity of microwaves is very low is shown in FIG. 3 (B). In FIG. 3B, the horizontal axis represents the time [nsec] after the irradiation of the excitation light is stopped, and the left vertical axis represents the reflection intensity [mV] of the microwave. As described above, in a sample having a low microwave reflection intensity, the influence of noise on the attenuation curve becomes large, and the lifetimes τ1 and τ2 may not be calculated.

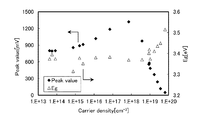

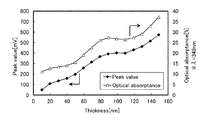

酸化物半導体の伝導帯が縮退していない範囲においては、酸化物半導体のキャリア密度が高くなるほど、μ―PCD測定で得られる反射強度のピーク値が高くなり、また、ライフタイムが長くなる傾向となる。キャリア密度とピーク値、ライフタイムの相関関係を事前に取得しておくことで、任意の酸化物半導体のμ―PCD測定を行うことにより、該酸化物半導体のキャリア密度を推測できる。 In the range where the conduction band of the oxide semiconductor is not degenerated, the higher the carrier density of the oxide semiconductor, the higher the peak value of the reflection intensity obtained by μ-PCD measurement, and the longer the lifetime tends to be. Become. By acquiring the correlation between the carrier density, the peak value, and the lifetime in advance, the carrier density of the oxide semiconductor can be estimated by performing the μ-PCD measurement of any oxide semiconductor.

酸化物半導体をトランジスタに用いる場合、良好なトランジスタの電気特性を得るには、酸化物半導体のキャリア密度の制御が重要となる。μ―PCD測定を行うことにより、酸化物半導体のキャリア密度を推測できることから、効率良く、トランジスタの電気特性の向上が可能となる。具体的には、しきい値電圧のマイナスシフトの抑制、オン電流の向上、または電界効果移動度の向上が可能となる。 When an oxide semiconductor is used for a transistor, it is important to control the carrier density of the oxide semiconductor in order to obtain good electrical characteristics of the transistor. Since the carrier density of the oxide semiconductor can be estimated by performing the μ-PCD measurement, it is possible to efficiently improve the electrical characteristics of the transistor. Specifically, it is possible to suppress the negative shift of the threshold voltage, improve the on-current, or improve the field effect mobility.

さらにキャリア密度が高くなり、伝導帯が縮退する範囲になると、キャリア密度が高くなるほど、μ―PCD測定で得られるピーク値は低くなる。また、酸化物半導体の伝導帯が縮退する範囲においては、キャリア密度が高くなるほど、μ―PCD測定で得られるライフタイムが短くなる。さらにキャリア密度が高くなると、ピーク値が低くなることから、図3(B)に示したように、減衰曲線のノイズの影響が大きくなり、ライフタイムを算出できなくなる。ピーク値と合わせて、ライフタイムも用いることにより、酸化物半導体のキャリア密度をより精度良く推測できる。 Further, when the carrier density becomes higher and the conduction band degenerates, the higher the carrier density, the lower the peak value obtained by the μ-PCD measurement. Further, in the range where the conduction band of the oxide semiconductor is degenerated, the higher the carrier density, the shorter the lifetime obtained by the μ-PCD measurement. As the carrier density increases, the peak value decreases, and as shown in FIG. 3B, the influence of noise on the attenuation curve increases, making it impossible to calculate the lifetime. By using the lifetime together with the peak value, the carrier density of the oxide semiconductor can be estimated more accurately.

縮退領域において、キャリア密度が高くなるほどピーク値が低くなる原因として、次の3つが考えられる。一つ目は、キャリア―キャリア散乱による移動度の低下である。二つ目は、キャリア―キャリア散乱による、励起光照射下でのキャリア密度の減少である。三つ目は、バースタイン・モスシフト(Burstein―Moss shift)効果による、励起光照射下でのキャリア密度の減少である。 In the degenerate region, there are three possible causes for the peak value to decrease as the carrier density increases. The first is a decrease in mobility due to carrier-carrier scattering. The second is the decrease in carrier density under excitation light irradiation due to carrier-carrier scattering. The third is a decrease in carrier density under excitation light irradiation due to the Burstein-Mossshift effect.

まず、一つ目及び二つ目の理由について説明する。励起光照射により過剰キャリアが生成し、酸化物半導体の導電率が増加する。励起光照射による導電率の変化量を、数式4で表すことができる。

First, the first and second reasons will be described. Excess carriers are generated by irradiation with excitation light, and the conductivity of the oxide semiconductor increases. The amount of change in conductivity due to excitation light irradiation can be expressed by

ここで、Δσは励起光照射による導電率の変化量、qは電気素量、μnは電子の移動度、ndarkは励起光照射前のキャリア密度、nphotoは励起光照射下でのキャリア密度を示す。 Here, Δσ is the amount of change in conductivity due to excitation light irradiation, q is the elementary charge, μ n is the electron mobility, n dark is the carrier density before excitation light irradiation, and n photo is the carrier under excitation light irradiation. Indicates density.

キャリア密度が高くなると、キャリア―キャリア散乱により移動度μnが低下することから、励起光照射による導電率の変化量が小さくなることが分かる。また、キャリア密度が高くなると、キャリア―キャリア散乱によりライフタイムが短くなり、励起光照射下でのキャリア密度nphotoが減少することから、励起光照射による導電率の変化量が小さくなることが分かる。よって、μ―PCD測定のピーク値が小さくなると考えられる。 As the carrier density increases, the mobility μ n decreases due to carrier-carrier scattering, so it can be seen that the amount of change in conductivity due to excitation light irradiation decreases. Further, when the carrier density is high, the lifetime is shortened due to carrier-carrier scattering, and the carrier density nphoto under excitation light irradiation is reduced, so that the amount of change in conductivity due to excitation light irradiation is small. .. Therefore, it is considered that the peak value of the μ-PCD measurement becomes small.

次に、三つ目の理由について説明する。キャリア密度が高くなり、伝導帯が縮退すると、光学バンドギャップが広がることが知られており、これはバースタイン・モスシフト(Burstein―Moss shift)効果と呼ばれる。光学バンドギャップが広がることにより、励起光照射で励起するキャリア密度が減少し、μ―PCD測定のピーク値が小さくなると考えられる。 Next, the third reason will be explained. It is known that the optical bandgap widens as the carrier density increases and the conduction band degenerates, which is called the Bernstein-Mossshift effect. It is considered that the widening of the optical band gap reduces the carrier density excited by the excitation light irradiation and reduces the peak value of the μ-PCD measurement.

酸化物半導体のキャリア密度測定方法の一つとして、ホール(Hall)効果測定が挙げられる。しかし、ホール(Hall)効果測定は、測定可能なサンプルサイズが小さい為、基板サイズが大きいと、基板を分断する必要がある。また、サンプルに針を接触させて測定する。ホール効果測定は破壊、接触測定になることから、例えば酸化物半導体を用いたトランジスタ作製工程において、ホール効果測定を工程管理に用いるのは好ましくない。 One of the methods for measuring the carrier density of an oxide semiconductor is the Hall effect measurement. However, in the Hall effect measurement, since the measurable sample size is small, if the substrate size is large, it is necessary to divide the substrate. In addition, the needle is brought into contact with the sample for measurement. Since the Hall effect measurement is fracture and contact measurement, it is not preferable to use the Hall effect measurement for process control in, for example, a transistor manufacturing process using an oxide semiconductor.

これに対して、μ―PCD測定は酸化物半導体を形成した後であれば、トランジスタ作製の工程途中に非接触、非破壊、短時間で酸化物半導体のキャリア密度を評価できる。 On the other hand, in the μ-PCD measurement, the carrier density of the oxide semiconductor can be evaluated in a non-contact, non-destructive, and short time during the transistor manufacturing process after the oxide semiconductor is formed.

また、トランジスタを作製する場合、チャネル、ソース、ドレイン、ゲートなどを形成するまで電気特性の測定を行うことができない。しかし、μ―PCD測定は工程途中に非接触、非破壊、短時間で酸化物半導体のキャリア密度を評価し、当該キャリア密度からトランジスタの電気特性を推測することができる。このように、工程途中に適宜μ―PCD測定を行うことにより、工程不良を容易に発見でき、μ−PCD測定結果を効率良く工程管理へフィードバックすることができる。 Further, when a transistor is manufactured, the electrical characteristics cannot be measured until a channel, a source, a drain, a gate, or the like is formed. However, in the μ-PCD measurement, the carrier density of the oxide semiconductor can be evaluated in a non-contact, non-destructive, and short time during the process, and the electrical characteristics of the transistor can be estimated from the carrier density. In this way, by appropriately performing μ-PCD measurement during the process, process defects can be easily found, and the μ-PCD measurement result can be efficiently fed back to process management.

よって、トランジスタ作製工程途中にμ―PCD測定を行うことにより、時間遅延なく異常工程を確認でき、即座に異常に対応できる。また、異常のあった試料をトランジスタ製造工程から外すことにより、後の工程を流す無駄を排除できる。その為、効率良く、トランジスタを歩留まり高く作製できる。または、トランジスタを生産性高く作製できる。または、効率良く、該トランジスタを有する半導体装置を生産性高く作製できる。 Therefore, by performing the μ-PCD measurement in the middle of the transistor manufacturing process, the abnormal process can be confirmed without a time delay, and the abnormal can be dealt with immediately. Further, by removing the abnormal sample from the transistor manufacturing process, it is possible to eliminate the waste of flowing the subsequent process. Therefore, the transistor can be efficiently manufactured with a high yield. Alternatively, the transistor can be manufactured with high productivity. Alternatively, a semiconductor device having the transistor can be efficiently manufactured with high productivity.

また、試料ステージ1311をX方向及びY方向に動かすことで、酸化物半導体1320aの面内において、複数個所の評価を行うことができる。μ―PCD測定は非接触、非破壊、短時間で試料面内の複数個所の測定が可能である。したがって、トランジスタ作製工程途中で試料面内の複数個所でμ―PCD測定を行うことにより、工程途中で酸化物半導体のキャリア密度の面内分布を評価し、当該キャリア密度からトランジスタの電気特性の面内分布を推測することができる。したがって、試料面内分布に異常が発生した場合でも、速やか工程管理へフィードバックすることができる。

Further, by moving the

なお、酸化物半導体の膜厚やバンドギャップにより、酸化物半導体のμ―PCD測定での励起光の吸収率は異なる。励起光の吸収率が異なると、酸化物半導体に発生するキャリア密度が異なる為、酸化物半導体の膜厚やバンドギャップにより、マイクロ波の反射強度のピーク値が異なる。トランジスタ作製に用いる酸化物半導体の膜厚やバンドギャップに合わせたサンプルを作製し、事前にホール(Hall)効果測定などによるキャリア密度と、μ―PCD測定によるピーク値及びライフタイムとの相関を取得しておくことで、より精度良く、キャリア密度を推測することができる。 The absorption rate of excitation light in the μ-PCD measurement of the oxide semiconductor differs depending on the film thickness and band gap of the oxide semiconductor. If the absorption rate of the excitation light is different, the carrier density generated in the oxide semiconductor is different, so that the peak value of the microwave reflection intensity is different depending on the film thickness and band gap of the oxide semiconductor. Prepare a sample that matches the film thickness and band gap of the oxide semiconductor used for transistor fabrication, and obtain the correlation between the carrier density by Hall effect measurement and the peak value and lifetime by μ-PCD measurement in advance. By doing so, the carrier density can be estimated more accurately.

また、図2のように、導波管1305a及び導波管1305bの二つの導波管と、マジックT1304と、有する装置を用いても構わない。なお、導波管1305aと導波管1305bとが、対称性を有すると好ましい。または、導波管1305aと導波管1305bとのマイクロ波の経路長が同じであればよい。なお、図2において、導波管1305a及び導波管1305bは、コーナー部が曲率を有する形状を示しているが、これに限定されるものではない。

Further, as shown in FIG. 2, a device having two waveguides, a

図2の場合も、まず、マイクロ波発振器1302より、マイクロ波を放射する。方向性結合器1303を介して進行波が、マジックT1304と位相器1315とに分かれる。マジックT1304において、進行波は、導波管1305a及び導波管1305bに分かれる。導波管1305aを通った進行波は、励起光とともに試料1320に入射する。また、導波管1305bを通った進行波は、そのまま試料1320に入射する。このとき、試料1320の酸化物半導体1320aで反射したマイクロ波が、再び導波管1305a及び導波管1305bを通り、マジックT1304に戻る。導波管1305aと導波管1305bと、を通った反射波は、マジックT1304において再び合流する、そして、マジックT1304はそれらの差信号を出力する。そして、ミキサー1306にて、位相器1315を介して分かれた進行波と混合される。混合された信号は、信号処理装置1307において検出される。

Also in the case of FIG. 2, first, microwaves are radiated from the

このとき、導波管1305bを通った反射波は、マイクロ波発振器1302に起因したノイズ、及び機械的振動による外乱などを、導波管1305aを通った反射波と同じだけ含む。したがって、その差信号をとることで、ノイズなどの影響を低減させられる。そのため、図2に示す装置は、励起光によるマイクロ波の反射強度の変化を、さらに感度よく検出できる。

At this time, the reflected wave passing through the

(実施の形態2)

本実施の形態においては、本発明の一態様に用いることのできる、酸化物半導体の組成、及び酸化物半導体の構造等について、図4及び図5を参照して説明する。

(Embodiment 2)

In the present embodiment, the composition of the oxide semiconductor, the structure of the oxide semiconductor, and the like that can be used in one aspect of the present invention will be described with reference to FIGS. 4 and 5.

[酸化物半導体]

以下に、本発明に係る酸化物半導体について説明する。

[Oxide semiconductor]

The oxide semiconductor according to the present invention will be described below.

酸化物半導体は、少なくともインジウムまたは亜鉛を含むことが好ましい。特にインジウム及び亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウムまたはスズなどが含まれていることが好ましい。また、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。 The oxide semiconductor preferably contains at least indium or zinc. In particular, it preferably contains indium and zinc. In addition to them, aluminum, gallium, yttrium, tin and the like are preferably contained. It may also contain one or more selected from boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium and the like.

ここでは、酸化物半導体が、インジウム、元素M及び亜鉛を有するInMZnOである場合を考える。なお、元素Mは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。 Here, consider the case where the oxide semiconductor is InMZnO having indium, element M, and zinc. The element M is aluminum, gallium, yttrium, tin, or the like. Examples of elements applicable to the other element M include boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, and magnesium. However, as the element M, a plurality of the above-mentioned elements may be combined in some cases.

<構造>

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、CAAC−OS(c−axis aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc−OS(nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体(a−like OS:amorphous−like oxide semiconductor)及び非晶質酸化物半導体などがある。

<Structure>

Oxide semiconductors are divided into single crystal oxide semiconductors and other non-single crystal oxide semiconductors. Examples of the non-single crystal oxide semiconductor include CAAC-OS (c-axis aligned semiconductor semiconductor), polycrystalline oxide semiconductor, nc-OS (nanocrystalline oxide semiconductor), and pseudo-amorphous oxide semiconductor (a-lique). OS: atomous-like oxide semiconductor) and amorphous oxide semiconductors.

CAAC−OSは、c軸配向性を有し、かつa−b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域と、の間で格子配列の向きが変化している箇所を指す。 CAAC-OS has a c-axis orientation and has a distorted crystal structure in which a plurality of nanocrystals are connected in the ab plane direction. The strain refers to a region where the orientation of the lattice arrangement changes between a region in which the lattice arrangement is aligned and a region in which another lattice arrangement is aligned in the region where a plurality of nanocrystals are connected.

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、及び七角形などの格子配列を有する場合がある。なお、CAAC−OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンダリーともいう)を確認することはできない。即ち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC−OSが、a−b面方向において原子配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためと考えられる。 Although nanocrystals are basically hexagonal, they are not limited to regular hexagons and may have non-regular hexagons. Further, in the strain, it may have a lattice arrangement such as a pentagon and a heptagon. In CAAC-OS, a clear grain boundary (also referred to as grain boundary) cannot be confirmed even in the vicinity of strain. That is, it can be seen that the formation of grain boundaries is suppressed by the distortion of the lattice arrangement. This is because CAAC-OS can tolerate distortion due to the fact that the atomic arrangement is not dense in the ab plane direction and the bond distance between atoms changes due to the substitution of metal elements. Conceivable.

また、CAAC−OSは、インジウム、及び酸素を有する層(以下、In層)と、元素M、亜鉛、及び酸素を有する層(以下、(M,Zn)層)とが積層した、層状の結晶構造(層状構造ともいう)を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、(M,Zn)層の元素Mがインジウムと置換した場合、(In,M,Zn)層と表すこともできる。また、In層のインジウムが元素Mと置換した場合、(In,M)層と表すこともできる。 Further, CAAC-OS is a layered crystal in which a layer having indium and oxygen (hereinafter, In layer) and a layer having elements M, zinc, and oxygen (hereinafter, (M, Zn) layer) are laminated. It tends to have a structure (also called a layered structure). Indium and the element M can be replaced with each other, and when the element M of the (M, Zn) layer is replaced with indium, it can be expressed as the (In, M, Zn) layer. Further, when the indium of the In layer is replaced with the element M, it can be expressed as the (In, M) layer.

nc−OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc−OSは、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc−OSは、分析方法によっては、a−like OSや非晶質酸化物半導体と区別が付かない場合がある。 The nc-OS has periodicity in the atomic arrangement in a minute region (for example, a region of 1 nm or more and 10 nm or less, particularly a region of 1 nm or more and 3 nm or less). In addition, nc-OS does not show regularity in crystal orientation between different nanocrystals. Therefore, no orientation is observed in the entire film. Therefore, the nc-OS may be indistinguishable from the a-like OS and the amorphous oxide semiconductor depending on the analysis method.

a−like OSは、nc−OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。a−like OSは、鬆または低密度領域を有する。即ち、a−like OSは、nc−OS及びCAAC−OSと比べて、結晶性が低い。 The a-like OS is an oxide semiconductor having a structure between nc-OS and an amorphous oxide semiconductor. The a-like OS has a void or low density region. That is, a-like OS has lower crystallinity than nc-OS and CAAC-OS.

酸化物半導体は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a−like OS、nc−OS、CAAC−OSのうち、二種以上を有していてもよい。 Oxide semiconductors have various structures, and each has different characteristics. The oxide semiconductor of one aspect of the present invention may have two or more of amorphous oxide semiconductor, polycrystalline oxide semiconductor, a-like OS, nc-OS, and CAAC-OS.

<原子数比>

次に、図4(A)、図4(B)、及び図4(C)を用いて、本発明に係る酸化物半導体が有するインジウム、元素M及び亜鉛の原子数比の好ましい範囲について説明する。なお、図4(A)、図4(B)、及び図4(C)には、酸素の原子数比については記載しない。また、酸化物半導体が有するインジウム、元素M、及び亜鉛の原子数比のそれぞれの項を[In]、[M]、及び[Zn]とする。

<Atomic number ratio>

Next, with reference to FIGS. 4 (A), 4 (B), and 4 (C), a preferable range of atomic number ratios of indium, element M, and zinc contained in the oxide semiconductor according to the present invention will be described. .. Note that FIG. 4 (A), FIG. 4 (B), and FIG. 4 (C) do not describe the atomic number ratio of oxygen. Further, the respective terms of the atomic number ratios of indium, element M, and zinc contained in the oxide semiconductor are [In], [M], and [Zn].

図4(A)、図4(B)、及び図4(C)において、破線は、[In]:[M]:[Zn]=(1+α):(1−α):1の原子数比(−1≦α≦1)となるライン、[In]:[M]:[Zn]=(1+α):(1−α):2の原子数比となるライン、[In]:[M]:[Zn]=(1+α):(1−α):3の原子数比となるライン、[In]:[M]:[Zn]=(1+α):(1−α):4の原子数比となるライン、及び[In]:[M]:[Zn]=(1+α):(1−α):5の原子数比となるラインを表す。 In FIGS. 4 (A), 4 (B), and 4 (C), the broken line indicates the atomic number ratio of [In]: [M]: [Zn] = (1 + α) :( 1-α): 1. Line where (-1 ≤ α ≤ 1), [In]: [M]: [Zn] = (1 + α): (1-α): Line where the atomic number ratio is 2, [In]: [M] : [Zn] = (1 + α): (1-α): A line having an atomic number ratio of 3, [In]: [M]: [Zn] = (1 + α): (1-α): 4 atomic numbers It represents a line having a ratio and a line having an atomic number ratio of [In]: [M]: [Zn] = (1 + α) :( 1-α): 5.

また、一点鎖線は、[In]:[M]:[Zn]=5:1:βの原子数比(β≧0)となるライン、[In]:[M]:[Zn]=2:1:βの原子数比となるライン、[In]:[M]:[Zn]=1:1:βの原子数比となるライン、[In]:[M]:[Zn]=1:2:βの原子数比となるライン、[In]:[M]:[Zn]=1:3:βの原子数比となるライン、及び[In]:[M]:[Zn]=1:4:βの原子数比となるラインを表す。 The one-point chain line is a line having an atomic number ratio of [In]: [M]: [Zn] = 5: 1: β (β ≧ 0), [In]: [M]: [Zn] = 2: Line with an atomic number ratio of 1: β, [In]: [M]: [Zn] = 1: 1: Line with an atomic number ratio of β, [In]: [M]: [Zn] = 1: 2: Atomic number ratio of β, [In]: [M]: [Zn] = 1: 3: β atomic number ratio, and [In]: [M]: [Zn] = 1 : Represents a line having an atomic number ratio of 4: β.

また、図4(A)、図4(B)、及び図4(C)に示す、[In]:[M]:[Zn]=0:2:1の原子数比、及びその近傍値の酸化物半導体は、スピネル型の結晶構造をとりやすい。 Further, the atomic number ratio of [In]: [M]: [Zn] = 0: 2: 1 and its vicinity values shown in FIGS. 4 (A), 4 (B), and 4 (C). Oxide semiconductors tend to have a spinel-type crystal structure.

また、酸化物半導体中に複数の相が共存する場合がある(二相共存、三相共存など)。例えば、原子数比が[In]:[M]:[Zn]=0:2:1の近傍値である場合、スピネル型の結晶構造と層状の結晶構造との二相が共存しやすい。また、原子数比が[In]:[M]:[Zn]=1:0:0の近傍値である場合、ビックスバイト型の結晶構造と層状の結晶構造との二相が共存しやすい。酸化物半導体中に複数の相が共存する場合、異なる結晶構造の間において、結晶粒界が形成される場合がある。 In addition, a plurality of phases may coexist in the oxide semiconductor (two-phase coexistence, three-phase coexistence, etc.). For example, when the atomic number ratio is in the vicinity of [In]: [M]: [Zn] = 0: 2: 1, two phases of a spinel-type crystal structure and a layered crystal structure tend to coexist. Further, when the atomic number ratio is in the vicinity of [In]: [M]: [Zn] = 1: 0: 0, two phases of a big bite-type crystal structure and a layered crystal structure tend to coexist. When a plurality of phases coexist in an oxide semiconductor, grain boundaries may be formed between different crystal structures.

図4(A)に示す領域Aは、酸化物半導体が有する、インジウム、元素M、及び亜鉛の原子数比の好ましい範囲の一例について示している。 The region A shown in FIG. 4A shows an example of a preferable range of atomic number ratios of indium, element M, and zinc contained in the oxide semiconductor.

酸化物半導体は、インジウムの含有率を高くすることで、酸化物半導体のキャリア移動度(電子移動度)を高くすることができる。従って、インジウムの含有率が高い酸化物半導体はインジウムの含有率が低い酸化物半導体と比較してキャリア移動度が高くなる。 By increasing the indium content of the oxide semiconductor, the carrier mobility (electron mobility) of the oxide semiconductor can be increased. Therefore, an oxide semiconductor having a high indium content has a higher carrier mobility than an oxide semiconductor having a low indium content.

一方、酸化物半導体中のインジウム及び亜鉛の含有率が低くなると、キャリア移動度が低くなる。従って、原子数比が[In]:[M]:[Zn]=0:1:0、及びその近傍値である場合(例えば図4(C)に示す領域C)は、絶縁性が高くなる。 On the other hand, when the content of indium and zinc in the oxide semiconductor is low, the carrier mobility is low. Therefore, when the atomic number ratio is [In]: [M]: [Zn] = 0: 1: 0 and its neighboring values (for example, region C shown in FIG. 4C), the insulating property is high. ..

従って、本発明の一態様の酸化物半導体は、キャリア移動度が高く、かつ、結晶粒界が少ない層状構造となりやすい、図4(A)の領域Aで示される原子数比を有することが好ましい。 Therefore, it is preferable that the oxide semiconductor of one aspect of the present invention has the atomic number ratio shown in the region A of FIG. 4A, which tends to have a layered structure having high carrier mobility and few grain boundaries. ..

特に、図4(B)に示す領域Bでは、領域Aの中でも、CAAC−OSとなりやすく、キャリア移動度も高い優れた酸化物半導体が得られる。 In particular, in the region B shown in FIG. 4B, an excellent oxide semiconductor that easily becomes CAAC-OS and has high carrier mobility can be obtained even in the region A.

CAAC−OSは結晶性の高い酸化物半導体である。一方、CAAC−OSは、明確な結晶粒界を確認することはできないため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC−OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。従って、CAAC−OSを有する酸化物半導体は、物理的性質が安定する。そのため、CAAC−OSを有する酸化物半導体は熱に強く、信頼性が高い。 CAAC-OS is a highly crystalline oxide semiconductor. On the other hand, in CAAC-OS, since a clear crystal grain boundary cannot be confirmed, it can be said that a decrease in electron mobility due to the crystal grain boundary is unlikely to occur. Further, since the crystallinity of the oxide semiconductor may be lowered due to the mixing of impurities or the generation of defects, CAAC-OS can be said to be an oxide semiconductor having few impurities and defects (oxygen deficiency, etc.). Therefore, the oxide semiconductor having CAAC-OS has stable physical properties. Therefore, the oxide semiconductor having CAAC-OS is resistant to heat and has high reliability.

なお、領域Bは、[In]:[M]:[Zn]=4:2:3から4.1、及びその近傍値を含む。近傍値には、例えば、[In]:[M]:[Zn]=5:3:4が含まれる。また、領域Bは、[In]:[M]:[Zn]=5:1:6、及びその近傍値、及び[In]:[M]:[Zn]=5:1:7、及びその近傍値を含む。 The region B includes [In]: [M]: [Zn] = 4: 2: 3 to 4.1, and values in the vicinity thereof. The neighborhood value includes, for example, [In]: [M]: [Zn] = 5: 3: 4. Further, the region B includes [In]: [M]: [Zn] = 5: 1: 6 and its neighboring values, and [In]: [M]: [Zn] = 5: 1: 7 and its vicinity. Includes neighborhood values.

なお、酸化物半導体が有する性質は、原子数比によって一義的に定まらない。同じ原子数比であっても、形成条件により、酸化物半導体の性質が異なる場合がある。例えば、酸化物半導体をスパッタリング装置にて成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される。また、成膜時の基板温度によっては、ターゲットの[Zn]よりも、膜の[Zn]が小さくなる場合がある。従って、図示する領域は、酸化物半導体が特定の特性を有する傾向がある原子数比を示す領域であり、領域A乃至領域Cの境界は厳密ではない。 The properties of oxide semiconductors are not uniquely determined by the atomic number ratio. Even if the atomic number ratio is the same, the properties of the oxide semiconductor may differ depending on the formation conditions. For example, when an oxide semiconductor is formed by a sputtering apparatus, a film having an atomic number ratio deviating from the target atomic number ratio is formed. Further, depending on the substrate temperature at the time of film formation, the [Zn] of the film may be smaller than the [Zn] of the target. Therefore, the region shown is a region showing an atomic number ratio in which the oxide semiconductor tends to have a specific characteristic, and the boundary between the region A and the region C is not strict.

[酸化物半導体を有するトランジスタ]

続いて、上記酸化物半導体をトランジスタに用いる場合について説明する。

[Transistor with oxide semiconductor]

Subsequently, a case where the oxide semiconductor is used for a transistor will be described.

なお、上記酸化物半導体をトランジスタに用いることで、結晶粒界におけるキャリア散乱等を減少させることができるため、高い電界効果移動度のトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。 By using the oxide semiconductor for the transistor, carrier scattering and the like at the grain boundaries can be reduced, so that a transistor with high field effect mobility can be realized. Moreover, a highly reliable transistor can be realized.

また、トランジスタには、キャリア密度の低い酸化物半導体を用いることが好ましい。酸化物半導体膜のキャリア密度を低くする場合においては、酸化物半導体膜中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性と言う。 Further, it is preferable to use an oxide semiconductor having a low carrier density for the transistor. When the carrier density of the oxide semiconductor film is lowered, the impurity concentration in the oxide semiconductor film may be lowered to lower the defect level density. In the present specification and the like, a low impurity concentration and a low defect level density is referred to as high-purity intrinsic or substantially high-purity intrinsic.

また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。 Further, since the oxide semiconductor film having high purity intrinsicity or substantially high purity intrinsicity has a low defect level density, the trap level density may also be low.

また、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。 In addition, the charge captured at the trap level of the oxide semiconductor takes a long time to disappear, and may behave as if it were a fixed charge. Therefore, a transistor in which a channel region is formed in an oxide semiconductor having a high trap level density may have unstable electrical characteristics.

従って、トランジスタの電気特性を安定にするためには、酸化物半導体中の不純物濃度を低減することが有効である。また、酸化物半導体中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。 Therefore, in order to stabilize the electrical characteristics of the transistor, it is effective to reduce the impurity concentration in the oxide semiconductor. Further, in order to reduce the impurity concentration in the oxide semiconductor, it is preferable to reduce the impurity concentration in the adjacent film. Impurities include hydrogen, nitrogen, alkali metals, alkaline earth metals, iron, nickel, silicon and the like.

<不純物>

ここで、酸化物半導体中における各不純物の影響について説明する。

<Impurities>

Here, the influence of each impurity in the oxide semiconductor will be described.

酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体において欠陥準位が形成される。このため、酸化物半導体におけるシリコンや炭素の濃度と、酸化物半導体との界面近傍のシリコンや炭素の濃度(二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)により得られる濃度)を、2×1018atoms/cm3以下、好ましくは2×1017atoms/cm3以下とする。

When silicon or carbon, which is one of the

また、酸化物半導体にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。従って、アルカリ金属またはアルカリ土類金属が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、SIMSにより得られる酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度を、1×1018atoms/cm3以下、好ましくは2×1016atoms/cm3以下にする。 Further, when the oxide semiconductor contains an alkali metal or an alkaline earth metal, defect levels may be formed and carriers may be generated. Therefore, a transistor using an oxide semiconductor containing an alkali metal or an alkaline earth metal tends to have a normally-on characteristic. Therefore, it is preferable to reduce the concentration of alkali metal or alkaline earth metal in the oxide semiconductor. Specifically, the concentration of the alkali metal or alkaline earth metal in the oxide semiconductor obtained by SIMS is set to 1 × 10 18 atoms / cm 3 or less, preferably 2 × 10 16 atoms / cm 3 or less.

また、酸化物半導体において、窒素が含まれると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を半導体に用いたトランジスタはノーマリーオン特性となりやすい。従って、該酸化物半導体において、窒素はできる限り低減されていることが好ましい、例えば、酸化物半導体中の窒素濃度は、SIMSにおいて、5×1019atoms/cm3未満、好ましくは5×1018atoms/cm3以下、より好ましくは1×1018atoms/cm3以下、さらに好ましくは5×1017atoms/cm3以下とする。 Further, in an oxide semiconductor, when nitrogen is contained, electrons as carriers are generated, the carrier density is increased, and the n-type is easily formed. As a result, a transistor using an oxide semiconductor containing nitrogen as a semiconductor tends to have a normally-on characteristic. Therefore, in the oxide semiconductor, nitrogen is preferably reduced as much as possible, for example, the nitrogen concentration in the oxide semiconductor is less than 5 × 10 19 atoms / cm 3 in SIMS, preferably 5 × 10 18 Atoms / cm 3 or less, more preferably 1 × 10 18 atoms / cm 3 or less, still more preferably 5 × 10 17 atoms / cm 3 or less.

また、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体において、SIMSにより得られる水素濃度を、1×1020atoms/cm3未満、好ましくは1×1019atoms/cm3未満、より好ましくは5×1018atoms/cm3未満、さらに好ましくは1×1018atoms/cm3未満とする。 Further, hydrogen contained in an oxide semiconductor reacts with oxygen bonded to a metal atom to become water, which may form an oxygen deficiency. When hydrogen enters the oxygen deficiency, electrons that are carriers may be generated. In addition, a part of hydrogen may be combined with oxygen that is bonded to a metal atom to generate an electron as a carrier. Therefore, a transistor using an oxide semiconductor containing hydrogen tends to have a normally-on characteristic. Therefore, it is preferable that hydrogen in the oxide semiconductor is reduced as much as possible. Specifically, in an oxide semiconductor, the hydrogen concentration obtained by SIMS is less than 1 × 10 20 atoms / cm 3 , preferably less than 1 × 10 19 atoms / cm 3 , and more preferably 5 × 10 18 atoms / cm. Less than 3 , more preferably less than 1 × 10 18 atoms / cm 3 .

不純物が十分に低減された酸化物半導体をトランジスタのチャネル領域に用いることで、安定した電気特性を付与することができる。 By using an oxide semiconductor in which impurities are sufficiently reduced in the channel region of the transistor, stable electrical characteristics can be imparted.

<バンド図>

続いて、該酸化物半導体を2層構造、または3層構造とした場合について述べる。酸化物半導体S1、酸化物半導体S2、及び酸化物半導体S3の積層構造、及び積層構造に接する絶縁体のバンド図と、酸化物半導体S2及び酸化物半導体S3の積層構造、及び積層構造に接する絶縁体のバンド図と、酸化物半導体S1及び酸化物半導体S2の積層構造、及び積層構造に接する絶縁体のバンド図と、について、図5を用いて説明する。

<Band diagram>

Subsequently, a case where the oxide semiconductor has a two-layer structure or a three-layer structure will be described. The laminated structure of the oxide semiconductor S1, the oxide semiconductor S2, and the oxide semiconductor S3, and the band diagram of the insulator in contact with the laminated structure, the laminated structure of the oxide semiconductor S2 and the oxide semiconductor S3, and the insulation in contact with the laminated structure. A band diagram of the body, a laminated structure of the oxide semiconductor S1 and the oxide semiconductor S2, and a band diagram of an insulator in contact with the laminated structure will be described with reference to FIG.

図5(A)は、絶縁体I1、酸化物半導体S1、酸化物半導体S2、酸化物半導体S3、及び絶縁体I2を有する積層構造の膜厚方向のバンド図の一例である。また、図5(B)は、絶縁体I1、酸化物半導体S2、酸化物半導体S3、及び絶縁体I2を有する積層構造の膜厚方向のバンド図の一例である。また、図5(C)は、絶縁体I1、酸化物半導体S1、酸化物半導体S2、及び絶縁体I2を有する積層構造の膜厚方向のバンド図の一例である。なお、バンド図は、理解を容易にするため絶縁体I1、酸化物半導体S1、酸化物半導体S2、酸化物半導体S3、及び絶縁体I2の伝導帯下端のエネルギー準位(Ec)を示す。 FIG. 5A is an example of a band diagram in the film thickness direction of a laminated structure having an insulator I1, an oxide semiconductor S1, an oxide semiconductor S2, an oxide semiconductor S3, and an insulator I2. Further, FIG. 5B is an example of a band diagram in the film thickness direction of a laminated structure having an insulator I1, an oxide semiconductor S2, an oxide semiconductor S3, and an insulator I2. Further, FIG. 5C is an example of a band diagram in the film thickness direction of a laminated structure having an insulator I1, an oxide semiconductor S1, an oxide semiconductor S2, and an insulator I2. The band diagram shows the energy level (Ec) at the lower end of the conduction band of the insulator I1, the oxide semiconductor S1, the oxide semiconductor S2, the oxide semiconductor S3, and the insulator I2 for easy understanding.

酸化物半導体S1、酸化物半導体S3は、酸化物半導体S2よりも伝導帯下端のエネルギー準位が真空準位に近く、代表的には、酸化物半導体S2の伝導帯下端のエネルギー準位と、酸化物半導体S1、酸化物半導体S3の伝導帯下端のエネルギー準位との差が、0.15eV以上、または0.5eV以上、かつ2eV以下、または1eV以下であることが好ましい。すなわち、酸化物半導体S1、酸化物半導体S3の電子親和力と、酸化物半導体S2の電子親和力との差が、0.15eV以上、または0.5eV以上、かつ2eV以下、または1eV以下であることが好ましい。 The oxide semiconductor S1 and the oxide semiconductor S3 have an energy level at the lower end of the conduction band closer to the vacuum level than the oxide semiconductor S2, and typically, the energy level at the lower end of the conduction band of the oxide semiconductor S2 and the energy level. The difference between the energy level at the lower end of the conduction band of the oxide semiconductor S1 and the oxide semiconductor S3 is preferably 0.15 eV or more, 0.5 eV or more, and 2 eV or less, or 1 eV or less. That is, the difference between the electron affinity of the oxide semiconductor S1 and the oxide semiconductor S3 and the electron affinity of the oxide semiconductor S2 is 0.15 eV or more, 0.5 eV or more, and 2 eV or less, or 1 eV or less. preferable.

図5(A)、図5(B)、及び図5(C)に示すように、酸化物半導体S1、酸化物半導体S2、酸化物半導体S3において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、連続的に変化または連続接合するともいうことができる。このようなバンド図を有するためには、酸化物半導体S1と酸化物半導体S2との界面、または酸化物半導体S2と酸化物半導体S3との界面において形成される混合層の欠陥準位密度を低くするとよい。 As shown in FIGS. 5 (A), 5 (B), and 5 (C), the energy level at the lower end of the conduction band changes gently in the oxide semiconductor S1, the oxide semiconductor S2, and the oxide semiconductor S3. do. In other words, it can also be said to be continuously changing or continuously joining. In order to have such a band diagram, the defect level density of the mixed layer formed at the interface between the oxide semiconductor S1 and the oxide semiconductor S2 or the interface between the oxide semiconductor S2 and the oxide semiconductor S3 is lowered. It is good to do.

具体的には、酸化物半導体S1と酸化物半導体S2、酸化物半導体S2と酸化物半導体S3が、酸素以外に共通の元素を有する(主成分とする)ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物半導体S2がIn−Ga−Zn酸化物半導体の場合、酸化物半導体S1、酸化物半導体S3として、In−Ga−Zn酸化物半導体、Ga−Zn酸化物半導体、酸化ガリウムなどを用いるとよい。 Specifically, the oxide semiconductor S1 and the oxide semiconductor S2, and the oxide semiconductor S2 and the oxide semiconductor S3 have a common element (main component) other than oxygen, so that the defect level density is low. Layers can be formed. For example, when the oxide semiconductor S2 is an In-Ga-Zn oxide semiconductor, In-Ga-Zn oxide semiconductor, Ga-Zn oxide semiconductor, gallium oxide or the like is used as the oxide semiconductor S1 and the oxide semiconductor S3. It is good.

このとき、キャリアの主たる経路は酸化物半導体S2となる。酸化物半導体S1と酸化物半導体S2との界面、及び酸化物半導体S2と酸化物半導体S3との界面における欠陥準位密度を低くすることができるため、界面散乱によるキャリア伝導への影響が小さく、高いオン電流が得られる。 At this time, the main path of the carrier is the oxide semiconductor S2. Since the defect level density at the interface between the oxide semiconductor S1 and the oxide semiconductor S2 and the interface between the oxide semiconductor S2 and the oxide semiconductor S3 can be lowered, the influence of interfacial scattering on carrier conduction is small. High on-current can be obtained.

トラップ準位に電子が捕獲されることで、捕獲された電子は固定電荷のように振る舞うため、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。酸化物半導体S1、酸化物半導体S3を設けることにより、トラップ準位を酸化物半導体S2より遠ざけることができる。当該構成とすることで、トランジスタのしきい値電圧がプラス方向にシフトすることを防止することができる。 When electrons are trapped at the trap level, the trapped electrons behave like a fixed charge, and the threshold voltage of the transistor shifts in the positive direction. By providing the oxide semiconductor S1 and the oxide semiconductor S3, the trap level can be kept away from the oxide semiconductor S2. With this configuration, it is possible to prevent the threshold voltage of the transistor from shifting in the positive direction.

酸化物半導体S1、及び酸化物半導体S3は、酸化物半導体S2と比較して、導電率が十分に低い材料を用いる。このとき、酸化物半導体S2、酸化物半導体S2と酸化物半導体S1との界面、及び酸化物半導体S2と酸化物半導体S3との界面が、主にチャネル領域として機能する。例えば、酸化物半導体S1、酸化物半導体S3には、図4(C)において、絶縁性が高くなる領域Cで示す原子数比の酸化物半導体を用いればよい。なお、図4(C)に示す領域Cは、[In]:[M]:[Zn]=0:1:0、及びその近傍値、[In]:[M]:[Zn]=1:3:2及びその近傍値、及び[In]:[M]:[Zn]=1:3:4、及びその近傍値である原子数比を示している。 The oxide semiconductor S1 and the oxide semiconductor S3 use a material having a sufficiently low conductivity as compared with the oxide semiconductor S2. At this time, the oxide semiconductor S2, the interface between the oxide semiconductor S2 and the oxide semiconductor S1, and the interface between the oxide semiconductor S2 and the oxide semiconductor S3 mainly function as a channel region. For example, for the oxide semiconductor S1 and the oxide semiconductor S3, the oxide semiconductor having the atomic number ratio shown in the region C where the insulating property is high may be used in FIG. 4C. The region C shown in FIG. 4C is [In]: [M]: [Zn] = 0: 1: 0 and its neighboring values, [In]: [M]: [Zn] = 1: It shows the atomic number ratio of 3: 2 and its neighboring values, [In]: [M]: [Zn] = 1: 3: 4, and its neighboring values.

特に、酸化物半導体S2に領域Aで示される原子数比の酸化物半導体を用いる場合、酸化物半導体S1及び酸化物半導体S3には、[M]/[In]が1以上、好ましくは2以上である酸化物半導体を用いることが好ましい。また、酸化物半導体S3として、十分に高い絶縁性を得ることができる[M]/([Zn]+[In])が1以上である酸化物半導体を用いることが好適である。 In particular, when an oxide semiconductor having an atomic number ratio shown in region A is used for the oxide semiconductor S2, the oxide semiconductor S1 and the oxide semiconductor S3 have [M] / [In] of 1 or more, preferably 2 or more. It is preferable to use an oxide semiconductor. Further, as the oxide semiconductor S3, it is preferable to use an oxide semiconductor having [M] / ([Zn] + [In]) of 1 or more, which can obtain sufficiently high insulating properties.

<CAC−OSの構成>

また、本発明の一態様に用いることのできる、CAC(Cloud Aligned Complementary)−OSの構成について説明する。

<CAC-OS configuration>

In addition, a configuration of CAC (Cloud Aligned Company) -OS that can be used in one aspect of the present invention will be described.

CAC−OSとは、例えば、酸化物半導体を構成する元素が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の金属元素が偏在し、該金属元素を有する領域が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。 The CAC-OS is, for example, a composition of a material in which the elements constituting the oxide semiconductor are unevenly distributed in a size of 0.5 nm or more and 10 nm or less, preferably 1 nm or more and 2 nm or less, or a size close thereto. In the following, in the oxide semiconductor, one or more metal elements are unevenly distributed, and the region having the metal elements is 0.5 nm or more and 10 nm or less, preferably 1 nm or more and 2 nm or less, or a size in the vicinity thereof. The state of being mixed with is also called a mosaic shape or a patch shape.

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウム及び亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。 The oxide semiconductor preferably contains at least indium. In particular, it preferably contains indium and zinc. Also, in addition to them, aluminum, gallium, yttrium, copper, vanadium, beryllium, boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, or magnesium, etc. One or more selected from the above may be included.

例えば、In−Ga−Zn酸化物におけるCAC−OS(CAC−OSの中でもIn−Ga−Zn酸化物を、特にCAC−IGZOと呼称してもよい。)とは、インジウム酸化物(以下、InOX1(X1は0よりも大きい実数)とする。)、またはインジウム亜鉛酸化物(以下、InX2ZnY2OZ2(X2、Y2、及びZ2は0よりも大きい実数)とする。)と、ガリウム酸化物(以下、GaOX3(X3は0よりも大きい実数)とする。)、またはガリウム亜鉛酸化物(以下、GaX4ZnY4OZ4(X4、Y4、及びZ4は0よりも大きい実数)とする。)などと、に材料が分離することでモザイク状となり、モザイク状のInOX1、またはInX2ZnY2OZ2が、膜中に均一に分布した構成(以下、クラウド状ともいう。)である。 For example, CAC-OS in In-Ga-Zn oxide (In-Ga-Zn oxide may be particularly referred to as CAC-IGZO in CAC-OS) is indium oxide (hereinafter, InO). X1 (X1 is a real number larger than 0), or indium zinc oxide (hereinafter, In X2 Zn Y2 O Z2 (X2, Y2, and Z2 are real numbers larger than 0)) and gallium. With oxide (hereinafter, GaO X3 (X3 is a real number larger than 0)) or gallium zinc oxide (hereinafter, Ga X4 Zn Y4 O Z4 (X4, Y4, and Z4 are real numbers larger than 0)) The material is separated into a mosaic-like structure, and the mosaic-like InO X1 or In X2 Zn Y2 O Z2 is uniformly distributed in the film (hereinafter, also referred to as cloud-like). be.

つまり、CAC−OSは、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の領域と比較して、Inの濃度が高いとする。

That is, CAC-OS is a composite oxide semiconductor having a structure in which a region containing GaO X3 as a main component and a region containing In X2 Zn Y2 O Z2 or InO X1 as a main component are mixed. In the present specification, for example, the atomic number ratio of In to the element M in the first region is larger than the atomic number ratio of In to the element M in the second region. It is assumed that the concentration of In is higher than that of

なお、IGZOは通称であり、In、Ga、Zn、及びOによる1つの化合物をいう場合がある。代表例として、InGaO3(ZnO)m1(m1は自然数)、またはIn(1+x0)Ga(1−x0)O3(ZnO)m0(−1≦x0≦1、m0は任意数)で表される結晶性の化合物が挙げられる。 In addition, IGZO is a common name, and may refer to one compound consisting of In, Ga, Zn, and O. As a typical example, it is represented by InGaO 3 (ZnO) m1 (m1 is a natural number) or In (1 + x0) Ga (1-x0) O 3 (ZnO) m0 (-1 ≦ x0 ≦ 1, m0 is an arbitrary number). Crystalline compounds can be mentioned.

上記結晶性の化合物は、単結晶構造、多結晶構造、または前述のCAAC構造を有する。なお、CAAC構造とは、複数のIGZOのナノ結晶がc軸配向を有し、かつa−b面においては配向せずに連結した結晶構造である。 The crystalline compound has a single crystal structure, a polycrystalline structure, or the CAAC structure described above. The CAAC structure is a crystal structure in which a plurality of IGZO nanocrystals have a c-axis orientation and are connected without being oriented on the ab plane.

一方、CAC−OSは、酸化物半導体の材料構成に関する。CAC−OSとは、In、Ga、Zn、及びOを含む材料構成において、一部にGaを主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。従って、CAC−OSにおいて、結晶構造は副次的な要素である。 On the other hand, CAC-OS relates to the material composition of oxide semiconductors. CAC-OS is a region that is partially observed as nanoparticles containing Ga as a main component and nanoparticles containing In as a main component in a material composition containing In, Ga, Zn, and O. The regions observed in a shape refer to a configuration in which the regions are randomly dispersed in a mosaic shape. Therefore, in CAC-OS, the crystal structure is a secondary element.

なお、CAC−OSは、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、Inを主成分とする膜と、Gaを主成分とする膜との2層からなる構造は、含まない。 The CAC-OS does not include a laminated structure of two or more types of films having different compositions. For example, it does not include a structure consisting of two layers, a film containing In as a main component and a film containing Ga as a main component.

なお、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とは、明確な境界が観察できない場合がある。 In some cases, a clear boundary cannot be observed between the region containing GaO X3 as the main component and the region containing In X2 Zn Y2 O Z2 or InO X1 as the main component.

なお、ガリウムの代わりに、アルミニウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれている場合、CAC−OSは、一部に該金属元素を主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。 Instead of gallium, select from aluminum, ittrium, copper, vanadium, beryllium, boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, or magnesium. When one or more of these are contained, CAC-OS has a region observed in the form of nanoparticles containing the metal element as a main component and a nano having In as a main component. The regions observed in the form of particles refer to a configuration in which the regions are randomly dispersed in a mosaic pattern.

CAC−OSは、例えば基板を加熱しない条件で、スパッタリング法により形成することができる。また、CAC−OSをスパッタリング法で形成する場合、成膜ガスとして、不活性ガス(代表的にはアルゴン)、酸素ガス、及び窒素ガスの中から選ばれたいずれか一つまたは複数を用いればよい。また、成膜時の成膜ガスの総流量に対する酸素ガスの流量比は低いほど好ましく、例えば酸素ガスの流量比を0%以上30%未満、好ましくは0%以上10%以下とすることが好ましい。 The CAC-OS can be formed by a sputtering method, for example, under the condition that the substrate is not heated. When the CAC-OS is formed by the sputtering method, one or more selected from an inert gas (typically argon), an oxygen gas, and a nitrogen gas may be used as the film forming gas. good. Further, the lower the flow rate ratio of the oxygen gas to the total flow rate of the film-forming gas at the time of film formation is preferable. For example, the flow rate ratio of the oxygen gas is preferably 0% or more and less than 30%, preferably 0% or more and 10% or less. ..

CAC−OSは、X線回折(XRD:X−ray diffraction)測定法のひとつであるOut−of−plane法によるθ/2θスキャンを用いて測定したときに、明確なピークが観察されないという特徴を有する。すなわち、X線回折から、測定領域のa−b面方向、及びc軸方向の配向は見られないことが分かる。 CAC-OS is characterized by the fact that no clear peak is observed when measured using the θ / 2θ scan by the Out-of-plane method, which is one of the X-ray diffraction (XRD) measurement methods. Have. That is, from the X-ray diffraction, it can be seen that the orientation of the measurement region in the ab plane direction and the c-axis direction is not observed.

またCAC−OSは、プローブ径が1nmの電子線(ナノビーム電子線ともいう。)を照射することで得られる電子線回折パターンにおいて、リング状に輝度の高い領域と、該リング領域に複数の輝点が観測される。従って、電子線回折パターンから、CAC−OSの結晶構造が、平面方向、及び断面方向において、配向性を有さないnc(nano−crystal)構造を有することがわかる。 Further, CAC-OS has a ring-shaped high-luminance region and a plurality of bright regions in the ring region in an electron diffraction pattern obtained by irradiating an electron beam (also referred to as a nanobeam electron beam) having a probe diameter of 1 nm. A point is observed. Therefore, from the electron diffraction pattern, it can be seen that the crystal structure of CAC-OS has an nc (nano-crystal) structure having no orientation in the planar direction and the cross-sectional direction.

また例えば、In−Ga−Zn酸化物におけるCAC−OSでは、エネルギー分散型X線分光法(EDX:Energy Dispersive X−ray spectroscopy)を用いて取得したEDXマッピングにより、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、偏在し、混合している構造を有することが確認できる。 Further, for example, in CAC-OS in In-Ga-Zn oxide, a region in which GaO X3 is a main component is obtained by EDX mapping acquired by using energy dispersive X-ray spectroscopy (EDX). And, it can be confirmed that the region in which In X2 Zn Y2 O Z2 or InO X1 is the main component is unevenly distributed and has a mixed structure.

CAC−OSは、金属元素が均一に分布したIGZO化合物とは異なる構造であり、IGZO化合物と異なる性質を有する。つまり、CAC−OSは、GaOX3などが主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。 CAC-OS has a structure different from that of the IGZO compound in which metal elements are uniformly distributed, and has properties different from those of the IGZO compound. That is, the CAC-OS is a region in which GaO X3 or the like is the main component and a region in which In X2 Zn Y2 O Z2 or InO X1 is the main component are phase-separated from each other and each element is the main component. Has a mosaic-like structure.

ここで、InX2ZnY2OZ2、またはInOX1が主成分である領域は、GaOX3などが主成分である領域と比較して、導電性が高い領域である。つまり、InX2ZnY2OZ2、またはInOX1が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。従って、InX2ZnY2OZ2、またはInOX1が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度(μ)が実現できる。 Here, the region in which In X2 Zn Y2 O Z2 or InO X1 is the main component is a region having higher conductivity than the region in which GaO X3 or the like is the main component. That is, when the carrier flows through the region where In X2 Zn Y2 O Z2 or InO X1 is the main component, the conductivity as an oxide semiconductor is exhibited. Therefore, a high field effect mobility (μ) can be realized by distributing the region containing In X2 Zn Y2 O Z2 or InO X1 as the main component in the oxide semiconductor in a cloud shape.

一方、GaOX3などが主成分である領域は、InX2ZnY2OZ2、またはInOX1が主成分である領域と比較して、絶縁性が高い領域である。つまり、GaOX3などが主成分である領域が、酸化物半導体中に分布することで、リーク電流を抑制し、良好なスイッチング動作を実現できる。 On the other hand, the region in which GaO X3 or the like is the main component is a region having higher insulating property than the region in which In X2 Zn Y2 O Z2 or InO X1 is the main component. That is, since the region containing GaO X3 or the like as the main component is distributed in the oxide semiconductor, the leakage current can be suppressed and a good switching operation can be realized.

従って、CAC−OSを半導体素子に用いた場合、GaOX3などに起因する絶縁性と、InX2ZnY2OZ2、またはInOX1に起因する導電性とが、相補的に作用することにより、高いオン電流(Ion)、及び高い電界効果移動度(μ)を実現することができる。 Therefore, when CAC-OS is used for a semiconductor element, the insulation property caused by GaO X3 and the like and the conductivity caused by In X2 Zn Y2 O Z2 or InO X1 act complementarily to be high. On-current (I on ) and high field-effect mobility (μ) can be achieved.

また、CAC−OSを用いた半導体素子は、信頼性が高い。従って、CAC−OSは、ディスプレイをはじめとするさまざまな半導体装置に最適である。 Further, the semiconductor element using CAC-OS has high reliability. Therefore, CAC-OS is most suitable for various semiconductor devices such as displays.

本明細書等において、金属酸化物(metal oxide)とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう)などに分類される。例えば、トランジスタに金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、金属酸化物が増幅作用、整流作用、及びスイッチング作用の少なくとも1つを有する場合、当該金属酸化物を、金属酸化物半導体(metal oxide semiconductor)、略してOSと呼ぶことができる。また、OS FETと記載する場合においては、金属酸化物または酸化物半導体を有するトランジスタと換言することができる。 In the present specification and the like, a metal oxide is a metal oxide in a broad expression. Metal oxides are classified into oxide insulators, oxide conductors (including transparent oxide conductors), oxide semiconductors (also referred to as Oxide Semiconductor or simply OS) and the like. For example, when a metal oxide is used for a transistor, the metal oxide may be referred to as an oxide semiconductor. That is, when the metal oxide has at least one of an amplification action, a rectifying action, and a switching action, the metal oxide can be referred to as a metal oxide semiconductor, or OS for short. Further, when the term "OS FET" is used, it can be rephrased as a transistor having a metal oxide or an oxide semiconductor.