JP6225554B2 - 演算処理装置及び演算処理装置の制御方法 - Google Patents

演算処理装置及び演算処理装置の制御方法 Download PDFInfo

- Publication number

- JP6225554B2 JP6225554B2 JP2013168694A JP2013168694A JP6225554B2 JP 6225554 B2 JP6225554 B2 JP 6225554B2 JP 2013168694 A JP2013168694 A JP 2013168694A JP 2013168694 A JP2013168694 A JP 2013168694A JP 6225554 B2 JP6225554 B2 JP 6225554B2

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- cycle

- staging

- staging latches

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/3001—Arithmetic instructions

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline or look ahead using instruction pipelines

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Advance Control (AREA)

Description

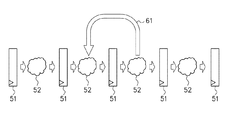

21 命令フェッチ部

22 分岐予測回路

23 一次命令キャッシュメモリ

24 命令バッファ

25 命令デコーダ

26 命令発行制御部

27 演算器制御回路

28 演算器

29 一次オペランドキャッシュメモリ

30 分岐制御部

31 レジスタ

32 命令完了制御部

33 分岐履歴更新部

34 二次キャッシュメモリ

35 メモリコントローラ

36 取出し可能命令検出部

37 ポート調停部

38 発行抑止信号設定部

39 エントリ本体

Claims (8)

- 複数のステージングラッチを有し、前記複数のステージングラッチのうち、最終段のステージングラッチを含む第1の複数のステージングラッチ間におけるデータの遷移に単一のクロックのみを必要とするパイプライン動作と、前記複数のステージングラッチのうち、前記第1の複数のステージングラッチよりも前段側に位置する第2の複数のステージングラッチ間におけるデータの遷移に複数のクロックを必要とするマルチサイクル動作とにより第1の命令を実行する第1の命令実行部と、

第2の命令を実行する第2の命令実行部と、

前記第1の命令と前記第2の命令とを入力し、前記第1の命令の実行と前記第2の命令の実行とが一部重複するように、前記第1の命令を前記第1の命令実行部に発行するとともに、前記第2の命令を前記第2の命令実行部に発行する命令制御部とを有し、

前記命令制御部は、前記第1の命令実行部が前記第1の命令の実行中に、前記第1の命令の不定の終了サイクルを確定し、前記確定した終了サイクルに応じて、前記第2の命令の前記第2の命令実行部への発行の抑止を解除することを特徴とする演算処理装置。 - 前記第2の命令実行部は、

複数の第2のステージングラッチを有し、前記複数の第2のステージングラッチのうち、最初段のステージングラッチを含む第3の複数のステージングラッチ間におけるデータの遷移に単一のクロックのみを必要とするパイプライン動作と、前記複数の第2のステージングラッチのうち、前記第3の複数のステージングラッチよりも後段側に位置する第4の複数のステージングラッチ間におけるデータの遷移に複数のクロックを必要とするマルチサイクル動作とにより、前記第2の命令を実行することを特徴とする請求項1記載の演算処理装置。 - 前記第2の命令実行部は、複数の第2のステージングラッチを有し、非共有マルチサイクル動作により、前記第2の命令を実行するものであり、

前記非共有マルチサイクル動作は、前記複数の第2のステージングラッチ間におけるデータの遷移に複数のクロックを必要とするものであり、

前記ステージングラッチ間にそれぞれ位置する回路の資源に関して、前記第2の命令実行部における前記非共有マルチサイクル動作と、前記演算処理装置が備える他の命令実行部は、回路の資源を共有していないことを特徴とする請求項1記載の演算処理装置。 - 前記第2の命令実行部は、複数の第2のステージングラッチを有し、非共有パイプライン動作と共有パイプライン動作により、前記第2の命令を実行するものであり、

前記非共有パイプライン動作は、前記複数の第2のステージングラッチのうち、最初段のステージングラッチを含む第3の複数のステージングラッチ間におけるデータの遷移に単一のクロックのみを必要とするものであり、

前記共有パイプライン動作は、前記複数の第2のステージングラッチのうち、前記第3の複数のステージングラッチよりも後段側に位置する第4の複数のステージングラッチ間におけるデータの遷移に単一のクロックのみを必要とするものであり、

前記ステージングラッチ間にそれぞれ位置する回路の資源に関して、前記第2の命令実行部における前記非共有パイプライン動作と、前記演算処理装置が備える他の命令実行部は、回路の資源を共有していないものであり、

前記ステージングラッチ間にそれぞれ位置する回路の資源に関して、前記第2の命令実行部における前記共有パイプライン動作と、前記演算処理装置が備える他の命令実行部は、回路の資源を共有しているものであることを特徴とする請求項1記載の演算処理装置。 - 前記命令制御部は、

前記第1の命令実行部が前記第1の命令の実行中において、前記第1の命令のマルチサイクル動作の実行と、前記第2の命令のマルチサイクル動作、非共有マルチサイクル動作又は共有パイプライン動作の実行とが重複しないように、前記第2の命令の前記第2の命令実行部への発行を抑止することを特徴とする請求項2〜4のいずれか1項に記載の演算処理装置。 - 前記命令制御部は、

前記第1の命令の実行における前記パイプライン動作と、前記第2の命令の実行とが一部重複するように、前記第1の命令を前記第1の命令実行部に発行するとともに、前記第2の命令を前記第2の命令実行部に発行することを特徴とする請求項1〜5のいずれか1項に記載の演算処理装置。 - 前記命令制御部は、

前記第1の命令の実行における前記パイプライン動作又は前記マルチサイクル動作と、前記第2の命令の実行とが一部重複するように、前記第1の命令を前記第1の命令実行部に発行するとともに、前記第2の命令を前記第2の命令実行部に発行することを特徴とする請求項1〜6のいずれか1項に記載の演算処理装置。 - 複数のステージングラッチを有し、前記複数のステージングラッチのうち、最終段のステージングラッチを含む第1の複数のステージングラッチ間におけるデータの遷移に単一のクロックのみを必要とするパイプライン動作と、前記複数のステージングラッチのうち、前記第1の複数のステージングラッチよりも前段側に位置する第2の複数のステージングラッチ間におけるデータの遷移に複数のクロックを必要とするマルチサイクル動作とにより第1の命令を実行する第1の命令実行部と、第2の命令を実行する第2の命令実行部とを有する演算処理装置の制御方法において、

前記演算処理装置が有する命令制御部が、前記第1の命令と前記第2の命令とを入力し、

前記命令制御部が、前記第1の命令の実行と前記第2の命令の実行とが一部重複するように、前記第1の命令を前記第1の命令実行部に発行するとともに、前記第2の命令を前記第2の命令実行部に発行し、

前記命令制御部が、前記第1の命令実行部が前記第1の命令の実行中に、前記第1の命令の不定の終了サイクルを確定し、前記確定した終了サイクルに応じて、前記第2の命令の前記第2の命令実行部への発行の抑止を解除することを特徴とする演算処理装置の制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013168694A JP6225554B2 (ja) | 2013-08-14 | 2013-08-14 | 演算処理装置及び演算処理装置の制御方法 |

| EP14177225.1A EP2843543B1 (en) | 2013-08-14 | 2014-07-16 | Arithmetic processing device and control method of arithmetic processing device |

| US14/335,973 US20150052334A1 (en) | 2013-08-14 | 2014-07-21 | Arithmetic processing device and control method of arithmetic processing device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013168694A JP6225554B2 (ja) | 2013-08-14 | 2013-08-14 | 演算処理装置及び演算処理装置の制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015036922A JP2015036922A (ja) | 2015-02-23 |

| JP6225554B2 true JP6225554B2 (ja) | 2017-11-08 |

Family

ID=51224726

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013168694A Expired - Fee Related JP6225554B2 (ja) | 2013-08-14 | 2013-08-14 | 演算処理装置及び演算処理装置の制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20150052334A1 (ja) |

| EP (1) | EP2843543B1 (ja) |

| JP (1) | JP6225554B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11403254B2 (en) * | 2018-08-16 | 2022-08-02 | Tachyum Ltd. | System and method for populating multiple instruction words |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07244588A (ja) * | 1994-01-14 | 1995-09-19 | Matsushita Electric Ind Co Ltd | データ処理装置 |

| GB2287108B (en) * | 1994-02-28 | 1998-05-13 | Intel Corp | Method and apparatus for avoiding writeback conflicts between execution units sharing a common writeback path |

| JPH08305567A (ja) * | 1995-05-10 | 1996-11-22 | Hitachi Ltd | 演算命令の並列処理方法および並列処理装置 |

| US6304954B1 (en) * | 1998-04-20 | 2001-10-16 | Rise Technology Company | Executing multiple instructions in multi-pipelined processor by dynamically switching memory ports of fewer number than the pipeline |

| AU2001245511A1 (en) * | 2000-03-10 | 2001-09-24 | Arc International Plc | Method and apparatus for enhancing the performance of a pipelined data processor |

| US20060224864A1 (en) * | 2005-03-31 | 2006-10-05 | Dement Jonathan J | System and method for handling multi-cycle non-pipelined instruction sequencing |

| US7313673B2 (en) | 2005-06-16 | 2007-12-25 | International Business Machines Corporation | Fine grained multi-thread dispatch block mechanism |

| US20070022277A1 (en) * | 2005-07-20 | 2007-01-25 | Kenji Iwamura | Method and system for an enhanced microprocessor |

| JP2012173755A (ja) | 2011-02-17 | 2012-09-10 | Nec Computertechno Ltd | 情報処理装置及び情報処理方法 |

-

2013

- 2013-08-14 JP JP2013168694A patent/JP6225554B2/ja not_active Expired - Fee Related

-

2014

- 2014-07-16 EP EP14177225.1A patent/EP2843543B1/en active Active

- 2014-07-21 US US14/335,973 patent/US20150052334A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| EP2843543A3 (en) | 2017-06-07 |

| US20150052334A1 (en) | 2015-02-19 |

| EP2843543A2 (en) | 2015-03-04 |

| EP2843543B1 (en) | 2022-08-10 |

| JP2015036922A (ja) | 2015-02-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9733945B2 (en) | Pipelining out-of-order instructions | |

| US10684860B2 (en) | High performance processor system and method based on general purpose units | |

| JP3547482B2 (ja) | 情報処理装置 | |

| CN101965554B (zh) | 选择性地提交已执行指令的结果的系统和方法 | |

| US9811340B2 (en) | Method and apparatus for reconstructing real program order of instructions in multi-strand out-of-order processor | |

| CN108089883B (zh) | 基于推测度量将资源分配给线程 | |

| CN105408860B (zh) | 多线程异步处理器系统和方法 | |

| US9658853B2 (en) | Techniques for increasing instruction issue rate and reducing latency in an out-of order processor | |

| CN105005463B (zh) | 具有世代重命名的计算机处理器 | |

| JP5047542B2 (ja) | マルチスレッドプロセッサのディスパッチ時にスレッドをブロックする方法、コンピュータプログラム、および装置(精細なマルチスレッドディスパッチロックメカニズム) | |

| KR20180021812A (ko) | 연속하는 블록을 병렬 실행하는 블록 기반의 아키텍쳐 | |

| JP2002268878A (ja) | スレッド間優先度可変プロセッサ | |

| JP5861354B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| WO2018026539A1 (en) | Transactional register file for a block-based processor | |

| JP2018005488A (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| CN105045562A (zh) | 利用生成重命名的计算机信息处理器 | |

| CN101763251A (zh) | 多线程微处理器的指令译码缓冲装置 | |

| JP6225554B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| JP2014044509A (ja) | 演算処理装置および演算処理装置の制御方法 | |

| JP4996945B2 (ja) | データ処理装置、データ処理方法 | |

| US20100100709A1 (en) | Instruction control apparatus and instruction control method | |

| US12118355B2 (en) | Cache coherence validation using delayed fulfillment of L2 requests | |

| US11194577B2 (en) | Instruction issue according to in-order or out-of-order execution modes | |

| US20060248320A1 (en) | Data processing apparatus and method for executing a sequence of instructions including a multiple iteration instruction | |

| JP6381019B2 (ja) | 情報処理装置及び制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160510 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170413 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170912 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170925 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6225554 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |