JP6157811B2 - ブート前データ検証のための方法及びシステム - Google Patents

ブート前データ検証のための方法及びシステム Download PDFInfo

- Publication number

- JP6157811B2 JP6157811B2 JP2012166673A JP2012166673A JP6157811B2 JP 6157811 B2 JP6157811 B2 JP 6157811B2 JP 2012166673 A JP2012166673 A JP 2012166673A JP 2012166673 A JP2012166673 A JP 2012166673A JP 6157811 B2 JP6157811 B2 JP 6157811B2

- Authority

- JP

- Japan

- Prior art keywords

- storage area

- data storage

- stored

- ofp

- verification number

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/4401—Bootstrapping

- G06F9/4406—Loading of operating system

- G06F9/4408—Boot device selection

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operation

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1415—Saving, restoring, recovering or retrying at system level

- G06F11/1417—Boot up procedures

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Computer Security & Cryptography (AREA)

- Detection And Correction Of Errors (AREA)

- Stored Programmes (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

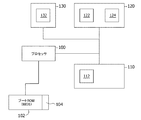

102 ブートROM(BIOS)

104 チェックサム

112 アプリケーションの1次イメージ

120、130 メモリデバイス

122、124 アプリケーションのイメージ

132 アプリケーションの単一イメージ

300 データ処理システム

302 通信ファブリック

304 プロセッサ装置

306 メモリ

308 固定記憶域

310 通信装置

312 入出力装置

314 表示装置

316 マシンコード

318 コンピュータで読込み可能な媒体

320 コンピュータプログラム製品

Claims (6)

- 航空機アビオニクスデバイス用のオペレーショナルフライトプログラム(OFP)の実行用のデータの読み込みに先立って、前記OFPを定義するデータを検証する方法であって、

a)前記OFPを定義する、航空機内の1次データ記憶領域内のデータに対する第1の検証番号を計算するステップと、

b)前記第1の検証番号と、航空機アビオニクスデバイスのブートROMに保存されている番号とを比較するステップと、

c)前記第1の検証番号が前記保存されている番号と一致しないことを確認するステップと、

d)前記第1の検証番号が前記保存されている番号と一致しないことの前記確認に基づき、前記1次データ記憶領域内のものと同一のOFPを定義している、前記航空機内の2次データ記憶領域内のデータに対する第2の検証番号を計算するステップと、

e)前記第2の検証番号と、前記航空機アビオニクスデバイスの前記ブートROMに保存されている前記番号とを比較するステップと、

f)前記第2の検証番号と前記保存されている番号とが一致することを確認するステップと、

g)前記第2の検証番号と前記保存された番号が一致することの確認に基づき、前記1次データ記憶領域内のデータを前記2次データ記憶領域内のデータで上書きするステップと、

h)前記OFPを実行させるステップと、を含む方法。 - 前記第1の検証番号を計算するステップ及び前記第2の検証番号を計算するステップの各々が、前記OFPのチェックサムを計算するステップを含む、請求項1に記載の方法。

- 前記第1の検証番号を計算するステップ及び前記第2の検証番号を計算するステップの各々が、前記OFPを定義するデータのチェックサムを計算するため、前記ブートROMデバイス内の命令を実行するステップを含む、請求項1に記載の方法。

- 航空機アビオニクスデバイスであって、

プロセシング装置と、

前記プロセシング装置によって基本入出力システムが実行されるブートROMと、

前記航空機アビオニクスデバイスに関連するオペレーショナルフライトプログラム(OFP)のイメージを保存するように構成されている1次データ記憶領域と、

前記航空機アビオニクスデバイスに関連する前記OFPの追加イメージを保存するように構成された少なくとも一つの2次データ記憶領域と、を含み、

前記プロセッシング装置が、

前記1次データ記憶領域内に保存されている前記イメージに対する第1の検証番号を計算し、

前記1次データ記憶領域内に保存されている前記イメージに対して計算された前記第1の検証番号と、前記ブートROMに保存されている番号とを比較し、

前記1次データ記憶領域内に保存されている前記イメージに対する前記第1の検証番号が前記保存されている番号と一致しないことを確認し、

前記1次データ記憶領域内に保存されている前記イメージに対する前記第1の検証番号が前記保存されている番号と一致しないことの前記確認に基づき、前記少なくとも一つの2次データ記憶領域内の前記追加イメージに対する第2の検証番号であって、前記少なくとも一つの2次データ記憶領域内の前記追加イメージに対応するデータが前記1次データ記憶領域内のものと同一のOFPを定義している、第2の検証番号を計算し、

前記少なくとも一つの2次データ記憶領域内に保存されている前記追加イメージに対して計算された前記第2の検証番号と、前記ブートROMに保存されている前記番号とを比較し、

前記第2の検証番号と前記保存されている番号とが一致することを確認し、

前記1次データ記憶領域の前記イメージを前記航空機アビオニクスデバイスに関連する前記OFPの前記追加イメージで上書きし、

前記2次データ記憶領域の前記追加イメージによって定義される前記OFPを実行する、ようにプログラムされている、航空機アビオニクスデバイス。 - 前記第1及び第2の検証番号の各々が前記OFPに対するチェックサムを含む、請求項4に記載の航空機アビオニクスデバイス。

- 前記少なくとも一つの2次データ記憶領域が、シリコンメモリデバイス、コンピュータハードドライブ、CD−ROM、フラッシュドライブ、及びサムドライブのうちの少なくとも一つを含む、請求項4に記載の航空機アビオニクスデバイス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/193,718 US8826080B2 (en) | 2011-07-29 | 2011-07-29 | Methods and systems for preboot data verification |

| US13/193,718 | 2011-07-29 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013178733A JP2013178733A (ja) | 2013-09-09 |

| JP2013178733A5 JP2013178733A5 (ja) | 2015-08-13 |

| JP6157811B2 true JP6157811B2 (ja) | 2017-07-05 |

Family

ID=46875641

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012166673A Active JP6157811B2 (ja) | 2011-07-29 | 2012-07-27 | ブート前データ検証のための方法及びシステム |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8826080B2 (ja) |

| EP (1) | EP2551765A1 (ja) |

| JP (1) | JP6157811B2 (ja) |

| CN (1) | CN102968348A (ja) |

| CA (1) | CA2780370C (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9471435B2 (en) * | 2012-01-05 | 2016-10-18 | Mitsubishi Electric Corporation | Information processing device, information processing method, and computer program |

| CN103617095A (zh) * | 2013-11-15 | 2014-03-05 | 中国航空无线电电子研究所 | 一种VxWorks映像文件正确性的检查方法 |

| US9135029B2 (en) * | 2014-01-02 | 2015-09-15 | Lenovo Enterprise Solutions (Singapore) Pte. Ltd. | Securely reconfiguring a multi-node system to prevent firmware rollback |

| CN103729597B (zh) * | 2014-01-16 | 2017-11-17 | 宇龙计算机通信科技(深圳)有限公司 | 系统启动校验方法、系统启动校验装置和终端 |

| FR3024869B1 (fr) * | 2014-08-14 | 2016-08-26 | Zodiac Aero Electric | Systeme de distribution electrique pour un aeronef et procede de commande correspondant |

| TWI599904B (zh) * | 2016-03-30 | 2017-09-21 | 緯創資通股份有限公司 | 電子裝置及其資料驗證方法 |

| CN108958819B (zh) * | 2018-06-29 | 2021-12-31 | 大陆汽车车身电子系统(芜湖)有限公司 | 多分区系统的启动方法及多分区系统 |

| JP7330681B2 (ja) * | 2018-10-04 | 2023-08-22 | キヤノン株式会社 | 情報処理装置、その制御方法、プログラム、及び画像形成装置 |

| US20220113982A1 (en) * | 2020-10-09 | 2022-04-14 | Arris Enterprises Llc | Selective switching of an active partition in an electronic device |

Family Cites Families (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5379342A (en) * | 1993-01-07 | 1995-01-03 | International Business Machines Corp. | Method and apparatus for providing enhanced data verification in a computer system |

| US5793943A (en) | 1996-07-29 | 1998-08-11 | Micron Electronics, Inc. | System for a primary BIOS ROM recovery in a dual BIOS ROM computer system |

| US6061788A (en) * | 1997-10-02 | 2000-05-09 | Siemens Information And Communication Networks, Inc. | System and method for intelligent and reliable booting |

| US5987605A (en) | 1998-02-28 | 1999-11-16 | Hewlett-Packard Co. | Methods and apparatus for dual-boot memory selection, update, and recovery in a programmable device |

| USH2040H1 (en) * | 1998-05-22 | 2002-08-06 | The United States Of America As Represented By The Secretary Of The Navy | Personal computer based utility program for an electronic countermeasure system |

| SE521456C2 (sv) * | 1998-12-15 | 2003-11-04 | Ericsson Telefon Ab L M | Förfarande och anordning vid ett distribuerat system |

| US6401218B1 (en) * | 1999-02-16 | 2002-06-04 | International Business Machines Corporation | Method and system for functional kernel verification testing within a data processing system |

| US6907602B2 (en) * | 2000-08-10 | 2005-06-14 | Mustek Systems Inc. | Method for updating firmware of computer device |

| US6651188B2 (en) | 2001-06-29 | 2003-11-18 | Intel Corporation | Automatic replacement of corrupted BIOS image |

| US7146525B2 (en) | 2001-08-31 | 2006-12-05 | Legend (Beijing) Limited | Method for backing up and recovering data in the hard disk of a computer |

| US7024581B1 (en) * | 2002-10-09 | 2006-04-04 | Xpoint Technologies, Inc. | Data processing recovery system and method spanning multiple operating system |

| AU2004273105B2 (en) * | 2003-09-18 | 2009-06-11 | Aristocrat Technologies Australia Pty Ltd | BIOS protection device |

| US20060047944A1 (en) * | 2004-09-01 | 2006-03-02 | Roger Kilian-Kehr | Secure booting of a computing device |

| CN100356337C (zh) * | 2004-10-16 | 2007-12-19 | 鸿富锦精密工业(深圳)有限公司 | 基本输入输出系统只读存储器数据检测系统及方法 |

| US7346793B2 (en) * | 2005-02-10 | 2008-03-18 | Northrop Grumman Corporation | Synchronization of multiple operational flight programs |

| JP2006227830A (ja) * | 2005-02-16 | 2006-08-31 | Seiko Epson Corp | 情報処理機器及び情報処理機器の制御方法 |

| CN1858713A (zh) * | 2005-04-30 | 2006-11-08 | 广东科龙电器股份有限公司 | 提高e/eprom存储器存储数据可靠性的方法 |

| TWI284284B (en) | 2005-08-08 | 2007-07-21 | Inventec Corp | Selective apparatus for main/backup basic input/output system (BIOS) |

| CN1971536A (zh) | 2005-11-24 | 2007-05-30 | 鸿富锦精密工业(深圳)有限公司 | 基本输入输出系统的纠错系统及方法 |

| US7669048B2 (en) | 2005-12-09 | 2010-02-23 | Microsoft Corporation | Computing device limiting mechanism |

| JP2008084291A (ja) * | 2006-08-28 | 2008-04-10 | Fujitsu Ltd | 記憶装置、制御方法及び制御装置 |

| US7987351B2 (en) * | 2006-10-06 | 2011-07-26 | Broadcom Corporation | Method and system for enhanced boot protection |

| US7783877B2 (en) | 2007-05-15 | 2010-08-24 | Inventec Corporation | Boot-switching apparatus and method for multiprocessor and multi-memory system |

| BRPI0815619A2 (pt) * | 2007-08-21 | 2015-02-18 | Thomson Licensing | Método e sistema para o reparo de sistemas de arquivos danificados do disco rígido |

| US20090063834A1 (en) | 2007-09-05 | 2009-03-05 | Inventec Corporation | Auto-Switching Bios System and the Method Thereof |

| TW200923783A (en) | 2007-11-30 | 2009-06-01 | Giga Byte Tech Co Ltd | Method for automatically repairing system configuration using single key control |

| CN101452410A (zh) * | 2007-12-06 | 2009-06-10 | 中兴通讯股份有限公司 | 一种嵌入式数据库的数据备份系统及数据备份和恢复方法 |

| CN101458647B (zh) | 2007-12-12 | 2012-11-21 | 鸿富锦精密工业(深圳)有限公司 | 双bios电路 |

| CN101458648A (zh) | 2007-12-12 | 2009-06-17 | 鸿富锦精密工业(深圳)有限公司 | 双bios电路 |

| JP5083890B2 (ja) * | 2007-12-27 | 2012-11-28 | 東芝エレベータ株式会社 | エレベータの制御装置 |

| TWI355608B (en) | 2008-01-30 | 2012-01-01 | Inventec Corp | Computer system with dual basic input output syste |

| DE102008021567B4 (de) * | 2008-04-30 | 2018-03-22 | Globalfoundries Inc. | Computersystem mit sicherem Hochlaufmechanismus auf der Grundlage einer Verschlüsselung mit symmetrischem Schlüssel |

| JP4802222B2 (ja) * | 2008-07-22 | 2011-10-26 | 株式会社東芝 | コンピュータシステムおよびコンテンツ保護方法 |

| CN101634960A (zh) * | 2008-07-23 | 2010-01-27 | 鸿富锦精密工业(深圳)有限公司 | 一种修改bios参数及重新生成校验和的方法 |

| US20100082963A1 (en) | 2008-10-01 | 2010-04-01 | Chun Hui Li | Embedded system that automatically updates its software and the method thereof |

| FR2938671B1 (fr) * | 2008-11-17 | 2011-06-03 | Sagem Defense Securite | Equipement avionique securise et procede de securisation associe |

| US20100235646A1 (en) * | 2009-03-13 | 2010-09-16 | Egis Technology Inc. | Verification method and system thereof |

| JP5493951B2 (ja) * | 2009-04-17 | 2014-05-14 | 株式会社リコー | 情報処理装置、正当性検証方法及びプログラム |

| JP5247887B2 (ja) * | 2009-05-27 | 2013-07-24 | 株式会社日立製作所 | ストレージ装置、及びその制御方法、並びにプログラム |

| JP5233869B2 (ja) * | 2009-06-26 | 2013-07-10 | 日立電線株式会社 | 処理システム及び処理装置が実行するプログラムの実行方法 |

| TWI399647B (zh) | 2009-10-15 | 2013-06-21 | Wistron Corp | 回復電腦系統之基本輸出入系統之方法及相關電腦系統 |

| US8621276B2 (en) * | 2010-12-17 | 2013-12-31 | Microsoft Corporation | File system resiliency management |

-

2011

- 2011-07-29 US US13/193,718 patent/US8826080B2/en active Active

-

2012

- 2012-06-14 CA CA2780370A patent/CA2780370C/en active Active

- 2012-07-27 CN CN2012102646118A patent/CN102968348A/zh active Pending

- 2012-07-27 EP EP12178371A patent/EP2551765A1/en not_active Withdrawn

- 2012-07-27 JP JP2012166673A patent/JP6157811B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CA2780370A1 (en) | 2013-01-29 |

| EP2551765A1 (en) | 2013-01-30 |

| JP2013178733A (ja) | 2013-09-09 |

| US20130031413A1 (en) | 2013-01-31 |

| CN102968348A (zh) | 2013-03-13 |

| US8826080B2 (en) | 2014-09-02 |

| CA2780370C (en) | 2015-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6157811B2 (ja) | ブート前データ検証のための方法及びシステム | |

| CN102521081B (zh) | 修复遭破坏的软件 | |

| CN103718165B (zh) | Bios闪存攻击保护和通知 | |

| JP5909264B2 (ja) | セキュア・リカバリ装置及び方法 | |

| US8135993B1 (en) | Updating a firmware image using a firmware debugger application | |

| US9027014B2 (en) | Updating firmware compatibility data | |

| US20170270301A1 (en) | Systems And Methods Using Virtual UEFI Path For Secure Firmware Handling In Multi-Tenant Or Server Information Handling System Environments | |

| US11017091B2 (en) | Firmware map data | |

| US7509544B2 (en) | Data repair and synchronization method of dual flash read only memory | |

| WO2016206514A1 (zh) | 启动处理方法及装置 | |

| KR20170067826A (ko) | 펌웨어의 업데이트 방법 | |

| WO2015184732A1 (zh) | 引导程序的存储方法、故障恢复方法及设备、计算机存储介质 | |

| TW201314574A (zh) | 用於電腦系統之基本輸入輸出系統程式更新方法及更新裝置 | |

| KR101844095B1 (ko) | 부트로더 실행 방법 및 장치 | |

| US9317454B2 (en) | Information processing apparatus, information processing method, and recording medium | |

| JP7084160B2 (ja) | 起動制御装置、起動制御システム、起動制御方法、及び、起動制御プログラム | |

| US9971659B1 (en) | Memory programming providing corruption protection | |

| US20220147343A1 (en) | Tranistionary firmware packages | |

| JP6822203B2 (ja) | ファームウェア実行装置、ドライバ実行装置、ドライバ管理装置、ファームウェア管理装置、コンピュータ装置、方法およびプログラム | |

| JP2019160133A (ja) | 情報処理装置、情報処理システムおよび方法 | |

| US20120166785A1 (en) | Information processing apparatus, restoring method of bios setup, restoring program | |

| US20230069169A1 (en) | Information processing apparatus and control method of the same | |

| JP5668518B2 (ja) | 情報処理装置、情報処理方法及びプログラム | |

| JP2022126549A (ja) | 情報処理装置 | |

| TWI457754B (zh) | 實現硬碟驅動器拷貝的應用伺服器及方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150618 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150618 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160809 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161025 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170223 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20170306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170516 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170607 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6157811 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |