JP6136834B2 - ストレージ制御装置、制御プログラムおよび制御方法 - Google Patents

ストレージ制御装置、制御プログラムおよび制御方法 Download PDFInfo

- Publication number

- JP6136834B2 JP6136834B2 JP2013210556A JP2013210556A JP6136834B2 JP 6136834 B2 JP6136834 B2 JP 6136834B2 JP 2013210556 A JP2013210556 A JP 2013210556A JP 2013210556 A JP2013210556 A JP 2013210556A JP 6136834 B2 JP6136834 B2 JP 6136834B2

- Authority

- JP

- Japan

- Prior art keywords

- control

- control unit

- memory

- storage

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0706—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation the processing taking place on a specific hardware platform or in a specific software environment

- G06F11/0727—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation the processing taking place on a specific hardware platform or in a specific software environment in a storage system, e.g. in a DASD or network based storage system

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0751—Error or fault detection not based on redundancy

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Quality & Reliability (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Debugging And Monitoring (AREA)

Description

図1は、実施の形態1にかかるストレージ制御装置100の一実施例を示す説明図である。図1において、ストレージ制御装置100は、複数の制御部101(図1の例では、制御部101−1〜101−3)と、第1の記憶部102と、第2の記憶部103とを有する。

実施の形態2では、複数の制御部101は、ストレージのI/Oを制御する複数のIOCと複数のコアを有するプロセッサから構成される。各IOCおよび各コアが、メモリDIF制御機能を有する。プロセッサのコアの1つが、メモリDIF制御を起動するIOCまたはコアを決定する。

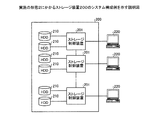

図2は、実施の形態2にかかるストレージ装置200のシステム構成例を示す説明図である。図2において、ストレージ装置200は、複数のストレージ制御装置201と、複数のストレージ210とを有する。ストレージ装置200は、例えば、FibreChannel、SAS、iSCSI等のインターフェースで複数のホストコンピュータ220に接続される。また、ストレージ装置200は、例えば、LAN(Local Area Network)、WAN(Wide Area Network)、インターネットなどのネットワークを介して複数のホストコンピュータ220に接続されてもよい。

図3は、実施の形態2にかかるストレージ制御装置201のハードウェア構成例を示すブロック図である。ストレージ制御装置201は、複数のコア311−1〜311−nを有するプロセッサ301と、メモリ302と、複数のIOC303−1〜303−3とを有する。複数のIOC303は、IOC(ホスト接続)303−1と、IOC(HDD接続)303−2と、IOC(通信)303−3とを有する。また、各構成部は、バス300によってそれぞれ接続される。コア311とIOC303は、メモリDIF制御機能を有する。

図4は、DIF構造の一例を示す説明図である。ストレージ装置200において、ホストコンピュータ220からのデータのI/OおよびHDD等のストレージ210に記憶するデータのI/Oは、ブロック単位に行われる。図4の例では、512バイト単位で行われる。DIF制御機能は、データの正当性を検証するため、元データ400の各ブロックに8バイトのチェックコードを付加することにより、DIF付加データ401が作成される。

図5は、実施の形態2にかかるIOC負荷特性テーブル500の一例を示す説明図である。IOC負荷特性テーブル500は、例えば、後述する作成部901によって作成され、メモリ302に記憶される。

図6は、実施の形態2にかかるコア負荷特性テーブル600の一例を示す説明図である。コア負荷特性テーブル600は、例えば、後述する作成部901によって作成され、メモリ302に記憶される。

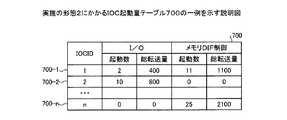

図7は、実施の形態2にかかるIOC起動量テーブル700の一例を示す説明図である。IOC起動量テーブル700は、IOC303ごとに、現在のIOC303の使用率とメモリDIF制御の転送量とを対応付けて記憶するテーブルである。IOC起動量テーブル700は、例えば、後述する作成部901によって作成され、メモリ302に記憶され、後述する更新部902によって更新される。IOC起動量テーブル700は、IOCID、I/Oの起動数、I/Oの総転送量、メモリDIF制御の起動数、およびメモリDIF制御の総転送量のフィールドを有する。IOC起動量テーブル700は、各フィールドに情報を設定することで、IOC起動量情報(例えば、IOC起動量情報700−1〜700−n)をレコードとして記憶する。

図8は、実施の形態2にかかるコア起動量テーブル800の一例を示す説明図である。コア起動量テーブル800は、コア311ごとに、現在のコア311のBusy率とメモリDIF制御の転送量とを対応付けて記憶するテーブルである。コア起動量テーブル800は、例えば、後述する作成部901によって作成され、メモリ302に記憶され、後述する更新部902によって更新される。コア起動量テーブル800は、コアID、Busy率、メモリDIF制御の起動数、およびメモリDIF制御の総転送量のフィールドを有する。コア起動量テーブル800は、各フィールドに情報を設定することで、コア起動量情報(例えばコア起動量情報800−1〜800−n)をレコードとして記憶する。

図9は、実施の形態2にかかるストレージ制御装置201の機能的構成例を示すブロック図である。図9において、ストレージ制御装置201は、作成部901と、更新部902と、決定部903とを含む構成である。各機能部は、具体的には、例えば、図3に示したメモリ302などの記憶装置に記憶されたプログラムをプロセッサ301に実行させることにより、その機能を実現する。各機能部の処理結果は、例えば、図3に示したメモリ302などの記憶装置に記憶される。

ここで、作成部901の具体的な処理内容について説明する。

IOC303は、メモリDIF制御以外に、HDDのリード、ライト処理やホストコンピュータからのデータ転送などI/O制御も実施している。IOC303に、I/O制御とメモリDIF制御を同時に動作させると、IOC303内の共有資源が競合することで、それぞれを単独に起動するより、I/Oの遅延やメモリDIF制御の性能低下が発生する。

プロセッサ301の各コア311は、メモリDIF制御以外に、ストレージ制御装置201の制御も実施している。このため、コア311でメモリDIF制御を起動した場合、コア311のメモリDIF制御の起動率とコア311のBusy率によりメモリDIF制御の性能は変動する。この低下特性を把握するために、作成部901は、コア311ごとに所定のBusy率でメモリDIF制御を起動し、コア311にかかる負荷を表す指標値LFCを記憶するコア負荷特性テーブル600を作成する。作成部901は、以下の手順でコア負荷特性テーブル600を作成する。

ここで、更新部902の具体的な処理内容について説明する。

(1)更新部902は、IOC303がI/O要求を受け付けたとき、IOC起動量テーブル700のI/O要求を受け付けたIOC303のレコードのI/Oの起動数を1加算する。さらに、更新部902は、当該I/O要求でのデータ転送量を、I/O要求を受け付けたIOC303のレコードのI/Oの総転送量に加算する。

(1’)更新部902は、コア311上で動作するOSのBusy率採取機能を使用して、コア起動量テーブル800のBusy率を定期的に更新する。または、更新部902は、定期的な割込みをコア311上で動作するOSに対して行い、タスクの動作状態またはアイドル状態を定期的に収集することでBusy率を求めることもできる。タスクとはOSから見た処理の実行単位であり、タスクの動作状態とは、コア311がプログラムを実行する状態であり、タスクのアイドル状態とは、実行するプログラムがない状態である。

図10は、実施の形態2にかかるストレージ制御装置201のIOC負荷特性テーブル500の作成処理手順の一例を示すフローチャートである。図10のフローチャートにおいて、まず、作成部901は、IOC303のIDを示すiを1に設定する(ステップS1001)。その後、作成部901は、IOC303の使用率を示すjを0に設定し(ステップS1002)、メモリDIF制御の起動率を示すkを0に設定する(ステップS1003)。

図11は、実施の形態2にかかるストレージ制御装置201のI/O処理手順の一例を示すフローチャートである。図11のフローチャートにおいて、まず、ストレージ制御装置201は、I/O要求を受け、他のストレージ制御装置201からのデータをIOC303が受信する(ステップS1101)。受信したデータは、メモリ302に記憶される。次に、ストレージ制御装置201は、メモリ302に記憶されたデータに対して、メモリDIF制御を実行するか否かを判定する(ステップS1102)。

前記複数の制御部に含まれる制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する第1の記憶部と、

前記制御部に対応して、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とを対応付けて記憶する第2の記憶部と、を有し、

前記複数の制御部のいずれかの制御部は、

前記制御部に対応して、実行対象となる検証処理で処理するデータ量と前記第2の記憶部の記憶内容とに基づき前記第1の記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、特定した当該指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

ことを特徴とするストレージ制御装置。

前記制御部に対応して、前記第1の記憶部の記憶内容を参照して、前記第2の記憶部に記憶された前記制御部の使用率と、前記第2の記憶部に記憶された前記制御部で起動中の前記検証処理で処理するデータ量に前記実行対象の検証処理で処理するデータ量を加算したデータ量との組み合わせに対応する指標値を特定することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定することを特徴とする付記1に記載のストレージ制御装置。

前記起動先の制御部を決定したことに応じて、前記第2の記憶部に記憶された、前記起動先の制御部で起動中の前記検証処理で処理するデータ量に、前記実行対象の検証処理で処理するデータ量を加算し、

前記起動先の制御部による前記実行対象の検証処理の実行が完了したことに応じて、前記第2の記憶部に記憶された、前記起動先の制御部で起動中の前記検証処理で処理するデータ量から、前記実行対象の検証処理で処理するデータ量を減算することを特徴とする付記1または2に記載のストレージ制御装置。

所定の使用率の前記制御部に所定のデータ量を処理する検証処理を実行させ、前記所定のデータ量に対する、前記所定のデータ量のうちの所定の時間内に前記制御部が処理できなかったデータ量の割合を、前記制御部にかかる負荷を表す指標値として算出し、算出した前記制御部にかかる負荷を表す指標値を、前記所定のデータ量と前記所定の使用率との組み合わせに対応付けて前記第1の記憶部に記憶することを特徴とする付記1〜3のいずれか一つに記載のストレージ制御装置。

特定した前記指標値が最小である前記制御部を、前記実行対象の検証処理を起動する制御部として決定する、

ことを特徴とする付記1〜5のいずれか一つに記載のストレージ制御装置。

前記複数の制御部のいずれかの制御部に、

前記複数の制御部に含まれる制御部に対応して、実行対象となる検証処理で処理するデータ量と、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とに基づき、前記制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、

特定した前記制御部にかかる負荷を表す指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

処理を実行させることを特徴とする制御プログラム。

前記複数の制御部のいずれかの制御部が、

前記複数の制御部に含まれる制御部に対応して、実行対象となる検証処理で処理するデータ量と、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とに基づき、前記制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、

特定した前記制御部にかかる負荷を表す指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

処理を実行することを特徴とする制御方法。

前記複数の制御部のいずれかの制御部に、

前記複数の制御部に含まれる制御部に対応して、実行対象となる検証処理で処理するデータ量と、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とに基づき、前記制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、

特定した前記制御部にかかる負荷を表す指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

処理を実行させる制御プログラムを記録したことを特徴とするコンピュータに読み取り可能な記録媒体。

101 制御部

102 第1の記憶部

103 第2の記憶部

200 ストレージ装置

201 ストレージ制御装置

210 ストレージ

901 作成部

902 更新部

903 決定部

Claims (7)

- データの正当性を検証する検証処理を実行可能な複数の制御部と、

前記複数の制御部に含まれる制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する第1の記憶部と、

前記制御部に対応して、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とを対応付けて記憶する第2の記憶部と、を有し、

前記複数の制御部のいずれかの制御部は、

前記制御部に対応して、実行対象となる検証処理で処理するデータ量と前記第2の記憶部の記憶内容とに基づき前記第1の記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、特定した当該指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

ことを特徴とするストレージ制御装置。 - 前記いずれかの制御部は、

前記制御部に対応して、前記第1の記憶部の記憶内容を参照して、前記第2の記憶部に記憶された前記制御部の使用率と、前記第2の記憶部に記憶された前記制御部で起動中の前記検証処理で処理するデータ量に前記実行対象の検証処理で処理するデータ量を加算したデータ量との組み合わせに対応する指標値を特定することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定することを特徴とする請求項1に記載のストレージ制御装置。 - 前記いずれかの制御部は、

前記起動先の制御部を決定したことに応じて、前記第2の記憶部に記憶された、前記起動先の制御部で起動中の前記検証処理で処理するデータ量に、前記実行対象の検証処理で処理するデータ量を加算し、

前記起動先の制御部による前記実行対象の検証処理の実行が完了したことに応じて、前記第2の記憶部に記憶された、前記起動先の制御部で起動中の前記検証処理で処理するデータ量から、前記実行対象の検証処理で処理するデータ量を減算することを特徴とする請求項1または2に記載のストレージ制御装置。 - 前記いずれかの制御部は、

所定の使用率の前記制御部に所定のデータ量を処理する検証処理を実行させ、前記所定のデータ量に対する、前記所定のデータ量のうちの所定の時間内に前記制御部が処理できなかったデータ量の割合を、前記制御部にかかる負荷を表す指標値として算出し、算出した前記制御部にかかる負荷を表す指標値を、前記所定のデータ量と前記所定の使用率との組み合わせに対応付けて前記第1の記憶部に記憶することを特徴とする請求項1〜3のいずれか一つに記載のストレージ制御装置。 - 前記制御部は、ストレージの入出力を制御する入出力コントローラまたは前記入出力コントローラを制御するプロセッサもしくは前記プロセッサに含まれるコアであることを特徴とする請求項1〜4のいずれか一つに記載のストレージ制御装置。

- データの正当性を検証する検証処理を実行可能な複数の制御部を有するストレージ制御装置の制御プログラムであって、

前記複数の制御部のいずれかの制御部に、

前記複数の制御部に含まれる制御部に対応して、実行対象となる検証処理で処理するデータ量と、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とに基づき、前記制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、

特定した前記制御部にかかる負荷を表す指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

処理を実行させることを特徴とする制御プログラム。 - データの正当性を検証する検証処理を実行可能な複数の制御部を有するストレージ制御装置の制御方法であって、

前記複数の制御部のいずれかの制御部が、

前記複数の制御部に含まれる制御部に対応して、実行対象となる検証処理で処理するデータ量と、前記制御部で起動中の前記検証処理で処理するデータ量と前記制御部の使用率とに基づき、前記制御部に対応して、前記検証処理を起動した際に前記制御部にかかる負荷を表す指標値を、前記検証処理で処理するデータ量と前記制御部の使用率との組み合わせに応じて記憶する記憶部の記憶内容を参照することにより、前記実行対象の検証処理を起動した際に前記制御部にかかる負荷を表す指標値を特定し、

特定した前記制御部にかかる負荷を表す指標値に基づいて、前記複数の制御部の中から、前記実行対象の検証処理を起動する起動先の制御部を決定する、

処理を実行することを特徴とする制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013210556A JP6136834B2 (ja) | 2013-10-07 | 2013-10-07 | ストレージ制御装置、制御プログラムおよび制御方法 |

| US14/479,865 US20150100865A1 (en) | 2013-10-07 | 2014-09-08 | Apparatus and method for determining one of control units to perform a verification process on data |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013210556A JP6136834B2 (ja) | 2013-10-07 | 2013-10-07 | ストレージ制御装置、制御プログラムおよび制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015075845A JP2015075845A (ja) | 2015-04-20 |

| JP6136834B2 true JP6136834B2 (ja) | 2017-05-31 |

Family

ID=52777973

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013210556A Expired - Fee Related JP6136834B2 (ja) | 2013-10-07 | 2013-10-07 | ストレージ制御装置、制御プログラムおよび制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20150100865A1 (ja) |

| JP (1) | JP6136834B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016194199A1 (ja) * | 2015-06-04 | 2016-12-08 | 株式会社日立製作所 | ストレージ装置 |

| KR102567224B1 (ko) | 2016-07-25 | 2023-08-16 | 삼성전자주식회사 | 데이터 저장 장치 및 이를 포함하는 컴퓨팅 시스템 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3405244B2 (ja) * | 1998-12-28 | 2003-05-12 | 日本電気株式会社 | データ処理負荷分散システム |

| US7020835B2 (en) * | 2000-10-19 | 2006-03-28 | Oracle International Corporation | Enhancements to data integrity verification mechanism |

| JP4406199B2 (ja) * | 2002-11-19 | 2010-01-27 | 株式会社日立製作所 | プロセッサ負荷制御機能をもつ記憶制御装置 |

| JP2007004456A (ja) * | 2005-06-23 | 2007-01-11 | Toshiba Corp | 携帯可能電子装置及び携帯可能電子装置のデータ出力方法 |

| JP5089896B2 (ja) * | 2006-03-17 | 2012-12-05 | 株式会社日立製作所 | マイクロプロセッサの負荷分散機能を備えたストレージシステム |

| WO2010116538A1 (en) * | 2009-04-06 | 2010-10-14 | Hitachi, Ltd. | Storage apparatus and data transfer method |

| JP5796447B2 (ja) * | 2011-10-07 | 2015-10-21 | 株式会社リコー | 情報処理装置、正当性検証方法、正当性検証プログラム |

| JP5776480B2 (ja) * | 2011-10-07 | 2015-09-09 | 株式会社リコー | 情報処理装置、正当性検証方法、正当性検証プログラム |

-

2013

- 2013-10-07 JP JP2013210556A patent/JP6136834B2/ja not_active Expired - Fee Related

-

2014

- 2014-09-08 US US14/479,865 patent/US20150100865A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015075845A (ja) | 2015-04-20 |

| US20150100865A1 (en) | 2015-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6113028B2 (ja) | インデックス・パーティション内のデータ終端に格納される高解像度テープ・ディレクトリ(hrtd)を利用可能なテープ・ドライブ、方法、及びプログラム | |

| US8856469B2 (en) | Apparatus and method for logging optimization using non-volatile memory | |

| US20150154050A1 (en) | Dependency management in task scheduling | |

| US20100262752A1 (en) | Storage virtual containers | |

| US9053064B2 (en) | Method for saving virtual machine state to a checkpoint file | |

| CN110941456B (zh) | 按需加载动态脚本语言代码以减少内存使用 | |

| KR102777103B1 (ko) | 구역 세그먼트 드라이브 관리 | |

| KR20220125198A (ko) | 데이터의 추가 기록 방법, 장치, 전자 기기, 저장 매체 및 컴퓨터 프로그램매체 | |

| US11210024B2 (en) | Optimizing read-modify-write operations to a storage device by writing a copy of the write data to a shadow block | |

| CN104685443A (zh) | 锁定引导数据用以更快引导 | |

| JP6136834B2 (ja) | ストレージ制御装置、制御プログラムおよび制御方法 | |

| US9158550B2 (en) | Caching based operating system installation | |

| US9933944B2 (en) | Information processing system and control method of information processing system | |

| JP5729479B2 (ja) | 仮想テープ装置及び仮想テープ装置の制御方法 | |

| KR102270789B1 (ko) | 프로세서 및 프로세서의 명령어 처리 방법 | |

| US20130246842A1 (en) | Information processing apparatus, program, and data allocation method | |

| JP6874348B2 (ja) | ストレージ制御装置、およびストレージ制御プログラム | |

| US8276041B2 (en) | Data integrity validation using hierarchical volume management | |

| WO2019221890A1 (en) | Pinning in a multi-tiered system | |

| US8977814B1 (en) | Information lifecycle management for binding content | |

| US11132401B1 (en) | Distributed hash table based logging service | |

| TWI497294B (zh) | 用於增加虛擬記憶體效能之電腦可讀儲存媒體、設備及電腦實施方法 | |

| JP7403465B2 (ja) | 短絡高速化のための複合条件の並べ替え | |

| JP6881847B2 (ja) | ストレージ装置、ファイル特定方法及びプログラム | |

| CN119343677A (zh) | 用于存储器的安全检测的方法、装置、计算机设备 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160606 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170404 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170417 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6136834 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |