以下、本実施の形態について図面を参照して説明する。なお各実施の形態は、矛盾のない範囲で複数の実施の形態を組み合わせて実施することができる。

〔第1の実施の形態〕

まず第1の実施の形態について説明する。第1の実施の形態は、参照先の記憶領域が部分的に重複する複数の変数がある場合でも、テスト対象のプログラムを特定の処理パスで実行させるためのテストデータを、正しく生成するものである。

なお、複数の変数に対する制約条件があるとき、その制約条件を充足する各変数の値は、ソルバによって算出することができる。ソルバは、例えば複数の変数の値を変化させながら、制約条件を充足する各変数の値を導き出すものである。ところが、分岐条件中で比較される変数の表現形式が異なる場合、ソルバにより正しい解を算出することができない。表現形式とは、1桁(数字や文字などの1文字)当たりの情報の表現に用いる形式であり、例えば1桁当たりのビット数が異なる複数の表現形式が存在する。分岐条件中で比較される複数の変数の表現形式が一致していないと、正しい条件判断をすることができず、パス条件を満たすテストデータを正しく生成することもできない。そこで、第1の実施の形態では、分岐条件における表現形式を統一した上で、特定の処理パスを実行させるためのテストデータを正しく生成可能とする。

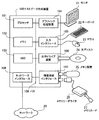

図1は、第1の実施の形態に係るテストデータ生成装置の機能を示すブロック図である。テストデータ生成装置10は、分割手段11、変換手段12、決定手段13、算出手段14、逆変換手段15、および記憶手段16を有する。

分割手段11は、テスト対象プログラムに基づいて実行される処理(処理パス)の中の分岐条件に含まれる複数の変数1により参照される記憶領域を、複数のビット列に分割する。ビット列は、共通の変数ごとに1以上のビット数のビット列としたものである。なお分割手段11は、各ビット列のビット数は、同じであっても、異なっていてもよい。

例えば分割手段11は、所定ビット数のビット列に、記憶領域を均等に分割することができる。このとき分割手段11は、複数の変数1それぞれの表現形式における1要素当たりのビット数の最大公約数を、ビット列のビット数とすることができる。この場合、ある表現形式における1要素当たりのビット数が4ビットであり、他の表現形式における1要素当たりのビット数が4の倍数であれば、分割手段11は、各変数で参照される記憶領域を、4ビットずつのビット列に分割する。このように、ビット列内のビット数を、複数の変数1それぞれの表現形式における1要素当たりのビット数の最大公約数とすることで、同じビット列内の各ビットは、共通の変数から参照されることが保証される。

変換手段12は、制約条件2における条件式の左辺と右辺とにおける要素の表現形式が同じとなるように、少なくとも一方の辺の表現形式を変換する。例えば変換手段12は、条件式の両辺の1要素当たりのビット数が同じとなるように変換した上で、一方の辺のビット列と同じビット数ずつに、他方の辺の値を分割する。これにより、表現形式が異なる変数が混在していても、正しい比較を行う制約条件が生成可能となる。なお、条件式の左辺と右辺とにおける要素の表現形式が元から同じであれば、変換手段12による表現形式の変換処理を省略することができる。変換手段12は、表現形式変換後の制約条件3を、決定手段13に送信する。

決定手段13は、一連の処理を実行させるための複数の変数1に対する制約条件2に基づいて、複数のビット列に対する制約条件4を決定する。例えば、決定手段13は、分岐条件ごとに、その分岐条件に含まれる変数で参照される記憶領域を分割したビット列を用いて、該ビット列に求められる条件を示す論理式4a,4bを生成する。制約条件4として、論理式4a,4bを生成することで、制約条件4を満たす各ビット列の値の算出を、容易にすることができる。

算出手段14は、複数のビット列に対する制約条件4を満たす、複数のビット列それぞれの値を算出する。例えば算出手段14は、決定手段13によって分岐条件ごとに求められた論理式4a,4bのすべてを充足するような、ビット列の値を算出する。なお算出手段14の機能は、例えば制約条件4によって制約された変数の値を算出するソルバ(制約ソルバ)を用いて実現できる。

逆変換手段15は、算出されたビット列ごとの値に基づいて、複数の変数1それぞれの値を算出する。例えば逆変換手段15は、複数の変数1それぞれで参照する記憶領域を分割して得られたビット列の値を、その変数の表現形式に応じた値に変換する。逆変換手段15は、複数の変数1それぞれの値を、テストデータ5として出力する。例えば逆変換手段15は、複数の変数1それぞれの値を、テストデータ5として記憶手段16に格納する。

記憶手段16は、変数で参照される記憶領域の値を、テストデータ5として記憶する。例えば記憶手段16は、逆変換手段15により表現形式が変換された後の値を、テストデータ5として記憶する。なお、表現形式の変換が行われなければ、算出手段14によって算出された各ビット列の値を、テストデータ5として記憶手段16に記憶させてもよい。

このようなテストデータ生成装置10によれば、分割手段11により、複数の変数1で参照される記憶領域を複数のビット列に分割される。このとき、分岐条件における条件式の左辺と右辺との表現形式が異なれば、変換手段12によって、両辺の表現形式が統一される。次に、決定手段13により、複数のビット列に対する制約条件4が決定される。さらに算出手段14により、複数のビット列に対する制約条件4を満たす、複数のビット列それぞれの値が算出される。そして、逆変換手段15により、算出されたビット列ごとの値に基づいて、複数の変数それぞれの値が算出される。算出された値は、テストデータ5として、記憶手段16に格納される。

このようにして、テストデータ5が生成される。生成されたテストデータ5は、ビット列単位で制約条件4が満たされている。第1の実施の形態では、記憶領域を分割したビット列ごとに、そのビット列を参照する変数の制約条件2に基づいた制約条件4が決定されている。しかもビット列内の各ビットは、参照している変数が共通である。そのため、制約条件4を満たすようなビット列ごとの値を算出することで、変数で参照される記憶領域内の各ビットに対して、制約条件4を満たす1つの値を算出することができる。その結果、変数で重複して参照される記憶領域内の個々のビットに対して、複数の異なる値がテストデータ5として算出されることが抑止され、テストする処理パスを確実に実行させることができるテストデータ5が生成される。

また第1の実施の形態では、分岐条件における条件式の左辺と右辺とにおける要素の表現形式が同じとなるように、少なくとも一方の辺の表現形式を変換している。これにより、表現形式の異なる変数が混在していても、正しくテストデータ5を生成することができる。

さらに、ビット列内のビット数を、複数の変数1それぞれの表現形式における1要素当たりのビット数の最大公約数として、記憶領域を均等に分割すれば、生成されるビット列の数を少なく抑えることができる。その結果、テストデータ生成処理の効率化が図れる。すなわち、記憶領域を均等な長さのビット列に分割する場合、1ビットずつのビット列に分割することも可能である。しかし、この場合、ビット列の数が増加してしまい、制約条件4を満たす各ビット列の値を求める際の演算量が増えてしまう。一方、ビット列のビット数が多すぎると、ビット列に含まれる複数のビットそれぞれを参照する変数が、共通とならなくなる可能性がある。そこで、複数の変数1それぞれの表現形式における1要素当たりのビット数の最大公約数分のビット列に、記憶領域を分割すれば、ビット列に含まれる各ビットを参照する変数が共通となることを保証できる。しかも、1ビット単位に分けてしまう場合に比べ、生成されるビット列の数を減らすことができ、テストデータ5の生成を効率的に行うことができる。

なお、分割手段11、変換手段12、決定手段13、算出手段14、および逆変換手段15は、例えばテストデータ生成装置10が有するプロセッサにより実現することができる。また、記憶手段16は、例えばテストデータ生成装置10が有するメモリなどの記憶媒体により実現することができる。

また、図1に示した各要素間を接続する線は通信経路の一部を示すものであり、図示した通信経路以外の通信経路も設定可能である。

〔第2の実施の形態〕

次に第2の実施の形態について説明する。第2の実施の形態は、COBOL(COmmon Business Oriented Language)で記述されたプログラムのテストデータを生成する例である。

図2は、第2の実施の形態のシステム構成例を示す図である。テストデータ生成装置100は、テスト装置30に接続されている。テストデータ生成装置100は、テスト対象のプログラムのテストに使用するテストデータを生成する。例えばテストデータ生成装置100では、プログラムで実行可能な特定の処理パスを実行させるためのテストデータを生成する。そして、テストデータ生成装置100で生成されたテストデータを変数に設定して、テスト装置30にプログラムを実行させることにより、特定の処理パスのテストを実行することができる。

図3は、本実施の形態に用いるテストデータ生成装置のハードウェアの一構成例を示す図である。テストデータ生成装置100は、プロセッサ101によって装置全体が制御されている。プロセッサ101には、バス109を介してメモリ102と複数の周辺機器が接続されている。プロセッサ101は、マルチプロセッサであってもよい。プロセッサ101は、例えばCPU(Central Processing Unit)、MPU(Micro Processing Unit)、またはDSP(Digital Signal Processor)である。プロセッサ101の機能の少なくとも一部を、ASIC(Application Specific Integrated Circuit)、PLD(Programmable Logic Device)などの電子回路で実現してもよい。

メモリ102は、テストデータ生成装置100の主記憶装置として使用される。メモリ102には、プロセッサ101に実行させるOS(Operating System)のプログラムやアプリケーションプログラムの少なくとも一部が一時的に格納される。また、メモリ102には、プロセッサ101による処理に必要な各種データが格納される。メモリ102としては、例えばRAM(Random Access Memory)などの揮発性の半導体記憶装置が使用される。

バス109に接続されている周辺機器としては、HDD(Hard Disk Drive)103、グラフィック処理装置104、入力インタフェース105、光学ドライブ装置106、機器接続インタフェース107およびネットワークインタフェース108がある。

HDD103は、内蔵したディスクに対して、磁気的にデータの書き込みおよび読み出しを行う。HDD103は、テストデータ生成装置100の補助記憶装置として使用される。HDD103には、OSのプログラム、アプリケーションプログラム、および各種データが格納される。なお、補助記憶装置としては、フラッシュメモリなどの不揮発性の半導体記憶装置を使用することもできる。

グラフィック処理装置104には、モニタ21が接続されている。グラフィック処理装置104は、プロセッサ101からの命令に従って、画像をモニタ21の画面に表示させる。モニタ21としては、CRT(Cathode Ray Tube)を用いた表示装置や液晶表示装置などがある。

入力インタフェース105には、キーボード22とマウス23とが接続されている。入力インタフェース105は、キーボード22やマウス23から送られてくる信号をプロセッサ101に送信する。なお、マウス23は、ポインティングデバイスの一例であり、他のポインティングデバイスを使用することもできる。他のポインティングデバイスとしては、タッチパネル、タブレット、タッチパッド、トラックボールなどがある。

光学ドライブ装置106は、レーザ光などを利用して、光ディスク24に記録されたデータの読み取りを行う。光ディスク24は、光の反射によって読み取り可能なようにデータが記録された可搬型の記録媒体である。光ディスク24には、DVD(Digital Versatile Disc)、DVD−RAM、CD−ROM(Compact Disc Read Only Memory)、CD−R(Recordable)/RW(ReWritable)などがある。

機器接続インタフェース107は、テストデータ生成装置100に周辺機器を接続するための通信インタフェースである。例えば機器接続インタフェース107には、メモリ装置25やメモリリーダライタ26を接続することができる。メモリ装置25は、機器接続インタフェース107との通信機能を搭載した記録媒体である。メモリリーダライタ26は、メモリカード27へのデータの書き込み、またはメモリカード27からのデータの読み出しを行う装置である。メモリカード27は、カード型の記録媒体である。

ネットワークインタフェース108は、ネットワーク20に接続されている。ネットワークインタフェース108は、ネットワーク20を介して、テスト装置30との間でデータの送受信を行う。

以上のようなハードウェア構成によって、第2の実施の形態の処理機能を実現することができる。なお、第1の実施の形態に示したテストデータ生成装置10も、図3に示したテストデータ生成装置100と同様のハードウェアにより実現することができる。

テストデータ生成装置100は、例えばコンピュータ読み取り可能な記録媒体に記録されたプログラムを実行することにより、第2の実施の形態の処理機能を実現する。テストデータ生成装置100に実行させる処理内容を記述したプログラムは、様々な記録媒体に記録しておくことができる。例えば、テストデータ生成装置100に実行させるプログラムをHDD103に格納しておくことができる。プロセッサ101は、HDD103内のプログラムの少なくとも一部をメモリ102にロードし、プログラムを実行する。またテストデータ生成装置100に実行させるプログラムを、光ディスク24、メモリ装置25、メモリカード27などの可搬型記録媒体に記録しておくこともできる。可搬型記録媒体に格納されたプログラムは、例えばプロセッサ101からの制御により、HDD103にインストールされた後、実行可能となる。またプロセッサ101が、可搬型記録媒体から直接プログラムを読み出して実行することもできる。

次に、COBOLを例に採り、テストデータ生成における課題について説明する。

図4は、テスト対象のプログラムの一例を示す図である。プログラム31では、行番号「00070」の行から行番号「00140」の行までに、入力変数のデータ構造が定義されている。また行番号「00180」の行から行番号「00330」の行までに、複数の分岐条件を含む処理手順が示されている。

なお、COBOLでは、変数がデータ項目と呼ばれる。図4に示したプログラム31のデータ構造は、データ項目表で表すことができる。

図5は、データ項目表の一例を示す図である。データ項目表32には、レベル、項目名、型、REDEFINES(参照先)、表現形式、およびバイト数の欄が設けられている。

レベルの欄には、データ項目のレベルが設定される。データ項目のレベルは、「1」が最も高い。高いレベルのデータ項目の下に、低いレベルの複数のデータ項目が設定されている場合、高いレベルのデータ項目内に、低いレベルの複数のデータ項目が順番に配置されていることを意味する。

項目名の欄には、データ項目の項目名が設定される。

型の欄には、データ項目の型が設定される。型の「9」は数値、「N」は日本語であることを示す。型の括弧内の数字は、何個の文字が入るかを示す。

REDEFINES(参照先)の欄には、同じレベルの他のデータ項目と同じメモリ領域を参照する場合の、参照先が設定される。例えば図5の例では、項目名「年月日−R」のデータ項目は、項目名「年月日」のデータ項目と同じメモリ領域を参照している。

表現形式の欄には、データ項目の1桁(数字または文字の1字)を表現するのに用いられるビット数が設定される。なお、第2の実施の形態における1桁は、第1の実施の形態における1要素の一例である。

バイト数の欄には、データ項目のデータ長がバイト数で設定される。なお、バイト数は、型の括弧内に示されている文字数と、表現形式(1文字当たりのビット数)から算出できる。

このようなデータ項目を有する、COBOL言語で記述されたプログラム31には、以下のような特徴がある。

(1)入力変数(データ項目)には集団項目というデータ構造が用いられる。図5の例では「項目G」の配下には4つのデータ項目(年月日と年月日−R、時刻、頭文字)がある。

(2)同じメモリ位置に対して別のデータ項目の宣言が可能である。図5の例では、データ項目「年月日−R」は、データ項目「年月日」と同じメモリ位置を参照している。

(3)メモリ上での表現形式によって1桁当たりのバイト数が異なる。図5の例では、データ項目「年月日」は1桁の値が8ビットで表現される。データ項目「時刻」は、1桁の値が4ビットで表現される。データ項目「頭文字」は、1桁の値が16ビットで表現される。

図6は、表現形式の一例を示す図である。COBOLでは、1桁の値が4ビットで表現できるデータ項目(例えばデータ項目の「時刻」)場合、メモリ上の領域4ビットごとに数値が入っている。1桁の値が8ビットで表現できるデータ項目(例えばデータ項目「年−R」)の場合は、メモリ上の8ビットの領域に文字コードが入る。1桁の値が16ビットで表現できるデータ項目(例えばデータ項目「頭文字」)の場合は、メモリ上の16ビットの領域に文字コードが入る。文字コードの形式はプログラムを動作させるホスト(例えばテスト装置30)により異なるが、以下の説明ではJISコードを想定する。

このようなデータ項目を有するプログラム31に対して、所定のパスの処理をテストすることを目的として、テストデータを生成するものとする。

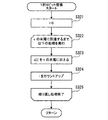

図7は、テストする処理パスの一例を示す図である。図7では、プログラム31に基づいて、テスト装置30が実行する処理の手順がフローチャートで示されている。

[ステップS11]テスト装置30は、データ項目「項目G」の入力を受け付ける。

[ステップS12]テスト装置30は、データ項目「項目G」が入力されると、まず、データ項目「年月日」の値が「20001231」ではないことの真偽を判定する。データ項目「年月日」の値が「20001231」でなければ(ステップS12が「真」)処理がステップS13に進められる。データ項目「年月日」の値が「20001231」であれば(ステップS12が「偽」)処理が終了する。

[ステップS13]テスト装置30は、データ項目「年月日」の値が「20001231」でなければ、データ項目「月−R」の値が「12」以下であることの真偽を判定する。データ項目「月−R」の値が「12」以下であれば(ステップS13が「真」)処理がステップS14に進められる。データ項目「月−R」の値が「12」以下でなければ(ステップS13が「偽」)処理が終了する。

[ステップS14]テスト装置30は、データ項目「月−R」の値が「12」以下であれば、データ項目「時刻」の値が「0000」であることの真偽を判定する。データ項目「時刻」の値が「0000」であれば(ステップS14が「真」)処理がステップS15に進められる。データ項目「時刻」の値が「0000」でなければ(ステップS14が「偽」)処理が終了する。

[ステップS15]テスト装置30は、データ項目「時刻」の値が「0000」であれば、データ項目「年−R」の値がデータ項目「時刻」の値より大きいことの真偽を判定する。データ項目「年−R」の値の方が大きければ(ステップS15が「真」)処理がステップS16に進められる。値が同じか、データ項目「年−R」の値の方が小さければ(ステップS15が「偽」)処理が終了する。

[ステップS16]テスト装置30は、データ項目「年−R」の値がデータ項目「時刻」の値より大きければ、データ項目「頭文字」の値が空白ではないことの真偽を判定する。データ項目「頭文字」の値が空白でなければ(ステップS16が「真」)処理がステップS17に進められる。データ項目「頭文字」の値が空白であれば(ステップS16が「偽」)処理が終了する。

[ステップS17]テスト装置30は、データ項目「頭文字」の値が空白でなければ、「受付処理を実行しました」のメッセージを表示して、処理を終了する。

このような処理のうち、例えばすべての分岐条件において「真」と判定される処理パス33をテストする場合を想定する。この場合、まずプログラム31に基づいて、処理パス33のパス条件が導出される。そして、パス条件を満たすテストデータが生成される。第2の実施の形態では、テストデータの生成に際し、参照先となるメモリ領域が重複する複数のデータ項目を考慮してテストデータが生成される。このような考慮をせずにテストデータを生成すると、テストしたいパス条件を満たさないテストデータが生成される可能性がある。

以下、図8、図9を参照して、参照先となるメモリ領域が重複する複数のデータ項目の存在を考慮しなかった場合に生じる問題について説明する。

図8は、参照先となるメモリ領域が重複する複数のデータ項目の存在を考慮せずに生成したテストデータの一例を示す図である。テスト対象のプログラム31に基づいて、テストしたい処理パス33のパス条件34が導出されている。パス条件34は、プログラム31の5つの分岐条件をすべて真とする条件である。

図8の例では、パス条件34に基づいて、「月−R」「年月日」という別々のデータ項目から重複して参照されているメモリ位置に対し、異なる複数のテストデータ35を生成している。テスト実施者が、テストデータ35を入力してプログラム31を実行すると、データ項目「年月日」のメモリ領域36には、「20009931」と入力するか、あるいは「20001231」と入力することとなる。この場合、メモリ領域36にいずれの値が入力されたとしても、テスト実施者がテストしたい処理パス33とは異なる処理パスが実行されてしまう。

図9は、図8のテストデータに基づいて実行される処理パスの一例を示す図である。例えば、複数のデータ項目で重複して参照されるメモリ領域36に「20001231」と設定し、プログラム31をテストした場合、ステップS12で「偽」と判定される。その結果、テストしたい処理パス33とは別の処理パス37が実行される。また、メモリ領域36に「20009931」と設定し、プログラム31をテストした場合、ステップS13で「偽」と判定される。その結果、テストしたい処理パス33とは別の処理パス38が実行される。

このように、同じメモリ領域を複数のデータ項目で参照していることを考慮せずに、個々のデータ項目ごとに、パス条件34を満たすテストデータを生成しても、テストしたい処理パス33を実行させることができないことがある。そこで、第2の実施の形態におけるテストデータ生成装置100では、すべてのデータ項目を4ビットずつに分割する。さらにテストデータ生成装置100は、4ビットずつのビット列をシンボルとし、そのシンボルごとにシンボル名を定義する。そしてテストデータ生成装置100は、シンボル名ごとに、パス条件34を満たす値を求める。

なお、シンボルに対応する値と分岐条件とを対比する際には、内部表現を合わせないと、正しく比較することができない。例えば、図6に示した1桁8ビットのデータ項目「年−R」には、「01000001」という値が設定されている。この値を元の内部表現のまま解釈すれば、「65」(10進数表現)という値となる。これは、半角の文字「A」の文字コードである。この8ビットの値を4ビットずつに区切ると、「4」と「1」となる。このような値のまま、文字コードに関する分岐条件と比較しても、所望の分岐をさせるためのテストデータを正しく得ることはできない。そこでテストデータ生成装置100では、内部表現を合わせた上で、パス条件に合致するシンボル名の値が求める。

以下、第2の実施の形態におけるテストデータ生成装置100の機能について、具体的に説明する。

図10は、テストデータ生成装置の機能の一例を示す図である。テストデータ生成装置100は、入力データ記憶部110、シンボル初期化部121、シンボル記憶部122、シンボル置換部123、表現形式変換部124、論理式生成部125、ソルバ実行部126、充足解記憶部127、シンボル逆置換部128、およびテストデータ記憶部130を有する。

入力データ記憶部110は、テストデータの生成のために入力されるデータを記憶する。例えば入力データ記憶部110には、データ項目表32とパス条件34が格納される。入力データ記憶部110としては、例えばメモリ102やHDD103の記憶領域の一部が用いられる。

シンボル初期化部121は、各データ項目の指すメモリ領域に、所定数のビット単位のシンボルを生成し、各シンボルにシンボル名を割り当てる。データ項目によってメモリ102上での表現方法が異なるので、1桁当たりに割り当てられるシンボル数は、データ項目の長さに応じて変わる。第2の実施の形態では、シンボル初期化部121は、4ビット単位のシンボルにシンボル名を割り当てる。

シンボル記憶部122は、シンボル初期化部121によって生成されたシンボルを記憶する。例えばシンボル記憶部122は、メモリ領域に対応付けて、シンボルを記憶する。シンボル記憶部122としては、例えばメモリ102またはHDD103の記憶領域の一部が使用される。

シンボル置換部123は、パス条件34に登場するデータ項目に対応するメモリ領域のシンボル列を、シンボル記憶部122から取得する。そしてシンボル置換部123は、パス条件34中のデータ項目をすべてシンボル列に書き換える。

表現形式変換部124は、条件文の左右両辺でデータ項目の表現形式(1桁当たりのビット数)が異なる場合に、両辺が同等の表現となるように、データ項目の表現形式を変換する。

論理式生成部125は、パス条件34に基づいて、ソルバに入力する論理式を生成する。例えば論理式生成部125は、メモリ領域を重複して参照する複数のデータ項目がある場合には、所定ビット数ごとのシンボルごとの値を求める論理式を生成する。また論理式生成部125は、メモリ領域を重複して参照する複数のデータ項目がない場合は、入力データ記憶部110に設定されているデータ項目ごとの値を求める論理式を生成してもよい。

ソルバ実行部126は、論理式生成部125で生成された論理式を従属する解を算出する。ソルバ実行部126は、算出した解を充足解記憶部127に格納する。

充足解記憶部127は、論理式を充足する解を記憶する。例えばメモリ102やHDD103の記憶領域の一部が、充足解記憶部127として使用される。

シンボル逆置換部128は、ソルバ実行部126により得られた、シンボル列に対する解を、入力変数に対する入力値へと変換する。例えばシンボル逆置換部128は、各シンボル列に対応する変数の表現形式に応じて、変換を行う。そしてシンボル逆置換部128は、入力変数のデータ項目ごとに得られた入力値を、テストデータとしてテストデータ記憶部130に格納する。

テストデータ記憶部130は、生成されたテストデータを記憶する。例えばメモリ102やHDD103の記憶領域の一部がテストデータ記憶部130として使用される。

なお、図10に示した各要素間を接続する線は通信経路の一部を示すものであり、図示した通信経路以外の通信経路も設定可能である。また図10に示したシンボル初期化部121およびシンボル置換部123は、図1に示した第1の実施の形態における分割手段11の一例である。図10に示した表現形式変換部124は、図1に示した第1の実施の形態における変換手段12の一例である。図10に示した論理式生成部125は、図1に示した第1の実施の形態における決定手段13の一例である。図10に示したソルバ実行部126は、図1に示した第1の実施の形態における算出手段14の一例である。図10に示したシンボル逆置換部128は、図1に示した第1の実施の形態における逆変換手段15の一例である。

このような機能を有するテストデータ生成装置100により、例えばプログラム31の処理パス33のテストを行うためのテストデータを生成することができる。

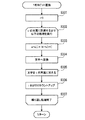

図11は、テストデータ生成処理の手順を示すフローチャートである。以下の処理は、例えば入力データ記憶部110内のデータ項目表32とパス条件34とを指定したテストデータ生成指示が入力された場合に実行される。

[ステップS101]シンボル初期化部121は、入力データ記憶部110からデータ項目表32とパス条件34を取得する。

[ステップS102]シンボル初期化部121は、データ項目の参照先のメモリ領域を複数のシンボルに分け、そのシンボルを初期化する。シンボル初期化部121は、初期化したシンボルをシンボル記憶部122に格納する。シンボル初期化部121は、シンボル初期化処理が終了すると、例えばシンボル置換部123に、シンボル初期化終了を通知する。シンボル初期化処理の詳細は後述する(図12、図13、図14参照)。

[ステップS103]シンボル置換部123は、シンボル初期化部121によるシンボル初期化処理が終了すると、シンボル記憶部122に記憶されたシンボルに基づいて、パス条件34中に記載されたデータ項目をシンボルに置換する。シンボル置換部123は、データ項目がシンボルに置換されたパス条件を、表現形式変換部124に送信する。シンボル置換処理の詳細は後述する(図15、図16参照)。

[ステップS104]表現形式変換部124は、パス条件中の各分岐条件について、左辺と右辺との表現形式が同等となるように、左辺または右辺の表現形式を変換する。そして、表現形式変換部124は、表現形式変換後のパス条件を、論理式生成部125に送信する。表現形式変換処理の詳細は後述する(図17〜図26参照)。

[ステップS105]論理式生成部125は、左辺と右辺との表現形式が統一された分岐条件に基づいて、各シンボルに関する制約条件を示す論理式を生成する。論理式生成部125は、生成した論理式をソルバ実行部126に送信する。論理式生成処理の詳細は、後述する(図27、図28参照)。

[ステップS106]ソルバ実行部126は、論理式を解くためのソルバを実行し、論理式の条件を充足する解を算出する。ソルバ実行部126は、得られた解を充足解記憶部127に格納する。

[ステップS107]シンボル逆置換部128は、充足解記憶部127に格納されたシンボルごとの値を、データ項目の値に置き換える。シンボル逆置換処理の詳細は後述する(図29〜図33参照)。

[ステップS108]シンボル逆置換部128は、データ項目ごとの解を、テストデータとしてテストデータ記憶部130に格納する。

以上のような手順でテストデータが生成される。以下、テストデータ生成処理を、さらに詳細に説明する。

まず、シンボル初期化処理について詳細に説明する。

図12は、シンボル初期化の一例を示す図である。シンボル初期化処理では、データ項目表32に基づいてシンボルが生成され、生成されたシンボルがシンボルテーブル41に設定される。なおデータ項目表32の内容は、図5に示した通りであるものとする。

シンボルテーブル41には、メモリ領域、シンボル、及び項目名が関連付けて登録されている。ここで、図5に示したデータ項目表32におけるレベル「1」のデータ項目「項目G」を、複数のシンボルに分割する場合を考える。データ項目「項目G」のバイト数は、12バイトである。12バイトが4ビットずつに分けられ、4ビットずつのビット列それぞれがシンボルとなる。そこで、12バイトのメモリ領域に対応付けて、24個のシンボルが生成される。図12に示すシンボルテーブル41では、24個のシンボルのシンボル名を「S1」〜「S24」としている。そしてシンボル「S1」〜「S24」の範囲のメモリ領域に対応付けて、データ項目「項目G」が設定されている。

ここで、データ項目の表現形式が1桁8ビットの項目であった場合、割り当てられた各シンボルには、文字コードの上位4ビットもしくは下位4ビットの値が入力される。データ項目の表現形式が1桁16ビットの項目であった場合、割り当てられた各シンボルには、文字コードの16ビットのうちの連続する4ビットの値が入力される。例えば、データ項目に割り当てられた4つのシンボルに、上位4ビット(第1〜第4ビット)、上位から2番目の4ビット(第5〜第8ビット)、上位から3番目の4ビット(第9〜第12ビット)、下位4ビット(第13〜第16ビット)の値が入力される。データ項目の表現形式が1桁4ビットであった場合、割り当てられた各シンボルには、そのデータ項目の数値が直接入力される。

例えばデータ項目「年月日」の表現形式は1桁8ビットであるが、シンボルは4ビットごとに割り当てが行われる。そのためデータ項目「年月日」には、1桁に対して2つのシンボルが割り当てられる。その結果、8桁であるデータ項目「年月日」には、シンボルテーブル上で「S1」から「S16」まで、計16個のシンボルが割り当てられている。同様に、データ項目「年月日−R」にも16個のシンボルを割り当てるが、データ項目「年月日−R」は「年月日」を再定義している項目であり、「年月日」と同じメモリ領域を参照している。そのためデータ項目「年月日−R」には、データ項目「年月日」と同じシンボル「S1」から「S16」が割り当てられている。集団項目「年月日−R」を構成する下位のデータ項目「年−R」・「月−R」・「日−R」は、データ項目「年月日−R」内のメモリ領域を参照するものである。そのためデータ項目「年−R」・「月−R」・「日−R」それぞれには、データ項目「年月日−R」に割り当てたシンボルの中から、それぞれの位置と長さに応じてシンボルが割り当てられている。例えば「年−R」は「年月日−R」の先頭4桁を指すので、「年月日−R」先頭4桁に該当する「S1」から「S8」が割り当てられている。

データ項目「時刻」の表現形式は、1桁4ビットである。そのためデータ項目「時刻」には、1桁に対して1つのシンボルが割り当てられる。その結果、4桁であるデータ項目「時刻」には、シンボルテーブル上で「S17」から「S20」まで、計4個のシンボルが割り当てられている。

データ項目「頭文字」の表現形式は、1桁16ビットである。そのためデータ項目「頭文字」には、1桁に対して4つのシンボルが割り当てられる。その結果、4桁であるデータ項目「頭文字」には、シンボルテーブル上で「S21」から「S24」まで、計4個のシンボルが割り当てられている。

このようなシンボルテーブル41が、シンボル記憶部122に格納される。以下、シンボル初期化処理の手順について詳細に説明する。

図13は、シンボル初期化処理の手順の一例を示すフローチャートである。

[ステップS111]シンボル初期化部121は、シンボルテーブル41を初期化する。例えば、シンボル初期化部121は、レベル「1」のデータ項目のデータ量に応じたサイズのシンボルテーブル41を生成する。

[ステップS112]シンボル初期化部121は、データ項目表32から、各データ項目のレベルを取得する。

[ステップS113]シンボル初期化部121は、レベル「1」のすべてのデータ項目に対して、ステップS114の処理を実行する。

[ステップS114]シンボル初期化部121は、レベル「1」のデータ項目(di)を引数として、初期化再帰処理を実行する。初期化再帰処理の詳細は後述する(図14参照)。

[ステップS115]シンボル初期化部121は、レベル「1」のすべてのデータ項目についてステップS114の処理が終了した場合、シンボル初期化処理を終了する。

図14は、初期化再帰処理の手順の一例を示すフローチャートである。初期化再帰処理は、図13のステップS114で実行されるか、あるいは図14に示す初期化再帰処理のステップS128で再帰的に実行される。なお初期化再帰処理は、ステップS114で実行される場合、レベル「1」のデータ項目が引数に設定されるが、ステップS128で再帰的に実行される場合、レベルが2以降のデータ項目が引数に設定される。

[ステップS121]シンボル初期化部121は、引数として設定されたデータ項目(di)のメモリ上のオフセットiと長さlを計算する。

[ステップS122]シンボル初期化部121は、引数として設定されたデータ項目(di)が、再定義項目か否かを判断する。再定義項目とは、同じメモリ領域を参照する他のデータ項目が、先に定義されているようなデータ項目である。図5の例では、「REDEFINES」の欄に参照先が設定されているデータ項目「年月日−R」が、再定義項目である。再定義項目であれば、処理がステップS126に進められる。再定義項目でなければ、処理がステップS123に進められる。

[ステップS123]シンボル初期化部121は、引数として設定されたデータ項目(di)の上位のレベルの項目があるか否かを判断する。例えばデータ項目表32において、引数として設定されたデータ項目(di)より上に、そのデータ項目より上位のレベルのデータ項目があれば、上位のレベルの項目ありと判断される。上位のレベルの項目がある場合、処理がステップS126に進められる。上位のレベルの項目がなければ、処理がステップS124に進められる。

[ステップS124]シンボル初期化部121は、引数として設定されたデータ項目(di)に対して割り当てられているメモリ領域分のシンボルを生成する。例えば、図5に示すデータ項目「項目G」が引数として設定された場合、12バイト分の24個のシンボルが生成される。

[ステップS125]シンボル初期化部121は、生成したシンボルを、シンボルテーブル41に追加する。例えばシンボル初期化部121は、シンボルテーブル41内の4ビットずつのメモリ領域に対応付けて、シンボル名を登録する。

[ステップS126]シンボル初期化部121は、引数として設定されたデータ項目(di)をシンボルテーブル41にマッピングする。例えばシンボル初期化部121は、レベル「1」のデータ項目「項目G」中の、データ項目(di)の範囲を判断する。例えばデータ項目「項目G」の先頭からの、データ項目(di)の先頭までのオフセットiと、データ項目(di)の長さlに基づいて、データ項目「項目G」中のデータ項目(di)の範囲を判断する。そしてシンボル初期化部121は、その範囲に対応するシンボルに対応付けて、データ項目(di)の項目名をシンボルテーブルに設定する。

[ステップS127]シンボル初期化部121は、引数として設定されたデータ項目(di)の下位のデータ項目(child)のすべてについて、ステップS128の処理を実行する。

[ステップS128]シンボル初期化部121は、データ項目(di)の下位のデータ項目(child)を引数として、初期化再帰処理を再帰的に実行する。

[ステップS129]シンボル初期化部121は、データ項目(di)の下位のデータ項目(child)すべてについて初期化再帰処理が終了したら、データ項目(di)について実行している初期化再帰処理を終了する。

以上のようにして、シンボルテーブル41が作成される。

次に、シンボル置換処理について詳細に説明する。

図15は、シンボル置換の一例を示す図である。シンボル置換部123は、パス条件34のデータ項目をシンボルに置換することで、データ項目について規定したパス条件34を、シンボルについて規定したパス条件42へ変換する。このシンボルの置換は、パス条件34とシンボルテーブル41に基づいて行われる。なお図15に示すパス条件34は、そのパス条件34に含まれる個々の分岐条件について、左辺、右辺、および演算子に分けて示されている。個々の分岐条件で「真」となることが、パス条件34である。またシンボルテーブル41の内容は、図12に示した通りであるものとする。

シンボル置換部123は、シンボルテーブル41を参照し、パス条件34に含まれる各分岐条件の左辺に示されているデータ項目を、シンボルに置き換える。例えばパス条件34の1行目にはデータ項目「年月日」が登場する。データ項目「年月日」には、シンボルテーブル41(図12参照)上で、「S1」から「S16」までのシンボルが割り当てられている。そこで、シンボルに関するパス条件42では、データ項目「年月日」が、「S1,S2,S3,S4,S5,S6,S7,S8,S9,S10,S11,S12,S13,S14,S15,S16」というシンボル名の列に置き換えられている。

図16は、シンボル置換処理の手順の一例を示すフローチャートである。この処理は、例えばシンボル置換部123が、シンボル初期化部121からシンボル初期化処理が終了したことを示す通知を受けたときに実行する。

[ステップS131]シンボル置換部123は、データ項目に関して規定したパス条件34のすべてに対して、ステップS132〜S136の処理を実行する。

[ステップS132]シンボル置換部123は、パス条件34中のデータ項目を探索する。

[ステップS133]シンボル置換部123は、パス条件34中に現れるすべてのデータ項目(di)について、ステップS134〜S135の処理を実行する。

[ステップS134]シンボル置換部123は、シンボルテーブル41から、データ項目(di)に対応するシンボル名の列slを取得する。

[ステップS135]シンボル置換部123は、パス条件34のデータ項目(di)のデータ項目名を、ステップS134で取得したシンボル名の列slに置換する。

[ステップS136]シンボル置換部123は、処理対象のパス条件34に現れるすべてのデータ項目についてシンボル名の列への置換が終了した場合、処理をステップS137に進める。

[ステップS137]シンボル置換部123は、すべてのパス条件について、データ項目からシンボルへの置換処理が終了した場合、シンボル置換処理を終了する。

このようにして、シンボルについて規定したパス条件42が生成される。

次に、表現形式変換処理について説明する。

図17は、表現形式変換の一例を示す図である。表現形式変換部124は、シンボルに関するパス条件42に含まれる各分岐条件の左辺と右辺を、左右で同じ表現形式となるように、表現形式を変換する。例えば、パス条件42の1行目では、左辺が1桁8ビットのデータ項目に割り当てられた16個のシンボル列である。右辺は8ビット単位の8桁の数値リテラルである。なおリテラルとは、プログラム中で使用される値を直接表記したものである。リテラルには、数値、文字列などがある。分岐条件の左右両辺の表現形式が異なると、ソルバにより充足解が求められない。そのためパス条件42の1行目は、右辺のリテラルが、文字コード列が以下のように変換される。

(50≫4),(50&15),(48≫4),(48&15),(48≫4),(48&15),(48≫4),(48&15)、(49≫4),(49&15),(50≫4),(50&15),(51≫4),(51&15),(49≫4),(49&15)

これにより、左右が同等の表現となる。

なお、「x≫4」は、8ビットのxの上位4ビットの値を得る式である(xは0以上の整数)。演算子「≫」は、ビット単位の右シフトを意味しており、この演算子の左の値がシフト対象であり、右の数値がシフトさせるビット数である。xが8ビットのときに「x≫4」の演算を行うことにより、xの上位4ビットののみが残される。例えば「50≫4」は、文字「2」(文字コードの10進数表記「50」)を表す8ビットの文字コードの上位4ビットを示す。

「x&15」は、xの下4ビットの値を得る式である。演算子「&」は、左右の値の論理積を意味している。xと15(2進数表記で「1111」)との論理積を求めることで、xの下位4ビットの値が得られる。「50&15」は、文字「2」を表す8ビットの文字コードの下位4ビットを示す。

パス条件42の2行目は、1行目と同様に、右辺が8ビット単位のリテラルである。そのため、右辺の各桁が、上位4ビットと下位4ビットとに分けられる。

パス条件42の3行目の左辺は1桁4ビットのデータ項目に割り当てられた4個のシンボル列であり、右辺は1桁4ビットの数値リテラルである。この場合、両辺とも4ビットの数値同士となるため、表現形式の変換は行われない。

パス条件42の4行目は、左辺が1桁8ビットのデータ項目に割り当てられた8個のシンボル列である。右辺は1桁4ビットのデータ項目(数値)に割り当てられた4個のシンボル列である。この場合、右辺の数値を表すデータ項目を、その数値を示す8ビットの文字コードに変換した上で、4ビットずつの値に分割される。なお文字コードがJISコードであれば、数値を示す値に「48」を加算することで、その数値を示す文字コードに変換できる。例えば右辺のシンボル「S17」は、「(S17+48)≫4,(S17+48)&15」に変換される。

パス条件42の5行目は、左辺が1桁16ビットのデータ項目に割り当てられた4個のシンボル列である。右辺は16ビットの文字リテラルである。そこで、右辺の値が、上位4ビット(第1ビットから第4ビット)、続く4ビット(第5ビットから第8ビット、さらに続く4ビット(第9ビットから第12ビット)、および下位4ビット(第13ビットから第16ビットに分割される。例えば右辺の値は、「(8481≫12),(8481&4095≫8),(8481&255≫4),(8481&15)」となる。なお「8481&4095≫8」は、16ビット中の下位12ビットを取り出し、右に8ビットシフトすることを示している。これにより、元の16ビットの値から、下位12ビットの内の上位4ビット(元の16ビット中の第4ビットから第8ビット)が抽出できる。

図18は、表現形式変換処理の手順の一例を示すフローチャートの前半である。

[ステップS141]表現形式変換部124は、パス条件に含まれるすべての分岐条件に対して、ステップS142〜S154(図19参照)の処理を実行する。

[ステップS142]表現形式変換部124は、シンボルテーブル41から、シンボルに対応するデータ項目を探索する。

[ステップS143]表現形式変換部124は、データ項目表32から左右両辺のデータ項目の表現形式を探索する。

[ステップS144]表現形式変換部124は、左辺と右辺の表現形式の組み合わせを判断する。リテラルと1桁8ビットのデータ項目のシンボル列との組み合わせであれば、処理がステップS145に進められる。リテラルと1桁16ビットのデータ項目のシンボル列との組み合わせであれば、処理がステップS146に進められる。1桁4ビットのデータ項目のシンボル列と1桁8ビットのデータ項目のシンボル列との組み合わせであれば、処理がステップS147に進められる。1桁4ビットのデータ項目のシンボル列と1桁16ビットのデータ項目のシンボル列との組み合わせであれば、処理がステップS148に進められる。1桁8ビットのデータ項目のシンボル列と1桁16ビットのデータ項目のシンボル列との組み合わせであれば、処理がステップS149に進められる。その他の組み合わせの場合、処理がステップS150(図19参照)に進められる。

[ステップS145]リテラルと1桁8ビットのデータ項目のシンボル列との組み合わせの場合、表現形式変換部124は、リテラルの1桁8ビット形式変換処理を行う。この処理の詳細は後述する(図20参照)。その後、処理がステップS150に進められる。

[ステップS146]リテラルと1桁16ビットのデータ項目のシンボル列との組み合わせの場合、リテラルの1桁16ビット形式変換処理が行われる。この処理の詳細は後述する(図21参照)。その後、処理がステップS150に進められる。

[ステップS147]1桁4ビットのデータ項目のシンボル列と1桁8ビットのデータ項目のシンボル列との組み合わせの場合、表現形式変換部124は、1桁4ビットデータ項目の1桁8ビット形式変換処理を行う。この処理の詳細は後述する(図22参照)。その後、処理がステップS150に進められる。

[ステップS148]1桁4ビットのデータ項目のシンボル列と1桁16ビットのデータ項目のシンボル列との組み合わせの場合、表現形式変換部124は、1桁4ビットデータ項目の1桁16ビット形式変換処理を行う。この処理の詳細は後述する(図23参照)。その後、処理がステップS150に進められる。

[ステップS149]1桁8ビットのデータ項目のシンボル列と1桁16ビットのデータ項目のシンボル列との組み合わせの場合、表現形式変換部124は、1桁8ビットデータ項目の1桁16ビット形式変換処理を行う。この処理の詳細は後述する(図24参照)。

図19は、表現形式変換処理の手順の一例を示すフローチャートの後半である。

[ステップS150]表現形式変換部124は、パス条件42における変換を行ったデータ項目(左辺または右辺)を、変換後の内容に更新する。

[ステップS151]表現形式変換部124は、左辺と右辺との桁数が異なるか否かを判断する。桁数が異なる場合、処理がステップS152に進められる。桁数が同じであれば、処理がステップS155に進められる。

[ステップS152]表現形式変換部124は、左辺か右辺のいずれかが、1桁16ビッのデータ項目か否かが判断される。何れか一方が1桁16ビットのデータ項目であれば、処理がステップS154に進められる。左辺と右辺とが、1桁4ビットまたは8ビットのデータ項目であれば、処理がステップS153に進められる。

[ステップS153]表現形式変換部124は、1桁8ビットの桁合わせ処理が行われる。この処理の詳細は後述する(図25参照)。

[ステップS154]表現形式変換部124は、1桁16ビットの桁合わせ処理が行われる。この処理の詳細は後述する(図26参照)。

[ステップS155]表現形式変換部124は、すべての分岐条件に対する処理が終了したら、表現形式変換処理を終了する。

次に、リテラルの1桁8ビット形式変換処理について詳細に説明する。

図20は、リテラルの1桁8ビット形式変換処理の手順の一例を示すフローチャートである。この処理は、リテラルを引数として開始される。

[ステップS161]表現形式変換部124は、配列aを用意する。

[ステップS162]表現形式変換部124は、リテラル中の文字Cのすべてに対して、ステップS163〜S167の処理を行う。

[ステップS163]表現形式変換部124は、配列bを用意する。

[ステップS164]表現形式変換部124は、文字Cの文字コード値Xを求める。

[ステップS165]表現形式変換部124は、文字コード値Xの上位4ビット分の値(X≫4)を、配列b(1)へ代入する。

[ステップS166]表現形式変換部124は、文字コード値Xの下位4ビット分の値(X&15)を、配列b(2)へ代入する。

[ステップS167]表現形式変換部124は、配列bのすべての値(b(1)、b(2))を、配列aの末尾に追加する。

[ステップS168]表現形式変換部124は、すべての文字に対する処理が終了したら、処理をステップS169に進める。

[ステップS169]表現形式変換部124は、リテラルを配列aと置換する。

このようにして、リテラルが1桁8ビット形式と同じ表現形式に変換される。

次に、リテラルの1桁16ビット形式変換処理について詳細に説明する。

図21は、リテラルの1桁16ビット形式変換処理の手順の一例を示すフローチャートである。この処理は、リテラルを引数として開始される。

[ステップS171]表現形式変換部124は、配列aを用意する。

[ステップS172]表現形式変換部124は、リテラル中の文字Cのすべてに対して、ステップS173〜S179の処理を行う。

[ステップS173]表現形式変換部124は、配列bを用意する。

[ステップS174]表現形式変換部124は、文字Cの文字コード値Xを求める。

[ステップS175]表現形式変換部124は、文字コード値Xの上位4ビット分(第1ビットから第4ビット)の値(X≫12)を、配列b(1)へ代入する。

[ステップS176]表現形式変換部124は、文字コード値Xの第4ビットから第8ビットの値(X&4095≫8)を、配列b(2)へ代入する。

[ステップS177]表現形式変換部124は、文字コード値Xの第9ビットから第12ビットの値(X&255≫4)を、配列b(3)へ代入する。

[ステップS178]表現形式変換部124は、文字コード値Xの下位4ビット分(第13ビットから第16ビット)の値(X&15)を、配列b(4)へ代入する。

[ステップS179]表現形式変換部124は、配列bのすべての値(b(1)、b(2)、b(3)、b(4))を、配列aの末尾に追加する。

[ステップS180]表現形式変換部124は、すべての文字に対する処理が終了したら、処理をステップS181に進める。

[ステップS181]表現形式変換部124は、リテラルを配列aと置換する。

このようにして、リテラルが1桁16ビット形式と同じ表現形式に変換される。

次に、1桁4ビット項目に対する1桁8ビット形式変換処理について説明する。

図22は、1桁4ビット項目の1桁8ビット形式変換処理の手順の一例を示すフローチャートである。この処理は、1桁4ビットのデータ項目のシンボル列lsを引数として開始される。

[ステップS191]表現形式変換部124は、配列aを用意する。

[ステップS192]表現形式変換部124は、引数に設定されたシンボル列lsのシンボルすべてに対して、ステップS193〜S197の処理を実行する。

[ステップS193]表現形式変換部124は、配列bを用意する。

[ステップS194]表現形式変換部124は、シンボルの値xに対応する文字コード値をf(x)とする。例えば文字コードとしてASCIIコードを用いる場合、「f(x)=x+48」となる。

[ステップS195]表現形式変換部124は、f(x)の上位4ビット分の値(f(x)≫4)を、配列b(1)へ代入する。

[ステップS196]表現形式変換部124は、f(x)の下位4ビット分の値(f(x)&15)を、配列b(2)へ代入する。

[ステップS197]表現形式変換部124は、配列bのすべての値(b(1)、b(2))を、配列aの末尾に追加する。

[ステップS198]表現形式変換部124は、すべての文字に対する処理が終了したら、処理をステップS199に進める。

[ステップS199]表現形式変換部124は、シンボル列lsを配列aと置換する。

このようにして、1桁4ビットのデータ項目のシンボル列が、1桁8ビット形式と同じ表現形式に変換される。

次に、1桁4ビット項目の1桁16ビット形式変換処理について説明する。

図23は、1桁4ビット項目の1桁16ビット形式変換処理の手順の一例を示すフローチャートである。この処理は、1桁4ビットのデータ項目のシンボル列lsを引数として開始される。

[ステップS201]表現形式変換部124は、配列aを用意する。

[ステップS202]表現形式変換部124は、引数に設定されたシンボル列lsのシンボルすべてに対して、ステップS203〜S209の処理を実行する。

[ステップS203]表現形式変換部124は、配列bを用意する。

[ステップS204]表現形式変換部124は、シンボルの値xに対応する文字コード値をf(x)とする。

[ステップS205]表現形式変換部124は、f(x)の上位4ビット分(第1ビットから第4ビット)の値(X≫12)を、配列b(1)へ代入する。

[ステップS206]表現形式変換部124は、f(x)の第4ビットから第8ビットの値(X&4095≫8)を、配列b(2)へ代入する。

[ステップS207]表現形式変換部124は、f(x)の第9ビットから第12ビットの値(X&255≫4)を、配列b(3)へ代入する。

[ステップS208]表現形式変換部124は、f(x)の下位4ビット分(第13ビットから第16ビット)の値(X&15)を、配列b(4)へ代入する。

[ステップS209]表現形式変換部124は、配列bのすべての値(b(1)、b(2)、b(3)、b(4))を、配列aの末尾に追加する。

[ステップS210]表現形式変換部124は、すべての文字に対する処理が終了したら、処理をステップS211に進める。

[ステップS211]表現形式変換部124は、シンボル列lsを配列aと置換する。

このようにして、1桁4ビットのデータ項目のシンボル列が、1桁16ビット形式と同じ表現形式に変換される。

次に、1桁8ビット項目の1桁16ビット形式変換処理について説明する。

図24は、1桁8ビット項目の1桁16ビット形式変換処理の手順の一例を示すフローチャートである。この処理は、1桁8ビットのデータ項目のシンボル列lsを引数として開始される。

[ステップS221]表現形式変換部124は、配列aを用意する。

[ステップS222]表現形式変換部124は、カウンタiに、引数として設定されたシンボル列lsの先頭の要素(シンボル)の要素番号を設定する。例えばシンボル列内の各シンボルに対して、先頭から順に昇順のシンボル番号が付与されているものとする。

[ステップS223]表現形式変換部124は、カウンタiがシンボル列lsの末尾の桁の要素番号に達するまで、ステップS224〜S230の処理を繰り返し実行する。カウンタiの値は、例えばステップS224〜S230を1回実行するごとに、2ずつカウントアップされる。

[ステップS224]表現形式変換部124は、配列bを用意する。

[ステップS225]表現形式変換部124は、シンボル列lsのi番目のシンボルの値を上位ビットs1に代入する(s1=ls[i])。また表現形式変換部124は、シンボル列lsのi+1番目のシンボルの値を下位ビットs2に代入する(s2=ls[i+1])。

[ステップS226]表現形式変換部124は、数値の0を、配列b(1)へ代入する。

[ステップS227]表現形式変換部124は、数値の0を、配列b(2)へ代入する。

[ステップS228]表現形式変換部124は、データ項目の上位4ビット分の値s1を、変数b(3)へ代入する。

[ステップS229]表現形式変換部124は、データ項目の下位4ビット分の値s2を、変数b(4)へ代入する。

[ステップS230]表現形式変換部124は、配列bのすべての値(b(1)、b(2)、b(3)、b(4))を、配列aの末尾に追加する。

[ステップS231]表現形式変換部124は、カウンタiで示される要素が、データ項目の末尾の桁(8ビット)に達したときのステップS224〜S230の処理が終了したら、処理をステップS232に進める。

[ステップS232]表現形式変換部124は、シンボル列lsを配列aと置換する。

このようにして、1桁8ビットのデータ項目のシンボル列が、1桁16ビット形式と同じ表現形式に変換される。

次に、1桁8ビットの桁合わせ処理について説明する。

図25は、1桁8ビットの桁合わせ処理の手順の一例を示すフローチャートである。

[ステップS241]表現形式変換部124は、左辺より右辺の方が長い(桁数が多い)か否かを判断する。右辺の方が長ければ、処理がステップS242に進められる。左辺の方が長ければ、処理がステップS243に進められる。

[ステップS242]表現形式変換部124は、左辺の値を変数o1へ代入し、右辺の値を変数o2へ代入する。その後、処理がステップS244に進められる。

[ステップS243]表現形式変換部124は、右辺の値を変数o1へ代入し、左辺の値を変数o2へ代入する。

[ステップS244]表現形式変換部124は、変数o1の桁数と、変数o2の桁数が同じになるまで、ステップS245〜S251の処理を繰り返し実行する。

[ステップS245]表現形式変換部124は、変数o1と変数o2とは数値か否かを判断する。数値であれば、処理がステップS246に進められる。数値でなければ、処理がステップS249に進められる。

[ステップS246]表現形式変換部124は、変数cに、「0」の文字コードを設定する。

[ステップS247]表現形式変換部124は、変数cの下位4ビット分の値(c&15)を、変数o1の先頭に追加する。

[ステップS248]表現形式変換部124は、変数cの上位4ビット分の値(c≫4)を、変数o1の先頭に追加する。その後、処理がステップS252に進められる。

[ステップS249]表現形式変換部124は、変数cに、半角スペースの文字コードを設定する。

[ステップS250]表現形式変換部124は、変数cの上位4ビット分の値(c≫4)を、変数o1の末尾に追加する。

[ステップS251]表現形式変換部124は、変数cの下位4ビット分の値(c&15)を、変数o1の末尾に追加する。

[ステップS252]表現形式変換部124は、変数o1と変数o2との桁数が同じになったら、各変数の値を、元の辺(左辺または右辺)に書き戻し、1桁8ビットの桁合わせ処理を終了する。

このようにして、1桁8ビットの表現形式による、左辺と右辺との桁合わせが完了する。

次に1桁16ビットの桁合わせ処理について説明する。

図26は、1桁16ビットの桁合わせ処理の手順の一例を示すフローチャートである。

[ステップS261]表現形式変換部124は、左辺より右辺の方が長い(桁数が多い)か否かを判断する。右辺の方が長ければ、処理がステップS262に進められる。左辺の方が長ければ、処理がステップS263に進められる。

[ステップS262]表現形式変換部124は、左辺の値を変数o1へ代入し、右辺の値を変数o2へ代入する。その後、処理がステップS264に進められる。

[ステップS263]表現形式変換部124は、右辺の値を変数o1へ代入し、左辺の値を変数o2へ代入する。

[ステップS264]表現形式変換部124は、変数o1の桁数と、変数o2の桁数が同じになるまで、ステップS265〜S270の処理を繰り返し実行する。

[ステップS265]表現形式変換部124は、配列bを用意する。

[ステップS266]表現形式変換部124は、変数cに、半角スペースの文字コードを設定する。

[ステップS267]表現形式変換部124は、変数cの上位4ビット分(第1ビットから第4ビット)の値(c≫12)を、配列b(1)へ代入する。

[ステップS268]表現形式変換部124は、変数cの第5ビットから第8ビットの値(c&4095≫8)を、配列b(2)へ代入する。

[ステップS269]表現形式変換部124は、変数cの第9ビットから第12ビットの値(c&255≫4)を、配列b(3)へ代入する。

[ステップS270]表現形式変換部124は、変数cの下位4ビット分(第13ビットから第16ビット)の値(c&15)を、配列b(4)へ代入する。

[ステップS271]表現形式変換部124は、変数o1と変数o2との桁数が同じになったら、各変数の値を、元の辺(左辺または右辺)に書き戻し、1桁16ビットの桁合わせ処理を終了する。

このようにして、1桁16ビットの表現形式による、左辺と右辺との桁合わせが完了する。

次に、論理式の生成処理について説明する。

図27は、論理式生成の一例を示す図である。論理式生成部125は、表現形式変換後のパス条件43に基づいて、論理式51〜55を生成する。パス条件43の1行目の分岐条件に基づいて、論理式51が生成される。パス条件43の2行目の分岐条件に基づいて、論理式52が生成される。パス条件43の3行目の分岐条件に基づいて、論理式53が生成される。パス条件43の4行目の分岐条件に基づいて、論理式54が生成される。パス条件43の5行目の分岐条件に基づいて、論理式55が生成される。

論理式51〜55中の「not」は、後に続く括弧内の条件の否定を表す。「and」は、後に続く括弧内の複数の条件の論理積を表す。「or」は、後に続く括弧内の複数の条件の論理和を表す。「=」は、後に続く括弧内の2つの値が等しいことを表す。「<=」は、後に続く括弧内の右の値が左の値以上であることを表す。「<」は、後に続く括弧内の右の値が左の値より大きいことを表す。「>」は、後に続く括弧内の左の値が右の値より大きいことを表す。

例えばパス条件43の1行目の右辺の先頭には、「50≫4」という要素がある。これは「50」(2進数表記で「00110010」)の上位4ビット「0011」(10進数表記で「3」)である。この要素と左辺の先頭のシンボル「S1」とが一致することが、論理式51内の「=(S1 3)」という制約で示されている。論理式51では、左辺と右辺との対応する要素が等しいという複数の制約の論理積を否定している。その結果、対応する要素間で、少なくとも1つでも等しくないものが存在すれば論理積は偽となり、その論理積を否定した論理式51が充足する。

次に論理式の生成手順について説明する。

図28は、論理式生成処理の手順の一例を示すフローチャートである。論理式生成処理は、パス条件43内の分岐条件ごとに行われる。

[ステップS281]論理式生成部125は、制約を書き出す領域dを用意する。

[ステップS282]論理式生成部125は、演算子の種別を判断する。演算子が等号であれば、処理がステップS283に進められる。演算子が不等号であれば、処理がステップS287に進められる。演算子が比較演算子であれば、処理がステップS292に進められる。

[ステップS283]演算子が等号の場合、論理式生成部125は、左辺と右辺との対応する要素対すべてに対して、ステップS284〜S285の処理を行う。なお、対応する要素対とは、左辺と右辺とのそれぞれにおける、先頭からの順番が同じとなる要素である。

[ステップS284]論理式生成部125は、左辺と右辺とにおける対応する要素対間で等号が成立するという制約eを生成する。

[ステップS285]論理式生成部125は、領域dに、それまでの領域dの内容に制約eの論理積を追加した内容を、新たに代入する。

[ステップS286]論理式生成部125は、対応する要素対のすべてについて、ステップS284〜S285の処理が終了した場合、処理をステップS298に進める。

[ステップS287]演算子が不等号の場合、論理式生成部125は、左辺と右辺との対応する要素対すべてに対して、ステップS288〜S289の処理を行う。

[ステップS288]論理式生成部125は、左辺と右辺とにおける対応する要素対間で等号が成立するという制約eを生成する。

[ステップS289]論理式生成部125は、領域dに、それまでの領域dの内容に制約eの論理積を追加した内容を、新たに代入する。

[ステップS290]論理式生成部125は、対応する要素対のすべてについて、ステップS288〜S289の処理が終了した場合、処理をステップS291に進める。

[ステップS291]論理式生成部125は、領域dに設定されている内容全体を否定する制約を、領域dに新たに代入する。その後、処理がステップS298に進められる。

[ステップS292]演算子が比較演算子の場合、論理式生成部125は、左辺と右辺との対応する要素対すべてに対して、ステップS293〜S296の処理を行う。

[ステップS293]論理式生成部125は、制約を書き出す領域fを用意する。

[ステップS294]論理式生成部125は、処理対象とする要素対よりも上位の要素対がすべて等しい関係にあるという制約を、領域fに追加する。

[ステップS295]論理式生成部125は、処理対象とする要素対で、演算子の関係が成立するという制約を、論理積で領域fに追加する。

[ステップS296]論理式生成部125は、領域dの内容に、領域fの内容を論理和(OR)で追加した内容を、新たに領域dに代入する。

[ステップS297]論理式生成部125は、対応する要素対のすべてについて、ステップS293〜S296の処理が終了した場合、処理をステップS298に進める。

[ステップS298]論理式生成部125は、領域dに格納された内容を、分岐条件に対応する論理式として出力する。

このようにして、論理式51〜55が生成される。その後、ソルバ実行部126によりソルバが実行され、論理式51〜55を充足する解(充足解)が得られる。充足解には、論理式51〜55のすべてを充足するシンボルごとの値が示される。充足解は、充足解記憶部127に格納される。そしてシンボル逆置換部128により、シンボルごとの充足解が、データ項目ごとの充足解に置換される。

図29は、シンボル逆置換の一例を示す図である。論理式51〜55に基づいて得られる充足解61は、シンボルごとの値となる。図29の例では、充足解61には、各シンボルのシンボル名に対応づけて、値が設定されている。このような充足解61に対してシンボル逆置換処理を行うことで、パス条件34を満たす項目名ごとの値を示す充足解62が得られる。この充足解62がテストデータとなる。

例えば、「年月日」にはシンボル「S1」から「S16」が割り当てられているので、シンボル逆置換部128は、シンボルのリスト「S1」「S2」…「S16」を取得する。「年月日」は1桁8ビットであるため、1桁目に対応するのはシンボル「S1」「S2」である。1桁目の値を求めるため、シンボル逆置換部128は、シンボル「S1」「S2」の値を合成して、1桁目の値を得る。すると「年月日」の1桁目は「50」となる。「v[i]×16+v[i+1]」が、シンボルv[i]とシンボルv[i+1]を合成する式である(iは1以上の整数、v[i]はi番目のシンボルの値)。この式で求まるのは文字コードである。そこでシンボル逆置換部128は、文字コードを対応する文字へと変換する(JISの場合、文字コード「50」は文字「2」に対応する)。同様にして、「年月日」のすべての桁の値を求めると、充足解「20001131」を得ることができる。

なおシンボル逆置換部128による変換処理は、データ項目の表現形式によって変わる。例えば、「時刻」のように1桁4ビットの変数に割り当てられるシンボルのリスト「S17」「S18」「S19」「S20」を変換する際には、シンボルの合成や文字コード変換などを行わずにすむ。

以下シンボル逆置換処理の手順について詳細に説明する。

図30は、シンボル逆置換処理の手順の一例を示すフローチャートである。

[ステップS301]シンボル逆置換部128は、すべてのデータ項目に対して、ステップS302〜S309の処理を実行する。

[ステップS302]シンボル逆置換部128は、シンボルテーブル41から、処理対象のデータ項目に対応するシンボルのリストvを取得する。

[ステップS303]シンボル逆置換部128は、リストv内のシンボルを、名前順でソートする。

[ステップS304]シンボル逆置換部128は、配列tを用意する。

[ステップS305]シンボル逆置換部128は、データ項目の表現形式を判断する。1桁4ビットの表現形式であれば、処理がステップS306に進められる。1桁8ビットの表現形式であれば、処理がステップS307に進められる。1桁16ビットの表現形式であれば、処理がステップS308に進められる。

[ステップS306]処理対象のデータ項目が1桁4ビットの表現形式の場合、シンボル逆置換部128は、配列tとリストvとを引数として、シンボル列の1桁4ビット置換処理を行う。この処理の詳細は後述する(図31参照)。

[ステップS307]処理対象のデータ項目が1桁8ビットの表現形式の場合、シンボル逆置換部128は、配列tとリストvとを引数として、シンボル列の1桁8ビット置換処理を行う。この処理の詳細は後述する(図32参照)。

[ステップS308]処理対象のデータ項目が1桁16ビットの表現形式の場合、シンボル逆置換部128は、配列tとリストvとを引数として、シンボル列の1桁16ビット置換処理を行う。この処理の詳細は後述する(図33参照)。

[ステップS309]シンボル逆置換部128は、処理対象のデータ項目に対応付けて、シンボル逆置換後の充足解62に、配列tを書き出す。

[ステップS310]シンボル逆置換部128は、すべてのデータ項目に対するステップS302〜S309の処理が終了したら、シンボル逆置換処理を終了する。

次に、1桁4ビット置換処理の手順について説明する。

図31は、1桁4ビット置換処理の手順の一例を示すフローチャートである。

[ステップS321]シンボル逆置換部128は、カウンタiに0を設定する。

[ステップS322]シンボル逆置換部128は、カウンタiの値がリストvの末尾に達するまで、ステップS323〜S324の処理を実行する。

[ステップS323]シンボル逆置換部128は、v[i](i番目のシンボルの値)を配列tの末尾に加える。

[ステップS324]シンボル逆置換部128は、iの値を1だけカウントアップする。

[ステップS325]シンボル逆置換部128は、iの値がリストv内のシンボル数を超えた場合、ステップS323〜S324の繰り返しを終了すると共に、1桁4ビット置換処理を終了する。

次に、1桁8ビット置換処理の手順について説明する。

図32は、1桁8ビット置換処理の手順の一例を示すフローチャートである。

[ステップS331]シンボル逆置換部128は、カウンタiに0を設定する。

[ステップS332]シンボル逆置換部128は、カウンタiの値がリストvの末尾に達するまで、ステップS333〜S336の処理を実行する。

[ステップS333]シンボル逆置換部128は、i番目のシンボルの値(v[i])を用いて、文字コードw=v[i]×16+v[i+1]を計算する。

[ステップS334]シンボル逆置換部128は、文字コードを、その文字コードで表される文字へと変換する。例えばシンボル逆置換部128は、数字の文字コードを、その文字コードで表される数値に変換する。なお、文字コードのままでテストデータとすることができる場合、文字への変換を行わなくてもよい。

[ステップS335]シンボル逆置換部128は、変換後の文字を、配列tの末尾に加える。

[ステップS336]シンボル逆置換部128は、カウンタiの値を、2だけカウントアップする。

[ステップS337]シンボル逆置換部128は、iの値がリストv内のシンボル数を超えた場合、ステップS333〜S336の繰り返しを終了すると共に、1桁8ビット置換処理を終了する。

次に、1桁16ビット置換処理の手順について説明する。

図33は、1桁16ビット置換処理の手順の一例を示すフローチャートである。

[ステップS341]シンボル逆置換部128は、カウンタiに0を設定する。

[ステップS342]シンボル逆置換部128は、カウンタiの値がリストvの末尾に達するまで、ステップS343〜S346の処理を実行する。

[ステップS343]シンボル逆置換部128は、i番目のシンボルの値(v[i])を用いて、文字コードw=v[i]×4096+v[i+1]×256+v[i+2]×16+v[i+3]を計算する。

[ステップS344]シンボル逆置換部128は、文字コードを、その文字コードで表される文字へと変換する。なお、文字コードのままでテストデータとすることができる場合、文字への変換を行わなくてもよい。

[ステップS345]シンボル逆置換部128は、変換後の文字を、配列tの末尾に加える。

[ステップS346]シンボル逆置換部128は、カウンタiの値を、4だけカウントアップする。

[ステップS347]シンボル逆置換部128は、iの値がリストv内のシンボル数を超えた場合、ステップS343〜S346の繰り返しを終了すると共に、1桁16ビット置換処理を終了する。

以上説明したように、第2の実施の形態によれば、複数のデータ項目(変数)で重複して参照される記憶領域が4ビットずつのシンボルに分割される。データ項目の表現形式は、最小でも1桁当たり4ビットで表されている。また1桁当たりのビット数が4ビットより多い場合でも、1桁当たりのビット数は4の倍数である。すなわち、各データ項目の表現形式による1桁当たりのビット数の最大公約数が4である。そのため、記憶領域を4ビットずつのシンボルに分割すれば、各シンボルに含まれるビットに関して、それらのビットを参照する1以上のデータ項目が共通となる。そのため制約条件を満たすようなシンボルに対して設定する値を求めることで、記憶領域の各ビットの値を1つに決定することができる。しかもその値を記憶領域に設定すれば、テスト装置30に対して、テスト対象の処理パスを実行させることができる。すなわち、参照先の記憶領域が部分的に重複する複数のデータ項目がある場合でも、適切なテストデータを生成することができる。

また、第2の実施の形態では、条件式の左辺と右辺との内部表現を合わせることにより、異なる内部表現のデータ項目が混在していても、正しくテストデータを生成することができる。例えば内部表現における1桁当たりのビット数が異なる場合、表現形式を揃えた上で、1桁当たりのビット数が左辺と右辺とで同じになるように分割される。これにより、内部表現における1桁当たりのビット数が異なる複数の変数が存在しても、適切なテストデータを生成することができる。

なお第2の実施の形態は、COBOLで作成されたプログラムをテストする場合の例を用いて説明したが、複数の変数で同じ記憶領域を参照可能な他の言語で作成されたプログラムをテストする場合にも、同様にテストデータを生成できる。例えば、PL/I(商標)で作成されたプログラムをテストする場合にも適切なテストデータを生成できる。

また、第2の実施の形態では、文字コードとしてASCIIやJISコードの例を示したが、他の文字コードを用いることもできる。

以上、実施の形態を例示したが、実施の形態で示した各部の構成は同様の機能を有する他のものに置換することができる。また、他の任意の構成物や工程が付加されてもよい。さらに、前述した実施の形態のうちの任意の2以上の構成(特徴)を組み合わせたものであってもよい。