JP6074955B2 - 情報処理装置および制御方法 - Google Patents

情報処理装置および制御方法 Download PDFInfo

- Publication number

- JP6074955B2 JP6074955B2 JP2012191491A JP2012191491A JP6074955B2 JP 6074955 B2 JP6074955 B2 JP 6074955B2 JP 2012191491 A JP2012191491 A JP 2012191491A JP 2012191491 A JP2012191491 A JP 2012191491A JP 6074955 B2 JP6074955 B2 JP 6074955B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- individual

- arithmetic

- thread

- circuits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/10—Protecting distributed programs or content, e.g. vending or licensing of copyrighted material ; Digital rights management [DRM]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/10—Protecting distributed programs or content, e.g. vending or licensing of copyrighted material ; Digital rights management [DRM]

- G06F21/105—Arrangements for software license management or administration, e.g. for managing licenses at corporate level

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Computer Hardware Design (AREA)

- Computer Security & Cryptography (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Multimedia (AREA)

- Technology Law (AREA)

- Hardware Redundancy (AREA)

Description

〔第1の実施の形態〕

図1は、第1の実施の形態に係る情報処理装置の構成例およびその動作例を示す図である。図1に示す情報処理装置1は、記憶部2、制御部3および複数の演算回路を有している。図1の例では、情報処理装置1は2つの演算回路11,12を備えているが、演算回路の搭載数は2つ以上の任意の数とすることができる。

次に、情報処理装置の例として、マルチコア・マルチスレッド方式のプロセッサが搭載されたサーバ装置を挙げて説明する。

なお、ビルディングブロック110aに搭載されるCPUチップの数やRAMの数、およびディスクユニット113に搭載される不揮発性記憶装置の数は、それぞれ任意の数とすることができる。

以上のように、サーバ装置100は、それぞれに1つ以上のプロセッサ(ここではCPUチップを指す)が搭載されたビルディングブロックを複数備える。このような構成により、サーバ装置100全体としてマルチプロセッサシステムが実現される。

ところで、本実施の形態のサーバ装置100は、CoD技術に対応している。サーバ装置100のユーザは、コアを単位としてライセンス(使用権)を購入する。サーバ装置100は、ライセンスが購入された台数分のコアを動作許可状態にし、その台数に含まれない残りのコアを動作禁止状態にする。また、ユーザがライセンスを追加購入した場合には、動作禁止状態のコアのうち、追加購入された台数分のコアが動作許可状態に変更される。これにより、ユーザは、サーバ装置100を導入する際の初期投資を抑制し、さらにその後に、必要に応じてサーバ装置100の能力を即座に増強することができる。

図4は、スレッドの故障が発生した場合の処理の参考例を示す図である。なお、この図4、および次の図5では、動作許可状態のハードウェアを実線で示し、動作禁止状態のハードウェアを点線で示す。

次に、サーバ装置100の処理の詳細について説明する。

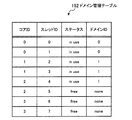

ステータスは、対応するスレッドの状態を示す。ステータスの欄には、「in use」,「free」,「fail」のいずれかが登録される。「in use」は、対応するスレッドに論理ドメインが割り当てられていることを示す。「free」は、対応するスレッドに論理ドメインが割り当てられていないことを示す。「fail」は、対応するスレッドから異常が検出され、そのスレッドに対する論理ドメインの割り当てが禁止されていることを示す。

以上のステップS23,S24の処理によれば、異常が検知されたスレッドが、すでに一方のスレッドに論理ドメインが割り当てられていたコアにおける他方のスレッドに置き換えられる。この場合、動作中のコアの数は増加しないため、ライセンス超過が発生することなく、異常が検知されたスレッドを置き換えることができる。

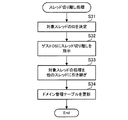

[ステップS31]ドメイン管理部140は、切り離し対象のスレッドのIDを決定する。

[ステップS41]ドメイン管理部140は、組み込み対象のスレッドのIDを決定する。

次に、コア単位の置き換えを行った場合における管理テーブルの遷移例を挙げる。図13は、コア管理テーブルの遷移の例を示す図である。また、図14は、ドメイン管理テーブルの遷移の例を示す図である。

図15は、第3の実施の形態に係る情報処理装置が備える機能の構成例を示すブロック図である。

以上のサーバ装置100aにおいては、第2の実施の形態におけるハイパーバイザ130、ドメイン管理部140およびゲストOSとの間の処理が、サービスプロセッサ120、システム管理部150およびOSとの間で実行される。すなわち、第3の実施の形態では、図9〜図12に示した処理が、ハイパーバイザ130をサービスプロセッサ120に、ドメイン管理部140をシステム管理部150に、ゲストOSをOSにそれぞれ置き換えることで実現される。これにより、第3の実施の形態でも、スレッドに異常が発生した場合に、ライセンス超過を発生させることなく、異常が発生したスレッドを他の正常なスレッドに置き換えることができる。

上記の第2,第3の実施の形態では、コアに対してライセンスを設定した場合について説明したが、例えば、サーバ装置が備える他のハードウェア資源に対してライセンスが設定されてもよい。

なお、図16の例では、メモリモジュール310を単位としてライセンスを設定したが、他の例として、同一メモリモジュール310内の隣接する複数個のメモリチップ310を単位としてライセンスが設定されてもよい。この場合、隣接する複数個のメモリチップ310の合計記憶容量を単位としてライセンスが設定されてもよい。

以上の各実施の形態に関し、さらに以下の付記を開示する。

前記演算回路を単位として設定された使用権の数を記憶する記憶部と、

複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可するとともに、動作中の前記演算回路に搭載されたいずれかの前記個別回路の異常を検知すると、異常が検知された前記個別回路が搭載された前記演算回路における他の前記個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させる制御部と、

を有することを特徴とする情報処理装置。

前記制御部は、前記管理情報においていずれかのオペレーティングシステムの処理に割り当てられた前記個別回路の異常を検知したとき、動作していない前記演算回路が存在しない場合には、前記管理情報に基づき、動作中の前記演算回路に搭載された前記個別回路の中にいずれのオペレーティングシステムの処理にも割り当てられていない前記個別回路があるかを判定し、いずれのオペレーティングシステムの処理にも割り当てられていない前記個別回路がある場合には、異常が検知された前記個別回路がいずれのオペレーティングシステムにも割り当てられていない前記個別回路に置き換えられるように前記管理情報を更新する、

ことを特徴とする付記1記載の情報処理装置。

前記記憶部は、前記メモリ装置を単位として設定されたメモリ使用権の数を記憶し、

前記制御部は、複数の前記メモリ装置のうち、前記メモリ使用権の数の前記メモリ装置の使用を許可するとともに、使用中の前記メモリ装置の記憶領域を分割した分割領域のいずれかから異常を検知すると、異常が検知された前記分割領域を含む前記メモリ装置における他の前記分割領域の使用を停止させ、使用されていないいずれかの前記メモリ装置の使用を開始する、

ことを特徴とする付記1〜3のいずれか1つに記載の情報処理装置。

前記演算回路を単位として設定された使用権の数を記憶する記憶部を参照して、複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可し、

動作中の前記演算回路に搭載されたいずれかの前記個別回路の異常を検知すると、異常が検知された前記個別回路が搭載された前記演算回路における他の前記個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させる、

ことを特徴とする制御方法。

処理をさらに含むことを特徴とする付記5記載の制御方法。

前記管理情報においていずれかのオペレーティングシステムの処理に割り当てられた前記個別回路の異常を検知したとき、動作していない前記演算回路が存在しない場合には、前記管理情報に基づき、動作中の前記演算回路に搭載された前記個別回路の中にいずれのオペレーティングシステムの処理にも割り当てられていない前記個別回路があるかを判定し、いずれのオペレーティングシステムの処理にも割り当てられていない前記個別回路がある場合には、異常が検知された前記個別回路がいずれのオペレーティングシステムにも割り当てられていない前記個別回路に置き換えられるように前記管理情報を更新する、

処理をさらに含むことを特徴とする付記5記載の制御方法。

前記記憶部は、前記メモリ装置を単位として設定されたメモリ使用権の数を記憶し、

複数の前記メモリ装置のうち、前記メモリ使用権の数の前記メモリ装置の使用を許可し、使用中の前記メモリ装置の記憶領域を分割した分割領域のいずれかから異常を検知すると、異常が検知された前記分割領域を含む前記メモリ装置における他の前記分割領域の使用を停止させ、使用されていないいずれかの前記メモリ装置の使用を開始する、

処理をさらに含むことを特徴とする付記5〜7のいずれか1つに記載の制御方法。

2 記憶部

3 制御部

11,12 演算回路

21〜24 個別回路

Claims (5)

- それぞれ処理を並列に実行する複数の個別回路を有する演算回路を、複数備えた情報処理装置において、

前記演算回路を単位として設定された使用権の数を記憶する記憶部と、

複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可するとともに、動作中の前記演算回路に搭載された前記複数の個別回路のうち第1の個別回路の異常を検知すると、動作していない前記演算回路が存在する場合には、前記第1の個別回路が搭載された前記演算回路における他の個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させ、動作していない前記演算回路が存在しない場合には、動作中の前記演算回路の中に使用されていない第2の個別回路があるかを判定し、前記第2の個別回路がある場合には、前記第1の個別回路を用いて実行されていた処理を、前記第2の個別回路を用いて実行させる制御部と、

を有することを特徴とする情報処理装置。 - それぞれ処理を並列に実行する複数の個別回路を有する演算回路を、複数備えた情報処理装置において、

前記演算回路を単位として設定された使用権の数と、動作中の前記演算回路に搭載された前記複数の個別回路のうち、1つまたは複数のオペレーティングシステムのいずれかの処理に割り当てられた第1の個別回路の情報を保持する管理情報とを記憶する記憶部と、

複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可するとともに、前記第1の個別回路の異常を検知すると、動作していない前記演算回路が存在する場合には、前記第1の個別回路が搭載された前記演算回路における他の個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させ、動作していない前記演算回路が存在しない場合には、前記管理情報に基づき、動作中の前記演算回路に搭載された前記複数の個別回路の中にいずれのオペレーティングシステムの処理にも割り当てられていない第2の個別回路があるかを判定し、前記第2の個別回路がある場合には、前記第1の個別回路が前記第2の個別回路に置き換えられるように前記管理情報を更新する制御部と、

を有することを特徴とする情報処理装置。 - 前記情報処理装置は、複数のメモリ装置を有し、

前記記憶部は、前記メモリ装置を単位として設定されたメモリ使用権の数を記憶し、

前記制御部は、複数の前記メモリ装置のうち、前記メモリ使用権の数の前記メモリ装置の使用を許可するとともに、使用中の前記メモリ装置の記憶領域を分割した分割領域のいずれかから異常を検知すると、異常が検知された前記分割領域を含む前記メモリ装置における他の前記分割領域の使用を停止させ、使用されていないいずれかの前記メモリ装置の使用を開始する、

ことを特徴とする請求項1または2記載の情報処理装置。 - それぞれ処理を並列に実行する複数の個別回路を有する演算回路を、複数備えた情報処理装置における制御方法であって、

前記演算回路を単位として設定された使用権の数を記憶する記憶部を参照して、複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可し、

動作中の前記演算回路に搭載された前記複数の個別回路のうち第1の個別回路の異常を検知すると、動作していない前記演算回路が存在する場合には、前記第1の個別回路が搭載された前記演算回路における他の個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させ、動作していない前記演算回路が存在しない場合には、動作中の前記演算回路の中に使用されていない第2の個別回路があるかを判定し、前記第2の個別回路がある場合には、前記第1の個別回路を用いて実行されていた処理を、前記第2の個別回路を用いて実行させる、

ことを特徴とする制御方法。 - それぞれ処理を並列に実行する複数の個別回路を有する演算回路を、複数備えた情報処理装置における制御方法であって、

前記演算回路を単位として設定された使用権の数と、動作中の前記演算回路に搭載された前記複数の個別回路のうち、1つまたは複数のオペレーティングシステムのいずれかの処理に割り当てられた第1の個別回路の情報を保持する管理情報とを記憶する記憶部を参照して、複数の前記演算回路のうち、前記使用権の数の前記演算回路の動作を許可し、

前記第1の個別回路の異常を検知すると、動作していない前記演算回路が存在する場合には、前記第1の個別回路が搭載された前記演算回路における他の個別回路の動作を停止させ、動作していないいずれかの前記演算回路の動作を開始させ、動作していない前記演算回路が存在しない場合には、前記管理情報に基づき、動作中の前記演算回路に搭載された前記複数の個別回路の中にいずれのオペレーティングシステムの処理にも割り当てられていない第2の個別回路があるかを判定し、前記第2の個別回路がある場合には、前記第1の個別回路が前記第2の個別回路に置き換えられるように前記管理情報を更新する、

ことを特徴とする制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012191491A JP6074955B2 (ja) | 2012-08-31 | 2012-08-31 | 情報処理装置および制御方法 |

| US13/966,330 US9032482B2 (en) | 2012-08-31 | 2013-08-14 | Information processing apparatus and control method |

| EP13181331.3A EP2704050B1 (en) | 2012-08-31 | 2013-08-22 | Capacity on Demand processing apparatus and control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012191491A JP6074955B2 (ja) | 2012-08-31 | 2012-08-31 | 情報処理装置および制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014048907A JP2014048907A (ja) | 2014-03-17 |

| JP6074955B2 true JP6074955B2 (ja) | 2017-02-08 |

Family

ID=49110984

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012191491A Expired - Fee Related JP6074955B2 (ja) | 2012-08-31 | 2012-08-31 | 情報処理装置および制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9032482B2 (ja) |

| EP (1) | EP2704050B1 (ja) |

| JP (1) | JP6074955B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9223574B2 (en) | 2014-03-27 | 2015-12-29 | International Business Machines Corporation | Start virtual execution instruction for dispatching multiple threads in a computer |

| US9213569B2 (en) | 2014-03-27 | 2015-12-15 | International Business Machines Corporation | Exiting multiple threads in a computer |

| US9772867B2 (en) * | 2014-03-27 | 2017-09-26 | International Business Machines Corporation | Control area for managing multiple threads in a computer |

| US9195493B2 (en) | 2014-03-27 | 2015-11-24 | International Business Machines Corporation | Dispatching multiple threads in a computer |

| US9361159B2 (en) | 2014-04-01 | 2016-06-07 | International Business Machines Corporation | Runtime chargeback in a simultaneous multithreading (SMT) environment |

| US9417927B2 (en) | 2014-04-01 | 2016-08-16 | International Business Machines Corporation | Runtime capacity planning in a simultaneous multithreading (SMT) environment |

| US9389897B1 (en) | 2014-12-18 | 2016-07-12 | International Business Machines Corporation | Exiting multiple threads of a simulation environment in a computer |

| JP2017033181A (ja) * | 2015-07-30 | 2017-02-09 | 富士通株式会社 | 情報処理装置、情報処理システム、情報処理装置の制御方法および情報処理装置の制御プログラム |

| WO2017022117A1 (ja) * | 2015-08-06 | 2017-02-09 | 富士通株式会社 | 制御装置,制御プログラム及び制御方法 |

| JP6819061B2 (ja) * | 2016-03-28 | 2021-01-27 | 日本電気株式会社 | 情報処理装置、プロセス切り替え方法及びプログラム |

| KR20220071182A (ko) | 2019-09-27 | 2022-05-31 | 인텔 코포레이션 | 소프트웨어 정의된 실리콘 구현 및 관리 |

| US11599368B2 (en) | 2019-09-27 | 2023-03-07 | Intel Corporation | Device enhancements for software defined silicon implementations |

| US11977612B2 (en) | 2020-07-07 | 2024-05-07 | Intel Corporation | Software defined silicon guardianship |

| US20220385962A1 (en) * | 2021-05-26 | 2022-12-01 | Arris Enterprises Llc | License management for vcores |

| CN117234763A (zh) * | 2022-06-07 | 2023-12-15 | 华为技术有限公司 | 处理器核故障处理方法、装置、设备及存储介质 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3561002B2 (ja) | 1994-05-18 | 2004-09-02 | 富士通株式会社 | ディスク装置 |

| US7451183B2 (en) | 2003-03-21 | 2008-11-11 | Hewlett-Packard Development Company, L.P. | Assembly and method for balancing processors in a partitioned server |

| US7275180B2 (en) | 2003-04-17 | 2007-09-25 | International Business Machines Corporation | Transparent replacement of a failing processor |

| US7814366B2 (en) * | 2005-11-15 | 2010-10-12 | Intel Corporation | On-demand CPU licensing activation |

| WO2007099606A1 (ja) | 2006-02-28 | 2007-09-07 | Fujitsu Limited | プロセサ制御方法 |

| US7493477B2 (en) * | 2006-06-30 | 2009-02-17 | Intel Corporation | Method and apparatus for disabling a processor core based on a number of executions of an application exceeding a threshold |

| WO2009118886A1 (ja) | 2008-03-28 | 2009-10-01 | 富士通株式会社 | ハードウェアリソースの管理装置 |

| WO2010046966A1 (ja) * | 2008-10-21 | 2010-04-29 | 富士通株式会社 | 情報処理システムおよび使用権一元管理方法 |

| JP5035299B2 (ja) * | 2009-06-15 | 2012-09-26 | 株式会社日立製作所 | マルチコアプロセッサ制御方法、その計算機システム、及び管理計算機のプログラム |

| JP2011227840A (ja) * | 2010-04-23 | 2011-11-10 | Hitachi Ltd | 非smp構成でのサーバー間のコアライセンスの授受を制御する装置 |

| US9286448B2 (en) * | 2010-06-09 | 2016-03-15 | Grant Philip Cushion | Enhanced software license management |

| US8627128B2 (en) * | 2010-11-09 | 2014-01-07 | International Business Machines Corporation | Power management for processing capacity upgrade on demand |

| US20120221884A1 (en) * | 2011-02-28 | 2012-08-30 | Carter Nicholas P | Error management across hardware and software layers |

| US8856602B2 (en) * | 2011-12-20 | 2014-10-07 | International Business Machines Corporation | Multi-core processor with internal voting-based built in self test (BIST) |

| EP3483771A1 (en) * | 2011-12-30 | 2019-05-15 | Intel Corporation | Multi-level cpu high current protection |

-

2012

- 2012-08-31 JP JP2012191491A patent/JP6074955B2/ja not_active Expired - Fee Related

-

2013

- 2013-08-14 US US13/966,330 patent/US9032482B2/en not_active Expired - Fee Related

- 2013-08-22 EP EP13181331.3A patent/EP2704050B1/en not_active Not-in-force

Also Published As

| Publication number | Publication date |

|---|---|

| EP2704050A1 (en) | 2014-03-05 |

| EP2704050B1 (en) | 2016-10-26 |

| JP2014048907A (ja) | 2014-03-17 |

| US20140068792A1 (en) | 2014-03-06 |

| US9032482B2 (en) | 2015-05-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6074955B2 (ja) | 情報処理装置および制御方法 | |

| US7937615B2 (en) | Method for improving reliability of multi-core processor computer | |

| JP5035299B2 (ja) | マルチコアプロセッサ制御方法、その計算機システム、及び管理計算機のプログラム | |

| CN110083494B (zh) | 在多核心环境中管理硬件错误的方法和装置 | |

| US9329937B1 (en) | High availability architecture | |

| US7426657B2 (en) | System and method for predictive processor failure recovery | |

| US9032180B2 (en) | Managing CPU resources for high availability micro-partitions | |

| JP6191686B2 (ja) | 情報処理装置、資源割当方法、及びプログラム | |

| EP3767470B1 (en) | Central processing unit cpu hot-remove method and apparatus, and central processing unit cpu hot-add method and apparatus | |

| US9244826B2 (en) | Managing CPU resources for high availability micro-partitions | |

| WO2015118679A1 (ja) | 計算機、ハイパーバイザ、物理コアの割り当て方法 | |

| JP2011186701A (ja) | リソース割当装置、リソース割当方法、およびリソース割当プログラム | |

| CN100409191C (zh) | 用于管理多节点smp系统的方法和系统 | |

| JP5998577B2 (ja) | クラスタ監視装置、クラスタ監視方法、及びプログラム | |

| US9158470B2 (en) | Managing CPU resources for high availability micro-partitions | |

| US20100083034A1 (en) | Information processing apparatus and configuration control method | |

| US11182183B2 (en) | Workload placement using conflict cost | |

| EP2979170B1 (en) | Making memory of compute and expansion blade devices available for use by an operating system | |

| JP2013254354A (ja) | コンピュータ装置及びソフトウェア管理方法及びプログラム | |

| JP2005234744A (ja) | マルチプロセッサシステム及び障害処理方法 | |

| KR101188413B1 (ko) | 차량 전자 제어 유닛의 안정성 확보를 위한 가상화 및 이중화 시스템 및 그 안정성 확보 방법 | |

| JP5201176B2 (ja) | 情報処理装置 | |

| JP2008123129A (ja) | マルチプロセッサシステム、障害処理方法、プログラム及び記録媒体 | |

| JP2013130999A (ja) | マルチコアプロセッサ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150512 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160412 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160613 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161213 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161226 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6074955 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |