JP5899653B2 - Imaging device - Google Patents

Imaging device Download PDFInfo

- Publication number

- JP5899653B2 JP5899653B2 JP2011105193A JP2011105193A JP5899653B2 JP 5899653 B2 JP5899653 B2 JP 5899653B2 JP 2011105193 A JP2011105193 A JP 2011105193A JP 2011105193 A JP2011105193 A JP 2011105193A JP 5899653 B2 JP5899653 B2 JP 5899653B2

- Authority

- JP

- Japan

- Prior art keywords

- focus detection

- unit

- period

- pixel

- transfer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Focusing (AREA)

- Automatic Focus Adjustment (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

本発明は、撮像装置に関する。 The present invention relates to an imaging apparatus.

近年、自動焦点調節機能(AF機能)を有するビデオカメラやデジタルカメラが広く一般に普及している。この種のデジタルカメラには、CMOS型の撮像装置やCCD型の撮像装置が用いられる。例えば、CMOS型の撮像装置は、複数の画素が2次元行列状に配置された画素アレイを有している。各画素は、光信号を電気信号に変換する光電変換部を有している。また、デジタルカメラは、撮像用の画素アレイとは別に、焦点検出を実施するための専用の焦点検出素子を有する場合もある。なお、撮像用の画素と焦点検出用の画素とを混在して配置した撮像装置も提案されている(例えば、特許文献1)。 In recent years, video cameras and digital cameras having an automatic focus adjustment function (AF function) have been widely used. For this type of digital camera, a CMOS type imaging device or a CCD type imaging device is used. For example, a CMOS-type imaging device has a pixel array in which a plurality of pixels are arranged in a two-dimensional matrix. Each pixel has a photoelectric conversion unit that converts an optical signal into an electrical signal. In addition, the digital camera may have a dedicated focus detection element for performing focus detection separately from the pixel array for imaging. An imaging apparatus in which imaging pixels and focus detection pixels are mixedly arranged has also been proposed (for example, Patent Document 1).

CMOS型の撮像装置では、選択された行毎にシャッタ動作を行うローリングシャッタ方式が用いられる場合が多い。このため、特許文献1の構成では、複数の焦点検出用の画素の露光タイミングを互いに同一にすることは、困難である。焦点検出用の画素の露光タイミングが複数の焦点検出用の画素で互いに異なる場合、焦点検出精度が低下するおそれがある。また、撮像用の画素と焦点検出用の画素とが同じ行に配置されている場合、撮像用の画素を適切な露光時間で露光しているときに、焦点検出用の画素を適切な露光時間で露光することは、困難である。焦点検出用の画素を適切な露光時間で露光できない場合、焦点検出精度が低下する。

In a CMOS type imaging apparatus, a rolling shutter system that performs a shutter operation for each selected row is often used. For this reason, in the configuration of

本発明の目的は、焦点検出用の画素の露光タイミングを適切に制御可能な撮像装置を提供することである。 An object of the present invention is to provide an imaging apparatus capable of appropriately controlling the exposure timing of pixels for focus detection.

撮像装置の一例は、複数の焦点検出用画素および複数の撮像用画素が配置された画素アレイを有している。各焦点検出用画素は、入射光を光電変換して電荷を生成する第1光電変換部と、電極を有し電極に印加される電圧により制御され第1光電変換部から転送される電荷を蓄積するメモリ部と、電極を有し電極に印加される電圧により制御され第1光電変換部からメモリ部に電荷を転送する第1の転送部と、メモリ部から増幅部に電荷を転送する第2の転送部と、メモリ部を遮光する遮光部とを有している。また、各撮像用画素は、入射光を光電変換して電荷を生成する第2光電変換部を有している。また、第1光電変換部は、第2光電変換部より小さく、メモリ部は、焦点検出用画素の遮光部で遮光された領域であって、第1光電変換部がない領域にのみ配置される。また、メモリ部の電極および第1の転送部の電極には共通の信号電圧が印加される。

撮像装置の他の例は、複数の焦点検出用画素および複数の撮像用画素が配置された画素アレイと、撮像用画素および焦点検出用画素の動作を制御する制御部とを有している。各焦点検出用画素は、入射光を光電変換して電荷を生成する第1光電変換部と、第1光電変換部から転送される電荷を蓄積するメモリ部と、第1光電変換部からメモリ部に電荷を転送する第1の転送部と、メモリ部から増幅部に電荷を転送する第2の転送部と、メモリ部を遮光する遮光部とを有している。また、各撮像用画素は、入射光を光電変換して電荷を生成する第2光電変換部を有している。また、第1光電変換部は、第2光電変換部より小さく、メモリ部は、焦点検出用画素の遮光部で遮光された領域であって、第1光電変換部がない領域にのみ配置される。また、制御部は、画素アレイで異なる行に配置された複数の焦点検出用画素の露光タイミングが互いに同じになるように、焦点検出用画素の動作を制御する。

An example of the imaging apparatus has a pixel array in which a plurality of focus detection pixels and a plurality of imaging pixels are arranged. Each focus detection pixel has a first photoelectric conversion unit that photoelectrically converts incident light to generate charges, and stores charges transferred from the first photoelectric conversion unit that are controlled by a voltage applied to the electrodes. A first transfer unit that has an electrode and is controlled by a voltage applied to the electrode and transfers charge from the first photoelectric conversion unit to the memory unit; and a second transfer unit that transfers charge from the memory unit to the amplification unit And a light-shielding part that shields the memory part. Each imaging pixel has a second photoelectric conversion unit that photoelectrically converts incident light to generate charges. In addition, the first photoelectric conversion unit is smaller than the second photoelectric conversion unit, and the memory unit is disposed only in a region that is shielded by the light shielding unit of the focus detection pixel and does not have the first photoelectric conversion unit. . A common signal voltage is applied to the electrodes of the memory section and the first transfer section.

Another example of the imaging apparatus includes a pixel array in which a plurality of focus detection pixels and a plurality of imaging pixels are arranged, and a control unit that controls operations of the imaging pixels and the focus detection pixels. Each focus detection pixel includes a first photoelectric conversion unit that photoelectrically converts incident light to generate charges, a memory unit that accumulates charges transferred from the first photoelectric conversion unit, and a memory unit from the first photoelectric conversion unit A first transfer unit that transfers charges to the second transfer unit, a second transfer unit that transfers charges from the memory unit to the amplification unit, and a light-shielding unit that shields the memory unit. Each imaging pixel has a second photoelectric conversion unit that photoelectrically converts incident light to generate charges. In addition, the first photoelectric conversion unit is smaller than the second photoelectric conversion unit, and the memory unit is disposed only in a region that is shielded by the light shielding unit of the focus detection pixel and does not have the first photoelectric conversion unit. . Further, the control unit controls the operation of the focus detection pixels so that the exposure timings of the plurality of focus detection pixels arranged in different rows in the pixel array are the same.

本発明によれば、焦点検出用の画素の露光タイミングを適切に制御可能な撮像装置を提供できる。 ADVANTAGE OF THE INVENTION According to this invention, the imaging device which can control appropriately the exposure timing of the pixel for focus detection can be provided.

以下、本発明の実施形態を図面を用いて説明する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings.

図1は、本発明の一実施形態を示している。図1の網掛け部分は、図2で説明する焦点検出用画素PXF内のメモリ部MUを示している。この実施形態の撮像装置IMUは、例えば、CMOS型の撮像装置であり、デジタルカメラに搭載される。例えば、撮像装置IMUは、画素アレイARYおよび制御部CNTを有している。 FIG. 1 shows an embodiment of the present invention. The shaded portion in FIG. 1 shows the memory unit MU in the focus detection pixel PXF described in FIG. The imaging device IMU of this embodiment is, for example, a CMOS type imaging device and is mounted on a digital camera. For example, the imaging device IMU includes a pixel array ARY and a control unit CNT.

画素アレイARYは、例えば、マイクロレンズおよびカラーフィルタを介して入射される光の量に応じた電気信号(以下、画像信号とも称する)を生成する複数の撮像用画素PXIと、複数の焦点検出用画素PXFとを有している。例えば、複数の撮像用画素PXIは、赤色(R)、緑色(Gr、Gb)、青色(B)のカラーフィルタをそれぞれ有し、ベイヤー配列で配置されている。なお、赤色(R)、緑色(Gr、Gb)、青色(B)のカラーフィルタをそれぞれ有する撮像用画素PXIの配列は、ベイヤー配列に限定されない。 The pixel array ARY includes, for example, a plurality of imaging pixels PXI that generate an electrical signal (hereinafter also referred to as an image signal) corresponding to the amount of light incident through a micro lens and a color filter, and a plurality of focus detection pixels. And a pixel PXF. For example, the plurality of imaging pixels PXI have red (R), green (Gr, Gb), and blue (B) color filters, respectively, and are arranged in a Bayer array. Note that the arrangement of the imaging pixels PXI each having red (R), green (Gr, Gb), and blue (B) color filters is not limited to the Bayer arrangement.

焦点検出用画素PXFは、例えば、公知の瞳分割方式による自動焦点検出処理に用いられる信号を生成するための画素であり、行方向(図1の横方向)に延在する焦点検出領域FDA(図1の破線で囲んだ領域)に配置される。なお、焦点検出用画素PXFが配置される焦点検出領域FDAは、列方向(図1の縦方向)に延在して設けられてもよいし、複数設けられてもよい。 The focus detection pixel PXF is, for example, a pixel for generating a signal used for an automatic focus detection process by a known pupil division method, and a focus detection area FDA (in the horizontal direction in FIG. 1) ( (Region surrounded by a broken line in FIG. 1). The focus detection area FDA in which the focus detection pixels PXF are arranged may be provided so as to extend in the column direction (vertical direction in FIG. 1), or a plurality of focus detection areas FDA may be provided.

制御部CNTは、例えば、画素アレイARYの撮像用画素PXIおよび焦点検出用画素PXFの動作を制御する。なお、制御部CNTは、撮像装置IMUとは別に設けられてもよい。すなわち、撮像装置IMUは、図1の構成から制御部CNTが省かれた構成でもよい。 For example, the control unit CNT controls the operations of the imaging pixels PXI and the focus detection pixels PXF of the pixel array ARY. Note that the control unit CNT may be provided separately from the imaging device IMU. That is, the imaging apparatus IMU may have a configuration in which the control unit CNT is omitted from the configuration in FIG.

図2は、図1に示した撮像用画素PXIおよび焦点検出用画素PXFの概要を示している。なお、図2は、画素アレイARYの撮像面側(後述する図3、図4の上側)から見た撮像用画素PXIおよび焦点検出用画素PXFを示している。また、図2では、図を見やすくするために、配線やカラーフィルタ等の記載を省略している。図2の網掛け部分は、メモリ部MUを示している。 FIG. 2 shows an outline of the imaging pixel PXI and the focus detection pixel PXF shown in FIG. FIG. 2 shows the imaging pixels PXI and the focus detection pixels PXF viewed from the imaging surface side of the pixel array ARY (upper side in FIGS. 3 and 4 described later). Further, in FIG. 2, illustrations of wirings, color filters, and the like are omitted for easy viewing of the drawing. The shaded portion in FIG. 2 indicates the memory unit MU.

撮像用画素PXIは、光電変換部としてのフォトダイオードPDaと、画像信号を読み出すための回路部CIRUとを有している。例えば、フォトダイオードPDaは、マイクロレンズMLNおよび開口部APを介して入射される光を光電変換して電荷を生成する。なお、例えば、開口部AP以外の回路部CIRU等の領域では、マイクロレンズMLNを介して入射される光は、図3に示す遮光部MS等により遮蔽される。 The imaging pixel PXI includes a photodiode PDa as a photoelectric conversion unit and a circuit unit CIRU for reading out an image signal. For example, the photodiode PDa generates electric charge by photoelectrically converting light incident through the microlens MLN and the opening AP. For example, in a region such as the circuit unit CIRU other than the opening AP, light incident through the microlens MLN is shielded by the light shielding unit MS illustrated in FIG.

回路部CIRUは、例えば、後述する図6、図7に示す転送トランジスタMTR、増幅トランジスタMAM、画素選択トランジスタMSE、リセットトランジスタMRSおよびフローティングディフュージョンFDを有している。例えば、撮像用画素PXIでは、回路部CIRUの転送トランジスタMTRは、フォトダイオードPDaに隣接して配置される。また、例えば、焦点検出用画素PXFでは、回路部CIRUの転送トランジスタMTRは、メモリ部MUに隣接して配置される。なお、回路部CIRUの配置は、この例に限定されない。 The circuit unit CIRU includes, for example, a transfer transistor MTR, an amplification transistor MAM, a pixel selection transistor MSE, a reset transistor MRS, and a floating diffusion FD shown in FIGS. For example, in the imaging pixel PXI, the transfer transistor MTR of the circuit unit CIRU is disposed adjacent to the photodiode PDa. For example, in the focus detection pixel PXF, the transfer transistor MTR of the circuit unit CIRU is disposed adjacent to the memory unit MU. The arrangement of the circuit unit CIRU is not limited to this example.

焦点検出用画素PXFは、光電変換部としてのフォトダイオードPDbと、フォトダイオードPDbから転送される電荷を蓄積するメモリ部MUと、画像信号を読み出すための回路部CIRUとを有している。例えば、フォトダイオードPDbは、マイクロレンズMLNおよび開口部APを介して入射される光を光電変換して電荷を生成する。なお、例えば、開口部AP以外のメモリ部MU等の領域では、マイクロレンズMLNを介して入射される光は、図4に示す遮光部MS等により遮蔽される。 The focus detection pixel PXF includes a photodiode PDb as a photoelectric conversion unit, a memory unit MU that accumulates charges transferred from the photodiode PDb, and a circuit unit CIRU for reading out an image signal. For example, the photodiode PDb photoelectrically converts light incident through the microlens MLN and the opening AP to generate charges. For example, in a region such as the memory unit MU other than the opening AP, light incident through the microlens MLN is shielded by the light shielding unit MS shown in FIG.

焦点検出用画素群PXFGは、例えば、行方向(図2の横方向)に配置された一対の焦点検出用画素PXFにより構成され、行方向に瞳分割した一対の像を生成する。例えば、焦点検出用画素群PXFG(一対の焦点検出用画素PXF)から生成される一対の像の像ずれ量を検出することにより、デフォーカス量が算出される。 The focus detection pixel group PXFG includes, for example, a pair of focus detection pixels PXF arranged in the row direction (horizontal direction in FIG. 2), and generates a pair of images that are pupil-divided in the row direction. For example, the defocus amount is calculated by detecting the image shift amount of a pair of images generated from the focus detection pixel group PXFG (a pair of focus detection pixels PXF).

ここで、例えば、焦点検出用画素群PXFGのうちの左側の焦点検出用画素PXFでは、フォトダイオードPDbおよびメモリ部MUがマイクロレンズMLNの左半分および右半分にそれぞれ配置される。また、例えば、焦点検出用画素群PXFGのうちの右側の焦点検出用画素PXFでは、フォトダイオードPDbおよびメモリ部MUは、マイクロレンズMLNの右半分および左半分にそれぞれ配置される。 Here, for example, in the left focus detection pixel PXF in the focus detection pixel group PXFG, the photodiode PDb and the memory unit MU are arranged in the left half and the right half of the microlens MLN, respectively. Further, for example, in the right focus detection pixel PXF in the focus detection pixel group PXFG, the photodiode PDb and the memory unit MU are arranged in the right half and the left half of the microlens MLN, respectively.

図3は、図2に示した撮像用画素PXIのA−A’線に沿う断面を示している。なお、図3では、配線等の記載を省略している。例えば、フォトダイオードPDaは、p型の半導体基板SUBの受光面側(図3では上側)に形成されたn型の半導体領域NA1を有している。なお、フォトダイオードPDaの導電型は、この例に限定されない。半導体基板SUBに形成された絶縁部ISは、例えば、互いに隣接するフォトダイオードPDa間を絶縁するための領域である。また、例えば、半導体基板SUB上に設けられたゲート層GLYには、上述した図2に示した回路部CIRUのトランジスタのゲート電極等が形成される。 FIG. 3 shows a cross section taken along the line A-A ′ of the imaging pixel PXI shown in FIG. 2. In FIG. 3, illustration of wiring and the like is omitted. For example, the photodiode PDa has an n-type semiconductor region NA1 formed on the light receiving surface side (upper side in FIG. 3) of the p-type semiconductor substrate SUB. Note that the conductivity type of the photodiode PDa is not limited to this example. The insulating part IS formed in the semiconductor substrate SUB is a region for insulating between adjacent photodiodes PDa, for example. Further, for example, in the gate layer GLY provided on the semiconductor substrate SUB, the gate electrode of the transistor of the circuit unit CIRU shown in FIG. 2 described above is formed.

そして、ゲート層GLY上には、複数の層を有する配線層MLYが設けられる。例えば、遮光部MSは、配線層MLYの最下層(半導体基板SUB側の層)に金属膜等で形成され、フォトダイオードPDa以外の領域(絶縁部IS等)に対応する位置に配置される。すなわち、フォトダイオードPDa上には、開口部APが形成される。なお、遮光部MSは、配線層MLYの最下層以外に形成されてもよいし、配線と兼用されてもよい。例えば、配線は、遮光部MSが設けられる層と別の層に形成されてもよいし、遮光部MSが設けられる層と同じ層に形成されてもよい。 A wiring layer MLY having a plurality of layers is provided on the gate layer GLY. For example, the light shielding portion MS is formed of a metal film or the like in the lowest layer (layer on the semiconductor substrate SUB side) of the wiring layer MLY, and is disposed at a position corresponding to a region (insulating portion IS or the like) other than the photodiode PDa. That is, the opening AP is formed on the photodiode PDa. The light shielding portion MS may be formed other than the lowermost layer of the wiring layer MLY, or may be shared with the wiring. For example, the wiring may be formed in a layer different from the layer in which the light shielding unit MS is provided, or may be formed in the same layer as the layer in which the light shielding unit MS is provided.

配線層MLY上には、カラーフィルタとして機能する光学フィルタOFLが配置される。図3では、緑色(Gb)および青色(B)のカラーフィルタとしてそれぞれ機能する光学フィルタOFLが交互に配置されている。光学フィルタOFL上には、平坦層PLYが形成されている。そして、平坦層PLY上にマイクロレンズMLNが配置されている。例えば、撮像用画素PXIでは、フォトダイオードPDaは、マイクロレンズMLN、光学フィルタOFL(カラーフィルタ)および開口部APを通過した光を受ける。 An optical filter OFL that functions as a color filter is disposed on the wiring layer MLY. In FIG. 3, optical filters OFL that function as green (Gb) and blue (B) color filters are alternately arranged. A flat layer PLY is formed on the optical filter OFL. The microlens MLN is disposed on the flat layer PLY. For example, in the imaging pixel PXI, the photodiode PDa receives light that has passed through the microlens MLN, the optical filter OFL (color filter), and the opening AP.

図4は、図2に示した焦点検出用画素PXFのB−B’線に沿う断面を示している。なお、図4では、配線等の記載を省略している。例えば、フォトダイオードPDbは、p型の半導体基板SUBの受光面側(図4では上側)に形成されたn型の半導体領域NA1を有している。 FIG. 4 shows a cross section taken along line B-B ′ of the focus detection pixel PXF shown in FIG. 2. In FIG. 4, description of wiring and the like is omitted. For example, the photodiode PDb has an n-type semiconductor region NA1 formed on the light receiving surface side (upper side in FIG. 4) of the p-type semiconductor substrate SUB.

メモリ部MUは、フォトダイオードPDbから転送される電荷を蓄積する蓄積部MEMと、フォトダイオードPDbの電荷を蓄積部MEMに転送するメモリ転送部MTXとを有している。例えば、メモリ転送部MTXは、p型の半導体基板SUBに形成されたn型の半導体領域NA2と、ゲート層GLYに形成されたゲート電極GTの一部(領域NA2上の部分のゲート電極GT)とを有している。 The memory unit MU includes a storage unit MEM that stores charges transferred from the photodiode PDb, and a memory transfer unit MTX that transfers charges of the photodiode PDb to the storage unit MEM. For example, the memory transfer unit MTX includes an n-type semiconductor region NA2 formed on the p-type semiconductor substrate SUB and a part of the gate electrode GT formed on the gate layer GLY (a portion of the gate electrode GT on the region NA2). And have.

また、例えば、メモリ転送部MTXは、領域NA1、NA2間に形成されるp型の半導体領域PA1と、ゲート電極GTの一部(領域PA1上の部分のゲート電極GT)と有している。すなわち、メモリ転送部MTXは、蓄積部MEMとフォトダイオードPDbとの間に形成される。なお、絶縁部ISは、互いに隣接する領域NA1間と、互いに隣接する領域NA2間とにそれぞれ形成される。すなわち、領域NA1、PA1、NA2は、絶縁部IS間に形成される。 For example, the memory transfer unit MTX includes a p-type semiconductor region PA1 formed between the regions NA1 and NA2, and a part of the gate electrode GT (a part of the gate electrode GT on the region PA1). That is, the memory transfer unit MTX is formed between the storage unit MEM and the photodiode PDb. The insulating part IS is formed between the adjacent areas NA1 and between the adjacent areas NA2. That is, the regions NA1, PA1, and NA2 are formed between the insulating portions IS.

ここで、例えば、フォトダイオードPDbの領域NA1、メモリ転送部MTXの領域PA1および蓄積部MEMの領域NA2の不純物濃度は、互いに異なる。領域NA1、PA1、NA2の不純物濃度は、例えば、後述する図9、図10に示すポテンシャルの関係を実現するように、それぞれ設定される。例えば、ゲート電極GTの電圧が接地電圧GNDのときの蓄積部MEMのポテンシャルがフォトダイオードPDbのポテンシャルとフローティングディフュージョンFDのポテンシャルとの間に位置するように、領域NA1、NA2の不純物濃度は、それぞれ設定される。なお、領域PA1の不純物濃度は、半導体基板SUBの不純物濃度と異なっていてもよいし、半導体基板SUBの不純物濃度と同じでもよい。 Here, for example, the impurity concentrations of the region NA1 of the photodiode PDb, the region PA1 of the memory transfer unit MTX, and the region NA2 of the storage unit MEM are different from each other. The impurity concentrations of the regions NA1, PA1, and NA2 are set so as to realize, for example, the potential relationship shown in FIGS. For example, the impurity concentrations of the regions NA1 and NA2 are respectively set so that the potential of the storage unit MEM when the voltage of the gate electrode GT is the ground voltage GND is located between the potential of the photodiode PDb and the potential of the floating diffusion FD. Is set. Note that the impurity concentration of the region PA1 may be different from the impurity concentration of the semiconductor substrate SUB, or may be the same as the impurity concentration of the semiconductor substrate SUB.

半導体基板SUB上には、ゲート層GLYが形成される。上述したように、蓄積部MEMおよびメモリ転送部MTXのゲート電極GTは、ゲート層GLYに形成される。例えば、蓄積部MEMおよびメモリ転送部MTXのゲート電極GTは、互いに共通に設けられている。なお、蓄積部MEMおよびメモリ転送部MTXのゲート電極GTは、互いに分離して設けられてもよい。また、例えば、ゲート層GLYには、蓄積部MEMおよびメモリ転送部MTXのゲート電極GTとは別に、上述した図2に示した回路部CIRUのトランジスタのゲート電極等が形成される。 A gate layer GLY is formed on the semiconductor substrate SUB. As described above, the gate electrode GT of the storage unit MEM and the memory transfer unit MTX is formed in the gate layer GLY. For example, the gate electrodes GT of the storage unit MEM and the memory transfer unit MTX are provided in common with each other. Note that the gate electrode GT of the storage unit MEM and the memory transfer unit MTX may be provided separately from each other. Further, for example, in the gate layer GLY, the gate electrode of the transistor of the circuit unit CIRU shown in FIG. 2 described above is formed separately from the gate electrode GT of the storage unit MEM and the memory transfer unit MTX.

そして、ゲート層GLY上には、複数の層を有する配線層MLYが設けられる。例えば、遮光部MSは、配線層MLYの最下層(半導体基板SUB側の層)に金属膜等で形成され、フォトダイオードPDb以外の領域(メモリ部MU、絶縁部IS等)に対応する位置に配置される。すなわち、フォトダイオードPDb上には、開口部APが形成される。このように、焦点検出用画素PXFは、メモリ部MUを遮光する遮光部MSを有している。なお、遮光部MSは、配線層MLYの最下層以外に形成されてもよいし、配線と兼用されてもよい。例えば、配線は、遮光部MSが設けられる層と別の層に形成されてもよいし、遮光部MSが設けられる層と同じ層に形成されてもよい。 A wiring layer MLY having a plurality of layers is provided on the gate layer GLY. For example, the light shielding portion MS is formed of a metal film or the like in the lowermost layer (semiconductor substrate SUB side layer) of the wiring layer MLY and is located at a position corresponding to a region other than the photodiode PDb (memory portion MU, insulating portion IS, etc.). Be placed. That is, the opening AP is formed on the photodiode PDb. As described above, the focus detection pixel PXF includes the light shielding unit MS that shields the memory unit MU. The light shielding portion MS may be formed other than the lowermost layer of the wiring layer MLY, or may be shared with the wiring. For example, the wiring may be formed in a layer different from the layer in which the light shielding unit MS is provided, or may be formed in the same layer as the layer in which the light shielding unit MS is provided.

配線層MLY上には、例えば、青色の波長から赤色の波長までの光を透過する光学フィルタOFL(CLR)が配置される。光学フィルタOFL上には、平坦層PLYが形成されている。そして、平坦層PLY上にマイクロレンズMLNが配置されている。例えば、焦点検出用画素PXFでは、フォトダイオードPDbは、マイクロレンズMLN、光学フィルタOFL(CLR)および開口部APを通過した光を受ける。また、フォトダイオードPDbで生成された電荷は、例えば、ゲート電極GTを制御することにより、メモリ転送部MTXを介して蓄積部MEMに転送される。したがって、この実施形態では、焦点検出用画素PXFのフォトダイオードPDbで生成された電荷を蓄積部MEMに蓄積できる。 On the wiring layer MLY, for example, an optical filter OFL (CLR) that transmits light from a blue wavelength to a red wavelength is disposed. A flat layer PLY is formed on the optical filter OFL. The microlens MLN is disposed on the flat layer PLY. For example, in the focus detection pixel PXF, the photodiode PDb receives light that has passed through the microlens MLN, the optical filter OFL (CLR), and the opening AP. In addition, the charge generated by the photodiode PDb is transferred to the storage unit MEM via the memory transfer unit MTX by controlling the gate electrode GT, for example. Therefore, in this embodiment, the charge generated by the photodiode PDb of the focus detection pixel PXF can be accumulated in the accumulation unit MEM.

なお、フォトダイオードPDb、メモリ転送部MTXおよび蓄積部MEM等の半導体の導電型は、この例に限定されない。 Note that the conductivity types of the semiconductors such as the photodiode PDb, the memory transfer unit MTX, and the storage unit MEM are not limited to this example.

図5は、図1に示した制御部CNTの概要を示している。なお、図5は、n行m列の画素アレイARYの撮像用画素PXIおよび焦点検出用画素PXFの動作を制御する制御部CNTの概要を示している。例えば、焦点検出用画素PXFは、4行目の2列目から“m−1”列目に配置されている。 FIG. 5 shows an overview of the control unit CNT shown in FIG. FIG. 5 shows an outline of the control unit CNT that controls the operations of the imaging pixels PXI and the focus detection pixels PXF of the pixel array ARY of n rows and m columns. For example, the focus detection pixels PXF are arranged in the “m−1” column from the second column of the fourth row.

制御部CNTは、例えば、垂直走査回路VSCおよびタイミングジェネレータTGを有している。垂直走査回路VSCは、制御信号RST、TR、SELを用いて、画素アレイARYの撮像用画素PXIを行毎に制御する。例えば、垂直走査回路VSCは、制御信号RST(1)、TR(1)、SEL(1)を制御し、1行目の撮像用画素PXIを制御する。また、例えば、垂直走査回路VSCは、制御信号RST(4)、TR(4)、SEL(4)を制御し、4行目の1列目およびm列目の撮像用画素PXIを制御する。 The control unit CNT includes, for example, a vertical scanning circuit VSC and a timing generator TG. The vertical scanning circuit VSC controls the imaging pixels PXI of the pixel array ARY for each row using the control signals RST, TR, and SEL. For example, the vertical scanning circuit VSC controls the control signals RST (1), TR (1), and SEL (1), and controls the imaging pixels PXI in the first row. Further, for example, the vertical scanning circuit VSC controls the control signals RST (4), TR (4), and SEL (4), and controls the imaging pixels PXI in the first and mth columns of the fourth row.

さらに、垂直走査回路VSCは、制御信号RST_f、TR_f、TX_f、SEL_fを用いて、画素アレイARYの焦点検出用画素PXFを、撮像用画素PXIとは独立に制御する。例えば、垂直走査回路VSCは、制御信号RST_f(4)、TR_f(4)、TX_f(4)、SEL_f(4)を制御し、4行目の焦点検出用画素PXFを制御する。以下、制御信号RST、RST_fをリセット信号RSTとも称する。また、制御信号TR、TR_fを転送信号TRとも称する。制御信号SEL、SEL_fを選択信号SELとも称する。さらに、制御信号TX_fをメモリ転送信号TX_fとも称する。 Further, the vertical scanning circuit VSC controls the focus detection pixels PXF of the pixel array ARY independently of the imaging pixels PXI using the control signals RST_f, TR_f, TX_f, and SEL_f. For example, the vertical scanning circuit VSC controls the control signals RST_f (4), TR_f (4), TX_f (4), and SEL_f (4), and controls the focus detection pixels PXF in the fourth row. Hereinafter, the control signals RST and RST_f are also referred to as reset signals RST. The control signals TR and TR_f are also referred to as transfer signals TR. The control signals SEL and SEL_f are also referred to as selection signals SEL. Further, the control signal TX_f is also referred to as a memory transfer signal TX_f.

タイミングジェネレータTGは、例えば、垂直走査回路VSCに駆動クロック等を供給し、垂直走査回路VSCの制御信号RST、TR、SEL、RST_f、TR_f、TX_f、SEL_fの出力タイミングを制御する。なお、タイミングジェネレータTGは、撮像装置IMUとは別に設けられてもよい。すなわち、撮像装置IMUは、図5の構成からタイミングジェネレータTGが省かれた構成でもよい。 The timing generator TG supplies, for example, a drive clock to the vertical scanning circuit VSC, and controls the output timing of the control signals RST, TR, SEL, RST_f, TR_f, TX_f, and SEL_f of the vertical scanning circuit VSC. Note that the timing generator TG may be provided separately from the imaging device IMU. That is, the imaging apparatus IMU may have a configuration in which the timing generator TG is omitted from the configuration in FIG.

ここで、画素アレイARYは、各画素(撮像用画素PXIおよび焦点検出用画素PXF)の出力信号OUTを出力するための垂直信号線VLを有している。例えば、列方向(図の縦方向)に配置された複数の画素(撮像用画素PXIおよび焦点検出用画素PXF)は、列毎に設けられた垂直信号線VLに接続されている。また、各垂直信号線VLには、各画素からの出力信号OUTを読み出すために、後述する図6、図7に示す定電流源CSが接続されている。 Here, the pixel array ARY has a vertical signal line VL for outputting an output signal OUT of each pixel (imaging pixel PXI and focus detection pixel PXF). For example, a plurality of pixels (imaging pixels PXI and focus detection pixels PXF) arranged in the column direction (vertical direction in the figure) are connected to a vertical signal line VL provided for each column. Each vertical signal line VL is connected to a constant current source CS shown in FIGS. 6 and 7 to be described later in order to read out an output signal OUT from each pixel.

図6は、図1に示した撮像用画素PXIの構成の一例を示している。撮像用画素PXIは、フォトダイオードPDaおよび回路部CIRUを有している。回路部CIRUは、例えば、転送トランジスタMTR、増幅トランジスタMAM、画素選択トランジスタMSE、リセットトランジスタMRSおよびフローティングディフュージョンFD(フローティングディフュージョン領域)を有している。例えば、回路部CIRU内に形成されるトランジスタMTR、MAM、MSE、MRSは、全てnMOSトランジスタである。 FIG. 6 shows an example of the configuration of the imaging pixel PXI shown in FIG. The imaging pixel PXI includes a photodiode PDa and a circuit unit CIRU. The circuit unit CIRU includes, for example, a transfer transistor MTR, an amplification transistor MAM, a pixel selection transistor MSE, a reset transistor MRS, and a floating diffusion FD (floating diffusion region). For example, the transistors MTR, MAM, MSE, and MRS formed in the circuit unit CIRU are all nMOS transistors.

フォトダイオードPDaは、アノードが接地され、カソードが転送トランジスタMTRのソースに接続されている。転送トランジスタMTRは、ゲートに印加される転送信号TRが高レベルの期間にオンし、フォトダイオードPDaに蓄積されている信号電荷をフローティングディフュージョンFDに転送する。 The photodiode PDa has an anode grounded and a cathode connected to the source of the transfer transistor MTR. The transfer transistor MTR is turned on while the transfer signal TR applied to the gate is at a high level, and transfers the signal charge stored in the photodiode PDa to the floating diffusion FD.

フローティングディフュージョンFDは、フォトダイオードPDaから転送される電荷を蓄積する寄生容量が形成される領域(トランジスタMTRのドレイン領域、トランジスタMTR、MAM間の配線領域、トランジスタMAMのゲート領域、リセットトランジスタMRSのソース領域等)である。したがって、フォトダイオードPDaから転送された信号電荷は、フローティングディフュージョンFDに蓄積される。 The floating diffusion FD is a region where parasitic capacitance for accumulating charges transferred from the photodiode PDa is formed (a drain region of the transistor MTR, a wiring region between the transistors MTR and MAM, a gate region of the transistor MAM, and a source of the reset transistor MRS). Area). Therefore, the signal charge transferred from the photodiode PDa is accumulated in the floating diffusion FD.

増幅トランジスタMAMは、ソースが画素選択トランジスタMSEのドレインに接続され、ドレインが電源VDDに接続され、ゲートが転送トランジスタMTRのドレインに接続されている。すなわち、フローティングディフュージョンFDに転送された信号電荷に応じた電圧は、増幅トランジスタMAMのゲートに入力される。そして、増幅トランジスタMAMは、例えば、ゲートの電圧から増幅トランジスタMAMの閾値電圧分降下した電圧を、ソースから出力する。このように、増幅トランジスタMAMは、フローティングディフュージョンFDに転送された信号電荷に応じた信号を生成する。 The amplification transistor MAM has a source connected to the drain of the pixel selection transistor MSE, a drain connected to the power supply VDD, and a gate connected to the drain of the transfer transistor MTR. That is, the voltage corresponding to the signal charge transferred to the floating diffusion FD is input to the gate of the amplification transistor MAM. For example, the amplification transistor MAM outputs, from the source, a voltage obtained by dropping the gate voltage by the threshold voltage of the amplification transistor MAM. As described above, the amplification transistor MAM generates a signal corresponding to the signal charge transferred to the floating diffusion FD.

画素選択トランジスタMSEは、ゲートに印加される選択信号SELが高レベルの期間にオンし、ソースに接続された垂直信号線VLと増幅トランジスタMAMのソースとの間を導通させる。したがって、画素選択トランジスタMSEがオンの期間では、増幅トランジスタMAMと、画素選択トランジスタMSEと、垂直信号線VLに接続された定電流源CSとにより、ソースフォロア回路が構成される。これにより、画素選択トランジスタMSEにより選択された撮像用画素PXIの信号が、垂直信号線VLに出力される。 The pixel selection transistor MSE is turned on when the selection signal SEL applied to the gate is at a high level, and conducts between the vertical signal line VL connected to the source and the source of the amplification transistor MAM. Therefore, during the period in which the pixel selection transistor MSE is on, the amplification transistor MAM, the pixel selection transistor MSE, and the constant current source CS connected to the vertical signal line VL constitute a source follower circuit. Thereby, the signal of the imaging pixel PXI selected by the pixel selection transistor MSE is output to the vertical signal line VL.

リセットトランジスタMRSは、ソースが増幅トランジスタMAMのゲートに接続され、ドレインが電源VDDに接続されている。例えば、リセットトランジスタMRSは、ゲートに印加されるリセット信号RSTが高レベルの期間にオンし、フローティングディフュージョンFDの電荷をリセットする。 The reset transistor MRS has a source connected to the gate of the amplification transistor MAM and a drain connected to the power supply VDD. For example, the reset transistor MRS is turned on while the reset signal RST applied to the gate is at a high level, and resets the charge of the floating diffusion FD.

図7は、図1に示した焦点検出用画素PXFの構成の一例を示している。焦点検出用画素PXFは、フォトダイオードPDb、メモリ部MUおよび回路部CIRUを有している。焦点検出用画素PXFの回路部CIRUの構成は、制御信号および転送トランジスタMTRのソースの接続先を除いて、撮像用画素PXIの回路部CIRUの構成と同じである。このため、回路部CIRUについては、詳細な説明を省略する。例えば、制御信号RST_f、TR_f、SEL_fは、図6に示した制御信号RST、TR、SELにそれぞれ対応している。 FIG. 7 shows an example of the configuration of the focus detection pixel PXF shown in FIG. The focus detection pixel PXF includes a photodiode PDb, a memory unit MU, and a circuit unit CIRU. The configuration of the circuit unit CIRU of the focus detection pixel PXF is the same as the configuration of the circuit unit CIRU of the imaging pixel PXI except for the connection destination of the source of the control signal and the transfer transistor MTR. Therefore, detailed description of the circuit unit CIRU is omitted. For example, the control signals RST_f, TR_f, and SEL_f correspond to the control signals RST, TR, and SEL shown in FIG.

フォトダイオードPDbは、アノードが接地され、カソードがメモリ転送部MTXに接続されている。メモリ部MUは、メモリ転送部MTXおよび蓄積部MEMを有している。例えば、メモリ転送部MTXは、nMOSトランジスタであり、ドレインが蓄積部MEMに接続され、ソースがフォトダイオードPDbのカソードに接続され、ゲートでメモリ転送信号TX_fを受ける。以下、メモリ転送部MTXをメモリ転送トランジスタMTXとも称する。例えば、メモリ転送トランジスタMTXは、メモリ転送信号TX_fが高レベルの期間にオンし、フォトダイオードPDbにより生成された信号電荷を蓄積部MEMに転送する。 The photodiode PDb has an anode grounded and a cathode connected to the memory transfer unit MTX. The memory unit MU includes a memory transfer unit MTX and a storage unit MEM. For example, the memory transfer unit MTX is an nMOS transistor, the drain is connected to the storage unit MEM, the source is connected to the cathode of the photodiode PDb, and the gate receives the memory transfer signal TX_f. Hereinafter, the memory transfer unit MTX is also referred to as a memory transfer transistor MTX. For example, the memory transfer transistor MTX is turned on while the memory transfer signal TX_f is at a high level, and transfers the signal charge generated by the photodiode PDb to the storage unit MEM.

蓄積部MEMは、例えば、MOS構造で形成され、ゲート電極の下に形成されるポテンシャル井戸に電荷を蓄積する。例えば、蓄積部MEMは、フォトダイオードPDbに蓄積される電荷の量より多い量の電荷を蓄積できるポテンシャル井戸を有している。なお、蓄積部MEMのゲート電極(ポテンシャル井戸上のゲート電極)は、例えば、メモリ転送信号TX_fにより制御される。 The accumulation unit MEM is formed of, for example, a MOS structure, and accumulates charges in a potential well formed under the gate electrode. For example, the storage unit MEM has a potential well that can store a larger amount of charge than the amount of charge stored in the photodiode PDb. Note that the gate electrode (gate electrode on the potential well) of the storage unit MEM is controlled by, for example, the memory transfer signal TX_f.

この実施形態では、蓄積部MEMのゲート電極とメモリ転送トランジスタMTXのゲートとが共通のメモリ転送信号TX_fにより制御されるため、メモリ部MUの動作の制御を簡易にできる。なお、例えば、蓄積部MEMのゲート電極とメモリ転送トランジスタMTXのゲートとが互いに分離された構成では、蓄積部MEMのゲート電極は、メモリ転送トランジスタMTXのゲートと異なる制御信号で制御されてもよい。 In this embodiment, since the gate electrode of the storage unit MEM and the gate of the memory transfer transistor MTX are controlled by the common memory transfer signal TX_f, the operation of the memory unit MU can be easily controlled. For example, in a configuration in which the gate electrode of the storage unit MEM and the gate of the memory transfer transistor MTX are separated from each other, the gate electrode of the storage unit MEM may be controlled by a control signal different from the gate of the memory transfer transistor MTX. .

転送トランジスタMTRは、ドレインが増幅トランジスタMAMのゲートに接続され、ソースが蓄積部MEMに接続され、ゲートで転送信号TR_fを受ける。例えば、転送トランジスタMTRは、転送信号TR_fが高レベルの期間にオンし、フォトダイオードPDbにより生成された信号電荷を、メモリ部MUを介してフローティングディフュージョンFDに転送する。あるいは、例えば、転送信号TR_fが高レベルの期間に、転送トランジスタMTRは、蓄積部MEMに蓄積された信号電荷をフローティングディフュージョンFDに転送する。 In the transfer transistor MTR, the drain is connected to the gate of the amplification transistor MAM, the source is connected to the storage unit MEM, and the gate receives the transfer signal TR_f. For example, the transfer transistor MTR is turned on while the transfer signal TR_f is at a high level, and transfers the signal charge generated by the photodiode PDb to the floating diffusion FD via the memory unit MU. Alternatively, for example, during a period when the transfer signal TR_f is at a high level, the transfer transistor MTR transfers the signal charge accumulated in the accumulation unit MEM to the floating diffusion FD.

増幅トランジスタMAMは、ソースが画素選択トランジスタMSEのドレインに接続され、ドレインが電源VDDに接続され、ゲートが転送トランジスタMTRのドレインに接続されている。画素選択トランジスタMSEは、ゲートに印加される選択信号SEL_fが高レベルの期間にオンし、垂直信号線VLと増幅トランジスタMAMのソースとの間を導通させる。これにより、画素選択トランジスタMSEにより選択された焦点検出用画素PXFの信号が、垂直信号線VLに出力される。 The amplification transistor MAM has a source connected to the drain of the pixel selection transistor MSE, a drain connected to the power supply VDD, and a gate connected to the drain of the transfer transistor MTR. The pixel selection transistor MSE is turned on when the selection signal SEL_f applied to the gate is at a high level, and conducts between the vertical signal line VL and the source of the amplification transistor MAM. As a result, the signal of the focus detection pixel PXF selected by the pixel selection transistor MSE is output to the vertical signal line VL.

リセットトランジスタMRSは、ソースが増幅トランジスタMAMのゲートに接続され、ドレインが電源VDDに接続されている。例えば、リセットトランジスタMRSは、ゲートに印加されるリセット信号RST_fが高レベルの期間にオンし、フローティングディフュージョンFDの電荷をリセットする。 The reset transistor MRS has a source connected to the gate of the amplification transistor MAM and a drain connected to the power supply VDD. For example, the reset transistor MRS is turned on while the reset signal RST_f applied to the gate is at a high level, and resets the charge of the floating diffusion FD.

図8は、図6に示した撮像用画素PXIの動作の一例を示している。図中の符号pは、ポテンシャル(電位)を示している。なお、図中の破線は、トランジスタの状態(オン・オフ)が切り替わる前のポテンシャルを示している。 FIG. 8 shows an example of the operation of the imaging pixel PXI shown in FIG. The symbol p in the figure indicates the potential (potential). Note that the broken line in the figure indicates the potential before the transistor state (on / off) is switched.

リセット期間RESaでは、転送信号TRおよびリセット信号RSTは、高レベルに維持され、転送トランジスタMTRおよびリセットトランジスタMRSは、オン(ON)状態に維持される。これにより、フォトダイオードPDaおよびフローティングディフュージョンFDに蓄積された電荷は、電源VDDに排出される。 In the reset period RESa, the transfer signal TR and the reset signal RST are maintained at a high level, and the transfer transistor MTR and the reset transistor MRS are maintained in an on (ON) state. As a result, the charges accumulated in the photodiode PDa and the floating diffusion FD are discharged to the power supply VDD.

露光期間EXPaでは、転送信号TRおよびリセット信号RSTは、低レベルに維持され、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ(OFF)状態に維持される。これにより、フォトダイオードPDaは、入射光に応じて電荷を生成し、生成した電荷を蓄積する。 In the exposure period EXPa, the transfer signal TR and the reset signal RST are maintained at a low level, and the transfer transistor MTR and the reset transistor MRS are maintained in an off state. As a result, the photodiode PDa generates charges according to the incident light, and accumulates the generated charges.

転送期間TRAaでは、転送信号TRおよびリセット信号RSTは、それぞれ高レベルおよび低レベルに維持される。したがって、転送期間TRAaでは、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオン状態およびオフ状態に維持される。これにより、フォトダイオードPDaに蓄積された電荷は、フローティングディフュージョンFDに転送される。なお、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。 In the transfer period TRAa, the transfer signal TR and the reset signal RST are maintained at a high level and a low level, respectively. Therefore, in the transfer period TRAa, the transfer transistor MTR and the reset transistor MRS are maintained in the on state and the off state, respectively. Thereby, the electric charge accumulated in the photodiode PDa is transferred to the floating diffusion FD. Since the reset transistor MRS is in an off state, the charge transferred to the floating diffusion FD is not discharged to the power supply VDD.

読み出し期間REAaでは、転送信号TRおよびリセット信号RSTは、低レベルに維持され、転送トランジスタMTRおよびリセットトランジスタMRSはオフ状態に維持される。これにより、フォトダイオードPDaからフローティングディフュージョンFDに転送された電荷は、フローティングディフュージョンFDに蓄積される。さらに、読み出し期間REAaでは、選択信号SELが高レベルに維持され、フローティングディフュージョンFDに蓄積された信号電荷に応じた電圧が垂直信号線VLに出力される。 In the read period REAa, the transfer signal TR and the reset signal RST are maintained at a low level, and the transfer transistor MTR and the reset transistor MRS are maintained in an off state. Thereby, the charge transferred from the photodiode PDa to the floating diffusion FD is accumulated in the floating diffusion FD. Further, in the read period REAa, the selection signal SEL is maintained at a high level, and a voltage corresponding to the signal charge accumulated in the floating diffusion FD is output to the vertical signal line VL.

図9は、図7に示した焦点検出用画素PXFの動作の一例を示している。なお、図9は、蓄積部MEMに電荷を蓄積しないときの焦点検出用画素PXFの動作の一例を示している。図中の破線の意味は、上述した図8と同じである。 FIG. 9 shows an example of the operation of the focus detection pixel PXF shown in FIG. FIG. 9 shows an example of the operation of the focus detection pixel PXF when no charge is accumulated in the accumulation unit MEM. The meaning of the broken line in the figure is the same as in FIG.

リセット期間RESbでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、高レベルに一定期間維持される(リセット期間RESbのうちの左側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSはオン(ON)状態に一定期間維持される。高レベルのメモリ転送信号TX_fが蓄積部MEMのゲート電極GTに印加されているため、蓄積部MEMのポテンシャルは、フォトダイオードPDbのポテンシャルより電源VDD側に維持される。これにより、フォトダイオードPDbに蓄積された電荷は、少なくとも蓄積部MEMに移動する。 In the reset period RESb, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a high level for a certain period (the left side diagram of the reset period RESb). Accordingly, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in an on state for a certain period. Since the high-level memory transfer signal TX_f is applied to the gate electrode GT of the storage unit MEM, the potential of the storage unit MEM is maintained closer to the power supply VDD than the potential of the photodiode PDb. Thereby, the electric charge accumulated in the photodiode PDb moves to at least the accumulation unit MEM.

メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTが高レベルに一定期間維持された後、メモリ転送信号TX_fは、高レベルから低レベルに変化する。そして、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、それぞれ低レベル、高レベルおよび高レベルに維持される(リセット期間RESbのうちの右側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオフ(OFF)状態、オン状態およびオン状態に維持される。 After the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a high level for a certain period, the memory transfer signal TX_f changes from a high level to a low level. Then, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level, a high level, and a high level, respectively (the diagram on the right side of the reset period RESb). Thereby, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in the off state, the on state, and the on state, respectively.

低レベルのメモリ転送信号TX_fが蓄積部MEMのゲート電極GTに印加されているため、蓄積部MEMのポテンシャルは、フローティングディフュージョンFDのポテンシャルより接地電圧GND側に維持される。これにより、蓄積部MEMおよびフローティングディフュージョンFDに蓄積された電荷は、電源VDDに排出される。この結果、リセット期間RESbでは、フォトダイオードPDb、蓄積部MEMおよびフローティングディフュージョンFDに蓄積された電荷は、電源VDDに排出される。 Since the low level memory transfer signal TX_f is applied to the gate electrode GT of the storage unit MEM, the potential of the storage unit MEM is maintained closer to the ground voltage GND than the potential of the floating diffusion FD. As a result, the charges accumulated in the accumulation unit MEM and the floating diffusion FD are discharged to the power supply VDD. As a result, in the reset period RESb, the charges accumulated in the photodiode PDb, the accumulation unit MEM, and the floating diffusion FD are discharged to the power supply VDD.

露光期間EXPbでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、低レベルに維持され、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSはオフ状態に維持される。これにより、フォトダイオードPDbは、入射光に応じて電荷を生成し、生成した電荷を蓄積する。 In the exposure period EXPb, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level, and the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in an off state. Thereby, the photodiode PDb generates charges according to the incident light, and accumulates the generated charges.

転送期間TRAbでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、それぞれ高レベル、高レベルおよび低レベルに一定期間維持される(転送期間TRAbのうちの左側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオン状態、オン状態およびオフ状態に一定期間維持される。高レベルのメモリ転送信号TX_fが蓄積部MEMのゲート電極GTに印加されているため、蓄積部MEMのポテンシャルは、フォトダイオードPDbのポテンシャルより電源VDD側に維持される。これにより、フォトダイオードPDbに蓄積された電荷は、蓄積部MEMに移動する。 In the transfer period TRAb, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are respectively maintained at a high level, a high level, and a low level for a certain period (the left side diagram of the transfer period TRAb). As a result, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in an on state, an on state, and an off state, respectively, for a certain period. Since the high-level memory transfer signal TX_f is applied to the gate electrode GT of the storage unit MEM, the potential of the storage unit MEM is maintained closer to the power supply VDD than the potential of the photodiode PDb. Thereby, the electric charge accumulated in the photodiode PDb moves to the accumulation unit MEM.

メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTがそれぞれ高レベル、高レベルおよび低レベルに一定期間維持された後、メモリ転送信号TX_fは、高レベルから低レベルに変化する。そして、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、それぞれ低レベル、高レベルおよび低レベルに維持される(転送期間TRAbのうちの右側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオフ状態、オン状態およびオフ状態に維持される。 After the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are respectively maintained at a high level, a high level, and a low level for a certain period, the memory transfer signal TX_f changes from a high level to a low level. Then, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level, a high level, and a low level, respectively (the diagram on the right side of the transfer period TRAb). Thereby, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in the off state, the on state, and the off state, respectively.

低レベルのメモリ転送信号TX_fが蓄積部MEMのゲート電極GTに印加されているため、蓄積部MEMのポテンシャルは、フローティングディフュージョンFDのポテンシャルより接地電圧GND側に維持される。これにより、フォトダイオードPDbから蓄積部MEMに転送された電荷は、フローティングディフュージョンFDに移動する。この結果、転送期間TRAbでは、フォトダイオードPDbに蓄積された電荷は、フローティングディフュージョンFDに転送される。なお、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。 Since the low level memory transfer signal TX_f is applied to the gate electrode GT of the storage unit MEM, the potential of the storage unit MEM is maintained closer to the ground voltage GND than the potential of the floating diffusion FD. Thereby, the charge transferred from the photodiode PDb to the storage unit MEM moves to the floating diffusion FD. As a result, in the transfer period TRAb, the charge accumulated in the photodiode PDb is transferred to the floating diffusion FD. Since the reset transistor MRS is in an off state, the charge transferred to the floating diffusion FD is not discharged to the power supply VDD.

読み出し期間REAbでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、低レベルに維持され、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ状態に維持される。これにより、フォトダイオードPDbからフローティングディフュージョンFDに転送された電荷は、フローティングディフュージョンFDに蓄積される。さらに、読み出し期間REAbでは、選択信号SELが高レベルに維持され、フローティングディフュージョンFDに蓄積された信号電荷に応じた電圧が垂直信号線VLに出力される。 In the read period REAb, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level, and the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in an off state. Thereby, the charge transferred from the photodiode PDb to the floating diffusion FD is accumulated in the floating diffusion FD. Further, in the read period REAb, the selection signal SEL is maintained at a high level, and a voltage corresponding to the signal charge accumulated in the floating diffusion FD is output to the vertical signal line VL.

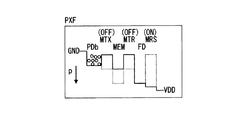

図10は、図7に示した焦点検出用画素PXFの動作の別の例を示している。なお、図10は、蓄積部MEMに電荷を蓄積するときの焦点検出用画素PXFの動作の一例を示している。図中の破線の意味は、上述した図8と同じである。また、図10に示した焦点検出用画素PXFの動作では、露光期間EXPbの後にメモリ転送期間METRの動作が実施され、図9示した転送期間TRAbの動作の代わりに転送期間TRAcの動作が実施される。その他の動作は、図9に示した焦点検出用画素PXFの動作と同じである。このため、メモリ転送期間METRおよび転送期間TRAcについて説明する。 FIG. 10 shows another example of the operation of the focus detection pixel PXF shown in FIG. FIG. 10 shows an example of the operation of the focus detection pixel PXF when charges are accumulated in the accumulation unit MEM. The meaning of the broken line in the figure is the same as in FIG. In the operation of the focus detection pixel PXF shown in FIG. 10, the operation of the memory transfer period METR is performed after the exposure period EXPb, and the operation of the transfer period TRAc is performed instead of the operation of the transfer period TRAb shown in FIG. Is done. Other operations are the same as the operations of the focus detection pixel PXF shown in FIG. Therefore, the memory transfer period METR and the transfer period TRAc will be described.

メモリ転送期間METRでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、それぞれ高レベル、低レベルおよび低レベルに一定期間維持される(メモリ転送期間METRのうちの左側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオン状態、オフ状態およびオフ状態に一定期間維持される。 In the memory transfer period METR, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a high level, a low level, and a low level for a certain period of time (the left diagram in the memory transfer period METR). As a result, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained for a certain period in an on state, an off state, and an off state, respectively.

高レベルのメモリ転送信号TX_fが蓄積部MEMのゲート電極GTに印加されているため、蓄積部MEMのポテンシャルは、フォトダイオードPDbのポテンシャルより電源VDD側に維持される。これにより、フォトダイオードPDbに蓄積された電荷は、蓄積部MEMに移動する。なお、転送トランジスタMTRがオフ状態であるため、蓄積部MEMに転送された電荷は、フローティングディフュージョンFDに移動しない。 Since the high-level memory transfer signal TX_f is applied to the gate electrode GT of the storage unit MEM, the potential of the storage unit MEM is maintained closer to the power supply VDD than the potential of the photodiode PDb. Thereby, the electric charge accumulated in the photodiode PDb moves to the accumulation unit MEM. Note that, since the transfer transistor MTR is in the off state, the charge transferred to the storage unit MEM does not move to the floating diffusion FD.

メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTがそれぞれ高レベル、低レベルおよび低レベルに一定期間維持された後、メモリ転送信号TX_fは、高レベルから低レベルに変化する。そして、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、低レベルに維持される(メモリ転送期間METRのうちの右側の図)。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ状態に維持される。この結果、蓄積部MEMに電荷が蓄積される。このように、メモリ転送期間METRでは、露光期間EXPbにフォトダイオードPDbで生成された電荷が蓄積部MEMに蓄積される。以下、メモリ転送期間METRのうち、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTが低レベルに維持される期間(メモリ転送期間METRのうちの右側の図)を、電荷保持期間とも称する。 After the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are respectively maintained at a high level, a low level, and a low level for a certain period, the memory transfer signal TX_f changes from a high level to a low level. Then, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level (the diagram on the right side of the memory transfer period METR). Thereby, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in the off state. As a result, charges are accumulated in the accumulation unit MEM. Thus, in the memory transfer period METR, charges generated by the photodiode PDb in the exposure period EXPb are accumulated in the accumulation unit MEM. Hereinafter, of the memory transfer period METR, a period during which the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level (the right side of the memory transfer period METR) is also referred to as a charge holding period.

転送期間TRAcでは、メモリ転送信号TX_f、転送信号TRおよびリセット信号RSTは、それぞれ低レベル、高レベルおよび低レベルに維持される。したがって、転送期間TRAcでは、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオフ状態、オン状態およびオフ状態に維持される。これにより、蓄積部MEMに蓄積された電荷(露光期間EXPbにフォトダイオードPDbで生成された電荷)は、フローティングディフュージョンFDに転送される。なお、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。 In the transfer period TRAc, the memory transfer signal TX_f, the transfer signal TR, and the reset signal RST are maintained at a low level, a high level, and a low level, respectively. Therefore, in the transfer period TRAc, the memory transfer transistor MTX, the transfer transistor MTR, and the reset transistor MRS are maintained in the off state, the on state, and the off state, respectively. As a result, charges accumulated in the accumulation unit MEM (charges generated by the photodiode PDb during the exposure period EXPb) are transferred to the floating diffusion FD. Since the reset transistor MRS is in an off state, the charge transferred to the floating diffusion FD is not discharged to the power supply VDD.

図11は、図5に示した画素アレイARYの動作の一例を示している。なお、図11は、焦点検出用画素PXFの露光期間EXPbが撮像用画素PXIの露光期間EXPaと同じときの画素アレイARYの動作の一例を示している。すなわち、図11は、蓄積部MEMに電荷を蓄積しないときの画素アレイARYの動作の一例を示している。図中の星印は、焦点検出用画素PXFを含む行を示している。例えば、焦点検出用画素PXFは、4行目(L4)に配置されている。したがって、4行目(L4)では、上側に撮像用画素PXIの動作を示し、下側に焦点検出用画素PXFの動作を示している。 FIG. 11 shows an example of the operation of the pixel array ARY shown in FIG. FIG. 11 shows an example of the operation of the pixel array ARY when the exposure period EXPb of the focus detection pixel PXF is the same as the exposure period EXPa of the imaging pixel PXI. That is, FIG. 11 shows an example of the operation of the pixel array ARY when charges are not accumulated in the accumulation unit MEM. Stars in the figure indicate rows including focus detection pixels PXF. For example, the focus detection pixels PXF are arranged in the fourth row (L4). Therefore, in the fourth row (L4), the operation of the imaging pixel PXI is shown on the upper side, and the operation of the focus detection pixel PXF is shown on the lower side.

垂直走査回路VSCは、例えば、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順に実施される一連の動作(上述した図8に示した動作)を、撮像用画素PXIに対して行毎に順次実施する。例えば、垂直走査回路VSCは、先ず、1行目(L1)の撮像用画素PXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。これにより、読み出し期間REAaでは、1行目(L1)の各列の撮像用画素PXIの出力信号OUT(OUT(1)、OUT(2)、・・・、OUT(m))が出力される。 The vertical scanning circuit VSC performs, for example, a series of operations (the operations illustrated in FIG. 8 described above) performed on the imaging pixel PXI in the order of the reset period RESa, the exposure period EXPa, the transfer period TRAa, and the readout period REAa. Sequentially for each row. For example, the vertical scanning circuit VSC first performs each operation on the imaging pixels PXI in the first row (L1) in the order of the reset period RESa, the exposure period EXPa, the transfer period TRAa, and the readout period REAa. Thereby, in the readout period REAa, the output signals OUT (OUT (1), OUT (2),..., OUT (m)) of the imaging pixels PXI in each column of the first row (L1) are output. .

そして、垂直走査回路VSCは、例えば、1行目(L1)のリセット期間RESaが終了した後に、2行目(L2)の撮像用画素PXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。例えば、1行目(L1)の読み出し期間REAaが終了した後に2行目(L2)の転送期間TRAaが開始されるように、2行目(L2)のリセット期間RESaは、開始される。ここで、例えば、1行目(L1)のリセット期間RESaの開始から最終行(Ln)の読み出し期間REAaの終了までが、1フレームFRMである。 Then, for example, after the reset period RESa of the first row (L1) ends, the vertical scanning circuit VSC performs the reset period RESa, the exposure period EXPa, and the transfer period for the imaging pixel PXI of the second row (L2). Each operation is performed in the order of TRAa and readout period REAa. For example, the reset period RESa of the second row (L2) is started so that the transfer period TRAa of the second row (L2) is started after the reading period REAa of the first row (L1) ends. Here, for example, one frame FRM is from the start of the reset period RESa of the first row (L1) to the end of the read period REAa of the last row (Ln).

さらに、垂直走査回路VSCは、例えば、リセット期間RESb、露光期間EXPb、転送期間TRAb、読み出し期間REAbの順に実施される一連の動作(上述した図9に示した動作)を、焦点検出用画素PXFに対して実施する。例えば、垂直走査回路VSCは、4行目(L4)の撮像用画素PXIの動作に合わせて、リセット期間RESb、露光期間EXPb、転送期間TRAb、読み出し期間REAbのそれぞれの動作を、4行目(L4)の焦点検出用画素PXFに対して実施する。 Further, the vertical scanning circuit VSC performs, for example, a series of operations (the operations illustrated in FIG. 9 described above) performed in the order of the reset period RESb, the exposure period EXPb, the transfer period TRAb, and the readout period REAb, as shown in FIG. It carries out against. For example, the vertical scanning circuit VSC performs the operations of the reset period RESb, the exposure period EXPb, the transfer period TRAb, and the readout period REAb in accordance with the operations of the imaging pixels PXI in the fourth row (L4). This is performed for the focus detection pixel PXF of L4).

このように、この実施形態では、焦点検出用画素PXFの蓄積部MEMに電荷を蓄積しないとき、焦点検出用画素PXFの動作を撮像用画素PXIの動作に合わせて実施できるため、画素アレイARYからの信号の読み出し動作を簡易にできる。なお、垂直走査回路VSCは、図16に示すように、転送期間TRAa、TRAbの前(露光期間EXPa、EXPb)に選択信号SELを高レベルにし、相関二重サンプリングのためのノイズ信号を読み出してもよい。ここで、ノイズ信号は、例えば、画素PXI、PXFのリセットノイズ成分等を含む固定ノイズ成分を示す信号である。 As described above, in this embodiment, when the charge is not accumulated in the accumulation unit MEM of the focus detection pixel PXF, the operation of the focus detection pixel PXF can be performed in accordance with the operation of the imaging pixel PXI. The signal read operation can be simplified. As shown in FIG. 16, the vertical scanning circuit VSC sets the selection signal SEL to the high level before the transfer periods TRAa and TRAb (exposure periods EXPa and EXPb), and reads out the noise signal for correlated double sampling. Also good. Here, the noise signal is a signal indicating a fixed noise component including, for example, a reset noise component of the pixels PXI and PXF.

また、ノイズ信号等を読み出さない場合、各行の転送期間TRA(TRAa、TRAb)は、前の行の読み出し期間REA(REAa、REAb)が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。 Further, when the noise signal or the like is not read, the transfer period TRA (TRAa, TRAb) of each row may be started before the read period REA (REAa, REAb) of the previous row ends. For example, the vertical scanning circuit VSC may start the transfer period TRA so that the start of the read period REA for each row is approximately the same as the end of the read period REA for the previous row.

図12は、図5に示した画素アレイARYの動作の別の例を示している。なお、図12は、焦点検出用画素PXFの露光期間EXPbが撮像用画素PXIの露光期間EXPaより短いときの画素アレイARYの動作の一例を示している。すなわち、図12は、蓄積部MEMに電荷を蓄積するときの画素アレイARYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。 FIG. 12 shows another example of the operation of the pixel array ARY shown in FIG. FIG. 12 shows an example of the operation of the pixel array ARY when the exposure period EXPb of the focus detection pixel PXF is shorter than the exposure period EXPa of the imaging pixel PXI. That is, FIG. 12 shows an example of the operation of the pixel array ARY when charges are accumulated in the accumulation unit MEM. The meaning of the star in the figure is the same as in FIG. The operation of the imaging pixel PXI is the same as that in FIG. Therefore, the operation of the focus detection pixel PXF will be described.

垂直走査回路VSCは、例えば、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順に実施される一連の動作(上述した図10に示した動作)を、焦点検出用画素PXFに対して実施する。例えば、垂直走査回路VSCは、4行目(L4)の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施する。 The vertical scanning circuit VSC, for example, performs focus detection on a series of operations (the operations shown in FIG. 10 described above) performed in the order of the reset period RESb, the exposure period EXPb, the memory transfer period METR, the transfer period TRAc, and the read period REAb. This is performed for the pixel PXF. For example, the vertical scanning circuit VSC operates on the focus detection pixels PXF in the fourth row (L4) in the order of the reset period RESb, the exposure period EXPb, the memory transfer period METR, the transfer period TRAc, and the readout period REAb. carry out.

例えば、垂直走査回路VSCは、4行目(L4)の撮像用画素PXIの転送期間TRAaと4行目(L4)の焦点検出用画素PXFの転送期間TRAcとが互いに同じタイミングになるように、メモリ転送期間METRの電荷保持期間を調整する。なお、焦点検出用画素PXFのリセット期間RESbの動作は、撮像用画素PXIのリセット期間RESaに合わせて実施されてもよい。このときにも、垂直走査回路VSCは、メモリ転送期間METRの電荷保持期間を調整することにより、焦点検出用画素PXFの転送期間TRAcを撮像用画素PXIの転送期間TRAaに合わせることができる。このように、垂直走査回路VSCは、蓄積部MEMに電荷を蓄積することにより、焦点検出用画素PXFの露光時間(露光期間EXPb)と撮像用画素PXIの露光時間(露光期間EXPa)とをそれぞれ独立に制御する。これにより、この実施形態では、焦点検出用画素PXFの露光を、1フレームFRM内の任意のタイミングで任意の時間実施できる。 For example, the vertical scanning circuit VSC is configured so that the transfer period TRAa of the imaging pixel PXI in the fourth row (L4) and the transfer period TRAc of the focus detection pixel PXF in the fourth row (L4) are at the same timing. The charge retention period of the memory transfer period METR is adjusted. Note that the operation of the reset period RESb of the focus detection pixel PXF may be performed in accordance with the reset period RESa of the imaging pixel PXI. Also at this time, the vertical scanning circuit VSC can adjust the charge holding period of the memory transfer period METR to match the transfer period TRAc of the focus detection pixel PXF with the transfer period TRAa of the imaging pixel PXI. As described above, the vertical scanning circuit VSC accumulates electric charges in the accumulating unit MEM, thereby reducing the exposure time (exposure period EXPb) of the focus detection pixel PXF and the exposure time (exposure period EXPa) of the imaging pixel PXI. Control independently. Thereby, in this embodiment, exposure of the focus detection pixel PXF can be performed at an arbitrary timing within one frame FRM for an arbitrary time.

したがって、この実施形態では、焦点検出用画素PXFの露光期間EXPbが撮像用画素PXIの露光期間EXPaと異なるときにも、焦点検出用画素PXFの転送期間TRAcを撮像用画素PXIの転送期間TRAaに合わせることができる。これにより、この実施形態では、焦点検出用画素PXFの露光期間EXPbが撮像用画素PXIの露光期間EXPaと異なるときにも、焦点検出用画素PXFの読み出し期間REAbを撮像用画素PXIの読み出し期間REAaに合わせることができる。この結果、この実施形態では、画素アレイARYからの信号の読み出し動作を簡易にできる。 Therefore, in this embodiment, even when the exposure period EXPb of the focus detection pixel PXF is different from the exposure period EXPa of the imaging pixel PXI, the transfer period TRAc of the focus detection pixel PXF is set to the transfer period TRAa of the imaging pixel PXI. Can be matched. Accordingly, in this embodiment, even when the exposure period EXPb of the focus detection pixel PXF is different from the exposure period EXPa of the imaging pixel PXI, the readout period REAb of the focus detection pixel PXF is set as the readout period REAa of the imaging pixel PXI. Can be adapted to As a result, in this embodiment, the signal read operation from the pixel array ARY can be simplified.

なお、垂直走査回路VSCは、図17に示すように、転送期間TRAa、TRAcの前(露光期間EXPa、メモリ転送期間METR)に選択信号SELを高レベルにし、相関二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、フローティングディフュージョンFDに電荷を転送するタイミングが撮像用画素PXIと焦点検出用画素PXFとで互いに同じであるため、簡易にノイズ信号を読み出すことができる。 As shown in FIG. 17, the vertical scanning circuit VSC sets the selection signal SEL to a high level before the transfer periods TRAa and TRAc (exposure period EXPa and memory transfer period METR), and generates a noise signal for correlated double sampling. May be read out. In this embodiment, since the timing for transferring charges to the floating diffusion FD is the same between the imaging pixel PXI and the focus detection pixel PXF, a noise signal can be easily read out.

また、ノイズ信号等を読み出さない場合、各行の転送期間TRA(TRAa、TRAc)は、前の行の読み出し期間REA(REAa、REAb)が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。 Further, when the noise signal or the like is not read, the transfer period TRA (TRAa, TRAc) of each row may be started before the read period REA (REAa, REAb) of the previous row ends. For example, the vertical scanning circuit VSC may start the transfer period TRA so that the start of the read period REA for each row is approximately the same as the end of the read period REA for the previous row.

図13は、複数の行に焦点検出用画素PXFが配置された画素アレイARYの動作の一例を示している。なお、図13は、4行目(L4)および7行目(L7)に焦点検出用画素PXFが配置された画素アレイARYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。なお、例えば、焦点検出用画素PXFの露光期間EXPbは、撮像用画素PXIの露光期間EXPaより短い。 FIG. 13 shows an example of the operation of the pixel array ARY in which the focus detection pixels PXF are arranged in a plurality of rows. FIG. 13 shows an example of the operation of the pixel array ARY in which the focus detection pixels PXF are arranged in the fourth row (L4) and the seventh row (L7). The meaning of the star in the figure is the same as in FIG. The operation of the imaging pixel PXI is the same as that in FIG. Therefore, the operation of the focus detection pixel PXF will be described. For example, the exposure period EXPb of the focus detection pixel PXF is shorter than the exposure period EXPa of the imaging pixel PXI.

垂直走査回路VSCは、例えば、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順に実施される一連の動作(上述した図10に示した動作)を、4行目(L4)および7行目(L7)の焦点検出用画素PXFに対して実施する。 The vertical scanning circuit VSC performs, for example, a series of operations (the operations shown in FIG. 10 described above) performed in the order of the reset period RESb, the exposure period EXPb, the memory transfer period METR, the transfer period TRAc, and the readout period REAb in four rows. This is performed for the focus detection pixels PXF in the eye (L4) and the seventh row (L7).

例えば、垂直走査回路VSCは、4行目(L4)の撮像用画素PXIの転送期間TRAaと4行目(L4)の焦点検出用画素PXFの転送期間TRAcとが互いに同じタイミングになるように、4行目(L4)の焦点検出用画素PXFのメモリ転送期間METRの電荷保持期間を調整する。さらに、垂直走査回路VSCは、4行目(L4)および7行目(L7)の焦点検出用画素PXFのそれぞれの露光期間EXPbが互いに同じタイミングになるように、7行目(L7)の焦点検出用画素PXFに対して、リセット期間RESbの動作を開始する。そして、垂直走査回路VSCは、例えば、7行目(L7)の撮像用画素PXIの転送期間TRAaと7行目(L7)の焦点検出用画素PXFの転送期間TRAcとが互いに同じタイミングになるように、7行目(L7)の焦点検出用画素PXFのメモリ転送期間METRの電荷保持期間を調整する。 For example, the vertical scanning circuit VSC is configured so that the transfer period TRAa of the imaging pixel PXI in the fourth row (L4) and the transfer period TRAc of the focus detection pixel PXF in the fourth row (L4) are at the same timing. The charge holding period of the memory transfer period METR of the focus detection pixel PXF in the fourth row (L4) is adjusted. Further, the vertical scanning circuit VSC focuses the seventh row (L7) so that the exposure periods EXPb of the focus detection pixels PXF in the fourth row (L4) and the seventh row (L7) are at the same timing. The operation of the reset period RESb is started for the detection pixel PXF. In the vertical scanning circuit VSC, for example, the transfer period TRAa of the imaging pixel PXI in the seventh row (L7) and the transfer period TRAc of the focus detection pixel PXF in the seventh row (L7) have the same timing. In addition, the charge holding period of the memory transfer period METR of the focus detection pixel PXF in the seventh row (L7) is adjusted.

このように、垂直走査回路VSCは、蓄積部MEMに電荷を蓄積することにより、互いに異なる行に配置された焦点検出用画素PXFの露光タイミングが互いに同じになるように、各行の焦点検出用画素PXFの動作を制御する。すなわち、焦点検出用画素PXFが複数の行に配置されたときにも、垂直走査回路VSCは、複数の焦点検出用画素PXFの露光タイミングが互いに同じになるように、複数の焦点検出用画素PXFの動作を制御する。 As described above, the vertical scanning circuit VSC accumulates charges in the accumulation unit MEM, so that the focus detection pixels PXF arranged in different rows have the same exposure timing, so that the focus detection pixels in each row are the same. Control the operation of PXF. That is, even when the focus detection pixels PXF are arranged in a plurality of rows, the vertical scanning circuit VSC causes the plurality of focus detection pixels PXF to have the same exposure timing. To control the operation.

これにより、この実施形態では、焦点検出時の露光を互いに異なる行に配置された焦点検出用画素PXFで同時に実施できる。この結果、この実施形態では、焦点検出精度を向上できる。さらに、この実施形態では、焦点検出用画素PXFが複数の行に配置されたときにも、焦点検出用画素PXFの読み出し期間REAbを撮像用画素PXIの読み出し期間REAaに簡易に合わせることができるため、画素アレイARYからの信号の読み出し動作を簡易にできる。 Thereby, in this embodiment, exposure at the time of focus detection can be simultaneously performed by the focus detection pixels PXF arranged in different rows. As a result, in this embodiment, focus detection accuracy can be improved. Furthermore, in this embodiment, even when the focus detection pixels PXF are arranged in a plurality of rows, the readout period REAb of the focus detection pixels PXF can be easily matched with the readout period REAa of the imaging pixels PXI. The signal read operation from the pixel array ARY can be simplified.

なお、垂直走査回路VSCは、焦点検出用画素PXFが複数の行に配置されたときにも、図17に示すように、転送期間TRAa、TRAcの前(露光期間EXPa、メモリ転送期間METR)に選択信号SELを高レベルにし、相関二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、焦点検出用画素PXFが複数の行に配置されたときにも、互いに同じ行に配置された焦点検出用画素PXFおよび撮像用画素PXIのそれぞれの転送期間TRAc、TRAaを互いに合わせることができる。したがって、この実施形態では、焦点検出用画素PXFが複数の行に配置されたときにも、簡易にノイズ信号を読み出すことができる。 As shown in FIG. 17, the vertical scanning circuit VSC also precedes the transfer periods TRAa, TRAc (exposure period EXPa, memory transfer period METR), as shown in FIG. 17, even when the focus detection pixels PXF are arranged in a plurality of rows. The noise signal for correlated double sampling may be read by setting the selection signal SEL to a high level. In this embodiment, even when the focus detection pixels PXF are arranged in a plurality of rows, the transfer periods TRAc and TRAa of the focus detection pixels PXF and the imaging pixels PXI arranged in the same row are matched with each other. be able to. Therefore, in this embodiment, a noise signal can be easily read even when the focus detection pixels PXF are arranged in a plurality of rows.

また、ノイズ信号等を読み出さない場合、各行の転送期間TRA(TRAa、TRAc)は、前の行の読み出し期間REA(REAa、REAb)が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。 Further, when the noise signal or the like is not read, the transfer period TRA (TRAa, TRAc) of each row may be started before the read period REA (REAa, REAb) of the previous row ends. For example, the vertical scanning circuit VSC may start the transfer period TRA so that the start of the read period REA for each row is approximately the same as the end of the read period REA for the previous row.

図14は、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときの画素アレイARYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。なお、例えば、焦点検出用画素PXFの露光期間EXPbは、撮像用画素PXIの露光期間EXPaより短い。 FIG. 14 shows an example of the operation of the pixel array ARY when exposure of the focus detection pixel PXF is performed a plurality of times during one frame FRM. The meaning of the star in the figure is the same as in FIG. The operation of the imaging pixel PXI is the same as that in FIG. Therefore, the operation of the focus detection pixel PXF will be described. For example, the exposure period EXPb of the focus detection pixel PXF is shorter than the exposure period EXPa of the imaging pixel PXI.

垂直走査回路VSCは、例えば、4行目(L4)の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施する。なお、1フレームFRM中に実施される焦点検出用画素PXFの露光の回数は、2回に限定されない。この実施形態では、焦点検出用画素PXFの独立露光および独立読み出しが可能であるため、焦点検出用画素PXFの任意時間の露光を、1フレームFRM内で複数回実施できる。 For example, for the focus detection pixels PXF in the fourth row (L4), the vertical scanning circuit VSC includes a reset period RESb, an exposure period EXPb, a memory transfer period METR, a transfer period TRAc, a read period REAb, an exposure period EXPb, and a memory. The respective operations are performed in the order of the transfer period METR, the transfer period TRAc, and the read period REAb. Note that the number of exposures of the focus detection pixels PXF performed during one frame FRM is not limited to two. In this embodiment, since the focus detection pixel PXF can be independently exposed and read out independently, exposure of the focus detection pixel PXF can be performed a plurality of times within one frame FRM.

例えば、図14の動作では、焦点検出用画素PXFの信号(焦点検出に用いられる信号)は、1フレームFRM中に複数回出力される。したがって、この実施形態では、1フレームFRM中に複数回の焦点検出を実施でき、高速な焦点検出を実現できる。なお、垂直走査回路VSCは、1回目のメモリ転送期間METRおよび転送期間TRAcの動作を実施する代わりに、転送期間TRAbの動作を実施してもよい。また、垂直走査回路VSCは、上述した図9に示した動作と上述した図10に示した動作とを1フレームFRM中に順に実施してもよい。あるいは、垂直走査回路VSCは、上述した図9や図10に示した動作を1フレームFRM中に複数回繰り返し実施してもよい。 For example, in the operation of FIG. 14, the signal of the focus detection pixel PXF (the signal used for focus detection) is output a plurality of times during one frame FRM. Therefore, in this embodiment, focus detection can be performed a plurality of times during one frame FRM, and high-speed focus detection can be realized. Note that the vertical scanning circuit VSC may perform the operation of the transfer period TRAb instead of performing the operations of the first memory transfer period METR and the transfer period TRAc. Further, the vertical scanning circuit VSC may sequentially perform the above-described operation illustrated in FIG. 9 and the above-described operation illustrated in FIG. 10 during one frame FRM. Alternatively, the vertical scanning circuit VSC may repeatedly perform the operations shown in FIGS. 9 and 10 a plurality of times during one frame FRM.

ここで、例えば、焦点検出用画素PXFのフォトダイオードPDbに蓄積される電荷の量より多い量の電荷を十分に蓄積できるポテンシャル井戸を焦点検出用画素PXFの蓄積部MEMが有しているとき、1回目の転送期間TRAcおよび読み出し期間REAbの動作は、省かれてもよい。例えば、垂直走査回路VSCは、4行目(L4)の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施してもよい。この場合、フォトダイオードPDbに蓄積された電荷が溢れる前に、フォトダイオードPDbの電荷を蓄積部MEMに転送できる。この結果、この実施形態では、フォトダイオードPDbに蓄積された電荷が溢れることを防止でき、焦点検出精度を向上できる。例えば、この実施形態では、高輝度の被写体の焦点検出および高照度の環境下での焦点検出を精度よく実施できる。 Here, for example, when the storage unit MEM of the focus detection pixel PXF has a potential well that can sufficiently store a larger amount of charge than the amount of charge stored in the photodiode PDb of the focus detection pixel PXF, The operations of the first transfer period TRAc and the read period REAb may be omitted. For example, the vertical scanning circuit VSC applies the reset period RESb, the exposure period EXPb, the memory transfer period METR, the exposure period EXPb, the memory transfer period METR, the transfer period TRAc to the focus detection pixels PXF in the fourth row (L4). Each operation may be performed in the order of the read period REAb. In this case, the charge stored in the photodiode PDb can be transferred to the storage unit MEM before the charge stored in the photodiode PDb overflows. As a result, in this embodiment, the charge accumulated in the photodiode PDb can be prevented from overflowing, and focus detection accuracy can be improved. For example, in this embodiment, focus detection of a high-luminance subject and focus detection in a high-illuminance environment can be performed with high accuracy.

また、垂直走査回路VSCは、4行目(L4)の撮像用画素PXIの転送期間TRAaと4行目(L4)の焦点検出用画素PXFの転送期間TRAcとが互いに同じタイミングになるように、4行目(L4)の焦点検出用画素PXFの2回目のメモリ転送期間METRの電荷保持期間を調整する。これにより、この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、画素アレイARYからの信号の読み出し動作を簡易にできる。 Further, the vertical scanning circuit VSC is configured so that the transfer period TRAa of the imaging pixel PXI in the fourth row (L4) and the transfer period TRAc of the focus detection pixel PXF in the fourth row (L4) are at the same timing. The charge retention period of the second memory transfer period METR of the focus detection pixel PXF in the fourth row (L4) is adjusted. Thereby, in this embodiment, even when the exposure of the focus detection pixel PXF is performed a plurality of times during one frame FRM, the signal reading operation from the pixel array ARY can be simplified.

また、垂直走査回路VSCは、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、図17に示すように、転送期間TRAa、TRAcの前(露光期間EXPa、メモリ転送期間METR)に選択信号SELを高レベルにし、相関二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、焦点検出用画素PXFの転送期間TRAcを撮像用画素PXIの転送期間TRAaに合わせることができる。したがって、この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、簡易にノイズ信号を読み出すことができる。 Further, as shown in FIG. 17, the vertical scanning circuit VSC also performs the exposure before the transfer periods TRAa and TRAc (exposure period EXPa, memory) when the focus detection pixel PXF is exposed a plurality of times during one frame FRM. In the transfer period METR), the selection signal SEL may be set to a high level to read a noise signal for correlated double sampling. In this embodiment, even when the exposure of the focus detection pixel PXF is performed a plurality of times during one frame FRM, the transfer period TRAc of the focus detection pixel PXF can be matched with the transfer period TRAa of the imaging pixel PXI. . Therefore, in this embodiment, the noise signal can be easily read even when the exposure of the focus detection pixel PXF is performed a plurality of times during one frame FRM.

なお、ノイズ信号等を読み出さない場合、各行の転送期間TRA(TRAa、TRAc)は、前の行の読み出し期間REA(REAa、REAb)が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。 When the noise signal or the like is not read, the transfer period TRA (TRAa, TRAc) of each row may be started before the read period REA (REAa, REAb) of the previous row ends. For example, the vertical scanning circuit VSC may start the transfer period TRA so that the start of the read period REA for each row is approximately the same as the end of the read period REA for the previous row.

図15は、焦点検出用画素PXFの露光が複数フレームFRMをまたいで実施されるときの画素アレイARYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。なお、例えば、焦点検出用画素PXFの露光期間EXPbは、撮像用画素PXIの露光期間EXPaより長い。 FIG. 15 shows an example of the operation of the pixel array ARY when exposure of the focus detection pixels PXF is performed across a plurality of frames FRM. The meaning of the star in the figure is the same as in FIG. The operation of the imaging pixel PXI is the same as that in FIG. Therefore, the operation of the focus detection pixel PXF will be described. For example, the exposure period EXPb of the focus detection pixel PXF is longer than the exposure period EXPa of the imaging pixel PXI.

フレームFRM(1)の期間では、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PXIに対して露光期間EXPaの動作を実施しているときに、4行目(L4)の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPbの順にそれぞれの動作を実施する。なお、4行目(L4)の焦点検出用画素PXFの露光期間EXPbの動作は、フレームFRM(2)の途中まで継続される。 In the period of the frame FRM (1), for example, when the vertical scanning circuit VSC is performing the operation of the exposure period EXPa on the imaging pixels PXI in the fourth row (L4), the fourth row (L4). The operations are performed on the focus detection pixels PXF in the order of the reset period RESb and the exposure period EXPb. Note that the operation in the exposure period EXPb of the focus detection pixel PXF in the fourth row (L4) is continued halfway through the frame FRM (2).

例えば、フレームFRM(1)の最後の読み出し期間REAaの動作が最終行(Ln)の撮像用画素PXIに対して実施された後に、フレームFRM(2)の最初のリセット期間RESaの動作が、1行目(L1)の撮像用画素PXIに対して実施される。すなわち、垂直走査回路VSCは、例えば、最終行(Ln)の読み出し期間REAaの後に、1行目(L1)の撮像用画素PXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。 For example, after the operation of the last readout period REAa of the frame FRM (1) is performed on the imaging pixel PXI of the last row (Ln), the operation of the first reset period RESa of the frame FRM (2) is 1 This is performed for the imaging pixel PXI in the row (L1). That is, the vertical scanning circuit VSC, for example, after the read period REAa of the last row (Ln), for the imaging pixel PXI of the first row (L1), the reset period RESa, the exposure period EXPa, the transfer period TRAa, and the readout Each operation is performed in the order of the period REAa.

フレームFRM(2)の期間では、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PXIに対して露光期間EXPaの動作を実施しているときに、4行目(L4)の焦点検出用画素PXFに対する露光期間EXPbの動作を終了する。すなわち、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PXIの動作を制御しているときに、4行目(L4)の焦点検出用画素PXFに対して、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施する。 In the period of the frame FRM (2), the vertical scanning circuit VSC performs, for example, the operation in the exposure period EXPa on the imaging pixels PXI in the fourth line (L4). The operation of the exposure period EXPb for the focus detection pixel PXF is terminated. That is, for example, when the vertical scanning circuit VSC controls the operation of the imaging pixel PXI in the fourth row (L4), the vertical scanning circuit VSC performs a memory transfer period for the focus detection pixel PXF in the fourth row (L4). Each operation is performed in the order of METR, transfer period TRAc, and read period REAb.

この実施形態では、焦点検出用画素PXFの独立露光および独立読み出しが可能であるため、焦点検出用画素PXFの任意時間の露光を、複数フレームFRMにまたいで実施できる。このように、この実施形態では、複数フレームFRMをまたいで焦点検出用画素PXFの露光を実施することにより、撮像用画素PXIの露光時間に拘わらず、長時間の露光を焦点検出用画素PXFに対して実施できる。これにより、この実施形態では、低輝度の被写体の焦点検出および低照度の環境下での焦点検出を精度よく実施できる。 In this embodiment, since the focus detection pixel PXF can be independently exposed and read out independently, the focus detection pixel PXF can be exposed at any time over a plurality of frames FRM. As described above, in this embodiment, by performing exposure of the focus detection pixel PXF across a plurality of frames FRM, long exposure is performed on the focus detection pixel PXF regardless of the exposure time of the imaging pixel PXI. Can be implemented. Thereby, in this embodiment, focus detection of a low-luminance subject and focus detection in a low-illuminance environment can be performed with high accuracy.