JP5875422B2 - Image processing apparatus and image processing apparatus control method - Google Patents

Image processing apparatus and image processing apparatus control method Download PDFInfo

- Publication number

- JP5875422B2 JP5875422B2 JP2012060206A JP2012060206A JP5875422B2 JP 5875422 B2 JP5875422 B2 JP 5875422B2 JP 2012060206 A JP2012060206 A JP 2012060206A JP 2012060206 A JP2012060206 A JP 2012060206A JP 5875422 B2 JP5875422 B2 JP 5875422B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- image data

- processing apparatus

- field

- image

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

本発明は、画像処理装置及び画像処理装置の制御方法に関する。 The present invention relates to an image processing apparatus and a control method for the image processing apparatus.

従来、インターレース画像データをプログレッシブ画像データに変換するIP変換処理を行う画像処理装置がある。そのような画像処理装置では、第1の周期でインターレース画像データが入力され、第2の周期でIP変換処理が行われる。第1の周期は、例えば、入力されるインターレース画像データの垂直同期信号(入力Vsync)の周期である。第2の周期は、例えば、表示するプログレッシブ画像データの垂直同期信号(出力Vsync)の周期である。 2. Description of the Related Art Conventionally, there is an image processing apparatus that performs IP conversion processing for converting interlaced image data into progressive image data. In such an image processing apparatus, interlaced image data is input in a first cycle, and IP conversion processing is performed in a second cycle. The first period is, for example, the period of the vertical synchronization signal (input Vsync) of the input interlaced image data. The second period is, for example, the period of the vertical synchronization signal (output Vsync) of the progressive image data to be displayed.

また、上記画像処理装置には、IP変換処理を行うIP変換処理部と、IP変換処理部から出力されたプログレッシブ画像データにスケーリング処理を施すスケーリング処理部との間にフレームメモリが設けられているものと、いないものとがある。スケーリング処理は、IP変換処理部から出力されたプログレッシブ画像データを、設定された倍率で拡大または縮小する処理である。

図2(a)は、IP変換処理部とスケーリング処理部の間にフレームメモリが設けられた従来の画像処理装置の構成を示す図である。このような構成の場合、IP変換処理部は、前段のフレームメモリ201からインターレース画像データを読み出し、IP変換処理を行う。そして、IP変換処理部は、IP変換処理の結果(プログレッシブ画像データ)を、後段のフレームメモリ202に書き込む。スケーリング処理部は、フレームメモリ202から、プログレッシブ画像データを読み出し、スケーリング処理を行う。

図2(b)は、IP変換処理部とスケーリング処理部の間にフレームメモリが設けられていない従来の画像処理装置の構成を示す図である。このような構成の場合、IP変換処理部は、フレームメモリ203からインターレース画像データを読み出し、IP変換処理を行う。そして、IP変換処理部は、プログレッシブ画像データのライン(スケーリング処理で必要なライン)のデータ(ラインデータ)を、プログレッシブタイミングでスケーリング処理部へ出力する。プログレッシブタイミングは、スケーリング処理後のプログレッシブ画像データの水平同期信号に同期したタイミングである。スケーリング処理部は、入力されたラインデータを用いて、スケーリング処理後の1ライン分のプログレッシブ画像データを生成する。

図2(b)の構成では、図2(a)の構成に比べフレームメモリの数を少なくすることができ、製造コストを低減することができる。

The image processing apparatus includes a frame memory between an IP conversion processing unit that performs IP conversion processing and a scaling processing unit that performs scaling processing on progressive image data output from the IP conversion processing unit. There are things that are not and those that are not. The scaling process is a process of enlarging or reducing the progressive image data output from the IP conversion processing unit at a set magnification.

FIG. 2A is a diagram illustrating a configuration of a conventional image processing apparatus in which a frame memory is provided between the IP conversion processing unit and the scaling processing unit. In the case of such a configuration, the IP conversion processing unit reads interlaced image data from the

FIG. 2B is a diagram illustrating a configuration of a conventional image processing apparatus in which no frame memory is provided between the IP conversion processing unit and the scaling processing unit. In the case of such a configuration, the IP conversion processing unit reads interlaced image data from the

In the configuration of FIG. 2B, the number of frame memories can be reduced compared to the configuration of FIG. 2A, and the manufacturing cost can be reduced.

ここで、入力Vsyncと出力Vsyncが異なることがある(インターレース画像データの入力装置側とプログレッシブ画像データの出力装置側とでクロック周波数に差がある場合など)。例えば、入力映像を入力Vsyncに同期してフレームメモリに書き込み、内部で生成した出力Vsyncに同期して読み出した場合には、入力Vsyncと出力Vsyncが異なる。

入力Vsyncと出力Vsyncが異なる場合に、入力Vsyncと出力Vsyncの位相差を吸収するフレーム同期制御を行うと、「フィールドスキップ」と「フィールドリピート」が発生する。「フィールドスキップ」は、或るフィールドを飛ばして、次のフィールドのインターレース画像データをIP変換処理の処理対象(IP変換処理対象)とするものである。「フィールドリピート」は、同じフィールドのインターレース画像データを2回続けてIP変換処理対象とするものである。以下、「フィールドスキップ」と「フィールドリピート」を「追い越し」と記載する。

Here, the input Vsync and the output Vsync may be different (for example, when there is a difference in clock frequency between the interlaced image data input device side and the progressive image data output device side). For example, when the input video is written in the frame memory in synchronization with the input Vsync and read out in synchronization with the internally generated output Vsync, the input Vsync and the output Vsync are different.

When the frame synchronization control is performed to absorb the phase difference between the input Vsync and the output Vsync when the input Vsync and the output Vsync are different, “field skip” and “field repeat” are generated. “Field skip” skips a certain field and sets interlaced image data of the next field as a processing target (IP conversion processing target) of the IP conversion processing. “Field repeat” is to subject interlaced image data in the same field twice as an IP conversion processing target. Hereinafter, “field skip” and “field repeat” are referred to as “overtaking”.

IP変換処理部では、例えば、補間画素(インターレース画像データに存在しない画素)を生成することにより、インターレース画像データがプログレッシブ画像データに変換される。補間画素を生成する処理には、フィールド内補間処理とフィールド間補間処理とがある。

図3(a)は、フィールド内補間処理の一例を示す図である。図3(b)は、フィールド間補間処理の一例を示す図である。

フィールド内補間処理では、現在のIP変換処理対象であるインターレース画像データの画素を用いて、補間画素が生成される。例えば、図3(a)に示すように、補間画素の生成位置の上下に隣接する画素を用いて補間画素が生成される。

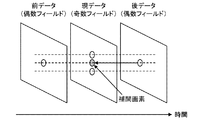

フィールド間補間処理では、現データと異なるフィールドのインターレース画像データの画素を用いて、補間画素が生成される。例えば、図3(b)に示すように、1つ前に処理対象とされたインターレース画像データ(前データ)の画素であって、補間画素の生成位置と同じ位置の画素を用いて補間画素が生成される。

In the IP conversion processing unit, for example, interlaced image data is converted into progressive image data by generating interpolation pixels (pixels that do not exist in the interlaced image data). The process for generating the interpolation pixel includes an intra-field interpolation process and an inter-field interpolation process.

FIG. 3A is a diagram illustrating an example of intra-field interpolation processing. FIG. 3B is a diagram illustrating an example of inter-field interpolation processing.

In the intra-field interpolation process, an interpolated pixel is generated using a pixel of interlaced image data that is the current IP conversion process target. For example, as illustrated in FIG. 3A, an interpolation pixel is generated using pixels adjacent above and below the interpolation pixel generation position.

In inter-field interpolation processing, interpolated pixels are generated using pixels of interlaced image data in a field different from the current data. For example, as shown in FIG. 3B, the interpolated pixel is the pixel of the interlaced image data (previous data) that was the previous processing target, and the pixel at the same position as the interpolation pixel generation position is used. Generated.

上述した「追い越し」が発生すると、上述したフィールド間補間処理が行えなかったり、上述したフィールド間補間処理を行った場合に画像が劣化したりすることがある。

図4を用いて、「追い越し」が発生した場合の従来のフィールド間補間処理について説明する。奇数フィールドのインターレース画像データは、奇数番目のラインのみで構成される。偶数フィールドのインターレース画像データは、偶数番目のラインのみで構成される。

「追い越し」が発生すると、図4に示すように、IP変換処理において、現データと前データの両方が奇数フィールドとなったり、それらの両方が偶数フィールドとなったりしてしまう。この場合、前データには、補間画素の生成位置と同じ位置の画素は存在しないため、図3(b)に示すようなフィールド間補間処理を行うことはできない。もしくは、補間画素の生成位置と異なる位置の画素が誤って使用され、補間画素が生成されてしまう。そのような誤った画素の使用は、表示画像の劣化を招く。

When the “overtaking” described above occurs, the inter-field interpolation processing described above may not be performed, or the image may deteriorate when the above-described inter-field interpolation processing is performed.

A conventional inter-field interpolation process when “overtaking” occurs will be described with reference to FIG. 4. The interlaced image data in the odd field is composed of only odd-numbered lines. The interlaced image data in the even field is composed of only even lines.

When “overtaking” occurs, as shown in FIG. 4, in the IP conversion process, both the current data and the previous data become odd fields, or both of them become even fields. In this case, since there is no pixel at the same position as the interpolation pixel generation position in the previous data, inter-field interpolation processing as shown in FIG. 3B cannot be performed. Alternatively, a pixel at a position different from the generation position of the interpolation pixel is erroneously used, and an interpolation pixel is generated. Such erroneous use of pixels leads to degradation of the display image.

従来、「追い越し」が生じた際に、一定フレーム期間、2フィールドのインターレース画像データのそれぞれからプログレッシブ画像データと同サイズの中間画像を作成し、作成した2つの中間画像をαブレンドする技術が提案されている(特許文献1)。 Conventionally, when "overtaking" occurs, a technique has been proposed in which an intermediate image of the same size as progressive image data is created from each of interlaced image data of two frames for a certain frame period, and the two created intermediate images are alpha blended (Patent Document 1).

しかしながら、上述した従来の技術では、複数フレームに渡ってαブレンドされた画像が表示されるため、補間ライン(補間画素のライン)に違和感のある画像が長時間表示されてしまう。 However, in the above-described conventional technology, an image that is α-blended over a plurality of frames is displayed, so that an image having a sense of incongruity on the interpolation line (interpolation pixel line) is displayed for a long time.

本発明は、「追い越し」が発生した場合にも、フィールド間補間処理を適切に行うことのできる技術を提供することを目的とする。 An object of the present invention is to provide a technique capable of appropriately performing inter-field interpolation processing even when “overtaking” occurs.

本発明の画像処理装置は、

偶数フィールドのインターレース画像データと、奇数フィールドのインターレース画像データとが第1の周期で交互に入力され、前記第1の周期と異なる第2の周期で、入力されたインターレース画像データを補間によりプログレッシブ画像データに変換するIP変換処理を行う画像処理装置であって、

インターレース画像データが入力されるタイミングと、前記インターレース画像データに対する前記IP変換処理を行うタイミングとの差が所定値以下となるように、前記IP変換処理の処理対象とするインターレース画像データを決定する決定手段と、

現在の処理対象のインターレース画像データである現データと、前記現データの1つ前に処理対象とされたインターレース画像データである前データ、及び、前記現データの1つ後に処理対象とされるインターレース画像データである後データのうちの一方のデータとを用いてフィールド間補間処理を行い、前記現データをプログレッシブ画像データに変換する変換手段と、

を有し、

前記変換手段は、前記現データと、前記前データ及び前記後データのうちの前記一方のデータとの両方が偶数フィールドまたは奇数フィールドであった場合に、前記現データと、前記前データ及び前記後データのうちの他方のデータとを用いてフィールド間補間処理を行う

ことを特徴とする。

The image processing apparatus of the present invention

Even field interlaced image data and odd field interlaced image data are alternately input in a first period, and the interlaced image data input in a second period different from the first period is a progressive image by interpolation. An image processing apparatus that performs IP conversion processing for converting data,

Determination to determine interlaced image data to be processed by the IP conversion process so that a difference between a timing at which the interlaced image data is input and a timing at which the IP conversion process is performed on the interlaced image data is equal to or less than a predetermined value. Means,

Current data that is the current interlaced image data to be processed, previous data that is the interlaced image data that was processed immediately before the current data, and the interlace that is processed after the current data Conversion means for performing inter-field interpolation processing using one of the subsequent data that is image data, and converting the current data into progressive image data;

Have

The converting means, when both the current data and the one of the previous data and the subsequent data are even fields or odd fields, the current data, the previous data, and the subsequent data. Inter-field interpolation processing is performed using the other data of the data.

本発明の画像処理装置の制御方法は、

偶数フィールドのインターレース画像データと、奇数フィールドのインターレース画像データとが第1の周期で交互に入力され、前記第1の周期と異なる第2の周期で、入力されたインターレース画像データを補間によりプログレッシブ画像データに変換するIP変換処理を行う画像処理装置の制御方法であって、

インターレース画像データが入力されるタイミングと、前記インターレース画像データに対する前記IP変換処理を行うタイミングとの差が所定値以下となるように、前記IP変換処理の処理対象とするインターレース画像データを決定する決定ステップと、

現在の処理対象のインターレース画像データである現データと、前記現データの1つ前に処理対象とされたインターレース画像データである前データ、及び、前記現データの1つ後に処理対象とされるインターレース画像データである後データのうちの一方のデータとを用いてフィールド間補間処理を行い、前記現データをプログレッシブ画像データに変換する変換ステップと、

を有し、

前記変換ステップでは、前記現データと、前記前データ及び前記後データのうちの前記一方のデータとの両方が偶数フィールドまたは奇数フィールドであった場合に、前記現データと、前記前データ及び前記後データのうちの他方のデータとを用いてフィールド間補間処理が行われる

ことを特徴とする。

The control method of the image processing apparatus of the present invention includes:

Even field interlaced image data and odd field interlaced image data are alternately input in a first period, and the interlaced image data input in a second period different from the first period is a progressive image by interpolation. A method for controlling an image processing apparatus that performs IP conversion processing for converting data,

Determination to determine interlaced image data to be processed by the IP conversion process so that a difference between a timing at which the interlaced image data is input and a timing at which the IP conversion process is performed on the interlaced image data is equal to or less than a predetermined value. Steps,

Current data that is the current interlaced image data to be processed, previous data that is the interlaced image data that was processed immediately before the current data, and the interlace that is processed after the current data A conversion step of performing inter-field interpolation using one of the subsequent data that is image data, and converting the current data into progressive image data;

Have

In the converting step, when both the current data and the one of the previous data and the subsequent data are even fields or odd fields, the current data, the previous data, and the subsequent data Inter-field interpolation processing is performed using the other data of the data.

本発明によれば、「追い越し」が発生した場合にも、フィールド間補間処理を適切に行うことができる。 According to the present invention, inter-field interpolation processing can be appropriately performed even when “overtaking” occurs.

<実施例1>

以下、本実施例に係る画像処理装置及びその制御方法について説明する。本実施例に係る画像処理装置には、偶数フィールドのインターレース画像データと、奇数フィールドのインターレース画像データとが、第1の周期で交互に入力される。そして、本実施例に係る画像処理装置は、第1の周期と異なる第2の周期で、入力されたインターレース画像データを補間によりプログレッシブ画像データに変換する。

偶数フィールドのインターレース画像データは、偶数番目のラインのみで構成される。奇数フィールドのインターレース画像データは、奇数番目のラインのみで構成される。第1の周期は、例えば、入力されるインターレース画像データの垂直同期信号の周期である。第2の周期は、例えば、表示するプログレッシブ画像データ(本実施例では、拡大処理や縮小処理などのスケーリング処理が施されたプログレッシブ画像データ)の垂直同期信号の周期である。

<Example 1>

Hereinafter, an image processing apparatus and a control method thereof according to the present embodiment will be described. In the image processing apparatus according to the present embodiment, even-field interlaced image data and odd-field interlaced image data are alternately input in the first cycle. The image processing apparatus according to the present embodiment converts the input interlaced image data into progressive image data by interpolation in a second period different from the first period.

The interlaced image data in the even field is composed of only even lines. The interlaced image data in the odd field is composed of only odd-numbered lines. The first period is, for example, the period of the vertical synchronization signal of the input interlaced image data. The second cycle is, for example, the cycle of the vertical synchronization signal of the progressive image data to be displayed (in this embodiment, progressive image data subjected to scaling processing such as enlargement processing and reduction processing).

(構成)

図1は、本実施例に係る画像処理装置の機能構成の一例を示すブロック図である。

フレームメモリ101は、複数フィールドのインターレース画像データを記憶する記憶装置である。

入力画像処理部102は、入力されたインターレース画像データのうち、IP変換処理の処理対象(IP変換処理対象)となるインターレース画像データをフレームメモリ101に書き込む。なお、入力画像処理部102は、入力されたインターレース画像データを所定の画像処理を施してフレームメモリ101に書き込んでもよいし、入力されたインターレース画像データをそのままフレームメモリ101に書き込んでもよい。

(Constitution)

FIG. 1 is a block diagram illustrating an example of a functional configuration of the image processing apparatus according to the present embodiment.

The

Of the input interlaced image data, the input

IP変換処理部112は、第2の周期で、インターレース画像データをプログレッシブ画像データに変換して出力する。具体的には、IP変換処理部112は、第2の周期で、フレームメモリ101に書き込まれたインターレース画像データのうち、現フィールド、現フィールドの1つ前のフィールド、及び、現フィールドの2つ前のフィールドの3つのフィールドのインターレース画像データを読み出す。そして、IP変換処理部112は、現フィールドの1つ前のインターレース画像データをプログレッシブ画像データに変換して出力する。現フィールドのインターレース画像データは、例えば、フレームメモリ101に書き込まれたインターレース画像データのうち、最後に書き込まれたインターレース画像データである。上述したように、フレームメモリ101に書き込まれたインターレース画像データは、IP変換処理対象となるインターレース画像データである。そのため、本実施例では、現在のIP変換処理対象のインターレース画像データ(現データ)、現データの1つ前にIP変換処理対象とされたインターレース画像データ(前データ)、現データの1つ後にIP変換処理対象とされるインターレース画像データ(後データ)が読み出される。そして、現データがプログレッシブ画像データに変換されて出力される。

The IP

スケーリング処理部111は、IP変換処理部112から出力されたプログレッシブ画像データにスケーリング処理を施す。スケーリング処理は、例えば、画像データを設定された拡大率で拡大する拡大処理や、画像データを設定された縮小率で縮小する縮小処理である。

図1に示すように、本実施例では、IP変換処理部112とスケーリング処理部111の間には、IP変換処理部112から出力されたプログレッシブ画像データを一時的に記

憶するフレームメモリなどの記憶装置は設けられていない。

The scaling

As shown in FIG. 1, in this embodiment, a storage such as a frame memory that temporarily stores progressive image data output from the IP

出力同期信号生成部110は、IP変換処理部112でIP変換処理を行う周期(第2の周期)の信号(出力同期信号)を生成する。本実施例では、出力同期信号生成部110は、スケーリング処理部111で生成されたプログレッシブ画像データ(スケーリング処理が施されたプログレッシブ画像データ)の垂直同期信号に同期した信号を生成する。

The output synchronization

制御部103は、入力されるインターレース画像データの垂直同期信号(第1の周期の垂直同期信号)と、出力同期信号生成部110で生成された出力同期信号(第2の周期の信号)とに基づいて、IP変換対象とするインターレース画像データを決定する。具体的には、制御部103は、インターレース画像データが入力されるタイミングと、当該インターレース画像データに対するIP変換処理を行うタイミングとの差が所定値以下となるように、IP変換処理対象とするインターレース画像データを決定する。そして、制御部103は、入力されたインターレース画像データのうち、IP変換処理対象のインターレース画像データが第2の周期でフレームメモリ101に書き込まれるように、入力画像処理部102を制御する。所定値は、例えば、インターレース画像データが入力されてから、次のインターレース画像データが入力されるまでの時間(第1の周期)である。

また、制御部103は、出力同期信号生成部110で生成された出力同期信号に同期してIP変換処理が行われるように(即ち第2の周期でIP変換処理が行われるように)、IP変換処理部112を制御する。

The

In addition, the

IP変換処理部112は、動き検出部104、フィールド内補間処理部105、フィールド間補間処理部106、追い越し検出部107、補間ライン画像生成部108、出力部109などを有する。

The IP

動き検出部104は、フィールド間の画像の動きを検出する。具体的には、動き検出部104は、フレームメモリ101から読み出された現データ、前データ、及び、後データの3フィールド分のインターレース画像データを用いて動きを検出する。そして、動きの検出結果を表す動き情報を補間ライン画像生成部108へ出力する。なお、動きの検出方法は、特に限定されない。例えば、ブロックマッチング法を用いてもよいし、フィールド間の画素値の差分から動きを判断する手法を用いてもよい。動きは、1画素単位、複数画素単位、画像単位など、どのような単位で検出されてもよい。

The

フィールド内補間処理部105は、現データを用いてフィールド内補間処理を行う。フィールド内補間処理は、現データの画素を用いて現データの補間画素(現データに存在しない画素)を生成する処理である。フィールド内補間処理部105は、フィールド内補間処理により生成された補間画素からなる画像データ(フィールド内補間画像データ)を、補間ライン画像生成部108に出力する。

The intra-field

フィールド間補間処理部106は、後述する追い越し検出部107の検出結果に基づいて、フィールド間補間処理を行う。

具体的には、フィールド間補間処理部106は、通常時に(「追い越し」が発生していない場合に)、現データと、前データ及び後データのうちの一方のデータとを用いて、フィールド間補間処理を行う。そして、フィールド間補間処理部106は、「追い越し」が発生している場合に、現データと、前データ及び後データのうちの他方のデータとを用いて、フィールド間補間処理を行う。

本実施例では、フィールド間補間処理部106は、通常時に、現データと前データを用いて、フィールド間補間処理を行う。そして、フィールド間補間処理部106は、「追い越し」が発生している場合に、現データと後データを用いて、フィールド間補間処理を行う。

そして、フィールド間補間処理部106は、フィールド間補間処理により生成された補間画素からなる画像データ(フィールド間補間画像データ)を、補間ライン画像生成部108に出力する。

フィールド間補間処理は、現データと異なるフィールドのインターレース画像データの画素を用いて、現データの補間画素を生成する処理である。「追い越し」は、インターレース画像データが入力されるタイミングと、当該インターレース画像データに対するIP変換処理を行うタイミングとの差を所定値以下とする制御を行う場合に生じる「フィールドスキップ」や「フィールドリピート」である。「フィールドスキップ」は、或るフィールドを飛ばして、次のフィールドのインターレース画像データをIP変換処理の処理対象(IP変換処理対象)とするものである。「フィールドリピート」は、同じフィールドのインターレース画像データを2回続けてIP変換処理対象とするものである。

The inter-field

Specifically, the inter-field

In the present embodiment, the inter-field

Then, the inter-field

Inter-field interpolation processing is processing for generating interpolated pixels of current data using pixels of interlaced image data in a field different from the current data. “Overtaking” is a “field skip” or “field repeat” that occurs when control is performed so that the difference between the timing at which interlaced image data is input and the timing at which IP conversion processing is performed on the interlaced image data is equal to or less than a predetermined value It is. “Field skip” skips a certain field and sets interlaced image data of the next field as a processing target (IP conversion processing target) of the IP conversion processing. “Field repeat” is to subject interlaced image data in the same field twice as an IP conversion processing target.

追い越し検出部107は、フィールド情報(インターレース画像データが偶数フィールドか奇数フィールドかを表す情報)を用いて、「追い越し」を検出する。具体的には、追い越し検出部107は、現データと前データの両方が偶数フィールドまたは奇数フィールドであった場合に、「追い越し」が発生したと判断する。そして、追い越し検出部107は、検出結果をフィールド間補間処理部106へ出力する。フィールド情報は、少なくとも現データのフィールドと前データのフィールドを表す情報である。例えば、フィールド情報は、現データのフィールドと前データのフィールドのみを表す情報である。なお、フィールド情報は、現データ、前データ、及び、後データの3つのフィールドを表す情報であってもよいし、フレームメモリ101に記憶されている全てのインターレース画像データのフィールドを表す情報であってもよい。フィールド情報は、インターレース画像データにメタデータとして付加されていてもよいし、入力画像処理部などの機能部により生成されてもよい。

The overtaking

補間ライン画像生成部108は、動き検出部104から出力された動き情報に基づいて、補間画素毎に、フィールド内補間画像データとフィールド間補間画像データを合成(ブレンド)して、補間画素からなる補間ライン画像データを生成する。フィールド内補間処理は、画像の動きが大きい場合に適した処理であり、フィールド間補間処理は、画像の動きが小さい場合に適した処理である。そこで、本実施例では、画像の動きが大きいときに、小さいときよりもフィールド内補間画像(フィールド内補間処理の処理結果)の重みが大きくなるように、フィールド間補間画像(フィールド間補間処理の処理結果)とフィールド内補間画像とを合成する。そして、補間ライン画像生成部108は、生成した補間ライン画像データを出力部109に出力する。

The interpolation line

出力部109は、補間ライン画像データを用いて、現データをプログレッシブ画像データに変換し、スケーリング処理部111に出力する。具体的には、出力部109は、プログレッシブ画像データのライン(スケーリング処理で必要なライン)のデータ(ラインデータ)を、プログレッシブタイミングでスケーリング処理部111へ出力する。プログレッシブタイミングは、スケーリング処理後のプログレッシブ画像データの水平同期信号に同期したタイミングである。スケーリング処理部111は、入力されたラインデータを用いて、スケーリング処理後の1ライン分のプログレッシブ画像データを生成する。

The

(フィールド間補間処理)

図5,6を用いて、本実施例に係るフィールド間補間処理の一例について説明する。図5は、本実施例に係るフィールド間補間処理の一例を模式的に示す図である。図6は、本実施例に係るフィールド間補間処理部106の処理の流れの一例を示すフローチャートである。

フィールド間補間処理部106は、追い越し検出部107の検出結果から、「追い越し」が検出されたか否かを判定する(S601)。

追い越しが検出されていない場合には(S601:No)、フィールド間補間処理部106は、前データの画素を、現データの補間画素とする(S602)。具体的には、図5に示すように、前データの画素であって、現データの補間画素の生成位置と同じ位置の画素が、現データの補間画素とされる。

追い越しが検出された場合には(S601:Yes)、フィールド間補間処理部106は、後データの画素を、現データの補間画素とする(S603)。具体的には、図5に示すように、後データの画素であって、現データの補間画素の生成位置と同じ位置の画素が、現データの補間画素とされる。このとき、現データと後データの一方が偶数フィールド、他方が奇数フィールドとなるため、補間画素の生成位置と同じ位置の画素を選択することができ、適切な補間画素を生成することができる。

(Inter-field interpolation processing)

An example of inter-field interpolation processing according to the present embodiment will be described with reference to FIGS. FIG. 5 is a diagram schematically illustrating an example of inter-field interpolation processing according to the present embodiment. FIG. 6 is a flowchart illustrating an example of the processing flow of the inter-field

The inter-field

When the overtaking is not detected (S601: No), the inter-field

When the overtaking is detected (S601: Yes), the inter-field

(追い越し検出処理)

図7,8を用いて、本実施例に係る「追い越し」の検出処理(追い越し検出処理)の一例について説明する。図7は、「追い越し」が検出されるタイミングの一例を示す図である。図8は、本実施例に係る追い越し検出部107の処理の流れの一例を示すフローチャートである。

追い越し検出部107は、フィールド情報を用いて、現データと前データの両方が偶数フィールドまたは奇数フィールドか否かを判定する(S801)。

現データと前データの両方が偶数フィールドまたは奇数フィールドである場合(S801:Yes)、追い越し検出部107は、「追い越し」が発生したと判断する(S802)。そのため、現データと前データが図7のように推移していく場合には、図7の矢印で示すタイミングで「追い越し」が検出されることとなる。

現データと前データの一方が偶数フィールド、他方が奇数フィールドである場合(S801:No)、追い越し検出部107は、「追い越し」が発生していないと判断する(S803)。

(Overtaking detection process)

An example of the “overtaking” detection process (overtaking detection process) according to the present embodiment will be described with reference to FIGS. FIG. 7 is a diagram illustrating an example of timing at which “overtaking” is detected. FIG. 8 is a flowchart illustrating an example of a processing flow of the overtaking

The overtaking

When both the current data and the previous data are even fields or odd fields (S801: Yes), the overtaking

When one of the current data and the previous data is an even field and the other is an odd field (S801: No), the overtaking

以上述べたように、本実施例によれば、通常時に現データと前データを用いたフィールド間補間処理が行われる。そして、現データと前データの両方が偶数フィールドまたは奇数フィールドとなるような「追い越し」が発生している場合には、現データと後データを用いたフィールド間補間処理が行われる。それにより、「追い越し」が発生した場合にも、フィールド間補間処理を適切に行うことができる。具体的には、「追い越し」が発生した場合にも、フィールド間補間処理において、補間画素の生成位置と同じ位置の画素を使用することが可能となる。 As described above, according to the present embodiment, the inter-field interpolation process using the current data and the previous data is performed at the normal time. When “overtaking” occurs such that both the current data and the previous data are even fields or odd fields, inter-field interpolation processing using the current data and the subsequent data is performed. Thereby, even when “overtaking” occurs, inter-field interpolation processing can be appropriately performed. Specifically, even when “overtaking” occurs, it is possible to use a pixel at the same position as the interpolation pixel generation position in the inter-field interpolation processing.

<実施例2>

以下、本実施例に係る画像処理装置及びその制御方法について説明する。フィールド間補間処理の方法には、図9に示すように、後データの画素であって、補間画素の生成位置と同じ位置の画素を用いて補間画素が生成する方法がある。

(課題)

図10を用いて、「追い越し」が発生した場合の従来のフィールド間補間処理について説明する。

「追い越し」が発生すると、図10に示すように、IP変換処理において、現データと後データの両方が奇数フィールドとなったり、それらの両方が偶数フィールドとなったりしてしまう。この場合、後データには、補間画素の生成位置と同じ位置の画素は存在しないため、図9に示すようなフィールド間補間処理を行うことはできない。もしくは、補間画素の生成位置と異なる位置の画素が誤って使用され、補間画素が生成されてしまう。そのような誤った画素の使用は、表示画像の劣化を招く。

そこで、本実施例では、以下のようにフィールド間補間処理及び追い越し検出処理を行う。

<Example 2>

Hereinafter, an image processing apparatus and a control method thereof according to the present embodiment will be described. As shown in FIG. 9, the inter-field interpolation processing method includes a method in which an interpolation pixel is generated using a pixel of the subsequent data and the same position as the generation position of the interpolation pixel.

(Task)

A conventional inter-field interpolation process when “overtaking” occurs will be described with reference to FIG.

When “overtaking” occurs, as shown in FIG. 10, in the IP conversion process, both the current data and the subsequent data become odd fields, or both of them become even fields. In this case, since there is no pixel at the same position as the interpolation pixel generation position in the subsequent data, inter-field interpolation processing as shown in FIG. 9 cannot be performed. Alternatively, a pixel at a position different from the generation position of the interpolation pixel is erroneously used, and an interpolation pixel is generated. Such erroneous use of pixels leads to degradation of the display image.

Therefore, in this embodiment, inter-field interpolation processing and overtaking detection processing are performed as follows.

(フィールド間補間処理)

図11,12を用いて、本実施例に係るフィールド間補間処理の一例について説明する。図11は、本実施例に係るフィールド間補間処理の一例を模式的に示す図である。図12は、本実施例に係るフィールド間補間処理部106の処理の流れの一例を示すフローチャートである。

フィールド間補間処理部106は、追い越し検出部107の検出結果から、「追い越し」が検出されたか否かを判定する(S1201)。

追い越しが検出されていない場合には(S1201:No)、フィールド間補間処理部106は、後データの画素を、現データの補間画素とする(S1202)。具体的には、図11に示すように、後データの画素であって、現データの補間画素の生成位置と同じ位置の画素が、現データの補間画素とされる。

追い越しが検出された場合には(S1201:Yes)、フィールド間補間処理部106は、前データの画素を、現データの補間画素とする(S603)。具体的には、図11に示すように、前データの画素であって、現データの補間画素の生成位置と同じ位置の画素が、現データの補間画素とされる。このとき、現データと前データの一方が偶数フィールド、他方が奇数フィールドとなるため、補間画素の生成位置と同じ位置の画素を選択することができ、適切な補間画素を生成することができる。

(Inter-field interpolation processing)

An example of inter-field interpolation processing according to the present embodiment will be described with reference to FIGS. FIG. 11 is a diagram schematically illustrating an example of inter-field interpolation processing according to the present embodiment. FIG. 12 is a flowchart illustrating an example of the processing flow of the inter-field

The inter-field

When the overtaking is not detected (S1201: No), the inter-field

If an overtaking is detected (S1201: Yes), the inter-field

(追い越し検出処理)

図13,14を用いて、本実施例に係る「追い越し」の検出処理(追い越し検出処理)の一例について説明する。図13は、「追い越し」が検出されるタイミングの一例を示す図である。図14は、本実施例に係る追い越し検出部107の処理の流れの一例を示すフローチャートである。

追い越し検出部107は、フィールド情報を用いて、現データと後データの両方が偶数フィールドまたは奇数フィールドか否かを判定する(S1401)。

現データと後データの両方が偶数フィールドまたは奇数フィールドである場合(S1401:Yes)、追い越し検出部107は、「追い越し」が発生したと判断する(S1402)。そのため、現データと後データが図13のように推移していく場合には、図13の矢印で示すタイミングで「追い越し」が検出されることとなる。

現データと後データの一方が偶数フィールド、他方が奇数フィールドである場合(S1401:No)、追い越し検出部107は、「追い越し」が発生していないと判断する(S1403)。

(Overtaking detection process)

An example of “overtaking” detection processing (overtaking detection processing) according to the present embodiment will be described with reference to FIGS. FIG. 13 is a diagram illustrating an example of timing at which “overtaking” is detected. FIG. 14 is a flowchart illustrating an example of a process flow of the overtaking

The overtaking

When both the current data and the subsequent data are even fields or odd fields (S1401: Yes), the overtaking

When one of the current data and the subsequent data is an even field and the other is an odd field (S1401: No), the overtaking

以上述べたように、本実施例によれば、通常時に現データと後データを用いたフィールド間補間処理が行われる。そして、現データと後データの両方が偶数フィールドまたは奇数フィールドとなるような「追い越し」が発生している場合には、現データと前データを用いたフィールド間補間処理が行われる。それにより、「追い越し」が発生した場合にも、フィールド間補間処理を適切に行うことができる。具体的には、「追い越し」が発生した場合にも、フィールド間補間処理において、補間画素の生成位置と同じ位置の画素を使用することが可能となる。 As described above, according to the present embodiment, the inter-field interpolation process using the current data and the subsequent data is performed at the normal time. When “overtaking” occurs such that both the current data and the subsequent data become even fields or odd fields, inter-field interpolation processing using the current data and the previous data is performed. Thereby, even when “overtaking” occurs, inter-field interpolation processing can be appropriately performed. Specifically, even when “overtaking” occurs, it is possible to use a pixel at the same position as the interpolation pixel generation position in the inter-field interpolation processing.

103 制御部

106 フィールド間補間処理部

112 IP変換処理部

103

Claims (16)

インターレース画像データが入力されるタイミングと、前記インターレース画像データに対する前記IP変換処理を行うタイミングとの差が所定値以下となるように、前記IP変換処理の処理対象とするインターレース画像データを決定する決定手段と、

現在の処理対象のインターレース画像データである現データと、前記現データの1つ前に処理対象とされたインターレース画像データである前データ、及び、前記現データの1つ後に処理対象とされるインターレース画像データである後データのうちの一方のデータとを用いてフィールド間補間処理を行い、前記現データをプログレッシブ画像データに変換する変換手段と、

を有し、

前記変換手段は、前記現データと、前記前データ及び前記後データのうちの前記一方のデータとの両方が偶数フィールドまたは奇数フィールドであった場合に、前記現データと、前記前データ及び前記後データのうちの他方のデータとを用いてフィールド間補間処理を行う

ことを特徴とする画像処理装置。 Even field interlaced image data and odd field interlaced image data are alternately input in a first period, and the interlaced image data input in a second period different from the first period is a progressive image by interpolation. An image processing apparatus that performs IP conversion processing for converting data,

Determination to determine interlaced image data to be processed by the IP conversion process so that a difference between a timing at which the interlaced image data is input and a timing at which the IP conversion process is performed on the interlaced image data is equal to or less than a predetermined value. Means,

Current data that is the current interlaced image data to be processed, previous data that is the interlaced image data that was processed immediately before the current data, and the interlace that is processed after the current data Conversion means for performing inter-field interpolation processing using one of the subsequent data that is image data, and converting the current data into progressive image data;

Have

The converting means, when both the current data and the one of the previous data and the subsequent data are even fields or odd fields, the current data, the previous data, and the subsequent data. An image processing apparatus that performs inter-field interpolation processing using the other of the data.

前記変換手段は、現データを用いたフィールド内補間処理を更に行い、画像の動きが大きいときに、小さいときよりもフィールド内補間処理の処理結果の重みが大きくなるように、フィールド間補間処理の処理結果とフィールド内補間処理の処理結果とを合成して、前記現データをプログレッシブ画像データに変換する

ことを特徴とする請求項1に記載の画像処理装置。 It further comprises detection means for detecting the movement of the image between the fields,

The conversion means further performs intra-field interpolation processing using the current data, and performs inter-field interpolation processing so that the weight of the processing result of the intra-field interpolation processing is greater when the image motion is large than when it is small. The image processing apparatus according to claim 1, wherein the processing result and the processing result of the intra-field interpolation processing are combined to convert the current data into progressive image data.

ことを特徴とする請求項2に記載の画像処理装置。The image processing apparatus according to claim 2.

前記変換手段と前記スケーリング手段の間には、前記変換手段から出力されたプログレッシブ画像データを一時的に記憶する記憶手段が設けられていない

ことを特徴とする請求項1〜3のいずれか1項に記載の画像処理装置。 A scaling unit for performing an enlargement process or a reduction process on the progressive image data output from the conversion unit;

Wherein during the conversion means and the scaling means is any one of claims 1-3, characterized in that storage means for temporarily storing the progressive image data output from said conversion means is not provided An image processing apparatus according to 1.

前記スケーリング手段は、拡大処理または縮小処理が施された後の1ライン分の画像データを、前記変換手段から出力された1ライン分のプログレッシブ画像データを用いて生成する処理、を繰り返し行う The scaling means repeatedly performs processing for generating image data for one line after being subjected to enlargement processing or reduction processing, using progressive image data for one line output from the conversion means.

ことを特徴とする請求項4に記載の画像処理装置。The image processing apparatus according to claim 4.

前記決定手段は、前記入力されたインターレース画像データの垂直同期信号と、前記生成手段で生成された垂直同期信号と、に基づいて、前記IP変換処理の処理対象とするインターレース画像データを決定する The determining unit determines interlaced image data to be processed by the IP conversion process based on a vertical synchronization signal of the input interlaced image data and a vertical synchronization signal generated by the generating unit.

ことを特徴とする請求項1〜5のいずれか1項に記載の画像処理装置。The image processing apparatus according to claim 1, wherein the image processing apparatus is an image processing apparatus.

前記変換手段は、前記判定手段の判定結果に基づいて、前記フィールド間補間処理を行う The converting means performs the inter-field interpolation processing based on the determination result of the determining means.

ことを特徴とする請求項1〜6のいずれか1項に記載の画像処理装置。The image processing apparatus according to claim 1, wherein the image processing apparatus is an image processing apparatus.

ことを特徴とする請求項1〜7のいずれか1項に記載の画像処理装置。The image processing apparatus according to claim 1, wherein the image processing apparatus is an image processing apparatus.

インターレース画像データが入力されるタイミングと、前記インターレース画像データに対する前記IP変換処理を行うタイミングとの差が所定値以下となるように、前記IP変換処理の処理対象とするインターレース画像データを決定する決定ステップと、

現在の処理対象のインターレース画像データである現データと、前記現データの1つ前に処理対象とされたインターレース画像データである前データ、及び、前記現データの1つ後に処理対象とされるインターレース画像データである後データのうちの一方のデータとを用いてフィールド間補間処理を行い、前記現データをプログレッシブ画像データに変換する変換ステップと、

を有し、

前記変換ステップでは、前記現データと、前記前データ及び前記後データのうちの前記一方のデータとの両方が偶数フィールドまたは奇数フィールドであった場合に、前記現データと、前記前データ及び前記後データのうちの他方のデータとを用いてフィールド間補間処理が行われる

ことを特徴とする画像処理装置の制御方法。 Even field interlaced image data and odd field interlaced image data are alternately input in a first period, and the interlaced image data input in a second period different from the first period is a progressive image by interpolation. A method for controlling an image processing apparatus that performs IP conversion processing for converting data,

Determination to determine interlaced image data to be processed by the IP conversion process so that a difference between a timing at which the interlaced image data is input and a timing at which the IP conversion process is performed on the interlaced image data is equal to or less than a predetermined value. Steps,

Current data that is the current interlaced image data to be processed, previous data that is the interlaced image data that was processed immediately before the current data, and the interlace that is processed after the current data A conversion step of performing inter-field interpolation using one of the subsequent data that is image data, and converting the current data into progressive image data;

Have

In the converting step, when both the current data and the one of the previous data and the subsequent data are even fields or odd fields, the current data, the previous data, and the subsequent data A method for controlling an image processing apparatus, wherein inter-field interpolation processing is performed using the other data of the data.

前記変換ステップでは、現データを用いたフィールド内補間処理が更に行われ、画像の In the conversion step, intra-field interpolation processing using the current data is further performed,

動きが大きいときに、小さいときよりもフィールド内補間処理の処理結果の重みが大きくなるように、フィールド間補間処理の処理結果とフィールド内補間処理の処理結果とが合成されて、前記現データがプログレッシブ画像データに変換されるWhen the motion is large, the inter-field interpolation processing result and the intra-field interpolation processing result are combined so that the weight of the intra-field interpolation processing result is greater than when the motion is small, and the current data is Converted to progressive image data

ことを特徴とする請求項9に記載の画像処理装置の制御方法。The method of controlling an image processing apparatus according to claim 9.

ことを特徴とする請求項10に記載の画像処理装置の制御方法。The method of controlling an image processing apparatus according to claim 10.

ことを特徴とする請求項9〜11のいずれか1項に記載の画像処理装置の制御方法。The method of controlling an image processing apparatus according to claim 9, wherein the image processing apparatus is a control method.

前記スケーリングステップでは、拡大処理または縮小処理が施された後の1ライン分の画像データを、前記変換ステップで得られた1ライン分のプログレッシブ画像データを用いて生成する処理、が繰り返し行われる In the scaling step, a process of generating image data for one line after the enlargement process or the reduction process is performed using the progressive image data for one line obtained in the conversion step is repeatedly performed.

ことを特徴とする請求項12に記載の画像処理装置の制御方法。The method of controlling an image processing apparatus according to claim 12.

前記決定ステップでは、前記入力されたインターレース画像データの垂直同期信号と、前記生成ステップで生成された垂直同期信号と、に基づいて、前記IP変換処理の処理対象とするインターレース画像データが決定される In the determining step, interlaced image data to be processed in the IP conversion process is determined based on the vertical synchronizing signal of the input interlaced image data and the vertical synchronizing signal generated in the generating step.

ことを特徴とする請求項9〜13のいずれか1項に記載の画像処理装置の制御方法。The method for controlling an image processing apparatus according to claim 9, wherein:

前記変換ステップでは、前記判定ステップでの判定結果に基づいて、前記フィールド間補間処理が行われる In the conversion step, the inter-field interpolation processing is performed based on the determination result in the determination step.

ことを特徴とする請求項9〜14のいずれか1項に記載の画像処理装置の制御方法。The method for controlling an image processing apparatus according to claim 9, wherein:

ことを特徴とする請求項9〜15のいずれか1項に記載の画像処理装置の制御方法。The method for controlling an image processing apparatus according to claim 9, wherein:

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012060206A JP5875422B2 (en) | 2012-03-16 | 2012-03-16 | Image processing apparatus and image processing apparatus control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012060206A JP5875422B2 (en) | 2012-03-16 | 2012-03-16 | Image processing apparatus and image processing apparatus control method |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013197676A JP2013197676A (en) | 2013-09-30 |

| JP2013197676A5 JP2013197676A5 (en) | 2015-04-30 |

| JP5875422B2 true JP5875422B2 (en) | 2016-03-02 |

Family

ID=49396160

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012060206A Expired - Fee Related JP5875422B2 (en) | 2012-03-16 | 2012-03-16 | Image processing apparatus and image processing apparatus control method |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5875422B2 (en) |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0865639A (en) * | 1994-08-26 | 1996-03-08 | Hitachi Ltd | Image processor |

| JP2000287181A (en) * | 1999-03-31 | 2000-10-13 | Victor Co Of Japan Ltd | Video signal processing circuit |

| JP2006303630A (en) * | 2005-04-15 | 2006-11-02 | Sony Corp | Frame rate conversion apparatus, overrun compensation method, and display apparatus |

| JP2009115910A (en) * | 2007-11-02 | 2009-05-28 | Denso Corp | Synchronous converter, synchronous converting method and program |

| JP2010199648A (en) * | 2009-02-23 | 2010-09-09 | Renesas Electronics Corp | Device, method, and program for processing image |

| JP2011055021A (en) * | 2009-08-31 | 2011-03-17 | Fujitsu Ten Ltd | Image generating device, display system and image generating method |

-

2012

- 2012-03-16 JP JP2012060206A patent/JP5875422B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013197676A (en) | 2013-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4438795B2 (en) | Video conversion device, video display device, and video conversion method | |

| EP2151996A2 (en) | Image signal processing unit and method of processing image signal | |

| JP2006165602A5 (en) | ||

| JP2014179818A (en) | Image processing device and image processing method | |

| JP5424926B2 (en) | Video processing apparatus and video processing method | |

| JP4119360B2 (en) | Video format conversion apparatus and method | |

| JP2010081330A (en) | Signal processing method and apparatus in three-dimensional image display | |

| JP2008011454A (en) | Device and method for moving image frame rate conversion | |

| JP5241632B2 (en) | Image processing circuit and image processing method | |

| JP2014033438A (en) | Image processing program and image processing apparatus | |

| JP5875422B2 (en) | Image processing apparatus and image processing apparatus control method | |

| JP4558614B2 (en) | Image processing apparatus, method and program for determining field order of moving image data | |

| JP2008009182A (en) | Liquid crystal display device | |

| EP1367820A2 (en) | Video signal processing device | |

| JP2007288483A (en) | Image converting apparatus | |

| JP2006174123A (en) | Successive scanning conversion apparatus | |

| JP5904480B2 (en) | Image processing apparatus and image processing apparatus control method | |

| JP2005295134A (en) | Adaptive frame synchronization system | |

| JP4181189B2 (en) | Motion vector detection method and apparatus, interpolation image generation method and apparatus, and image display system | |

| JP4230903B2 (en) | Video signal processing apparatus and video signal processing method | |

| US20050046742A1 (en) | Image signal processing circuit | |

| JP2006332975A (en) | Video signal processing circuit | |

| KR100620930B1 (en) | Image signal processing circuit | |

| JP2010098513A (en) | Apparatus and method for generating interpolated image | |

| JP5672116B2 (en) | Video processing device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150313 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150313 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151127 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151222 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160119 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5875422 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |