JP5729544B2 - Temperature detection circuit - Google Patents

Temperature detection circuit Download PDFInfo

- Publication number

- JP5729544B2 JP5729544B2 JP2011021761A JP2011021761A JP5729544B2 JP 5729544 B2 JP5729544 B2 JP 5729544B2 JP 2011021761 A JP2011021761 A JP 2011021761A JP 2011021761 A JP2011021761 A JP 2011021761A JP 5729544 B2 JP5729544 B2 JP 5729544B2

- Authority

- JP

- Japan

- Prior art keywords

- temperature

- resistor

- voltage

- resistors

- resistance

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000001514 detection method Methods 0.000 title claims description 56

- 238000013459 approach Methods 0.000 claims description 5

- 230000007423 decrease Effects 0.000 claims description 5

- 101100532521 Homo sapiens AHCYL1 gene Proteins 0.000 description 13

- 102100022479 S-adenosylhomocysteine hydrolase-like protein 1 Human genes 0.000 description 13

- 238000010586 diagram Methods 0.000 description 7

- 238000000034 method Methods 0.000 description 6

- 230000000630 rising effect Effects 0.000 description 5

- 238000006243 chemical reaction Methods 0.000 description 4

- 230000035945 sensitivity Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 239000000470 constituent Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Landscapes

- Measuring Temperature Or Quantity Of Heat (AREA)

Description

本発明は、温度検出回路に関する。 The present invention relates to a temperature detection circuit.

従来より、温度センサーとマイクロコンピューターを内蔵し、温度センサーが出力する温度情報を用いて、マイクロコンピューターが各種データの温度補償を行う装置やシステムが知られている。温度センサーの多くは、PN接合のバンドギャップの温度特性と抵抗の温度特性を利用して温度情報を含むアナログ電圧を生成する。一方、マイクロコンピューターはデジタル処理を行うため、デジタル値の温度情報が必要となる。そのため、アナログの温度情報をAD変換回路でデジタル値に変換してからマイクロコンピューターに入力したり、AD変換回路が内蔵されたマイクロコンピューターが用いられる。あるいは、AD変換回路を内蔵したデジタル出力の温度センサーが用いられる場合もある(特許文献1)。 2. Description of the Related Art Conventionally, there have been known devices and systems that incorporate a temperature sensor and a microcomputer, and the microcomputer performs temperature compensation of various data using temperature information output from the temperature sensor. Many of the temperature sensors generate an analog voltage including temperature information using the temperature characteristics of the band gap and the resistance of the PN junction. On the other hand, since a microcomputer performs digital processing, temperature information of a digital value is required. For this reason, analog temperature information is converted into a digital value by an AD conversion circuit and then input to a microcomputer, or a microcomputer incorporating an AD conversion circuit is used. Alternatively, a digital output temperature sensor incorporating an AD conversion circuit may be used (Patent Document 1).

しかしながら、従来のデジタル出力の温度センサーは、バンドギャップリファレンス回路やADC回路を必要とするため、消費電流が大きく回路サイズも大きくなるという問題がある。 However, the conventional digital output temperature sensor requires a bandgap reference circuit and an ADC circuit, so that there is a problem that current consumption is large and the circuit size is large.

本発明は、以上のような問題点に鑑みてなされたものであり、本発明のいくつかの態様によれば、従来よりも小さな消費電力と回路サイズでデジタルの温度情報を生成可能な温度検出回路を提供することができる。 The present invention has been made in view of the above problems, and according to some aspects of the present invention, temperature detection capable of generating digital temperature information with smaller power consumption and circuit size than conventional ones. A circuit can be provided.

(1)本発明は、2つの電源間に抵抗値の温度特性が異なる少なくとも2種類の抵抗を含む複数の抵抗が直列に接続された抵抗部と、前記抵抗部の複数の接続点の電圧が入力され、選択信号に応じて前記複数の接続点の電圧から1の電圧を選択する電圧選択部と、前記電圧選択部が選択する電圧を一定の基準電圧と比較する電圧比較部と、前記電圧比較部の比較結果に応じて、前記電圧選択部が選択する電圧が前記基準電圧に近づくように前記選択信号を逐次的に変更し、前記選択信号に基づいて温度情報を表すデジタルコードを生成する温度情報コード生成部と、を含む、温度検出回路である。 (1) In the present invention, a resistance portion in which a plurality of resistors including at least two types of resistors having different resistance temperature characteristics between two power supplies are connected in series, and voltages at a plurality of connection points of the resistance portions are A voltage selection unit that selects one voltage from the voltages at the plurality of connection points according to a selection signal, a voltage comparison unit that compares a voltage selected by the voltage selection unit with a certain reference voltage, and the voltage In accordance with the comparison result of the comparison unit, the selection signal is sequentially changed so that the voltage selected by the voltage selection unit approaches the reference voltage, and a digital code representing temperature information is generated based on the selection signal. And a temperature information code generation unit.

本発明の温度検出回路では、抵抗部には温度特性が異なる少なくとも2種類の抵抗が含まれるので、2つの電源間を抵抗分圧して得られる各接続点の電圧は温度に応じて変化する。そして、温度情報コード生成部により、電圧選択部が最終的に選択する電圧は一定の基準電圧により近い接続点の電圧になるので、この電圧を選択する選択信号は温度情報を含んでおり、簡易な回路によりこの選択信号からデジタルの温度情報を生成することができる。すなわち、本発明の温度検出回路によれば、バンドギャップリファレンス回路やAD変換回路が不要であり、抵抗部の各抵抗の抵抗値を適切に選択することで従来よりも小さな消費電力と回路サイズにすることができる。 In the temperature detection circuit of the present invention, since the resistance portion includes at least two types of resistors having different temperature characteristics, the voltage at each connection point obtained by dividing the resistance between the two power sources varies depending on the temperature. Then, since the voltage finally selected by the voltage selection unit by the temperature information code generation unit becomes a voltage at a connection point closer to a certain reference voltage, the selection signal for selecting this voltage includes temperature information and is simple. Digital temperature information can be generated from this selection signal by a simple circuit. That is, according to the temperature detection circuit of the present invention, a band gap reference circuit and an AD conversion circuit are not required, and by appropriately selecting the resistance value of each resistance of the resistance unit, the power consumption and circuit size can be reduced compared to the conventional one. can do.

(2)この温度検出回路において、前記抵抗部は、前記複数の抵抗の少なくとも1つは温度が高いほど抵抗値が高くなる正の温度特性を有する抵抗であり、前記複数の抵抗の他の少なくとも1つは温度が高いほど抵抗値が低くなる負の温度特性を有する抵抗であるようにしてもよい。 (2) In this temperature detection circuit, the resistance unit is a resistor having a positive temperature characteristic in which at least one of the plurality of resistors has a higher resistance value as the temperature is higher, and at least another of the plurality of resistors. One may be a resistor having a negative temperature characteristic in which the resistance value decreases as the temperature increases.

このようにすれば、抵抗部に含まれる少なくとも2つの抵抗に関して温度変化に対する抵抗値の変化の方向が逆向きになるので、温度変化に対する抵抗部の各接続点の電圧の変化量をより大きくすることができる。これにより、温度検出感度を向上させることができる。 In this way, the direction of change in resistance value with respect to temperature change is reversed with respect to at least two resistors included in the resistance part, so that the amount of change in voltage at each connection point of the resistance part with respect to temperature change is further increased. be able to. Thereby, temperature detection sensitivity can be improved.

(3)この温度検出回路において、前記抵抗部は、前記複数の抵抗の少なくとも1つをバイパスするための第1のスイッチを含むようにしてもよい。 (3) In this temperature detection circuit, the resistor section may include a first switch for bypassing at least one of the plurality of resistors.

このようにすれば、第1のスイッチのオン/オフにより、抵抗部の全体抵抗値が変わるので、2つの電源間を抵抗分圧して得られる各接続点の電圧を変更することができる。これにより、温度情報のオフセットをある程度補正することができる。 In this way, since the overall resistance value of the resistor section changes by turning on / off the first switch, the voltage at each connection point obtained by dividing the resistance between the two power sources can be changed. Thereby, the offset of temperature information can be corrected to some extent.

(4)この温度検出回路において、前記抵抗部は、前記複数の抵抗の少なくとも1つを、抵抗値の温度特性が異なる他の抵抗に切り替えるための第2のスイッチを含むようにしてもよい。 (4) In this temperature detection circuit, the resistor section may include a second switch for switching at least one of the plurality of resistors to another resistor having a different resistance temperature characteristic.

このようにすれば、第2のスイッチを切り替えることにより、温度変化に対する抵抗部の各接続点の電圧の変化量が変わるので、温度情報の変化率(傾き)、すなわち温度検出感度を調整することができる。 In this way, by changing the second switch, the amount of change in the voltage at each connection point of the resistance section with respect to the temperature change changes, so the change rate (slope) of temperature information, that is, the temperature detection sensitivity can be adjusted. Can do.

(5)この温度検出回路は、補正ビット情報に基づいて、前記温度情報コード生成部が生成する前記デジタルコードを補正する温度情報コード補正部をさらに含むようにしてもよい。 (5) The temperature detection circuit, based on the compensation bit information, the digital code by the temperature information code generation unit generates may further include a temperature information code correcting unit for correcting.

このようにすれば、温度情報のオフセットを正確に補正することができる。 In this way, the offset of the temperature information can be corrected accurately.

以下、本発明の好適な実施形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成の全てが本発明の必須構成要件であるとは限らない。 DESCRIPTION OF EMBODIMENTS Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the drawings. The embodiments described below do not unduly limit the contents of the present invention described in the claims. Also, not all of the configurations described below are essential constituent requirements of the present invention.

1.第1実施形態

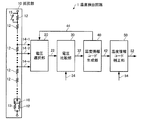

図1は、第1実施形態の温度検出回路の機能ブロック図である。本実施形態の温度検出回路1は、抵抗部10、電圧選択部20、電圧比較部30、温度情報コード生成部40、温度情報コード補正部50を含む。なお、本実施形態の温度検出回路1は、これらの一部の構成(要素)を省略した構成としてもよい。

1. First Embodiment FIG. 1 is a functional block diagram of a temperature detection circuit according to a first embodiment. The

抵抗部10は、2つの電源間に抵抗値の温度特性が異なる少なくとも2種類の抵抗を含む複数の抵抗12が直列に接続されている。例えば、抵抗部10は、複数の抵抗12の少なくとも1つは温度が高いほど抵抗値が高くなる正の温度特性を有する抵抗であり、複数の抵抗12の他の少なくとも1つは温度が高いほど抵抗値が低くなる負の温度特性を有する抵抗である。

In the

前記抵抗部10は、複数の抵抗12の少なくとも1つをバイパスするための第1のスイッチ15を含むようにしてもよい。第1のスイッチ15は、1つでもよいし複数でもよい。

The

電圧選択部20は、抵抗部10の複数の接続点の電圧14−1〜14−nが入力され、選択信号44に応じて複数の接続点の電圧14−1〜14−nから1の電圧を選択する処理を行う。

The

電圧比較部30は、電圧選択部20が選択する電圧22を温度に依存せずに一定の基準電圧34と比較する処理を行う。

The

温度情報コード生成部40は、電圧比較部30の比較結果32に応じて、電圧選択部20が選択する電圧22が基準電圧34に近づくように選択信号44を逐次的に変更し、選択信号44に基づいて温度情報を表すデジタルコード42を生成する処理を行う。

The temperature information

温度情報コード補正部50は、所与の補正ビット情報54に基づいて、温度情報コード生成部40が生成するデジタルコード42を補正してデジタルコード52を生成する処理を行う。

The temperature information

図2は、第1実施形態の温度検出回路の構成例を示す図である。図2に示すように、第1実施形態の温度検出回路1は、ビット調整回路110、64個の抵抗120−0〜120−63(図1の抵抗12の一例)、抵抗122(図1の抵抗12の一例)、マルチプレクサー200(図1の電圧選択部20の一例)、コンパレーター300(図1の電圧比較部30の一例)、基準電圧生成回路310、逐次比較回路400(図1の温度情報コード生成部40の一例)、デジタル調整回路500(図1の温度情報コード補正部50の一例)を含む。なお、本実施形態の温度検出回路1は、これらの一部の構成(要素)を省略した構成としてもよい。

FIG. 2 is a diagram illustrating a configuration example of the temperature detection circuit according to the first embodiment. As shown in FIG. 2, the

図3に、ビット調整回路110の構成例を示す。本実施形態のビット調整回路110は、電源電圧VDDと抵抗120−0(図2参照)の間に直列に接続された15個の抵抗112−1〜112−15(図1の抵抗12の一例)、15個のスイッチ114−1〜114−15(図1の第1のスイッチ15の一例)、デコーダー116を含む。抵抗112−1〜112−15は、電源電圧VDDと抵抗120−0(図2参照)の間に直列に接続されており、スイッチ114−1〜114−15は、それぞれ、抵抗112−1〜112−15と並列に接続されている。本実施形態では、抵抗112−1〜112−15は、温度が高いほど抵抗値が低くなる負の温度特性を有する抵抗であり、例えばポリ抵抗で実現される。

FIG. 3 shows a configuration example of the

デコーダー116は、外部から供給される4ビットの調整コードCALB_A[3:0]に応じて、スイッチ114−1〜114−15の開閉(オン/オフ)をそれぞれ制御する制御信号S1〜S15を生成する。図4に、デコーダー116の真理値表の一例を示す。図4の例では、CALB_A[3:0]の値が0000(10進数の0)の時、制御信号S1〜S15はそれぞれスイッチ112−1〜112−15をオフ(すべてのスイッチをオフ)し、CALB_A[3:0]の値が1111(10進数の15)の時、制御信号S1〜S15はそれぞれスイッチ112−1〜112−15をオン(すべてのスイッチをオン)する。また、CALB_A[3:0]の値が0001〜1110(10進数の1〜14)の時は、各値Nに対して、制御信号S1〜SNがスイッチ112−1〜112−Nをそれぞれオンするとともに、制御信号SN+1〜S15がスイッチ112−N+1〜112−15をそれぞれオフする。つまり、CALB_A[3:0]の値を変更することで、電源電圧VDDと抵抗120−0(図2参照)の間の抵抗値(以下、「ビット調整回路110の抵抗値」という)を変更することができるようになっている。

The

なお、CALB_A[3:0]の初期値は例えば0111になっており、スイッチ114−1〜114−15は図3に示す状態(スイッチ114−1〜114−7がオン、スイッチ114−8〜114−15がオフ)になっている。そして、CALB_A[3:0]を初期値よりも大きい値に変更することでビット調整回路110の抵抗値を高くし、CALB_A[3:0]を初期値よりも小さい値に変更することでビット調整回路110の抵抗値を低くすることができる。

Note that the initial value of CALB_A [3: 0] is, for example, 0111, and the switches 114-1 to 114-15 are in the state shown in FIG. 3 (switches 114-1 to 114-7 are on, switches 114-8 to 114-15 is off). Then, by changing CALB_A [3: 0] to a value larger than the initial value, the resistance value of the

図2及び図3に示すように、ビット調整回路110の抵抗112−1〜112−15、抵抗120−0〜120−63、抵抗122は、電源電圧VDDとグランド電圧VSSの間に直列に接続されており、図1の抵抗部10に対応する。抵抗120−0〜120−63、抵抗122は、温度が高いほど抵抗値が高くなる正の温度特性を有する抵抗であり、例えば拡散抵抗で実現される。

2 and 3, the resistors 112-1 to 112-15, resistors 120-0 to 120-63, and

このような構成において、VSS=0V、基準温度T0(例えば25℃)での抵抗120−i(i=0〜63)の抵抗値をRpi、抵抗122の抵抗値をRpbase、ビット調整回路110の抵抗値をRmbaseとすると、温度Tでの各電圧Vx(x=0〜63)は次式(1)で計算される。なお、式(1)では、抵抗120−0〜120−63の1次の温度係数をtclrp(>0)、抵抗112−1〜15の1次の温度係数をtclrm(<0)とし、2次以上の温度係数は無視できるものとしている。

In such a configuration, the resistance value of the resistor 120-i (i = 0 to 63) at VSS = 0V and the reference temperature T 0 (for example, 25 ° C.) is Rp i , the resistance value of the

tclrp>0、tclrm<0なので、式(1)より、温度Tが高いほど各電圧Vx(x=0〜63)が高くなる。 Since tcl rp > 0 and tcl rm <0, from equation (1), the higher the temperature T, the higher the voltages V x (x = 0 to 63).

マルチプレクサー200は、逐次比較回路400が生成する6ビットコードDA[5:0]に応じて、ビット調整回路110と抵抗120−0の接続点(抵抗112−15と抵抗120−0の接続点)の電圧V0、抵抗120−0と抵抗120−1の接続点の電圧V1、抵抗120−1と抵抗120−2の接続点の電圧V2、・・・、抵抗120−61と抵抗120−62の接続点の電圧V62、抵抗120−62と抵抗120−63の接続点の電圧V63のいずれかの電圧を選択し、選択電圧Vmuxとしてコンパレーター300の反転入力端子に供給する。図5に、マルチプレクサー200の真理値表の一例を示す。図5の例では、DA[5:0]の10進数の値がx(x=0〜63)の時、Vmux=Vxとなる。

The multiplexer 200 connects the connection point between the

基準電圧生成回路310は、抵抗値の温度特性が同じ2つの抵抗312,314が電源電圧VDDとグランド電圧VSSの間に直列に接続されて構成されており、抵抗312と抵抗314の抵抗比に応じた分圧により基準電圧Vrefを生成する。抵抗312,314の抵抗値の温度特性が同じであるため、温度が変化しても抵抗312と抵抗314の抵抗比が一定である。従って、基準電圧Vrefは温度によらず一定である。

The reference voltage generation circuit 310 is configured by connecting two

コンパレーター300は、反転入力端子と非反転入力端子に、それぞれ、マルチプレクサー200の選択電圧Vmuxと基準電圧生成回路310が生成する基準電圧Vrefが供給され、クロック信号MCLKに同期して、VmuxがVrefよりも高い時はVSSとなり、VmuxがVrefよりも低い時はVDDとなる信号CMPを出力する。 In the comparator 300, the selection voltage V mux of the multiplexer 200 and the reference voltage V ref generated by the reference voltage generation circuit 310 are supplied to the inverting input terminal and the non-inverting input terminal, respectively, and in synchronization with the clock signal MCLK, When V mux is higher than V ref, VSS is output, and when V mux is lower than V ref , a signal CMP that is VDD is output.

逐次比較回路400は、クロック信号MCLKに同期して、コンパレーター300の出力信号CMPがローレベル(VmuxがVrefよりも高い)であれば6ビットコードDA[5:0]の値を増加させ、コンパレーター300の出力信号CMPがハイレベル(VmuxがVrefよりも低い)であれば6ビットコードDA[5:0]の値を減少させることにより、VmuxがVrefに近づくように制御する。そして、逐次比較回路400は、VmuxがVrefに最も近づくDA[5:0]の値を探索し、探索結果のDA[5:0]を6ビットの出力コードD[5:0]にセットする。

The

逐次比較回路400は、例えば図6に示すフローチャートに従い、Vrefに近いVmuxを二分探索するようにしてもよい。すなわち、まず、DA[5:0]を中間値32に初期設定し(S10)、CMPがハイレベルであれば(S20のY)DA[5:0]から16を減算し(S30)、CMPがローレベルであれば(S20のN)DA[5:0]に16を加算する(S32)。次に、CMPがハイレベルであれば(S40のY)DA[5:0]から8を減算し(S50)、CMPがローレベルであれば(S40のN)DA[5:0]に8を加算する(S52)。次に、CMPがハイレベルであれば(S60のY)DA[5:0]から4を減算し(S70)、CMPがローレベルであれば(S60のN)DA[5:0]に4を加算する(S72)。次に、CMPがハイレベルであれば(S80のY)DA[5:0]から2を減算し(S90)、CMPがローレベルであれば(S80のN)DA[5:0]に2を加算する(S92)。次に、CMPがハイレベルであれば(S100のY)DA[5:0]から1を減算し(S110)、CMPがローレベルであれば(S100のN)DA[5:0]に1を加算する(S112)。次に、CMPがハイレベルであれば(S120のY)DA[5:0]から1を減算する(S130)。最後に、出力コードD[5:0]にDA[5:0]をセットする(S140)。

For example, the

デジタル調整回路500は、クロック信号MCLKに同期して、逐次比較回路400の6ビット出力コードD[5:0]に、4ビットの補正コードCALB_D[3:0](−8〜+7)を加算することで補正された6ビットコードDCAL[5:0]を生成して出力する。具体的には、D[5:0]とCALB_D[3:0]をともに7ビットコードに符号拡張して加算することにより7ビットの加算結果SUM[6:0]を生成し、SUM[5:0]をDCAL[5:0]にセットする。ただし、オーバーフロー対策として、SUM[6]=1かつCALB_D[3]=0であればDCAL[5:0]=63、SUM[6]=1かつCALB_D[3]=1であればDCAL[5:0]=0にセットする。

The

前述したように、ビット調整回路110の抵抗値はCALB_A[3:0]の設定値に応じて変わり、式(1)より、ビット調整回路110の抵抗値Rmbaseを変更することで電圧V1〜V63の値を変更することができる。そして、逐次比較回路400は、VmuxがVrefに最も近づくDA[5:0]の値を6ビットの出力コードD[5:0]にセットするようになっており、CALB_A[3:0]を適切に設定することにより、基準温度T0(例えば25℃)でD[5:0]が32になるべく近い値になるように粗調整することができる。本実施形態では、基準温度T0(例えば25℃)においてD[5:0]が32±7の範囲のいずれかの値になるように粗調整される。そして、デジタル調整回路500により、D[5:0]に−8〜+7の補正コードCALB_D[3:0]が加算されるので、CALB_D[3:0]を適切に設定することにより、基準温度T0(例えば25℃)においてDCAL[5:0]が32になるように微調整することができる。

As described above, the resistance value of the

ところで、電圧V1〜V63の値は、式(1)に従い、温度が高くなるほど高くなる。つまり、電圧V1〜V63のうちVrefに最も近い電圧が温度に応じて変化する。これにより、DCAL[5:0]は温度が高いほど大きく温度が低いほど小さくなり、本実施形態の温度検出回路1は温度センサーとして機能する。

By the way, the values of the voltages V 1 to V 63 become higher as the temperature becomes higher according to the equation (1). That is, the voltage closest to V ref among the voltages V 1 to V 63 changes according to the temperature. As a result, DCAL [5: 0] increases as the temperature increases and decreases as the temperature decreases, and the

なお、コンパレーター300と逐次比較回路400は、イネーブル信号ENがアクティブ(例えばハイレベル)の時のみ動作し、イネーブル信号ENが非アクティブ(例えばローレベル)の時は動作を停止する。これにより、消費電力を低減することができる。

Note that the comparator 300 and the

図7は、温度検出回路1による温度検出動作のタイミングチャートの一例を示す図である。図7の例は、基準温度T0(例えば25℃)においてD[5:0]が35になるように粗調整され、CALB_D[3:0]=−3に設定することでDCAL[5:0]が32になるように微調整されているものとし、温度が基準温度T0(例えば25℃)よりも少し高い時の温度検出動作を示している。

FIG. 7 is a diagram illustrating an example of a timing chart of the temperature detection operation by the

図7に示すように、時刻t0においてイネーブル信号ENをローレベル(非アクティブ)からハイレベル(アクティブ)に変更することにより、温度検出回路1による温度検出動作が開始する。時刻t1におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が32に初期設定される(図6のS10)。これにより、マルチプレクサー200の選択電圧VmuxがV32となる。そして、時刻t2におけるクロック信号MCLKの立ち上がりにおいてV32<Vrefなので、コンパレーター300の出力信号CMPはローレベルのままである。

As shown in FIG. 7, by changing the enable signal EN from the low level (inactive) to a high level (active) at time t 0, a temperature detection operation by the

次に、CMPがローレベルなので、時刻t3におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が48(=32+16)に設定される(図6のS32)。これにより、マルチプレクサー200の選択電圧VmuxがV48となる。そして、時刻t4におけるクロック信号MCLKの立ち上がりにおいてV48>Vrefなので、コンパレーター300の出力信号CMPはローレベルからハイレベルに変化する。 Next, the CMP is low, in synchronization at time t 3 to the rise of the clock signal MCLK, DA [5: 0] is set to 48 (= 32 + 16) ( S32 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 48 . Since V 48 > V ref at the rise of the clock signal MCLK at time t 4, the output signal CMP of the comparator 300 changes from low level to high level.

次に、CMPがハイレベルなので、時刻t5におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が40(=48−8)に設定される(図6のS50)。これにより、マルチプレクサー200の選択電圧VmuxがV40となる。そして、時刻t6におけるクロック信号MCLKの立ち上がりにおいてV40>Vrefなので、コンパレーター300の出力信号CMPはハイレベルのままである。 Next, the CMP is high level, in synchronization with the rising edge of the clock signal MCLK at time t 5, DA [5: 0 ] is set to 40 (= 48-8) (S50 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 40 . Since V 40 > V ref at the rise of the clock signal MCLK at time t 6, the output signal CMP of the comparator 300 remains at a high level.

次に、CMPがハイレベルなので、時刻t7におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が36(=40−4)に設定される(図6のS70)。これにより、マルチプレクサー200の選択電圧VmuxがV36となる。そして、時刻t8におけるクロック信号MCLKの立ち上がりにおいてV36<Vrefなので、コンパレーター300の出力信号CMPはハイレベルからローレベルに変化する。 Next, the CMP is high level, in synchronization at time t 7 to the rise of the clock signal MCLK, DA [5: 0] is set to 36 (= 40-4) (S70 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 36 . Since V 36 <V ref at the rising edge of the clock signal MCLK at time t 8, the output signal CMP of the comparator 300 changes from high level to low level.

次に、CMPがローレベルなので、時刻t9におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が38(=36+2)に設定される(図6のS92)。これにより、マルチプレクサー200の選択電圧VmuxがV38となる。そして、時刻t10におけるクロック信号MCLKの立ち上がりにおいてV38>Vrefなので、コンパレーター300の出力信号CMPはローレベルからハイレベルに変化する。 Next, the CMP is low, in synchronization at time t 9 to the rise of the clock signal MCLK, DA [5: 0] is set to 38 (= 36 + 2) ( S92 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 38 . Since V 38 > V ref at the rise of the clock signal MCLK at time t 10, the output signal CMP of the comparator 300 changes from low level to high level.

次に、CMPがハイレベルなので、時刻t11におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が37(=38−1)に設定される(図6のS110)。これにより、マルチプレクサー200の選択電圧VmuxがV37となる。そして、時刻t12におけるクロック信号MCLKの立ち上がりにおいてV37>Vrefなので、コンパレーター300の出力信号CMPはハイレベルのままである。 Next, the CMP is high level, in synchronization at time t 11 to the rising edge of the clock signal MCLK, DA [5: 0] is set to 37 (= 38-1) (S110 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 37 . Since V 37 > V ref at the rising edge of the clock signal MCLK at time t 12, the output signal CMP of the comparator 300 remains at a high level.

次に、CMPがハイレベルなので、時刻t13におけるクロック信号MCLKの立ち上がりに同期して、DA[5:0]が36(=37−1)に設定される(図6のS130)。これにより、マルチプレクサー200の選択電圧VmuxがV36となる。 Next, the CMP is high level, in synchronization at time t 13 to the rising edge of the clock signal MCLK, DA [5: 0] is set to 36 (= 37-1) (S130 in FIG. 6). As a result, the selection voltage V mux of the multiplexer 200 becomes V 36 .

最後に、時刻t14におけるクロック信号MCLKの立ち下がりに同期して、逐次比較回路400の出力コードD[5:0]が35から36に更新された後(図6のS140)、デジタル調整回路500の出力コードDCAL[5:0]が32(=35−3)から33(=36−3)に更新される。 Finally, in synchronization at time t 14 to the falling edge of the clock signal MCLK, the output code D of the successive approximation circuit 400 [5: 0] after it that have been updated from 35 36 (S140 in FIG. 6), the digital adjustment circuit The output code DCAL [5: 0] of 500 is updated from 32 (= 35-3) to 33 (= 36-3).

以上に説明したように、第1実施形態の温度検出回路では、VDD−VSSの間に、負の温度係数を有する複数の抵抗(112−1〜112−15)と正の温度係数を有する複数の抵抗(120−0〜120−63、122)が直列に接続されているので、各接続点の電圧V0〜V63は温度に応じて変化する。そして、逐次比較回路400により、マルチプレクサー200の選択電圧Vmuxは基準電圧Vref以下で基準電圧Vrefに最も近い電圧になるので、この電圧を選択するコードDA[5:0]は温度情報を含んでいる。そして、第1実施形態の温度検出回路によれば、バンドギャップリファレンス回路やAD変換回路が不要であり、各抵抗(112−1〜112−15、120−0〜120−63、122)の抵抗値を適切に選択することで従来よりも小さな消費電力と回路サイズにすることができる。

As described above, in the temperature detection circuit according to the first embodiment, a plurality of resistors (112-1 to 112-15) having a negative temperature coefficient and a plurality having a positive temperature coefficient are between VDD and VSS. Since the resistors (120-0 to 120-63, 122) are connected in series, the voltages V 0 to V 63 at each connection point change according to the temperature. Then, the

また、第1実施形態の温度検出回路によれば、負の温度係数を有する複数の抵抗(112−1〜112−15)と正の温度係数を有する複数の抵抗(120−0〜120−63、122)は温度変化に対する抵抗値の変化の方向が逆向きになるので、温度変化に対する各接続点の電圧V0〜V63の変化量をより大きくすることができる。これにより、温度検出感度を向上させることができる。 Further, according to the temperature detection circuit of the first embodiment, a plurality of resistors (112-1 to 112-15) having a negative temperature coefficient and a plurality of resistors (120-0 to 120-63) having a positive temperature coefficient. 122), the direction of change of the resistance value with respect to the temperature change is reversed, so that the amount of change in the voltages V 0 to V 63 at each connection point with respect to the temperature change can be further increased. Thereby, temperature detection sensitivity can be improved.

また、第1実施形態の温度検出回路によれば、スイッチ114−1〜114−15のオン/オフにより、ビット調整回路の抵抗値が変わるので、VDD−VSS間を抵抗分圧して得られる各接続点の電圧V0〜V63を調整することができる。これにより、コードD[5:0]のオフセット(基準温度T0での基準値(32)との差)を粗調整することができる。さらに、デジタル調整回路500により微調整することで、出力コードDCAL[5:0]のオフセットを完全にキャンセルすることができる。

Further, according to the temperature detection circuit of the first embodiment, the resistance value of the bit adjustment circuit changes depending on the on / off of the switches 114-1 to 114-15. The voltages V 0 to V 63 at the connection point can be adjusted. Thereby, the offset of the code D [5: 0] (difference from the reference value (32) at the reference temperature T 0 ) can be roughly adjusted. Furthermore, the fine adjustment by the

2.第2実施形態

図8は、第2実施形態の温度検出回路の機能ブロック図である。本実施形態の温度検出回路1は、抵抗部10、電圧選択部20、電圧比較部30、温度情報コード生成部40、温度情報コード補正部50を含む。なお、本実施形態の温度検出回路1は、これらの一部の構成(要素)を省略した構成としてもよい。第2実施形態の温度検出回路では、抵抗部10は、複数の抵抗12の少なくとも1つを、抵抗値の温度特性が異なる他の抵抗13に切り替えるための第2のスイッチ16を含む。第2のスイッチ16は、1つでもよいし複数でもよい。図8のその他の構成は、図1に示した第1実施形態の温度検出回路と同じであるため、説明を省略する。

2. Second Embodiment FIG. 8 is a functional block diagram of a temperature detection circuit according to a second embodiment. The

図9は、第2実施形態の温度検出回路の構成例を示す図である。図9に示すように、第2実施形態の温度検出回路1は、ビット調整回路110、64個の抵抗120−0〜120−63、抵抗122、抵抗124、スイッチ126、マルチプレクサー200、コンパレーター300、基準電圧生成回路310、逐次比較回路400、デジタル調整回路500を含む。なお、本実施形態の温度検出回路1は、これらの一部の構成(要素)を省略した構成としてもよい。第2実施形態の温度検出回路では、図2に示した第1実施形態の温度検出回路に対して、抵抗124(図8の抵抗13の一例)とスイッチ126(図8の第2のスイッチ16の一例)が追加されているとともに、ビット調整回路110の構成が異なり、その他の構成は同じである。第1実施形態と同じ構成については説明を省略する。

FIG. 9 is a diagram illustrating a configuration example of the temperature detection circuit of the second embodiment. As shown in FIG. 9, the

抵抗124は、基準温度T0(例えば25℃)での抵抗値は抵抗124と等しいが、温度特性は抵抗124と異なる。抵抗122が正の温度特性を有するのに対して、抵抗124は、抵抗122と温度係数が異なる正の温度特性を有するようにしてもよいし、負の温度特性を有するようにしてもよい。例えば、抵抗122を拡散抵抗で実現し、抵抗124をウェル抵抗やポリ抵抗で実現してもよい。

The

第2実施形態の温度検出回路1では、制御信号SEL_RPによってスイッチ126を制御することで、抵抗122と抵抗124のいずれか一方を選択して抵抗120−63とグランドの間に接続可能になっている。基準温度T0(例えば25℃)ではスイッチ126を切り替えても抵抗値は変わらないが、基準温度T0(例えば25℃)以外の温度では、スイッチ126を切り替えることで抵抗値が変わる。

In the

図10に、第2実施形態におけるビット調整回路110の構成例を示す。図10に示すように、第2実施形態のビット調整回路110は、図3に示した第1実施形態のビット調整回路に対して、抵抗113(図8の抵抗13の一例)とスイッチ115(図8の第2のスイッチ16の一例)が追加されており、その他の構成は同じである。第1実施形態と同じ構成については説明を省略する。抵抗113は、基準温度T0(例えば25℃)での抵抗値は抵抗112−15と等しいが、温度特性は抵抗112−15と異なる。抵抗112−15が負の温度特性を有するのに対して、抵抗113は、正の温度特性を有するようにしてもよいし、抵抗112−15と温度係数が異なる負の温度特性を有するようにしてもよい。例えば、抵抗112−15をポリ抵抗で実現し、抵抗113を拡散抵抗やウェル抵抗で実現してもよい。

FIG. 10 shows a configuration example of the

第2実施形態のビット調整回路110では、スイッチ114−15がオフの時、制御信号SEL_RMによってスイッチ115を制御することで、抵抗113と抵抗112−15のいずれか一方を選択して抵抗112−14と抵抗120−0の間に接続可能になっている。基準温度T0(例えば25℃)ではスイッチ115を切り替えてもビット調整回路110の抵抗値は変わらないが、基準温度T0(例えば25℃)以外の温度では、スイッチ115を切り替えることでビット調整回路110の抵抗値が変わる。

In the

このような構成により、第2実施形態の温度検出回路1は、スイッチ115とスイッチ126の少なくとも一方を切り替えることで、温度変化に対する各電圧Vxの変化率を変更することができるようになっている。例えば、抵抗124が抵抗122の温度係数よりも大きい正の温度係数を有する場合、スイッチ115の選択を抵抗112−15に固定したままスイッチ126の選択を抵抗122から抵抗124に切り替えることにより、式(1)のtclrpの絶対値が実質的に大きくなるため、温度変化に対する各電圧Vxの変化率が増加する。また、例えば、抵抗113が正の温度係数を有する場合、スイッチ126の選択を抵抗122に固定したままスイッチ115の選択を抵抗112−15から抵抗113に切り替えることにより、式(1)のtclrmの絶対値が実質的に小さくなるため、温度変化に対する各電圧Vxの変化率が減少する。

With such a configuration, the

すなわち、スイッチ115とスイッチ126の少なくとも一方を切り替えることで、温度検出回路1の出力コードDCAL[5:0]の温度に対する傾き(変化率)を変更することができる。例えば、図11に示すように、プロセス変動に起因して実線で示す仕様上の特性よりも傾きが小さい特性(一点鎖線の特性)の出力コードDCAL[5:0]が得られた場合、スイッチ126の選択を抵抗122から温度係数がより大きい抵抗124に切り替えることにより、実線の特性に近づけることができる。また、実線で示す仕様上の特性よりも傾きが大きい特性(二点鎖線の特性)のDCAL[5:0]が得られた場合、スイッチ115の選択を抵抗112−15から正の温度係数の抵抗113に切り替えることにより、実線の特性に近づけることができる。

That is, by switching at least one of the

以上に説明した第2実施形態の温度検出回路によれば、第1実施形態と同様の効果を奏することができる。さらに、第2実施形態の温度検出回路によれば、スイッチ115やスイッチ126を切り替えることにより、温度変化に対する各接続点の電圧V0〜V63の変化量が変わるので、出力コードDCAL[5:0]の温度に対する変化率(傾き)、すなわち温度検出感度を調整することができる。

According to the temperature detection circuit of the second embodiment described above, the same effect as that of the first embodiment can be obtained. Furthermore, according to the temperature detection circuit of the second embodiment, by changing the

なお、本発明は本実施形態に限定されず、本発明の要旨の範囲内で種々の変形実施が可能である。 In addition, this invention is not limited to this embodiment, A various deformation | transformation implementation is possible within the range of the summary of this invention.

例えば、第2実施形態において、スイッチ115やスイッチ126が、温度係数が互いに異なるより多くの抵抗から1の抵抗を選択するように変形してもよい。このようにすれば、温度に対する出力コードDCAL[5:0]の傾きをより細かく調整可能になる。

For example, in the second embodiment, the

本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。 The present invention includes configurations that are substantially the same as the configurations described in the embodiments (for example, configurations that have the same functions, methods, and results, or configurations that have the same objects and effects). In addition, the invention includes a configuration in which a non-essential part of the configuration described in the embodiment is replaced. In addition, the present invention includes a configuration that exhibits the same operational effects as the configuration described in the embodiment or a configuration that can achieve the same object. Further, the invention includes a configuration in which a known technique is added to the configuration described in the embodiment.

1 温度検出回路、10 抵抗部、12,13 抵抗、15 第1のスイッチ、16 第2のスイッチ、20 電圧選択部、22 選択電圧、30 電圧比較部、32 比較結果、34 基準電圧、40 温度情報コード生成部、42 デジタルコード、44 選択信号、50 温度情報コード補正部、52 デジタルコード、54 補正ビット情報、110 ビット調整回路、112−1〜112−15 抵抗、113 抵抗、114−1〜114−15 スイッチ、115 スイッチ、116 デコーダー、120−0〜120−63 抵抗、122,124 抵抗、126 スイッチ、200 マルチプレクサー、300 コンパレーター、310 基準電圧生成回路、312,314 抵抗、400 逐次比較回路、500 デジタル調整回路

DESCRIPTION OF

Claims (5)

前記抵抗部の複数の接続点の電圧が入力され、選択信号に応じて前記複数の接続点の電圧から1の電圧を選択する電圧選択部と、

前記電圧選択部が選択する電圧を一定の基準電圧と比較する電圧比較部と、

前記電圧比較部の比較結果に応じて、前記電圧選択部が選択する電圧が前記基準電圧に近づくように前記選択信号を逐次的に変更し、前記選択信号に基づいて温度情報を表すデジタルコードを生成する温度情報コード生成部と、を含む、温度検出回路。 A resistance unit in which a plurality of resistors including at least two types of resistors having different temperature characteristics of resistance values are connected in series between two power sources;

A voltage selection unit that receives voltages at a plurality of connection points of the resistance unit and selects one voltage from the voltages at the plurality of connection points according to a selection signal;

A voltage comparison unit that compares a voltage selected by the voltage selection unit with a constant reference voltage;

According to the comparison result of the voltage comparison unit, the selection signal is sequentially changed so that the voltage selected by the voltage selection unit approaches the reference voltage, and a digital code representing temperature information based on the selection signal is provided. A temperature detection circuit including a temperature information code generation unit to be generated.

前記抵抗部は、

前記複数の抵抗の少なくとも1つは温度が高いほど抵抗値が高くなる正の温度特性を有する抵抗であり、前記複数の抵抗の他の少なくとも1つは温度が高いほど抵抗値が低くなる負の温度特性を有する抵抗である、温度検出回路。 In claim 1,

The resistance portion is

At least one of the plurality of resistors is a resistor having a positive temperature characteristic in which a resistance value increases as the temperature increases, and at least one of the plurality of resistors is a negative resistor whose resistance value decreases as the temperature increases. A temperature detection circuit that is a resistor having temperature characteristics.

前記抵抗部は、

前記複数の抵抗の少なくとも1つをバイパスするための第1のスイッチを含む、温度検出回路。 In claim 1 or 2,

The resistance portion is

A temperature detection circuit including a first switch for bypassing at least one of the plurality of resistors.

前記抵抗部は、

前記複数の抵抗のいずれとも異なり、かつ、前記複数の抵抗のうちの少なくとも1つの抵抗と抵抗値の温度特性が異なる他の抵抗と、前記少なくとも1つの抵抗を前記他の抵抗に切り替えるための第2のスイッチと、を含む、温度検出回路。 In any one of Claims 1 thru | or 3,

The resistance portion is

Unlike with any of said plurality of resistors, and other and resistance-temperature characteristics are different at least one resistor and the resistance value of said plurality of resistors, for switching said at least one resistor to the other resistor including a second switch, a temperature detection circuit.

補正ビット情報に基づいて、前記温度情報コード生成部が生成する前記デジタルコード

を補正する温度情報コード補正部をさらに含む、温度検出回路。 In any one of Claims 1 thru | or 4,

A temperature detection circuit further comprising a temperature information code correction unit that corrects the digital code generated by the temperature information code generation unit based on correction bit information.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011021761A JP5729544B2 (en) | 2011-02-03 | 2011-02-03 | Temperature detection circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011021761A JP5729544B2 (en) | 2011-02-03 | 2011-02-03 | Temperature detection circuit |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012163356A JP2012163356A (en) | 2012-08-30 |

| JP2012163356A5 JP2012163356A5 (en) | 2014-03-13 |

| JP5729544B2 true JP5729544B2 (en) | 2015-06-03 |

Family

ID=46842890

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011021761A Expired - Fee Related JP5729544B2 (en) | 2011-02-03 | 2011-02-03 | Temperature detection circuit |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5729544B2 (en) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5987639B2 (en) * | 2012-11-01 | 2016-09-07 | 株式会社デンソー | Current measuring device |

| JP6750211B2 (en) | 2015-12-03 | 2020-09-02 | セイコーエプソン株式会社 | Circuit devices, oscillators, electronic devices and mobile units |

| JP6784020B2 (en) | 2015-12-03 | 2020-11-11 | セイコーエプソン株式会社 | Circuits, oscillators, electronics and mobiles |

| CN107764431B (en) * | 2017-12-06 | 2023-12-08 | 西安智多晶微电子有限公司 | Chip core temperature detection circuit |

| JP6844589B2 (en) * | 2018-06-27 | 2021-03-17 | 株式会社デンソー | Current detector |

| CN110487436B (en) * | 2019-08-29 | 2020-12-01 | 深迪半导体(上海)有限公司 | Temperature sensor and gyroscope |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS54147060A (en) * | 1978-05-11 | 1979-11-16 | Toshiba Corp | Temperature display device |

| JPS6025426A (en) * | 1983-07-22 | 1985-02-08 | Seiko Epson Corp | Temperature detecting circuit |

| JP3074083B2 (en) * | 1993-01-08 | 2000-08-07 | キヤノン株式会社 | Temperature detector |

| JP2954483B2 (en) * | 1994-05-10 | 1999-09-27 | 大崎電気工業株式会社 | Integrating calorimeter |

| JP2000243839A (en) * | 1999-02-18 | 2000-09-08 | Fuji Xerox Co Ltd | Semiconductor integrated circuit device and recording device |

| KR100546384B1 (en) * | 2003-09-30 | 2006-01-26 | 삼성전자주식회사 | Temperature sensor for sensing current temperature and generating digital data corresponding to current temperature |

-

2011

- 2011-02-03 JP JP2011021761A patent/JP5729544B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012163356A (en) | 2012-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5729544B2 (en) | Temperature detection circuit | |

| JP5407685B2 (en) | Successive comparison type AD converter and method of adjusting operation clock of successive approximation type AD converter | |

| US7209069B2 (en) | Successive approximation analog-to-digital converter with current steered digital-to-analog converter | |

| JP3807381B2 (en) | A / D conversion circuit, temperature sensor circuit, integrated circuit, and method of adjusting temperature sensor circuit | |

| US20130015996A1 (en) | Ad converter and information processing apparatus | |

| JP4426590B2 (en) | Variable gain analog-to-digital converter, gain-adjustable analog-digital converter gain adjustment method, and system including variable gain analog-to-digital converter | |

| JP6102521B2 (en) | SAR analog-digital conversion method and SAR analog-digital conversion circuit | |

| JP2009192507A (en) | Temperature detection circuit | |

| Iizuka et al. | A 14-bit digitally self-calibrated pipelined ADC with adaptive bias optimization for arbitrary speeds up to 40 MS/s | |

| US10367517B2 (en) | Analog to digital conversion apparatus and analog to digital converter calibration method of the same | |

| US9866232B2 (en) | Analog-to-digital converter, radiation detector and wireless receiver | |

| CN112751565B (en) | Self-calibration on-chip reference voltage module | |

| US10224884B2 (en) | Circuit for and method of implementing a multifunction output generator | |

| TWI632778B (en) | Digital-to-analog converter and an operation method thereof | |

| KR20180032710A (en) | Hybrid on-chip cmos temperature sensor and temperature measurement method thereof | |

| US20100052639A1 (en) | Power supply controller having analog to digital converter | |

| US8618972B1 (en) | Analog-to-digital signal conversion method and apparatus therefor | |

| WO2013099121A1 (en) | Cr oscillation circuit | |

| JP2014098614A (en) | Temperature sensor and semiconductor device | |

| US10700694B2 (en) | Calibration method and related calibration system | |

| US8587465B2 (en) | Successive approximation analog to digital converter with comparator input toggling | |

| JP2010273008A (en) | Analog/digital converter | |

| JPWO2010137095A1 (en) | Resistive digital / analog converter | |

| KR102243301B1 (en) | Dc offset correction apparatus of analog circuit | |

| JP2004080238A (en) | D/a converter and automatic correction method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140124 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140124 |

|

| RD07 | Notification of extinguishment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7427 Effective date: 20140619 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140905 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141022 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141216 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150311 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150324 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5729544 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |