JP5201791B2 - Display device and electronic device - Google Patents

Display device and electronic device Download PDFInfo

- Publication number

- JP5201791B2 JP5201791B2 JP2005351497A JP2005351497A JP5201791B2 JP 5201791 B2 JP5201791 B2 JP 5201791B2 JP 2005351497 A JP2005351497 A JP 2005351497A JP 2005351497 A JP2005351497 A JP 2005351497A JP 5201791 B2 JP5201791 B2 JP 5201791B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- power supply

- supply line

- layer

- source signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 claims description 349

- 230000008569 process Effects 0.000 claims description 63

- 239000011159 matrix material Substances 0.000 claims description 24

- 238000007639 printing Methods 0.000 claims description 14

- 239000010410 layer Substances 0.000 description 718

- 239000010408 film Substances 0.000 description 210

- 239000004065 semiconductor Substances 0.000 description 149

- 239000000758 substrate Substances 0.000 description 135

- 239000000463 material Substances 0.000 description 120

- 239000000203 mixture Substances 0.000 description 61

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 55

- 239000004020 conductor Substances 0.000 description 55

- 229910052760 oxygen Inorganic materials 0.000 description 55

- 239000001301 oxygen Substances 0.000 description 55

- 239000007789 gas Substances 0.000 description 54

- 230000001699 photocatalysis Effects 0.000 description 50

- 239000000126 substance Substances 0.000 description 50

- 230000015572 biosynthetic process Effects 0.000 description 49

- 239000010409 thin film Substances 0.000 description 45

- 238000004519 manufacturing process Methods 0.000 description 43

- 238000004544 sputter deposition Methods 0.000 description 41

- 238000005530 etching Methods 0.000 description 38

- 229910052581 Si3N4 Inorganic materials 0.000 description 35

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 35

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 34

- 239000010949 copper Substances 0.000 description 34

- 238000010438 heat treatment Methods 0.000 description 32

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 30

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 29

- 229910052814 silicon oxide Inorganic materials 0.000 description 29

- 239000004642 Polyimide Substances 0.000 description 28

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 28

- 229920001721 polyimide Polymers 0.000 description 28

- 229910052710 silicon Inorganic materials 0.000 description 28

- 239000010703 silicon Substances 0.000 description 28

- 229910052709 silver Inorganic materials 0.000 description 28

- 239000004332 silver Substances 0.000 description 27

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 26

- 229910052802 copper Inorganic materials 0.000 description 26

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 25

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 25

- 239000013078 crystal Substances 0.000 description 25

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 25

- 238000009832 plasma treatment Methods 0.000 description 25

- 229910052739 hydrogen Inorganic materials 0.000 description 24

- 239000001257 hydrogen Substances 0.000 description 24

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 24

- 239000011368 organic material Substances 0.000 description 24

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 24

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 23

- 239000003990 capacitor Substances 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 22

- 239000002184 metal Substances 0.000 description 22

- 239000010936 titanium Substances 0.000 description 22

- 239000010931 gold Substances 0.000 description 21

- 239000011347 resin Substances 0.000 description 21

- 229920005989 resin Polymers 0.000 description 21

- 125000001424 substituent group Chemical group 0.000 description 21

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 20

- 239000012298 atmosphere Substances 0.000 description 20

- 229910052757 nitrogen Inorganic materials 0.000 description 17

- 239000002904 solvent Substances 0.000 description 17

- 239000011521 glass Substances 0.000 description 16

- 230000001681 protective effect Effects 0.000 description 16

- 229910052721 tungsten Inorganic materials 0.000 description 16

- 239000011651 chromium Substances 0.000 description 15

- 229910052719 titanium Inorganic materials 0.000 description 15

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 15

- 239000010937 tungsten Substances 0.000 description 15

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 14

- 239000003570 air Substances 0.000 description 14

- 238000012986 modification Methods 0.000 description 14

- 230000004048 modification Effects 0.000 description 14

- 239000002356 single layer Substances 0.000 description 14

- -1 Ti (titanium) Chemical class 0.000 description 13

- 229910052782 aluminium Inorganic materials 0.000 description 13

- 229910052737 gold Inorganic materials 0.000 description 13

- 239000012212 insulator Substances 0.000 description 13

- 238000012545 processing Methods 0.000 description 13

- 239000011135 tin Substances 0.000 description 13

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 12

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 12

- 230000003071 parasitic effect Effects 0.000 description 12

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 11

- 229910052786 argon Inorganic materials 0.000 description 11

- 238000007599 discharging Methods 0.000 description 11

- 238000002347 injection Methods 0.000 description 11

- 239000007924 injection Substances 0.000 description 11

- 229910021417 amorphous silicon Inorganic materials 0.000 description 10

- 125000000962 organic group Chemical group 0.000 description 10

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 10

- 238000007740 vapor deposition Methods 0.000 description 10

- 239000011787 zinc oxide Substances 0.000 description 10

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 9

- 125000000217 alkyl group Chemical group 0.000 description 9

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 9

- 150000002739 metals Chemical class 0.000 description 9

- 229910052759 nickel Inorganic materials 0.000 description 9

- 238000005192 partition Methods 0.000 description 9

- 238000004528 spin coating Methods 0.000 description 9

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 8

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 229910052804 chromium Inorganic materials 0.000 description 8

- 125000001153 fluoro group Chemical group F* 0.000 description 8

- 239000002923 metal particle Substances 0.000 description 8

- 238000000206 photolithography Methods 0.000 description 8

- 238000001020 plasma etching Methods 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 7

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- 239000000853 adhesive Substances 0.000 description 7

- 230000001070 adhesive effect Effects 0.000 description 7

- 230000008901 benefit Effects 0.000 description 7

- 238000002425 crystallisation Methods 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 238000001035 drying Methods 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 229910052731 fluorine Inorganic materials 0.000 description 7

- 239000011737 fluorine Substances 0.000 description 7

- 229910052750 molybdenum Inorganic materials 0.000 description 7

- 239000011733 molybdenum Substances 0.000 description 7

- 230000001590 oxidative effect Effects 0.000 description 7

- 239000002245 particle Substances 0.000 description 7

- 229920000642 polymer Polymers 0.000 description 7

- 238000002203 pretreatment Methods 0.000 description 7

- 239000003870 refractory metal Substances 0.000 description 7

- 229910052715 tantalum Inorganic materials 0.000 description 7

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 7

- 229910052725 zinc Inorganic materials 0.000 description 7

- 239000011701 zinc Substances 0.000 description 7

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 6

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 6

- 230000007547 defect Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 238000001704 evaporation Methods 0.000 description 6

- 238000010304 firing Methods 0.000 description 6

- 230000005525 hole transport Effects 0.000 description 6

- 229910010272 inorganic material Inorganic materials 0.000 description 6

- 239000011147 inorganic material Substances 0.000 description 6

- 150000004767 nitrides Chemical class 0.000 description 6

- 238000007747 plating Methods 0.000 description 6

- 230000003252 repetitive effect Effects 0.000 description 6

- 238000007789 sealing Methods 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 229910001887 tin oxide Inorganic materials 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- 230000000903 blocking effect Effects 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 230000008859 change Effects 0.000 description 5

- 238000006243 chemical reaction Methods 0.000 description 5

- 230000008025 crystallization Effects 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 5

- 239000012071 phase Substances 0.000 description 5

- 239000011241 protective layer Substances 0.000 description 5

- 229920001187 thermosetting polymer Polymers 0.000 description 5

- 229910052718 tin Inorganic materials 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 239000004372 Polyvinyl alcohol Substances 0.000 description 4

- 229910006404 SnO 2 Inorganic materials 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 4

- 239000000356 contaminant Substances 0.000 description 4

- 238000011109 contamination Methods 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 235000019441 ethanol Nutrition 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 239000011810 insulating material Substances 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 229920002451 polyvinyl alcohol Polymers 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 239000003566 sealing material Substances 0.000 description 4

- 229910021332 silicide Inorganic materials 0.000 description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 230000005236 sound signal Effects 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- 150000001298 alcohols Chemical class 0.000 description 3

- QDWJUBJKEHXSMT-UHFFFAOYSA-N boranylidynenickel Chemical compound [Ni]#B QDWJUBJKEHXSMT-UHFFFAOYSA-N 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 238000007598 dipping method Methods 0.000 description 3

- 150000002148 esters Chemical class 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 3

- 239000002105 nanoparticle Substances 0.000 description 3

- 238000007645 offset printing Methods 0.000 description 3

- 239000003960 organic solvent Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 238000002161 passivation Methods 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 238000007650 screen-printing Methods 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- CERQOIWHTDAKMF-UHFFFAOYSA-N Methacrylic acid Chemical compound CC(=C)C(O)=O CERQOIWHTDAKMF-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- 229910002808 Si–O–Si Inorganic materials 0.000 description 2

- PPBRXRYQALVLMV-UHFFFAOYSA-N Styrene Chemical compound C=CC1=CC=CC=C1 PPBRXRYQALVLMV-UHFFFAOYSA-N 0.000 description 2

- 239000004760 aramid Substances 0.000 description 2

- 229920003235 aromatic polyamide Polymers 0.000 description 2

- 125000003118 aryl group Chemical group 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 2

- 238000000354 decomposition reaction Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000007865 diluting Methods 0.000 description 2

- 238000003618 dip coating Methods 0.000 description 2

- 239000002270 dispersing agent Substances 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 230000004927 fusion Effects 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 238000004050 hot filament vapor deposition Methods 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 2

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 2

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical compound C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 2

- 230000010355 oscillation Effects 0.000 description 2

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 2

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 2

- 238000007750 plasma spraying Methods 0.000 description 2

- 229920002480 polybenzimidazole Polymers 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 239000004094 surface-active agent Substances 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004693 Polybenzimidazole Substances 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- 229910003087 TiOx Inorganic materials 0.000 description 1

- 239000011358 absorbing material Substances 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 238000003763 carbonization Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 238000000295 emission spectrum Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 150000002483 hydrogen compounds Chemical class 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052976 metal sulfide Inorganic materials 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- KDLHZDBZIXYQEI-UHFFFAOYSA-N palladium Substances [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000011941 photocatalyst Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 230000003334 potential effect Effects 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000012827 research and development Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 150000003839 salts Chemical class 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- HLLICFJUWSZHRJ-UHFFFAOYSA-N tioxidazole Chemical compound CCCOC1=CC=C2N=C(NC(=O)OC)SC2=C1 HLLICFJUWSZHRJ-UHFFFAOYSA-N 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000007738 vacuum evaporation Methods 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of El Displays (AREA)

Description

本発明はEL(エレクトロルミネッセンス)素子を基板上に作り込んで形成された電子ディスプレイ(電気光学装置)に関する。特に半導体素子(半導体薄膜を用いた素子)を

用いた表示装置に関する。またEL表示装置を表示部に用いた電子機器に関する。

The present invention relates to an electronic display (electro-optical device) formed by forming an EL (electroluminescence) element on a substrate. In particular, the present invention relates to a display device using a semiconductor element (an element using a semiconductor thin film). The present invention also relates to an electronic device using an EL display device for a display portion.

近年、基板上に薄膜トランジスタ(以下、本明細書中ではTFTと表記する)を形成する技術が大幅に進歩し、アクティブマトリクス型表示装置への応用開発が進められている。特に、ポリシリコンなどの多結晶半導体膜を用いたTFTは、従来のアモルファスシリコン等の非晶質半導体膜を用いたTFTよりも電界効果移動度(モビリティともいう)が高いので、高速動作が可能である。そのため、従来、基板外の駆動回路で行っていた画素の制御を、画素と同一の基板上に形成した駆動回路で行うことが可能となっている。 In recent years, a technology for forming a thin film transistor (hereinafter referred to as TFT in this specification) on a substrate has greatly advanced, and application development to an active matrix display device has been advanced. In particular, a TFT using a polycrystalline semiconductor film such as polysilicon has higher field-effect mobility (also called mobility) than a conventional TFT using an amorphous semiconductor film such as amorphous silicon, so that high-speed operation is possible. It is. For this reason, it is possible to control a pixel, which has been conventionally performed by a drive circuit outside the substrate, with a drive circuit formed on the same substrate as the pixel.

このような多結晶半導体膜を用いたアクティブマトリクス型表示装置では、同一基板上に、様々な回路や素子を作り込むことが可能であり、製造コストの低減、表示装置の小型化、歩留まりの上昇、スループットの改善など、様々な利点が得られる。 In such an active matrix display device using a polycrystalline semiconductor film, various circuits and elements can be formed on the same substrate, thereby reducing the manufacturing cost, downsizing the display device, and increasing the yield. Various advantages such as improved throughput can be obtained.

そしてさらに、自発光型素子としてEL素子を有したアクティブマトリクス型のEL表示装置の研究が活発化している。EL表示装置は、有機ELディスプレイ(OELD:Organic EL Display)又は有機ライトエミッティングダイオード(OLED:Organic Light Emitting Diode)とも呼ばれている。 In addition, active matrix EL display devices having EL elements as self-luminous elements have been actively researched. The EL display device is also called an organic EL display (OELD) or an organic light emitting diode (OLED).

EL素子は一対の電極(陽極と陰極)間にEL層が挟まれた構造となっているが、EL層は通常、積層構造となっている。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層、発光層、電子輸送層」という積層構造が挙げられる。この構造は非常に発光効率が高く、現在、研究開発が進められているEL表示装置はほとんどこの構造を採用している。 An EL element has a structure in which an EL layer is sandwiched between a pair of electrodes (anode and cathode), and the EL layer usually has a laminated structure. A typical example is a stacked structure of “hole transport layer, light emitting layer, electron transport layer” proposed by Tang et al. Of Kodak Eastman Company. This structure has very high luminous efficiency, and most EL display devices currently under research and development employ this structure.

また他にも、陽極上に正孔注入層、正孔輸送層、発光層、電子輸送層、または正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。 In addition, a hole injection layer, a hole transport layer, a light emitting layer, an electron transport layer, or a hole injection layer, a hole transport layer, a light emitting layer, an electron transport layer, and an electron injection layer are sequentially stacked on the anode. Structure may be sufficient. You may dope a fluorescent pigment | dye etc. with respect to a light emitting layer.

本明細書において、陰極と陽極との間に設けられる全ての層を総称してEL層と呼ぶ。よって上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、全てEL層に含まれる。 In this specification, all layers provided between a cathode and an anode are collectively referred to as an EL layer. Therefore, the above-described hole injection layer, hole transport layer, light emitting layer, electron transport layer, electron injection layer, and the like are all included in the EL layer.

そして、上記構造でなるEL層に、一対の電極から所定の電圧をかけると、発光層においてキャリアの再結合が起こって発光する。なお本明細書においてEL素子が発光することを、EL素子が駆動すると呼ぶ。また、本明細書中では、陽極、EL層及び陰極で形成される発光素子をEL素子と呼ぶ。 When a predetermined voltage is applied from the pair of electrodes to the EL layer having the above structure, carrier recombination occurs in the light emitting layer to emit light. Note that light emission of an EL element in this specification is referred to as driving of the EL element. In this specification, a light-emitting element formed using an anode, an EL layer, and a cathode is referred to as an EL element.

なお、本明細書中において、EL素子とは、一重項励起状態からの発光(蛍光)を利用するものと、三重項励起状態からの発光(燐光)を利用するものの両方を含むものとする。 Note that in this specification, an EL element includes both an element that uses light emission (fluorescence) from a singlet excited state and an element that uses light emission (phosphorescence) from a triplet excited state.

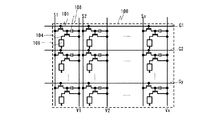

EL表示装置の駆動方法として、アナログ方式の駆動方法(アナログ駆動)と、デジタル方式の駆動方法(デジタル駆動)が挙げられる。まず、EL表示装置のアナログ駆動について、図1及び図2を用いて説明する。 As a driving method of the EL display device, an analog driving method (analog driving) and a digital driving method (digital driving) can be given. First, analog driving of the EL display device will be described with reference to FIGS.

図1に、アナログ駆動のEL表示装置の画素部100の構造を示す。ゲート信号線駆動回路からの選択信号を入力するゲート信号線(G1〜Gy)は、各画素が有するスイッチング用TFT101のゲート電極に接続されている。また各画素の有するスイッチング用TFT101のソース領域とドレイン領域は、一方がアナログのビデオ信号を入力するソース信号線(データ信号線ともいう)(S1〜Sx)に、もう一方が各画素が有する駆動用TFT104のゲート電極及び各画素が有する保持容量108にそれぞれ接続されている。

FIG. 1 shows a structure of a pixel portion 100 of an analog drive EL display device. Gate signal lines (G1 to Gy) for inputting selection signals from the gate signal line driver circuit are connected to the gate electrode of the switching

各画素が有する駆動用TFT104のソース領域とドレイン領域はそれぞれ、一方は電源供給線(V1〜Vx)に、もう一方はEL素子106に接続されている。電源供給線(V1〜Vx)の電位を電源電位と呼ぶ。また電源供給線(V1〜Vx)は、各画素が有する保持容量108に接続されている。

One of the source region and the drain region of the driving TFT 104 included in each pixel is connected to the power supply line (V1 to Vx), and the other is connected to the

EL素子106は、陽極と、陰極と、陽極と陰極との間に設けられたEL層とを有する。EL素子106の陽極が駆動用TFT104のソース領域またはドレイン領域と接続している場合、EL素子106の陽極が画素電極、陰極が対向電極となる。逆にEL素子106の陰極が駆動用TFT104のソース領域またはドレイン領域と接続している場合、EL素子106の陽極が対向電極、陰極が画素電極となる。

The

なお本明細書において、対向電極の電位を対向電位と呼ぶ。なお対向電極に対向電位を与える電源を対向電源と呼ぶ。画素電極の電位と対向電極の電位の電位差がEL駆動電圧であり、このEL駆動電圧がEL層にかかる。 Note that in this specification, the potential of the counter electrode is referred to as a counter potential. A power source that applies a counter potential to the counter electrode is referred to as a counter power source. A potential difference between the potential of the pixel electrode and the potential of the counter electrode is an EL drive voltage, and this EL drive voltage is applied to the EL layer.

図1で示したEL表示装置を、アナログ方式で駆動させた場合のタイミングチャートを図2に示す。1つのゲート信号線が選択されてから、その次に別のゲート信号線が選択されるまでの期間を1ライン期間(L)と呼ぶ。また1つの画像が表示されてから次の画像が表示されるまでの期間が1フレーム期間(F)に相当する。図1のEL表示装置の場合、ゲート信号線はy本あるので、1フレーム期間中にy個のライン期間(L1〜Ly)が設けられている。 FIG. 2 shows a timing chart when the EL display device shown in FIG. 1 is driven in an analog manner. A period from when one gate signal line is selected to when another gate signal line is selected next is referred to as one line period (L). A period from when one image is displayed until the next image is displayed corresponds to one frame period (F). In the case of the EL display device of FIG. 1, since there are y gate signal lines, y line periods (L1 to Ly) are provided in one frame period.

まず電源供給線(V1〜Vx)は一定の電源電位に保たれている。そして対向電極の電位である対向電位も一定の電位に保たれている。対向電位は、EL素子が発光する程度に電源電位との間に電位差を有している。 First, the power supply lines (V1 to Vx) are kept at a constant power supply potential. The counter potential, which is the potential of the counter electrode, is also kept constant. The counter potential has a potential difference from the power supply potential to such an extent that the EL element emits light.

第1のライン期間(L1)において、ゲート信号線G1には、ゲート信号線駆動回路からの選択信号が入力される。そして、ソース信号線(S1〜Sx)に順にアナログのビデオ信号が入力される。ゲート信号線G1に接続された全てのスイッチング用TFTはオンの状態になるので、ソース信号線に入力されたアナログのビデオ信号は、スイッチング用TFTを介して駆動用TFTのゲート電極に入力される。 In the first line period (L1), a selection signal from the gate signal line driver circuit is input to the gate signal line G1. Then, analog video signals are sequentially input to the source signal lines (S1 to Sx). Since all the switching TFTs connected to the gate signal line G1 are turned on, the analog video signal input to the source signal line is input to the gate electrode of the driving TFT via the switching TFT. .

駆動用TFTのチャネル形成領域を流れる電流の量は、そのゲート電圧によって制御される。 The amount of current flowing through the channel formation region of the driving TFT is controlled by the gate voltage.

ここで、駆動用TFTのソース領域が電源供給線に接続され、ドレイン領域がEL素子に接続されている場合を例に説明する。 Here, a case where the source region of the driving TFT is connected to the power supply line and the drain region is connected to the EL element will be described as an example.

駆動用TFTのソース領域は、電源供給線に接続されているため、画素部の各画素に同じ電位が入力されている。このとき、ソース信号線にアナログの信号が入力されると、この信号電圧の電位と、駆動用TFTのソース領域の電位との差がゲート電圧になる。EL素子に流れる電流は、駆動用TFTのゲート電圧によって決まる。ここで、EL素子の発光輝度は、EL素子の両電極間を流れる電流に比例する。こうしてEL素子はアナログのビデオ信号の電圧に制御されて発光を行う。 Since the source region of the driving TFT is connected to the power supply line, the same potential is input to each pixel in the pixel portion. At this time, when an analog signal is input to the source signal line, a difference between the potential of the signal voltage and the potential of the source region of the driving TFT becomes a gate voltage. The current flowing through the EL element is determined by the gate voltage of the driving TFT. Here, the light emission luminance of the EL element is proportional to the current flowing between both electrodes of the EL element. Thus, the EL element emits light by being controlled by the voltage of the analog video signal.

上述した動作を繰り返し、ソース信号線(S1〜Sx)へのアナログのビデオ信号の入力が終了すると、第1のライン期間(L1)が終了する。なお、ソース信号線(S1〜Sx)への、アナログのビデオ信号の入力が終了するまでの期間と水平帰線期間とを合わせて1つのライン期間としても良い。次に第2のライン期間(L2)となりゲート信号線G2に選択信号が入力される。第1のライン期間(L1)と同様に、ソース信号線(S1〜Sx)に順にアナログのビデオ信号が入力される。 When the operation described above is repeated and the input of the analog video signal to the source signal lines (S1 to Sx) is finished, the first line period (L1) is finished. The period until the input of the analog video signal to the source signal lines (S1 to Sx) and the horizontal blanking period may be combined into one line period. Next, in the second line period (L2), a selection signal is input to the gate signal line G2. Similar to the first line period (L1), analog video signals are sequentially input to the source signal lines (S1 to Sx).

全てのゲート信号線(G1〜Gy)に選択信号が入力されると、全てのライン期間(L1〜Ly)が終了する。全てのライン期間(L1〜Ly)が終了すると、1フレーム期間が終了する。1フレーム期間中において全ての画素が表示を行い、1つの画像が形成される。なお全てのライン期間(L1〜Ly)と垂直帰線期間とを合わせて1フレーム期間としても良い。 When selection signals are input to all the gate signal lines (G1 to Gy), all the line periods (L1 to Ly) are completed. When all the line periods (L1 to Ly) end, one frame period ends. All pixels display during one frame period, and one image is formed. All the line periods (L1 to Ly) and the vertical blanking period may be combined into one frame period.

以上のように、アナログのビデオ信号によってEL素子の発光量が制御され、その発光量の制御によって階調表示がなされる。この方式は、いわゆるアナログ駆動方法と呼ばれる駆動方式であり、ソース信号線に入力されるアナログのビデオ信号の電圧の変化で階調表示が行われる。 As described above, the light emission amount of the EL element is controlled by the analog video signal, and gradation display is performed by controlling the light emission amount. This method is a so-called analog driving method, and gradation display is performed by changing the voltage of an analog video signal input to the source signal line.

次に、EL表示装置のデジタル駆動について説明する。デジタル階調方式では、EL駆動用TFT104のゲート・ソース間電圧Vgは、EL素子106に全く電流が流れない範囲(点灯開始電圧以下)か、あるいは最大電流が流れる範囲(輝度飽和電圧以上)の2段階でのみ動作する。すなわちEL素子は、点灯状態と消灯状態のみをとる。

Next, digital driving of the EL display device will be described. In the digital gray scale method, the gate-source voltage Vg of the

ELディスプレイにおいては、TFTのしきい値等の特性のばらつきが表示に影響しにくいデジタル階調方式が主に用いられる。しかし、デジタル階調方式の場合、そのままでは2階調表示しか出来ないため、別の方式と組み合わせて、多階調化を図る技術が複数提案されている。 In an EL display, a digital gray scale method in which variation in characteristics such as a threshold value of TFT hardly affects display is mainly used. However, in the case of the digital gradation method, only two gradations can be displayed as it is, and therefore, a plurality of techniques for increasing the number of gradations in combination with another method have been proposed.

そのうちの1つは、面積階調方式とデジタル階調方式を組み合わせる方式である。面積階調方式とは、点灯している部分の面積を制御して、階調を出す方式である。つまり、1つの画素を複数のサブ画素に分割し、点灯しているサブ画素の数や面積を制御して、階調を表現している。この方式の欠点としては、サブ画素の数を多くすることが出来ないため、高解像度化や、多階調化が難しいことである。面積階調方式については、非特許文献1、非特許文献2などに報告がされている。

One of them is a method combining the area gradation method and the digital gradation method. The area gradation method is a method for producing gradation by controlling the area of a lighted portion. That is, one pixel is divided into a plurality of sub-pixels, and the number and area of sub-pixels that are lit are controlled to express gradation. The disadvantage of this method is that it is difficult to increase the resolution and increase the number of gradations because the number of subpixels cannot be increased. The area gradation method is reported in

もう1つの多階調化を図る方式として、時間階調方式とデジタル階調方式を組み合わせる方式がある。時間階調方式とは、点灯している時間の差を利用して、階調を出す方式である。つまり、1フレーム期間を、複数のサブフレーム期間に分割し、点灯しているサブフレーム期間の数や長さを制御して、階調を表現している。(特許文献1参照) As another method for increasing the number of gradations, there is a method combining a time gradation method and a digital gradation method. The time gradation method is a method for producing a gradation using a difference in lighting time. That is, one frame period is divided into a plurality of subframe periods, and the number of subframe periods that are lit and the length thereof are controlled to express gradation. (See Patent Document 1)

デジタル階調方式と面積階調方式と時間階調方式を組み合わせた場合については、非特許文献3に報告されている。

次に、デジタル階調を用いて階調表示する場合の、定電流駆動と定電圧駆動について説明する。 Next, constant current driving and constant voltage driving in the case of gradation display using digital gradation will be described.

定電流駆動とは、EL素子106の点灯時に駆動用TFT104を飽和領域で動作させ、全ての画素で一定の電流を供給する駆動方法である。この駆動方法は、EL素子106が劣化して電圧−電流特性が変化しても、一定の電流をEL素子106に供給できるため、EL表示装置の寿命を長くすることが出来るという利点がある。

The constant current driving is a driving method in which the driving

一方、定電圧駆動とは、EL素子106の点灯時に駆動用TFT104を線形領域で動作させ、全ての画素で一定の電圧を供給する駆動方法である。この駆動方法は、駆動用TFT104の特性がばらついても、全ての画素で一定の電圧をEL素子106に供給できるため、画素間の輝度にムラがなく、高い表示品位が得られるという利点がある。

本発明の目的は、歩留まりよく、かつ低コストで作製できる、大型で解像度の高いEL表示装置を提供することである。そのためには、以下に挙げるような問題点が存在する。 An object of the present invention is to provide a large-sized and high-resolution EL display device that can be manufactured with high yield and low cost. For this purpose, the following problems exist.

まず、EL表示装置の駆動方法として、デジタル階調と時間階調を組み合わせた場合の問題点について述べる。デジタル階調と時間階調を組み合わせた場合、多階調を表現するために、1フレーム期間を、複数のサブフレーム期間に分割し、点灯しているサブフレーム期間の数や長さを制御して、階調を表現している。つまり、アナログ階調で1枚の画像を表示させるのにかけることの出来る時間に比べて、デジタル階調と時間階調を組み合わせた場合では、1枚の絵を表示させるのにかけることの出来る時間はサブフレーム数分の1となり、アナログ階調に比べて、駆動回路を非常に高速に動作させなければならない。 First, as a driving method of the EL display device, problems in the case of combining digital gradation and time gradation will be described. When digital gradation and time gradation are combined, in order to express multiple gradations, one frame period is divided into a plurality of subframe periods, and the number and length of the lit subframe periods are controlled. To express gradation. In other words, compared to the time that can be taken to display one image with analog gradation, when a digital gradation and time gradation are combined, it can be taken to display one picture. The time is a fraction of the number of subframes, and the driving circuit must be operated at a very high speed as compared with analog gradation.

また、駆動回路の動作周波数には限界があり、サブフレームをあまり多くしたり、解像度が高くなったりすると、書き込み時間が不足する。すなわち、表示装置の駆動方法として、デジタル階調と時間階調を組み合わせた場合の問題点の一つは、書き込み時間の不足である。本発明における目的を達成するためには、書き込み時間を出来るだけ長く出来るようにしなければならない。 In addition, there is a limit to the operating frequency of the drive circuit, and if the number of subframes is too large or the resolution is increased, the writing time is insufficient. In other words, as a driving method of the display device, one of the problems when combining digital gradation and time gradation is insufficient writing time. In order to achieve the object of the present invention, it is necessary to make the writing time as long as possible.

次に、寄生容量の増大の問題について述べる。大型で解像度の高い表示装置ほど、画素部における配線は長くなり、またその配線と交差する配線の数も多くなるため、画素部における配線につく寄生容量は大きくなる。 Next, the problem of increase in parasitic capacitance will be described. As the display device is larger and has higher resolution, the wiring in the pixel portion becomes longer and the number of wirings intersecting the wiring increases, so that the parasitic capacitance attached to the wiring in the pixel portion increases.

寄生容量が大きくなると、その配線に伝わる電気信号の波形のなまりの増大を引き起こす。波形のなまりは、信号の正しい伝達を妨げ、表示品位の低下をもたらす。すなわち、大型で解像度の高いEL表示装置を得るための問題点の一つは、寄生容量の増大である。本発明における目的を達成するためには、寄生容量を出来るだけ小さくしなければならない。 When the parasitic capacitance is increased, the rounding of the waveform of the electric signal transmitted to the wiring is increased. The rounding of the waveform hinders the correct transmission of the signal and causes the display quality to deteriorate. That is, one of the problems for obtaining a large EL display device with high resolution is an increase in parasitic capacitance. In order to achieve the object of the present invention, the parasitic capacitance must be made as small as possible.

次に、低コストで作製するための問題点について述べる。現在、TFT及びそれを用いた電子回路は、半導体、絶縁体及び導電体などの各種薄膜を基板上に積層し、適宜フォトリソグラフィ技術により所定のパターンを形成して製造されるのが一般的である。フォトリソグラフィ技術とは、フォトマスクと呼ばれる透明な平板面上に光を通さない材料で形成した回路等のパターンを、光を利用して目的とする基板上に転写する技術であり、半導体集積回路等の製造工程において広く用いられている。 Next, problems for manufacturing at low cost will be described. Currently, TFTs and electronic circuits using the TFTs are generally manufactured by laminating various thin films such as semiconductors, insulators, and conductors on a substrate and appropriately forming a predetermined pattern by a photolithography technique. is there. Photolithographic technology is a technology that uses a light to transfer a circuit pattern or other pattern formed on a transparent flat plate called a photomask onto a target substrate. It is widely used in the manufacturing process.

フォトリソグラフィ技術を用いた製造工程は、フォトレジストと呼ばれる感光性の有機樹脂材料を用いて形成されるマスクパターンの取り扱いだけでも、露光、現像、焼成、剥離といった多段階の工程が必要になる。従って、フォトリソグラフィ工程の回数が増える程、製造コストは必然的に上がってしまうことになる。 The manufacturing process using the photolithography technique requires a multi-step process such as exposure, development, baking, and peeling only by handling a mask pattern formed using a photosensitive organic resin material called a photoresist. Therefore, the manufacturing cost inevitably increases as the number of photolithography processes increases.

次に、配線抵抗の問題点について述べる。まず、EL表示装置の駆動方法として、アナログ駆動を用いた場合について述べる。 Next, the problem of wiring resistance will be described. First, a case where analog driving is used as a driving method of the EL display device will be described.

図3は、飽和領域 (Vds > Vg − Vth) における駆動用TFTの特性を示すグラフである。ここで、Vdsはソース−ドレイン間電圧、Vgはゲート−ソース間電圧、Vthは閾値電圧である。301はId−Vg特性(又はId−Vg曲線)と呼ばれている。ここでIdはドレイン電流である。このグラフにより任意のゲート電圧に対して流れる電流量を知ることができる。 FIG. 3 is a graph showing the characteristics of the driving TFT in the saturation region (Vds> Vg−Vth). Here, Vds is a source-drain voltage, Vg is a gate-source voltage, and Vth is a threshold voltage. 301 is called an Id-Vg characteristic (or Id-Vg curve). Here, Id is a drain current. From this graph, the amount of current flowing for an arbitrary gate voltage can be known.

アナログ方式の駆動方法では、駆動用TFTにおいて、飽和領域を用い、そのゲート電圧を変化させることによってドレイン電流を変化させる。 In the analog driving method, a saturation region is used in a driving TFT, and the drain current is changed by changing the gate voltage.

スイッチング用TFTがオンとなり、画素内に、ソース信号線より入力されたアナログのビデオ信号は、駆動用TFTのゲート電極に印加される。こうして、駆動用TFTのゲート電圧が変化する。このとき、図3に示したId−Vg特性に従い、ゲート電圧に対してドレイン電流が1対1で決まる。こうして、駆動用TFTのゲート電極に入力されるアナログのビデオ信号の電圧に対応して、所定のドレイン電流がEL素子に流れ、その電流量に対応した発光量で前記EL素子が発光する。 The switching TFT is turned on, and an analog video signal input from the source signal line into the pixel is applied to the gate electrode of the driving TFT. Thus, the gate voltage of the driving TFT changes. At this time, in accordance with the Id-Vg characteristic shown in FIG. Thus, a predetermined drain current flows through the EL element corresponding to the voltage of the analog video signal input to the gate electrode of the driving TFT, and the EL element emits light with a light emission amount corresponding to the current amount.

以上のように、アナログのビデオ信号によってEL素子の発光量が制御され、その発光量の制御によって階調表示がなされる。 As described above, the light emission amount of the EL element is controlled by the analog video signal, and gradation display is performed by controlling the light emission amount.

ここで、各画素の駆動用TFTのゲート電圧は、たとえソース信号線から同じ信号が入力されても、駆動用TFTのソース領域の電位が変化すると変化してしまう。ここで、駆動用TFTのソース領域の電位は、電源供給線から与えられている。しかし、電源供給線の電位は、配線抵抗による電位降下のために、画素部内部の位置によって変化する。 Here, even if the same signal is input from the source signal line, the gate voltage of the driving TFT of each pixel changes when the potential of the source region of the driving TFT changes. Here, the potential of the source region of the driving TFT is supplied from a power supply line. However, the potential of the power supply line changes depending on the position inside the pixel portion due to the potential drop due to the wiring resistance.

また、電源供給線の配線抵抗が小さな場合や、表示装置が、比較的小さな場合、また、電源供給線に流れる電流が比較的小さな場合は、それほど問題とならないが、そうでない場合、特に表示装置が比較的大きな場合は、この配線抵抗による電源供給線の電位の変化が大きくなる。 Further, when the wiring resistance of the power supply line is small, the display device is relatively small, or the current flowing through the power supply line is relatively small, it does not matter so much. Is relatively large, the change in the potential of the power supply line due to the wiring resistance becomes large.

特に、表示装置が大きくなるほど、外部入力端子から画素部の各電源供給線までの距離のばらつきが大きくなるため、電源供給線引き回し部の配線の長さのばらつきが大きくなる。そのため、電源供給線引き回し部の電位降下による電源供給線の電位の変化が大きくなる。 In particular, the larger the display device, the greater the variation in the distance from the external input terminal to each power supply line in the pixel portion, and the greater the variation in the wiring length of the power supply line routing portion. For this reason, the change in the potential of the power supply line due to the potential drop in the power supply line routing portion becomes large.

これらの要因による電源供給線の電位ばらつきは、各画素のEL素子の発光輝度に影響を与え、表示輝度を変化させるため表示ムラの原因となる。 Variation in the potential of the power supply line due to these factors affects the light emission luminance of the EL element of each pixel and causes display unevenness because the display luminance is changed.

以下に、電源供給線の電位のばらつきの具体的な例を示す。 Hereinafter, specific examples of variations in the potential of the power supply line are shown.

図4に示すように、表示画面中に白または黒のボックスを表示させたときには、クロストークと呼ばれる現象が発生していた。これはボックスの上方または下方にボックスの横方向と輝度の違いが発生する現象である。 As shown in FIG. 4, when a white or black box is displayed on the display screen, a phenomenon called crosstalk has occurred. This is a phenomenon in which a difference in luminance between the lateral direction of the box and the luminance occurs above or below the box.

クロストークは、ボックスの上方、下方と、横方向それぞれの画素において、駆動用TFT104に流れる電流に、差分を生じることから起こるものである。この差分の原因は、電源供給線V1、V2がソース信号線S1、S2に平行に配置されているために起こる。

Crosstalk occurs because a difference occurs in the current flowing through the driving

例えば図4のように、表示画面の一部に白いボックスを表示した場合、このボックス表示をする画素に対応する電源供給線において、ボックス表示画素の駆動用TFTのソースとドレインの間を介してEL素子に電流が流れる分、この電源供給線の配線抵抗による電位降下は、ボックスを表示しない画素のみにしか電源を供給しない電源供給線と比べて、大きくなる。そのため、ボックスの上下で、ボックス表示をしない他の画素より暗い部分が発生する。

ここで、表示装置の表示画面のサイズが小さい場合には、それでも、問題は発生しなかったが、表示装置の表示画面のサイズが大きくなると、表示画面の面積に比例して、EL素子に流れる電流の総和が増加する。

For example, as shown in FIG. 4, when a white box is displayed on a part of the display screen, the power supply line corresponding to the pixel displaying the box is interposed between the source and drain of the driving TFT of the box display pixel. Since the current flows through the EL element, the potential drop due to the wiring resistance of the power supply line is larger than that of the power supply line that supplies power only to the pixels that do not display the box. For this reason, darker portions occur at the top and bottom of the box than other pixels that do not display the box.

Here, when the size of the display screen of the display device is small, no problem has occurred. However, when the size of the display screen of the display device increases, the display device flows in proportion to the area of the display screen. The total current increases.

例えば、対角4インチの表示画面を有する表示装置と、対角20インチの表示画面を有する表示装置におけるEL素子に流れる電流の総和を比較すると、後者の表示画面の面積は前者の25倍であるので、EL素子に流れる電流の総和も、およそ25倍となる。 For example, when the total sum of currents flowing through EL elements in a display device having a 4-inch diagonal display screen and a display device having a 20-inch diagonal display screen is compared, the area of the latter display screen is 25 times that of the former. Therefore, the sum total of the currents flowing through the EL elements is about 25 times.

そのため、表示画面のサイズが大きい表示装置では、前述の電位降下の問題が大きな課題となる。 Therefore, in the display device having a large display screen size, the above-described problem of potential drop becomes a big problem.

例えば、20インチの表示装置において、配線長は700mm、配線幅10mm、シート抵抗0.1オームとしても、電流が1A程度流れると電位降下は10Vになってしまい、正常な表示が不可能となる。 For example, in a 20-inch display device, even if the wiring length is 700 mm, the wiring width is 10 mm, and the sheet resistance is 0.1 ohm, if the current flows about 1 A, the potential drop becomes 10 V, and normal display becomes impossible. .

次に、EL表示装置の駆動方法として、デジタル駆動で定電圧駆動を用いた場合の配線抵抗の問題点について述べる。 Next, the problem of the wiring resistance when the constant voltage drive is used in the digital drive as the drive method of the EL display device will be described.

定電圧駆動を用いると、EL素子106に供給される電圧が各画素で一定となるため、各画素の輝度は駆動用TFT104の特性ばらつきの影響を受けず、非常に高い画質の表示能力を備えるEL表示装置を得ることが出来る。しかしながら、配線抵抗が大きいと、EL素子106に供給される電圧が各画素で一定であるという定電圧駆動を行うための必要な条件を満たすことが出来なくなる。このことについて、図5(A)、(B)を用いて説明する。

When constant voltage driving is used, the voltage supplied to the

図5の(A)は、全画素数に対し3分の1の画素が同時に点灯しているときを表している。図5の(B)は、全画素数に対し3分の2の画素が同時に点灯しているときを表している。 FIG. 5A shows the case where one third of the pixels are lit simultaneously with respect to the total number of pixels. FIG. 5B shows the case where two-thirds of the pixels are lit simultaneously.

図5の(A)と図5の(B)とでは、同時に点灯している画素数が違うので、点灯時に画素部の電源供給線(V1〜Vx)に流れる電流値は、図5の(A)のときと図5の(B)のときで異なる。ここで、画素部の電源供給線(V1〜Vx)に配線抵抗が存在すると、電流値の大きさにしたがって、電圧が降下する。つまり、電流値の異なる図5の(A)と図5の(B)とでは、1画素あたりに供給される電圧が異なっている。供給される電圧が異なっているということは、EL素子の輝度が図5の(A)のように表示するときと、図5の(B)のように表示するときとで異なってしまうということである。 5A and FIG. 5B are different in the number of pixels that are lit at the same time, the value of the current flowing through the power supply lines (V1 to Vx) of the pixel portion during lighting is shown in FIG. It differs between A) and FIG. 5B. Here, when wiring resistance exists in the power supply lines (V1 to Vx) of the pixel portion, the voltage drops according to the magnitude of the current value. That is, the voltage supplied per pixel differs between FIG. 5A and FIG. 5B with different current values. The fact that the supplied voltage is different means that the luminance of the EL element is different between when the display is as shown in FIG. 5A and when the display is as shown in FIG. It is.

このように表示画像の点灯率によって1画素あたりの輝度が変化することは、時間階調によって階調を表示するときに、悪影響を及ぼす。たとえば、図5の(A)と図5の(B)を連続的に同じ時間表示して3つの階調を表示するときを考える。このとき、表示領域503では階調0、表示領域504では階調2、表示領域505では階調1、が表示されるはずである。しかし、配線抵抗が存在すると、図5の(A)と図5の(B)では1画素あたりの輝度が図5の(A)のほうが大きいので、領域505に表示される階調は1よりも小さくなる。このように、配線抵抗が存在すると、デジタル駆動で定電圧駆動用いた場合に、意図した階調が得られない。

Thus, the change in luminance per pixel depending on the lighting rate of the display image has an adverse effect when the gradation is displayed by the time gradation. For example, consider the case where three gradations are displayed by continuously displaying (A) in FIG. 5 and (B) in FIG. 5 for the same time. At this time,

この輝度の差は、電源供給線(V1〜Vx)の配線抵抗が大きいほど大きくなる。そして、表示装置が大型になるほど電源供給線が長くなるので、配線抵抗は大きくなる。すなわち、大型で解像度の高いEL表示装置を得るための問題点の一つは、配線抵抗の増大である。本発明における目的を達成するためには、配線抵抗を出来るだけ小さくしなければならない。 The difference in luminance increases as the wiring resistance of the power supply lines (V1 to Vx) increases. And since a power supply line becomes long, so that a display apparatus becomes large, wiring resistance becomes large. That is, one of the problems for obtaining a large and high resolution EL display device is an increase in wiring resistance. In order to achieve the object of the present invention, the wiring resistance must be made as small as possible.

本発明は、上記問題点を鑑みてなされたものであり、鮮明な多階調カラー表示の可能なアクティブマトリクス型のEL表示装置を提供することを課題とする。そして、そのようなアクティブマトリクス型EL表示装置を用いた高性能な電子機器(電子デバイス)を提供することを課題とする。 The present invention has been made in view of the above problems, and an object of the present invention is to provide an active matrix EL display device capable of clear multi-tone color display. It is another object of the present invention to provide a high-performance electronic device (electronic device) using such an active matrix EL display device.

本発明の目的は、歩留まりよく、かつ低コストで作製できる、大型で解像度の高いEL表示装置を提供することである。そのための手段として、以下に、本発明の構成について記載する。 An object of the present invention is to provide a large-sized and high-resolution EL display device that can be manufactured with high yield and low cost. As means for that purpose, the configuration of the present invention will be described below.

本発明の構成は、複数のソース信号線と、複数のゲート信号線と、行方向の複数の電源供給線と列方向の複数の電源供給線とマトリクス状の複数の画素を有し、複数の画素のそれぞれは、スイッチング用薄膜トランジスタと、駆動用薄膜トランジスタと、発光素子とを有し、複数の画素のそれぞれは、行方向の複数の電源供給線のうちの1つ及び列方向の複数の電源供給線のうちの1つに接続され、絶縁性を有する薄膜が、複数のソース信号線、複数のゲート信号線、行方向の複数の電源供給線、列方向の複数の電源供給線のうちの少なくとも1つの下の一部に形成されていることを特徴とする。 The configuration of the present invention includes a plurality of source signal lines, a plurality of gate signal lines, a plurality of power supply lines in the row direction, a plurality of power supply lines in the column direction, and a plurality of pixels in a matrix. Each of the pixels includes a switching thin film transistor, a driving thin film transistor, and a light emitting element, and each of the plurality of pixels includes one of a plurality of power supply lines in the row direction and a plurality of power supplies in the column direction. An insulating thin film connected to one of the lines includes at least one of a plurality of source signal lines, a plurality of gate signal lines, a plurality of power supply lines in the row direction, and a plurality of power supply lines in the column direction. It is characterized in that it is formed in one lower part.

また、上記発明において、スイッチング用薄膜トランジスタの電極又は駆動用薄膜トランジスタの電極は、液滴吐出法又は印刷法によって形成してもよい。また、複数のソース信号線、複数のゲート信号線、行方向の複数の電源供給線、列方向の複数の電源供給線のいずれか一は、液滴吐出法又は印刷法によって形成してもよく、スパッタリング法又はCVD法によって形成してもよい。ここでCVD法とは、プラズマCVD法(RFプラズマCVD法、マイクロ波CVD法、電子サイクロトロン共鳴CVD法、熱フィラメントCVD法等)、LPCVD法、熱CVD法を含むものとする。 In the above invention, the electrode of the switching thin film transistor or the electrode of the driving thin film transistor may be formed by a droplet discharge method or a printing method. Any one of the plurality of source signal lines, the plurality of gate signal lines, the plurality of power supply lines in the row direction, and the plurality of power supply lines in the column direction may be formed by a droplet discharge method or a printing method. Alternatively, it may be formed by sputtering or CVD. Here, the CVD method includes a plasma CVD method (RF plasma CVD method, microwave CVD method, electron cyclotron resonance CVD method, hot filament CVD method, etc.), LPCVD method, and thermal CVD method.

また、絶縁性を有する薄膜は、液滴吐出法又は印刷法によって形成しても良い。 In addition, the insulating thin film may be formed by a droplet discharge method or a printing method.

また、本発明の他の構成は、複数のソース信号線を形成し、複数のゲート信号線を形成し、マトリクス状の複数の画素を形成し、前記複数の画素のそれぞれはスイッチング用薄膜トランジスタと、駆動用トランジスタと、発光素子を有し、行方向の複数の電源供給線を形成し、列方向の複数の電源供給線を形成し、複数の画素のそれぞれは、液滴吐出法又は印刷法によって、行方向の複数の電源供給線のうちの1つ及び列方向の複数の電源供給線のうちの1つに接続することを特徴とする。 In another configuration of the present invention, a plurality of source signal lines are formed, a plurality of gate signal lines are formed, a plurality of pixels in a matrix are formed, and each of the plurality of pixels includes a switching thin film transistor, A plurality of power supply lines in the row direction are formed and a plurality of power supply lines in the column direction are formed, and each of the plurality of pixels is formed by a droplet discharge method or a printing method. And connecting to one of the plurality of power supply lines in the row direction and one of the plurality of power supply lines in the column direction.

また、上記発明において、絶縁性を有する薄膜を、液滴吐出法又は印刷法によって、ソース信号線、ゲート信号線、行方向の複数の電源供給線、列方向の複数の電源供給線のうちの少なくとも1つの下の一部に形成してもよい。また、複数のソース信号線、複数のゲート信号線、行方向の複数の電源供給線、前記列方向の複数の電源供給線のいずれか一を、液滴吐出法又は印刷法で形成してもよく、スパッタリング法又はCVD法によって形成してもよい。 In the above invention, the insulating thin film may be formed from a source signal line, a gate signal line, a plurality of power supply lines in the row direction, and a plurality of power supply lines in the column direction by a droplet discharge method or a printing method. You may form in at least one lower part. Further, any one of the plurality of source signal lines, the plurality of gate signal lines, the plurality of power supply lines in the row direction, and the plurality of power supply lines in the column direction may be formed by a droplet discharge method or a printing method. Alternatively, it may be formed by sputtering or CVD.

また、本発明の他の構成は、ソース信号線を形成し、ゲート信号線を形成し、電源供給線を形成し、スイッチング用薄膜トランジスタ、駆動用薄膜トランジスタ、発光素子を含む画素を形成し、絶縁性を有する薄膜を、ソース信号線、ゲート信号線、電源供給線のうちの少なくとも1つの下の一部に形成することを特徴とする。 In another structure of the present invention, a source signal line is formed, a gate signal line is formed, a power supply line is formed, a pixel including a switching thin film transistor, a driving thin film transistor, and a light emitting element is formed. The thin film having the structure is formed in a part below at least one of the source signal line, the gate signal line, and the power supply line.

また、上記発明において、絶縁性を有する薄膜は、液滴吐出法又は印刷法によって形成しても良い。また、ソース信号線、ゲート信号線、電源供給線のいずれか一は、液滴吐出法又は印刷法で形成しても良く、スパッタリング法又はCVD法で形成してもよい。 In the above invention, the insulating thin film may be formed by a droplet discharge method or a printing method. Further, any one of the source signal line, the gate signal line, and the power supply line may be formed by a droplet discharge method or a printing method, or may be formed by a sputtering method or a CVD method.

また、本発明は、上記発明に記載の表示装置を用いたパーソナルコンピュータ、テレビ受像器、カメラ、画像表示装置、ヘッドマウントディスプレイ、携帯情報端末である。 The present invention also relates to a personal computer, a television receiver, a camera, an image display device, a head mounted display, and a portable information terminal using the display device described in the above invention.

本発明によれば、歩留まりよく、かつ低コストで作製できる、大型で解像度の高いEL表示装置を提供することが出来る。また、信号書き込み時間を多くとれるので、正確な信号を画素へ入力することができ、きれいな画像を表示できる。また、配線抵抗の影響を小さくできるので、配線抵抗による画質不良を低減することができる。 According to the present invention, a large-sized and high-resolution EL display device that can be manufactured with high yield and low cost can be provided. In addition, since a long signal writing time can be taken, an accurate signal can be input to the pixel, and a clear image can be displayed. In addition, since the influence of the wiring resistance can be reduced, image quality defects due to the wiring resistance can be reduced.

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。 Embodiments of the present invention will be described in detail with reference to the drawings. However, the present invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details can be variously changed without departing from the spirit and scope of the present invention. Therefore, the present invention should not be construed as being limited to the description of the embodiments below. Note that in structures of the present invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description thereof is not repeated.

なお、本発明において、適用可能なトランジスタの種類に限定はなく、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI(Silicon On Insulator)基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類に限定はなく、単結晶基板、SOI基板、ガラス基板などに配置することが出来る。 Note that in the present invention, the type of applicable transistor is not limited, and a thin film transistor (TFT) using a non-single crystal semiconductor film typified by amorphous silicon or polycrystalline silicon, a semiconductor substrate, or an SOI (Silicon On Insulator). It is possible to apply a MOS transistor, a junction transistor, a bipolar transistor, a transistor using an organic semiconductor or a carbon nanotube, and other transistors formed using a substrate. There is no limitation on the kind of the substrate over which the transistor is provided, and the transistor can be provided over a single crystal substrate, an SOI substrate, a glass substrate, or the like.

(実施の形態1)

本発明の実施の形態について、図13、図14、図15、図16、図8及び図6を用いて説明する。まず、本発明においては低コストでEL表示装置を作製するのが克服すべき課題の一つである。低コスト化を実現するために、フォトリソグラフィ工程を削減してTFTを製造することが試みられている。

(Embodiment 1)

Embodiments of the present invention will be described with reference to FIGS. 13, 14, 15, 16, 8, and 6. FIG. First, in the present invention, manufacturing an EL display device at low cost is one of the problems to be overcome. In order to realize cost reduction, attempts have been made to manufacture TFTs by reducing the photolithography process.

フォトリソグラフィ工程を削減する方法として、配線層若しくは電極を形成する導電層や、所定のパターンを形成するためのマスク層など表示パネルを作製するために必要なパターンのうち、少なくとも一つ若しくはそれ以上を、選択的にパターンを形成可能な方法により形成して、表示装置を作製する方法を考案した。選択的にパターンを形成可能な方法として、特定の目的に調合された組成物の液滴を選択的に吐出して所定のパターンを形成することが可能な、液滴吐出法(その方式によっては、インクジェット法とも呼ばれる)を考案した。また、パターンが転写、または描写できる方法、例えば印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)なども用いることで、低コスト化を実現できる。すなわち、低コストでEL表示装置を得るための問題点の一つは、フォトリソグラフィ工程回数の多さである。本発明における目的を達成するためには、フォトリソグラフィ工程回数を出来るだけ少なくしなければならない。その方法として、選択的にパターン形成が可能な方法が有効である。 As a method for reducing the photolithography process, at least one or more of patterns necessary for manufacturing a display panel such as a conductive layer for forming a wiring layer or an electrode or a mask layer for forming a predetermined pattern is used. Has been devised by a method capable of selectively forming a pattern to devise a method for manufacturing a display device. As a method capable of selectively forming a pattern, a droplet discharge method (depending on the method) can form a predetermined pattern by selectively discharging droplets of a composition prepared for a specific purpose. , Also called the inkjet method). In addition, the cost can be reduced by using a method capable of transferring or drawing a pattern, for example, a printing method (a method for forming a pattern such as screen printing or offset printing). That is, one of the problems for obtaining an EL display device at low cost is the large number of photolithography processes. In order to achieve the object of the present invention, the number of photolithography processes must be reduced as much as possible. As the method, a method capable of selectively forming a pattern is effective.

したがって、本実施の形態では、以下に説明する、選択的にパターン形成が可能なEL表示装置の作製方法の一つである、液滴吐出法によってEL表示装置を作製するものとする。ただし、これは一例であって、本実施の形態はこの方法のみに限定されるものではない。 Therefore, in this embodiment mode, an EL display device is manufactured by a droplet discharge method, which is one of the manufacturing methods of an EL display device which can be selectively formed as described below. However, this is only an example, and the present embodiment is not limited to this method.

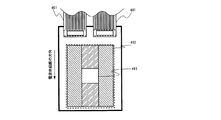

まず、ゲート電極とソース又はドレイン配線の作製に密着性を向上する手段を適用した、チャネル保護型の薄膜トランジスタを有する表示装置の作製方法について、図13、図14を用いて説明する。 First, a method for manufacturing a display device having a channel protective thin film transistor, in which a means for improving adhesion is applied to manufacturing a gate electrode and a source or drain wiring, is described with reference to FIGS.

基板800の上に、下地前処理として密着性を向上させる下地膜801を形成する。基板800は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等からなるガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板又は本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いる。また、基板800の表面が平坦化されるようにCMP(Chemical Mechanical Polishing)法などによって、研磨しても良い。なお、基板800上に、絶縁層を形成してもよい。絶縁層は、CVD法、プラズマCVD法、スパッタリング法、スピンコート法等の公知の方法により、珪素を含む酸化物材料、窒化物材料を用いて、単層又は積層して形成される。この絶縁層は、形成しなくても良いが、基板800からの汚染物質などを遮断する効果がある。ガラス基板よりの汚染を防ぐための下地層を形成する場合は、その上に液滴吐出法によって形成する導電層802、803の前処理として下地膜801を形成する。

Over the

パターンの形成に用いる液滴吐出装置の一態様は図15に示されている。液滴吐出手段903の個々のヘッド905は制御手段907に接続され、それがコンピュータ910で制御することにより予めプログラミングされたパターンを描画することができる。描画するタイミングは、例えば、基板900上に形成されたマーカー911を基準に行えば良い。或いは、基板900の縁を基準にして基準点を確定させても良い。これをCCDなどの撮像手段904で検出し、画像処理手段909にてデジタル信号に変換したものをコンピュータ910で認識して制御信号を発生させて制御手段907に送る。勿論、基板900上に形成されるべきパターンの情報は記憶媒体908に格納されたものであり、この情報を基にして制御手段907に制御信号を送り、液滴吐出手段903の個々のヘッド905を個別に制御することができる。一つのヘッドで、導電材料や有機、無機材料などをそれぞれ吐出し、描画することができ、層間膜のような広領域に描画する場合は、スループットを向上させるため複数のノズルより同材料を同時に吐出し、描画することができる。大型基板を用いる場合、ヘッド905は基板上を、自在に走査し、描画する領域を自由に設定することができ、同じパターンを一枚の基板に複数描画することができる。

One mode of a droplet discharge device used for forming a pattern is shown in FIG. The individual heads 905 of the droplet discharge means 903 are connected to the control means 907, which can draw a pre-programmed pattern under the control of the

本実施の形態では、密着性を向上させる機能を有する下地膜として、光触媒の機能を有する物質を用いる。光触媒物質は、ゾルゲル法のディップコーティング法、スピンコーティング法、液滴吐出法、イオンプレーティング法、イオンビーム法、CVD法、スパッタリング法、RFマグネトロンスパッタリング法、プラズマ溶射法、プラズマスプレー法、又は陽極酸化法により形成することができる。また物質は、その形成方法により膜としての連続性を有さなくても良い。複数の金属を含む酸化物半導体からなる光触媒物質の場合、構成元素の塩を混合、融解して形成することができる。ディップコーティング法、スピンコーティング法等の塗布法により光触媒物質を形成する場合、溶媒を除去する必要があるとき、焼成したり、乾燥すればよい。具体的には、所定の温度(例えば、300℃以上)で加熱すればよく、好ましくは酸素を有する雰囲気で行う。例えば、導電ペーストとしてAgを用い、酸素及び窒素を有する雰囲気で焼成を行うと、熱硬化性樹脂などの有機物が分解されるため、有機物を含まないAgを得ることができる。その結果、Ag表面の平坦性を高めることができる。 In this embodiment mode, a substance having a photocatalytic function is used as the base film having a function of improving adhesion. The photocatalytic substance is a sol-gel dip coating method, spin coating method, droplet discharge method, ion plating method, ion beam method, CVD method, sputtering method, RF magnetron sputtering method, plasma spraying method, plasma spraying method, or anode. It can be formed by an oxidation method. The substance may not have continuity as a film depending on the formation method. In the case of a photocatalytic substance made of an oxide semiconductor containing a plurality of metals, it can be formed by mixing and melting constituent element salts. When the photocatalytic substance is formed by a coating method such as a dip coating method or a spin coating method, it may be fired or dried when it is necessary to remove the solvent. Specifically, heating may be performed at a predetermined temperature (for example, 300 ° C. or higher), and preferably performed in an atmosphere containing oxygen. For example, when Ag is used as the conductive paste and baking is performed in an atmosphere containing oxygen and nitrogen, an organic substance such as a thermosetting resin is decomposed, so that Ag containing no organic substance can be obtained. As a result, the flatness of the Ag surface can be improved.

この加熱処理により、光触媒物質は所定の結晶構造を有することができる。例えば、アナターゼ型やルチル−アナターゼ混合型を有する。低温相ではアナターゼ型が優先的に形成される。そのため光触媒物質が所定の結晶構造を有していない場合も加熱すればよい。また塗布法により形成する場合、所定の膜厚を得るために複数回にわたって光触媒物質を形成することもできる。 By this heat treatment, the photocatalytic substance can have a predetermined crystal structure. For example, it has an anatase type and a rutile-anatase mixed type. In the low temperature phase, the anatase type is preferentially formed. Therefore, heating may be performed even when the photocatalytic substance does not have a predetermined crystal structure. Moreover, when forming by the apply | coating method, in order to obtain a predetermined film thickness, a photocatalyst substance can also be formed in multiple times.

本実施の形態では、光触媒物質としてスパッタリング法により所定の結晶構造を有するTiOx(代表としてはTiO2)結晶を形成する場合を説明する。ターゲットには金属チタンチューブを用い、アルゴンガスと酸素を用いてスパッタリングを行う。更にHeガスを導入してもよい。光触媒活性の高いTiOxを形成するためには、酸素を多く含む雰囲気とし、形成圧力を高めにする。更に成膜室又は処理物が設けられた基板を加熱しながらTiOxを形成すると好ましい。 In this embodiment, a case where a TiO x (typically TiO 2 ) crystal having a predetermined crystal structure is formed as a photocatalytic substance by a sputtering method will be described. A metal titanium tube is used as a target, and sputtering is performed using argon gas and oxygen. Further, He gas may be introduced. In order to form TiO x having high photocatalytic activity, the atmosphere is rich in oxygen and the formation pressure is increased. Further, it is preferable to form TiO x while heating the substrate provided with the film forming chamber or the processed material.

このように形成されるTiOXは非常に薄膜(1nm〜1μm程度)であっても光触媒機能を有する。 TiOX formed in this way has a photocatalytic function even if it is a very thin film (about 1 nm to 1 μm).

また他の下地前処理として、スパッタリング法や蒸着法などの方法により、Ti(チタン)、W(タングステン)、Cr(クロム)、Ta(タンタル)、Ni(ニッケル)、Mo(モリブデン)などの金属材料若しくはその酸化物で形成される下地膜801を形成することが好ましい。

In addition, as other base pretreatments, metals such as Ti (titanium), W (tungsten), Cr (chromium), Ta (tantalum), Ni (nickel), and Mo (molybdenum) are obtained by sputtering or vapor deposition. It is preferable to form a

下地膜801は0.01〜10nmの厚さで形成すれば良いが、極薄く形成すれば良いので、必ずしも層構造を持っていなくても良い。下地膜として、高融点金属材料を用いる場合、ゲート電極層となる導電層802、803を形成した後、表面に露出している下地膜を下記の2つの工程のうちどちらかの工程を行って処理することが望ましい。

The

第1の方法としては、導電層802、803と重ならない下地膜801を絶縁化して、絶縁層を形成する工程である。つまり、導電層802、803と重ならない下地膜801を酸化して絶縁化する。このように、下地膜801を酸化して絶縁化する場合には、当該下地膜801を0.01〜10nmの厚さで形成しておくことが好適であり、そうすると容易に酸化させることができる。なお、酸化する方法としては、酸素雰囲気下に晒す方法を用いてもよいし、熱処理を行う方法を用いてもよい。

The first method is a step of insulating the

第2の方法としては、導電層802、803をマスクとして、下地膜801をエッチングして除去する工程である。この工程を用いる場合には下地膜801の厚さに制約はない。

The second method is a step of removing the

また、下地前処理の他の方法として、形成領域(被形成面)に対してプラズマ処理を行う方法がある。プラズマ処理の条件は、空気、酸素又は窒素を処理ガスとして用い、圧力を数十Torr〜1000Torr(133000Pa)、好ましくは100(13300Pa)〜1000Torr(133000Pa)、より好ましくは700Torr(93100Pa)〜800Torr(106400Pa)、つまり大気圧又は大気圧近傍の圧力となる状態で、パルス電圧を印加する。このとき、プラズマ密度は、1×1010〜1×1014m−3、所謂コロナ放電やグロー放電の状態となるようにする。空気、酸素又は窒素の処理ガスを用いプラズマ処理を用いることにより、材質依存性なく、表面改質を行うことができる。その結果、あらゆる材料に対して表面改質を行うことができる。 Further, as another method for the base pretreatment, there is a method for performing plasma treatment on a formation region (formation surface). The plasma treatment is performed using air, oxygen, or nitrogen as a treatment gas, and the pressure is several tens of Torr to 1000 Torr (133000 Pa), preferably 100 (13300 Pa) to 1000 Torr (133000 Pa), more preferably 700 Torr (93100 Pa) to 800 Torr ( 106400 Pa), that is, a pulse voltage is applied in a state where the pressure becomes atmospheric pressure or a pressure near atmospheric pressure. At this time, the plasma density is set to 1 × 10 10 to 1 × 10 14 m −3 , so-called corona discharge or glow discharge. By using plasma treatment using a treatment gas of air, oxygen, or nitrogen, surface modification can be performed without material dependency. As a result, surface modification can be performed on any material.

また、他の方法として、液滴吐出法によるパターンのその形成領域との密着性を上げるために、接着材として機能するような有機材料系の物質を形成してもよい。有機材料(有機樹脂材料)(ポリイミド、アクリル)やシロキサンを用いても良い。なお、シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。 As another method, an organic material substance that functions as an adhesive may be formed in order to improve the adhesion of the pattern formed by the droplet discharge method to the formation region. An organic material (organic resin material) (polyimide, acrylic) or siloxane may be used. Note that siloxane has a skeleton structure formed of a bond of silicon (Si) and oxygen (O). As a substituent, an organic group containing at least hydrogen (for example, an alkyl group or an aromatic hydrocarbon) is used. A fluoro group may be used as a substituent. Alternatively, an organic group containing at least hydrogen and a fluoro group may be used as a substituent.

次に、導電性材料を含む組成物を吐出して、後にゲート電極として機能する導電層802、803を形成する。

Next, a composition containing a conductive material is discharged to form

液滴吐出手段とは、組成物の吐出口を有するノズルや、1つ又は複数のノズルを具備したヘッド等の液滴を吐出する手段を有するものの総称とする。液滴吐出手段が具備するノズルの径は、0.02〜100μm(好適には30μm以下)に設定し、該ノズルから吐出される組成物の吐出量は0.001pl〜100pl(好適には10pl以下)に設定する。吐出量は、ノズルの径の大きさに比例して増加する。また、被処理物とノズルの吐出口との距離は、所望の箇所に滴下するために、出来る限り近づけておくことが好ましく、好適には0.1〜3mm(好適には1mm以下)程度に設定する。 The droplet discharge means is a general term for a device having means for discharging droplets such as a nozzle having a composition discharge port and a head having one or a plurality of nozzles. The diameter of the nozzle provided in the droplet discharge means is set to 0.02 to 100 μm (preferably 30 μm or less), and the discharge amount of the composition discharged from the nozzle is 0.001 pl to 100 pl (preferably 10 pl). Set to: The discharge amount increases in proportion to the size of the nozzle diameter. In addition, the distance between the object to be processed and the nozzle outlet is preferably as close as possible in order to drop it at a desired location, preferably about 0.1 to 3 mm (preferably about 1 mm or less). Set.