JP4819325B2 - Integrated circuit device and operation method thereof - Google Patents

Integrated circuit device and operation method thereof Download PDFInfo

- Publication number

- JP4819325B2 JP4819325B2 JP2004161460A JP2004161460A JP4819325B2 JP 4819325 B2 JP4819325 B2 JP 4819325B2 JP 2004161460 A JP2004161460 A JP 2004161460A JP 2004161460 A JP2004161460 A JP 2004161460A JP 4819325 B2 JP4819325 B2 JP 4819325B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- switches

- write

- write data

- parallel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title description 15

- 239000000872 buffer Substances 0.000 claims description 133

- 230000004044 response Effects 0.000 claims description 51

- 230000006870 function Effects 0.000 claims description 8

- 230000004913 activation Effects 0.000 claims description 7

- 230000003111 delayed effect Effects 0.000 claims description 7

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 42

- 238000006243 chemical reaction Methods 0.000 description 12

- 230000000630 rising effect Effects 0.000 description 11

- 101001074449 Crotalus durissus terrificus Phospholipase A2 inhibitor CNF Proteins 0.000 description 6

- 230000008569 process Effects 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 238000003491 array Methods 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1018—Serial bit line access mode, e.g. using bit line address shift registers, bit line address counters, bit line burst counters

- G11C7/1027—Static column decode serial bit line access mode, i.e. using an enabled row address stroke pulse with its associated word line address and a sequence of enabled bit line addresses

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4093—Input/output [I/O] data interface arrangements, e.g. data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1078—Data input circuits, e.g. write amplifiers, data input buffers, data input registers, data input level conversion circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M9/00—Parallel/series conversion or vice versa

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/10—Aspects relating to interfaces of memory device to external buses

- G11C2207/107—Serial-parallel conversion of data or prefetch

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

Description

本発明は、集積回路装置及びその動作方法に係り、例えば、集積回路メモリ装置の書込みデータ経路及びその動作方法に関する。 The present invention relates to an integrated circuit device and an operation method thereof, for example, a write data path of an integrated circuit memory device and an operation method thereof.

集積回路メモリ装置は、多くの消費財及び商業上の応用に広く使われている。集積回路メモリ装置の集積度が高まることによって、集積回路メモリ装置内のメモリセルの数も増加する。その上、集積回路メモリ装置のプリフェッチスキームもさらに増加する。当業者に周知のように、プリフェッチは、集積回路メモリ装置において、どれだけのビットを同時に書込みまたは読出しできるかを意味する。プリフェッチスキームはまた、一度に外部ターミナルへ/から直列に出力または入力されるビット数を意味するバースト長で表される。多くの集積回路装置は、例えば4ビットバースト長の4ビットプリフェッチスキームを使用する。しかし、高いデータレートのために8ビットバースト長または8ビットプリフェッチスキームに増加することが要求される。将来は、さらに高いプリフェッチスキームやバースト長が使われる。 Integrated circuit memory devices are widely used in many consumer and commercial applications. As the degree of integration of an integrated circuit memory device increases, the number of memory cells in the integrated circuit memory device also increases. In addition, the prefetch scheme of integrated circuit memory devices is further increased. As is well known to those skilled in the art, prefetch means how many bits can be written or read simultaneously in an integrated circuit memory device. The prefetch scheme is also expressed in burst length, which means the number of bits output or input serially to / from an external terminal at a time. Many integrated circuit devices use a 4-bit prefetch scheme, for example, a 4-bit burst length. However, increasing to an 8-bit burst length or 8-bit prefetch scheme is required for high data rates. In the future, higher prefetch schemes and burst lengths will be used.

高いプリフェッチスキームに増加するほど、集積回路メモリ装置の書込みデータ経路はそのサイズ及び複雑性がさらに大きくなる。当業者に周知のように、書込みデータ経路は、外部ターミナルから多数のデータビットを直列に受信し、メモリセルアレイに多数のデータビットを並列に書き込むために提供される。これによりデータ書込み経路はチップ面積の相当部分を占める。 As the number of high prefetch schemes increases, the size and complexity of the write data path of an integrated circuit memory device increases. As is well known to those skilled in the art, a write data path is provided for receiving multiple data bits in series from an external terminal and writing multiple data bits to the memory cell array in parallel. As a result, the data write path occupies a considerable portion of the chip area.

図1は、典型的なDRAMのブロックダイアグラムである。図1のDRAMは、ファストサイクルDRAM(FCDRAM)とも称する。これを参照すれば、FCRAM100は、クロック信号を受信して内部クロック信号を発生させるクロックバッファ102、外部入力にしたがって命令を発生するコマンドデコーダ104、アドレスデータA0〜A14とバンク選択信号BA0、BA1にしたがってアドレス信号を発生するアドレスバッファ106、及び、リフレッシュカウンタ108を含む。制御信号発生部110は、コマンドデコーダ104から提供される信号にしたがって制御信号を発生する。モードレジスタMRS112は、適切なモード信号を発生する。上位アドレスラッチ114と下位アドレスラッチ116とは、ローデコーダとカラムデコーダとにそれぞれ提供されるアドレス信号を発生する。バーストカウンタ118は、読出し及び書込みデータのバースト長を制御するために使われる。書込みアドレスラッチ/比較部120は、以前の書込みアドレスと現在の書込みアドレスとを比較するために使われる。

FIG. 1 is a block diagram of a typical DRAM. The DRAM of FIG. 1 is also referred to as a fast cycle DRAM (FCDRAM). Referring to this, the FCRAM 100 receives a clock signal to generate an internal clock signal, a

メモリセルアレイとして、例えば4個のバンク122〜128が提供される。しかし、これより少数または多数のバンクが提供されてもよい。入出力データ経路200は、データ制御及びラッチ回路130、読出しデータバッファ132、書込みデータバッファ134、及び、入出力DQバッファ136を含む。DQバッファ136は、所定の入力をマスキングするデータマスク信号DMに応答する。図1に記載されたFCDRAMは、当業者に周知の技術であるので、これ以上の説明は省略する。

As the memory cell array, for example, four banks 122 to 128 are provided. However, fewer or more banks may be provided. The input /

図2は、図1のデータ入出力経路200のさらに具体的なブロックダイアグラムである。図2に示されたように、図1のモードレジスタ112がバースト長4を選択する時、各入出力ターミナルDQ0〜DQ15は、外部ターミナルから伝えられる4データビットを順次に受信する。この後、各入力データビットは、DQバッファ136内のデータ入力バッファ38によって直列−並列(S−P)変換部30に伝えられる。直列−並列S−P変換部30により直列から並列に変換された書込みデータバスDBW上の入力データは、バンクアドレスビットBA0、BA1により選択される適切な書込みデータ経路31、32、33、34に伝えられる。

FIG. 2 is a more specific block diagram of the data input /

図2において、データの読出しを説明すると、多数のバンクBANK0〜BANK3のうち何れか1つのバンクからデータが出力され、バンクアドレスビットBA0、BA1により選択される読出しデータ経路41、42、43、44を通じて読出しデータバスラインDBRに伝えられる。読出しデータバスラインDBR上の並列データは、並列−直列変換部40により直列データに変換される。この後、直列データは、データ出力バッファ48とデータ入出力ターミナルDQ0〜DQ15を通じて外部に出力される。したがって、データ入出力ターミナルDQ0〜DQ15を通じて、64(4×16)ビットの入力データが選択されたバンクのメモリセルアレイに同時に書き込まれ、64ビットのデートが同時に読出される。

Referring to FIG. 2, the reading of data will be described. Data is output from any one of a number of banks BANK0 to BANK3, and read

図3は、図1及び図2と連結する従来のFCDRAMにおいて、4ビットプリフェッチスキームを説明するブロックダイアグラムである。図3を参照すれば、バースト長4が図1のMRS 112により選択される時、入力バッファ38を通じてバッファされた第1入力データビットは、第1内部データストローブ信号PDSの立上がりエッジに応答して直列−並列変換部30の入力データラッチ301の第1ラッチ311に保存される。直列に受信された第2入力データビットは、第1内部データストローブ信号PDSの立下りエッジに応答して直列−並列変換部30の入力データラッチ301の第2ラッチ312に保存される。

FIG. 3 is a block diagram illustrating a 4-bit prefetch scheme in a conventional FCDRAM connected to FIGS. Referring to FIG. 3, when the

この時、第1ラッチ311に保存された第1入力データビットと第2ラッチ312に保存された第2入力データビットは、第2内部データストローブ信号PDSPに応答して並列変換部302の第1レジスタ313と第2レジスタ314とにそれぞれ伝えられる。第3入力データビットは、第1内部データストローブ信号PDSの次の立上がりエッジに応答して第1ラッチ311に保存され、第4入力データビットは、第1内部データストローブ信号PDSの次の立下りエッジに応答して第2ラッチ312に保存される。

At this time, the first input data bit stored in the

また、第3入力データビット及び第4入力データビットは、第1内部データストローブ信号PDSの立上がり及び立下りエッジに応答して、並列変換部302の第3レジスタ315と第4レジスタ316とにそれぞれ伝えられる。したがって、図3に示されたように、第1及び第3入力データビットのような奇数入力データDIN−Oは、連続的に第1及び第3レジスタ313、315に伝えられ、第2及び第4入力データビットのような偶数入力データDIN−Eは、第2及び第4レジスタ314、316に伝えられる。全ての入力デートD0、D1、D2、D3が並列変換部302に伝えられた後、全ての入力データは、第3内部データストローブ信号PDSENに応答して並列に並列データ出力回路303に伝えられて保存される。

The third input data bit and the fourth input data bit are respectively sent to the

図4は、入力DQパッド上の4つのデータビットD0〜D3の直列入力とデータラインDBW_0〜DBW_3上の4つのデータビットの並列出力とを含む前述した動作を説明するタイミングダイアグラムである。 FIG. 4 is a timing diagram illustrating the above-described operation including serial input of four data bits D0-D3 on the input DQ pad and parallel output of four data bits on data lines DBW_0-DBW_3.

また、図3を参照すれば、直列−並列変換部30に保存された入力データは、図2の書込みデータ経路31、32、33、34の部分を形成する書込みデータバッファ330、331、332、333に保存される。書込みデータバッファ330、331、332、333から、入力データは、並列ビットスイッチPSW、340〜343に印加される制御信号PS4に応答してカラム選択ラインCSL、350に伝えられる。4ビットの入力デートは、メモリセルブロック360に同時に書き込まれる。図3及び4では、4ビットデータがメモリセルブロックに同時に書き込まれるので、4ビットプリフェッチスキームを説明する。図3において、書込みデータバッファ330〜333と並列ビットスイッチPSW340〜343を連結させるラインをグロ−バルデータラインGDL_0〜GDL_3と呼ぶ。並列ビットスイッチPSWとカラム選択ラインCSLとを連結させるラインをローカルデータラインLDL_0〜LDL_3と呼ぶ。最後に、メモリセルアレイのビットラインは、図3でBL_0−BL_511と表示される。

Referring to FIG. 3, the input data stored in the serial-

図5は、8ビットプリフェッチスキームを含む従来のFCDRAMのブロックダイアグラムである。当業者に周知のように、8ビットプリフェッチスキームでは、FCDRAMがさらに高いデータレートで動作する。図5において、図3の参照符号と同一に使われた参照符号は、同様の構成要素を示す。8ビットプリフェッチスキームに適合するために、図3の構成要素は、図5においてその個数が2倍となる。したがって、レジスタの第2セット313’〜316’は並列変換部302に、そして、レジスタの第2セット317’〜320’が並列データ出力回路303に提供される。また、書込みデータバッファの第2セット334〜337と並列ビットスイッチ344〜347も提供される。

FIG. 5 is a block diagram of a conventional FCDRAM including an 8-bit prefetch scheme. As is well known to those skilled in the art, in an 8-bit prefetch scheme, the FCDRAM operates at a higher data rate. In FIG. 5, the same reference numerals as those in FIG. 3 indicate the same components. In order to conform to the 8-bit prefetch scheme, the number of components in FIG. 3 is doubled in FIG. Accordingly, the second set of

図5に示されたように、ローカルデータラインLDLとグロ−バルデータラインGDLとは、図3と比較して2倍である。言い換えれば、図5の8ビットプリフェッチスキームにおいて、グローバルデータラインGDLとローカルデータラインLDLとの数は、図3の4ビットプリフェッチスキームと比較して2倍に増加する。さらに具体的には、図5において、8個のグローバルデータラインGDL_0〜GDL_7は、それぞれの書込みデータバッファ330〜337をそれぞれの並列ビットスイッチ340〜347に連結させるために使われる。また、8個のローカルデータラインLDL_0〜LDL_7は、それぞれの並列ビットスイッチ340〜347をカラム選択ライン350に連結させるために使われる。これにより、多数のローカル及び/又はグローバルデータラインが集積回路メモリ装置の面積を過度に占める。

As shown in FIG. 5, the local data line LDL and the global data line GDL are doubled as compared with FIG. In other words, in the 8-bit prefetch scheme of FIG. 5, the number of global data lines GDL and local data lines LDL increases twice as compared with the 4-bit prefetch scheme of FIG. More specifically, in FIG. 5, eight global data lines GDL_0 to GDL_7 are used to connect the respective write data buffers 330 to 337 to the respective parallel bit switches 340 to 347. The eight local data lines LDL_0 to LDL_7 are used to connect the respective parallel bit switches 340 to 347 to the

他の高速メモリ装置における読出及び/又は書込みデータ経路は、特許文献1(Suzukiなどによる“半導体メモリ装置”)と特許文献2(Seigoなどによる“高速データ読出し及びデータ書込み動作のためにクロック信号に同期されて動作する半導体メモリ装置”)に、そして特許文献3(Ochumaなどによる“向上されたデータ書込み動作を有するファストサイクルRAM”)に記載されている。

本発明の目的は、nビットプリフェッチ構造を利用して2nビットプリフェッチスキームを具現するメモリ装置を提供するところにある。 An object of the present invention is to provide a memory device that implements a 2n-bit prefetch scheme using an n-bit prefetch structure.

本発明の他の目的は、バースト長の変化により自動プリチャージ時点を調節するメモリ装置を提供するところにある。 Another object of the present invention is to provide a memory device that adjusts an automatic precharge time according to a change in burst length.

本発明のさらに他の目的は、nビットプリフェッチ構造のメモリ装置を利用して2nビットプリフェッチスキームを具現する方法を提供するところにある。 It is still another object of the present invention to provide a method for implementing a 2n-bit prefetch scheme using a memory device having an n-bit prefetch structure.

本発明のさらに他の目的は、バースト長の変化による自動プリチャージ制御方法を提供するところにある。 Still another object of the present invention is to provide an automatic precharge control method by changing a burst length.

本発明の1つの側面の集積回路メモリ装置は、N個のデータビットを並列に書き込むメモリセルアレイと外部ターミナルから2N個のデータビットを直列に受信する書込みデータ経路とを含む。書込みデータ経路は、2N個のデータビットを保存する2N個の書込みデータバッファと、2N個のスイッチと、並列にN個のデータビットをメモリセルアレイに書き込むために2N個のスイッチのうち少なくともN個とメモリセルアレイを連結させるN個のデータラインとを含む。これによりローカルデータライン及びグロ−バルデータラインの数が減る。 An integrated circuit memory device according to one aspect of the present invention includes a memory cell array that writes N data bits in parallel and a write data path that receives 2N data bits in series from an external terminal. The write data path includes 2N write data buffers storing 2N data bits, 2N switches, and at least N of 2N switches for writing N data bits to the memory cell array in parallel. And N data lines connecting the memory cell arrays. This reduces the number of local data lines and global data lines.

本発明の実施形態において、書込みデータ経路は、外部ターミナルと連結される第1及び第2直列−並列変換部、N個の第1グロ−バルデータライン及びN個の第2グロ−バルデータラインを含む。本発明の実施形態において、第1直列−並列変換部は、第1内部データストローブ信号に応答し、第2直列−並列変換部は、第2内部データストローブ信号に応答する。他の実施形態において、第1及び第2直列−並列変換部は、同じ内部データストローブ信号に応答する。2N個の書込みデータバッファは、N個の第1書込みデータバッファとN個の第2書込みデータバッファで構成され、2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとで構成される。これら実施形態において、N個の第1書込みデータバッファは、第1直列−並列変換部に連結され、N個の第1グローバルデータラインのそれぞれは、N個の第1スイッチのそれぞれとN個の第1書込みデータバッファのそれぞれとの間に連結される。これら実施形態において、N個の第2書込みデータバッファは、第2直列−並列変換部に連結され、N個の第2グローバルデータラインのそれぞれは、N個の第2スイッチのそれぞれとN個の第2書込みデータバッファのそれぞれとの間に連結される。これらの実施形態において、N個のデータラインは、N個のローカルデータラインであり、N個のローカルデータラインのそれぞれは、N個の第1スイッチ及びN個の第2スイッチとメモリセルアレイとの間にそれぞれ連結される。 In an embodiment of the present invention, the write data path includes first and second serial-parallel converters connected to an external terminal, N first global data lines and N second global data lines. including. In an embodiment of the present invention, the first serial-parallel converter is responsive to the first internal data strobe signal, and the second serial-parallel converter is responsive to the second internal data strobe signal. In other embodiments, the first and second serial-to-parallel converters are responsive to the same internal data strobe signal. The 2N write data buffers are composed of N first write data buffers and N second write data buffers, and 2N switches include N first switches and N second switches. Composed. In these embodiments, the N first write data buffers are coupled to the first serial-parallel converter, and each of the N first global data lines includes each of the N first switches and the N number of first switches. Each of the first write data buffers is connected to each other. In these embodiments, the N second write data buffers are coupled to the second serial-parallel converter, and each of the N second global data lines includes each of the N second switches and the N number of the second switches. It is connected between each of the second write data buffers. In these embodiments, the N data lines are N local data lines, and each of the N local data lines includes N first switches and N second switches and a memory cell array. Each is connected in between.

これら実施形態において、書込みデータ経路は、第1及び第2直列−並列変換部のうち何れか1つとN個の第1書込みデータバッファ及びN個の第2書込みデータバッファのうち何れか1つとの間にそれぞれ連結される第1及び第2データオーダリング回路をさらに含む。さらに、これら実施形態において、N個の第1スイッチは第1制御信号に応答し、N個の第2スイッチは第1制御信号から遅延された第2制御信号に応答する。第1及び第2制御信号は、書込み活性化信号から異なる遅延時間をもって遅延されて生成されうる。 In these embodiments, the write data path is any one of the first and second serial-parallel converters and any one of the N first write data buffers and the N second write data buffers. First and second data ordering circuits connected between the first and second data ordering circuits, respectively. Further, in these embodiments, the N first switches are responsive to a first control signal, and the N second switches are responsive to a second control signal delayed from the first control signal. The first and second control signals may be generated with a different delay time from the write activation signal.

これら実施形態は、チップ選択命令及びファンクション命令に応答して書込み活性化信号を発生させる命令デコーダと、書込み活性化信号に応答して第1及び第2制御信号を発生させる制御信号発生部をさらに含む。命令デコーダは、チップ選択命令及び前記ファンクション命令に応答してアクティブ命令及び読出命令をさらに発生させ、命令デコーダは、チップ選択命令及びファンクション命令に応答して読出命令、リフレッシュ命令及びモードレジスタ命令をさらに発生させうる。 The embodiments further include a command decoder that generates a write activation signal in response to a chip selection command and a function command, and a control signal generator that generates first and second control signals in response to the write activation signal. Including. The instruction decoder further generates an active instruction and a read instruction in response to the chip selection instruction and the function instruction, and the instruction decoder further receives a read instruction, a refresh instruction, and a mode register instruction in response to the chip selection instruction and the function instruction. Can be generated.

これら実施形態は、N個の第3スイッチとN個の第4スイッチをさらに含む。N個の第3スイッチのそれぞれは、第1直列−並列変換部とN個の第1書込みデータバッファのそれぞれとの間に連結され、N個の第4スイッチは、第2直列−並列変換部とN個の第2書込みデータバッファのそれぞれとの間に連結される。実施形態において、N個の第3スイッチは第3制御信号に応答し、N個の第4スイッチは第3制御信号から遅延された第4制御信号に応答する。第3及び第4制御信号は、データストローブ信号のオフセット立下りエッジに応答して発生する。最後に、データストローブカウンタは、データストローブ信号に応答してデータストローブ信号の立下りエッジをカウントしてデータストローブ信号のオフセット立下りエッジから第3及び第4制御信号を発生しうる。 These embodiments further include N third switches and N fourth switches. Each of the N third switches is connected between the first serial-parallel converter and each of the N first write data buffers, and each of the N fourth switches includes a second serial-parallel converter. And each of the N second write data buffers. In an embodiment, the N third switches are responsive to a third control signal, and the N fourth switches are responsive to a fourth control signal delayed from the third control signal. The third and fourth control signals are generated in response to the offset falling edge of the data strobe signal. Finally, the data strobe counter may count the falling edge of the data strobe signal in response to the data strobe signal and generate the third and fourth control signals from the offset falling edge of the data strobe signal.

本発明の他の実施形態において、書込みデータ経路は、外部ターミナルと連結される直列−並列変換部とN個のグローバルデータラインとを含む。これらの実施形態において、2N個の書込みデータバッファは、N個の第1書込みデータバッファとN個の第2データバッファとで構成され、2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとで構成される。N個の第1書込みデータバッファは、第1直列−並列変換部に連結され、N個の第1書込みデータバッファのそれぞれは、N個の第1スイッチに連結される。N個の第2書込みデータバッファのそれぞれは、N個の第1スイッチそれぞれと連結され、N個のグロ−バルデータラインのそれぞれは、N個の第2スイッチのそれぞれとN個の第2書込みデータバッファのそれぞれとの間に連結される。最後に、N個のローカルデータラインのそれぞれは、N個の第2スイッチとメモリセルアレイとの間にそれぞれ連結される。 In another embodiment of the present invention, the write data path includes a serial-parallel converter connected to an external terminal and N global data lines. In these embodiments, the 2N write data buffers are composed of N first write data buffers and N second data buffers, and the 2N switches include N first switches and N second data buffers. The second switch. The N first write data buffers are connected to the first serial-parallel converter, and each of the N first write data buffers is connected to the N first switches. Each of the N second write data buffers is connected to each of the N first switches, and each of the N global data lines is connected to each of the N second switches and the N second write. It is connected between each of the data buffers. Finally, each of the N local data lines is connected between the N second switches and the memory cell array.

これらの他の実施形態において、書込みデータ経路は、直列−並列変換部とN個の第1書込みデータバッファとの間に連結されるデータオーダリング回路をさらに含む。また、これらの実施形態は、直列−並列変換部とN個の第1書込みデータバッファのそれぞれとの間に連結されるN個の第3スイッチをさらに含む。さらに、N個の第3スイッチは、第1制御信号に応答し、N個の第1スイッチは、前記第1制御信号から遅延された第2制御信号に応答する。第1及び第2制御信号は、データストローブ信号のオフセット立下りエッジに応答して発生されうる。 In these other embodiments, the write data path further includes a data ordering circuit coupled between the serial-parallel converter and the N first write data buffers. In addition, these embodiments further include N third switches connected between the serial-parallel converter and each of the N first write data buffers. Further, the N third switches are responsive to a first control signal, and the N first switches are responsive to a second control signal delayed from the first control signal. The first and second control signals may be generated in response to the offset falling edge of the data strobe signal.

本発明のさらに他の実施形態は、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間にメモリセルアレイのワードラインをイネーブルさせるプリチャージ制御回路を含む。これら実施形態において、プリチャージ制御回路は、集積回路装置の第1プリチャージモードの間、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間の間、メモリセルアレイのワードラインをイネーブルさせる。プリチャージ制御回路は、集積回路装置の第2プリチャージモードの間、1グループのN並列ビットであるN個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。モードレジスタは、第1または第2プリチャージモードを選択するように設定され、プリチャージ制御回路はモードレジスタに応答する。 Yet another embodiment of the present invention includes a precharge control circuit that enables a word line of a memory cell array at a time sufficient to store 2N data bits, which are two groups of N parallel bits, in the memory cell array. In these embodiments, the precharge control circuit has a sufficient time to store 2N data bits, which are two groups of N parallel bits, in the memory cell array during the first precharge mode of the integrated circuit device. Enable the word line of the memory cell array. The precharge control circuit sets the word line of the memory cell array for a time sufficient to write N data bits, which are a group of N parallel bits, to the memory cell array during the second precharge mode of the integrated circuit device. Activate. The mode register is set to select the first or second precharge mode, and the precharge control circuit responds to the mode register.

これらの実施形態において、プリチャージ制御回路は、第1及び第2遅延部で構成される。第1遅延部は、第1プリチャージモードに応答し、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。第2遅延部は、第2プリチャージモードに応答し、第1グループのN並列ビットのN個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。 In these embodiments, the precharge control circuit includes first and second delay units. The first delay unit activates the word line of the memory cell array in response to the first precharge mode for a time sufficient to store 2N data bits, which are two groups of N parallel bits, in the memory cell array. Let The second delay unit is responsive to the second precharge mode and activates the word line of the memory cell array for a time sufficient to write N data bits of the N parallel bits of the first group to the memory cell array. .

本発明の他の実施形態によれば、書込みデータバッファの少なくとも1つは、書込みアドレスをラッチするアドレスラッチと、アドレスラッチにラッチされた書込みアドレスと現在のアドレスとを比較するアドレス比較部と、書込みアドレスに対応する書込みデータをラッチするデータラッチを含む。これらの実施形態において、現在のアドレスが読出しアドレスであり、アドレス比較部が、読出しアドレスとアドレスラッチにラッチされた書込みアドレスとが一致していると判断する場合、メモリセルアレイではなくデータラッチから外部ターミナルに読出しデータを出力する。他の実施形態において、集積回路メモリ装置は、現在のアドレスが読出しアドレスであり、アドレス比較部が、読出しアドレスとアドレスラッチにラッチされた書込みアドレスとが一致していないと判断する場合、メモリセルアレイから外部ターミナルに読出しデータを出力する。 According to another embodiment of the present invention, at least one of the write data buffers includes an address latch that latches a write address, an address comparison unit that compares the write address latched in the address latch with a current address, A data latch for latching write data corresponding to the write address is included. In these embodiments, when the current address is a read address and the address comparison unit determines that the read address and the write address latched in the address latch match, the external address is not from the memory cell array but from the data latch. Outputs read data to the terminal. In another embodiment, the integrated circuit memory device provides a memory cell array when the current address is a read address and the address comparator determines that the read address and the write address latched in the address latch do not match. Read data to the external terminal.

したがって、本発明の多様な実施例による集積回路メモリ装置は多数のデータビットを並列に書き込むメモリセルアレイを含む。書込みデータ経路は外部ターミナルから多数のデータビットを2回直列に受信し、データビットの最初の半分を並列にメモリセルアレイに書込み、データビットの最後の2番目の半分を並列にメモリセルアレイに書き込む。 Accordingly, an integrated circuit memory device according to various embodiments of the present invention includes a memory cell array that writes a number of data bits in parallel. The write data path receives a number of data bits from the external terminal twice in series, writes the first half of the data bits to the memory cell array in parallel, and writes the last second half of the data bits to the memory cell array in parallel.

本発明の実施形態による多数のデータビットを並列に保存するメモリセルアレイを持つ集積回路装置は、外部ターミナルから複数のデータビットを直列に2回にわたって受信しながら動作する。受信されたデータビットは、複数の書込みデータバッファに保存される。複数のデータビットの最初の半分(第1の半分)が書込みデータバッファからメモリセルアレイに並列に書き込まれる。その後、複数のデータビットの残りの半分(第2の半分)が書込みデータバッファからメモリセルアレイに並列に書き込まれる。 An integrated circuit device having a memory cell array for storing a large number of data bits in parallel according to an embodiment of the present invention operates while receiving a plurality of data bits from an external terminal twice in series. The received data bits are stored in a plurality of write data buffers. The first half (first half) of the plurality of data bits is written in parallel from the write data buffer to the memory cell array. Thereafter, the remaining half (second half) of the plurality of data bits is written in parallel from the write data buffer to the memory cell array.

これら実施形態では、2回にわたるデータビットの受信において、複数のデータビットの最初の半分(第1の半分)を直列に受信してから前記複数のデータビットの残りの半分(第2の半分)を直列に受信する。複数のデータビットの最初の半分(第1の半分)が書込みデータバッファの第1セットに保存されてから、前記複数のデータビットの残りの半分(第2の半分)が書込みデータバッファの第2セットに保存される。最後に、第1及び第2セットの書込みデータバッファのそれぞれから前記複数のデータビットの最初の半分(第1の半分)及び残りの半分(第2の半分)が共通にローカルデータラインを通じてメモリセルアレイに書き込まれる。 In these embodiments, in receiving data bits twice, the first half (first half) of the plurality of data bits is received in series and then the remaining half (second half) of the plurality of data bits. Are received in series. After the first half (first half) of the plurality of data bits is stored in the first set of write data buffers, the remaining half (second half) of the plurality of data bits is the second of the write data buffer. Saved in a set. Finally, the first half (first half) and the remaining half (second half) of each of the plurality of data bits from each of the first and second sets of write data buffers are shared through the local data line. Is written to.

本発明の他の実施形態によれば、複数のデータビットの最初の半分(第1の半分)が直列に受信されてから前記複数のデータビットの残りの半分(第2の半分)が直列に受信される。複数のデータビットの最初の半分(第1の半分)が第1書込みデータバッファに保存され、第1書込みデータバッファの前記複数のデータビットの最初の半分(第1の半分)が第2書込みデータバッファにシフトされ、第1書込みデータバッファに複数のデータビットの残りの半分(第2の半分)が保存される。第2書込みデータバッファから複数のビットデータの最初の半分(第1の半分)がメモリセルアレイに書き込まれる。第1書込みデータバッファの複数のデータビットの残りの半分(第2の半分)が第2書込みデータバッファにシフトされ、第2書込みデータバッファから複数のデータビットの残りの半分(第2の半分)がメモリセルアレイに書き込まれる。 According to another embodiment of the present invention, a first half (first half) of the plurality of data bits is received in series, and then the remaining half (second half) of the plurality of data bits is serially received. Received. The first half (first half) of the plurality of data bits is stored in the first write data buffer, and the first half (first half) of the plurality of data bits of the first write data buffer is the second write data. Shifted to the buffer, the remaining half (second half) of the plurality of data bits is stored in the first write data buffer. The first half (first half) of the plurality of bit data is written from the second write data buffer to the memory cell array. The remaining half (second half) of the plurality of data bits of the first write data buffer is shifted to the second write data buffer, and the remaining half of the plurality of data bits (second half) from the second write data buffer. Are written into the memory cell array.

また、本発明の実施形態によれば、グローバルデータラインとローカルデータラインとの数を増加させずに、例えば4ビットプリフェッチ構造で8ビットプリフェッチスキムを具現することによって、チップサイズを増加させずに超高速動作が可能な集積回路メモリ装置を提供することができる。 In addition, according to the embodiment of the present invention, without increasing the number of global data lines and local data lines, for example, by implementing an 8-bit prefetch scheme with a 4-bit prefetch structure, without increasing the chip size. An integrated circuit memory device capable of ultra-high speed operation can be provided.

また、本発明の実施形態によれば、例えば、4ビットプリフェッチ構造を有するメモリ装置でバースト長によってビットラインの自動プリチャージ時点を調節して、例えば、バースト長が8に対応するデータをメモリセルに書き込めるようにワードラインイネーブル時間が延びた集積回路メモリ装置を提供することができる。 Also, according to the embodiment of the present invention, for example, in a memory device having a 4-bit prefetch structure, the bit line automatic precharge time is adjusted according to the burst length, and for example, data corresponding to a burst length of 8 Therefore, an integrated circuit memory device with an extended word line enable time can be provided.

本発明によれば、nビットプリフェッチ構造を利用して2nビットプリフェッチスキームを具現することができる。 According to the present invention, a 2n-bit prefetch scheme can be implemented using an n-bit prefetch structure.

或いは、本発明によれば、バースト長の変化により自動プリチャージ時点を調節することができる。 Alternatively, according to the present invention, the automatic precharge time can be adjusted by changing the burst length.

或いは、本発明によれば、nビットプリフェッチ構造のメモリ装置を利用して2nビットプリフェッチスキームを具現することができる。 Alternatively, according to the present invention, a 2n-bit prefetch scheme can be implemented using a memory device having an n-bit prefetch structure.

或いは、本発明によれば、バースト長の変化による自動プリチャージ制御方法を提供するができる。 Alternatively, according to the present invention, it is possible to provide an automatic precharge control method by changing the burst length.

本発明とその動作上の利点及び本発明の実施によって達成される目的を十分に理解するためには本発明の望ましい実施形態を例示する添付図面及び添付図面に記載された内容を参照すべきである。 For a full understanding of the invention and its operational advantages and objects achieved by the practice of the invention, reference should be made to the accompanying drawings illustrating preferred embodiments of the invention and the contents described in the accompanying drawings. is there.

以下、図面を参照して本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に提示された同じ参照符号は、同様の構成要素を示す。 Hereinafter, the present invention will be described in detail by describing preferred embodiments of the present invention with reference to the drawings. The same reference numbers provided in each drawing indicate similar components.

図6は、本発明の1つの実施形態の集積回路メモリ装置のブロックダイアグラムである。図6に示されたように、集積回路メモリ装置400は、N個のデータビットが並列に書き込まれるメモリセルアレイ410を含む。書込みデータ経路420は、外部ターミナル426から直列ライン428に直列に2N個のデータビットを受信する。図6に示されたように、書込みデータ経路420は、直列ライン428上に受信される2N個のデータビットを保存するための2N個の書込みデータバッファ422と2N個のスイッチ424とで構成される。N個のデータライン412はまた、メモリセルアレイ410に並列にNデータビットを書き込むために、2N個のスイッチ424のうち少なくともN個をメモリセルアレイ410にする連結。

FIG. 6 is a block diagram of an integrated circuit memory device according to one embodiment of the present invention. As shown in FIG. 6, the integrated

図6は、複数データビットを並列に保存するためのメモリセルアレイ410を含む集積回路メモリ装置400として具体化された本発明の1つの実施形態を示している。書込みデータ経路420は、外部ターミナル426から2N個のデータビットを並列に受信し、2N個のデータビットをそれぞれN個に2分したうちの一方である第1グループ(最初の半分、或いは、第1の半分)を並列にメモリセルアレイ410に保存してから、2N個のデータビットをそれぞれN個に2分したうちの残りである第2グループ(残りの半分、或いは、第2の半分)を並列にメモリセルアレイ410に保存する。図6は、本発明の1つの実施形態の集積回路メモリ装置400の動作方法を示している。この動作方法は、外部ターミナル426から2N個のデータビットを直列に受信し、これらを2N個の書込みデータバッファ422に保存し、書込みデータバッファ422から2N個のデータビットをそれぞれN個に2分したうちの第1グループを並列にメモリセルアレイ410に保存してから、書込みデータバッファ422から2個のデータビットをそれぞれN個に2分したうちの残りの第2グループを並列にメモリセルアレイ410に保存する。

FIG. 6 illustrates one embodiment of the present invention embodied as an integrated

図7及び図8は、本発明の実施形態の書込みデータ経路のブロックダイアグラムである。図7に示す実施形態は、本発明の第1実施形態であり、図9乃至図12と関連して具体的に説明される。図8に示す実施形態は、本発明の第2実施形態であり、図15と21と関連して具体的に説明される。 7 and 8 are block diagrams of the write data path of the embodiment of the present invention. The embodiment shown in FIG. 7 is a first embodiment of the present invention, and will be specifically described in conjunction with FIGS. 9 to 12. The embodiment shown in FIG. 8 is a second embodiment of the present invention and will be specifically described in connection with FIGS.

図7を参照すれば、書込みデータ経路420’は、直列ライン428を通じて外部ターミナル426と連結される第1及び第2直列−並列変換部430a、430bで構成される。書込みデータ経路420’には、N個の第1グロ−バルデータライン434aとN個の第2グロ−バルデータライン434bとがさらに設けられている。図6の2N個の書込みデータバッファ422は、N個の第1書込みデータバッファ432aとN個の第2書込みデータバッファ432bとで構成される。また、図6の2N個のスイッチ424は、N個の第1スイッチ436aとN個の第2スイッチ436bとで構成される。図7に示されたように、N個の第1書込みデータバッファ432aは、第1直列−並列変換部430aと連結され、N個の第1グロ−バルデータラインのそれぞれは、N個の第1スイッチ436aそれぞれとN個の第1書込みデータバッファ432aのそれぞれの間に連結される。これと同様に、図7に示されたように、N個の書込みデータバッファ432bは、第2直列−並列変換部430bと連結され、N個の第2グロ−バルデータラインのそれぞれは、N個の第2スイッチ436bのそれぞれとN個の第2書込みデータバッファ432bのそれぞれの間に連結される。最後に、図7においては、図6のN個のデータラインは、N個のローカルデータライン438である。N個のローカルデータライン438のそれぞれは、N個の第1スイッチ436a及びN個の第2スイッチ436bのそれぞれとメモリセルのアレイ410との間に連結される。

Referring to FIG. 7, the

外部ターミナル426を通じて直列に受信される2N個のデータビットをそれぞれN個に2分したうちの第1グループが第1直列−並列変換部430aに保存され、外部ターミナル426を通じて直列に受信される2N個のデータビットをそれぞれN個に2分したうちの残りの第2グループが第2直列−並列変換部430bに受信される。2N個のデータビットのうちのN個の第1グループは、第1書込みデータバッファ432aに保存され、2N個のデータビットのうちの残りのN個の第2グループは、第2書込みデータバッファ432bに保存される。2N個のデータビットのうちのN個の第1グループは、第1書込みデータバッファ432aからメモリセルアレイ410に、そして、2N個のデータビットのうちの残りのN個の第2グループは、第2書込みデータバッファ432bからメモリセルアレイ410に、ローカルデータライン438を通じて書き込まれる。

Of the 2N data bits received in series through the

図8は、本発明の第2実施形態の書込みデータ経路のブロックダイアグラムである。図8に示されたように、書込みデータ経路420'’は、外部ターミナル426と連結される直列−並列変換部440を含む。書込みデータ経路420'’には、N個の第1書込みデータバッファ442aとN個の第2書込みデータバッファ442b、及び、N個の第1スイッチ446aとN個の第2スイッチ446bも提供される。N個の第1書込みデータバッファ442aは、直列−並列変換部440と連結され、N個の書込みデータバッファ442aのそれぞれはN個の第1スイッチ446aのそれぞれと連結される。また、N個の第2書込みデータバッファ442bは、N個の第2スイッチ446bのそれぞれと連結される。N個のグローバルデータライン444のそれぞれは、N個の第2スイッチ446bのそれぞれとN個の第2書込みデータバッファ442bのそれぞれとの間に連結される。最後に、N個のローカルデータライン448のそれぞれは、N個の第2スイッチ446bのそれぞれとメモリセルアレイ410との間に連結される。

FIG. 8 is a block diagram of the write data path of the second embodiment of the present invention. As shown in FIG. 8, the

図8は、本発明の第2実施形態の動作方法を示している。この動作方法は、2N個のデータビットをそれぞれN個に2分したうちのN個の第1グループが外部ターミナル426から直列に受信されてから、2N個のデータビットをそれぞれN個に2分したうちの残りのN個の第2グループが外部ターミナル426から直列に受信される動作を示している。2N個のデータビットのうちのN個の第1グループは、第1書込みデータバッファ442aに保存された後、2N個のデータビットのうちの残りのN個の第2グループが第1書込みデータバッファ442aに保存される際に、N個の第1スイッチ446aを通じて第1書込みデータバッファ442aから第2書込みデータバッファ442bにシフトされる。2N個のデータビットのうちのN個の第1グループは、N個の第2スイッチ446bを通じて第2書込みデータバッファ442bからメモリセルアレイ410に書き込まれる。2N個のデータビットのうちの残りのN個の第2グループは、N個の第1スイッチ446aを通じて第1書込みデータバッファ442aから第2書込みデータバッファ442bにシフトされた後、第2スイッチ446bを通じてメモリセルアレイ410に書き込まれる。すなわち、図8は、2N個のデータビットが書込みデータ経路420'’に保存され、N個のデータビットが並列にメモリセルアレイ410に書き込まれる書込みデータのパイプライン方式を示している。

FIG. 8 shows an operation method according to the second embodiment of the present invention. In this operation method, after N first groups of 2N data bits divided into 2 parts are received in series from the

図9A及び図9Bは、図7に示す第1実施形態の集積回路メモリ装置の具体的なブロックダイアグラムである。図9A及び図9Bに示された実施形態では、バースト長が4(BL=4)のスキームで8ビットプリフェッチ動作を行う。しかし、他の実施形態において、それより小さいかまたは大きいプリフェッチスキームとして使われうることは当業者に自明である。図9A及び図9Bに示されたように、8ビットプリフェッチ動作にもかかわらず、8個のグローバルデータラインGDL_0〜GDL_7が使われる一方で4個のローカルデータラインLDL_0〜LDL_3のみが使われる。したがって、メモリ装置のレイアウト面積は、8ビットプリフェッチ動作を行っても、図5のメモリ装置に比べて減る。 9A and 9B are specific block diagrams of the integrated circuit memory device of the first embodiment shown in FIG. In the embodiment shown in FIGS. 9A and 9B, an 8-bit prefetch operation is performed in a scheme with a burst length of 4 (BL = 4). However, it will be apparent to those skilled in the art that in other embodiments, it can be used as a smaller or larger prefetch scheme. As shown in FIGS. 9A and 9B, despite the 8-bit prefetch operation, only eight local data lines LDL_0 to LDL_3 are used while eight global data lines GDL_0 to GDL_7 are used. Therefore, the layout area of the memory device is reduced as compared with the memory device of FIG. 5 even when the 8-bit prefetch operation is performed.

図9Aを参照すれば、モードレジスタMRSによりバースト長=8(BL=8)が選択され、BL=8に相当する8ビットの入力デートが直列にバッファ502に受信される。バッファ502から出力される第1入力データビットは、第1内部データストローブ信号PDSの立上がりエッジに応答して第1入力データラッチ回路512の第1ラッチ511に保存される。第2入力データビットは、第1内部データストローブ信号PDSの立下りエッジに応答して第1入力データラッチ回路512の第2ラッチ513に保存される。2つの入力データビットが第1入力データラッチ回路512に保存された後に、第1ラッチ511の第1入力データビットと第2ラッチ513の第2入力データビットとがPDS信号の最初の立下りエッジに発生する第2内部データストローブ信号PDSPに応答して同時に並列変換部514の第3ラッチ515と第4ラッチ517とにそれぞれ伝えられる。

Referring to FIG. 9A, burst length = 8 (BL = 8) is selected by the mode register MRS, and an 8-bit input date corresponding to BL = 8 is received by the

次いで、図9Aにおいて、第3入力データビットは、第1内部データストローブ信号PDSの第2の立上がりエッジに応答して第1入力データラッチ回路512の第1ラッチ511に保存され、第4入力データビットは、第1内部データストローブ信号PDSの第2の立下りエッジに応答して第1入力データラッチ回路512の第2ラッチ513に保存される。同時に、第3及び第4入力データビットは、PDS信号の第2の立上がりエッジ及び立下りエッジに応答して並列変換部514のP1及びP4ノードにそれぞれ伝えられる。これにより、直列入力データの4ビットが並列変換部514内のP1ないしP4として示されたように、4ビットの並列入力データに変換される。並列データ出力516は、4ビット入力データをデータオーダリング回路520に出力する。データオーダリング回路520は、4ビット並列入力データの出力順序を決定する。しかし、本発明の他の実施形態では、データオーダリング回路520を使用しない場合もある。4ビット並列データP1〜P4は、複数の書込みスイッチ(WSW)522〜528に提供される第1書込み制御信号WDBICSに応答してそれぞれの書込みデータバッファ532、534、536、538に保存される。第1書込み制御信号WDBICSは、図10を参照して説明されるデータストローブカウンタから発生する。

Next, in FIG. 9A, the third input data bit is stored in the first latch 511 of the first input data latch circuit 512 in response to the second rising edge of the first internal data strobe signal PDS, and the fourth input data The bit is stored in the second latch 513 of the first input data latch circuit 512 in response to the second falling edge of the first internal data strobe signal PDS. At the same time, the third and fourth input data bits are transmitted to the P1 and P4 nodes of the parallel conversion unit 514 in response to the second rising edge and falling edge of the PDS signal, respectively. As a result, 4 bits of the serial input data are converted into 4-bit parallel input data as indicated by P1 to P4 in the parallel conversion unit 514. The parallel data output 516 outputs 4-bit input data to the data ordering circuit 520. The data ordering circuit 520 determines the output order of 4-bit parallel input data. However, in other embodiments of the present invention, the data ordering circuit 520 may not be used. The 4-bit parallel data P1 to P4 are stored in the respective

更に、バッファ502から出力される第5入力データビットは、第4内部データストローブ信号PDS’の立上がりエッジに応答して第2入力データラッチ回路612の第5ラッチ611に保存される。第6入力データビットは、第4内部データストローブ信号PDS’の立下りエッジに応答して第2入力データラッチ回路612の第6ラッチ613に保存される。第5及び第6入力データビットが第2入力データラッチ回路610に保存された後、第5及び第6ラッチ611、613内の第5及び第6入力データビットは、PDS’信号の最初の立下りエッジから発生する第5内部データストローブ信号PDSP’に応答して並列変換部614の第7及び第8ラッチ615、617にそれぞれ同時に伝えられる。

Further, the fifth input data bit output from the

その後、第7入力データビットは、第4内部データストローブ信号PDS’の第2の立上がりエッジに応答して第5ラッチ611に保存され、第8入力データビットは、第4内部データストローブ信号PDS’の第2の立下りエッジに応答して第6ラッチ613に保存される。これと同時に、第7及び第8入力データビットは、PDS’信号の第2の立上がりエッジ及び立下りエッジにそれぞれ応答して並列変換部614のノードP1’とP4’とにそれぞれ伝えられる。これにより直列に受信される第5ないし第8入力データビットは、第5ないし第8並列データビットP1’〜P4’に変換される。並列データ出力616は、4ビット並列入力データを、4ビット並列入力データの順序を決定するデータオーダリング回路620に出力する。前述したように、他の実施形態では、データオーダリング回路620を使用しない場合もある。 Thereafter, the seventh input data bit is stored in the fifth latch 611 in response to the second rising edge of the fourth internal data strobe signal PDS ′, and the eighth input data bit is stored in the fourth internal data strobe signal PDS ′. In the sixth latch 613 in response to the second falling edge. At the same time, the seventh and eighth input data bits are transmitted to the nodes P1 'and P4' of the parallel conversion unit 614 in response to the second rising edge and falling edge of the PDS 'signal, respectively. As a result, the fifth to eighth input data bits received in series are converted into the fifth to eighth parallel data bits P1 'to P4'. The parallel data output 616 outputs the 4-bit parallel input data to the data ordering circuit 620 that determines the order of the 4-bit parallel input data. As described above, in other embodiments, the data ordering circuit 620 may not be used.

次いで、4ビット並列データは、第2書込み制御信号WDBICS’に応答して複数の書込みデータバッファ632〜638に保存される。第2書込み制御信号WDBICS’は、図10で説明されるデータストローブカウンタにより生成される。したがって、直列に受信されたデータの8ビットは、8ビットの並列データに変換され、8個の書込みデータバッファ532〜538、632〜638に保存される。

Then, the 4-bit parallel data is stored in the plurality of

したがって、図9Aに記載された本発明の実施形態では、第1直列−並列変換部510は、第1内部データストローブ信号、例えばPDS、PDSP及びPDSENに応答し、第2直列−並列変換部610は、第2内部データストローブ信号、例えばPDS’、PDSP’及びPDSEN’に応答する。一方、図9Bを参照すれば、第1直列−並列変換部510’と第2直列−並列変換部610’は、両方とも同時に内部データストローブ信号、例えばPDS、PDSP及びPDSENに応答する。 Therefore, in the embodiment of the present invention described in FIG. 9A, the first serial-parallel converter 510 responds to the first internal data strobe signals, eg, PDS, PDSP and PDSEN, and the second serial-parallel converter 610. Responds to a second internal data strobe signal, eg PDS ′, PDSP ′ and PDSEN ′. Meanwhile, referring to FIG. 9B, both the first serial-parallel converter 510 'and the second serial-parallel converter 610' respond to internal data strobe signals, eg, PDS, PDSP, and PDSEN at the same time.

次いで、図9A及び9Bに示す集積回路メモリ装置の動作を説明する。この集積回路メモリ装置では、8ビットの直列入力データが8個の書込みデータバッファに保存された後、第1書込みデータバッファ532〜538に保存された並列入力データである第1グループの4ビットは、複数の制御スイッチ(CSW)542〜548に提供される第1スイッチング信号CICSに応答してそれぞれのローカルデータラインLDL_0〜LDL_3に伝えられ、カラム選択ライン部550に提供されるカラム選択信号CSLに応答して選択されるビットラインBLを通してメモリセルアレイ560の選択されたメモリセルに書き込まれる。次いで、第2書込みデータバッファ632〜638に保存された第2グループの4ビット並列入力データは、第2制御スイッチ(CSW)642〜648に提供される第2スイッチング信号CICS’に応答してそれぞれのローカルデータラインLDL_0〜LDL_3に伝えられる。

Next, the operation of the integrated circuit memory device shown in FIGS. 9A and 9B will be described. In this integrated circuit memory device, after the 8-bit serial input data is stored in the eight write data buffers, the first group of 4 bits, which are the parallel input data stored in the first

ここで、CSW542〜548を第1制御スイッチと呼び、CSW642〜648を第2制御スイッチと呼ぶ。また、WSW522〜528を第3スイッチと呼び、WSW622〜628を第4スイッチと呼ぶ。

Here, the CSWs 542 to 548 are called first control switches, and the

したがって、図9A及び図9Bに示されたように、本発明の実施形態では、8個のグローバルデータラインGDL_0〜GDL_7と共に4個のローカルデータラインLDL_0〜LDL_3のみが使われる。したがって、集積回路レイアウト面積は、従来の8個のグロ−バルデータラインと8個のローカルデータラインとで8ビットプリフェッチを行う書込みデータ経路に比べて減る。 Therefore, as shown in FIGS. 9A and 9B, in the embodiment of the present invention, only four local data lines LDL_0 to LDL_3 are used together with eight global data lines GDL_0 to GDL_7. Therefore, the integrated circuit layout area is reduced as compared with the conventional write data path in which 8-bit prefetch is performed with 8 global data lines and 8 local data lines.

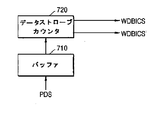

図10は、本発明の1つの実施形態における第1書込み制御信号WDBICS及び第2書込み制御信号WDBICS’の発生回路を説明するブロックダイアグラムである。図10に示されたように、書込み制御信号は、第1データストローブ信号PDSに応答するバッファ710と、バッファ710の出力に応答して第1データストローブ信号PDSの立上がり及び立下りエッジ数をカウントするデータストローブカウンタ720とにより発生する。第1書込み制御信号WDBICSは、データストローブ信号PDSの第2の立下りエッジに応答して発生し、第2書込み制御信号WDBICS’は、データストローブ信号PDSの第4の立下りエッジに応答して発生する。この実施形態によりPDSEN及びPDSEN’信号も生成されうる。

FIG. 10 is a block diagram illustrating a circuit for generating the first write control signal WDBICS and the second write control signal WDBICS ′ according to an embodiment of the present invention. As shown in FIG. 10, the write control signal counts the

図11は、図9で説明された実施形態のためのスイッチング信号の発生回路の実施形態を説明するブロックダイアグラムである。図11に示されたように、スイッチング信号は、チップ選択信号/CSとファンクション信号FNに応答してアクティブ命令信号ACT、読出命令信号RDA及び書込み命令信号WRAを発生させるコマンダーデコーダ104を使用して発生する。制御信号発生回路1110は、書込み命令信号WRAに応答して所定の時間間隔で第1及び第2スイッチング信号CICS、CICS’を発生する。

FIG. 11 is a block diagram illustrating an embodiment of a switching signal generation circuit for the embodiment described in FIG. As shown in FIG. 11, the switching signal is generated using the

次いで、本発明の他の実施形態では、図11の命令デコーダ1104は、1104’として示され、命令デコーダ1104に提供されるチップ選択信号/CSとファンクション信号とFNに応答してモードリセット命令とリフレッシュ命令REFをも発生する。

Next, in another embodiment of the present invention, the

図12A及び12Bは、図7及び9A乃至図11に記載された本発明の実施形態によって8ビットプリフェッチ動作を行うタイミングダイアグラムである。さらに具体的には、図12Aは、図9Aのタイミングダイアグラムであり、図12Bは図9Bのタイミングダイアグラムである。これらのタイミングダイアグラムは、前述した書込みデータバッファ532〜538、632〜638の動作だけでなく、多様な制御信号を説明する。これに対する比較のために、図13及び14は、図3を参照して前述したFCRAMの4ビットプリフェッチ動作とDDR SDRAMでの4ビットプリフェッチ動作を説明するタイミングダイアグラムである。 12A and 12B are timing diagrams for performing an 8-bit prefetch operation according to the embodiment of the present invention described in FIGS. 7 and 9A to 11. More specifically, FIG. 12A is the timing diagram of FIG. 9A, and FIG. 12B is the timing diagram of FIG. 9B. These timing diagrams illustrate various control signals as well as the operation of the write data buffers 532-538, 632-638 described above. For comparison, FIGS. 13 and 14 are timing diagrams illustrating the 4-bit prefetch operation of the FCRAM and the 4-bit prefetch operation of the DDR SDRAM described above with reference to FIG.

図13において、”0000”番地に書き込むための4ビット入力データは、以前の書込み命令WR0に応答して書き込まれるのではなく、次の書込み命令WR1を受信した後に書き込まれる。したがって、入力データは、以前のサイクルCYC#1で書込みデータバッファに保存された後にサイクルCYC#2において次の書込み命令WR1に応答してメモリセルに書き込まれる。

In FIG. 13, the 4-bit input data for writing to the address “0000” is not written in response to the previous write command WR0, but is written after receiving the next write command WR1. Therefore, the input data is stored in the write data buffer in the previous

図14において、DDR SDRAMでは、”0000”番地に書き込むための4ビット入力データは、図13に示されたように、次の書込み命令WR1に応答するのではなく、書込み命令WR0に応答して該当メモリセルに書き込まれる。このDDR SDRAMは、入力データを書込みデータバッファに保存せずに直ちにメモリセルに書き込むため、書込みデータバッファを含まない。 In FIG. 14, in the DDR SDRAM, the 4-bit input data for writing to the address “0000” is not in response to the next write command WR1, but in response to the write command WR0, as shown in FIG. Data is written in the corresponding memory cell. The DDR SDRAM does not include a write data buffer because input data is immediately written to a memory cell without being stored in the write data buffer.

図15は、図8に記載された本発明の第2実施形態のさらに具体的なブロックダイアグラムである。図8に示されたように、単にN個のグローバルデータラインとN個のローカルデータラインとを2N個の書込みデータ経路に使用するために、書込みデータ経路にパイプライン構成が使われる。これにより、グロ−バルデータラインとローカルデータラインの数は従来の書込みデータ経路と比較して減る。 FIG. 15 is a more specific block diagram of the second embodiment of the present invention described in FIG. As shown in FIG. 8, a pipeline configuration is used for the write data path to simply use N global data lines and N local data lines for 2N write data paths. This reduces the number of global data lines and local data lines compared to the conventional write data path.

さらに具体的には、図15を参照すれば、書込みデータ経路700は、例えば既に図9で説明されたような直列−並列変換部510、オプションであるデータオーダリング回路520、第1スイッチ722〜728、第1書込みデータバッファ732〜738、第2スイッチ742〜748、第2書込みデータバッファ752〜758及び第3スイッチ762〜768を含むパイプラインステージで構成される。図15に示されたように、このような実施形態は、例えば図9の実施形態よりデータラインが少数である。なぜなら、グロ−バルデータラインGDL_0〜GDL_3の数は、4ビットプリフェッチスキームと同じであり、ローカルデータラインLDL_0〜LDL_3の数は、4ビットプリフェッチスキームと同じであるためである。それゆえに、メモリ装置のレイアウト面積は減る。

More specifically, referring to FIG. 15, the

次いで、図15において、BL=8に対応する8ビット入力データは、バッファ502を通じて直列に受信される。直列入力データの第1の4ビットは、並列出力データ回路510において4ビット並列入力データに変換され、並列入力データの第1の4ビットはオプションであるデータオーダリング回路520に提供される。データオーダリング回路520は、4ビット並列入力データの出力順序を決定する。その後、並列入力データの最初の4ビットは、書込みスイッチ(WSW)722〜728に提供される第1書込み制御信号WDBICSに応答して第1書込みデータバッファ732〜738に保存される。これと同時に、直列入力データの第2の4ビットは、並列データ出力回路510から4ビットの並列入力データに変換され、もし存在するならば、データオーダリング回路520に提供される。

Next, in FIG. 15, 8-bit input data corresponding to BL = 8 is received serially through the

次いで、第1書込みデータバッファ732〜738に保存された並列入力データの第1の4ビットは、書込みスイッチWSW、742〜748に提供される第2書込み制御信号WDBICS’に応答して第2書込みデータバッファ752〜758に保存される。これと同時に、データオーダリング回路520から並列ビットデータの第2の4ビットはまた、第1書込み制御信号WDBICSの第2の活性化に応答して第1書込みデータバッファ732〜738に保存される。これにより、並列入力データの第1の4ビットと第2の4ビットとは、順次にメモリセルアレイ560に伝えられ、多数のWDBICS、WDBICS’、CICS、CSL信号に応答して選択されたメモリセルに書き込まれる。図15に示されたように、これらのWDBICS、WDBICS’、CICS、CSL信号は、パイプライン動作のために第1の4ビットのために、そして、第2の4ビットのために2回イネーブルされる。

Then, the first four bits of the parallel input data stored in the first

次いで、本発明の実施形態のプリチャージ制御回路について説明する。このプリチャージ制御回路は、各N個の並列ビットを2グループとして、メモリセルアレイに2N個のデータビットを書き込むために十分な時間にわたってメモリセルアレイのワードラインを活性化させるために図6乃至図12及び図15の実施形態と関連して使われる。本発明の実施形態のプリチャージ制御回路を説明するために、図16を参照して従来のプリチャージ制御回路を説明する。 Next, a precharge control circuit according to an embodiment of the present invention will be described. This precharge control circuit groups each of the N parallel bits into two groups, and activates the word lines of the memory cell array for a time sufficient to write 2N data bits to the memory cell array. And in connection with the embodiment of FIG. In order to describe the precharge control circuit according to the embodiment of the present invention, a conventional precharge control circuit will be described with reference to FIG.

図16は、図13と共に使われる従来のプリチャージ制御回路に対するタイミングダイアグラムである。図16に示されたように、4ビットプリフェッチスキームを使用してあらゆる入力データD0、D1、D2、D3を該当メモリセルに書き込むためにワードラインを活性化させるために、ワードラインはT0時間にわたってイネーブルされる。 FIG. 16 is a timing diagram for a conventional precharge control circuit used in conjunction with FIG. In order to activate the word line to write any input data D0, D1, D2, D3 to the corresponding memory cell using a 4-bit prefetch scheme as shown in FIG. Enabled.

図17は、図5を参照して説明した8ビットプリフェッチスキームにおいてワードラインをイネーブルさせる従来の技術を示している。図17において、図5に示す8ビットプリフェッチスキームでは、8ビットが並列に書き込まれるために、図16に示す4ビットプリフェッチスキームで使われたT0時間は、メモリセルに8ビットの入力データを書き込むのに十分な時間である。なぜなら、図5において、8ビット入力デートは、並列入力データに変換された後、同時に該当メモリセルに書き込まれるためである。 FIG. 17 shows a conventional technique for enabling a word line in the 8-bit prefetch scheme described with reference to FIG. In FIG. 17, in the 8-bit prefetch scheme shown in FIG. 5, 8 bits are written in parallel, and therefore, T0 time used in the 4-bit prefetch scheme shown in FIG. 16 writes 8-bit input data to the memory cell. It is enough time. This is because an 8-bit input date in FIG. 5 is written into the corresponding memory cell at the same time after being converted into parallel input data.

図18は、図16及び図17に示すプリチャージスキームが本発明の実施形態に適用されない理由を説明する。特に、図18に示されたように、同じプリフェッチ時間T0が本発明の実施形態に使われれば、2N個のデータビットをそれぞれN個に2分したうちのN個の第2グループは、メモリセルアレイに書き込むことができない。言い換えれば、入力データD4〜D7が失われる。本発明の実施形態によって、プリチャージ制御回路は、N個の並列データの2グループ分である2N個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルのワードラインを活性化させる。 FIG. 18 explains why the precharge scheme shown in FIGS. 16 and 17 is not applied to the embodiment of the present invention. In particular, as shown in FIG. 18, if the same prefetch time T0 is used in the embodiment of the present invention, the N second groups of the 2N data bits divided into two are divided into memory. Cannot write to the cell array. In other words, the input data D4 to D7 are lost. According to an embodiment of the present invention, the precharge control circuit activates the word line of the memory cell for a time sufficient to write 2N data bits, which are two groups of N parallel data, to the memory cell array. Let

さらに具体的には、図18に示されたように、4ビットプリフェッチスキームに使われたT0時間は、本発明の実施形態による8ビット入力データをメモリセルアレイに書き込むのに十分ではない。なぜなら、前述されたように、本発明の実施形態によれば、8ビット入力デートは、同時にメモリセルに書き込まれないためである。言い換えれば、8ビットの直列入力データは、第1及び第2グループに分けられるためである。4ビット直列入力データの第1グループが4ビット並列データに変換される。その後、4ビット直列入力データの第2グループが4ビット並列入力データに変換される。それにより、第1の4ビット入力データがメモリセルに並列に書き込まれた後、第2の4ビット入力データがメモリセルに並列に書き込まれる。したがって、本発明の実施形態において、ワードラインイネーブル時間は、バースト長(BL)=4、BL=8によって調整されねばならない。 More specifically, as shown in FIG. 18, the T0 time used for the 4-bit prefetch scheme is not sufficient to write 8-bit input data to the memory cell array according to an embodiment of the present invention. This is because, as described above, according to the embodiment of the present invention, the 8-bit input date is not simultaneously written into the memory cell. In other words, 8-bit serial input data is divided into first and second groups. A first group of 4-bit serial input data is converted to 4-bit parallel data. Thereafter, the second group of 4-bit serial input data is converted to 4-bit parallel input data. Thereby, after the first 4-bit input data is written in parallel to the memory cell, the second 4-bit input data is written in parallel to the memory cell. Therefore, in the embodiment of the present invention, the word line enable time must be adjusted by burst length (BL) = 4, BL = 8.

図19は、集積回路メモリ装置の第1プリチャージモードの間において、N並列ビットの2グループ分である2N個のデータビットをメモリセルアレイに書き込むのに十分な時間のためにメモリセルアレイのワードラインをイネーブルさせるプリチャージ制御回路の回路ダイアグラムである。プリチャージ制御回路1900は、集積回路メモリ装置の第2プリチャージモードの間において、N並列ビットの1つの形式であるNデータビットのグループをメモリセルアレイに書き込むのに十分な時間にわたってメモリセルアレイのワードラインを活性化させる。 FIG. 19 illustrates the word line of the memory cell array for a time sufficient to write 2N data bits, which are two groups of N parallel bits, into the memory cell array during the first precharge mode of the integrated circuit memory device. 2 is a circuit diagram of a precharge control circuit for enabling The precharge control circuit 1900 provides a word of the memory cell array for a time sufficient to write a group of N data bits, one form of N parallel bits, to the memory cell array during a second precharge mode of the integrated circuit memory device. Activate the line.

さらに具体的には、図19に示されたように、プリチャージ制御回路1900は、バースト長信号BL−1、BL−2と命令デコーダ1904が発生するプリチャージ命令信号AP_CMDを受信した後に、プリチャージ制御信号APを出力する。命令デコーダ1904は、外部命令信号/CS、FNと外部クロック信号CLK、/CLKに応答することができる。例えば、メモリ装置が4ビットプリフェッチ(BL=4が選択された時)で動作する時は、BL−1がイネーブルされる。また、本発明の実施形態において、メモリ装置が8ビットプリフェッチ(BL=8が選択された時)で動作する時は、BL−2がイネーブルされる。

More specifically, as shown in FIG. 19, the precharge control circuit 1900 receives the burst length signals BL-1 and BL-2 and the precharge command signal AP_CMD generated by the

図19に示されたように、BL=4のための遅延時間DT1は、BL=8のための遅延時間DT2より短い。したがって、第1遅延回路1910は相対的に短い第1遅延時間DT1を提供し、第2遅延回路1920は相対的に長い第2遅延時間DT2を提供する。1つの実施形態において、DT1は3.5クロックサイクルであり、一方、DT2は5.5クロックサイクルである。結合回路1930は、第1遅延回路1910及び第2遅延回路1920からプリチャージ制御信号APを提供する。したがって、BL=4のためのプリチャージ制御信号APは、BL=8のためのプリチャージ制御信号APより速く活性化されてワードラインを非活性化させる。したがって、BL=8のためのワードラインイネーブル時間は、図18に示されたT0時間と比較して長くなる。

As shown in FIG. 19, the delay time DT1 for BL = 4 is shorter than the delay time DT2 for BL = 8. Accordingly, the

図13に示されたように、BL=4のためのワードラインイネーブル時間は、ほぼ3.5クロックサイクルである。一方、図12に示されたように、BL=8のためのワードラインイネーブル時間は、ほぼ5.5クロックサイクルである。1つの実施形態において、モードレジスタは、第1及び第2プリチャージモードを選択するように設定されて、プリチャージ制御回路1910は、モードレジストに応答する。

As shown in FIG. 13, the word line enable time for BL = 4 is approximately 3.5 clock cycles. On the other hand, as shown in FIG. 12, the word line enable time for BL = 8 is approximately 5.5 clock cycles. In one embodiment, the mode register is set to select the first and second precharge modes, and the

次いで、本発明の実施形態の書込みデータバッファの追加的な事項について説明する。図20には、図6乃至9及び図15の書込みデータバッファの1つが例示的に示されている。書込みデータバッファ2010は、書込みアドレスをラッチするアドレスラッチ2012を含む。アドレス比較部2014は、アドレスラッチ2012にラッチされた書込みアドレスと現在の書込みアドレスとを比較する。データラッチ2016は、書込みアドレスに対応する書込みデータをラッチする。1つの実施形態において、現在のアドレスが読出しアドレスであり、アドレス比較部2014が読出しアドレスとアドレスラッチ2012にラッチされた書込みアドレスとが一致すると判断する場合、集積回路メモリ装置は、メモリセルアレイからではなく、データラッチ2016から外部ターミナルに読出しデータを出力する。他の実施形態において、現在のアドレスが読出しアドレスであり、アドレス比較部2014が読出しアドレスとアドレスラッチ2012にラッチされた書込みアドレスとが一致していないと判断する場合、集積回路メモリ装置は、メモリセルアレイから外部ターミナルに読出しデータを出力する。

Next, additional items of the write data buffer according to the embodiment of the present invention will be described. FIG. 20 exemplarily shows one of the write data buffers of FIGS. 6 to 9 and FIG. The

図20は、本発明の実施形態のデータ書込み構造及び過程だけでなく、データ読出構造及び過程も示している。書込みデータバッファ2010は、アドレスラッチ2012、アドレス比較部2014及びデータラッチ2016を含む。アドレスラッチ2012は、命令デコーダ104のような命令デコーダから提供される書込み命令信号WRにより制御され、アドレスバッファ106から受信される入力アドレスを保存する。これと同時に、入力アドレスに対応する入力データがデータラッチ2016に保存される。アドレス比較部2014は、アドレスラッチ2012に保存された入力アドレスと現在の入力アドレスとを比較してアドレス比較信号ADCMPをDQバッファ2020に出力する。現在の入力アドレスが保存された入力アドレスと一致する場合、ADCMP信号は、例えばハイレベルに活性化される。これにより、データラッチ2016に保存された読出しデータが第1伝送ゲート2022を通じてDQパッドに出力される。しかし、現在の入力アドレスが保存された入力アドレスと異なる場合、ADCMP信号は非活性化される。このような状況下で、メモリセルアレイに保存された読出しデータが第2伝送ゲート2024を通じてDQパッドに出力される。

FIG. 20 shows not only the data write structure and process of the embodiment of the present invention, but also the data read structure and process. The

図21は、図15及び図18乃至図20と連係して本発明の実施形態のデータ読出し/書込み過程を説明するタイミングダイアグラムである。図21に示されたように、データビットのパイプライン書込みは、拡張されたワードラインイネーブル信号を含む2つのサイクルCYC#1、CYC#2の間に起きる。その上、図21に示されたように、メモリ装置が命令デコーダ104から読出命令RDを受信すれば、図20のアドレス比較部2014は、現在の入力アドレス(0001;RD命令入力)とアドレスラッチに保存された入力アドレス(0001;WR1命令入力)とを比較する。ここでは、両者が同じアドレスであるために、読出しデータは、メモリセルアレイではなく書込みデータバッファ532〜538から直ちに出力される。

FIG. 21 is a timing diagram illustrating a data read / write process according to an embodiment of the present invention in conjunction with FIGS. 15 and 18 to 20. As shown in FIG. 21, pipeline writing of data bits occurs between two

本発明は実施形態を通じて説明されたが、これは例示的なものに過ぎず、本技術分野の当業者であれば、これより多様な変形及び均等な他の実施形態が可能である点が理解できるであろう。したがって、本発明の真の技数的保護範囲は、特許請求の範囲の技数的思想により定められねばならない。 Although the present invention has been described through the embodiments, this is merely an example, and it is understood by those skilled in the art that various modifications and other equivalent embodiments are possible. It will be possible. Accordingly, the true technical protection scope of the present invention must be determined by the technical ideas of the claims.

本発明による集積回路メモリ装置は、消費材及び商業上の応用に広く使われている。 Integrated circuit memory devices according to the present invention are widely used in consumer and commercial applications.

510 第1直列−並列変換部

511 BL_0−BL_

512 第1入力データラッチ回路

513 第2ラッチ

514 並列変換部

515 第3ラッチ

516 並列データ出力

517 第4ラッチ

520 データオーダリング回路

522、524、526、528 書込みスイッチ

532、534、536、538 書込みデータバッファ

542、544、546、548 制御スイッチ

550 カラム選択ライン部

560 メモリセルアレイ

610 第2入力データラッチ回路

611 第5ラッチ

612 第2入力データラッチ回路

613 第6ラッチ

614 並列変換部

615、617 第7及び第8ラッチ

616 並列データ出力

620 データオーダリング回路

622、624、626、628 書込みスイッチ

632、634、636、638 書込みデータバッファ

642、644、646、648 第2制御スイッチ

510 1st serial-parallel conversion part 511 BL_0-BL_

512 First input data latch circuit 513 Second latch 514

Claims (8)

外部ターミナルから2N個のデータビットを直列に受信する書込みデータ経路と、を具備し、

前記書込みデータ経路は、

2N個の書込みデータバッファと、

2N個のスイッチと、

N個のデータビットを並列に前記メモリセルアレイに書き込むために前記2N個のスイッチのうち少なくともN個のスイッチと連結されるN個のデータラインと、を具備し、

前記書込みデータ経路は、

前記外部ターミナルと連結される第1及び第2直列−並列変換部と、

N個の第1グローバルデータラインとN個の第2グローバルデータラインとを具備し、

前記2N個の書込みデータバッファは、N個の第1書込みデータバッファとN個の第2書込みデータバッファとを含んで構成され、

前記2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとを含んで構成され、

前記N個の第1書込みデータバッファは、第1直列−並列変換部に連結され、前記N個の第1グローバルデータラインのそれぞれは、前記N個の第1スイッチのそれぞれと前記N個の第1書込みデータバッファのそれぞれとの間に連結され、

前記N個の第2書込みデータバッファは、第2直列−並列変換部に連結され、前記N個の第2グローバルデータラインのそれぞれは、前記N個の第2スイッチのそれぞれと前記N個の第2書込みデータバッファのそれぞれとの間に連結され、

前記N個のデータラインは、N個のローカルデータラインであり、

前記N個のローカルデータラインのそれぞれは、前記N個の第1スイッチ及び前記N個の第2スイッチと前記メモリセルアレイとの間にそれぞれ連結され、

前記書込みデータ経路は、

前記第1及び第2直列−並列変換部のうち何れか1つと前記N個の第1書込みデータバッファ及び前記N個の第2書込みデータバッファのうち何れか1つとの間にそれぞれ連結される第1及び第2データオーダリング回路をさらに具備し、

前記N個の第1スイッチは、第1制御信号に応答し、

前記N個の第2スイッチは、前記第1制御信号から遅延された第2制御信号に応答し、

前記第1及び第2制御信号は、

書込み活性化信号から異なる遅延時間をもって遅延されて生成される

ことを特徴とする集積回路装置。 A memory cell array including a plurality of memory cells;

A write data path for receiving in serial 2N data bits from an external terminal,

The write data path is:

2N write data buffers;

2N switches,

N data lines connected to at least N of the 2N switches to write N data bits to the memory cell array in parallel,

The write data path is:

First and second series-parallel converters connected to the external terminal;

Comprising N first global data lines and N second global data lines;

The 2N write data buffers include N first write data buffers and N second write data buffers.

The 2N switches are configured to include N first switches and N second switches,

The N first write data buffers are connected to a first serial-parallel converter, and each of the N first global data lines includes each of the N first switches and the N first switches. 1 write data buffer connected to each

The N second write data buffers are connected to a second serial-to-parallel converter, and each of the N second global data lines includes each of the N second switches and the N second switches. Connected to each of the two write data buffers,

The N data lines are N local data lines;

Each of the N local data lines is connected between the N first switches, the N second switches, and the memory cell array, respectively.

The write data path is:

The first and second serial-to-parallel converters may be connected between one of the first and second serial-parallel converters and one of the N first write data buffers and the N second write data buffers, respectively. 1 and a second data ordering circuit,

The N first switches are responsive to a first control signal;

The N second switches are responsive to a second control signal delayed from the first control signal;

The first and second control signals are:

An integrated circuit device produced by being delayed from a write activation signal with different delay times.

チップ選択命令及びファンクション命令に応答して前記書込み活性化信号を発生する命令デコーダと、

前記書込み活性化信号に応答して前記第1及び第2制御信号を発生する制御信号発生部と、をさらに具備する

ことを特徴とする請求項1に記載の集積回路装置。 The integrated circuit device includes:

An instruction decoder for generating the write activation signal in response to a chip selection instruction and a function instruction;

2. The integrated circuit device according to claim 1, further comprising: a control signal generation unit that generates the first and second control signals in response to the write activation signal.

前記チップ選択命令及び前記ファンクション命令に応答してアクティブ命令及び読出命令をさらに発生する

ことを特徴とする請求項2に記載の集積回路装置。 The instruction decoder

The integrated circuit device according to claim 2, further generating an active command and a read command in response to the chip selection command and the function command.

前記チップ選択命令及び前記ファンクション命令に応答して読出命令、リフレッシュ命令及びモードレジスタ命令をさらに発生する

ことを特徴とする請求項2に記載の集積回路メモリ装置。 The instruction decoder

The integrated circuit memory device according to claim 2, further comprising a read command, a refresh command, and a mode register command in response to the chip selection command and the function command.

外部ターミナルから2N個のデータビットを直列に受信する書込みデータ経路と、を具備し、

前記書込みデータ経路は、

2N個の書込みデータバッファと、

2N個のスイッチと、

N個のデータビットを並列に前記メモリセルアレイに書き込むために前記2N個のスイッチのうち少なくともN個のスイッチと連結されるN個のデータラインと、を具備し、

前記書込みデータ経路は、

前記外部ターミナルと連結される第1及び第2直列−並列変換部と、

N個の第1グローバルデータラインとN個の第2グローバルデータラインとを具備し、

前記2N個の書込みデータバッファは、N個の第1書込みデータバッファとN個の第2書込みデータバッファとを含んで構成され、

前記2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとを含んで構成され、

前記N個の第1書込みデータバッファは、第1直列−並列変換部に連結され、前記N個の第1グローバルデータラインのそれぞれは、前記N個の第1スイッチのそれぞれと前記N個の第1書込みデータバッファのそれぞれとの間に連結され、

前記N個の第2書込みデータバッファは、第2直列−並列変換部に連結され、前記N個の第2グローバルデータラインのそれぞれは、前記N個の第2スイッチのそれぞれと前記N個の第2書込みデータバッファのそれぞれとの間に連結され、

前記N個のデータラインは、N個のローカルデータラインであり、

前記N個のローカルデータラインのそれぞれは、前記N個の第1スイッチ及び前記N個の第2スイッチと前記メモリセルアレイとの間にそれぞれ連結され、

前記書込みデータ経路は、

前記第1及び第2直列−並列変換部のうち何れか1つと前記N個の第1書込みデータバッファ及び前記N個の第2書込みデータバッファのうち何れか1つとの間にそれぞれ連結される第1及び第2データオーダリング回路をさらに具備し、

前記N個の第1スイッチは、第1制御信号に応答し、

前記N個の第2スイッチは、前記第1制御信号から遅延された第2制御信号に応答し、

前記集積回路装置は、

N個の第3スイッチとN個の第4スイッチとをさらに具備し、

前記N個の第3スイッチのそれぞれは、前記第1直列−並列変換部と前記N個の第1書込みデータバッファのそれぞれとの間に連結され、

前記N個の第4スイッチは、前記第2直列−並列変換部と前記N個の第2書込みデータバッファのそれぞれとの間に連結される

ことを特徴とする集積回路装置。 A memory cell array including a plurality of memory cells;

A write data path for receiving in serial 2N data bits from an external terminal,

The write data path is:

2N write data buffers;

2N switches,

N data lines connected to at least N of the 2N switches to write N data bits to the memory cell array in parallel,

The write data path is:

First and second series-parallel converters connected to the external terminal;

Comprising N first global data lines and N second global data lines;

The 2N write data buffers include N first write data buffers and N second write data buffers.

The 2N switches are configured to include N first switches and N second switches,

The N first write data buffers are connected to a first serial-parallel converter, and each of the N first global data lines includes each of the N first switches and the N first switches. 1 write data buffer connected to each

The N second write data buffers are connected to a second serial-to-parallel converter, and each of the N second global data lines includes each of the N second switches and the N second switches. Connected to each of the two write data buffers,

The N data lines are N local data lines;

Each of the N local data lines is connected between the N first switches, the N second switches, and the memory cell array, respectively.

The write data path is:

The first and second serial-to-parallel converters may be connected between one of the first and second serial-parallel converters and one of the N first write data buffers and the N second write data buffers, respectively. 1 and a second data ordering circuit,

The N first switches are responsive to a first control signal;

The N second switches are responsive to a second control signal delayed from the first control signal;

The integrated circuit device includes:

Further comprising N third switches and N fourth switches;

Each of the N third switches is connected between the first serial-parallel converter and each of the N first write data buffers.

The integrated circuit device, wherein the N fourth switches are connected between the second serial-parallel converter and each of the N second write data buffers.

前記N個の第4スイッチは、前記第3制御信号から遅延された第4制御信号に応答する

ことを特徴とする請求項5に記載の集積回路装置。 The N third switches are responsive to a third control signal;

The integrated circuit device according to claim 5, wherein the N fourth switches are responsive to a fourth control signal delayed from the third control signal.

データストローブ信号のオフセット立下りエッジに応答して発生される

ことを特徴とする請求項6に記載の集積回路装置。 The third and fourth control signals are:

The integrated circuit device according to claim 6, wherein the integrated circuit device is generated in response to an offset falling edge of the data strobe signal.

前記データストローブ信号に応答して前記データストローブ信号の立下りエッジをカウントして、前記データストローブ信号のオフセット立下りエッジにしたがって前記第3及び第4制御信号を発生するデータストローブカウンタをさらに具備する

ことを特徴とする請求項7に記載の集積回路装置。 The integrated circuit device includes:

A data strobe counter for counting the falling edge of the data strobe signal in response to the data strobe signal and generating the third and fourth control signals according to the offset falling edge of the data strobe signal; The integrated circuit device according to claim 7.

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR20030035604 | 2003-06-03 | ||

| KR2003-035604 | 2003-06-03 | ||

| KR10-2003-0042840A KR100532444B1 (en) | 2003-06-03 | 2003-06-27 | Memory device implementing 2N bit prefetch scheme using N bit prefetch structure and 2N bit prefetching method and auto-precharge method |

| KR2003-042840 | 2003-06-27 | ||

| US10/792425 | 2004-03-03 | ||

| US10/792,425 US7054202B2 (en) | 2003-06-03 | 2004-03-03 | High burst rate write data paths for integrated circuit memory devices and methods of operating same |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004362756A JP2004362756A (en) | 2004-12-24 |

| JP2004362756A5 JP2004362756A5 (en) | 2007-03-22 |

| JP4819325B2 true JP4819325B2 (en) | 2011-11-24 |

Family

ID=33545117

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004161460A Expired - Fee Related JP4819325B2 (en) | 2003-06-03 | 2004-05-31 | Integrated circuit device and operation method thereof |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JP4819325B2 (en) |

| DE (1) | DE102004026526B4 (en) |

| GB (1) | GB2403575B (en) |

| TW (1) | TWI250530B (en) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102005001894A1 (en) | 2005-01-14 | 2006-08-03 | Infineon Technologies Ag | Synchronous parallel-to-serial converter |

| JP5052056B2 (en) * | 2005-09-29 | 2012-10-17 | エスケーハイニックス株式会社 | Data input device for semiconductor memory device |

| JP4470183B2 (en) | 2006-08-28 | 2010-06-02 | エルピーダメモリ株式会社 | Semiconductor memory device |

| KR20080065100A (en) | 2007-01-08 | 2008-07-11 | 주식회사 하이닉스반도체 | Semiconductor memory device and operation method thereof |

| KR101094946B1 (en) | 2010-01-29 | 2011-12-15 | 주식회사 하이닉스반도체 | Semiconductor Integrated Circuit |

| JP2013206492A (en) * | 2012-03-27 | 2013-10-07 | Toshiba Corp | Semiconductor device and driving method thereof |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59180871A (en) * | 1983-03-31 | 1984-10-15 | Fujitsu Ltd | Semiconductor memory device |

| US4745577A (en) * | 1984-11-20 | 1988-05-17 | Fujitsu Limited | Semiconductor memory device with shift registers for high speed reading and writing |

| JPH0740430B2 (en) * | 1986-07-04 | 1995-05-01 | 日本電気株式会社 | Memory device |

| US5854767A (en) * | 1994-10-28 | 1998-12-29 | Matsushita Electric Industrial Co., Ltd. | Semiconductor memory device having a plurality of blocks each including a parallel/serial conversion circuit |

| JP3788867B2 (en) * | 1997-10-28 | 2006-06-21 | 株式会社東芝 | Semiconductor memory device |

| US6459393B1 (en) * | 1998-05-08 | 2002-10-01 | International Business Machines Corporation | Apparatus and method for optimized self-synchronizing serializer/deserializer/framer |

| JP2000163969A (en) * | 1998-09-16 | 2000-06-16 | Fujitsu Ltd | Semiconductor storage |

| DE19951677B4 (en) * | 1998-10-30 | 2006-04-13 | Fujitsu Ltd., Kawasaki | Semiconductor memory device |

| JP3859885B2 (en) * | 1998-11-24 | 2006-12-20 | Necエレクトロニクス株式会社 | Semiconductor memory device |

| JP4083944B2 (en) * | 1999-12-13 | 2008-04-30 | 東芝マイクロエレクトロニクス株式会社 | Semiconductor memory device |

-

2004

- 2004-05-25 DE DE102004026526A patent/DE102004026526B4/en not_active Expired - Fee Related

- 2004-05-31 JP JP2004161460A patent/JP4819325B2/en not_active Expired - Fee Related

- 2004-06-03 GB GB0412446A patent/GB2403575B/en not_active Expired - Fee Related

- 2004-06-03 TW TW093115984A patent/TWI250530B/en not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| TW200516595A (en) | 2005-05-16 |

| TWI250530B (en) | 2006-03-01 |

| DE102004026526A1 (en) | 2005-01-13 |

| GB0412446D0 (en) | 2004-07-07 |

| DE102004026526B4 (en) | 2010-09-23 |

| JP2004362756A (en) | 2004-12-24 |

| GB2403575A (en) | 2005-01-05 |

| GB2403575B (en) | 2007-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101055768B (en) | Semiconductor memory device | |

| US8509020B2 (en) | Data processing system | |

| US7966446B2 (en) | Memory system and method having point-to-point link | |

| US7054202B2 (en) | High burst rate write data paths for integrated circuit memory devices and methods of operating same | |

| KR100735024B1 (en) | An address converter of a semiconductor device and semiconductor memory device | |

| US20020105842A1 (en) | Semiconductor memory device having improved data transfer rate without providing a register for holding write data | |

| US11355180B2 (en) | Semiconductor devices and semiconductor systems including the same | |

| US8437209B2 (en) | Integrated circuit | |

| US7773448B2 (en) | Semiconductor memory device | |

| JP3177094B2 (en) | Semiconductor storage device | |

| US20020031037A1 (en) | Random access memory with divided memory banks and data read/write architecture therefor | |

| JP2010277620A (en) | Semiconductor storage device, and information processing system provided with the same, and controller | |

| JP4439033B2 (en) | Semiconductor memory device | |

| US7596049B2 (en) | Semiconductor memory device with a plurality of bank groups each having a plurality of banks sharing a global line group | |

| JP6468971B2 (en) | Semiconductor memory, memory system | |

| KR100578233B1 (en) | Variable control apparatus of data input/output in synchronous semiconductor memory device | |

| US9368175B2 (en) | Semiconductor memory device receiving multiple commands simultaneously and memory system including the same | |

| US6115321A (en) | Synchronous dynamic random access memory with four-bit data prefetch | |

| JP4819325B2 (en) | Integrated circuit device and operation method thereof | |

| JP5314640B2 (en) | Semiconductor device | |

| US20210208816A1 (en) | Processing-in-memory(pim) device | |

| US7532527B2 (en) | Semiconductor memory device | |

| KR100532444B1 (en) | Memory device implementing 2N bit prefetch scheme using N bit prefetch structure and 2N bit prefetching method and auto-precharge method | |

| JP2004362756A5 (en) | ||

| US7376041B2 (en) | Semiconductor memory device and data read and write method of the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040921 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070131 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070131 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080201 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080616 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110329 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110627 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110802 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110901 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140909 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |