JP4635147B2 - パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 - Google Patents

パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 Download PDFInfo

- Publication number

- JP4635147B2 JP4635147B2 JP2005333199A JP2005333199A JP4635147B2 JP 4635147 B2 JP4635147 B2 JP 4635147B2 JP 2005333199 A JP2005333199 A JP 2005333199A JP 2005333199 A JP2005333199 A JP 2005333199A JP 4635147 B2 JP4635147 B2 JP 4635147B2

- Authority

- JP

- Japan

- Prior art keywords

- pattern matching

- unit

- header

- circuit

- network

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Data Exchanges In Wide-Area Networks (AREA)

Description

1)検査ルールからNFAを生成して、ルール中のマッチングパターンそれぞれを集約したNFAを再生成するステップと、

2)生成したNFA中に存在する重複ステートを抽出して、仮のパターンマッチング回路を構成するステップと、

3)上記の仮のパターンマッチング回路における重複ゲートを抽出して、パターンマッチング回路を生成するステップと、

4)また、ヘッダ検査ルールからはヘッダ検査回路を、生成するステップと、

5)ヘッダ−ペイロードルールの対応表から検出判定回路を生成するステップと、

6)生成したパターンマッチング回路とヘッダ検査回路と検出判定回路とを、上記の再構成可能な半導体集積回路に書き込む、というものである。

1)ネットワークインタフェースを通じて入力したネットワークストリームからネットワークフレームを抽出するステップと、

2)ネットワークフレームの種別を解析してヘッダとペイロードに分離するステップと、

3)上記の分離したヘッダとペイロードとを、それぞれヘッダ検査部、パターンマッチング部に入力するステップと、

4)上記のヘッダ検査部、パターンマッチング部で各々検出された結果を、検出判定部でルールに合致するかどうか判断するステップと、

5)上記のルールに合致する場合は、検出結果を整形し外部に出力するステップと、を含み、上記のパターンマッチング部は請求項1のパターンマッチング装置で構成したものである。

侵入防止システムに請求項1に記載のパターンマッチング装置を用いる方法で、

1)ネットワークインタフェースより入力されたネットワークストリームからネットワークフレームを抽出するステップと、

2)ネットワークフレームをヘッダ・ペイロード分離部とディレイ部とにそれぞれ複製して入力するステップと、

3)ヘッダ・ペイロード部によりネットワークフレームの種別を解析してヘッダとペイロードに分離し、それぞれヘッダ検査部、パターンマッチング部に入力するステップと、

4)ヘッダ部、パターンマッチング部で各々検出された結果を検出判定部でルールに合致するかどうか判断するステップと、

5)上記のルールに合致する場合は、選択されたルールをメモリ上に一時的に蓄積するステップと、

6)ディレイ部からネットワークフレームが出力される際に、対応する既に算出した検査結果をメモリより読み出すステップと、

7)上記の検査結果に従ってネットワークフレームを遮断するか出力するか決定するステップと、を含み、

上記のパターンマッチング部は上記のパターンマッチング装置で構成したものである。

1)攻撃あるいは侵入パケットを検出するルールを入力すると、

2)ネットワークフレーム中のヘッダを検査するルールとペイロードを検査するルール(マッチングパターン)、そしてヘッダルールとペイロードルールを対応付ける表の3つに分離する。

3)ペイロード検査ルールからはNFAを生成し、ルール中のマッチングパターンそれぞれを集約したNFAを再生成する。

4)そして、生成したNFA中に存在する重複ステートを抽出し、

5)仮のパターンマッチング回路を構成後、

6)さらに重複ゲートを抽出して、パターンマッチング回路を生成する。

7)また、ヘッダ検査ルールからはヘッダ検査回路、ヘッダ−ペイロードルールの対応表からは検出判定回路を生成する。

本装置では、入力した攻撃・侵入ルールからサブセットのルールを生成し回路化することもできる。また、回路が処理するデータ幅を指定することができ、容易に高いスループットを持つ回路を生成することもできる。

1)まずネットワークIF(インタフェース)より入力されたネットワークストリームからネットワークフレームを抽出する。

2)そして、ネットワークフレームの種別を解析してヘッダとペイロードに分離し、

3)それぞれヘッダ検査部、パターンマッチング部に入力する。

4)ヘッダ部、パターンマッチング部で各々検出された結果を検出判定部でルールに合致するかどうか判断する。

5)1つのネットワークフレームが複数のルールに合致する場合は、プライオリティエンコーダにより重要なルールが選択される。最後に結果を整形し外部に出力する。

2)ネットワークフレームはヘッダ・ペイロード分離部とディレイ部にそれぞれ複製されて入力される。

3)そして、ヘッダ・ペイロード部によりネットワークフレームの種別を解析してヘッダとペイロードに分離し、

4)それぞれヘッダ検査部、パターンマッチング部に入力する。

5)ヘッダ部、パターンマッチング部で各々検出された結果を検出判定部でルールに合致するかどうか判断する。1つのネットワークフレームが複数のルールに合致する場合は、プライオリティエンコーダにより重要なルールが選択される。選択されたルールはメモリ上に一時的に蓄積される。

6)最後に、ディレイ部からネットワークフレームが出力される際に、対応する既に算出した検査結果をメモリより読み出される。

7)このとき、検査結果に従ってネットワークフレームを遮断するか出力するか決定する。

2 ANDゲート

3 ORゲート

4 単位ステートマシン

5 ルール解析部

6 分離部

7 NFA生成部

8 ヘッダ検査回路生成部

9 重複ステート・重複ゲート抽出部

10 検出判定回路生成部

11 パターンマッチング回路生成部

12 再構成部

Claims (4)

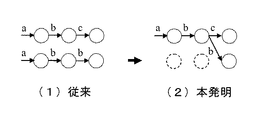

- 複数の入力信号の積をとる演算回路と、前記演算回路の演算結果を予め決められた時間保持する保持回路と、からなる単位ステートマシンを複数備えるNFAステートマシンと、

伝送された符号と、探索する符号と、の比較を行なう比較器と、

を含み、

前記の演算回路は、初段では予め決められた論理値の出力、あるいは、それ以降の段では前段の単位ステートマシンの出力と、上記の比較器の出力との積をとり、予め決められた段から探索結果を出力するものであって、

複数の単位ステートマシンが出力端まで直列接続された少なくともひとつの構成Aと、

上記の直列接続の中間点から分岐し、他の出力端まで接続された構成Bと、をもち、

上記の分岐点の位置を、該分岐点の前段では、構成Aと構成Bとの行なう探索が共通の探索であるように定めたことを特徴とするパターンマッチング装置。 - 再構成可能な半導体集積回路上のステートマシンを用いたパターンマッチング装置の形成方法で、

1)検査ルールからNFAを生成して、ルール中のマッチングパターンそれぞれを集約したNFAを再生成するステップと、

2)生成したNFA中に存在する重複ステートを抽出して、仮のパターンマッチング回路を構成するステップと、

3)上記の仮のパターンマッチング回路における重複ゲートを抽出して、パターンマッチング回路を生成するステップと、

4)また、ヘッダ検査ルールからはヘッダ検査回路を、生成するステップと、

5)ヘッダ−ペイロードルールの対応表から検出判定回路を生成するステップと、

6)生成したパターンマッチング回路とヘッダ検査回路と検出判定回路とを、上記の再構成可能な半導体集積回路に書き込むことを特徴とする請求項1に記載のパターンマッチング装置の形成方法。 - ネットワークインタフェース部と、ネットワークフレーム抽出部と、ヘッダ・ペイロード分離部と、ヘッダ検査部と、パターンマッチング部とに入力するステップと、パターンマッチング部と、検出判定部とを備えるネットワーク不正侵入検知装置の動作方法で、

1)ネットワークインタフェースを通じて入力したネットワークストリームからネットワークフレームを抽出するステップと、

2)ネットワークフレームの種別を解析してヘッダとペイロードに分離するステップと、

3)上記の分離したヘッダとペイロードとを、それぞれヘッダ検査部、パターンマッチング部に入力するステップと、

4)上記のヘッダ検査部、パターンマッチング部で各々検出された結果を、検出判定部でルールに合致するかどうか判断するステップと、

5)上記のルールに合致する場合は、検出結果を整形し外部に出力するステップと、を含み、

上記のパターンマッチング部は請求項1のパターンマッチング装置で構成されていることを特徴とするネットワーク不正侵入検知装置の動作方法。 - ネットワークインタフェース部と、ネットワークフレーム抽出部と、ヘッダ・ペイロード分離部と、ヘッダ検査部と、パターンマッチング部とに入力するステップと、パターンマッチング部と、検出判定部と、フレーム遮断・出力部とを備える侵入防止システムの動作方法で、

侵入防止システムに請求項1に記載のパターンマッチング装置を用いる方法で、

1)ネットワークインタフェースより入力されたネットワークストリームからネットワークフレームを抽出するステップと、

2)ネットワークフレームをヘッダ・ペイロード分離部とディレイ部とにそれぞれ複製して入力するステップと、

3)ヘッダ・ペイロード部によりネットワークフレームの種別を解析してヘッダとペイロードに分離し、それぞれヘッダ検査部、パターンマッチング部に入力するステップと、

4)ヘッダ部、パターンマッチング部で各々検出された結果を検出判定部でルールに合致するかどうか判断するステップと、

5)上記のルールに合致する場合は、選択されたルールをメモリ上に一時的に蓄積するステップと、

6)ディレイ部からネットワークフレームが出力される際に、対応する既に算出した検査結果をメモリより読み出すステップと、

7)上記の検査結果に従ってネットワークフレームを遮断するか出力するか決定するステップと、を含み、

上記のパターンマッチング部は請求項1のパターンマッチング装置で構成されていることを特徴とする侵入防止システムの動作方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005333199A JP4635147B2 (ja) | 2005-11-17 | 2005-11-17 | パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005333199A JP4635147B2 (ja) | 2005-11-17 | 2005-11-17 | パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007142767A JP2007142767A (ja) | 2007-06-07 |

| JP4635147B2 true JP4635147B2 (ja) | 2011-02-16 |

Family

ID=38205104

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005333199A Expired - Lifetime JP4635147B2 (ja) | 2005-11-17 | 2005-11-17 | パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635147B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104135730A (zh) * | 2014-07-22 | 2014-11-05 | 西南大学 | 一种基于压缩感知的无线网络的物理层入侵检测方法 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5120263B2 (ja) * | 2007-01-12 | 2013-01-16 | 日本電気株式会社 | パターンマッチング装置及び方法 |

| JP4957500B2 (ja) * | 2007-10-12 | 2012-06-20 | 日本電気株式会社 | 文字列照合回路 |

| JP5327315B2 (ja) * | 2009-03-17 | 2013-10-30 | 日本電気株式会社 | イベント処理システム、イベント処理方法、ルール分配装置、及びプログラム記憶媒体 |

| JP5327314B2 (ja) * | 2009-03-17 | 2013-10-30 | 日本電気株式会社 | イベント処理システム、イベント処理方法、ローカルシステム、ディスパッチャ、及びプログラム記憶媒体 |

| JP5494935B2 (ja) * | 2009-10-30 | 2014-05-21 | 日本電気株式会社 | Nfa回路 |

| US8766666B2 (en) | 2010-06-10 | 2014-07-01 | Micron Technology, Inc. | Programmable device, hierarchical parallel machines, and methods for providing state information |

| KR102045702B1 (ko) * | 2019-05-03 | 2019-11-15 | 한국과학기술원 | 심층 패킷 분석에서 정규 표현식 매칭 방법 및 그 장치 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7093023B2 (en) * | 2002-05-21 | 2006-08-15 | Washington University | Methods, systems, and devices using reprogrammable hardware for high-speed processing of streaming data to find a redefinable pattern and respond thereto |

-

2005

- 2005-11-17 JP JP2005333199A patent/JP4635147B2/ja not_active Expired - Lifetime

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104135730A (zh) * | 2014-07-22 | 2014-11-05 | 西南大学 | 一种基于压缩感知的无线网络的物理层入侵检测方法 |

| CN104135730B (zh) * | 2014-07-22 | 2017-10-13 | 西南大学 | 一种基于压缩感知的无线网络的物理层入侵检测方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007142767A (ja) | 2007-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102075511B (zh) | 一种数据匹配设备和方法以及网络入侵检测设备和方法 | |

| Cho et al. | Deep packet filter with dedicated logic and read only memories | |

| Elnawawy et al. | FPGA-based network traffic classification using machine learning | |

| Yang et al. | High-performance and compact architecture for regular expression matching on FPGA | |

| Le et al. | A memory-efficient and modular approach for large-scale string pattern matching | |

| CN109474641B (zh) | 一种可破坏硬件木马的可重构交换机转发引擎解析器 | |

| US20100161536A1 (en) | Pattern matching | |

| Yu et al. | Revisiting state blow-up: Automatically building augmented-fa while preserving functional equivalence | |

| JP4635147B2 (ja) | パターンマッチング装置、その形成方法、それを用いたネットワーク不正侵入検知装置の動作方法、およびそれを用いた侵入防止システムの動作方法 | |

| Xu et al. | BGP anomaly detection based on automatic feature extraction by neural network | |

| Yang et al. | PiDFA: A practical multi-stride regular expression matching engine based on FPGA | |

| CN102201948A (zh) | 用于网络入侵检测系统的快速匹配方法 | |

| Aldwairi et al. | Efficient Wu-Manber pattern matching hardware for intrusion and malware detection | |

| Gardner et al. | Pattern discovery and specification techniques for alarm correlation | |

| Suresh et al. | Efficient pattern matching algorithm for security and Binary Search Tree (BST) based memory system in Wireless Intrusion Detection System (WIDS) | |

| Lin et al. | Efficient pattern matching algorithm for memory architecture | |

| Gong et al. | GoldenEye: stream-based network packet inspection using GPUs | |

| CN119155128A (zh) | 金融云数据中心加密隧道通信检测的方法及装置 | |

| KR101276796B1 (ko) | 패턴 매칭 장치 및 방법 | |

| TW202018566A (zh) | 資訊處理裝置、資訊處理方法及資訊處理程式產品 | |

| Weng et al. | Deep packet pre-filtering and finite state encoding for adaptive intrusion detection system | |

| Antonello et al. | Characterizing signature sets for testing DPI systems | |

| CN103957131A (zh) | 一种基于有限自动机的深度报文检测方法 | |

| Lacroix et al. | Node configuration for the Aho-Corasick algorithm in intrusion detection systems | |

| JP6096084B2 (ja) | トラヒック走査装置及び方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100408 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101005 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101018 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635147 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |